# A VOLTAGE SAG SUPPORTER UTILIZING A PWM-SWITCHED AUTOTRANSFORMER

A Thesis Presented to The Academic Faculty

by

Dong-Myung Lee

In Partial Fulfillment of the Requirements for the Degree

Doctor of Philosophy In Electrical Engineering

School of Electrical & Computer Engineering

Georgia Institute of Technology

Atlanta, GA 30332-0250

April 2004

# A VOLTAGE SAG SUPPORTER UTILIZING A PWM-SWITCHED AUTOTRANSFORMER

| Approved:                        |

|----------------------------------|

| Dr. Thomas G. Habetler, Chairman |

| Dr. Ronald G. Harley             |

| Dr. A.P. Sakis Meliopoulos       |

|                                  |

Date Approved: <u>April 8, 2004</u>

To My Parents,

My Loving Wife, Joo-Youn,

And My Daughters, Do-Young and Do-Yun.

#### **ACKNOWLEDGEMENT**

Without the involvement and support of many people in my studies, it would not have been possible for me to complete this work.

I would like to express my gratitude to my adviser Dr. Thomas G. Habetler for his support, help, and guidance. I have benefited tremendously from his knowledge and experience in the fields of power electronics, and machine drives.

I am extremely grateful to Dr. Ronald G. Harley for his invaluable inputs and guidance throughout the project.

I would like to thank Dr. A.P. Sakis Meliopoulos, Dr. David G. Taylor, and Dr. Stephen L. Dickerson for their time and for serving on my thesis committee.

I would like to acknowledge Southern State Inc. (SSI) for financial support to conduct this research.

I really express my gratitude to Mr. Joe Rostron of SSI for his wise technical suggestion and enthusiasm for this research work.

I am indebted to Mr. Tom Keister of JSL, Inc. for his invaluable hardware work, and for his help during various stages of the project. Without his endless, much of this work would not have been completed.

I wish to thank my colleagues, Dr. Sang-Bin Lee, Dr. Jung-Wook Park, Jae-Hyeong Seo, Young-Kook Lee, Xianghui Huang, Satish Rajagopalan, Salman Mohagheghi, Zhi Gao, Jahagirdar Deepak, and Afroz Imam for their help.

I would like to express my thanks to Jin-Woo Jung, Tae-Hyeong Kim, Hyun-Soo Kang, and Hee-Sung Moon for their encouragement and support.

I am deeply indebted to my wife, and my daughters for their love, caring, and understanding. Without their love and support, this journey would have been much harder.

I would like to express my sincere gratitude to my wife's parents, my brother-in-law, and my sister-in-law for their love, and support.

I am eternally grateful to my parents, my brother, and my sister for being a constant source of encouragement and motivation throughout my life.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENT                                                 | iv |

|-----------------------------------------------------------------|----|

| TABLE OF CONTENTS                                               | vi |

| LIST OF TABLES                                                  | X  |

| LIST OF FIGURES                                                 | xi |

| SUMMARY                                                         | XV |

| CHAPTER 1                                                       | 1  |

| INTRODUCTION                                                    |    |

| 1.1 Background                                                  | 1  |

| 1.2 Problem Statement                                           | 2  |

| 1.3 Thesis Outline                                              | 5  |

| CHAPTER 2                                                       | 7  |

| PREVIOUS WORK ON VOLTAGE SAG AND VOLTAGE SAG MITIGATION DEVICES |    |

| 2.1 Power Quality Surveys                                       | 7  |

| 2.2 Voltage Sag                                                 | 9  |

| 2.2.1 Causes of Voltage Sags                                    | 9  |

| 2.2.2 Sensitivity of Voltage Sags                               | 11 |

| 2.3. Voltage Sag Mitigation Devices                             | 14 |

| 2.3.1 Tap Changers                                              | 14 |

| 2.3.2 Flexible AC Transmission Systems (FACTS) Devices          | 15 |

| 2.3.2.a Series Compensation Method                              | 17 |

| 2.3.2.b Shunt Compensation Method                               | 19 |

| 2.3.2.c Combined Compensator                                    | 21 |

| 2.4 AC Converters                                               | 23 |

| 2.5 Modified Scheme                                                    | 25         |

|------------------------------------------------------------------------|------------|

| 2.6 Chapter Summary                                                    | 25         |

| CHAPTER 3                                                              | 27         |

| SELECTION OF VOLTAGE SAG MITIGATION TOPOLOGY                           |            |

| 3.1 Selection of Compensation Method                                   | 27         |

| 3.1.1 Comparisons between Series type and Shunt type Compensation      | 29         |

| 3.2 Configuration of the Proposed System                               | 31         |

| 3.3 Comparison of the Voltage Magnitude of Series type and Shunt type. | 33         |

| 3.3.1 Bridge Configuration                                             | 34         |

| 3.3.2 Entire System Configuration                                      | 35         |

| 3.3.3 Voltage Distribution during Lightning Surge                      | 36         |

| 3.4 Chapter Summary                                                    | 47         |

| CHAPTER 4                                                              | 48         |

| DESIGN OF SYSTEM                                                       |            |

| 4.1 Voltage Detection Methods                                          | 48         |

| 4.1.1 DQ Transformation for Voltage Detection                          | 49         |

| 4.1.2 Peak Voltage Detection Method                                    | 53         |

| 4.2 Voltage Controller                                                 | 57         |

| 4.3. Snubber Design                                                    | 59         |

| 4.3.1 Role of Snubber                                                  | 59         |

| 4.3.2 Selection of the RC values                                       | 60         |

| 4.3.3 Equivalent Circuit during IGBT turn-off                          | 64         |

| 4.4 Design of Output Filters                                           | 68         |

| 4.5 Thyristor Commutation Scheme                                       | 71         |

| 4.5.1 Thyristor Commutation Logic using Thyristor Current and Input    | ut Voltage |

|                                                                        | 71         |

| 4.5.2 Thyristor Commutation Logic using Input Current and Input Vol    | tage 75    |

| 4.6 Simulation Results                                                    | 77     |

|---------------------------------------------------------------------------|--------|

| 4.7 Chapter Summary                                                       | 80     |

| CHAPTER 5                                                                 | 82     |

| FAILURE DETECTION AND PROTECTION LOGIC                                    |        |

| 5.1 Gate Signals                                                          | 82     |

| 5.2 Faults in IGBT Switching Block                                        | 84     |

| 5.2.1 Summary of Possible Failures and Detection Method related to IGBT   | -<br>- |

| Switch Block                                                              | 84     |

| 5.2.2 Procedure after Detecting Faults related to the IGBT Switch Block   | 86     |

| 5.3 Faults in Thyristor Switch Block                                      | 86     |

| 5.3.1 Summary of Possible Failures and Detection Method related to Thyri  |        |

| Switch Block                                                              | 87     |

| 5.3.2 Procedure after Fault Detection in Thyristor Gate Driver            | 88     |

| 5.3.3 Faults in Components                                                | 89     |

| 5.4 Fault Detection Logic                                                 | 97     |

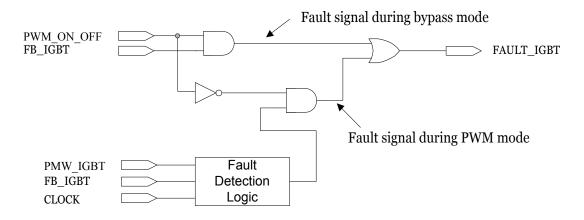

| 5.4.1 Detection Logic for the IGBT using Signals from its Gate Driver     | 100    |

| 5.4.2 Fault Detection Logic for the Thyristor using Signals from its Gate | Driver |

|                                                                           | 103    |

| 5.4.3 Fault Detection Logic for Reed Relay Circuit                        | 106    |

| 5.5 Chapter Summary                                                       | 107    |

| CHAPTER 6                                                                 | 109    |

| EXPERIMENTAL VALIDATIONS                                                  |        |

| 6.1 Experimental Setup                                                    | 109    |

| 6.2 Voltage Sag Generator                                                 | 114    |

| 6.3 Control Board                                                         | 115    |

| 6.4 Switch Blocks                                                         | 119    |

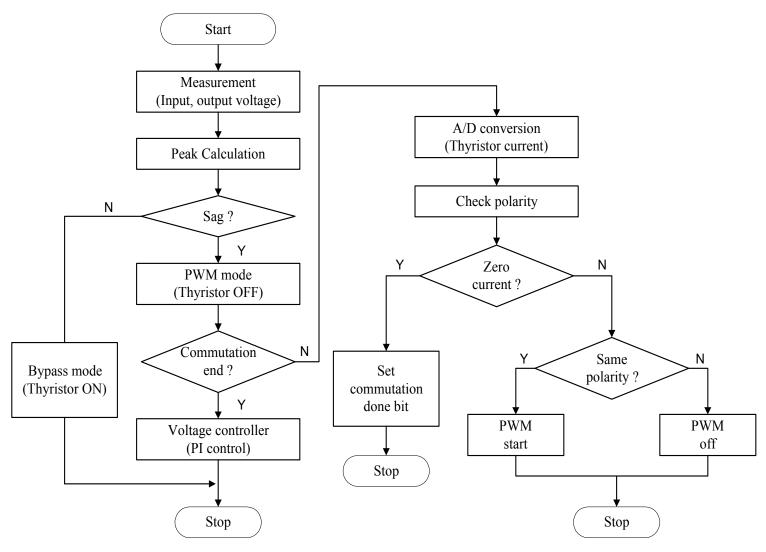

| 6.5 Control Program Software                                              | 122    |

|    | 6.6 Experimental Results                     | 127  |

|----|----------------------------------------------|------|

|    | 6.7 Chapter Summary                          | 131  |

| CI | HAPTER 7                                     | 132  |

|    | CONCULSIONS AND RECOMMENDATIONS FOR FUTURE V | VORK |

|    | 7.1 Conclusions                              | 132  |

|    | 7.2 Contributions                            | 135  |

|    | 7.3 Recommendations for Future Research      | 137  |

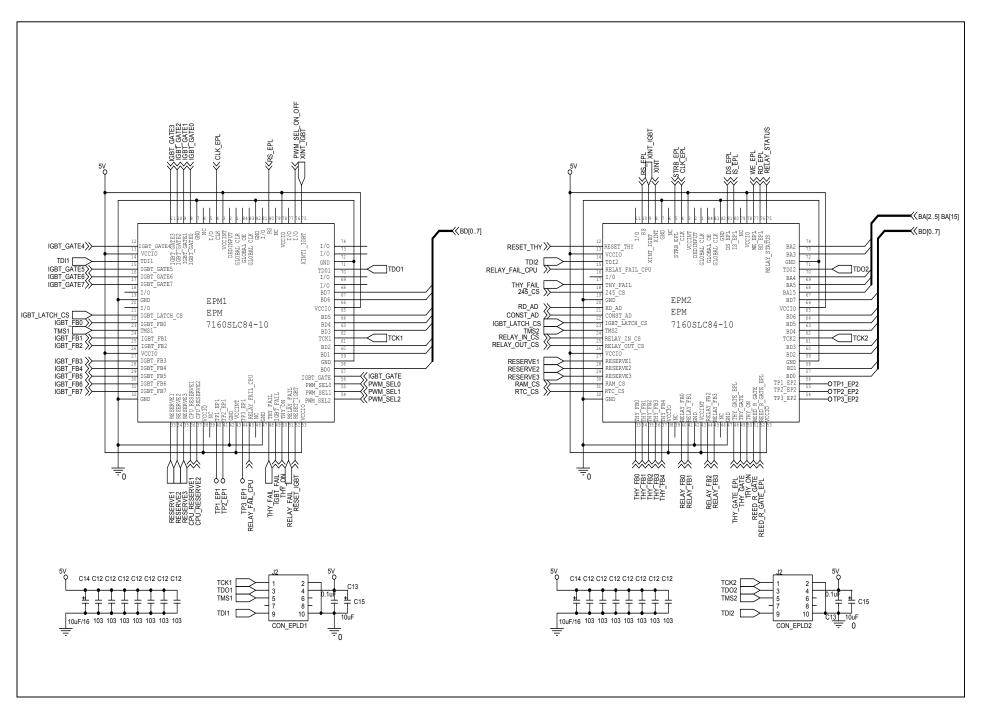

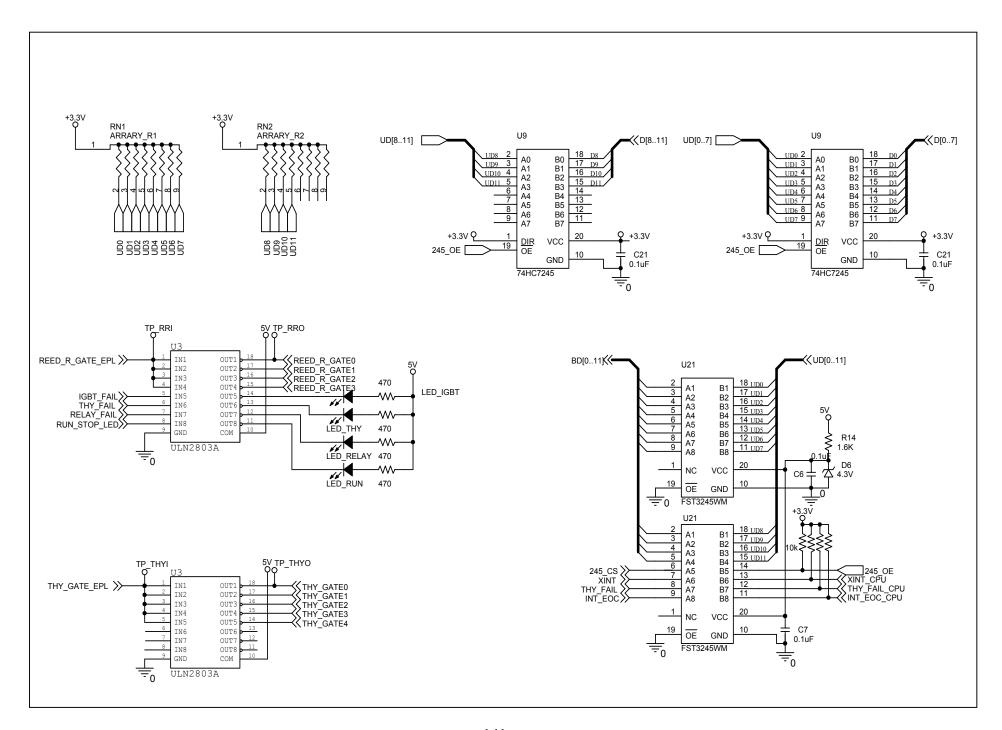

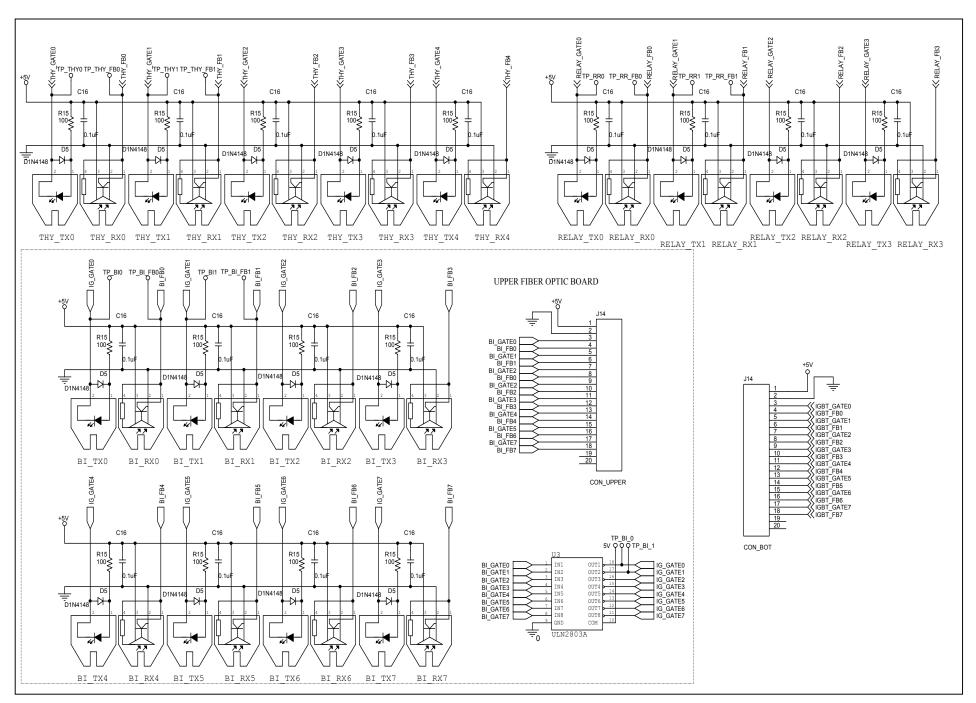

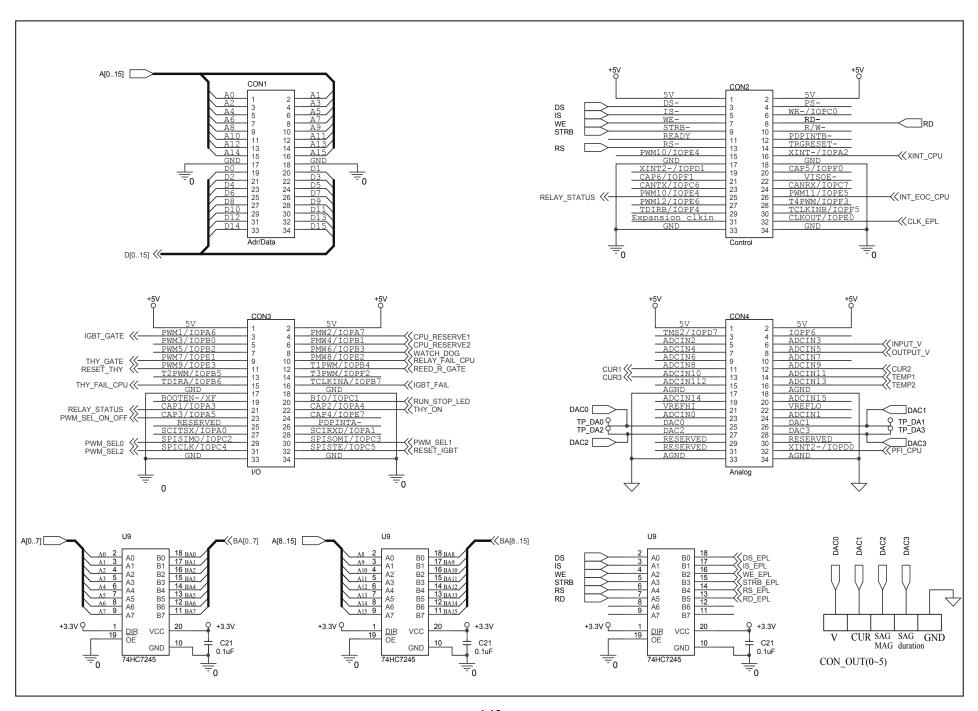

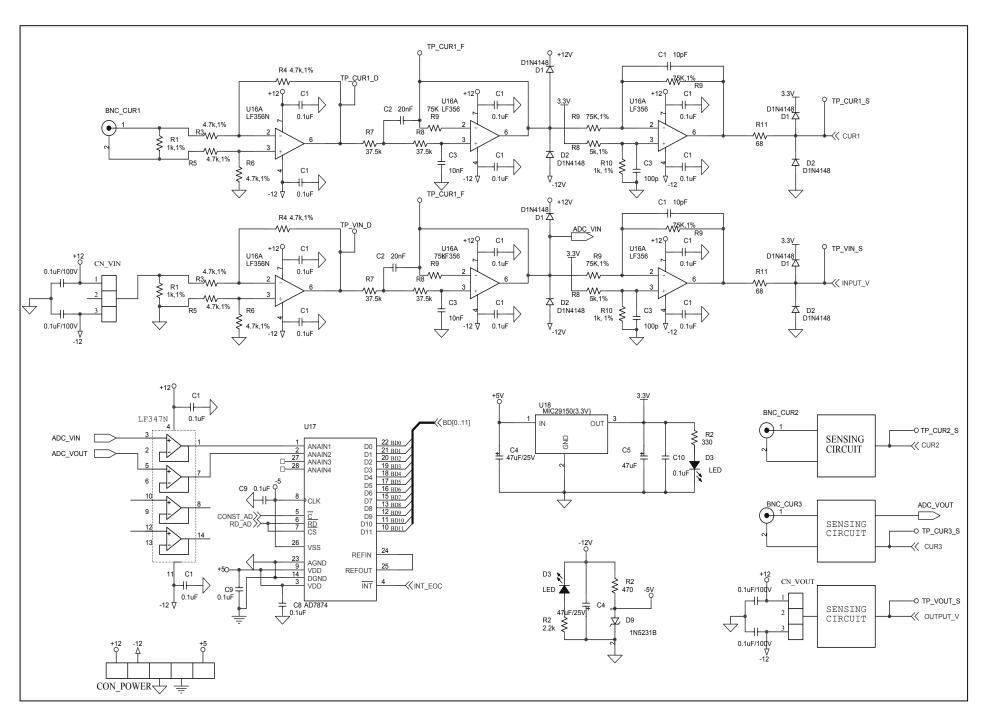

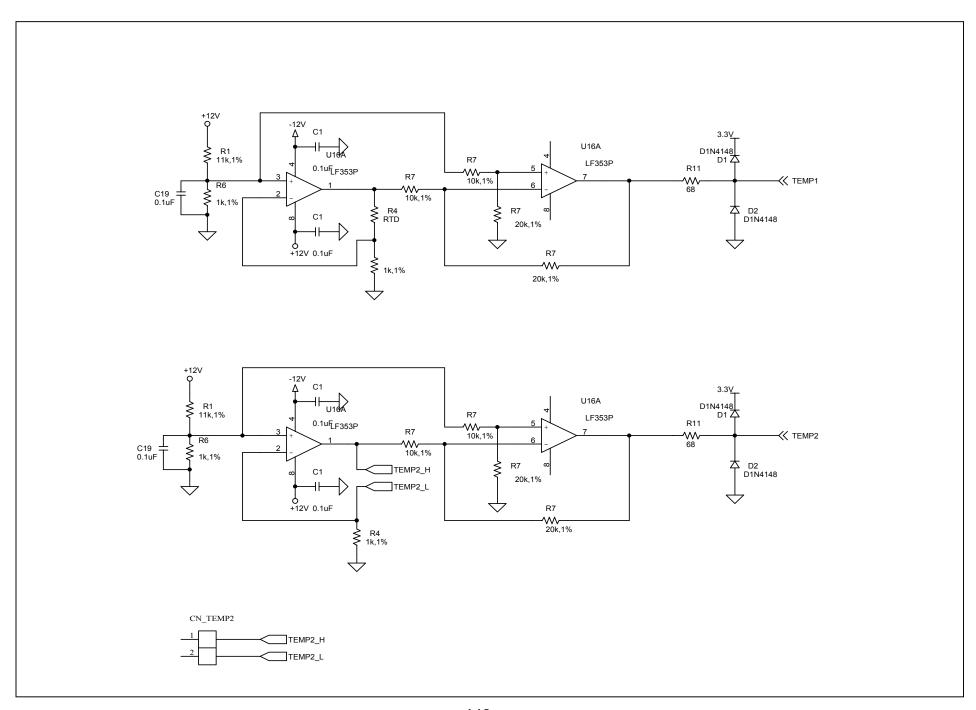

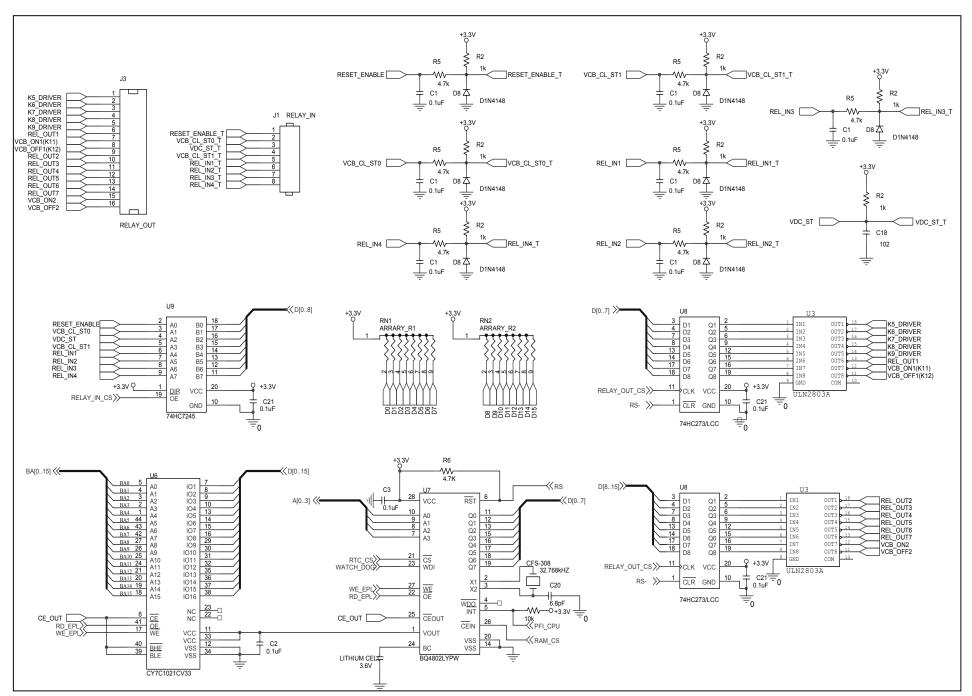

| Al | PPENDIX                                      | 139  |

|    | SCHEMATIC OF THE CONTROL BOARD               |      |

| RI | EFERENCES                                    | 147  |

| VI | IT A                                         | 153  |

### LIST OF TABLES

| Table 2.1 | Summary of the CEA, NPL, and EPRI power quality survey9                      |

|-----------|------------------------------------------------------------------------------|

| Table 2.2 | Recommended voltage for semiconductor industry                               |

| Table 2.3 | Voltage tolerance ranges of equipment                                        |

| Table 3.1 | System parameters used in the lightning surge simulations                    |

| Table 4.1 | Parameters of the system                                                     |

| Table 5.1 | Summary of possible failures and detection method related to IGBT switch     |

|           | block91                                                                      |

| Table 5.2 | Summary of possible failures and detection method related to thyristor block |

|           | 93                                                                           |

| Table 5.3 | Summary of possible failures and detection method related to sensors and     |

|           | control board                                                                |

| Table 6.1 | Specifications of power devices used in experiments                          |

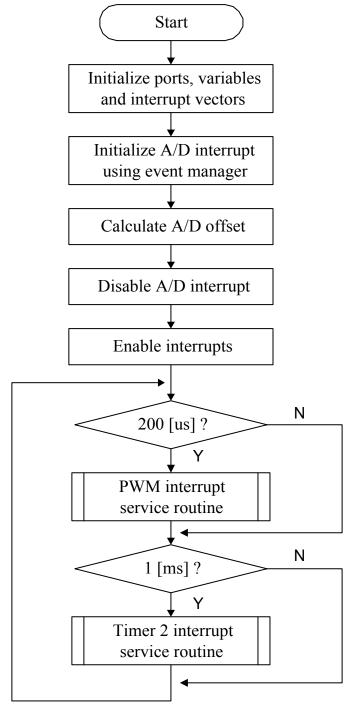

| Table 6.2 | Overview of function of interrupts                                           |

## LIST OF FIGURES

| Figure 2.1.  | A shape of voltage sag due to SLG fault                                  | 11 |

|--------------|--------------------------------------------------------------------------|----|

| Figure 2.2.  | Voltage divider model for a voltage sag event                            | 11 |

| Figure 2.3.  | The ITIC curve                                                           | 12 |

| Figure 2.4.  | Thyristor tap changer using two thyristor pairs                          | 15 |

| Figure 2.5.  | Output voltage waveforms of thyristor tap changer                        | 15 |

| Figure 2.6.  | Configuration of a dynamic voltage restorer                              | 18 |

| Figure 2.7.  | Schematic of a D-STATCOM                                                 | 21 |

| Figure 2.8.  | Configuration of a UPFC.                                                 | 22 |

| Figure 2.9.  | AC converter topologies                                                  | 24 |

| Figure 2.10. | Voltage regulation scheme using an AC converter                          | 24 |

| Figure 2.11. | Single phase DySC topology                                               | 25 |

| Figure 3.1.  | Shunt type and series type compensators                                  | 28 |

| Figure 3.2.  | Voltage and current relation in an autotransformer                       | 31 |

| Figure 3.3.  | Basic configuration of the proposed voltage compensation scheme          | 33 |

| Figure 3.4.  | AC Switch with IGBT and snubber in bridge configuration                  | 34 |

| Figure 3.5.  | Overall system configuration showing serially connected switches         | 36 |

| Figure 3.6.  | Lightening surge voltage waveforms having 1.2 / 200 $\mu s$ with 140kV ? | 39 |

| Figure 3.7.  | Equivalent circuit for lightning surge simulations                       | 44 |

| Figure 3.8.  | Voltage waveforms across one IGBT switch block of the lightning sur      | ge |

|              | during bypass mode (thyristor on, IGBT off)                              | 45 |

| Figure 3.9.  | (a) Voltage waveforms across one thyristor block without MOV across t    | he |

|              | branch during PWM mode with IGBT ON, (b) Voltage waveforms acro          | SS |

|              | one thyristor block with MOV across it                                   | 45 |

| Figure 3.10. | Voltage waveforms across one IGBT switch block for the lightning sur     | ge |

|              | during PWM mode with IGBT OFF (from the top-downwards volta              | ge |

|              | across IGBT and thyristor)                                               | 46 |

| Figure 3.11. | Voltage waveforms across one IGBT switch block of the lightning surge                                             |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------|--|--|

|              | during PWM mode (IGBT OFF) with MOV across thyristor (from the top-                                               |  |  |

|              | downwards voltage across IGBT and thyristor)                                                                      |  |  |

| Figure 4.1.  | The result of DQ transformation of balance three-phase voltage                                                    |  |  |

| Figure 4.2.  | Resulting values of DQ transformation of unbalance three-phase voltage                                            |  |  |

|              | 51                                                                                                                |  |  |

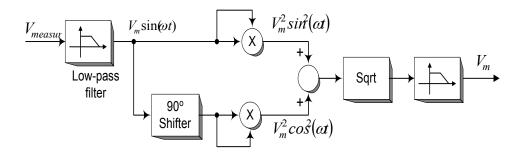

| Figure 4.3.  | Voltage measurement using the peak detection method                                                               |  |  |

| Figure 4.4.  | Measured voltage waveforms using the peak detection method 55                                                     |  |  |

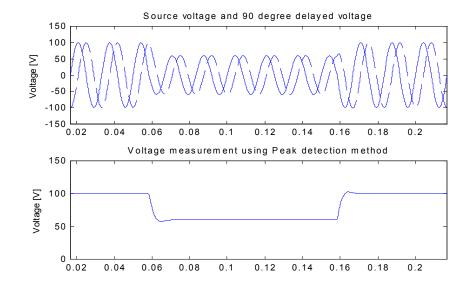

| Figure 4.5.  | Comparison of voltage detection time for various detection methods 57                                             |  |  |

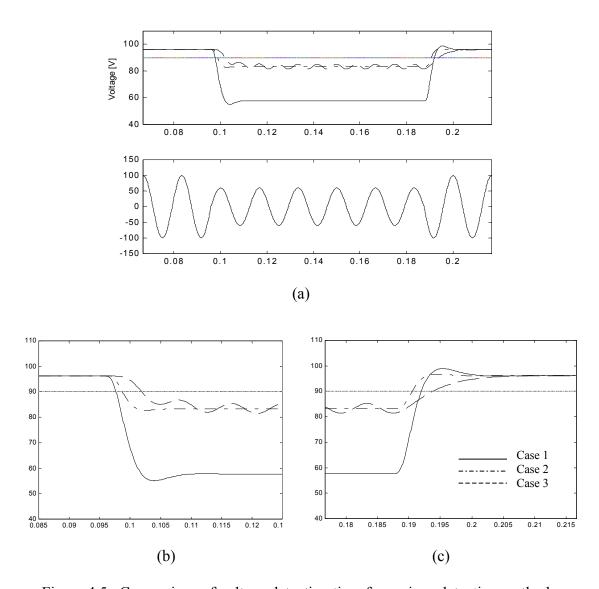

| Figure 4.6.  | Output voltage controller based on PI controller                                                                  |  |  |

| Figure 4.7.  | Simplified diagram of the shunt voltage compensator                                                               |  |  |

| Figure 4.8.  | Equivalent circuit diagram during the IGBT is off                                                                 |  |  |

| Figure 4.9.  | Simplified equivalent circuit during IGBT turn-off showing equivalent                                             |  |  |

|              | parameters 65                                                                                                     |  |  |

| Figure 4.10. | Voltage across the IGBT using parameters of R <sub>S</sub> =7 $\Omega$ , C <sub>S</sub> =20 $\mu$ F, $L_s$ =10mH, |  |  |

|              | and $L_1 = L_2 = 20 \text{mH}$                                                                                    |  |  |

| Figure 4.11. | Equivalent circuit for selecting filter values                                                                    |  |  |

| Figure 4.12. | Bode diagrams: (a) notch filter and (b) system having the notch filter and                                        |  |  |

|              | capacitor filter71                                                                                                |  |  |

| Figure 4.13. | Commutation scheme showing the positive thyristor current                                                         |  |  |

| Figure 4.14. | Thyristor commutation scheme for four different cases (from the top-                                              |  |  |

|              | downwards IGBT gate signal, thyristor gated signal, thyristor current,                                            |  |  |

|              | input voltage, and load voltage)74                                                                                |  |  |

| Figure 4.15. | Showing the relation of the input current and the thyristor current to use                                        |  |  |

|              | the input current for the thyristor commutation logic                                                             |  |  |

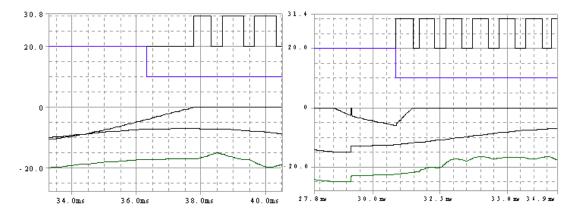

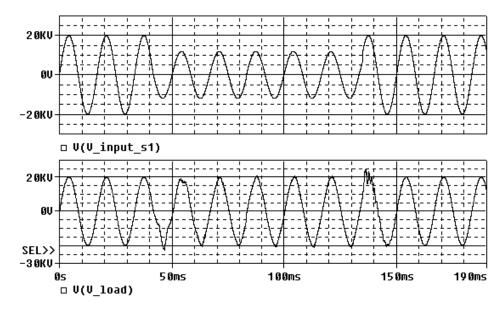

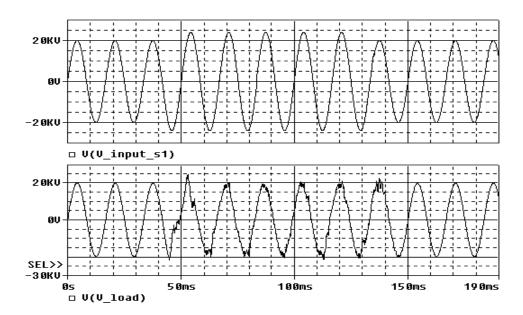

| Figure 4.16. | Output voltage waveform when the input voltage has 20% sag                                                        |  |  |

| Figure 4.17. | Output voltage waveform when the input voltage has 40% sag                                                        |  |  |

| Figure 4.18. | Output voltage waveform when the input voltage has 20% swell                                                      |  |  |

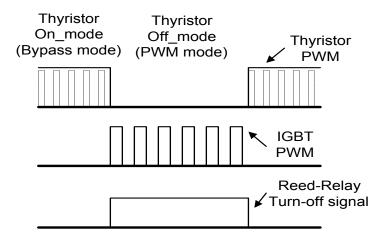

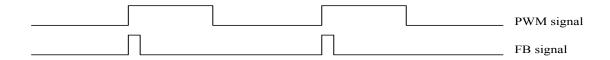

| Figure 5.1.  | Gate signals corresponding to PWM and bypass mode                           |

|--------------|-----------------------------------------------------------------------------|

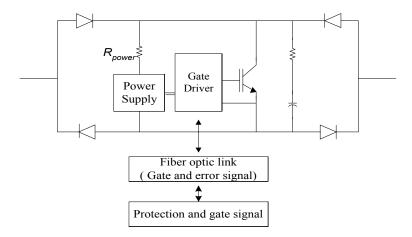

| Figure 5.2.  | IGBT switch block showing the power supply and gate driver 85               |

| Figure 5.3.  | Sensors for the purpose of control and protection                           |

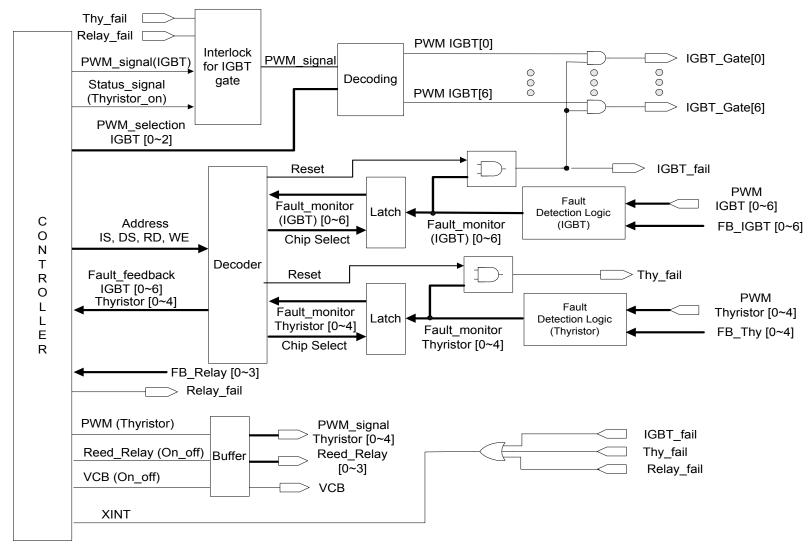

| Figure 5.4.  | Overall hardware block diagram for fault detection                          |

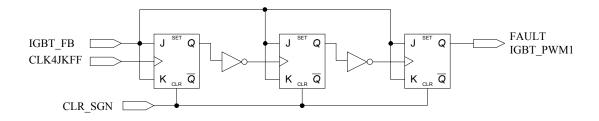

| Figure 5.5.  | Overall IGBT fault detection circuit for bypass and PWM mode 100            |

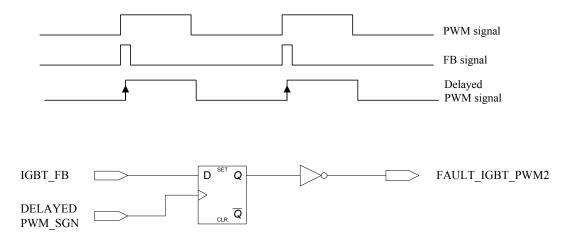

| Figure 5.6.  | The PWM signal and the FB signal having a short pulse corresponding to      |

|              | a rising edge of the PWM signal                                             |

| Figure 5.7.  | The logic circuits for checking the duration of the FB signal 102           |

| Figure 5.8.  | Logic circuit and related signals for checking the existence of the IGBT    |

|              | FB signal                                                                   |

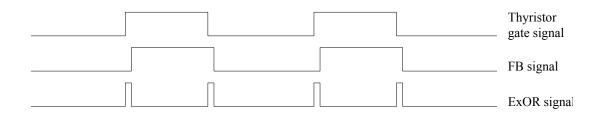

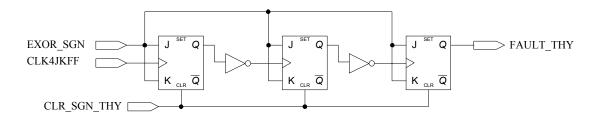

| Figure 5.9.  | The exclusive OR signal between the thyristor gate signal and its FB        |

|              | signal                                                                      |

| Figure 5.10. | Logic and logic circuit for checking faults in thyristor gate driver 105    |

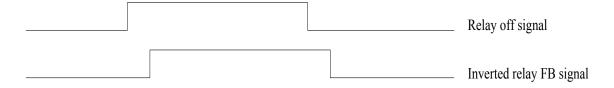

| Figure 5.11. | Reed-relay off signal and its FB signal 106                                 |

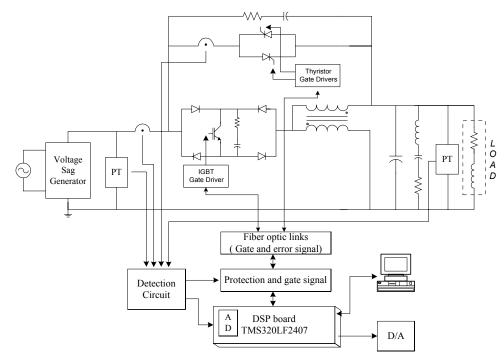

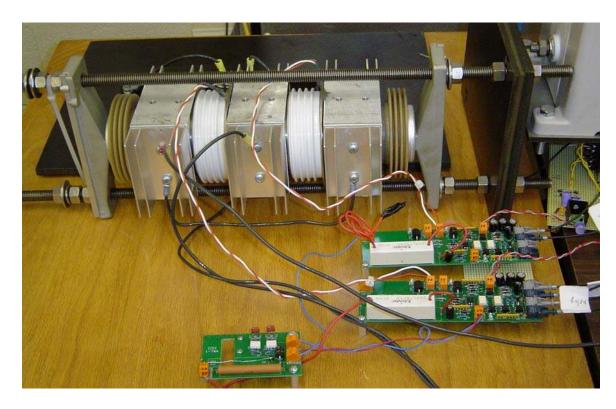

| Figure 6.1.  | Schematic of experimental setup                                             |

| Figure 6.2.  | Experimental setup using high voltage devices                               |

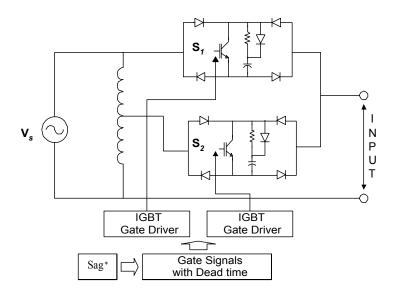

| Figure 6.3.  | A voltage sag generator using an autotransformer and IGBT switch blocks     |

|              |                                                                             |

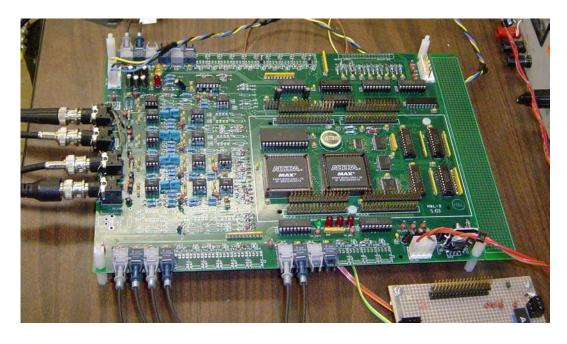

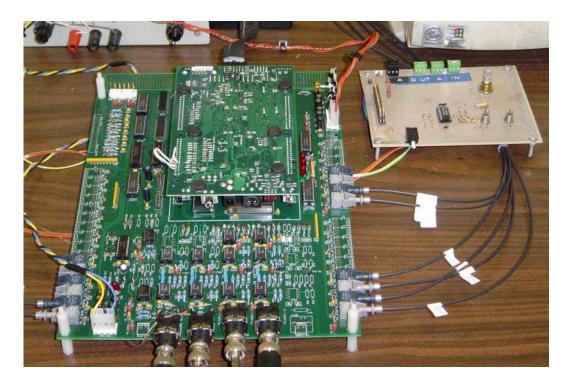

| Figure 6.4.  | The control board having sensing, logic array, and circuits for gate signal |

|              | etc                                                                         |

| Figure 6.5.  | The control board with the EVM board mounted on the top                     |

| Figure 6.6.  | IGBT switch block 121                                                       |

| Figure 6.7.  | Thyristor switch block                                                      |

| Figure 6.8.  | Flow chart of main loop                                                     |

| Figure 6.9.  | Flow chart of PWM interrupt service routine                                 |

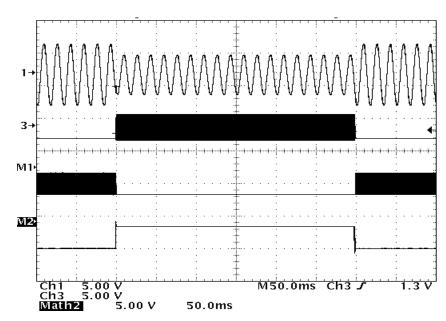

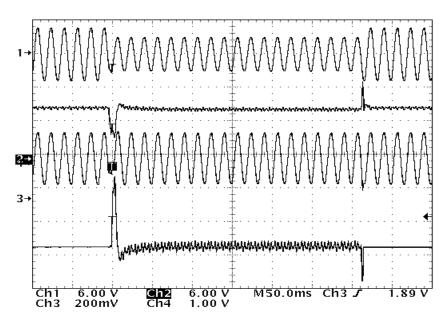

| Figure 6.10. | Gate signals corresponding to voltage sag event (from the top-downwards     |

|              | input voltage, PWM signal, Thyristor gate signal, and relay signal) 128     |

| Figure 6.11. | Thyristor current and related gate signals (from the top-downwards input    |

|              | voltage, PWM gate signal, Thyristor gate signal, and thyrsitor current)     |

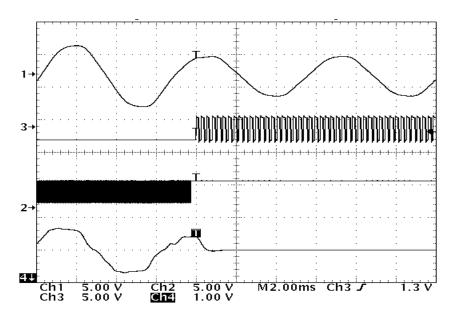

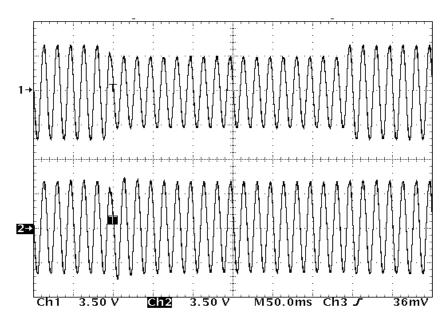

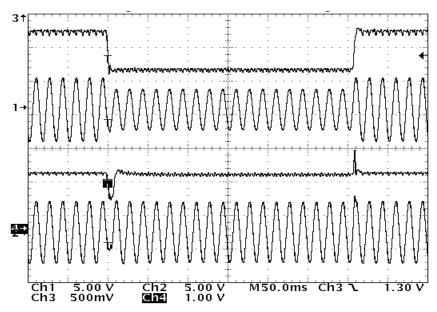

| Figure 6.12. | Output voltage and input voltage having 20% voltage sag (from the top-  |

|--------------|-------------------------------------------------------------------------|

|              | downwards input voltage, and output voltage)                            |

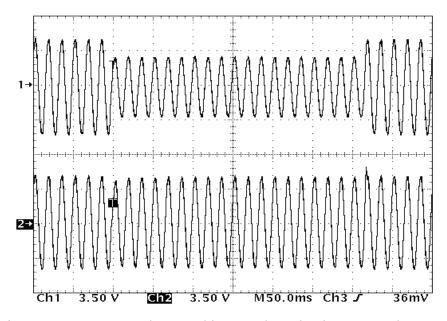

| Figure 6.13. | Output voltage and input voltage having 40% voltage sag (from the top-  |

|              | downwards input voltage, and output voltage)                            |

| Figure 6.14. | Voltage error signal and the magnitude of output voltage (from the top- |

|              | downwards input voltage, magnitude of output voltage, output voltage,   |

|              | and error of voltage magnitude)                                         |

| Figure 6.15. | Input and output voltage and its magnitude measured by peak detection   |

|              | method (from the top-downwards magnitude of input voltage, input        |

|              | voltage, magnitude of output voltage, and output voltage)               |

#### **SUMMARY**

The objective of this research is to develop a novel voltage control scheme that can compensate for voltage sag and swell conditions in three-phase power systems. Faults occurring in power distribution systems or facilities in plants cause the voltage sag or swell. If a fault occurs, it can damage the power system or user's facility. Sensitivity to voltage sags and swells varies within different applications. For sensitive loads, even voltage sags of short duration can cause serious problems in the entire system. Normally, a voltage interruption triggers a protection device, which causes shutdown of the entire system.

In order to mitigate power interruptions, this research proposes a scheme called "Voltage Sag Supporter utilizing a PWM (Pulse Width Modulation) - Switched Autotransformer." The proposed scheme is able to quickly recognize the voltage sag or swell condition, and it can correct the voltage by either boosting the input voltage during voltage sag events or reducing the input voltage during voltage swell events. Among existing methods, the scheme based on the inverter system such as dynamic voltage restorers (DVR) require an inverter, a rectifier, and a step-up down transformer, which makes the system expensive. AC converters can be used for the purpose of the research. However, they consist of two solid-state switches per one phase and include energy storage devices such as reactors and capacitors.

The switching device for the high voltage application is relatively expensive so that this research suggests a scheme utilizing only one switch for the output voltage control, which makes the system more stable and cost effective. The proposed scheme can be applied at any voltage and provides cost and size advantages over existing methods due to the reduced number of switching components and no need of energy storage devices. This research includes many design issues such as a voltage controller, a voltage detection, snubber design, and a commutation logic for thyristors. Fast fault detection is essential for the high voltage application so that fault detection logics for each switch device are devised and implemented either in hardware or software based logic. Simulations and experiments have been carried out to verify the validity of the proposed scheme, and prototype experiments are being done to confirm the control scheme.

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Background

A power distribution system is similar to a vast network of rivers. It is important to remove any system faults so that the rest of the power distribution service is not interrupted or damaged. When a fault occurs somewhere in a power distribution system, the voltage is affected throughout the power system. Among various power quality problems, the majority of events are associated with either a voltage sag or a voltage swell, and they often cause serious power interruptions.

A voltage sag condition implies that the voltage on one or more phases drops below the specified tolerance for a short period of time. A voltage swell condition occurs when the voltage of one or more phases rises above the specified tolerance for a short period of time. The causes of voltage sags and swells are associated with faults within the power distribution system. Users located a close distance to the fault experience voltage sags much greater in magnitude and duration than users located farther away, and as the electrical system recovers after removing the fault, voltage swells are produced throughout the system for short periods of time. Often all users who are served by the

power distribution system have power interruptions during a fault because of the effects of a voltage sag or voltage swell produced in the system by the fault. The objective of this research is to develop a novel voltage control scheme that can compensate for voltage sag and swell conditions in three-phase power systems.

Power systems supply power for a wide variety of different user applications, and sensitivity to voltage sags and swells varies widely for different applications. Some applications such as automated manufacturing processes are more sensitive to voltage sags and swells than other applications. For sensitive loads, even a voltage sag of short duration can cause serious problems in the manufacturing process. Normally, a voltage interruption triggers a protection device, which causes the entire branch of the system to shut down.

#### 1.2 Problem Statement

In order to increase the reliability of a power distribution system, many methods of solving power quality problems have been suggested. The development and improvement of power switching devices capable of carrying large current with high voltage enable power electronics technologies to be applied to this area. In addition, self-commutable devices, i.e., gate turn-off device such as GTOs and high power IGBTs, give rise to a variety of schemes to mitigate power quality problems.

Much research has been performed in an effort to solve power quality problems.

Many voltage mitigation schemes are based on inverter systems consisting of energy

storage and power switches. Large energy storage is required when it is necessary to supply real power, which makes these systems expensive.

The main goal of this research is the development of a voltage sag mitigation scheme with high reliability at low cost. This research proposes a scheme called "Voltage Sag Supporter utilizing a PWM - Switched Autotransformer." The proposed scheme is able to quickly recognize the voltage sag and swell conditions and can correct the voltage by either boosting the input voltage during voltage sag events or reducing the input voltage during voltage swell events.

Any power electronic switch in for high voltage applications is expensive, and the peripheral circuits such as gate drivers and power supplies are even more expensive than the device itself. The overall cost of power electronics-based equipment is nearly linearly dependent on the overall number of switches in the circuit topology. Hence, this research suggests a scheme that uses only one PWM switch with no energy storage. Since fewer components are required in this scheme, the system becomes more reliable and less expensive.

Existing methods of voltage sag mitigation using gate turn-off switches for PWM need at least two switches per phase. Other methods use a direct AC-AC converter topology. In addition to requiring at least two switches per phase, they require energy storing reactive components. Therefore, it should be clear that the proposed system having only one PWM switch per phase with no energy storage is a very low cost solution for voltage sag mitigation.

As a first step, this research reviews the statistical surveys of power quality problems in order to determine the specifications of the target system, and this research evaluates existing methods used to compensate for voltage sags and swells. Since the majority of voltage sag events occur under severe weather conditions, the voltage distribution of the system under lightning surge must be investigated. From the power quality surveys, it is known that most voltage sag events last for less than 2 seconds. Hence, it is necessary to operate this device only for a short period. Therefore, to increase the system efficiency and to provide the means of bypass of a short current, the system employs another switch in addition to the PWM switch, which is a bypass switch implemented with thyristors. The bypass switch is in the on-state most of time, and the PWM switch, which is actually a high voltage bidirectional AC switch, operates only during a voltage sag condition and regulates the output voltage according to the PWM duty-cycle.

In order to quickly and precisely control the output voltage or mitigate the input voltage sag, this research includes several design issues such as the design of the voltage controller, the voltage sag detector, and the snubber circuitry. To hasten the transition from bypass mode to PWM mode, i.e., from normal voltage mode to sag mitigation mode, this research suggests a commutation logic for the bypass switch that minimizes the commutation process.

The fault detection logic for switching devices and components are also presented. Fault situations in the sag supporter itself are analyzed, along with their resultant causes and effects, so that appropriate logic and detection circuits can be developed to maximize the reliability of the system. In order to quickly detect faults in the supporter and lessen

the burden of the voltage controller, hardware-based fault detection is preferred over those realized by software logic.

In order to test the performance of the system and to find any problems caused by using actual devices, prototype experiments were done and their results are presented.

#### 1.3 Thesis Outline

A brief overview of the results of a literature survey related to voltage sag and mitigation devices are presented in Chapter 2.

In Chapter 3, this research proposes two schemes of voltage sag mitigation, the so-called "shunt type" and "series type" of topologies. The voltage distributions of the two schemes in the case of a lightning surge are analyzed using PSPICE simulations. In this chapter, the final mitigation scheme is chosen, and the basic configuration of the sag supporter system is presented.

To efficiently mitigate the voltage sag event with the proposed method, many system designs are required. In Chapter 4, design issues such as a snubber, filters, and a voltage controller etc. are explained. Simulation results of voltage sag and swell conditions are presented to show the fast control response and the well-regulated output voltage using the proposed scheme.

Chapter 5 describes the internal fault detection algorithm for each switching device as well as the other components in the system. To detect a device fault, each gate driver circuit is designed with a signal showing either a healthy or and faulty status. The circuitry is implemented using a programmable logic device. The complete logic scheme for internal fault detection is explained in Chapter 5.

Experiments have been carried out to demonstrate the validity of the proposed scheme, and the results are presented in Chapter 6. In this chapter, the software routines for the voltage controller, and the hardware configuration, are briefly explained.

The conclusions and contributions resulting from this research work are summarized in Chapter 7, and recommendations for future research are also provided in this chapter.

#### **CHAPTER 2**

# PREVIOUS WORK ON VOLTAGE SAG AND VOLTAGE SAG MITIGATION DEVICES

This chapter reviews the typical characteristics of voltage sag, and gives a brief review of previous work in power electronic systems for voltage sag mitigation.

#### 2.1 Power Quality Surveys

With an increase in the use of sensitive loads, the power quality issues have become an increasing concern. Poor distribution power quality results in power disruption for the user and huge economical losses due to the interruption of production processes. According to an EPRI report, the economical losses due to poor power quality are \$400 billion dollars a year in the U.S. alone [1]. A power disturbance can be classified as voltage sag, swell, over voltage, under voltage, surge, outage, etc. More widespread use of advanced power-line monitoring technology is enabling useful surveys of electric power quality that can be used to statistically characterize power quality problems. Three power quality surveys for North America had been done by the National Power Laboratory (NPL), the Canadian Electrical Association (CEA), and the Electric Power

Research Institute (EPRI) [2]–[4]. Table 2.1 shows summary of these three power quality surveys.

In each of the three surveys, the definition of a power disturbance event is different. For instance, "voltage sag" is defined as being less than 92% and 90% of nominal voltage for the CEA and the EPRI survey, respectively. In case of "voltage swell", the CEA defines it as the voltage level greater than 104% of nominal voltage, while that of the EPRI is 110%. The data of the three surveys was summarized by Duglas D. Dorr [5]. This paper shows the voltage sag events defined by 0% to 87% of nominal voltage comprise 68% of power disturbances, in which no filter was applied for NPL data. Where, no filter means that every power disturbance is recorded. In the NPL survey, the voltage range of 106% to 110% of nominal voltage is considered to be a voltage swell event. If the EPRI definition of voltage swell, greater than 110% of nominal voltage, is applied to the same data, it results in that voltage sags events having 0–87% consists of 93.3% of total event, and voltage sag having 50%–87% of nominal voltage consists of 70% of total disturbances.

In addition, the EPRI survey shows that in most of the cases (92%), the voltage sags have duration of less than 2 seconds and down to 40–50% of nominal voltage [6]. Besides the above three surveys, many papers have reported power quality surveys. The survey reported in [7] shows that 68% of the power disturbances were voltage sags, and these types of disturbances were the only cause of production losses. From power quality surveys, it can be concluded that voltage sags are the most common power disturbances

and main cause of power disruption. Therefore, this research focuses on voltage sags and their mitigation techniques.

Table 2.1 Summary of the CEA, NPL, and EPRI power quality survey.

| Survey | Period      | Number of<br>Site | Measure Parameter      | Voltage rating |

|--------|-------------|-------------------|------------------------|----------------|

| CEA    | 1991 – 1994 | 550               | Voltage                | 120 or 347 V   |

| NPL    | 1990 – 1995 | 130               | Voltage                | -              |

| EPRI   | 1993 – 1995 | 277               | Voltage and<br>Current | 4.16 – 34.5 kV |

#### 2.2 Voltage Sag

A voltage sag is a momentary decrease of the voltage RMS value with the duration of half a cycle up to many cycles. Voltage sags are given a great deal of attention because of the wide usage of voltage-sensitive loads such as adjustable speed drives (ASD), process control equipment, and computers. In case of sensitive loads, even a shallow voltage dip can cause malfunctions and a stoppage of operation, which results in the loss of production.

#### 2.2.1 Causes of Voltage Sags

Faults in systems and starting large motors create voltage sags. In case of starting large motors, the voltage sags are usually shallow and last a relatively long time. Faults

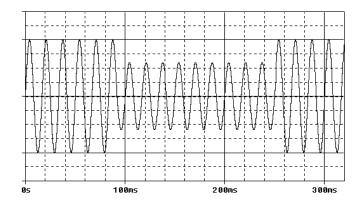

in the distribution or transmission line can be classified as single-line-to-ground (SLG), and line-to-line (L-L) faults. SLG faults often result from severe weather conditions such as lightning, ice, and wind. Animal or human activity such as construction or accidents also causes SLG faults. Lightning may cause flashover across conductor insulators and is the major source of SLG faults. Figure 2.1 shows a typical shape of voltage sag due to a short SLG fault. Many statistical power quality studies have been performed in various locations and show that most voltage sags are caused by SLG faults. SLG faults can occur at any place in the power system and are nuisance to industrial and commercial customers.

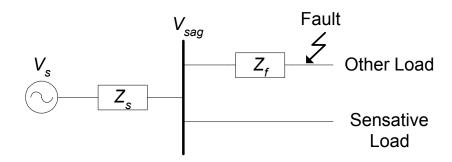

The magnitude of voltage sag can be expressed by the voltage divider model of voltage sag events as shown in Figure 2.2. With ignoring the load current, the sag voltage  $V_{sag}$  can be expressed as (2.1).

$$V_{sag} = \frac{Z_s}{Z_s + Z_f} \times V_s \tag{2.1}$$

Where,  $Z_s$  represents the source impedance at the point of common coupling (PCC) and  $Z_f$  represents impedance between the PCC to the location of the fault [8]. At the point of fault, the voltage is almost zero. Therefore, the impedance of  $Z_s$  and  $Z_f$  determines the magnitude of voltage dip, and the duration of voltage sags is determined by the fault clearance time of the protection device. From (2.1), it can be known that the fault occurs near to PCC, which causes deeper voltage sag.

Figure 2.1. A shape of voltage sag due to SLG fault.

Figure 2.2. Voltage divider model for a voltage sag event.

#### 2.2.2 Sensitivity of Voltage Sags

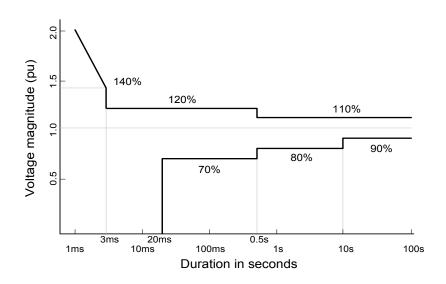

Figure 2.3 shows the Information Technology Industry Council (ITIC) curve that has been introduced to suggest a guideline for voltage quality in power distribution systems serving main computers, and it has become an industry reference for acceptable voltage tolerance. This curve specifies the voltage dip magnitude and the duration of the voltage sag for 120 V single-phase applications. The curve shows that a 10% voltage deviation is acceptable even if the voltage sag or swell remains for a long time, but a 30% voltage

drop for a time period longer than 0.5 second is not acceptable. This curve is useful for providing general insight into acceptable voltage quality. The SEMI–F47 [9] specifies the requirement of voltage quality for the voltage sag immunity of semiconductor manufacturing processing. Table 2.2 shows the duration and magnitude of voltage sag specified by the SEMI–F47.

Figure 2.3. The ITIC curve.

Table 2.2 Recommended voltage for semiconductor industry.

| Duration  | < 0.05s | 0.05s - 0.2s | 0.2s - 0.5s | 0.5s - 1.0s | > 10s |

|-----------|---------|--------------|-------------|-------------|-------|

| Magnitude | -       | > 50%        | > 70%       | > 80%       | > 90% |

Voltage sags affect the performance of equipment and may trigger the system's protection circuit, which interrupts power. As a result of the loss of power, the process of work will stop. The voltage sag tolerance of devices varies widely, and the range can be

shown in Table 2.3 [8]. For instance, a value of X ms, Y% indicates that a voltage sag lower than Y% and longer than X ms causes a trip or malfunction of the equipment. This table does not show the tolerance range for specific devices. For reliable operation, the tolerance range should be higher than the average level.

In addition, many literature surveys have been performed to specify the threshold voltage that causes a trip or malfunction of the system. The research [10] shows that in case of ASD (adjustable speed drive), voltage sag with a duration of 12 cycles or more and lower than 20% voltage drop may trip out some ASD's involved in continuous processes. Program logic controller with computerized numerically controlled (CNC) machines can be disrupted with a sag of longer than 1 cycle and less than 86% of nominal voltage. However, the sensitivity highly depends on the equipment itself, and the survey of threshold voltage test says that some equipment has a threshold at 30% voltage.

Table 2.3 Voltage tolerance ranges of equipment.

|                   | Voltage Tolerance |             |             |

|-------------------|-------------------|-------------|-------------|

| Equipment         | Upper Range       | Average     | Lower Range |

| PLC               | 20 ms, 75%        | 260 ms, 60% | 620 ms, 45% |

| PLC input card    | 20 ms, 80%        | 40 ms, 55%  | 40 ms, 30%  |

| 5 HP AC drive     | 30 ms, 80%        | 50 ms, 75%  | 80 ms, 60%  |

| Personal computer | 30 ms, 80%        | 50 ms, 60%  | 70 ms, 50%  |

#### 2.3. Voltage Sag Mitigation Devices

To better understand the most effective method of voltage sag mitigation, a brief review of existing methods is presented.

#### 2.3.1 Tap Changers

Tap changers are the most cost-effective method for regulating the output voltage when the input voltage has a sag condition that exists for a relatively long period of time. It is possible to vary the output voltage by changing taps located in the primary or secondary side of a transformer. Most existing tap changers use mechanical moving parts to change the tap location. Usually, three or four cycles are needed to move the mechanical switch to the desired position. Therefore, its response is relatively slow [11]. To overcome this problem, thyristors have been used recently to replace the mechanical parts of the tap changer.

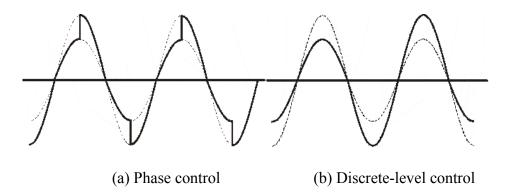

The simplified configuration of a thyristor tap changer is shown in Figure 2.4 to show the output voltage waveforms controlled by either phase control or discrete-level control. The output voltage waveforms generated by phase control are shown in Figure 2.5 (a). It can be seen from the figure that the voltage waveform controlled by the phase control contains a relatively high harmonic distortion component. To reduce the harmonic distortion, discrete-level control can be used. In discrete-level control, the thyristor pairs conduct during one cycle. However, to get many discrete voltage levels, it

is necessary to have many transformer taps, which means that it needs many thyristor pairs as well. This is another disadvantage of thyristor tap changers.

Figure 2.4. Thyristor tap changer using two thyristor pairs.

Figure 2.5. Output voltage waveforms of thyristor tap changer.

#### 2.3.2 Flexible AC Transmission Systems (FACTS) Devices

FACTS devices have abilities of controlling active powers and reactive powers of the distribution system, which are able to maximize the utilization of existing lines. In addition, they can stabilize the voltage at point of common coupling and can reduce the damping of the power oscillation. FACTS devices can be divided into three categories such as series controller, shunt controller, and combined controller [12].

- Series connected controllers: Static Synchronous Series Compensator (SSSC),

Thyristor-Switched Series Capacitor (TSSC), Thyristor-Switched Series

Reactor (TSSR), etc.

- Shunt connected controllers: Static Synchronous Generator (SSG), Static Var Compensator (SVC), Static Synchronous Compensator (STATCOM), Thyristor-Controlled Reactor (TCR), Thyristor-Switched Capacitor (TSC), etc.

- Combined controllers: Unified Power Flow Controller (UPFC), Thyristor-Controlled Phase Shifting Transformer (TCPST), etc.

Among the FACTS devices, many methods are based on inverter topologies such as STATCOMs. On the other hand, TSCs or TCRs based on thyristor switches use passive elements such as capacitors or reactors to change the reactive impendence of systems for controlling active and reactive powers. The inverter system gives more flexibility of controlling power and improving the power stability as well as control of the magnitude and phase of the voltage. Since this research mainly focuses on the mitigation of voltage sags, only the inverter based FACTS devices will be explained in the viewpoint of compensation of voltage sag events.

#### 2.3.2.a Series Compensation Method

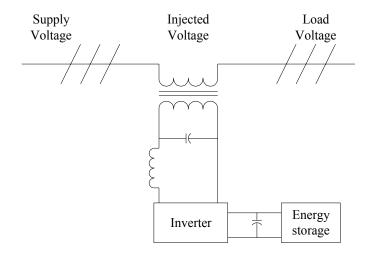

Recently, a dynamic voltage restorer (DVR) was introduced for mitigating a voltage sag [13]–[20]. The DVR shown in Figure 2.6 is based on an inverter system that has energy storage for supplying active power, an output filter to make more sinusoidal voltage, and a step up transformer.

The DVR is one of the FACTS devices that use the power electronics technology, especially inverter technology and is configured as a series-connected voltage controller. To control the output voltage of the DVR, the inverter supplies the missing load voltage using self-commutable electronic switches such as a gate turn-off thyristor (GTO), an insulated gate bipolar transistor (IGBT), or an insulated gate commutated thyristor (IGCT). The DVR injects the missing voltage in a series. Therefore, it can be called a series voltage controller, but the term DVR is commonly used now.

DVRs have a same configuration of SSSC. The DVRs can be operated with a relatively small capacitor to exchange reactive power or can supply active powers to loads with energy storage. The large capacitor bank, flywheel, superconducting magnetic device, and battery can be used for the energy storage.

The DVR, located between the supply and critical loads, has demonstrated excellent dynamic capability for mitigating voltage sags or swells. Each phase can be controlled independently, and the DVR can adjust the magnitude of the load voltage and the voltage phase angle as well. The advantages of the DVR are its fast response and ability to compensate for a voltage sag and a voltage phase shift using an inverter system.

Figure 2.6. Configuration of a dynamic voltage restorer.

Three schemes can be used to generate the missing voltage in series with the source voltage for compensating the voltage sag such as,

- i) In-phase voltage injection

- ii) Phase-invariant voltage injection

- iii) Phase-advanced voltage injection

In the in-phase voltage injection scheme, the injecting voltage has a same phase angle of the source voltage. Therefore, the magnitude of the injected voltage is the smallest among three compensation schemes. However, this scheme requires the largest active power. In case of the phase invariant voltage injection scheme, the DVR injects the missing voltage that keeps the magnitude of the voltage as well as the phase of the supply voltage. This scheme needs a large injected voltage and may cause over injection of reactive power. Since the size of energy storage is closely related to the requirement

of active power, various compensation methods to reduce the requirement of active energy have been proposed [21]–[22]. If the injected voltage is in quadrature with the load current, the DVR does not inject active power. This scheme is highly depends on the load power factor and can generate a sudden jump of the voltage phase angle. To avoid sudden phase angle jump, the phase of the injected voltage should be gradually changed at the beginning of the compensation as well as at the restoration in order to do not disturb the operation of sensitive loads. The high-speed PWM switching and output filter make it possible to achieve a fast response with less harmonic distortion. However, DVRs are relatively expensive because of the inverter systems, the inserting transformer, and energy storages that need to contain energy to supply active and reactive power for the missing voltage.

#### 2.3.2.b Shunt Compensation Method

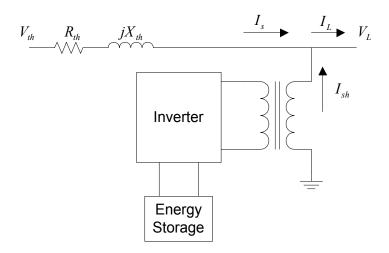

A distribution static synchronous compensator (D-STATCOM) is shown in Figure 2.7, which controls the load voltage in a shunt configuration. The DVR method injects a missing voltage, while the D-STATCOM injects a current to compensate the load voltage variation.

D-STATCOM mainly consists of the inverter circuit with  $X_{sh}$  coupling inductance, the leakage inductance of the transformer. Also, the D-STATCOM, a shunt-connected voltage controller, is connected to the critical load with system impedance [23]. The effectiveness of D-STATCOM depends on the source impedance  $Z_{th}$  and the fault level.

When the phase of the  $V_{sh}$  is in quadrature with the  $I_{sh}$ , without injecting real power the D-STATCOM can achieve the voltage sag mitigation. The shunt injecting current  $i_{sh}$  and  $V_L$  in Figure 2.7 can be expressed as (2.2).

$$I_{sh} = I_{L} - I_{s} = I_{L} - \frac{V_{th} - V_{L}}{Z_{th}}$$

$$V_{L} = V_{th} + (I_{sh} - I_{L}) \cdot Z_{th}$$

(2.2)

Equation (2.2) shows that the compensation voltage is closely related to the impedance  $Z_{th}$ . The complex power developed in the D-STATCOM controller to support the load voltage is given as (2.3).

$$S_{th} = V_L I_{sh}^* \tag{2.3}$$

Notice that the impedance  $Z_{th}$  is connected in parallel with the load impedance. When a short occurs near the load, the equivalent impedance  $Z_{th}$  becomes a small value. Hence, from (2.2) it can be known that the D-STATCOM is then required to generate a large reactive current  $I_{sh}$  to support the load voltage  $V_L$ . This is why the D-STATCOM controller is rarely used as a voltage sag supporter. The D-STATCOM controller is often used for power factor correction, voltage flicker mitigation, and active filtering.

From the operation principles of DVR and D-STATCOM, it can be known that both devices have an ability of the absorbing or generating of reactive power. However, it is

necessary to have large power energy storage to inject active power. Several researches have compared the performance of the DVR and the STATCOM and power rating with various fault voltage levels. These studies show that the power rating of the series voltage injection method such as the DVR is lower than the shunt current injection method such as the STATCOM.

Figure 2.7. Schematic of a D-STATCOM.

#### 2.3.2.c Combined Compensator

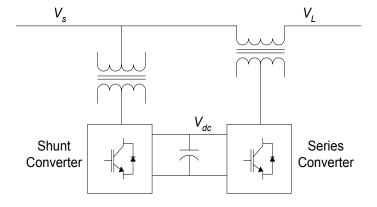

The unified power flow controller (UPFC) shown in Figure 2.8 is the combination of the static synchronous series compensator (SSSC) and the shunt compensator (STATCOM) with a common DC-link energy storage capacitor. The UPFC can control reactive and real power. Therefore, the UPFC can maximize the power line capability and reduce power loss in the system [24]. The operating modes of two voltage source inverters (series, shunt) in the UPFC can be summarized as follows.

The shunt compensator has two modes. One is the VAR control mode, in which it controls the reactive power according to an inductive or capacitive VAR reference, and the other is automatic voltage control mode. In this mode, the compensator regulates the transmission line voltage at the connection as a constant value by changing the shunt converter reactive current, and this mode is normally used in practical applications.

There are five possible control modes in the serial compensator [12]: bus voltage regulation and control, direct voltage injection, phase angle shifter, line impedance emulation, and automatic power flow control. In many possible control modes, the automatic power flow mode is used in majority of practical applications. In this mode, the magnitude and the angle of the injected voltage is controlled with respect to the line current, the series compensator controls real and reactive power in the line. Using a closed-loop control, the series converter independently controls real and reactive power with desired values regardless of changes of the power system. Since this research mainly focuses on mitigating voltage sags not controlling the power flow, the UPFC can be regarded as an expensive alternative solution for voltage sag compensation.

Figure 2.8. Configuration of a UPFC.

#### 2.4 AC Converters

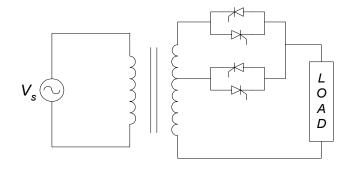

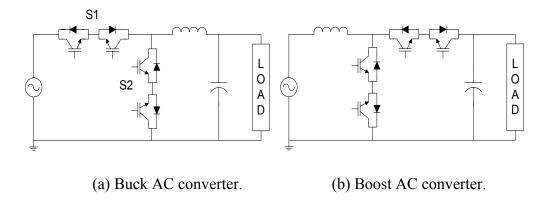

Various AC converter technologies have been proposed for AC output voltage control [25]–[35]. The well-known DC to DC conversion technology has been adapted to AC to AC conversion technology. Also, mature PWM technology is used to regulate the output voltage as constant values during sags or swells. The AC converter topology can be classified as buck, boost, and buck-boost type, and its role is step-down, step-up, and step-up/down, respectively. The ratio of input voltage to output voltage can be expressed as D, I/(I-D), and -D/(I-D), respectively. D represents duty-cycle. Since the phase of the output voltage of the buck-boost type AC converter is inversed with respect to the phase of the input voltage, the buck-boost type converters are not desirable for line conditioner [28]. The buck and boost type are used to only step-down and step-up function, respectively.

Figure 2.9 shows the buck and the boost topology for a single-phase application. AC converters consist of two solid-state switches per one phase, and reactive elements such as a capacitor and an inductor are used for step-up or step-down operation. Since the current in the AC converter flows in both directions, static switches and diodes that are serially connected to allow both directions current. Switches  $S_1$  and  $S_2$  operate complementarily; hence, it is necessary to provide a turn-on delay between  $S_1$  and  $S_2$  switching to avoid the short circuit.

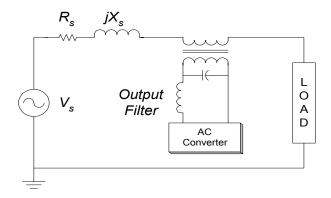

Figure 2.9. AC converter topologies.

One example of an output voltage control scheme based on AC converters is shown in Figure 2.10, in which the LC filter is included to generate a more sinusoidal output voltage. A buck type converter with a boosting transformer may be one of several possible voltage sag mitigation schemes. This topology is similar to that of the DVR shown in Figure 2.6. In this scheme, the AC converter replaces the function of the inverter in the DVR topology, which generates the missing voltage. Because the AC converter does not need a large DC link capacitor, it makes the overall system less expensive.

Figure 2.10. Voltage regulation scheme using an AC converter.

#### 2.5 Modified Scheme

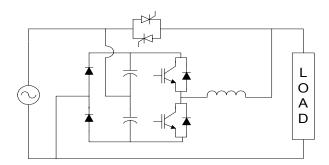

Besides above schemes, several topologies for voltage sag mitigations have been proposed [36]–[37]. In [36], the inverter-based topology so called Dynamic Sag Corrector (DySC) is presented as shown in Figure 2.11. This topology is capable of bypass mode and voltage boost mode. During the voltage boost mode, the missing voltage is added to the input voltage to generate the output voltage. In [37], a PWM AC converter-based scheme is presented, in which an autotransformer is used to boost the input voltage. Same as [36], the output voltage is obtained by summation of the input voltage and the missing voltage generated by the AC converter. In the scheme of [37], same as AC converters, two switch pairs are used for single-phase application.

Figure 2.11. Single phase DySC topology.

#### 2.6 Chapter Summary

In this chapter, the causes and effects of voltage sags have been briefly reviewed. It was known from various power quality researches that most of power quality problems are voltage sag events, and they can cause serious power distribution problems.

A summary of the state of the art methods proposed for voltage sag mitigation has been presented in this chapter. It has been shown that many kinds of methods can be used for the purpose of this research, and the PWM scheme has been successfully used the voltage sag mitigation devices, such as FACTS devices and AC converters. These various schemes for mitigating the voltage sag have been reviewed to determine the direction of the research.

From result of the literature survey, it was known that the FACTS devices show a fast control response. However, the cost of the system is relatively expensive due to inverter systems and large energy storage for supplying active power. Also, it was known that the PWM AC converter could be used for cost-effective solution for this research. It was shown that buck type converter with a boosting transformer and boost type converter were successfully applied for voltage sag mitigation of single-phase and three-phase applications. It was noted that the AC converter topology uses two switches per one-phase application.

# **CHAPTER 3**

# **SELECTION OF**

# **VOLTAGE SAG MITIGATION TOPOLOGY**

# 3.1 Selection of Compensation Method

The literature survey done in the previous chapter showed that tap changers, DVRs, and AC converters are some of the better existing voltage compensation solutions. However, tap changer topology has a slow response time for mechanical switching units. Tap changers using thyristors have high harmonic distortion for phase control units and the high cost for discrete-level control units. These disadvantages make this technology unattractive for this research. The DVR topology is also unattractive as a solution for large power systems because of the high cost. Hence, this research focuses on the AC converter topology shown in Figure 2.9 as the basis for a new voltage sag compensator and further study. For example, a voltage sag compensator can be realized using the topology shown in Figure 2.10 with a buck AC converter and a boosting transformer.

Eliminating the electrical switches reduces the cost and complexity of the system. The AC converters in Figure 2.9 need two switch pairs per phase. One switch pair consists of two switches conducting current in both directions. The AC converter

topology is an inexpensive approach for low voltage and low power implementation, but the switch used for high voltage system is expensive. The switch cost is a significant portion of the overall system cost in this research. Therefore, minimizing the number of switches significantly reduces cost.

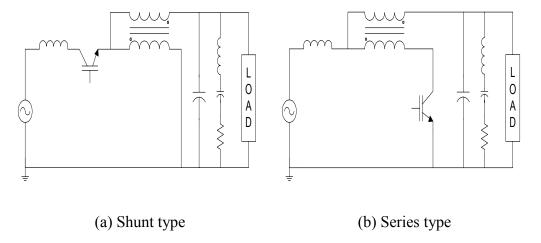

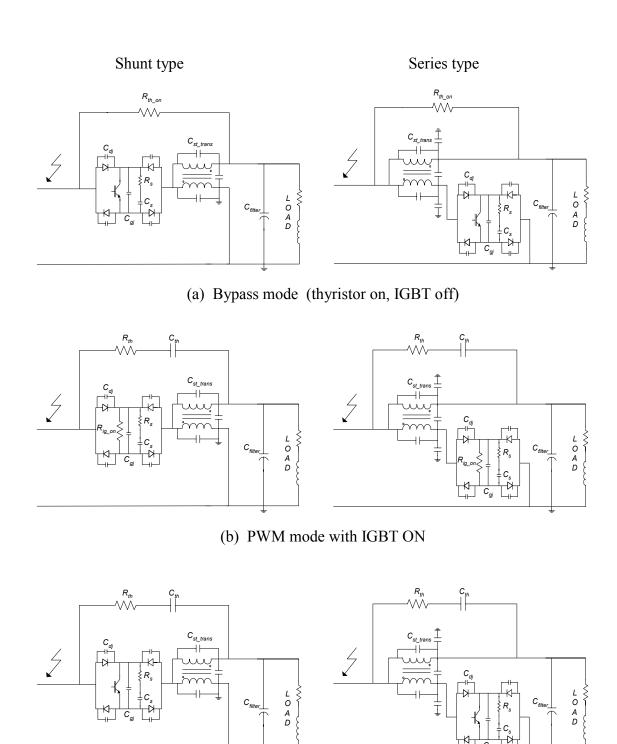

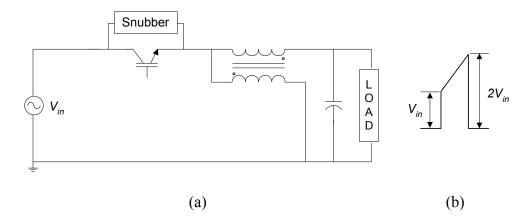

Reducing the number of switches has a high priority in this research. The series type and shunt type voltage compensators are shown in Figure 3.1 (a) and (b), respectively. These schemes have only one switch, and an autotransformer is used for a boosting transformer instead of a two-winding transformer.

The schemes can be classified as either "shunt type" or "series type." The names are based on how the injecting voltage is added to the output voltage. In the shunt type scheme, the switch is located before the autotransformer, and the developed voltage is injected in a shunt manner. In the series type scheme, the switch is located after the autotransformer, and the developed voltage is serially added to the supply voltage.

Figure 3.1. Shunt type and series type compensators.

## 3.1.1 Comparisons between Series type and Shunt type Compensation

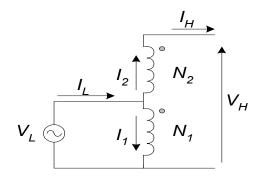

The autotransformer shown in Figure 3.2 is used in the proposed system to boost the input voltage instead of a two winding transformer. The autotransformer does not offer electrical isolation between primary side and secondary side, but this autotransformer has advantages of high efficiency with small volume.

The relationship of the autotransformer voltage and current is shown in Figure 3.2 and expressed as (3.1), where a is the turns ratio. In this research, the transformer with ratio  $N_1:N_2=1:1$  is used to boost up to 50% voltage sag.  $N_1:N_2$  is common notation for the turns ratio of a two-winding transformer. From equation (3.1), it can be known that the turns ratio of an autotransformer is defined by  $N_1:(N_1+N_2)$ , which is 1:2 in this case. However, in order to easily recognize that the autotransformer has same turns of primary and secondary side, the term of "1:1 turns ratio" is used for convenience of later analysis.

As the turns ratio equals 1:1, the magnitude of the load current  $I_H$  (high voltage side) is same as that of the primary current  $I_I$  (low voltage side). Therefore, so that from Equation (3.1) it can be known that  $V_H = 2V_L$  and  $I_L = 2I_H$ .

The series type and shunt type topologies are compared to determine the best topology for high voltage implementation. Initially, the magnitudes of the switch current and the voltage across the switch are compared to understand the advantages of a particular topology. It is assumed that the autotransformer has a 1:1 turns ratio and a 100% duty-cycle of the switch.

In the series type topology, since the switch is located in the autotransformer's primary side, the magnitude of the switch current equals the load current, whereas in the shunt type topology, the switch current is two times the load current. Based on the magnitudes of the switch currents in both topologies, the series type compensator is found to be a better choice.

Because voltage sag conditions occur only a few times, and the duration of a 92% voltage sag event is less than 2 seconds as shown in the previous chapter, this voltage sag supporter works only a few seconds and remains off-state most of its operation time. Since the switches in the voltage sag supporter remain in the off-state most of the time and must withstand the voltage across it, the voltage across switch should be considered. The magnitude of voltage across the switch in the off-state is an important factor to decide a topology because it affects the expected lifetime of the switch.

In the shunt type topology, the voltage across the switch in the off-state is equal to one half of the input voltage, while in the series type case, the voltage across the switch in the off-state is equal to the magnitude of the input voltage.

In summary, the series type topology has the advantage of lower switch current, and the shunt type topology has the advantage of lower off-state voltage. Since the voltage across the switch is a more important factor for deciding overall system safety, the shunt type topology is chosen for the voltage compensation scheme. The voltage sag supporter will operate during severe weather conditions such as lightning. To determine the final topology, effects of surge voltage during a lightning strike must be considered. Voltage

distributions of the system under lightning surge condition are simulated, and results are given in Section 3.3.3.

$$\frac{V_L}{V_H} = a = \frac{I_H}{I_L}, \quad a = \frac{N_1}{N_1 + N_2}$$

(3.1)

Figure 3.2. Voltage and current relation in an autotransformer.

#### 3.2 Configuration of the Proposed System

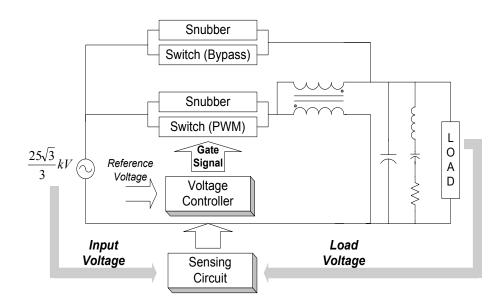

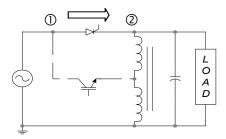

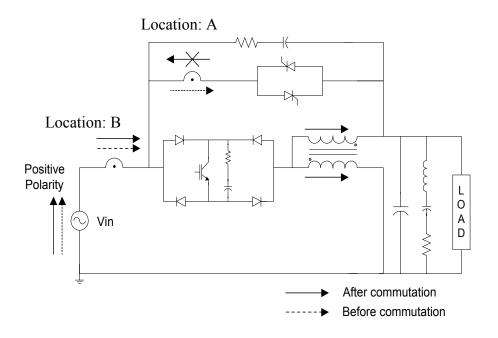

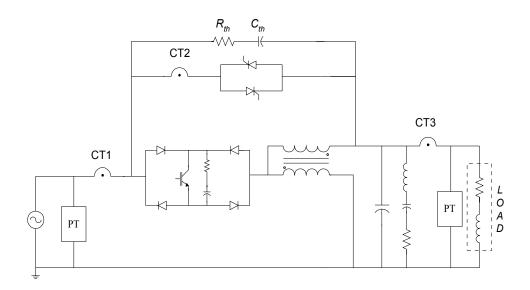

It is now necessary to introduce a new configuration and control logics that are suitable for normal operating conditions as well as voltage sag conditions. To do that, a thyristor is connected to the load side to serve as a bypass switch. Design issues of the proposed system will explain in detail in next chapter. This research suggests a scheme for mitigating voltage sag as shown in Figure 3.3.

The proposed system consists of a PWM switch block, a bypass switch block, output filters, an autotransformer, and a voltage controller. Two kinds of switches are present in this system, a IGBT and a thyristor. The IGBT operates only during a voltage sag

condition and regulates the output voltage corresponding a PWM duty-cycle. A thyristor is used as the bypass switch in an inverse parallel configuration. This bypass switch connects the input power to the load unless the sag condition is present. The efficiency of the voltage compensator is very high because during normal operation power passes only through the thyristor.

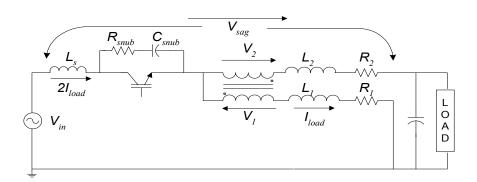

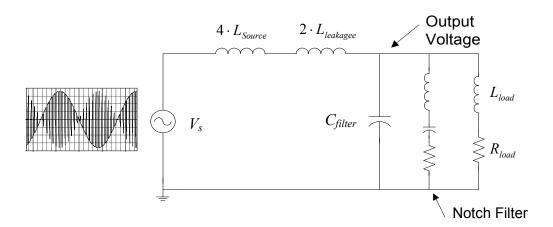

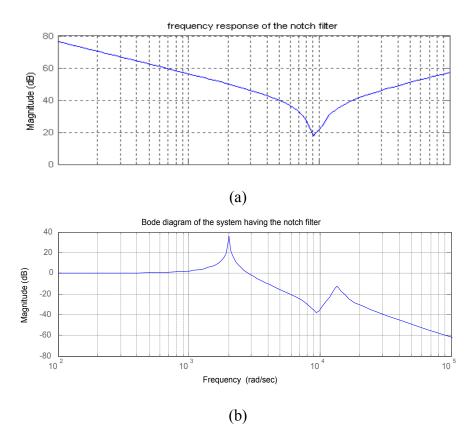

In the proposed voltage sag supporter, an autotransformer having a 1:1 turns ratio is used for boosting the input voltage. To filter out the switching noise and reduce harmonics, output filters (a main capacitor filter and a notch filter) are attached to the output side. To suppress the over voltage when the power switches are turned off, RC snubber circuits are connected across every IGBT and thyristor.

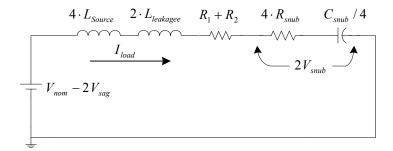

In this research, the input voltage is about 15 kV RMS, and rated voltage of the IGBT and thyristor are 6500 V. Therefore, it is necessary to serially connect the switches to withstand the input voltage. Circuit simulations are done to determine the total number of serially connected IGBTs for PWM switch and thyristors for static bypass switch. Because the snubbers are serially connected, they have a function of dynamic voltage sharing as well as the role of a turn-off snubber.

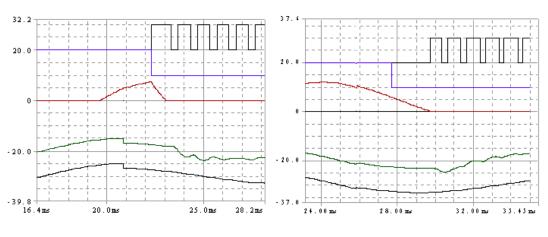

The proposed voltage sag supporter starts the PWM switching when the input voltage becomes lower than 90% of nominal voltage, i.e., this compensator does not operate if the input voltage remains within 10% deviation of the nominal value. The 10% deviation is inferred from the investigations of the voltage quality studies in Chapter 2 and Figure 2.3. In Figure 2.3, it is shown that a 10% voltage dip is allowable even the dip exists longer than 10 seconds. Therefore, under normal conditions, i.e., bypass mode

can be defined as the magnitude of the input voltage is higher than 90% of nominal voltage. During normal conditions, the bypass switch remains on.

On the other hand, when the sensing circuit detects more than 10% voltage sag, the voltage controller immediately commands turn-off process (commutation) of bypass switch and then commands the IGBTs to start PWM switching to regulate the output voltage.

Figure 3.3. Basic configuration of the proposed voltage compensation scheme.

## 3.3 Comparison of the Voltage Magnitude of Series type and Shunt type

This section compares the peak voltage magnitude of the shunt and the series type during lightning surge. To better understand the voltage distribution in the system during the lightning surge, configuration of the IGBT switch block should be known first.

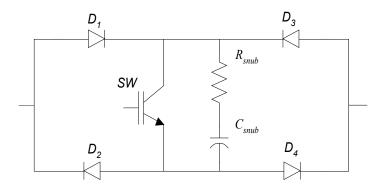

# 3.3.1 Bridge Configuration

The IGBT switch block consisting of diodes, a switch, and a snubber, which is socalled a bridge configuration is shown in Figure 3.4. The bridge configuration allows current flow in both directions by using just one switch. The switch configuration shown in Figure 2.9 (a) and (b) for AC converters is equivalent to the bridge configuration, except that it uses two switches connected in a common emitter configuration for each switch pair  $S_1$  and  $S_2$ . The diode bridge arrangement is used to achieve bi-directionality at the lowest cost. When the switch is on, a positive current flows in the path  $D_1 \rightarrow SW$  $\rightarrow D_4$ , and a negative current flows in the path  $D_3 \rightarrow SW \rightarrow D_2$ . When the switch turns off, the current in the switch changes its path to the RC snubber noted as  $R_{snub}$  and  $C_{snub}$ .

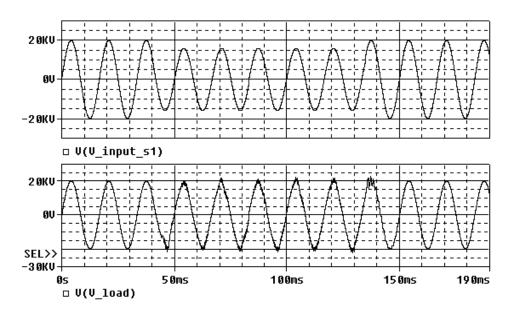

In this research, the magnitude of the input three-phase line-to-line voltage is 25 kV RMS, which is equivalent to 14.4 kV (20 kV peak) line-to-neutral single-phase voltage. Therefore, to keep the peak voltage of the switch under the rating of the switch, seven bridges are connected in series, operating as one AC switch.

Figure 3.4. AC Switch with IGBT and snubber in bridge configuration.

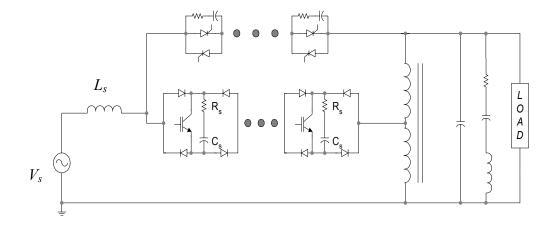

## 3.3.2 Entire System Configuration

Figure 3.5 shows the actual circuit configuration. The inductor located between the input voltage source and switches represents source impedance. In Figure 3.5, it is shown that IGBT switch blocks and back-to-back connected thyristor switch pairs are serially connected to withstand the voltage across the switches. The total switch number of serial connection is seven and four for IGBT and thyristor, respectively. To determine the total number of IGBT switch pairs, circuit parameters such as the source impedance, the transformer leakage inductances, and minimum PWM duty-cycle are considered. More details are explained in the next section dealing with design of the RC turn-off snubber.

To determine the total number of thyristor pairs, it is necessary to check the condition when the largest voltage exists across each thyristor pair. During PWM mode, thyristor pairs should withstand a voltage difference between the output voltage and the input voltage. The maximum voltage across the thyristor occurs at 50% voltage sag. Since the output voltage is controlled to have nominal magnitude of the input voltage, the voltage across the thyristor pairs is 50% of the nominal voltage, which results in about 10 kV peak across the thyristor. Considering safety factors and over voltage condition, quantity four thyristor pairs (with each thyristor rated at 6.5 kV) are selected for the serial connection.

Figure 3.5. Overall system configuration showing serially connected switches.

#### 3.3.3 Voltage Distribution during Lightning Surge

In the previous section, it was shown that the shunt type topology shows less voltage stress than the series type, while in the viewpoint of current stress in the series type was lower than the shunt type. These facts are inferred from the current and voltage relation of the autotransformer as shown in Figure 3.2.

To finalize the topology of the voltage mitigation device, it is necessary to examine the voltage distribution in the system during normal as well as abnormal conditions. During bypass mode under normal condition regardless of compensation types, the thyristor pair has a few volts showing the thyristor turn-on voltage drop. However, the voltages in the PWM switch (IGBT) corresponding to two compensation types have different voltage levels. The IGBT switch block has a bridge configuration with the RC turn-off snubber as shown in Figure 3.4, which works as a RC charging circuit similar to a rectifier circuit in inverter systems. When power is applied to the system, the capacitor

in the IGBT RC snubber will charge up, and it will stop charging when the diode in the bridge configuration becomes a reverse bias. If the energy in the source impedance  $L_s$  is ignored, the snubber capacitors charge up to the peak input voltage for series type and to a half of the peak input voltage for shunt type. For instance, considering the 20 kV input voltage and seven serially connected IGBT switch blocks, the capacitor charging voltage becomes 20 kV / 7 / 2 = 1.5 kV for the shunt type and 20 kV / 7 = 3 kV for the series type.

6.5 kV rating IGBTs are used in this research. The series type has a 3 kV peak voltage across the IGBT during normal condition. Therefore, it seems that the series type has enough voltage safety margins. However, 3 kV was obtained only under normal condition. Peak voltage across the IGBT and thyristor under abnormal condition should be considered as well. Lightning in power system is main cause of voltage sag events, and this voltage sag mitigation device has a more chance to operate under such a severe weather condition. Therefore, it is required to investigate the voltage across PWM and bypass switches during lightning surge.

In the proposed system, to protect the system from over voltage, MOVs (Metal Oxide Varistor) are placed in several places such as the input side, across the switch block, and the output side. A MOV has a non-linear V-I (Voltage-Current) characteristic, which can be realized by changing its resistance according to the voltage across the device. If the voltage across a MOV exceeds a certain level, the MOV offers a shunt path of the surge current, which suppresses the surge voltage. Several models of a MOV have been proposed to show the frequency dependent characteristic [38]–[42]. It is the

characteristic that the peak voltage of a MOV occurs before the peak of the current especially for fast front surge. In addition, MOVs show the characteristic that the maximum discharge voltage of MOVs is varied by the rising time of the surge current. The discharge voltage for a given current level is increased by 6% as the rising time of the surge current decreases from 8 µs to 1.3 µs [38]. To represent these effects, the IEEE W.G. 3.4.11 [38] suggested a model that has two non-linear resistors and R-L filters. However, this model has a difficulty in finding the parameters in the model. An inductor is required to show the frequency characteristic of MOVs. Datasheet for MOVs does not have enough of the actual voltage and current time response curves to determine the inductance value.

In simulations, MOVs are modeled as nonlinear resistors, because the main purpose of the simulation is to find out the peak voltage not the frequency response. In addition, the simulation uses a surge having a fixed time response, thus it is not necessary to model MOVs to have a different response for the surge having a different time response. The voltages across the IGBT switch and the thyristor are investigated under following three conditions. There exist two modes of PWM corresponding to IGBT ON and OFF, while the thyristor remains off in PWM mode.

- BYPASS mode (IGBT off, Thyristor on)

- PWM mode with IGBT ON (IGBT on, Thyristor off)

- PWM mode with IGBT OFF (IGBT off, Thyristor off)

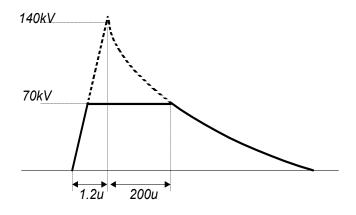

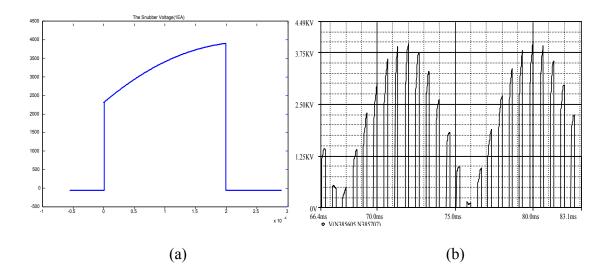

Figure 3.6 shows the lightning surge waveform used for simulations, which has 140 kV peak voltage of 1.2 / 200  $\mu$ s pulse duration. A typical surge voltage waveform has duration of 1.2 / 50  $\mu$ s with a certain peak surge voltage. 1.2  $\mu$ s is the time of reaching zero value to peak in the ascending slope, and 50  $\mu$ s is the time of reaching from the peak to a half value in the descending slope. In simulations, it was assumed that the lightning surge exists relatively longer than conventional one with higher peak value of 140 kV in order to check the voltage distribution at worst case.

Where, the peak voltage is limited to 70 kV due to the MOV clamping. MOVs having 15.3 kV MCOV rating (maximum continuous operating voltage) have a maximum discharge voltage ranging from 40 kV to 63 kV corresponding to the surge current ranging from 1.5 kA to 40 kA with 8 / 20  $\mu$ s duration [42]. As mentioned earlier, the discharge voltage of the MOV for the fast front surge such as 1  $\mu$ s is higher than that for conventional surge current such as 8  $\mu$ s. Therefore, 70 kV peak is chosen for the clamping voltage of the MOV.

Figure 3.6. Lightning surge voltage waveform having 1.2 / 200 µs with 140 kV.

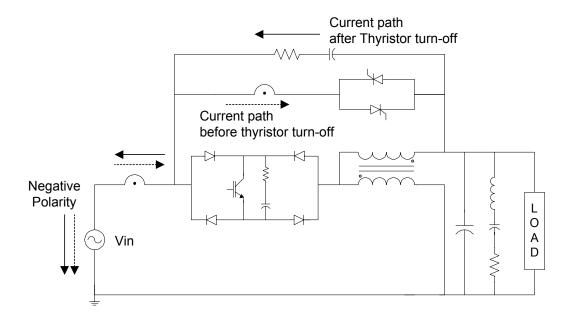

Figure 3.7 (a)–(c) show the equivalent circuits for lightning surge simulations. In bypass mode as shown in Figure 3.7 (a), thyristors are modeled as a resister to represent the turn-on voltage drop in the thyristors. The IGBT does switching during PWM mode. Therefore, there exist two states, which are IGBT ON and IGBT OFF. Two states of the PWM mode are described as "PWM mode with IGBT ON" and "PWM mode with IGBT OFF." In case of PWM mode with IGBT ON as shown in (b), the IGBT switch is modeled as a resistor to represent on-voltage drop in the IGBT. Figure 3.7 (c) shows the equivalent circuit during PWM mode with IGBT OFF. Since both IGBT and thyristor remain off, no resistor is required to show the turn-on voltage drop.

Stay capacitances of the transformer  $C_{st\_trans}$  are taken account into the simulations. There exist stray capacitances of winding to winding, and that of winding to core. The junction capacitances of the diodes  $C_{dj}$  in the switch block and that of the anti-parallel diode  $C_{gj}$  in the IGBT are considered. Table 3.1 shows parameters used in lightning surge simulations.

Table 3.1 System parameters used in the lightning surge simulations.

| Parameter             | Value  | Parameter       | Value |

|-----------------------|--------|-----------------|-------|

| $R_{th}$              | 100 Ω  | $R_{trans}$     | 1.7 Ω |

| $C_{th}$              | 10 μF  | $L_{leakage}$   | 20 mH |

| $R_{snub}$            | 49 Ω   | $C_{snub}$      | 4 μF  |

| $C_{\mathit{filter}}$ | 1.5 μF | $C_{st\_trans}$ | 1 nF  |

| $C_{gj}$              | 5 nF   | $C_{dj}$        | 5 nF  |

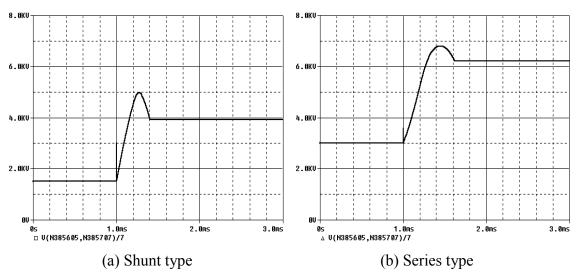

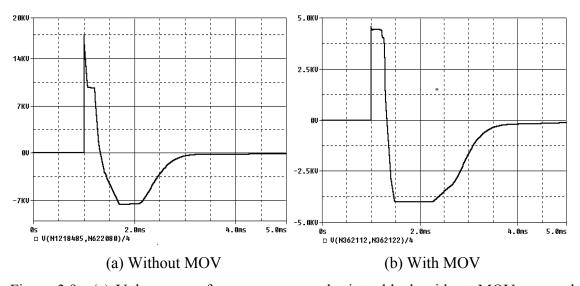

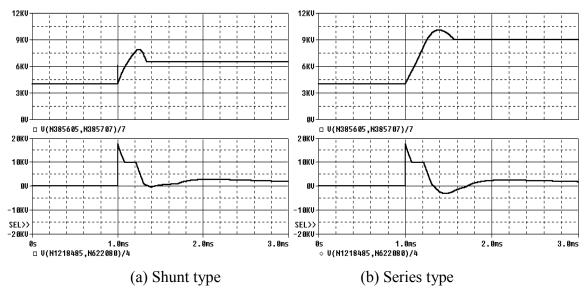

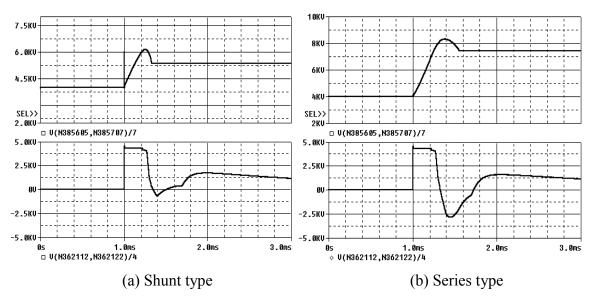

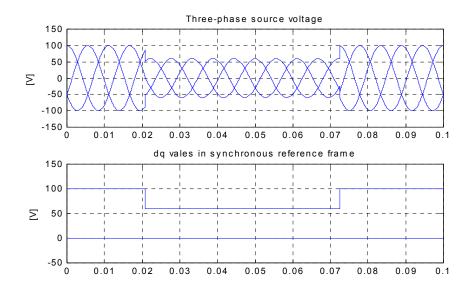

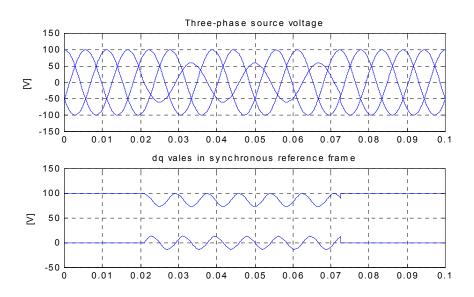

The voltage waveforms across the IGBT or/and the thyristor are shown from Figure 3.8 to 3.11. Figure 3.8 shows the IGBT voltage waveforms during bypass mode. In Figure 3.8 for series type, it can be seen that the peak value reaches around 7 kV. On the other hand, in case of shunt type the peak value remains lower than 5 kV, which is lower than the breakdown voltage of 6.5 kV rating IGBT. The leakage inductance of the autotransformer has a role to suppress the peak voltage across the IGBT. The higher leakage inductance, the lower peak voltage across the IGBT. In these simulations, the initial capacitor voltages of the RC snubber capacitor are selected as 1.5 kV, 3 kV, as explained in Section 3.3.3, for shunt and series type, respectively.