Open access • Proceedings Article • DOI:10.1109/ISSCC.2010.5434061

# A wideband beamformer for a phased-array 60GHz receiver in 40nm digital CMOS — Source link [2]

Kuba Raczkowski, Walter De Raedt, Bart Nauwelaers, Piet Wambacq Institutions: IMEC, Katholieke Universiteit Leuven Published on: 18 Mar 2010 - International Solid-State Circuits Conference Topics: Wideband, Beamforming, Phased array, Link budget and Bandwidth (signal processing)

Related papers:

- A 65 nm CMOS 4-Element Sub-34 mW/Element 60 GHz Phased-Array Transceiver

- A 52 GHz Phased-Array Receiver Front-End in 90 nm Digital CMOS

- A 77-GHz Phased-Array Transceiver With On-Chip Antennas in Silicon: Transmitter and Local LO-Path Phase Shifting

- A 60GHz CMOS phased-array transceiver pair for multi-Gb/s wireless communications

- A Fully Integrated 16-Element Phased-Array Transmitter in SiGe BiCMOS for 60-GHz Communications

### 2.2 A Wideband Beamformer for a Phased-Array 60GHz Receiver in 40nm Digital CMOS

Kuba Raczkowski<sup>1,2</sup>, Walter De Raedt<sup>1</sup>, Bart Nauwelaers<sup>2</sup>, Piet Wambacq<sup>1,3</sup>

<sup>1</sup>IMEC, Heverlee, Belgium <sup>2</sup>K.U. Leuven, Leuven, Belgium <sup>3</sup>Vrije Universiteit Brussel, Brussels, Belgium

For high-data-rate wireless communication in the 7GHz band around 60GHz, the IEEE 802.15.3c standard [1] provides channels with a 0.88GHz bandwidth for the AV-OFDM mode. For the single-carrier modes, the ECMA 387 standard [2] foresees the possibility of bonding together adjacent channels, yielding higher data-rates. Radios for these 60GHz standards often use phased antenna arrays to relax the link budget. A phased-array receiver needs a variable phase shift on each antenna path and a combiner that sums the signals from the individual paths after phase shifting. The beamforming circuitry presented here handles 4 paths. It can operate both with one 0.88GHz channel and with bonding of two such channels. Phase shifts are realized with a resolution better than 20°. Bandwidth is high thanks to the use of current amplifiers with very low input impedance.

Phased-array receivers that implement beamforming in the RF signal path [3,4] suffer from large losses and need a high power consumption to overcome this. As an alternative, phase shifting in the LO paths [5] requires duplication of the I/Q mixers, but this is a limited overhead. However, it extends the LO buffering causing an increase in power consumption. In this design beamforming is implemented entirely at analog baseband. It requires less LO buffering, and is more robust because it is less sensitive to parasitics than mm-Wave frequency circuits.

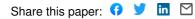

The beamformer (see Fig. 2.2.1) fits in a direct downconversion receiver which yields baseband I and Q components for the received signal at each path. Those signals must be individually phase-shifted and combined to generate a single beamformed I/Q output. For path m (m = 1, ..., 4) a phase shift  $\varphi$  is obtained from the I and Q components  $I_m$  and  $Q_m$  as follows:

$$I'_{m} = A[\cos(\varphi)I_{m} - \sin(\varphi)Q_{m}]$$

$$Q'_{m} = A[\sin(\varphi)I_{m} + \cos(\varphi)Q_{m}]$$

(1)

Factor *A* is an overall gain factor. The signals  $I_m$  and  $Q_m$  are the current outputs of the I/Q mixers. The phase-shifted replicas  $I'_m$  and  $Q'_m$  are also generated in the current domain, as currents are easier to combine than voltages. Therefore, phase shifters are implemented using 4 digitally controlled variable-gain current amplifiers (VGAs). Using switches as in [6], would limit phase resolution to 90 degrees. Further, the signals are combined in two levels (see Fig. 2.2.1). For a phased-array receiver with many antenna paths, there is an inevitable long distance between the output of the RF mixers at the extreme sides of the chip and the output after the final signal combination. To bridge these distances, repeaters are provided in the form of current amplifiers. Signals are combined at the inputs of these repeaters. Because of the signal combination at baseband these long distances are not bridged at RF, yielding lower power consumption for the repeaters and less sensitivity to losses and parasitics. The last combining stage is a transimpedance amplifier (TIA) providing a low output impedance.

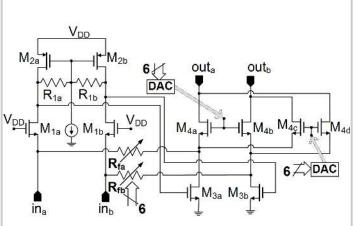

The current amplifiers (see Fig. 2.2.2) have very low input impedance  $R_{in}$  due to the combination of common-gate stages ( $M_{1a-b}$ ) and resistive shunt feedback ( $R_{fa-b}$ ). The output impedance at the drains of  $M_{4a-d}$  is high. The use of two parallel branches ( $M_{4a-b}$  and  $M_{4c-d}$ ) yields a coverage of the 4 quadrants in the complex I/Q plane. The current gain is the product of  $g_{m4}$  and  $R_f$ , where  $R_f$  is used to control the gain *A* in (1), whereas  $gm_4$  steering sets the values for either  $sin(\varphi)$ or  $cos(\varphi)$ , both of which are digitally adjustable. The current amplifier acts as the load of the mixer described in [7], which only requires one transistor per branch between the inputs (in<sub>a</sub> and in<sub>b</sub>) and DC ground so that headroom problems are avoided. This transistor is included in the fabricated design.

The repeaters that bridge the long interconnects are similar to the current amplifiers, except that the branch with  $M_{\rm 4c-d}$  is omitted and the gates of  $M_{\rm 4a-b}$  are fixed to  $V_{\rm DD}$ . The cascade of phase shifters and repeaters has a large bandwidth in

spite of the parasitic capacitance  $C_{inter}$  of the interconnects, as the pole  $-1/(R_{in}C_{inter})$  occurs at very high frequencies due to the very low value of  $R_{in}$ .

The TIA has the same input stage as the current amplifier, but low output impedance by applying resistive shunt feedback (via  $R_{fa\text{-}b}$ ) at the output of source followers  $M_{\text{Sa-b}}$ .

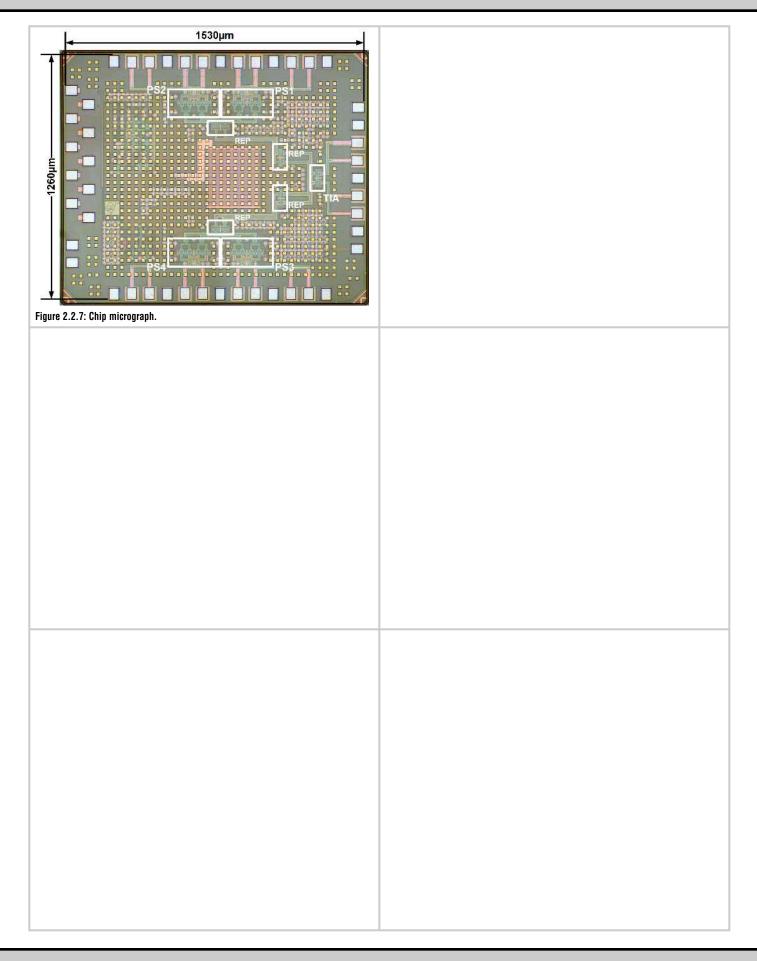

The circuit is fabricated in a 1P7M digital 40nm low-power CMOS technology. The chip (see Fig. 2.2.7), with an area of  $2mm^2$ , is heavily bond pad limited. The area consumed by the phaseshifter is only  $0.03mm^2$ . The chip consumes 35mW from a 1.1V V<sub>DD</sub>. Power consumption per phase shifter is 7mW (including a branch shared with the mixer), which is similar to the LO phase shifter of [5]. However, LO buffering is much more demanding for the latter approach.

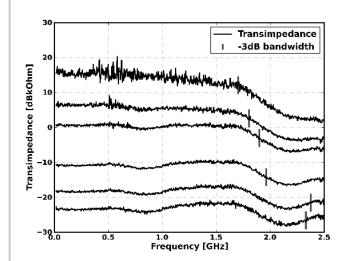

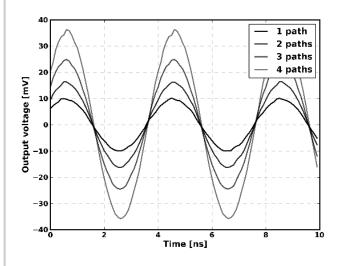

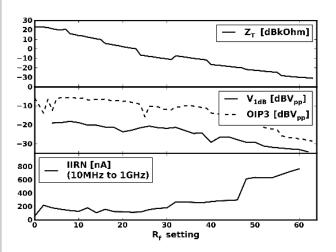

The chip is measured in a 50 $\Omega$  system using off-chip baluns at input and output. Bandwidth is evaluated by deriving the overall transimpedance from S-parameters with one path active and for different gain settings (R<sub>f</sub> values) of the amplifiers (see Fig. 2.2.3, Fig. 2.2.6 top). Clearly, bandwidth is sufficient for bonding of 2 channels.

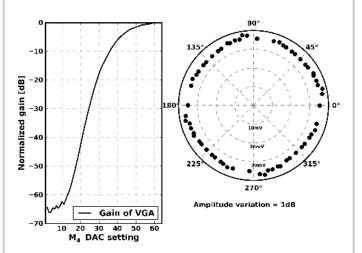

Phase shifts are derived from a lookup table with gains of a single VGA (Fig. 2.2.4 left) as a function of the DAC settings at the gate of the  $M_4$  transistors, which change  $g_{m4}$ . This method could be fully automated by applying an internal input signal (e.g. from a low frequency DAC) and measuring the amplitudes with an ADC at the end of the receiver chain. Phase shift is applied by checking the correct gain setting in the table to match  $sin(\varphi)$  or  $cos(\varphi)$  for a given  $\varphi$ . This approach is verified using an arbitrary waveform generator (AWG) providing I/Q signals for one path (Fig. 2.2.4) and observing output signals on an oscilloscope. The phase resolution in the vicinity of 0, 90, 180 and 270 degrees is limited by the resolution of the DAC.

The constructive combination of signals from all paths, measured at 500MHz, is shown in Fig. 2.2.5.

Noise is measured at the TIA output by presenting an open circuit to the input of one path and with other paths turned off (see Fig. 2.2.6, bottom).

The IP3 and 1dB compression point are measured at 500MHz (see Fig. 2.2.6, middle) by exciting the I inputs of all paths. Output IP3 is -6dBV, which is satisfactory as the signal strength right after downconversion is not yet high.

The presented circuit is the first beamformer that meets the specifications for 0.88GHz channels as provided in the AV-OFDM mode of IEEE 802.15.3c and has enough bandwidth to accommodate bonding of two such channels.

#### Acknowledgements:

The authors thank their colleagues from the INVOMEC division and P. Van Wesemael for support in digital synthesis and layout and V. Szortyka for support with the measurements.

#### References:

[1] IEEE 802.15 WPAN Millimeter-wave alternative PHY task group 3c (TG3c) http://www.ieee802.org/15/pub/TG3c.html.

[2] Standard ECMA-387 for High Rate 60 GHz PHY, MAC and HDMI PAL, http://www.ecma-international.org/publications/standards/Ecma-387.htm.

[3] Y.Yu, P.G.M. Baltus, A.J.M. de Graauw, E. van der Heijden, M. Collados, C. Vaucher, A.H.M. van Roermund, "A 60GHz Digitally-Controlled RF-Beamforming Receiver Front-end in 65nm CMOS," *IEEE Radio Frequency Integrated Circuits Symp.*, 2009.

[4] K. J. Koh, G. Rebeiz, "A 0.13-μm CMOS Digital Phase Shifter for K-band Phased Arrays," *IEEE Radio Frequency Integrated Circuits Symp.*, pp. 383-386, 2007.

[5] K. Scheir, S. Bronckers, J. Borremans, P. Wambacq, Y. Rolain, "A 52GHz Phased-Array Receiver Front-End in 90nm Digital CMOS," *ISSCC Dig. Tech. Papers*, pp. 184-185, 2008.

[6] S. Kishimoto, N. Orihashi, Y. Hamada, M. Ito, and K. Maruhashi, "A 60GHz Band CMOS Phased Array Transmitter Utilizing Compact Baseband Phase Shifters," *IEEE Radio Frequency Integrated Circuits Symp.*, pp. 215-218, 2009.

[7] J. Borremans K. Raczkowski and P. Wambacq, "A digitally-controlled compact 57-66GHz receiver front-end for phased-arrays in 45nm digital CMOS," *ISSCC Dig. Tech. Papers*, pp. 492-493, 2009.

2

Figure 2.2.5: Measured signal combination at 500 MHz: 1, 2, 3 and 4 paths. Distortion in the waveforms is caused by the AWG.

Figure 2.2.4: Gain of one current amplifier as a function of the DAC bit settings at the gate of the M4 transistors (left); phase and output amplitude at 500MHz (right).

## **ISSCC 2010 PAPER CONTINUATIONS**