#### KTH Information and Communication Technology

Aug 2010

# A Wideband High Dynamic Range Continuous-Time Sigma-Delta ADC for Wireless Applications

Ye Xu

Master's Thesis at school of ICT

Integrated Devices and Circuits /RaMSiS Group

Supervisor: Dr. Ana Rusu (KTH), Dr. Gabriele Manganaro (National

Semiconductor)

Examiner: Dr. Ana Rusu

School of Information and Communication Technolog

# Abstract

In recent years, the research toward the development of high speed and high resolution analog-to-digital converters (ADCs) has been equally driven by the demand of high-speed wire line and wireless communication services. Delta-Sigma ADCs are widely used in wireless applications due to their oversampling and noise shaping characteristics.

This thesis aims to design a continuous-time sigma-delta modulator which can provide a dynamic range of 75 dB over a 25 MHz signal bandwidth. The proposed topology is a 4<sup>th</sup> order 3-bit low-pass sigma-delta modulator, which employs a combination of feedforward and feedback schemes. The design starts from system level using Matlab/Simulink. Then the behavioral level design is performed using Cadence VerilogA. Finally, the first integrator in the loop, which is the most critical block in the modulator, is implemented at transistor level using 90nm CMOS technology.

The most important non-idealities of the continuous time sigma-delta modulator, such as clock jitter, excess loop delay, DAC mismatch and time constant variance are considered. Their effects are analyzed and compensation techniques are proposed and introduced in the MATLAB models.

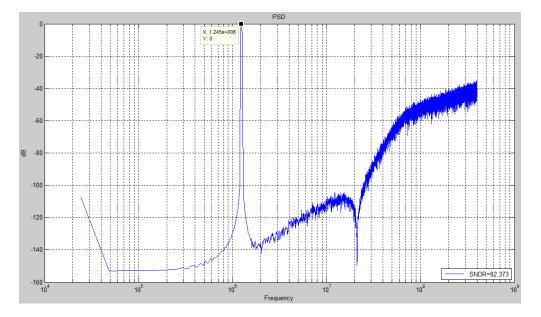

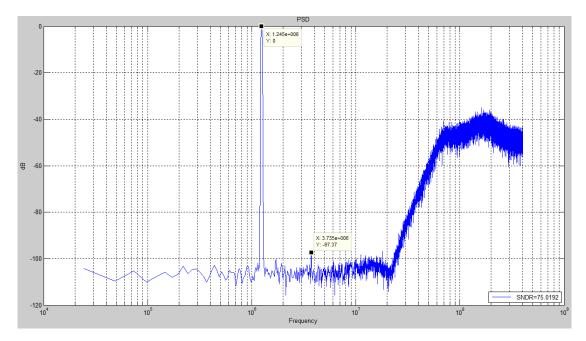

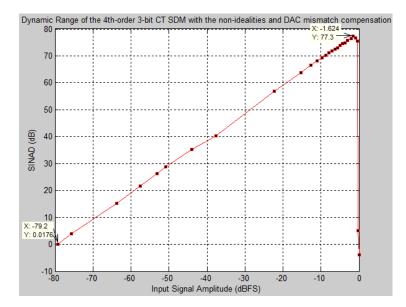

Combining all the issues, the modulator achieves the SNDR 75.02dB, dynamic range 77.58dB over signal bandwidth 25MHz at system level. The modulator with a SNDR 75.71 dB, dynamic range 76.14 dB over signal bandwidth 12.5MHz has been verified at system level together with the schematic design of the first integrator in 90nm CMOS technology.

# Acknowledgement

I would like to thank Dr. Ana Rusu and Dr. Gabriele Manganaro giving me the chance to do a research on such an interesting and challenging topic. I sincerely appreciate their kindly instructions during my thesis work.

I also would like to thank for the helps from Saúl Alejandro Rodríguez Dueñas, Julian Garcia and Tao Sha, the nice colleagues worked together with me in RamSiS group.

# **List of Figures**

Figure 1.1 Basic diagram of a direct conversion wireless receiver

Figure 2.1 Block diagram of an oversampling A/D converter

Figure 2.2 Output spectrum of a first-order sigma-delta modulator

Figure 2.3 Basic architecture and Linearized model of a  $\Delta\Sigma$  A/D modulator

Figure 2.2 Fourth-order sigma-delta modulators with feedforward and feedback compensation

Figure 2.3 NTF of fifth-order sigma-delta modulator with feedforward compensation (a) with local feedback, and (b) without local feedback

Figure 2.4 Fourth-order sigma-delta modulators with a combination of feedforward and feedback

Figure 2.5 Common DAC feedback impulse responses and the corresponding laplace transforms (a) NRZ DAC (b) RZ DAC

Figure 2.6 Feedback DAC pulse shaping with clock jitter

Figure 2.7 Delayed NRZ pulse as a linear combination

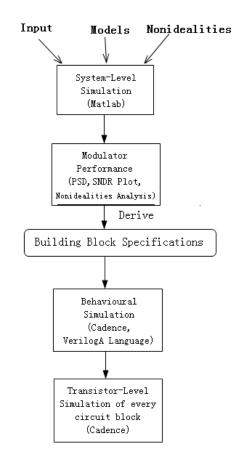

Figure 2.8 Typical top-down design flow for continuous-time modulators

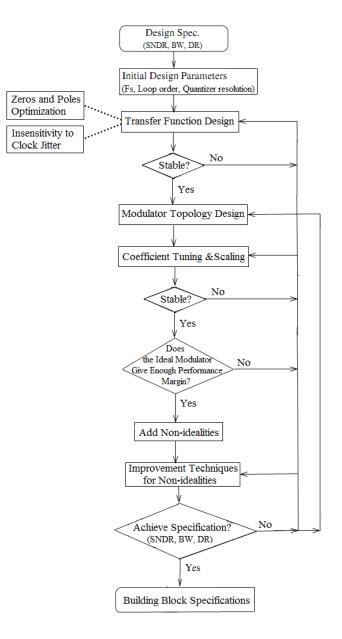

Figure 2.9 SYstem-level design flow of continuous-time modulator

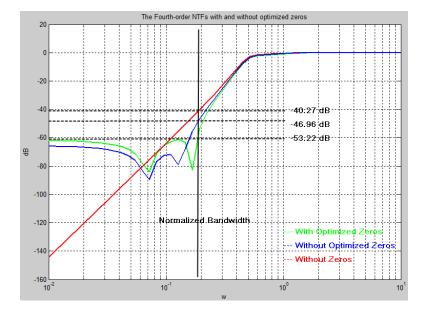

Figure 3.10 The fourth-order NTFs with and without optimized zeros

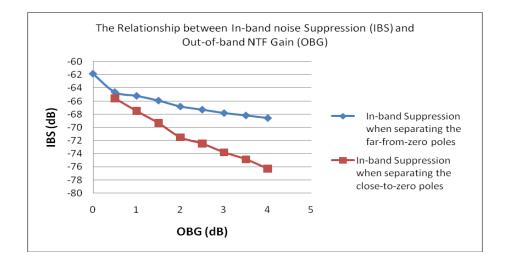

Figure 3.11 The relationship between In-band noise suppression (IBS) and out-of-band NTF gain (OBG)

Figure 3.12 Model used in root locus analysis

Figure 3.13 Root locus of a fourth-order modulator with different sets of ntfs

Figure 3.14 Comparison between the simulated psd and theoretical PSD

Figure 3.15 Pole zero location and root locus of the more accurate NTF

Figure 3.16 Illustration of excess loop delay on NRZ DAC pulse

Figure 3.17 The effect of excess loop delay on maximum stable amplitude (different NTFs with different IBS)

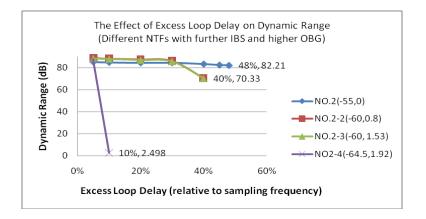

Figure 3.18 The effect of excess loop delay on dynamic range (different NTFs with different IBS)

Figure 3.19 The effect of excess loop delay on maximum stable amplitude (different NTFs with further IBS and higher OBG)

Figure 3.20 The effect of excess loop delay on dynamic range (different NTFs with further IBS and higher OBG)

- Figure 3.21 Classical ELD compensation

- Figure 3.22 ELD compensation using a digital differentiator

- Figure 3.23 Dynamic range vs excess loop delay

- Figure 3.15 Model of clock jitter

- Figure 3.16 PSD of the modulator with different clock jitter deviation

- Figure 3.17 The effect of clock jitter on SNDR (different NTFs with different IBS)

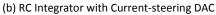

- Figure 3.18 RC integrators with DAC feedback for continuous time implementation

- Figure 3.19 N-bit current-steering DACs with binary weighted coded and thermometer code

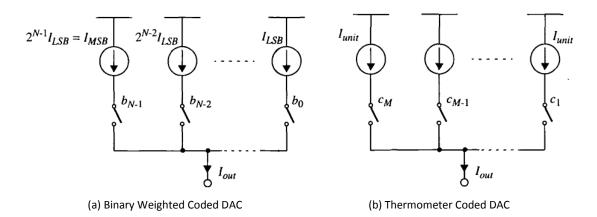

- Figure 3.20 Modeling of current source with error current source  $riangle I_i$

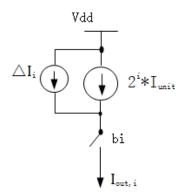

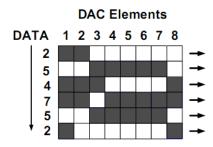

- Figure 3.21 Unit-element DAC with randomized element selection

- Figure 3.22 Illustration of DWA

- Figure 3.23 The DWA DAC

- Figure 3.24 Model of DWA DAC

- Figure 3.24 The effect of DAC Mismatch on SNDR

- Figure 3.26 The effect of time constant variance on IBN and SINAD

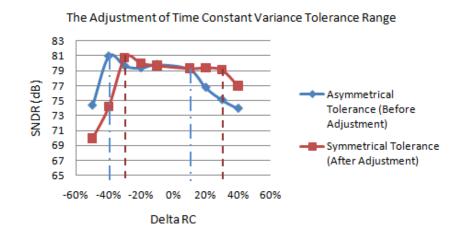

- Figure 3.25 The adjustment of time constant variance tolerance range

- Figure 3.28 Active RC integrator used in CT SD modulators

- Figure 3.29 System-level description of a real integrator

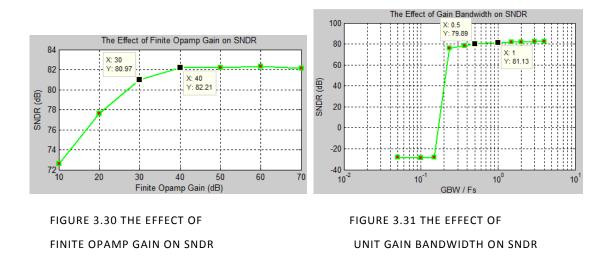

Figure 3.26 The effect of finite opamp gain on SNDR

Figure 3.27 The effect of unit gain bandwidth on SNDR

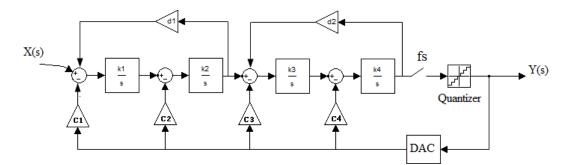

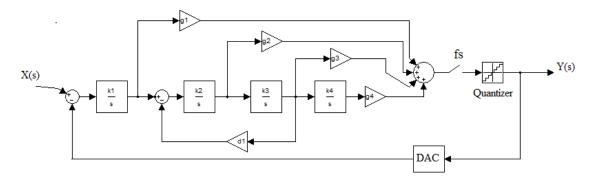

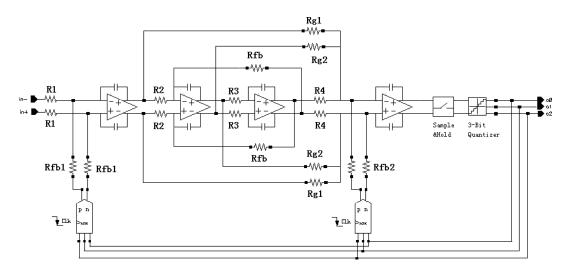

Figure 4.28 Fourth-order three-bit continuous-time sigma-delta modulator

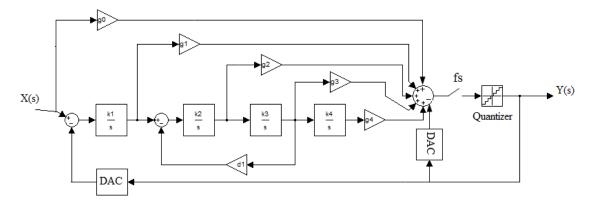

Figure 4.29 Fourth-order three-bit continuous-time sigma-delta modulator with excess loop compenstation and feedforward g0

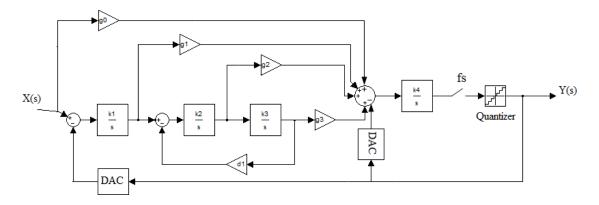

Figure 4.30 Fourth-order three-bit continuous-time sigma-delta modulator with the summation operation moved forward

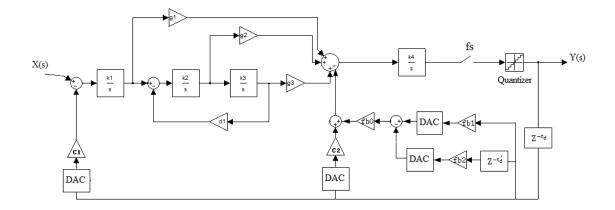

Figure 4.31 Fourth-order three-bit continuous-time sigma-delta modulator

Figure 4.32 Top level circuit diagram of the continuous-time sigma-delta modulator

Figure 4.6 Output power spectrum density in Ideal case, normailized to the maximum power

Figure 4.7 Output powder spectrum density with all non-idealities added, normalized to the maximum power

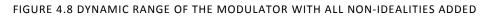

Figure 4.8 Dynamic range of the modulator with all non-idealities added

Figure 4.9 Two tone test of the modulator

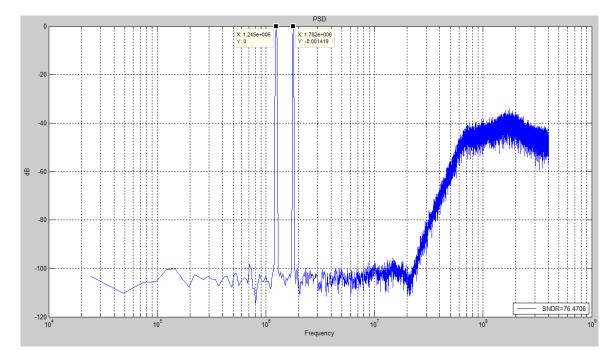

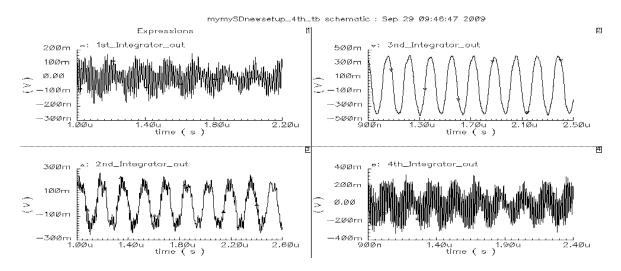

Figure 4.10 Output power spectrum of The modulator using VerilogA blocks

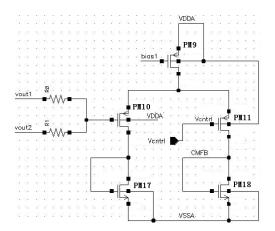

Figure 5.33

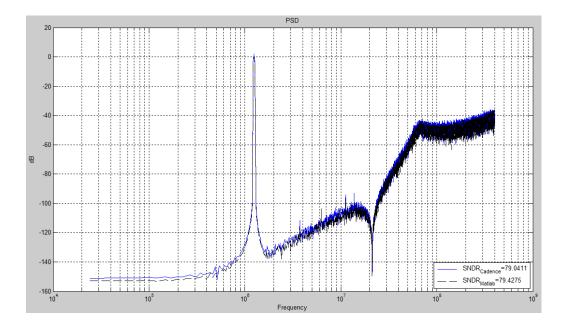

Figure 5.34 The schematic of fully differential opamp

Figure 5.35 The schematic of CMFB circuit

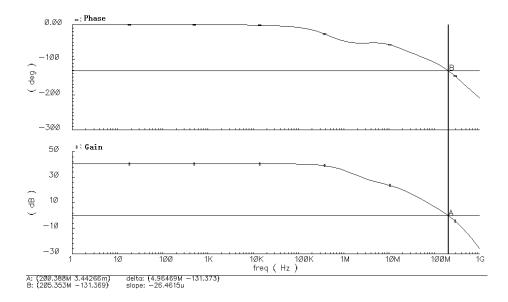

Figure 5.36 Open-loop frequency response of the amplifier

Figure 5.37 Output power spectrum of the modulator using VerilogA blocks

Figure 5.38 Output power spectrum of the co-simulation

# **List of Tables**

Table 3.1 the critical gain and overloading input level

- Table 3.2 Decimal, binary offset, themometer code representations

- Table 3.3 Time constant tolerance relative to different delay compensation

- Table 3.4 The effect of finite output swing

- Table 4.5 Survey on the previous work of continuous-time sigma-delta modulator

- Table 4.6 Coefficients of the modulator

- Table 4.7 DC gain and unit gain bandwidth of integrators

- Table 4.8 Nonidealities summary

- Table 4.9 DC gain and unit gain bandwidth of integrators

- Table 4.10 Performance summary

- Table 5.11 Specifications for the opamp

- Table 5.12 Circuitry parameters of two-stage fully differential amplifier

- Table 5.13 Circuitry parameters of CMFB amplifier

# **List of Abbreviations**

- CT Continuous Time

- DT Discrete Time

- DAC Digital to Analog Converter

- A/D Analog-Digital

- ADC Analog to Digital Converter

- DR Dynamic Range

- OSR Over Sampling Ratio

- SNAD Signal to Noise and Distortion

- SFDR Spurious-Free Dynamic Range

- PSD Power Spectrum Density

- NTF Noise Transfer Function

- STF Signal Transfer Function

- IBS In-band noise suppression

- OBG out-band gain

- ELD excess loop delay

- INL Integral Non-Linearity

- LSB Least Significant Bit

- Opamp Operational Amplifier

- CMFB Common Mode Feed Back

# Contents

## Abstract

Acknowledgement

List of Abbreviations

List of Figures

List of Tables

| 1 | Introduction            | 1 |

|---|-------------------------|---|

|   |                         |   |

|   | 1.1 Background          | 1 |

|   |                         |   |

|   | 1.2 Thesis Organization | 2 |

|   | 12 meas 0.8m.2dion      |   |

| 2 | Overview of Continuous-time Sigma-delta Modulator  | 3  |

|---|----------------------------------------------------|----|

|   | 2.1 Overview                                       |    |

|   | 2.2 Performance metrics                            | 5  |

|   | 2.3 Design Choices                                 | 7  |

|   | 2.3.1 OSR Selection                                | 7  |

|   | 2.3.2 Multi-bit Quantizer and High Loop Order      | 7  |

|   | 2.3.3 Multi-loop Topology VS. Single-loop Topology | 8  |

|   | 2.3.4 Feedforward VS. Feedback                     | 8  |

|   | 2.3.5 Feedback pulse of DAC                        | 10 |

|   | 2.4 Design Methodology                             | 12 |

| 3 D | Design Issues of | Continuous-time Sigma-delta Modulators1 | .5 |

|-----|------------------|-----------------------------------------|----|

|-----|------------------|-----------------------------------------|----|

|   | 3.1 Transfer Function15                                     |

|---|-------------------------------------------------------------|

|   | 3.1.1 NTF Zero Optimization15                               |

|   | 3.1.2 NTF Pole Optimization17                               |

|   | 3.2 Stability                                               |

|   | 3.2.1 Root Locus                                            |

|   | 3.2.2 NTF Aggressiveness21                                  |

|   | 3.3 Excess Loop Delay22                                     |

|   | 3.3.1 Excess Loop Delay, NTF Aggressiveness and Stability22 |

|   | 3.3.2 Compensation of Excess Loop Delay25                   |

|   | 3.4 Clock Jitter27                                          |

|   | 3.5 Multi-bit DAC Mismatch                                  |

|   | 3.5.1 DAC Architecture                                      |

|   | 3.5.2 Dynamic and Element Matching                          |

|   | 3.6 Time Constant Variance                                  |

|   | 3.7 Other Non-idealities                                    |

|   | 3.7.1 Finite Opamp Gain                                     |

|   | 3.7.2 Finite Amplifier Gain-Bandwidth Product40             |

|   | 3.7.3 Integrator Output Swing42                             |

|   | 3.7.4 Thermal Noise42                                       |

|   |                                                             |

| 4 | System Level Design43                                       |

|   | 4.1 System Level Parameters43                               |

|   | 4.2 Loop Filter Architecture44                              |

|   | 4.3 Architecture Optimization45                             |

|   | 4.4 Loop Filter Design48                                    |

| 4.5 Simulation Results50 |

|--------------------------|

|--------------------------|

| 5 | Circuit Level Design                                           | .54 |

|---|----------------------------------------------------------------|-----|

|   | 5.1 Transistor level of the OpAmp in the First Integrator      | .54 |

|   | 5.2 Design Analysis and Equations                              | .55 |

|   | 5.3 Circuit Design Challenges and Specifications of the Opamp  | 57  |

|   | 5.4 Summary of the Circuitry Parameters and Simulation Results | .58 |

|   |                                                                |     |

| 6 | Conclusion and Future work | .61 | L |

|---|----------------------------|-----|---|

|---|----------------------------|-----|---|

# Reference

# **1** Introduction

### 1.1 Background

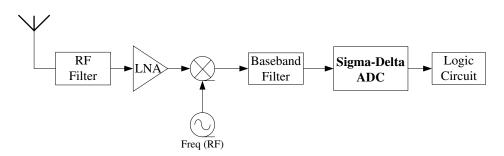

Analog-to-digital converters (ADCs) are widely used in wireless applications. Modern wireless base-station receivers require the ADCs with bandwidth up to 20 MHz and resolutions of 10-14 bits or better. The evolving research toward the development of ADCs with higher speeds and higher resolutions is being equally driven by the demand of high-speed wire line and wireless communication services. 1.1 shows the basic diagram of a popular direct conversion wireless receiver which employs a sigma-delta ADC.

FIGURE 1.1 BASIC DIAGRAM OF A DIRECT CONVERSION WIRELESS RECEIVER

In such systems, pipeline ADCs are usually employed. Recently continuous-time sigma-delta (CT  $\Sigma\Delta$ ) modulators become attractive. Compared with Nyquist rate ADCs, oversampling ADCs trade digital signal processing complexity for relaxed requirements on the analog components <sup>[38]</sup>. Delta-Sigma analog-to-digital converters (ADCs) are widely used in wireless applications <sup>[1,2,3,4]</sup> due to their oversampling, high dynamic range, and low power consumption characteristics.

Most reported MHz range sigma-delta modulators are implemented using switched-capacitor(SC) techniques<sup>[1,2,13-18]</sup>, mainly due to mature design methodologies and robustness. The discrete-time Sigma-Delta ADC offers a good degree of accuracy. But the circuit speed is limited by the settling of switched-capacitor integrator.

Compared with the traditional discrete-time (DT) counterparts, the continuous-time (CT) sigma-delta ADCs have the advantages of higher speed and lower power consumption. Absence of stringent settling requirements enables CT modulators to digitize signals up to several hundreds MHz. Moreover, they provide implicit anti-alias filtering, thus reducing the need for explicit anti-alias filtering prior to the modulator. Input-signal sampling errors, like settling error, charge injection and some other discrete-time problems do not exist in continuous-time circuits.

However, continuous-time sigma-delta modulators also face a lot of design challenges. They are very sensitive to clock jitter, excess loop delay and DAC mismatch. They suffer from the large loop coefficient variations due to the process variations of resistors and capacitors. All these issues limit their overall performance.

Some early studies either have high resolution for low bandwidth <sup>[20-24]</sup>, or have high bandwidth but low resolution <sup>[25-28]</sup>. In recent years, more and more work success in both the wide bandwidth and the high resolution. <sup>[29-35]</sup> There are still lots of space for improvement in continuous-time sigma-delta modulator design.

This thesis work targets a 75dB dynamic range, 25MHz input signal bandwidth continuous-time sigma-delta modulator. The most important non-idealities of continuous time sigma-delta modulator, such as clock jitter, excess loop delay, DAC mismatch and time constant variance are considered. Their effects are analyzed and techniques to compensate these effects are studied at system level using MATLAB environment.

# **1.2 Thesis Organization**

The thesis work covers the theoretical analysis, the system level and the circuit level design of a wideband, high resolution continuous-time sigma-delta A/D converter.

Chapter 2 gives an overview of sigma-delta A/D converters, including performance metrics, design choices and methodology.

Chapter 3 analyses the issues for continuous-time sigma-delta A/D modulators. Effects of various non-idealities and potential solutions to deal with them are discussed.

Chapter 4 presents the details of system level design of the modulator, including the simulation results in Matlab and Cadence.

Chapter 5 covers the details of circuit level designs, including the transistor level design of the first integrator.

Chapter 6 concludes the thesis project and proposes recommendations for future improvement of this work.

## 2 Overview of Continuous-time Sigma-delta Modulator

This chapter gives an overview of continuous-time sigma-delta modulator design. It begins with an introduction of the background knowledge. Then the performance metrics, which are used to evaluate the modulator performance, are described. After that, the design choices are discussed, which become the main considerations for composing the sigma-delta modulator architecture. Finally, the design methodology of continuous-time sigma-delta modulator is presented.

#### 2.1 Overview

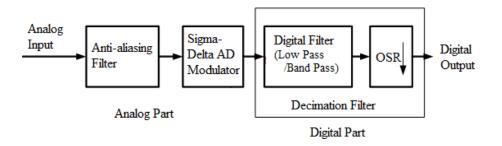

The system architecture of a general oversampling sigma-delta modulator is shown in Figure 2.1. The analog input first passes through an anti-aliasing filter to attenuate out-of-band frequency components so that its output becomes band-limited and, aliasing due to sampling inside the following sigma-delta A/D modulator can be suppressed. The sigma-delta A/D modulator converts the analog signal to a high speed, low-resolution digital signal. The last stage, called the decimation filter, converts the modulator output into a high-resolution digital signal at a lower speed usually equal to twice the frequency of the desired signal bandwidth.

FIGURE 2.1 BLOCK DIAGRAM OF AN OVERSAMPLING A/D CONVERTER<sup>[36]</sup>

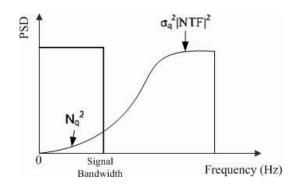

Sigma-delta A/D modulators employ oversampling techniques to push quantization noise and errors due to imperfect analog circuits into a higher frequency band. Noise shaping techniques shape the spectral density such that most of the quantization noise power is outside the band of interest, shown in Figure 2.2 with a first-order sigma-delta modulator. The noise power is then removed by digital filtering so that high in-band signal-to-noise ratio can be obtained.

FIGURE 2.2 OUTPUT SPECTRUM OF A FIRST-ORDER SIGMA-DELTA MODULATOR

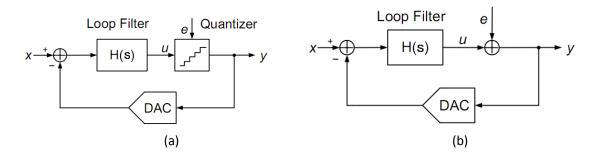

Figure 2.3 shows the basic block diagram of a sigma-delta modulator and its corresponding linear model.

FIGURE 2.3 BASIC ARCHITECTURE AND LINEARIZED MODEL OF A  $\Delta\Sigma$  A/D MODULATOR <sup>[37]</sup>

The sigma-delta analog-to-digital converter consists of three important components:

#### 1. A loop filter or loop transfer function H(s)

The loop filter has large gain within the signal band while it attenuates out-of-band signals. A loop filter is realized with continuous-time integrators in a CT implementation.

2. A clocked quantizer

The quantizer is a strongly-nonlinear circuit in an otherwise linear system. Thus the sigma-delta A/D modulators cannot be considered as a linear system. However, if the inherent quantization noise can be modeled as white noise, the nonlinear quantizer can thus be approximated by a linearized model, as shown in Figure 2.3(b).

#### 3. A feedback digital-to-analog converter (DAC)

The feedback DAC is employed to convert the digital modulator output to analog and subtract it from the modulator input. It is normally implemented with a charge-redistribution DAC in DT converters while current-steering DACs are used in CT converters.

In Figure 2.3, the quantizer is replaced by an adder. The quantization noise is represented by e, which assumed to be independent of the signal input x. The output of the modulator may now be written in terms of the two inputs X(s) and E(s) as

$$Y(s) = \frac{H(s)}{1 + H(s)}X(s) + \frac{1}{1 + H(s)}E(s)$$

(2.1.1)

$$Y(s) = STF(s) \times X(s) + NTF(s) \times E(s)$$

(2.1.2)

where STF(s) and NTF(s) are the signal transfer function and noise transfer function respectively. Seen from equation (2.1.1), the poles of H(s) become the zeros of NTF(s), hence inside the input signal bandwidth where H(s) >>1,

$$Y(s) \approx X(s)$$

(2.1.3)

In other words, the input and output spectra are in greatest agreement at frequencies where the gain of H (s) is large.

#### **2.2 Performance metrics**

This section reviews the performance metrics, such as SNDR, dynamic range and so on, which are needed to evaluate the sigma-delta modulators performance.

Signal-to-noise ratio (SNR) is the ratio of the RMS signal amplitude to the RMS value of the noise spectral components, excluding the signal harmonics and leaving only the noise terms.

$$SNR = 10log\left(\frac{Signal_{RMS}}{Noise_{RMS}}\right) [45]$$

(2.2.1)

Signal-to-Noise-and-Distortion Ratio (SNDR) is the ratio of the rms signal amplitude to the noise spectral components, including harmonics. SINAD is a good indication of the overall dynamic performance of an ADC because it includes all components which make up noise and distortion.

$$SNDR = 10log\left(\frac{Signal_{RMS}}{Noise_{RMS} + Distortion_{RMS}}\right) [45]$$

(2.2.2)

SNDR is often converted to effective-number-of-bits (ENOB) using the relationship for the theoretical SNR of an ideal N-bit ADC, SNR = 6.02N + 1.76 dB. The equation is solved for N, and the value of SNDR is substituted for SNR:

$$ENOB = \frac{SINAD - 1.76 \, dB}{6.02}$$

[45] (2.2.3)

Note that equation (2.2.3) assumes a full-scale input signal. A full-scale input is one whose magnitude equals the maximum magnitude of the quantizer feedback, assuming a quantizer whose output is centered at 0. However, due to the possible overloading and stability problem, the input signal usually cannot be as large as full-scale amplitude. If the signal level is reduced, the value of SNDR decreases and the ENOB decreases. It is necessary to add a correction factor for calculating ENOB at reduced signal amplitudes as shown in equation (2.2.4):

$$ENOB = \frac{SNDR_{measured} - 1.76 \text{ dB} + 20\log\left(\frac{Fullscale Amplitude}{Input Amplitude}\right)}{6.02} \quad (2.2.4)$$

The oversampling ratio (OSR) is defined as the ratio between the sampling frequency fs and the Nyquist frequency fn, which is double of the signal bandwidth fb.

$$OSR = \frac{f_s}{f_n} = \frac{f_s}{2f_b}$$

[36] (2.2.5)

Dynamic range (DR) is the ratio in power between the maximum input signal level that the modulator can handle and the minimum detectable input signal.

Practically, the maximum input signal level is the input level where the SNDR drops 3 dB beyond the peak. For an analog-to-digital converter (ADC), if the signal is too large, it will over-range the ADC input. If it is too small, the signal will get lost in the quantization noise of the converter.

To actually find the DR for a given modulator, SNDR is plotted against input amplitude. The input amplitude range which gives  $SNDR \ge 0$  is precisely the dynamic range. Meanwhile, the maximum SNDR can be easily found from the plot.

Signal-to-quantization-noise-ratio (SQNR) can be expressed as a function of OSR, number of bit in the quantization (N), and loop order (L), as follows. <sup>[38]</sup>

$$SQNR = \frac{3}{2} \left( \frac{2L+1}{\pi^{2L}} \right) (2^N - 1)^2 \times OSR^{2L+1}$$

(2.2.6)

This is useful to asses some of the design parameters such as L or OSR. But the overall DR needs to account for device noise and noise induced by clock phase noise as these may be dominating in some cases.

Spurious-free dynamic range (SFDR) is the difference, expressed in dB, between the rms value of the input signal and the peak spurious signal at the output spectator. A spurious signal is any signal present in the output spectrum that is not present at the input. SFDR is a useful metric in communication applications, where the distortion component can be much larger than the signal of interest due to the intermodulation of unwanted interferential signals.

Another important metric is intermodulation distortion, which is a multi-tone distortion product that results when two or more signals are present at the input of a non-linear device. Especially for sigma-delta modulator when the input is a sine wave, strong higher order harmonics fall outside the signal band and will be filtered, leading to the wrong conclusion that the modulator is linear. Two-tone tests are applied to assess the distortion of the modulator. In these tests, the intermodulation tones fall close to the input tones, hence within the signal band.

# **2.3 Design Choices**

#### 2.3.1 OSR Selection

Extending the sigma-delta A/D converters to broadband applications requires lowering the oversampling ratio (OSR) in order to be realizable within the nanometer CMOS technologies and to meet a moderate power budget. For sigma-delta modulators with signal bandwidth up to megahertz range, the clock frequency cannot be increased without reducing OSR.

#### 2.3.2 Multi-bit Quantizer and High Loop Order

The high resolution at a low OSR can be achieved either: 1) by using a higher order loop filter, and/or 2) by increasing internal quantizer resolution.<sup>[24]</sup>

The SNDR improvement gained by increasing the loop filter order however leads to the stability problem. The integrator gain or maximum input amplitude should be reduced to maintain the stability when the loop order is increased.

Another way to achieve high resolution is to use multi-bit internal quantization. There are several benefits of the multi-bit quantizer. Multi-bit quantization enhances modulator stability as well as relaxes slew rate and settling requirements on the operational amplifiers. More than 20log<sub>10</sub>(2N-1) dB dynamic range improvement can be expected compared with single-bit quantization. Then a more aggressive noise-shaping transfer function can be employed to suppress the in-band noise, with the benefit of extra dynamic range. Besides, multi-bit quantization lowers the clock jitter sensitivity if a NRZ multi-bit DAC is used. However, the linearity of a multi-bit sigma-delta modulator is limited by the multi-bit

feedback D/A converter. Linearization techniques are required to correct the mismatch errors in the DAC elements.

#### 2.3.3 Multi-loop Topology VS. Single-loop Topology

To achieve high-order noise shaping without inherent stability problems in single-loop higher-order sigma-delta modulator, multi-loop (MASH) topologies, with two or three cascaded loops of first-order and/or second-order may be used for sigma-delta modulators. The basic idea of MASH, taking a two-stage modulator as an example, is to feed the quantization error of the first stage into the second stage. The digital outputs of the two stages are combined through digital cancellation logic so that the first stage quantization error is removed and only the noise shaped second stage quantization error is left. <sup>[24]</sup>

In multi-loop cascaded topologies, perfect matching is required between the analog noise-shaping transfer function and the digital noise cancellation logic. Thus, multi-loop topologies are viable solutions for switched-capacitor implementations, thanks to the excellent matching properties of on-chip capacitors. However, for continuous-time multi-loop cascaded implementations, large RC time constant variation introduces mismatch. Significant SNDR degradation may result. On the other hand, single-loop topologies are more tolerant of non-idealities such as RC time-constant variation and more suitable for continuous-time sigma-delta modulator design.

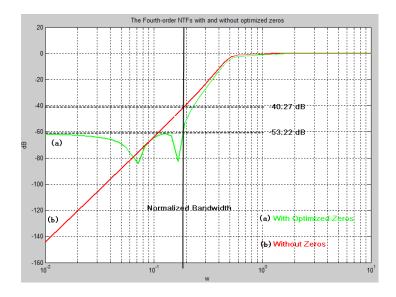

#### 2.3.4 Feedforward VS. Feedback

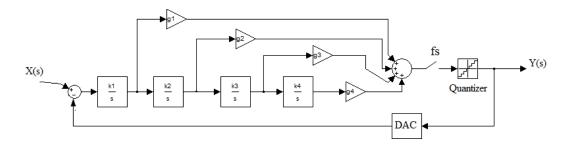

There are two commonly used loop filter architectures for single-stage modulators, CIFF (chain of integrators with weighted feedforward summation) and CIFB (chain of integrators with distributed feedback) <sup>[38]</sup>. The examples of the 4<sup>th</sup>-order sigma-delta modulators with feedforward and feedback compensation are shown in Figure 2.4(a) and (b) respectively.

(a) Modulator with Feedforward Compensation

(b) Modulator with Feedback Compensation

FIGURE 2.4 FOURTH-ORDER SIGMA-DELTA MODULATORS WITH FEEDFORWARD AND FEEDBACK COMPENSATION<sup>[42]</sup>

As it can be seen from Figure 2.4(b), the feedback structure requires several DACs feeding back to each integrator output, though it does not need a large adder before the quantizer.

In the feed-forward structure, only one DAC is needed in the feedback path, which is more area-efficient. However, the feed-forward architecture requires a multi-input adder to sum all feedforward branches before the quantizer. Due to the requirement of RC/GmC time constant tuning, the active adder is usually preferred for the continuous-time modulator. But the adder will become the speed bottleneck of the whole loop as well as consume much power.

One more advantage of the feedforward structure is the small output swing of the first integrator. With a certain output range, the first integrator allows a bigger loop gain, and hence lower performance requirements on the following stages.

Generally, the signal transfer function (STF) of a feedforward architecture has an out-of-band peaking at a certain frequency. This implies that at the peaking frequency the maximum stable input level is reduced by the gain of the peaking. As a result, the dynamic range is reduced and a lot of big out-of-band interferers exist. The feedback filter does not suffer from significant peaking.

Besides the above fundamental topologies, local feedback paths can add zeros to noise transfer function, which benefit to shift the DC gain of the integrators to a finite resonance frequency. In this way, the gain can be spread more equally in the signal band. The quantization noise at the end of the signal band can be suppressed more, as shown in Figure 2.5. With local feedback paths, it is possible to implement an inverse Chebyshev NTF rather than a Butterworth NTF.<sup>[42]</sup>

FIGURE 2.5 NTF OF FIFTH-ORDER SIGMA-DELTA MODULATOR WITH FEEDFORWARD COMPENSATION (A) WITH LOCAL FEEDBACK, AND (B) WITHOUT LOCAL FEEDBACK

An example of the fifth-order modulators with local feedback paths is shown in Figure 2.6.

(a) Modulator with Feedforward Compensation and Local Feedback

(b) Modulator with Feedback Compensation and Local Feedback

FIGURE 2.6 FOURTH-ORDER SIGMA-DELTA MODULATORS WITH A COMBINATION OF FEEDFORWARD AND FEEDBACK

#### 2.3.5 Feedback Pulse of DAC

Before choosing the transfer function, the DAC pulse shape usually has to be decided. Continuous-time sigma-delta modulators are sensitive to every deviation from the ideal shape of the DAC feedback pulse, as the analog continuous-time feedback waveform is integrated over time. Any non-idealities and non-uniformities will tend to degrade performance.

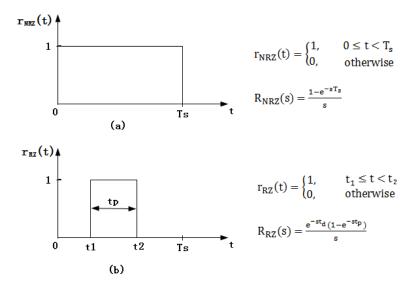

The two most common DAC feedback pulses are NRZ (None-return-zero) pulse, and RZ (Return-zero) pulse, shown in Figure 2.7. Their waveforms can be generated by simply switching the feedback current or voltage sources on and off using the clock and its edges [43].

FIGURE 2.7 COMMON DAC FEEDBACK IMPULSE RESPONSES AND THE CORRESPONDING LAPLACE TRANSFORMS (A) NRZ DAC (B) RZ DAC

The rectangular feedback realization arises one major non-ideality, the sampling clock jitter. Any timing jitter in the sampling clock modulates directly the ADC decision point as well as the rising and falling edges of the DAC output, and thus the quantity of the DAC feedback signals. The resulting DAC error is directly introduced into the modulator input, thus clock jitter can limit the overall sigma-delta modulator performance.

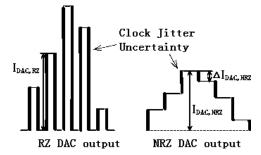

It is meaningful to compare NRZ feedback and RZ feedback. NRZ DAC pulse is preferred because of low sensitivity to clock jitter. As illustrated in figure 2.8, assuming that the duty cycle of the RZ pulse shaping is 0.5, the amplitude of the RZ DAC has to be twice as high as that of the NRZ DAC, to keep the area of the DAC output waveform unchanged. Thus, with the same clock jitter variance, the modulator with NRZ feedback can achieve higher SNR than that with RZ feedback. If the noise introduced by the random clock jitter is assumed to have a white spectrum, the SNR improvement (in dB) of NRZ pulse shaping over RZ pulse shaping can be derived as <sup>[24]</sup>

$$SNDR_{NRZ-RZ} = 10log_{10} \left( \frac{8 \times \delta_{I_{DAC,NRZ}}^2}{\delta_{\Delta I_{DAC,NRZ}}^2} \right)$$

(2.3.3)

Where  $\delta_{I_{DAC,NRZ}}^2$  is the variance of the NRZ DAC output current, and  $\delta_{\Delta_{I_{DAC,NRZ}}}^2$  is the variance of  $\Delta I_{DAC,NRZ}$ .

Besides, the RZ feedback DAC pulse also has the advantage of reducing distortion and makes it more linear. A lot of the distortion performance in a DAC is associated with the transient seen at the output when the DAC swings from one output level to the next one. In a RZ DAC the output always starts from ground and return to ground, hence there is no memory of the prior sample, reducing code dependence and distortion. Also the DAC can be designed in such a way that all internal node glitches die out before the output is turned on. It allows the designer to mask all internal code-dependent glitches, keeping them inside the DAC, before the output is generated, hence making it more linear. Conversely, in an NRZ DAC the output is always active so the transient could vary depending on the present output level and the next one, which may cause distortion. Any undesired glitch originating in an internal node of the DAC will be visible at the output.

FIGURE 2.8 FEEDBACK DAC PULSE SHAPING WITH CLOCK JITTER

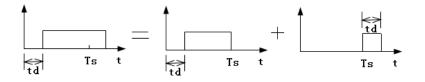

Another unavoidable problem is the excess loop delay, which is caused by the non-zero switching time of the quantizer latch and the feedback DAC <sup>[37]</sup>. The delay in the feedback path changes the overall loop transfer function in a way that moves the poles of the linearized equivalent system toward the right plane, hence degrading its stability. If the delay becomes excessive, the loop will degrade its stability and could oscillate. The delayed NRZ pulse can be presented as a linear combination of two pulses, as shown in Figure 2.9.

FIGURE 2.9 DELAYED NRZ PULSE AS A LINEAR COMBINATION

#### 2.4 Design Methodology

The typical top-down design flow for continuous-time sigma-delta modulator is shown in Figure 2.10. Firstly, the ADC has been designed at system level using Matlab/Simulink. Various high-level simulations have been performed including non-ideal behaviors of the sigma-delta ADC components in order to count for the real circuit behavior of the design. The modulator performance, such as desired SNDR and stability must be achieved and the specifications for every building block derived. After that, the sigma-delta ADC is implemented using behavioral description language in Cadence environment. After validating the model at behavioral level, the most critical block of the ADC was replaced by its circuit level implementation using 1.2V 90nm CMOS technology.

FIGURE 2.10 TYPICAL TOP-DOWN DESIGN FLOW FOR CONTINUOUS-TIME MODULATORS

At the system level, the design follows the flow shown in Figure 2.11. The design specifications are defined first. According to the specifications, initial design parameters are chosen, including sampling frequency, loop order, quantizer resolution and the DAC feedback pulse.

The transfer function is designed directly in continuous-time domain. Zeros and poles are optimized based on the analysis in Section 3.1. The clock jitter issue is also taken into account during the selection of the transfer function. Before building the topology, stability is predicted using the methodology described in Section 3.2. The modulator topology which

implements the transfer function is designed. Coefficients are tuned and scaled to achieve higher performance. Stability is measured again by checking the signal in time domain as well as using the previous methodology with the actual transfer function realized by the designed topology. During the examination of stability, one of the critical issues, excess loop delay will be analyzed carefully.

When the modulator achieves the required performance with certain margin in the ideal case, various non-idealities are added to examine their effects based on the methods and equations described in Chapter 3. The other main issues, such as DAC feedback mismatch and time constant variance are involved here. Some techniques are explored to compensate the performance degradation. Finally, the building block specifications for the circuit level design are derived.

FIGURE 2.11 SYSTEM-LEVEL DESIGN FLOW OF CONTINUOUS-TIME MODULATOR

# 3 Design Issues of Continuous-time Sigma-delta Modulators

After selecting the basic parameters, such as oversampling ratio (OSR), quantizer number of bits, loop order and DAC feedback pulse, and the modulator topology, the design starts with the transfer function selection. For a modulator design, not only the required signal-to-noise-and-Distortion ratio (SNDR) must be fulfilled, but the stability should also be assured.

The non-idealities, including finite operational amplifier gain, bandwidth, slew rate, quantizer delay, multi-bit feedback DAC element mismatch, loop filter coefficients variation and clock jitter affect the performance and stability of continuous-time sigma-delta modulators. To guarantee a successful design, a thorough understanding of these non-ideal phenomena is required. They will be analyzed by adding them into the ideal architecture.

This chapter discusses the critical design issues, including the transfer function selection, the stability measurement and the analysis of non-idealities. Among the non-idealities, excess loop delay, clock jitter, multi-bit DAC mismatch and time constant variance are four key problems in the design of continuous-time sigma-delta modulators.

## **3.1 Transfer Function**

At the beginning stage, there are two considerations when choosing a transfer function, the required SNDR and stability. A desired modulator should be stable for high input signal amplitude and simultaneously achieve maximum SNDR.

Significant improvement of the SNDR can be obtained by separating zeros over the signal range for high attenuation in the signal band and laying poles far away from the zeros. However, a system can be made more stable by placing poles near to zeros.

For the continuous time sigma-delta modulator, the excess loop delay and clock jitter are two main inevitable problems. The selection of transfer function becomes more complicated when these two effects are taken into account. They will be covered in the following section.

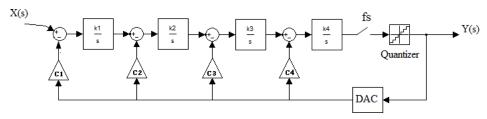

#### 3.1.1 NTF Zero Optimization

Zeros are optimized assuming that the quantization noise is white, and the poles of the NTF have no significant effect on the in-band noise. The zeros are constrained for efficient noise shaping to the signal-band region.

Figure 3.1 shows the frequency responses of the NTFs without zeros, with zeros and with the best optimized zeros, and the simulated SNDR of the modulators with different NTFs. Seen

from the figure, shifting the zeros from dc results in a great SNDR improvement. An even greater benefit can be expected by optimizing the location of zeros of higher-order NTFs.

FIGURE 3.1 THE FOURTH-ORDER NTFS WITH AND WITHOUT OPTIMIZED ZEROS

The optimized zeros can be obtained by the filter design tools embedded in Matlab. They can be chosen according to the normalized cut off frequency and the required in-band noise suppression (IBS). More studies of zeros are done based on the 4<sup>th</sup>-order sigma-delta modulator, which has two pairs of zeros. The four zeros result in three areas of noise floor, the noise floor at low frequency, the noise floor between two zeros, and the noise floor at the edge of the bandwidth. The distance between the two pairs of zeros can have an effect on the noise floor. As the blue line plot in figure 3.1, although a little closer distance of the two pairs of zeros reduces the noise floor between two zeros, it increases the noise floor at the bandwidth edge by about 6.26dB, which can kill the performance largely. Through several simulations, the most optimized zero locations make the noise suppression equal in band, which is important for the suppression of quantization noise at the end of the signal band.

Moreover, the zeros can also be calculated theoretically. As the values of all the NTF zeros is relative to the normalized noise power, given by the integral of the squared magnitude of the NTF over the signal band, the optimal zeros can be found by equating the partial derivatives of the integral to zero. The method chooses  $\pm \sqrt{\frac{3}{7} \pm \sqrt{(\frac{3}{7})^2 - \frac{3}{35}}}$ , which is normalized to the bandwidth rad/ sec, as the optimized zero values for the 4<sup>th</sup>-order sigma-delta modulator. The values are the same with that obtained using the previous method.

#### 3.1.2 NTF Pole Optimization

After the zeros are optimized, the choice of the poles can further reduce the quantization noise power in the signal band by increasing the distance of the poles from zeros, which leads an increase in the out-of-band NTF gain (OBG) at high frequencies, and consequently, leads to an increase in the total quantization noise power. Thus, the system becomes prone to instability.

Looking deeply into a fourth-order modulator, the relationship between the in-band noise suppression (IBS) and the out-of-band NTF gain (OBG) is not exactly a direct proportion. A fourth-order modulator has two pairs of poles. Figure 3.2 plots the relationship between IBS and OBG when adjusting each pair of poles. The simulation is performed based on the architecture shown in Figure 2.4 (a). It can be seen that there is a large difference in the amounts of IBS in two cases at the same OBG steps. The IBS can have a difference of 7.7dB when the OBG is 4dB. This means that it is possible to achieve a higher IBS without increasing the OBG by adjusting the two pairs of poles.

FIGURE 3.2 THE RELATIONSHIP BETWEEN IN-BAND NOISE SUPPRESSION (IBS) AND OUT-OF-BAND NTF GAIN (OBG)

In this section, the zeros and poles are discussed mainly for the purpose of a better in-band noise shaping, as the first step. The critical concern is stability, which is largely determined by the poles. Hence, the location of the poles should be partially based on stability considerations. The problem will be studied in the next section.

# 3.2 Stability

For higher-order sigma-delta modulators, the tendency to instability is an important issue. A system is defined to be stable when all the integrator outputs remain bounded over time. A more stable system allows larger input amplitude.

Because of the non-linear quantizer, it has not been possible to find a mathematical solution for guaranteed loop stability of higher-order modulators. However, an insight to stability can be based on the analysis of limit cycles in order to predict the stability of the system. The first work here is to define the good measure ways used in the design.

Before the analysis, it is necessary to define the overloading input level (OVL), which is an important measure of the stability. The input signal above the overloading input level (OVL) makes the noise shaping useless, and adds more intolerable noise present inside the signal band. To have a comparison with the full-scale level (OdB), the OVL is expressed in dB to reference level (dBFS). In an ideal system, the OVL equals to full-scale level (0dBFS). In a realistic system, the OVL is usually a few dB lower than the full-scale level because of the modulation of the quantization noise with the input signal spectral components. The OVL varies with loop order, loop topology, quantizer resolution and NTF aggressiveness.

#### 3.2.1 Root Locus

After the noise transfer function has been selected, the NTF is analyzed using the linear model first. Although the multi-bit quantizer cannot avoid the non-linearity problem, it is ignored in the first step. There are many ways for linear stability analysis: root locus, bode plot, etc. The root locus is more visible for the effect of the poles and zeros locations on the stability.

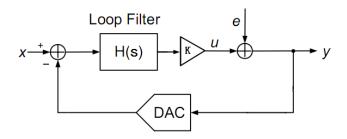

Figure 3.3 shows the model used in the root locus analysis. Before the quantizer, a gain k is inserted to model the effective quantizer gain kq, which is used as the variable gain of the root locus. The open loop transfer function H(s) is needed for the root locus calculation.

FIGURE 3.3 MODEL USED IN ROOT LOCUS ANALYSIS

Using this method, the root locus of a set of NTFs is plotted in Figure 3.4(b). Figure 3.4(a) shows the poles and zeros of the chosen NTFs. The NTFs are chosen as a group of Chebyshev I filters with gradually closer poles to the same zeros.

(a) Poles and Zeros of the NTFs

(b) Root Locus of the NTFs

# FIGURE 3.4 ROOT LOCUS OF A FOURTH-ORDER MODULATOR WITH DIFFERENT SETS OF NTFS

As it can be seen in Figure 3.4, the pair of poles, which is closer to zeros, starts at dc s=(0,0) for kq=0, then goes towards kq=infinite. When kq=1, the pole values are exactly the poles of the chosen NTFs plot in Figure 3.4 (a). The possible instability arises from the poles, which leave the left plane for small quantizer gains kq and enter the right plane at a critical gain kcrit. The four sets of NTFs in the plot achieve a conditional stability, if the quantizer gain is larger than the critical gain. Moreover, for the fourth-order modulator, the other pair of poles, which is far from zeros, is always located inside the right plane. So they do not become a threat to the stability.

The critical gain is the minimum limitation of the effective quantizer gain to keep the system stable. Meanwhile, a high effective quantizer gain corresponds to a small quantizer input signal and thus to a limitation of the modulator input u, since the quantizer output is fixed to the reference. So the critical gain can be used to predict the overloading input level, which reflects the potential of stability. The system with a smaller Kcrit allows a larger OVL. That means the NTFs with a smaller Kcrit have more potential to build a stable system.

The four noise transfer functions are mapped to real modulator architecture for simulation. The OVLs are found as in Table 3.1, which proves the above analysis.

| No. | IBS    | SNDR     | Kcrit | OVL      |

|-----|--------|----------|-------|----------|

| 1   | -50 dB | 79.9 dB  | 0.38  | -1dBFS   |

| 2   | -55 dB | 85.28 dB | 0.401 | -1.4dBFS |

TABLE 3.1 THE CRITICAL GAIN AND OVERLOADING INPUT LEVEL

| 3 | -60 dB | 89.68 dB | 0.405 | -2dBFS |

|---|--------|----------|-------|--------|

| 4 | -65 dB | 92.78 dB | 0.41  | -3dBFS |

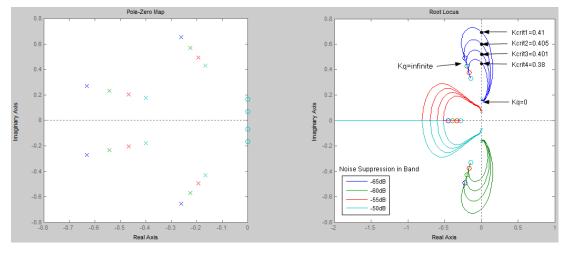

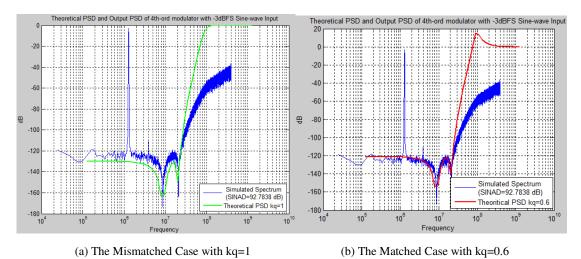

The question is how much accuracy the method provides. To what extent, the linear approach can predict the stability of the real system? As it can be seen in Figure 3.5(a), when the chosen NTF is mapped to the architecture, the simulated output power spectrum does not agree with the theoretical NTF curve closely. The figure is obtained from the simulation of the system with the 4<sup>th</sup> NTF in the above table. The simulated PSD is similar with the theoretical curve in shape, but the in-band noise is about 5 dB higher, and the 3<sup>rd</sup> harmonic distortion can be seen.

FIGURE 3.5 COMPARISON BETWEEN THE SIMULATED PSD AND THEORETICAL PSD

The inconsistence makes the stability measure using root locus less accurate. To take the disagreement between the simulated PSD and the theoretical PSD into account, it is useful to find out the actual NTF realized by the simulated modulator and come back to measure the stability using root locus again. Then the prediction of stability becomes more accurate.

The method is as follows. Assume the NTF chosen at the beginning is  $NTF_1$ , while the actual NTF from the simulation is  $NTF_k$ . As mentioned previously, the  $NTF_1$  has its poles at kq=1. When the input amplitude is lowered, simulations show that the optimal value of the quantizer gain changes slightly. Thus, the  $NTF_k$  can be presented as

$$NTF_{k} = \frac{NTF_{1}}{kq + (1 + kq)NTF_{1}}$$

[39] (3.2.1)

The effective quantizer gain kq is evaluated to achieve the match between the simulated power spectrum and the theoretical plot. In the above example, simulations indicated that a

more accurate NTF with small inputs can be derived if k is assumed to be 0.6. The new result is shown in Figure 3.5(b).

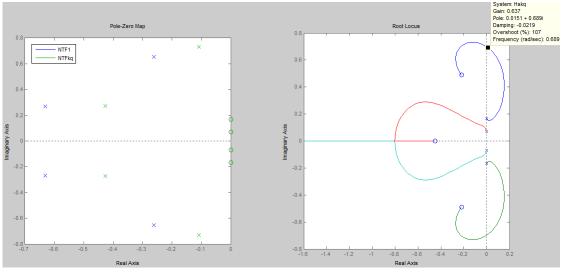

The root locus of the  $NTF_k$  is shown in Figure 3.6. The critical gain increases to 0.637dB, which means that the implemented system is less stable than the previous prediction.

<sup>(</sup>a) Poles and Zeros of the NTF

(b) Root Locus of the NTF

FIGURE 3.6 POLE ZERO LOCATION AND ROOT LOCUS OF THE MORE ACCURATE NTF

In conclusion, the implemented system could be less stable than the theoretical one. It is very dangerous if the stability is only predicted with the theoretical NTF using the linear model. It is necessary to take the nonlinearity effects in the reality into account to get an accurate prediction of the stability.

## **3.2.2 NTF Aggressiveness**

The stability is the cost paid for the system aggressiveness. It is necessary to define the aggressiveness, as the concept will be used frequently in the later analysis.

As it is mentioned in many books, the NTF aggressiveness equals to a higher OBG. However, the conclusion mainly comes from the simulation based on 2<sup>nd</sup>-order sigma-delta modulators, but not exactly true for higher-order modulators which has several pairs of poles.

An aggressive NTF means to move more in-band noise outside, and hence achieve a higher SNDR. This is mainly achieved by a high IBS. A higher OBG can suppress the in-band noise floor further. However, OBG can also be kept flat with the adjustment of pole locations, as mentioned in section 3.1.2. On the other hand, in the system with the same IBS, a higher OBG may sharpen the slop at the bandwidth edge, which benefit to the SNDR. So the NTF aggressiveness must be evaluated by both IBS and OBG.

# 3.3 Excess Loop Delay

Excess loop delay arises because of nonzero transistor switching time, which makes the edge of the DAC pulse begin after the sampling clock edge. Practical comparators have non-zero time to generate the correct outputs. This delay is mainly determined by the comparator design and IC process, together with the finite time for the feedback DAC to respond, and the delay between the quantizer clock edge and valid DAC output.

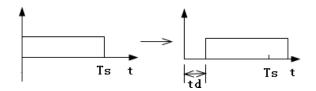

For an NRZ DAC pulse, the excess loop delay can be depicted as in Figure 3.7. <sup>[37]</sup>

FIGURE 3.7 ILLUSTRATION OF EXCESS LOOP DELAY ON NRZ DAC PULSE

The loop delay t<sub>d</sub> can be expressed as a fraction of the sampling period

$$t_d = \beta T_s^{[37]}$$

(3.3.1)

#### 3.3.1 Excess Loop Delay, NTF Aggressiveness and Stability

The main problem caused by excess loop delay is the stability of the modulator. The excess loop delay in an aggressive system is pushing the system easily to instability. As defined in Section 3.2.2, the NTF aggressiveness is associated with both IBS and OBG. So the excess loop delay is examined using NTFs with different IBS and OBS.

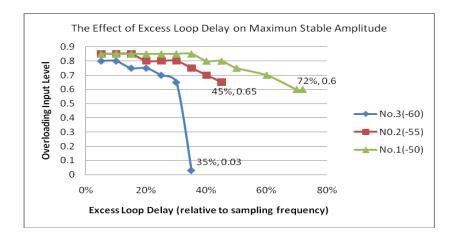

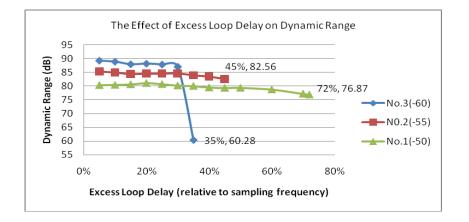

Firstly, a set of NTFs with different IBS and same OBG are simulated. The three NTFs 1-3 in Section 3.2.1 are used again here to check their tolerance for excess loop delay. They have 5 dB differences in IBS and the flat OBG 0dB. Figure 3.8 and Figure 3.9 shows the simulation results. The NTFs are marked by numbers and their IBS (dB). In Figure 3.8 the tolerance to loop delay and OVL of each NTF are indicated near each plot, when in Figure 3.9 the dynamic range is indicated together with the tolerance.

It can be seen that the more aggressive the NTF is, the less tolerance to excess loop delay the system has. The dynamic range of the most aggressive NTF (No.3) drops earliest. NTF No.2 is chosen for the following analysis, because it is moderate aggressive and achieves the dynamic range, which gives enough margins for other non-idealities.

FIGURE 3.8 THE EFFECT OF EXCESS LOOP DELAY ON MAXIMUM STABLE AMPLITUDE (DIFFERENT NTFS

WITH DIFFERENT IBS)

FIGURE 3.9 THE EFFECT OF EXCESS LOOP DELAY ON DYNAMIC RANGE (DIFFERENT NTFS WITH DIFFERENT IBS)

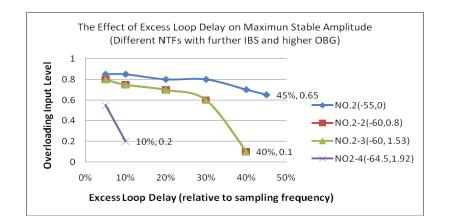

Further improvement in performance can be achieved by increasing the out-of-band gain, which degrades the tolerance to excess loop delay. So it is also meaningful to check the delay tolerance when the OBG is larger than OdB. The simulations are performed using a set of NTFs based on the NTF No.2. The NTFs have the OBG which gradually increases. The IBS is increased from -55dB due to the non-zero OBG. Figure 3.10 and Figure 3.11 show the simulation results. The NTFs are marked by numbers, its IBS (dB) and OBS (dB).

NTFS WITH FURTHER IBS AND HIGHER OBG)

FIGURE 3.11 THE EFFECT OF EXCESS LOOP DELAY ON DYNAMIC RANGE (DIFFERENT NTFS WITH FURTHER IBS AND HIGHER OBG)

It can be seen from the figures, the NTFs No.2-2 and 2-3 have 5 dB IBS more than NTF No.2 due to a higher OBG. But their OVLs drop from 0.8 to 0.6 due to the stability problem caused by the higher OBG. Finally, the benefit of high IBS is counteracted by the decreased OVL. NTF No.2 achieves the same dynamic range because its OVL remains higher than NTFs No.2-2 and 2-3.

When the delay is larger than 30%, NTFs No.2-2 and 2-3 cannot tolerant any more loop delay and the systems go unstable immediately. The NTF No.2 is still stable until the delay is larger than 45%. The NTF No.2-4 with the largest IBS and OBG suffer the worst delay tolerance.

The conclusion here is that, non-zero OBG is of course an easy way to increase the IBS for higher SNDR. However, OBG should be monitored seriously when the system suffers excess loop delay. It would be better to keep OBG flat if the excess loop delay may become large. The above analysis shows that the high OBG does not benefit a lot in my case, so NTF No.2 is kept for the other analysis.

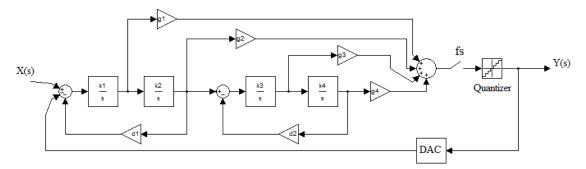

#### 3.3.2 Compensation of Excess Loop Delay

The study of the excess loop delay compensation is simplified based on a second-order feedback architecture. Two main techniques have been used during the research, classical ELD compensation and ELD compensation using a differentiator.

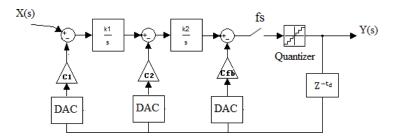

In the classical ELD compensation, one extra DAC feedback path is added from the modulator output to the quantizer input, as shown in Figure 3.12.

FIGURE 3.12 CLASSICAL ELD COMPENSATION

If the loop gains of the modulator without the extra DAC feedback are k1' and k2', the coefficients of the modulator with ELD compensation can be calculated with

$$\begin{cases} K_{1} = \frac{K'_{1}}{1+K'_{1}t_{d}} \\ K_{2} = K'_{2}(1+K'_{1}t_{d}) \\ C_{3} = \frac{1}{2}K'_{2}t_{d}(2+K'_{1}t_{d}) \\ \end{bmatrix} (3.3.1)$$

In this way, the excess loop delay of up to one clock period may be compensated. However, this approach requires at least one additional DAC as well as one differential summing amplifier.

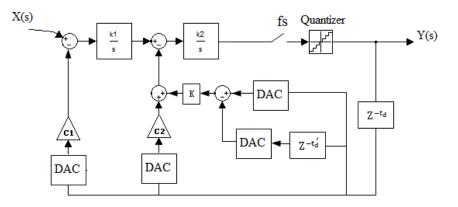

For the ELD compensation using a differentiator, the excess loop delay compensation path is moved from the output of the last integrator to its input, as shown in Figure 3.13.

FIGURE 3.13 ELD COMPENSATION USING A DIGITAL DIFFERENTIATOR [34]

The delay  $t'_{d}$  added to compensate the excess loop delay must meet the requirement (3.3.2)

$$t'_d + t_d \le \frac{1}{f_s}$$

The compensation feedback coefficient K can be calculated with

$$K = \frac{C_3}{t'_d K'_2} [34]$$

(3.3.3)

since for low frequencies

$$1 - z^{-t'_d} \approx \frac{t'_d}{f_s} s_{[34]}$$

(3.3.4)

In this method, the differentiator is realized by an NRZ and a half-delayed return-to-zero DAC. This compensation technique avoids the use of summing amplifier.

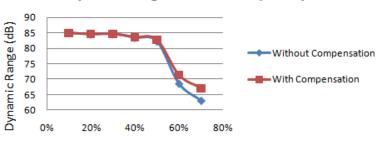

By applying this compensation technique, the dynamic range of the modulator is improved. Table 3.2 and Figure 3.14 show the comparison.

| Delay | Dynamic Range (dB)   |                   |  |  |  |  |

|-------|----------------------|-------------------|--|--|--|--|

|       | Without Compensation | With Compensation |  |  |  |  |

| 10%   | 84.94                | 84.94             |  |  |  |  |

| 20%   | 84.55                | 84.55             |  |  |  |  |

| 30%   | 84.62                | 84.62             |  |  |  |  |

| 40%   | 83.44                | 83.59             |  |  |  |  |

| 50%   | 82.21                | 82.74             |  |  |  |  |

| 60%   | 68.48                | 71.33             |  |  |  |  |

| 70%   | 62.95                | 67.1              |  |  |  |  |

TABLE 3.2 DYNAMIC RANGE VS EXCESS LOOP DELAY

Dynamic Range vs. Excess Loop Delay

Excess Loop Delay (relative to sampling frequency)

FIGURE 3.14 DYNAMIC RANGE VS EXCESS LOOP DELAY

## **3.4 Clock Jitter**

The clock jitter causes a slight random variation in the amount of charge feedback per clock cycle, which causes the out-band noise to fold into the signal band, raising the noise floor and degrading the resolution.

There are two sources of clock jitter, the jitter at the internal ADC input and the timing error of the feedback DAC in the main loop. As the clock jitter of feedback DAC is critical, only this source is considered.

The error caused by clock jitter is the error in the area of the feedback pulses for every sampling period. <sup>[37]</sup> A reason for this is that the feedback pulse is at least integrated once in the loop filter. This integrated value corresponds with the area of the pulses, and hence, only the area is significant at the sampling instants at sampler S, instead of the actual shape of the pulse. For a NRZ feedback pulse, the expression of this area error is

$$\Delta A[n] = (y[n] - y[n-1]) * \Delta T_{DAC}[n]$$

(3.4.1)

The additive error sequence  $e_i[n]$  equals to the area error in the feedback pulses divided by the ideal timing T.

$$e_{j}[n] = \frac{\Delta A[n]}{T} = (y[n] - y[n-1]) * \frac{\Delta T_{DAC}[n]}{T}$$

(3.4.2)

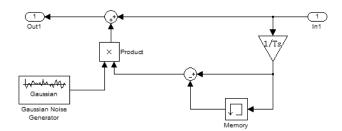

This equation leads to the model in Figure 3.15. The jitter variance is generated by a Gaussian noise source.

FIGURE 3.15 MODEL OF CLOCK JITTER

The clock jitter adds noise in band and raises the in-band noise floor. The Figure 3.16 shows the out power spectrum of the modulator implementing NTF No.2 with three different values of jitter deviation. It can be seen that the noise floor rises gradually when the jitter deviation increases. Although the noise floor of the system with 1% jitter deviation is the same as that of the system without jitter, the noise suppression benefit from separated zeros is reduced. The in-band noise is still dominated by the quantizer noise. With the increasing clock jitter, the notches produced by zeros are covered by the jitter-induced noise, which reduces the SNDR largely.

FIGURE 3.16 PSD OF THE MODULATOR WITH DIFFERENT CLOCK JITTER DEVIATION

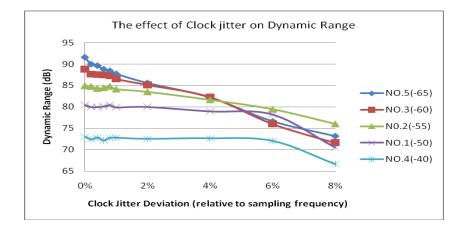

Further simulations are done based on the set of NTFs used in the previous simulation. To show the effects more clearly, two more NTFs (No.4 and 5) are added. They are chosen with the same way as NTF No.1-3, setting different IBS. Figure 3.17 shows the simulation results. In the figure, the NTFs are marked with the number and their IBS.

It can be seen from the figure that the system performance benefits from the high IBS, only when the clock jitter deviation is small. However, when the jitter goes higher, the system with the most aggressive NTF (No.5) suffers first and merges with the plot of NTF No.3. The dynamic range of NTFs No. 1-3 and 5 become the same when the clock jitter equals to 5% of fs. That means there is no use to have higher IBS when the system has clock jitter larger than 5% of fs. Meanwhile, the systems with NTFs NO.1 and 4 do not suffer jitter-induced noise when the clock jitter is less than 6% of fs, hence the dynamic range remains stable.

## FIGURE 3.17 THE EFFECT OF CLOCK JITTER ON SNDR (DIFFERENT NTFS WITH DIFFERENT IBS)

From the above analysis, the conclusion is reached that although an aggressive system can achieve better performance in ideal case, it can be more sensitive to even small clock jitter. When the clock jitter is taken into account, the NTF achieving the highest dynamic range is no longer the best choice.

In many previous works, the NTF is usually chosen at first according to the requirements of performance without taking the clock jitter into account. Afterwards, the techniques of reducing clock jitter are applied to release the sensitivity. However, the above analysis shows the necessity to choose a NTF less sensible to clock jitter at early stage of the design. As long as the required performance is guaranteed, the insensitivity to clock jitter can be achieved by minimizing the in-band noise suppression.

By taking the clock jitter and the stability into consideration, the proposed noise transfer function is chosen as

$$NTF = \frac{s^4 + 0.028s^2}{s^4 + 1.321s^3 + 0.905s^2 + 0.366s + 0.074}$$

(3.4.3)

#### 3.5 Multi-bit DAC Mismatch

For a high-speed modulator with MHz range input signal, low oversampling ratios (<32) are a must for a reasonable high clock frequency. In such cases, a multi-bit quantizer is needed to lower the quantization noise, improve the loop stability and reduce the clock jitter sensitivity for CTsigma-delta modulators. The multi-bit quantizer also means a multi-bit DAC in the feedback path. While a single-bit DAC has inherent linearity, a multi-bit DAC leads to unavoidable element mismatch and nonlinearities. The nonlinearity problem may severely limit the modulator performance.

The DAC mismatch error is added directly to the input signal directly, and goes through the signal transfer function together with the signal. This means the DAC mismatch experiences no attenuation in the signal band when it appears in the modulator output. High DAC linearity requires precise matching of the DAC unit element. However, current CMOS processes can only provide 0.1% matching accuracy (10-bit) for capacitors, and matching accuracy for transistors is even poorer than that of capacitors. To obtain more than 10-bit resolution, DAC mismatch errors must be suppressed below the modulator overall linearity requirement.

#### **3.5.1 DAC Architecture**

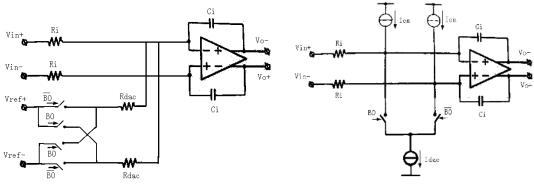

Figure 3.18 (a) shows the integrator using resistor based DAC feedback for continuous time sigma-delta modulators. The currents from both paths are summed and integrated on Ci. Moreover, due to the necessity of high-precision calibration, it is more common to implement the DAC using current sources, especially in CMOS technologies, as shown in figure 3.18 (b). Both the circuits can be extended for multi-bit DACs by adding DAC paths, independently connected to the same Vref.

#### FIGURE 3.18 RC INTEGRATORS WITH DAC FEEDBACK FOR CONTINUOUS TIME IMPLEMENTATION

Since the reference and sum elements as well as switches are relatively easy to implement, the current-steering DAC is commonly used for continuous-time modulators in a CMOS process. The current-steering DAC is suitable for high-speed high-resolution applications.

The disadvantage is its sensitivity to device mismatch, glitches, and current source output impedance. So special care should be taken to improve the matching of the DAC.

Figure 3.19 shows the N-bit current steering DAC architectures with binary weighted code and thermometer code. In a binary weighted DAC, the current sources, which are controlled by the input bits bi, are binary weighted, as shown in figure 3.19(a). The output current lout is given by

$$I_{out}(k) = I_{LSB} \cdot b_0 + 2I_{LSB} \cdot b_1 + \dots + 2^{N-1}I_{LSB} \cdot b_{N-1} = I_{LSB} \cdot k$$

(3.5.1)

The advantage of binary weighted DAC is that the number of switches and digital encoding circuits become minimal in this architecture. The disadvantage is that for a large number of bits, the difference between the  $MSB(b_{N-1})$  and  $LSB(b_0)$  weight is very large and the converter is very sensitive to mismatch errors.

FIGURE 3.19 N-BIT CURRENT-STEERING DACS

In the thermometer coded DAC, the binary input code is encoded into a thermometer code as illustrated in Table 3.3. The current sources representing the reference elements are all equally weighted and the matching of the individual elements becomes simpler than for the binary case. The transfer function of the DAC is monotonic and the requirement on element matching is relaxed. However, there are  $M=2^{N}-1$  thermometer coded bits for N binary bits. The number of switches and current sources is increased to M, which makes the circuit more complicated.

| TABLE 3.3 DECIMAL, E | BINARY OFFSET, | , THEMOMETER | CODE REPRESEN | TATIONS |

|----------------------|----------------|--------------|---------------|---------|

|                      |                |              |               |         |

| Decimal | Binary Offset | Thermometer |

|---------|---------------|-------------|

| 0       | 000           | 0000000     |

| 1       | 001           | 0000001     |

| 2 | 010 | 0000011 |

|---|-----|---------|

| 3 | 011 | 0000111 |

| 4 | 100 | 0001111 |

| 5 | 101 | 0011111 |

| 6 | 110 | 0111111 |

| 7 | 111 | 1111111 |

The mismatch error of a current source can be modeled as an additional current source in parallel with the nominal current source, as shown in Figure 3.20 for the current source corresponding to bit i.

FIGURE 3.20 MODELING OF CURRENT SOURCE WITH ERROR CURRENT SOURCE  $\bigtriangleup I_{\rm I}$

The actual output is then given by

$$I_{out,i}=bi*(2^{i}*I_{unit}+\triangle I_{i})$$

(3.5.2)

In the thermometer-coded DAC, the currents from the selected elements are summed to compose the output current. The total current error equals to the sum of the error of every element, as given by

$$I_{out,actual} = I_{out,ideal} + \Delta I = I_{out,ideal} + \sum_{i=0}^{N-1} \Delta I_i(b_i)$$

(3.5.3)

$\triangle I_i(b_i)$  is estimated by the relative error current in the i-th bit, $\delta_i(b_i)$ . For one specific DAC the matching error associated with one current source is fixed. Assume the design is used for a large number of chips, the matching error will be Gaussian distributed and uncorrelated with each other.

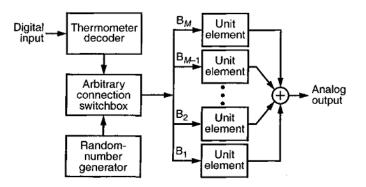

#### 3.5.2 Dynamic and Element Matching

A multi-bit DAC can utilize the principle of noise shaping to reduce its nonlinearity effects. The procedure of suppressing the mismatch error is the same as that of sigma-delta data conversion: use filtering to suppress the noise spectrum in the signal band and to shift its power to out-of-band frequencies.

There are two signal-processing techniques to enhance the linearity of multi-bit sigma-delta modulators due to DAC element mismatch, dynamic element matching (DEM) and digital calibration. The digital calibration schemes are usually expensive to implement in terms of system design complexity, hardware requirement, and power consumption. The dynamic element matching (DEM) is the most extensively used technique to reduce the DAC mismatch error. However, DEM introduces additional delay in series with the DAC that leads to additional excess loop delay which must be accounted and dealt with.

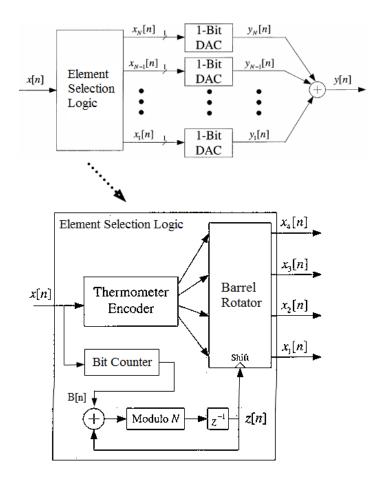

For the DAC built with unit elements, DEM technique encodes the quantizer output bits into thermometer codes, and rearranges them according to certain strategies for the selection of the unit elements. The element selection logic determines the DEM algorithm to be employed.

In a conventional thermometer coded DAC, the input number is represented by fixed reference elements in the DAC, which causes the matching errors to be strongly signal-dependent. The rearrangement of the DAC elements does not affect the data value, but changes the priority of selecting the unit elements. By doing this, different references are chosen to represent the input number so that the matching errors are no longer signal dependent. The average DAC output matches the ideal mean value. The unit-element DAC structure is shown in Figure 3.21. For the DEM technique, it is commonly assumed that the offset and gain errors of the DAC are acceptable, and only the DAC nonlinearity error is of concern.

FIGURE 3.21 UNIT-ELEMENT DAC WITH RANDOMIZED ELEMENT SELECTION

Among the commonly used strategies of DEM technique, data-weighted averaging (DWA) is selected in this design. DWA algorithm uses all the DAC elements at the maximum possible rate while ensuring that each element is used the same number of times. The unit elements participating in the D/A conversion are selected sequentially from the DAC array, beginning with the next available unused element, as it is shown in figure 3.22. Through such a rotational element-selection process, DWA achieves first-order high-pass shaping of the DAC mismatch errors. The DAC errors will quickly sum to zero, moving distortion to high frequencies. Besides, compared with other algorithms, DWA algorithm preserves the modulator noise shaping.

FIGURE 3.22 ILLUSTRATION OF DWA

However, DWA has some disadvantages. Firstly, it suffers the in-band tonal problem resulting from its intrinsic periodicity. For example, if a dc level signal is applied to the ADC, the DWA will continue repeating the same sequence of elements. Since these elements contain mismatch, the corresponding mismatch sequence will create a fixed repetitive pattern, namely it will generate an oscillation. The tones introduced by the DWA out of band mix with out of band noise and other undesired signals, and then is downconverted back into the desired signal band.

The DWA DAC used in this design is shown in figure 3.23. Its input comes from the quantizer, which is in the range  $\{-1, -1+LSB, ..., 1-LSB, 1\}$ . The element selection logic consists of a thermometer encoder and a barrel shifter. In addition, the barrel shifter consists of a modulo-N block, a unit delay, and a bit counter. At each sample time n, the bit counter counts the number of 1's in the incoming code. The barrel rotator uses the output z[n] originated from the bit counter to control the operation of rotation, so that the input digital signal is converted to analog signal using the next unused unit elements of DAC. The control data z[n] at sample time n is calculated as  $(z[n-1]+B[n])mod (2^{BN}-1)$ . BN is the bit number of the DAC.

FIGURE 3.23 THE DWA DAC

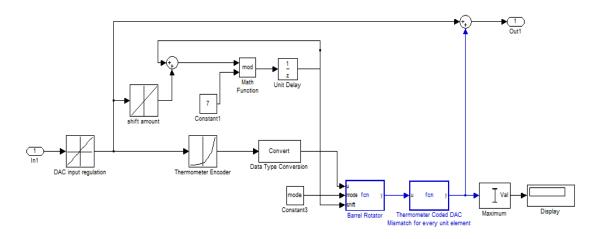

Based on the algorithm in the above figure, the model is built in Matlab, as shown in Figure 3.24.

FIGURE 3.24 MODEL OF DWA DAC

Table 3.4 and Figure 3.25 show the effects of DAC mismatch on the SNDR when the modulator uses nonlinear DAC and the DAC applying DEM technique.

| INL    | SNDR (dB)     |         |  |  |  |

|--------|---------------|---------|--|--|--|

|        | Nonlinear DAC | DEM DAC |  |  |  |

| 0.002% | 81.95         | 82.47   |  |  |  |

| 0.03%  | 73.05         | 79.66   |  |  |  |

| 0.04%  | 74            | 77.95   |  |  |  |

| 0.05%  | 72.79         | 75.32   |  |  |  |

| 0.06%  | 72.08         | 74.52   |  |  |  |

| 0.10%  | 60.8          | 65.99   |  |  |  |

| 0.30%  | 57.19         | 61.04   |  |  |  |

TABLE 3.4 THE EFFECT OF DAC MISMATCH ON SNDR

FIGURE 3.25 THE EFFECT OF DAC MISMATCH ON SNDR

### 3.6 Time Constant Variance

In a continuous time sigma-delta modulator, the transfer functions depend on the absolute values of resistors and capacitors, which largely vary over process, supply voltage, temperature, etc. Process variations of the absolute component values may be 10-20%, which increases the possible variation of the RC-product to more than 30%. Therefore, the time constant variance is very important to investigate in continuous time sigma-delta ADCs.

The common way to keep control over the transfer function variation over PVT (process-supply voltage-temperature) variations is to calibrate the resistors, capacitors and other parameters, e.g. amplifier transconductances etc. Some automatic resistor and capacitor trimming scheme can be employed to tune the time constants of the active RC integrators.

A model can be built at system level to investigate the tolerance of the time constant variance for the modulator. The integrator transfer function is modified by adding the

variance term  $\Delta$  rc, as follows. The additional term with  $\Delta$  rc can be modeled as an equivalent gain error GErc of the integrator.

$$H(s) = \frac{1}{sR_{IN}C_{FB}(1+\Delta rc)} = GErc * \frac{1}{sR_{IN}C_{FB}} [41] \qquad (3.6.1)$$

$$GErc = \frac{1}{1+\Delta rc} \qquad (3.6.2)$$

The gain variations add in-band noise (IBN), which is given in the following equation for multi-bit Nth-order single-loop modulator.

$$\text{IBN(GE)} \approx \frac{\pi^{2N}}{2N+1} \frac{\text{LSB}^2}{12} \frac{1}{\text{OSR}^{2N+1}} \frac{1}{\text{GErc}^2} \quad [41]$$

(3.6.3)

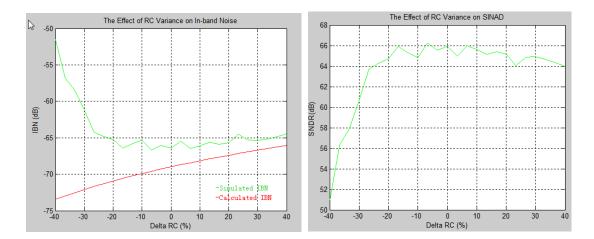

Figure 3.26 shows the effect of the RC time constant variation on IBN and SNDR by plotting both the calculated IBN and simulated IBN. The RC variance is swept in the range from -40% to 40%.

FIGURE 3.26 THE EFFECT OF TIME CONSTANT VARIANCE ON IBN AND SINAD

The analysis can be divided into two parts. Firstly, when the RC variation is positive, the simulated values are very close to the calculated values. According to equation (3.6.3), the gain error leads to a reduced integrator gain; hence the in-band noise is increased. Fortunately, the SNDR is reduced only a little. This is because the variation of the integrator gain varies the poles of the NTF slightly, but not the zeros at dc.

Secondly, when the RC variation is negative, the increased integrator gain results in aggressive noise shaping. The simulation results show that a slight increase in SNDR can be achieved. However, when the negative RC variation is larger, the simulation results do not agree with the calculated values anymore and dropped dramatically. By checking the signals in the time domain, the quantizer is found to be overloaded. That means a large negative RC

variation results in the instability problem, hence largely decreased SNDR. The equation (3.6.3) is only limited to the stable system.

It is gained from the above analysis that the task to increase the tolerance of time constant includes two parts. One is to enlarge the range of closed loop gain of the integrator. The other is to set a symmetric tolerance of negative and positive time constant by adjusting the loop gain at the middle of its range.

To enlarge the range of loop gain is actually to minimize the negative edge of time variance range. This is because the positive edge is set according to the performance requirement, while the negative edge is limited by the instability. There has a trade-off between time constant variance and excess loop delay. The loop gain is tuned to achieve the maximum range in a stable system.

After the range of loop gain is enlarged, the loop gain is set to have a symmetric tolerance of negative and positive time constant. Table 3.5 and Figure 3.27 show the SNDR of the modulator with asymmetrical tolerance range and symmetrical tolerance range. The asymmetrical range (-40%~10%) is adjusted to the symmetrical range (-30%~30%) by increase the loop gain. The increased loop gain reduces the tolerance of negative time constant to allow more tolerance of positive constant.

|              | Delta RC (%)              |       | -40   | -30   | -20   | -10   | 10    | 20    | 30    | 40    |

|--------------|---------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| SNDR<br>(dB) | Asymmetrical<br>Tolerance | 74.38 | 80.96 | 79.65 | 79.4  | 79.85 | 79.2  | 76.77 | 75.12 | 73.96 |

|              | Symmetrical<br>Tolerance  | 69.97 | 74.21 | 80.77 | 80.01 | 79.69 | 79.32 | 79.39 | 79.12 | 76.98 |

TABLE 3.5 THE ADJUSTMENT OF TIME CONSTANT VARIANCE TOLERANCE RANGE

FIGURE 3.27 THE ADJUSTMENT OF TIME CONSTANT VARIANCE TOLERANCE RANGE

## 3.7 Other Non-idealities

### 3.7.1 Finite Opamp Gain

The finite operational amplifier gain affects the transfer function of the continuous time integrator.

The main building block for continuous time sigma-delta modulator is an ideal low-pass filter or integrator, which implements a transfer function with its only pole at DC:

$$H(s) = \frac{a}{s}$$

(3.7.1)

where a is the gain-bandwidth product (GBW) of the integrator.

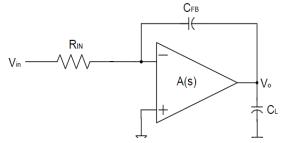

To implement this function, an active RC integrator can be used, as shown in Figure 3.28.

FIGURE 3.28 ACTIVE RC INTEGRATOR USED IN CT SD MODULATORS

The transfer function of the ideal integrator is

$$H(s) = \frac{1}{sR_{IN}C_{FB}}$$

(3.7.2)

where  $R_{IN}$  is the value of input resistror, and  $C_{FB}$  is the value of the integration capacitor.

When a finite amplifier gain is taken into account, the integrator transfer function changes to

$$H'(s) = \frac{1}{\frac{1}{A_{DC}} + sR_{IN}C_{FB}}$$

[44] (3.7.3)

where  $A_{DC}$  is the dc gain of opamp.

The equation shows that both the DC gain of the integrator and its pole are affected by the finite DC gain of the amplifier. The pole is pushed away from dc to  $1/A_{DC}R_{IN}C_{FB}$ . However, the pole of the loop filter becomes the zero of the NTF. The away-from-dc zero at the frequency given by  $f=(2\prod A_{DC}R_{IN}C_{FB})^{-1}$  reduces the amount of attenuation of the quantization noise in the baseband. High  $A_{DC}$  is beneficial.

The equation for the in-band noise caused by the leaky integrators in a 2nd-order modulator is shown as follows:

$$IBN(A_{DC}) \approx \frac{\Delta^2}{12} \left(\frac{\pi^4}{5} \frac{1}{OSR^5} + \frac{2\pi^2}{3} \frac{1}{OSR^3A_{DC}^2} + \frac{1}{OSRA_{DC}^4}\right)_{[41]}$$

(3.7.4)

As it can be seen from the equation, if the dc gain  $A_{DC}$  of the Opamp is set in the range of the oversampling ratio  $A_{DC}\approx$ OSR of the modulator, every part of the in-band noise keeps proportional to  $1/OSR^5$ . Even though the modulator can still benefit from large dc gain, the CT sigma-delta modulators have more relaxation on the dc gain compared with DT implementations.

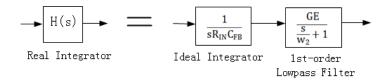

#### 3.7.2 Finite Gain-Bandwidth Product

For a continuous-time implementation, the finite gain-bandwidth product of the amplifier affects the in-band quantization noise power by changing the NTF shape. It introduces a gain error and an additional second pole into the ideal transfer function of the integrator.