# Achieving Energy Efficiency in Analogue and Mixed Signal Integrated Circuit Design

E. López-Morillo, F. Márquez, T. Sánchez-Rodríguez, C.I. Luján-Martínez and F. Munoz Electronics Engineering Department, Universidad de Sevilla Spain

#### 1. Introduction

Wireless communications are one of the major successes of the engineering over the past two decades. The progress made in this area has not only produced a huge technological growth, but also a great impact at social and economical level. In fact, the possibility of being connected anywhere at any time has radically changed people habits.

The evolution of wireless communications is obviously linked to the power consumption of devices, which also continues increasing due to the growing amount of data and transmission speed required by the new communication standards. In contrast, the energy available in portable batteries does not grow at the same rate, improving only their capacity in a 10% every two years (Shahab, 2010). This leads to an increasingly gap between power needs and battery capacity. Therefore, energy efficiency of electronics systems has become a crucial factor to maximize the lifetime of the available batteries and one of the most important research topics in integrated circuits design in recent years.

The increase in power consumption is less dramatic for the digital domain, since it is partially compensated, as the technology scales-down, by the reduction of the supply voltage and the geometrical dimensions of a single device. The main reason for decreasing the supply voltage in modern CMOS technology is to avoid the possible breakdown of the transistors due to the extremely thin oxide. For a CMOS logic gate, e.g. an inverter, the simplest logic cell, the power consumption can be expressed as:

$$P = C_L \cdot V_{dd^2} \cdot f \tag{1}$$

where  $C_L$  is the load capacitor at the output of the inverter,  $V_{\rm dd}$  is the supply voltage and f is the operating frequency. Despite of the ever-increasing working speed, the power consumption in CMOS logic circuits is reduced as the supply voltage and geometry sizes scale down. For instance, the power consumption of microprocessors is reduced in a 50% for each technology generation if the supply voltage scales down in a 30% (Bokar, 1999) and according to Gene's law, the power dissipation in embedded DSP processors will be decreased by a half every 18 months. As it will be explained later, this relative "low cost" of digital computation in terms of power dissipation, supports the idea of maximizing the

digitization level of an electronic system not only to dismiss the fabrication costs but also as a way of reducing its power consumption.

The System-On-Chip (SoC) trend is the main cause for the analogue and mixed-signal and digital integrated circuits (ICs) to be fabricated on the same wafer. This fact eventually requires the analogue and mixed-signal ICs to be fabricated in modern CMOS technologies to save cost. However, several challenges are encountered in the scaling-down of the CMOS technologies for analogue designs with not much clear advantages (Yao et al. 2006). The threshold voltage is not scaled as aggressively as the supply voltage to avoid leakage current in transistors. As a consequence, the available signal swing is lower and a reduction of the noise of the circuit to maintain the same dynamic range is required. Reducing thermal noise increases the power consumption of analogue and mixed-signal circuitry. Particularly, in discrete time applications, reducing circuit noise means increasing the capacitances which results in higher power consumption in order to maintain the same operation speed. Additionally, as technologies are scaled down, the output resistance of the MOS transistors decreases resulting in lower op-amp gain. In order to increase the gain, it is required to use either cascode transistors or cascade amplifiers, increasing the complexity of the circuits. These solutions worsen the swing problems and increase the power consumption.

The analogue-to-digital (A/D) converter is one of the most important and power consuming building blocks in modern electronics systems. Moreover, A/D converter (ADC) requirements tend to be more stringent as the analogue functionality is moved to the digital domain. In recent years, the demand of more and more performance (speed and/or resolution) within a limited energy budget has pushed the IC research community to put a huge effort into increasing the energy efficiency of the ADCs. For instance, data collected from the literature over the last years indicate that the power efficiency of ADCs has improved by a factor of two every two years (Murmann, 2008), allowing some designs to become portable, such as those for biomedical applications. Due to this fact, a special attention to ADC architectures will be taken in some sections of this chapter, as they are the most limiting blocks in recent systems.

In portable bio-signals acquisition micro-systems, the power consumption requirements are taken to the extreme. For instance, medical implant devices, such as modern pacemakers, require extremely low power consumption (about 10-40  $\mu$ W) in order to operate up to 10 years or more using a small non-rechargeable battery (Yeknami et al., 2010).

In wearable electronics for biomedical monitoring applications, extreme miniaturization is required and this will limit the battery size and power draw. Wearable electroencephalography (EEG) is a good example of such a power-limited system. EEG records the voltage between electrodes placed on the scalp and provides a non-invasive interface to the brain. Discrete, lightweight and comfortable devices are essential for user acceptance in applications such as epilepsy diagnosis (Casson & Rodriguez-Villegas, 2011). Long-term EEG monitoring of patients in their daily environment is generally required for epilepsy diagnosis. As these types of medical tests can take long periods of time, ultra-low power and miniaturized electronics systems need to be developed.

Another interesting arising application is the Energy Autonomous Sensors (EAS) which will represent a revolution in the use of wireless technologies, such as wireless sensor networks, in the ambient intelligence paradigms. Exploiting this continuously improving energy

efficiency and advances in energy harvesting, miniaturized battery-less sensors that do not need to be recharged for their whole operational life are becoming possible nowadays (Belleville et al. 2010).

In the second section of the chapter, we give a summary on the most common techniques that have been used by the IC research community in the last years to reduce the power consumption in analogue and mixed signal circuits. Several references to relevant works where each technique is detailed are provided. The following four general categories have been considered to classify the presented techniques:

- Biasing point optimization.

- Digitally assisted techniques.

- Analogue circuitry simplification.

- Efficient use of biasing.

The authors' main contribution in this chapter is described in the third section. Some of the techniques commented on section two will be illustrated with some actual designs, a micropower channel filter for an Ultra Low Power Bluetooth (ULPBT) receiver and a compact continuous time (CT) Sigma Delta ( $\Sigma\Delta$ ) modulator for a sensor interface powered by a passive Radio Frequency Identification (RFID) front-end.

# 2. Power reduction techniques in analogue integrated circuit design

# 2.1 Biasing point optimization

CMOS technology is used in most of the electronic devices because of its high density of integration. Traditional analysis of MOS circuits is often based on the assumption that every transistor is operating in the strong inversion region, although signal amplification can be done in any of the three inversion regions. The better knowledge of the strong inversion models and equations is one of the main reasons for its use.

Although simple MOS amplifier stages have much higher bandwidths in the strong inversion region, parameters like voltage gain, power dissipation, white noise, and distortion can be optimized by operating in the weak or moderate inversion regions (Binkley et al., 2003; D. J. Comer & D. T. Comer, 2004a, 2004b; Vittoz, 1994). Most often operation in weak inversion is synonymous to minimum power operation (Markovic et al., 2010).

There are several advantages that make operating in weak inversion an interesting issue:

- 1. It is possible to achieve higher gains (Allen & Holberg, 2002; D. J. Comer & D. T. Comer, 2004; Gray et al., 2001; Tsividis, 2002).

- 2. Low power consumption can be achieved as the quiescent drain current needed for this level of inversion is quite low.

- Lower distortion compared to the strong inversion region (D. J. Comer & D. T. Comer, 2004a, 2004b).

- 4. Higher output resistance of the devices of the input stage due to the low drain currents of transistors operating in weak inversion region.

But there are also some disadvantages when designing in weak inversion region. The most important is the reduction in circuit bandwidth and therefore in frequency operation, although, they can be maximized if some issues are taken into account. In a single transistor, the maximum operating frequency is determined by the gate capacitances,  $C_{GS}$  and  $C_{GD}$ . In order to maximize the device bandwidth, these capacitors need to be kept as small as possible which is achieved with minimum transistor width and length.

In order to improve MOS modelling techniques, a large amount of research has been done until this moment regarding transistor MOS operation at the three levels of inversion (Binkley et al., 2003; Vittoz, 2009). All this research has been quite useful to define accurate equations for the weak inversion region, as for instance the EKV model (Enz et al., 1995).

Many analogue circuits have been designed using weak inversion region, such as operational transconductance amplifiers (Chanapromma et al., 2010), filters (Corbishley& Rodríguez-Villegas, 2007; Omeni, 2005), ADCs (Farshidi&Alaei-sheini, 2009; Ou et al., 2006), etc., all of them performing very low power consumption.

# 2.2 Digitally assisted techniques

Recent CMOS technologies open an interesting possibility for ADC design by translating analogue precision problems to the digital domain, where higher frequency signals can be processed at much lower energy cost. The additional complexity of digital processing circuits can be compensated by relaxing the analogue requirements and, as a consequence, lowering the total required energy per conversion.

Digitally assisted techniques have become a major concern in ADC design nowadays. Some traditional A/D conversion architectures (such as Successive-Approximation-Register-based -SAR- and  $\Sigma\Delta$  ADCs) can be considered digitally assisted architectures since they make extensive use of CMOS digital logic. On the one hand, oversampling is a widely implemented technique in  $\Sigma\Delta$  converters with high energy efficiency. As modern technologies allow a more efficient digital data processing, there are trends to extend these techniques to other Nyquist ADC architectures to decrease the required energy per conversion. On the other hand, there are a great number of approaches based on compensating errors generated in the analogue parts (such as mismatch and offset of the comparators) by means of implementing redundancy-based architectures and digital calibration methods instead of very power-demanding analogue compensation techniques.

In next sections, some of the most interesting trends involving digitally assisted techniques will be explained.

#### 2.2.1 Digital calibration and redundancy

As it was commented before, the analogue circuits suffer some difficulties due to the MOSFET size reduction. One of the most applied techniques to compensate these errors is to introduce some digital calibration schemes, usually employing redundancy-based ADC architectures.

As an example, a widely employed architecture in wireless communication systems to reach fast operation at very high frequencies is the Flash ADC. Traditionally, these schemes have been characterized by using very power-demanding topologies with multiple gain stages for offset compensation. Actually, there are different design trends, mainly based on "relaxed precision" comparators redundancy combined with digital error compensation of mismatch

and offset deviations. A first approach is illustrated in (Flynn et al., 2003), where a bank of comparators with a factor-four redundancy is implemented with no special care about their offset or mismatch properties, drastically decreasing the consumption in the analogue blocks. In an initial calibration phase, the most suitable comparator for every input range is selected and the rest are powered down, with no contribution to power consumption of the system. Another example is a Flash ADC using process variations to generate the input references from random comparators offsets (Sundström & Alvandpour, 2009), whose resolution and input signal range are optimized by means of digital calibration.

A great variety of similar approaches combining redundancy and digital error correction methods can be implemented in a similar way. For instance, there are redundancy-based ADC with a current trimming DAC for error compensation to minimize the input-referred offset of the comparators (Park et al., 2007) or partially redundant schemes -with only some additional comparators- with background calibration implemented during conversion, as shown in (Kijima et al., 2009).

#### 2.2.2 Time-Interleaving

Time-Interleaving (TI) technique is a method based on the concept of running a system with M parallel channels by taking just one sample alternatively from each one. As a consequence, the ADC as a block would operate at an M times higher frequency than each individual channel. This allows reaching higher operation frequencies at no additional cost of analogue power consumption. However, mismatch between channels (usually the most limiting factors are offset and gain mismatch and clock skew errors) will reduce the resolution of the system. It is possible to compensate these errors using digital calibration or post processing.

An example of this technique can be found on (Cao et al., 2009), where a 6-bit Time-interleaving ADC working at 1.25 GS/s without any off-line calibration, error correction or post processing has been designed. The proposed architecture has been implemented using a two time-interleaved SAR ADCs topology combined with flash ADC sub-conversion processes, allowing a reduction from 65 to 6 comparators and lowering its power consumption well below typical values for state-of-art flash ADCs without digital calibration techniques. Another example of a Time-interleaving 7-bit SAR ADC working at 2.5 GHz is described on (Alpman et al., 2009). The proposed scheme is based on 16 parallel ADC running at 1.25GS/s with two additional ADC to allow background calibration to compensate offset and mismatch errors. Timing calibration can be done by means of adjusting a programmable delay line, which can be done during the packet header of the communication standard used for data transmission.

#### 2.2.3 Time-domain processing

With the evolution of CMOS fabrication processes, higher bandwidth is available for analogue designers. Therefore, systems that process signals in the time domain can benefit of the improved speeds to achieve larger resolutions. Traditional time-based architectures, such as dual-slope converters, can achieve very high resolution at the cost of large conversion times. Nowadays, as technology scales down, such time-based architectures are not only limited to low speed applications.

A good example of achieving high-energy efficiency using time-domain processing and an extensive use of digital logic is the ADC architecture presented in (Yang & Sharpeshkar, 2005, 2006). They propose a current-mode ADC that works like a pipelined converter which performs the residue amplification and subtraction in time domain, without the use of conventional amplifiers. The ADC is made of only two matched capacitors, a comparator and a switched reference current source controlled by a digital state machine. Since only a single comparator and one reference current source are used for the entire conversion process, the ADC consumes minimal power and avoids inaccuracies due to gain errors and offsets.

In (Jimenez-Irastorza et al. 2011) an interesting Time-to-Digital converter (TDC) achieving high energy efficiency is presented. It implements a recursive successive approximation algorithm in the time domain to perform the conversion with a low-voltage fully digital circuitry and very low power consumption.

Another example of a simplified scheme lowering power consumption in a  $\Sigma\Delta$  ADC is presented in (Colodro & Torralba, 2008). This paper presents a CT  $\Sigma\Delta$  modulator where the N-bit Flash quantizer is replaced by an asynchronous comparator. As a result, the feedback signal is coded in the time-domain as a PWM signal.

# 2.3 Analogue circuitry simplification

In previous sections, the way of successfully translating most of the analogue complexity to the digital domain by applying some techniques has been discussed. Another complementary approach to improve power efficiency could be based on the design of simplified analogue sub-circuits, allowing higher speed operation and power consumption decrease in basic building blocks. These techniques would include not only system level designs strategies but also analogue basic topologies that can be applied to many different architectures. In this way, higher energy efficiency can be obtained also at SoC level.

In the next sections, a review of some of the most interesting approaches for circuitry simplification will be provided.

#### 2.3.1 Switched Op-amp and Op-amp sharing

Op-amps are usually one the most power-consuming basic analogue blocks; therefore, a feasible option to reduce power consumption is to minimize their number in designs. Many switched-capacitor circuits need an active op-amp only during one clock phase, the amplification phase. As a consequence, there are two widely used techniques to reduce the number of active op-amps (Kim et al, 2006); one shares op-amps between successive stages and the other switches them off during the sampling phase.

Op-amp sharing is a technique based on using the op-amp for two adjacent stages in successive alternative phases. This technique is widely implemented in pipelined ADCs (Hashemi & Shoaei, 2007; Sasidhar, 2009), but can be applied to any op-amp based topology.

Two-stage Class-A switched-op-amp (SO) is the most popular solution for low power switched capacitor (SC) sigma-delta modulators with ultra low supply voltage conditions. The SO saves about 30%-40% of the total power since its output stage is just turned off at the integrating phase. For instance, an application to implement a 4th order band-pass  $\Sigma\Delta$

modulator using switched op-amps is presented in (Kuo & Liu, 2004). While a classic opamp topology would require four integrators working in two phases, in the proposed architecture the  $\Sigma\Delta$  modulator is implemented only with two switched op-amps, drastically reducing the power consumption. To further increase efficiency, class AB output and input stages can be used in the op-amp implementation. In (Wang et al., 2009) by turning off the entire SO together, instead of only the output stage, with its common mode feedback (CMFB) circuit, the power consumption of the SO can be reduced about 50%.

#### 2.3.2 Op-amp less

The traditional way of designing analogue circuits relies on high gain op-amps in negative feedback loops. As it was stated before, the op-amp power consumption directly impacts in the overall system. Recently, there is the trend of replacing the op-amps by more power efficient blocks such as comparators, inverters or simple structures based on local feedback. In this section, some of these approaches are described to illustrate this trend.

# CBSC (Comparator Based Switched Capacitors) and zero-crossing detector based circuits

The CBSC technique was firstly proposed in (Fiorenza et al., 2006) and is applicable to any traditional op-amp based SC circuit. This technique consists in replacing the op-amp by a comparator and one or more switched current sources. As the author explains, the power reduction relies in the fact that a CBSC circuit senses the virtual ground while in traditional op-amp based SC circuit the virtual ground is forced which is less energy efficient.

Several ADC prototypes have demonstrated the practical application of CBSS and its potential high energy efficiency. In (Shin et al. 2008), a 10 bits pipelined ADC based in zero-crossing detector fabricated using 65nm CMOS technology is reported.

Another pipelined zero-crossing detector based is presented in (Brooks & Lee, 2009). It achieves 12 bits of ENOB sampling at 50MS/s with high power efficiency indicated by a FOM of 88fJ/step.

## Inverter based $\Delta\Sigma$ modulators

This technique is another approach in which the op-amp is replaced by a simple inverter, which can be considered as a very simplified amplifier architecture. In the past, inverters had been applied to SC circuits as low-performance amplifiers for micropower consumption (Hosticka, 1979). In spite of the limited performance of inverters compared with op-amps, inverters attract attention again to be used in deep submicron technologies. This is because of their ability to operate with very low supply voltages. Recent works have demonstrated that inverter-based design techniques can be applicable to high-performance SC circuits in aggressively scaled CMOS technologies.

For example, (van Veldhoven et al., 2008) present a hybrid  $\Sigma\Delta$  modulator fabricated in 65nm CMOS technology. It uses a highly digitized architecture with a five bits quantizer and a digital filter in order to reduce the complexity of the feedback DAC. A first order analogue loop filter (implemented using inverters) reduces the analogue parts to the minimum, so the area and power consumption are drastically reduced.

In (Chae & Han, 2009) the inverter behaviour used as an extremely simple amplifier is explained in detail. Three discrete time (DT)  $\Delta\Sigma$  modulators of second and third order

completely implemented by means of inverters are presented in this work. All of them achieve high dynamic range under low voltage supply conditions with a power consumption that places the best of them in the state-of-the-art nowadays.

## Simple analogue cells based in local feedback

Simple local feedback can lead to substantial enhancement of the performance with low cost in terms of noise, area and power consumption as it is usually implemented by a simple structure.

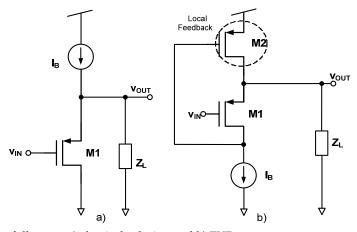

One good example is the structure called the Flipped Voltage Follower (FVF), a popular building block that relies on the local feedback idea. It was proposed in (Carvajal et al., 2005) to improve the performance of the classical voltage follower by means of local feedback.

A very commonly implemented basic cell in analogue microelectronics is the voltage follower (Fig. 1a). However, the gate-to-source voltage ( $v_{CS}$ ) of the transistor acting as the follower (M1) depends on the output current, which leads to a high distortion for large output current variations. Some solutions have been proposed to address this problem (Sánchez-Sinencio & Silva-Martínez, 2000), (Barthélemy & Kussener, 2001), (Carvajal et al., 2005). The FVF is the basic cell made up by transistors  $M_1$  and  $M_2$  and the current source  $I_B$  shown in Fig. 1b. The local feedback implemented by transistor  $M_2$  keeps constant the current through transistor  $M_1$ ; this decreases the output impedance increasing the linearity of the current copy and in spite of output current variations.

A modified version of the FVF was proposed in (Luján et al., 2011) showing a better performance for large excursions of the input signal up to 10MHz and allowing a reduction in the quiescent power consumption of about 15 times when comparing with the classical solution, for the same linearity performances.

The idea of using local feedback to maintain the linearity requirements, while the power consumption is decreased, can be extended to more complex systems such as ADCs. One example of this is the CT  $\Sigma\Delta$  modulator described in the section 3.2 of this chapter. A low power extremely low area CT  $\Sigma\Delta$  modulator implementation based on the FVF is explained.

Fig. 1. Voltage followers: a) classical solution and b) FVF.

### Other op-amp-less approaches

Another example of a simplified op-amp-less architecture is the ADC array (Draxelmayr, 2004). Using parallelism to exploit the power efficiency of simple structures, a 6-bit ADC working at 600 MS/s based on eight SAR ADCs using a charge redistribution architecture is proposed. A power consumption of only 10 mW is obtained with very simple analogue circuitry (capacitors, switches and a comparator are sufficient) and no need for "precision" analogue blocks, like high gain op-amps.

In (Van der Plas, 2006) a 4-bit flash scheme with a comparator based simplified structure is proposed to design a high speed low-power ADC. Its structure is reduced to save power by removing all the non essential blocks: Track &Hold, preamplifiers, reference ladder and bubble error correction. A comparator circuit combining sampling, amplification and reference level generation is used to implement the ADC obtaining a power consumption of only 2.5 mW.

### 2.4 Efficient use of biasing

Charge transfer in class-A op-amp circuitry is inherently inefficient; the amplifier is biased with a constant current, while delivering on average only a small fraction of this current to the load. In this section, a more efficient use of biasing is discussed and various approaches adopted to solve this problem are commented.

### 2.4.1 Dynamic and adaptive biasing

In the last decades, several approaches have been proposed to optimize the efficient use of biasing towards the challenge of minimizing the power consumption-performance ratio. Most of them can be classified according to the concepts of dynamic and adaptive biasing. The term *dynamic biasing* was first coined in (Copeland & Rabaey, 1979), where a method to reduce the power consumption by taking advantage of having several clock phases in a SC integrator was proposed. This method is valid for all those circuits where there is a capacitive feedback between the output and a virtual ground.

Since then, the concept of dynamic biasing has been extended, in general, to those approaches in which a block or part of it is connected or disconnected according to the received input power. An example of this technique is proposed in (Ozun et al., 2006) where a parallel combination of transconductors is used, increasing the power consumption only if very low noise is required.

At the same time, the term of *adaptive biasing* (Degrauwe et al., 1981) has also become popular. It is usually referred to a continuous time change in the biasing according to the input. One of the most important adaptive biasing techniques is the class AB operation. In this technique, the slew rate limitation is tackled by boosting automatically dynamic tail currents for large inputs, keeping a well-controlled low quiescent current (Degrauwe et al., 1981), (Callewaert & Sansen, 1990), (Castello & Gray, 1985), (Tan & Chen, 2007), (Klinke et al., 1989), (Harjani et al., 1999).

Several schemes can be found in the literature for class AB operation amplifiers. Most of them require of additional circuitry, which increases both power consumption and active area. Often they also imply additional parasitic capacitances to the internal nodes (Degrauwe et al., 1981), degrading the small signal performance of the circuit which is already poor due to the low quiescent current. In some cases, the stability issues get worse due to the use of positive feedback or structures that are sensitive to variations in process and environmental parameters (Callewaert & Sansen, 1990), (Klinke et al., 1989). Although other contributions consider negative feedback (Harjani et al., 1999), the required additional amplifiers to implement the feedback loops lead to complex designs. Another weakness of the tail current boosting topologies is that usually are not suitable for low voltage applications as in (Castello & Gray, 1985) due to the stacking of gate to source voltages.

Recently, some topologies based in the FVF (López-Martín et al., 2009) or using "Quasi" Floating Gate (QFG) techniques have been proposed (Ramírez-Angulo et al., 2006), while the first one offers simplicity of design and suitability for low-voltage operation simultaneously to high efficiency; the second one also minimizes the additional circuitry required just substituting a normal MOS transistor by a QFG MOS.

Class AB operation can be applied to the input, to the output or both. This last option is known as superclass AB operation (López-Martín et al., 2005). The concept of class AB operation is so spread that today we can talk, for instance, about Class AB DACs (Seo et al., 2009), Sample & Holds (Sawigun & Serdjin, 2011) and multipliers (Sawigun & Serdjin, 2009) among others.

# 2.4.2 Assisted op-amp and helper techniques

Instead of removing op-amps, as it has been explained in section 2.3.2, a less aggressive technique consists in keeping the op-amp but adding helper circuits that increase the energy efficiency by relaxing the requirements for the op-amp gain or bandwidth.

For instance, in (Musah et al. 2007) the concept of correlated level shifting (CLS) is introduced. Correlated double sampling (CDS) technique can be used to reduce the error caused by finite open-loop gain, but it limits the maximum speed and its performance is poor near the rails. This makes it unsuitable for low voltage conditions, since the voltage swing is reduced too much. CLS is a SC technique similar to CDS, which also decreases the errors due to finite open-loop gain and allows rail-to-rail operation increasing the "distortion-free" swing. A third clock phase is needed but the settling time is about the same, so it does not have impact on the circuit speed. Open-loop gain requirements can be relaxed for a given resolution, leading to power consumption saving.

Another approach of op-amp helper is the assisted op-amp technique proposed in (Pavan et al. 2010). It is well known that the op-amp in the first integrator of high resolution single-bit CT  $\Sigma\Delta$  modulators has stringent slew rate requirements, increasing power dissipation. In CT single bit  $\Sigma\Delta$  modulators the feedback DAC injects a very high frequency current signal at the virtual ground node of the op-amp which the first integrator is implemented with. If the op-amp is not fast enough, this high frequency signal produces strong variations at the virtual ground node which result in distortion. The conventional way of addressing this issue is to bias the op-amps with large currents, so that the bandwidth and slew rate of the op-amp are enhanced. This work introduces the "assisted op-amp" integrator, which offers a way of relaxing the speed specifications of the op-amp in the first integrator, achieving low distortion operation with low power consumption.

# 3. Applications examples

In this section, two examples of design which make use of some of the previous power reduction techniques are presented. Firstly, the design of an active-RC channel filter for ULPBT applications is explained. It achieves micro-power consumption by using an efficient class-AB op-amp biased in the weak inversion region. Then, the design of an efficient op-amp less implementation for CT  $\Sigma\Delta$  modulators is described. In the proposed implementation, the op-amp is replaced by the compact local feedback structure explained in section 2.3.2.

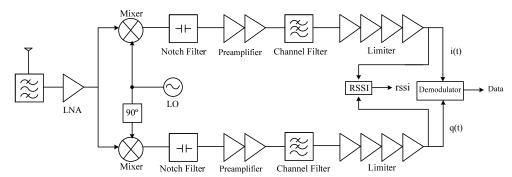

# 3.1 Micropower active-RC channel filter for a Zero-IF Ultra Low Power Bluetooth receiver

In the case of the low-power RC filter and in order to reduce the power consumption, an adaptive biasing technique has been used. Specifically, a new topology of class-AB op-amp has been used so that the current consumption is adapted to the output requirements. The designed filter will be used in the ULPBT receiver based on a Zero-IF architecture like the one shown in Fig. 2. The main challenge of this design is the implementation of an efficient low-pass channel filter meeting the stringent demands of the receiver.

Fig. 2. Zero-IF receiver architecture for Ultra Low Power Bluetooth Standard.

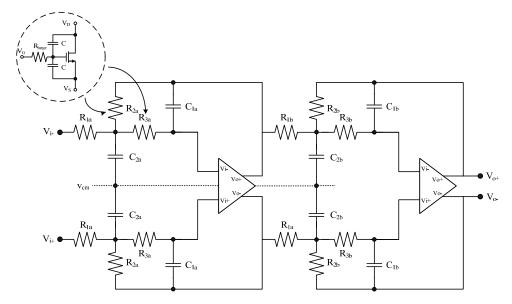

An active RC topology has been chosen to implement the filter. Sallen-Key (SK) and multifeedback (MFB) topologies are usually employed in this kind of filters. Both architectures are attractive for low power design, since they comprise an active element per biquad performing at the same time low noise and high linearity. The main drawback of active RC filters for low power design is the high op-amp bandwidth required. The power consumption is optimized by using class-AB two-stage op-amp with enhanced gain and rail-to-rail output swing.

Based on the overall receiver planning, the low pass filter should provide a gain of 10 dB with a cut-off frequency of 1 MHz and a noise figure of less than 50 dB. According to the required stop-band attenuation of 45 dB at 3 MHz, a fourth-order Butterworth filter meets the requirements.

The topology of the active RC filter is shown in Fig. 3. It has been implemented by two biquadratic sections in cascade. Several combinations of second-order sections connected in cascade have been studied to fulfil the requirements for noise and op-amp bandwidth.

Fig. 3. Fourth-order low pass Butterworth filter with MFB topology.

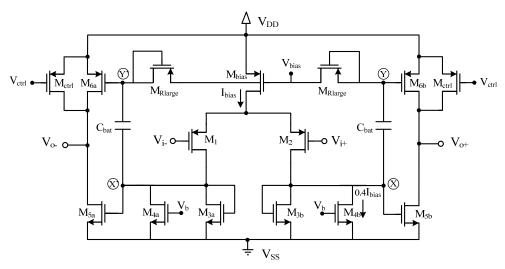

The low voltage environment of this work (1.2 V power supply) leads to an amplifier topology that should provide rail-to-rail output swing. This fact precludes the use of cascode transistors to increase the voltage gain. In this context, two-stage op-amps are the natural choice, since they have rail-to-rail output swing and can drive both resistive and capacitive loads. In active RC topologies, the high op-amp bandwidth required (the op-amp unity-gain bandwidth has to be much larger than the filter pole) leads easily to high power consumption.

The fully balanced two-stage amplifier is shown in Fig. 4. This topology can provide rail-to-rail operation with better power efficiency than a Miller amplifier since the conventional two-stage amplifier needs a compensation capacitor to ensure the stability, and additional current to drive this capacitance. The main drawback is the low voltage gain. The operational amplifier often consumes large power to obtain a high gain. However, in this case, the gain is increased by placing two current sources  $M_{4a}$  and  $M_{4b}$  in parallel with the diode-connected transistors. In this design, the current of transistors  $M_{4a}$  and  $M_{4b}$  has been set at  $k(I_{bias}/2)$  where the k factor is 0.8, boosting the gain 1/(1 - k) times (Steyaert et al., 1991; Yao et al., 2004).

For minimum power consumption and large current drive capability, one of the techniques explained in this chapter, the class-AB operation is used. Class AB output stages generate output currents larger than the output stage quiescent current. The class-AB performance of the output stage is achieved, without additional current, including a large resistive element implemented using a minimum size diode connected PMOS transistor  $M_{Rlarge}$  and a small capacitor  $C_{bat}$  (Ramírez-Angulo et al., 2006). The value of  $C_{bat}$  can be small, as transistor  $M_{Rlarge}$  is intended to operate as a very large resistive element. Under quiescent conditions and given that no DC current flows through  $M_{Rlarge}$  the voltage at the gate of  $M_{6b}$  is the same as at the gate of  $M_{bias}$  so that the quiescent current in  $M_{bias}$  and  $M_{6b}$  has the same value  $I_{bias}$ . During dynamic operation, when the output of the op-amp is slewing, the voltage at node X

Fig. 4. Fully differential single-stage amplifier with class-AB output.

is subject to a large change. Given that capacitor  $C_{\text{bat}}$  cannot charge or discharge rapidly through  $M_{\text{Rlarge}}$ , it acts as a floating battery and transfers the voltage variations at node X to node Y. This provides class AB (push-pull) operation to the output stage. No additional circuitry to control the desired value of the quiescent output current is necessary due to the large resistor.

A conventional CMFB circuit is incorporated to control the output voltage. The output stage has low supply requirements since it can operate with a voltage close to the threshold voltage of a transistor:  $V_{DD}^{\min} = V_{GS,5b} + V_{SDsat,2} + V_{SDsat,bias}$ .

The biasing current of the op-amp is 20  $\mu A$ . The current through transistors  $M_4$  is adjusted at 0.4 $I_{bias}$  and  $M_5$  size is ten times larger than  $M_3$  size. The CMFB consumes 20  $\mu A$ . Thus the total supply current is 80  $\mu A$ .

Due to process variations, integrated components can differ significantly from their nominal values. In order to compensate for these variations, RC-opamp filters must be tuneable. A switched array of passive resistors and/or capacitors and MOSFET-C technique are usually employed. The latter is the simplest way and features continuous programmability. Passive resistors are replaced by MOSFET operated in triode region and the gate voltage is tuned to make the filter parameters programmable.

In this work, the device coined as "quasi" floating gate MOS (Ramírez-Angulo et al., 2003) is used to replace the passive resistors. A QFG MOS transistor consists of a MOS transistor with capacitive gate voltage averaging biased using a large resistive element  $R_{large}$  (Ramírez-Angulo et al., 2004), as shown in Fig. 3. for resistances  $R_{2a}$  and  $R_{3a}$ . The large resistance  $R_{large}$  for QFG MOS resistors has been implemented using MOS transistors operating in subthreshold region (Bikumandla et al., 2004), since the resistance of a transistor operating in this region is very large (tens of  $G\Omega$ ). Transistors operate in subthreshold region with a bias current  $I_{subth}$  of 10 nA. This method to implement programmable linear resistors

improves the linearity at the cost of increasing the area, mainly due to the use of two capacitors (C in Fig. 3). In order to save area, resistors  $R_1$  are implemented by polysilicon ensuring a linear V-I conversion. Resistors  $R_2$  and  $R_3$  will be tuned to control the main parameters of the filter: gain, quality factor and cut-off frequency.

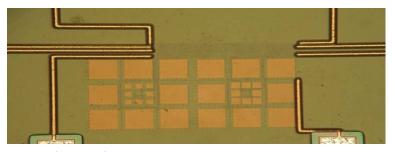

The proposed fourth-order Butterworth filter has been fabricated in a  $0.18 \mu m$  CMOS technology. Figure 5 shows the chip microphotograph. The active area of the chip is  $0.45 \text{ mm} \times 0.27 \text{ mm} = 0.12 \text{ mm}^2$  and it is dominated by the capacitors. The filter operates with a single 1.2 V supply voltage.

Fig. 5. Filter microphotograph.

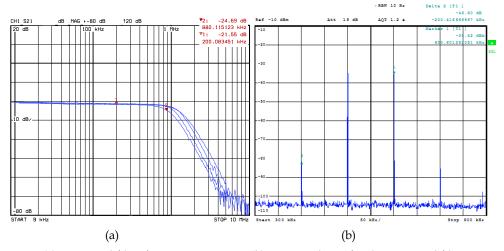

Figure 6a illustrates the measured frequency tuning around the nominal frequency of 1 MHz. The cut-off frequency can be tuned from 800 kHz to 1.3 MHz. The measured two-tone intermodulation distortion for the filter is shown in Fig .6b. In this measurement, the cut-off frequency of the filter was set to the nominal value of 1 MHz. The frequencies of the input tones are at 500 and 600 kHz and the third intermodulation (IM3) products are at 400 and 700 kHz. Note that the IM3 of the filter is -46.8 dB, the noise figure is 46 dB and the input noise 85 nV/ $\sqrt{\rm Hz}$ , which is approximately 85  $\mu V$  in the 3 dB passband. Low noise behaviour is achieved in a low power environment mainly due to the use of only two amplifiers.

Fig. 6. (a) Measured filter frequency response (b) Measured IM3 for the proposed filter.

A summary of the experimental results is given in Table 1.

| Supply Voltage           | 1.2 V                    |

|--------------------------|--------------------------|

| Technology               | 0.18 μm CMOS             |

| Silicon Area             | 0.12 mm <sup>2</sup>     |

| Transfer Function        | Fourth-order Butterworth |

| Cut-off Frequency        | 1 MHz                    |

| Frequency tuning range   | 800 KHz - 1.3 MHz        |

| DC Gain                  | 10 dB                    |

| IIP3                     | 16 dBm                   |

| Input-referred noise     | 85 μV                    |

| Static Power Consumption | 290 μW                   |

Table 1. Summary of experimental results.

# 3.2 Compact op-amp less CT $\Sigma\Delta$ modulator implementation for passive RFID applications

Combining sensors with passive RFID tags opens the way for new applications such as automotive and healthcare. As the passive RFID sensor nodes are intended to be powered by energy scavenging, ultra-low power consumption and robustness against process variations and changes in the supply voltage are essential requirements. In addition, low area occupancy is crucial in order to decrease the fabrication costs.

Low-bandwidth, moderate-resolution ADCs consuming a few microwatts are key elements for the sensor interface. Successive approximation register (SAR) converters are the typical choice for moderate-resolution low-frequency applications with ultra-low power requirements such as passive RFID. This type of converter achieves moderate resolution with very low power consumption and sets the state-of-the art in terms of energy efficiency. However, they consume large active area as the required DAC is normally implemented by a capacitor network. In this work the CT  $\Sigma\Delta$  modulator architecture is proposed as an alternative to SAR architecture when the application also requires from very low area occupancy. CT  $\Sigma\Delta$  modulators have become very popular over the last years, especially for lower power applications.

Traditionally, the loop filter is implemented either using an active-RC integrator or a gm-C approach. As it has been explained in the section 2 of this chapter, recent trends in low-power ADC design replace the internal op-amps (which usually are the most power consuming building blocks) with simple analogue circuitry. Following this trend, in this work a novel CT  $\Sigma\Delta$  modulator implementation based on a local feedback is presented. The feedback provides a virtual ground node for reference subtraction without the need of op-amps or Operational Transconductance Amplifiers (OTAs). A first-order  $\Sigma\Delta$  modulator prototype with low complexity at system level and minimum area occupancy has been designed in order to validate the idea.

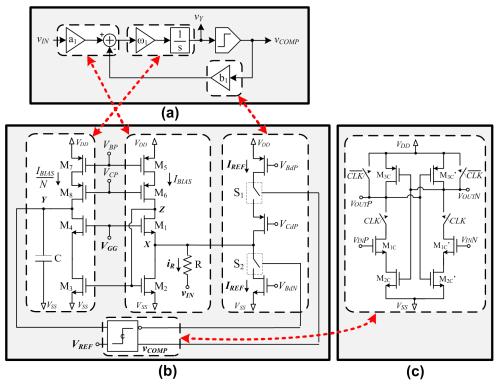

Fig. 7. First-order CT single-bit  $\Sigma\Delta$  modulator. (a) Block diagram, (b) Proposed implementation, (c) Comparator schematic.

In Fig .7a the block diagram of a typical first-order CT single-bit  $\Sigma\Delta$  modulator is shown. The modulator is made up of a comparator and a CT loop filter, which performs the subtraction and integration, as expressed in equation (1).

$$v_Y(s) = \omega_1 \frac{a_1 v_{IN}(s) - b_1 v_{COMP}(s)}{s}$$

(2)

The compact implementation shown in Fig 7.b is proposed, where the input stage, the integrator stage and the feedback DAC have been highlighted.

The input voltage,  $v_{IN}$  is converted into a current  $i_R$  by means of resistor R which connects the input signal to node X. Thanks to the feedback loop built up with transistors M1 and M2 and current source  $I_{BIAS}$ , the equivalent resistance at node X is extremely low.

In order to close the  $\Sigma\Delta$  feedback loop the comparator controls two switches,  $S_1$  and  $S_2$ , so that a reference current  $I_{REF}$  is injected or subtracted at node X depending on the comparator output. Therefore, the subtraction between the input signal and the comparator output is performed at node X in current mode. Note that both functions, the input voltage-to-current conversion and the feedback signal subtraction, are carried out by one resistor, two transistors and a current source. Then, the resulting current is copied and integrated in a capacitor.

By a proper selection of  $V_{GG}$ , so that the quiescent value of the input voltage ( $V_{IN}Q$ ) is equal to the bias voltage of node X ( $V_XQ$ ), the drain current of transistor M2 is given by:

$$i_{D,M2} = I_{BIAS} + \frac{v_{in} + V_{IN}^{Q} - V_{X}^{Q}}{R} \pm I_{REF} = I_{BIAS} + \frac{v_{IN}}{R} \pm I_{REF}$$

(3)

As the input voltage is converted to current by a linear resistor, having a very low impedance at node *X* is crucial to achieve a good linearity at the input stage. This requirement is achieved thanks to the local feedback that keeps constant the current through transistor M1 in spite of output current variations at node *X*. Neglecting the body effect, the input impedance at node *X* is given by (Carvajal et al., 2005)

$$r_X = \frac{r_{o2}}{1 + g_{m1}r_{o2} + g_{m1}g_{m2}r_{o1}r_{o2}} \approx \frac{1}{g_{m1}g_{m2}r_{o1}}$$

which, for typical parameter values in the selected technology, is low enough to guarantee the linearity requirements for this application.

The current at the drain of M2,  $i_{D,M2}$ , is copied to node Y by the current mirror implemented with transistors M3 and M4, where the current  $I_{BIAS}$  is removed. The resulting current is injected into capacitor C where the integration is carried out. Finally, the voltage at node Y is given by (in the s-Domain):

$$v_Y(s) = \frac{v_{IN}(s)}{RCs} \mp \frac{I_{REF}}{Cs} \tag{4}$$

Expressions (2) and (4) are equivalent if  $a_1\omega_1=1/RC$  and  $b_1\omega_1V_{COMP}=I_{REF}/C$ . Note that no additional circuitry is required to bias the node Y. To reduce power consumption, the current through M3 (and M7) can be downscaled by modifying the gain of the current mirror. In our implementation a ratio of N=3 was chosen.

To save power, the dynamic latch-type comparator show in Fig .7c has been selected to close the modulator loop. Two switches open the latch branches during the reset phase so that the quiescent current consumption is zero.

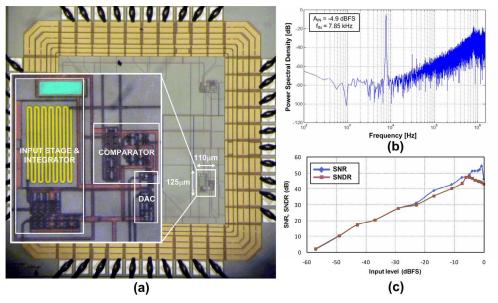

To verify the proper operation of the proposed implementation, a first-order CT  $\Sigma\Delta$  modulator prototype has been fabricated. The modulator digitalizes the signal coming from a MEMS accelerometer, which is a single-ended structure presently available in a 0.35µm CMOS technology. The ADC will be integrated in the same die with the MEMS accelerometer so it was designed in the same technology and with a single-ended input. The whole system is intended to be powered by an UHF RFID front-end which provides a 3V nominal supply voltage typical for the selected technology (Vaz et al., 2010). Fig. 8a shows a microphotograph of the fabricated prototype. The total area consumption (without pads) is only 110µm x 125µm for the whole proposed circuit which makes it, to the author's knowledge, the smallest  $\Sigma\Delta$  modulator published for this range of specifications.

The measured output spectrum for a 7.85kHz sinusoidal input signal is shown in Fig. 8b. A peak SNDR (Signal-to-Noise plus Distortion Ratio) of 49dB has been obtained for a -5dBFS input signal. Fig .8c shows the measured SNR/SNDR versus input signal amplitude. It can be seen that the prototype achieves 56dB of Dynamic Range (DR), which means about 9 bits of ENOB over a 25kHz signal bandwidth. Experimental results are summarized in Table 2.

Fig. 8. (a) Circuit microphotograph, (b) Measured output spectrum, (c) SNR/SNDR versus input signal amplitude. Input signal frequency = 7.85 kHz.  $V_{DD}$  = 3V.

The designed modulator has also shown to be very robust against supply voltage and bias current variations. The DR remains over 52dB for a supply voltage variation in the range 2.25 to 5 volts even for a 50% decrease of nominal bias current.

The FOM defined by (5) has been used to have an estimation of the energy efficiency achieved by the proposed  $\Sigma\Delta$  modulator implementation. The minimum power consumption

| Sampling frequency (MHz) | 3.2               |

|--------------------------|-------------------|

| Signal Bandwidth (kHz)   | 25                |

| Oversampling ratio       | 64                |

| Peak SNR (dB)            | 54.5 (@7.85kHz)   |

| Peak SNDR (dB)           | 49 (@7.85kHz)     |

| Dynamic range (dB)       | 56.2              |

| ENOB (bit)               | 9.04              |

| Input range (mVpp)       | 700               |

| Power consumption (µW)   | 4.35 (@Vdd=2.25V) |

| Power supply (V)         | 3                 |

| PSRR (dB)                | 32                |

| Vdd for ENOB > 7bits (V) | 2.25 to 5         |

| Active area (mm²)        | 0.01375           |

| Technology               | AMS 0.35μm CMOS   |

Table 2. Summary of measured modulator performances.

$(4.35\mu W)$  was measured for a 2.25V supply voltage, leading to a FOM of 0.267 pJ/step. This value places this work close to the most power efficient CT  $\Sigma\Delta$  modulators recently published, despite that it has been implemented in a reasonable old technology.

$$FOM = \frac{P}{2^{ENOB} \cdot 2BW} \tag{5}$$

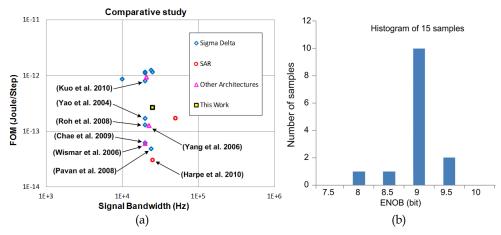

Fig. 9a gives a graphical representation of the state-of-the-art of power efficient ADCs in the same range of bandwidth. The measured performance of the proposed implementation is competitive in terms of energy efficiency compared with the state-of-the-art. The SAR converter (Harpe et al., 2010) sets the state-of-the-art and only a few  $\Sigma\Delta$  modulators perform better than the proposed in this work.

Fig. 9. (a) State of the art of ADCs regarding the selected FOM. (b) ENOB deviation for 15 measured samples (second version of the converter,  $V_{\rm DD}$  = 3V, input signal frequency = 7.85 kHz

Fig. 9b shows a histogram of the ENOB deviation for 15 samples fabricated. Every sample worked properly with an ENOB variation lower than  $\pm 0.5$  bits, which is an indication of the robustness of the proposed modulator implementation against the process variation.

A compact implementation for CT  $\Sigma\Delta$  modulators based on a local feedback has been presented. In order to validate the idea, a first order CT  $\Sigma\Delta$  modulator for a self powered sensor interface (9-bits of resolution and 25-kHz of signal bandwidth) has been designed in a 0.35µm CMOS technology. Experimental results confirm the idea and show that the proposed implementation leads to an extremely low area and highly power efficient  $\Sigma\Delta$  modulator. The measured prototype has also shown to be very robust against process, supply voltage and bias current variations.

#### 4. Conclusions

In this chapter, the need of minimizing power consumption in electronic devices has been pointed out. For this reason, a review of the most common techniques used by IC designers

with this purpose has been done. These techniques have been classified in four categories: biasing point optimization, digitally assisted techniques, analogue circuitry simplification and efficient use of biasing. In order to illustrate the large number of techniques that these categories involve, several references have been proposed through the chapter. Furthermore, two approaches based on the use of some of the reported techniques have been described. The first one proposes a micropower active-RC channel filter for an Ultra Low Power Bluetooth Receiver based on a zero-IF architecture. It uses a new topology of class-AB op-amp so that the current consumption is adapted to the output requirements. The second design proposes a compact op-amp less CT  $\Sigma\Delta$  modulator for passive RFID applications. In order to reduce the power consumption, a local feedback technique is used.

# 5. Acknowledgment

This work was supported in part by the Spanish Ministry of Science and Technology and in part by the Andalusian Regional Government under Projects TEC2010-21563-C02-02 and TIC-6323-2011, respectively.

#### 6. References

- Allen, P. E. & Holberg, D. R. (2002). CMOS Analog Circuit Design (2), Oxford Univ. Press, ISBN: 0195116445, New York.

- Barthélemy, H. & Kussener, E., (2001), High speed voltage follower for standard BICMOS technology, *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*. Vol. 48, No.7, (July 2001), pp. (727-732). ISSN 1057-7130.

- Belleville, M.; Fanet, H.; Fiorini, P.; Nicole, P.; Pelgrom, M.J.M.; Piguet, C.; Hahn, R.; VanHoof, C.; Vullers, R.; Tartagni, M. & Cantatore, E. (2010). Energy autonomous sensor systems: Towards a ubiquitous sensor technology. *Elsevier Microelectronics Journal*. Vol., No. 41, (March 2010), pp.(740-745).

- Bikumandla, M.; Ramírez-Angulo, J.; Urquidi, C. A.; González-Carvajal, R. & López-Martín, A. J. (2004). Biasing CMOS amplifiers using MOS transistors in subthreshold region, *IEICE Electronics Express*, Vol. 1, No. 12, (September 2004), pp. (339–345).

- Binkley, D. M.; Hopper, C. E.; Tucker, S. D.; Moss, B. C.; Rochelle, J. M. & Foty, D. P (2003). A CAD methodology for optimizing transistor current and sizing in analog CMOS design. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 22, No. 2, (February 2003), pp. (225–237).

- Borkar, S. (1999). Design challenges of technology scaling. *IEEE Micro*, Vol.19, No.4, Jul-Aug 1999, pp. (23-29).

- Brooks, L. and Hae-Seung Lee; (2009). *A 12b 50MS/s fully differential zero-crossing-based ADC without CMFB, IEEE International* Solid-State Circuits Conference Digest of Technical Papers, ISSCC 2009, (8-12 Feb. 2009), pp.(166 167).

- Callewaert, L.G.A. & Sansen, W.M.C (1990). Class AB CMOS amplifiers with high efficiency, *IEEE Journal of Solid-State Circuits*. Vol. 25, No.3, (June 1990), pp. (684-691). ISSN 0018-9200.

- Cao, Z.; Yan, S. & Li, Y. A 32 mW 1.25 GS/s 6b 2b/Step SAR ADC in 0.13 µm CMOS. IEEE Journal of Solid State Circuits, vol. 44, n<sup>a</sup> 3, March 2009, pp. (862-873).

- Carvajal, R. G.; Ramírez-Angulo, A. J.; Torralba, A.; Gómez Galán, J. A.; Carlosena, A & Muñoz-Chavero, F. (2005), The Flipped Voltage Follower: A useful cell for low-

- power low-voltage design, IEEE Transactions on Circuits and Systems I: Regular Papers. Vol. 52, No.7, (July 2005), pp.(1276-1291), ISSN 1549-8328.

- Casson, A.J. and Rodriguez-Villegas, E. A 60 pW gm-C Continuous Wavelet Transform Circuit for Portable EEG Systems. IEEE Journal of Solid-State Circuits, Vol.46, No.6, (June 2011), pp.(1406-1415).

- Castello, R. & Gray, P.R. (1985). A high-performance micropower switched-capacitor filter, *IEEE Journal of Solid-State Circuits*. Vol.20, No.6, (December 1985), pp. (1122- 1132). ISSN 0018-9200.

- Chae, Y. and Han. G (2009). *Low Voltage, Low Power, Inverter-Based Switched-Capacitor Delta-Sigma Modulator.* IEEE J. Solid-State Circuits, Vo. 44, No. 2, (Jan. 2009), pp. (458 - 472).

- Chanapromma, C.; Silapan, P.; Duangmalai, D. & Siripruchyanun, M. (2010). An Ultra Low-Power Fully Differential Operational Transconductance Amplifier (FD-OTA) operating in Weak-Inversion Region and Its Applications, *Proceedings of the 1st International Conference on Technical Education, ICTE2009*, (January 2010), pp. (176-179).

- Colodro, P.; Torralba, A. & Laguna, M. Continuous-Time Sigma-Delta Modulator With an Embedded Pulsewidth Modulation. *IEEE Trans. on Circuits and Systems-I*, vol. 55, Issue 3, March 2008, pp. (775-785).

- Comer, D. J. & Comer, D. T (2004). Using the weak inversion region to optimize input stage design of op amps. *IEEE Transactions on Circuits and Systems II*, Vol. 51, No. 1, (January 2004), pp. (8–14).

- Comer, D. J. & Comer, D. T (2004). Operation of analog MOS circuits in the weak or moderate inversion region. *IEEE Transactions on Education*, Vol. 47, No. 4, (November 2004), pp. (430–435).

- Copeland, M. A. & Rabaey, J.M., E. (1979). Dynamic amplifier for m.o.s. technology. Electronic Letters. Vol. 15, No. 10, (May 2010), pp. (301-302). ISSN 0013-5194.

- Corbishley, P. & Rodríguez-Villegas, E. (2007). A Nanopower Bandpass Filter for Detection of an Acoustic Signal in a Wearable Breathing Detector, *IEEE Transactions On Biomedical Circuits and Systems*, Vol. 1, No. 3, (September 2007), pp. (163-171).

- Degrauwe, M.; Rijmenants, J.; Vittoz, E. & De Man, H. (1981). CMOS Adaptive Biasing Amplifier. *Proceedings of the European Solid State Circuits Conference, ESSCIRC 1981*, ISBN: 3800712385, Freiburg, September 1981.

- Draxelmayr, D. A 6b 600MHz 10mW ADC Array in Digital 90nm CMOS. Digest of Technical Papers of IEEE International Solid-State Circuits Conference 2004, February 2004.

- Enz, C. C.; Krummenacher, F. & Vittoz, E. A (1995). An analytical MOS transistor model valid in all regions of operation and dedicated to low voltage and low-current applications, *Analog Integr. Circuits Signal Process. J.*, Vol. 8, (July 1995), pp. (83–114).

- Farshidi, E. & Alaei-sheini, N. (2009). A Micropower Current-Mode Sigma-Delta Modulator for Biomedical Applications, *IEEE Signal Processing and Communications Applications Conference*, SIU 2009, (2009), pp. (856-859).

- Fiorenza, J. K.; Sepke, T.; Holloway, P.; Sodini, C. G. and Lee, H.-S. (2006). *Comparator-based switched-capacitor circuits for scaled CMOS technologies*, IEEE J. Solid-State Circuits, Vol. 41, (Dec. 2006), pp. (2658–2668).

- Flynn, M. P.; Donovan, C. & Satler, L. Digital calibration incorporating redundancy of Flash ADCs. *IEEE Transactions on Circuits and Systems II*, vol. 50, no 5, May 2003, pp. (205-213)

- Gray, P. R.; Hurst, P. J.; Lewis, S. H. & Meyer, R. G. (2001). *Analysis and Design of Analog Integrated Circuits*. Wiley, ISBN: 0471321680, New York.

- Harjani, R.; Heineke, R. & Feng W. (1999). An integrated low-voltage class AB CMOS OTA, *IEEE Journal of Solid-State Circuits*. Vol.34, No.2, (February 1999), pp.(134-142). ISSN 0018-9200.

- Harpe, P.; Cui Zhou; Xiaoyan Wang; Dolmans, G and de Groot, H. (2010). A 30ff/conversionstep 8b 0-to-10MS/s asynchronous SAR ADC in 90nm CMOS, ISSCC Dig. Tech. Papers, (7-11 Feb. 2010), pp. (388-389).

- Hashemi, S. & Shoaei, O.; A 0.9-V 10-bit 100-MSample/s pipelined ADC using switched-RC and opamp sharing techniques. 50th Midwest Symposium on Circuits and Systems 2007, Aug. 2007.

- Hosticka, B. J. (1979). *Dynamic CMOS amplifiers*, IEEE J. Solid-State Circuits, Vol. 14, (Dec. 1979), pp. (1111–1114).

- Jimenez-Irastorza, A.; Sevillano, J.F.; Berenguer, R. and Rebollo, I. (2011). *Recursive Successive Approximation Time-to-Digital Converter for low-power RFID tag sensors, XXVI Conference on Design of Circuits and Integrated Systems (DCIS), (November 2011).*

- Kijima, M.; Ito, K.; Kamei, K. & Tsukamoto, S. A 6b 3GS/s Flash ADC with Background Calibration. *Proceedings of IEEE 2009 Custom Intergrated Circuits Conference*, San Jose, CA, September 2009.

- Kim, H.-C.; Jeong, D.-K. & Kim, W. A partially switched-opamp technique for high-speed low-power pipelined analog-to-digital converters. *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol.53, no.4, April 2006, pp. (795-801).

- Klinke, R.; Hosticka, B.J. & Pfleiderer, H. (1989). A very-high-slew-rate CMOS operational amplifier, *IEEE Journal of Solid-State Circuits*. Vol.24, No.3, (June 1989), pp. (744-746). ISSN 0018-9200.

- Kuo, C.-H. & Liu, S.-H. A 1-V 10.7-MHz Fourth-Order Bandpass ΣΔ Modulators Using Two Switched Opamps. IEEE Journal of Solid-State Circuits, vol. 39, n<sup>a</sup> 11, November 2004, pp. (2041-2045).

- Kuo, C-H.; Shi, D-Y. & Chang K-S. (2010). A Low-Voltage Fourth-Order Cascade Delta-Sigma Modulator in 0.18-µm CMOS. *IEEE Transactions on Circuits and Systems I:* Regular Papers, Vol. 57, No. 9, (Sept. 2010), pp.(2450-2461).

- López-Martin, A.J.; Baswa, S.; Ramirez-Angulo, J & Carvajal, R.G. (2005). Low-Voltage Super class AB CMOS OTA cells with very high slew rate and power efficiency, *IEEE Journal of Solid-State Circuits*. Vol.40, No.5, (May 2005), pp. (1068- 1077). ISSN 0018-9200.

- López-Martin, A.J.; Ramirez-Angulo, J.; Carvajal, R.G. & Acosta, L. (2009). Power-efficient class AB CMOS buffer, *Electronics Letters*. Vol.45, No.2, (January 2009), pp. (89-90). ISSN 0013-5194.

- Luján, C.I.; Torralba, A.; Carvajal, R.G.; Ramírez-Angulo, J. (2011), Highly linear voltage follower based on local feedback and cascode transistor with dynamic biasing, *Electronics Letters*, Vol.47, No.4, (February 2011) pp.244-246. ISSN 0013-5194.

- Markovic, D.; Wang, C. C.; Alarcon, L. P.; Tsung-Te, Liu & Rabaey, J. M (2010). Ultralow-Power Design in Near-Threshold Region. *Proceedings of the IEEE*, Vol. 98, No. 2, (February 2010), pp. (237-252).

- Murmann, B. (2008). A/D Converter Trends: Power Dissipation, Scaling and Digitally Assisted Architectures. *Proceedings of IEEE Custom Integrated Circuits Conference*, 2008, CICC 2008. ISBN 978-1-4244-2018-6, San Jose, CA, November 2008.

- Musah, T.; Gregoire, B.R.; Naviasky, E. and Moon, U.-K. (2007). Parallel correlated double sampling technique for pipelined analogue-to-digital converters, Electronics Letters, Vol. 43, No. 23, (Nov. 2007), pp. (1260-1261).

- Omeni, O.; Rodríguez-Villegas, E. & Toumazou, C. (2005). A Micropower CMOS Continuous-Time Filter With On-Chip Automatic Tuning, *IEEE Transactions on Circuits and Systems I, Vol.* 52, No. 4, (April 2005), pp. (695-705).

- Ou, Hsin-Hung; Chen, Ya-Chi & Liu, Bin-Da (2006). A 0.7-V 10-bit 3 μW Analog-to-digital Converter for Implantable Biomedical Applications, *IEEE Biomedical Circuits and Systems Conference, BioCAS 2006*, (2006), pp. (122-125).

- Ozgun, M. T.; Tsividis, Y. & Burra, G. (2006). Dynamic power optimization of active filters with application to zero-IF receivers, *IEEE Journal of Solid-State Circuits*. Vol. 41, No 6. (June 2006), pp. (1344-1352). ISSN 0018-9200.

- Park, S.; Palaskas, Y. & Flynn, M.P. A 4-GS/s 4-bit Flash ADC in 0.18-μm CMOS. IEEE *Journal of Solid state circuits*, vol. 42, n°2, September 2007, pp. (1865-1872).

- Pavan, S; Krishnapura, N.; Pandarinathan, R. & Sankar, P. (2008). A Power Optimized Continuous-Time SD ADC for Audio Applications. *IEEE Journal of Solid-State Circuits*, Vol. 43, No. 2, (Feb. 2008), pp.(351-360).

- Pavan, S. and Sankar, P. (2010). Power Reduction in Continuous-Time Delta-Sigma Modulators Using the Assisted Opamp Technique. IEEE Journal of Solid-State Circuits, Vo. 45, No. 7, (July 2010), pp. (1365-1379).

- Ramírez-Angulo, J. & Holmes, M. (2002). Simple technique using local CMFB to enhance slew rate and bandwidth of one-stage CMOS op-amps, *Electronics Letters*, Vol.38, No.23, (November 2002), pp. (1409-1411). ISSN 0013-5194.

- Ramírez-Angulo, J.; Urquidi, C. A.; González-Carvajal, R.; Torralba, A. & López-Martín, A. J. (2003). A new family of very low voltage analog circuits based on quasi-floating-gate transistors, *IEEE Transactions on Circuits and Systems II*, Vol. 50, No. 5, (May 2003), pp. (568–571).

- Ramírez-Angulo, J.; López-Martín, A. J.; Carvajal, R. G. & Muñoz-Chavero, F. (2004). Very low-voltage analog signal processing based on quasi-floating gate transistors, *IEEE Journal of Solid-State Circuits*, Vol. 39, No. 3, (March 2004), pp. (434–442).

- Ramírez-Angulo, J.; Carvajal, R. G.; Galan, J. & López-Martín, A. J. (2006). A free but efficient low-voltage class-AB two-stage operational amplifier, *IEEE Transactions on Circuits and Systems II*, Vol. 53, No. 7, (July 2006), pp. (214–220), ISSN 1549-7747.

- Roh, J.; Byun, S.; Choi, Y.; Roh, H.; Kim, Y. & Kwon, J. (2008). A 0.9-V 60μW 1-Bit Fourth-Order Delta-Sigma Modulator With 83-dB Dynamic Range. *IEEE Journal of Solid-State Circuits*, Vol. 43, No. 2, (Feb. 2008), pp.(361-370).

- Sánchez-Sinencio, E. & Silva-Martínez, J., (2000), CMOS transconductance amplifiers, architectures and active filters: a tutorial, *IEE Proceedings Circuits, Devices and Systems*. Vol. 147, No. 1, (February 2001), pp. (3-12). ISSN 1350-2409.

- Sasidhar, N.; Y.-J. Kook; Takeuchi, S.; Hamashita, K.; Takasuka, K.; Hanumolu, P.K. & U.-K. Moon; A Low Power Pipelined ADC Using Capacitor and Opamp Sharing Technique With a Scheme to Cancel the Effect of Signal Dependent Kickback. *IEEE Journal of Solid-State Circuits*, vol.44, no.9, Sept. 2009, pp. (2392-2401)

- Sawigun, C. & Serdijn, W.A. (2009). Ultra-low-power, class-AB, CMOS four-quadrant current multiplier, *Electronics Letters*. Vol.45, No.10, (May 2007), pp. (483-484). ISSN 0013-5194.

- Sawigun, C.; Serdijn, W.A. (2011). Analysis and Design of a Low-Voltage, Low-Power, High-Precision, Class-AB Current-Mode Subthreshold CMOS Sample and Hold Circuit, IEEE Transactions on Circuits and Systems I: Regular Papers. Vol.58, No.7, (July 2011), pp.(1615-1626). ISSN 1549-8328.

- Shahab, A. (December 2010). On Achieving the Minimum Energy for Sending One Single Bit with Feedback. MSc Thesis from Delft University of Technology. Available from: http://repository.tudelft.nl/.

- Shin, S.-K.; You, Y.-S.; Lee, S.-H.; Moon, K.-H.; Kim, J.-W.; Brooks, L. and Lee, H. S. (2008). *A fully-differential zero-crossing-based 1.2 V 10b 26 MS/s pipelined ADC in 65 nm CMOS, IEEE Trans. VLSI Syst.*, (Jun. 2008).

- Steyaert, M.; Bijker, W. & Sevenhans, J. (1991). ECL-CMOS and CMOS-ECL interface in 1.2-pm CMOS for 1.50-MHz digital ECL data transmission systems, *IEEE Journal of Solid-State Circuits*, Vol. 26, No. 1, (January 1991), pp. (18–24).

- Sundström, T. & Alvandpour, A. Utilizing process variations for reference generation in a Flash ADC. *IEEE transactions on circuits and systems II*, vol. 56, no 5, May 2009, pp. (364-368).

- Tan, C. & Chen, Z., An efficient CMOS operational amplifier for driving large capacitive loads, International Conference on ASIC, ASICON 2007, ISBN 978-1-4244-1132-0, Guilin, October 2007.

- Tsividis, Y. (2002). *Mixed Analog-Digital VLSI Devices and Technology*. World Scientific, ISBN: 9812381112, Singapore.

- Van der Plas, G.; Decoutere, S. & Donnay, S. A 0.16pJ/Conversion-Step 2.5mW 1.25 GS/s 4b ADC in a 90nm Digital CMOS Process. *Digest of Technical Papers of IEEE International Solid-State Circuits Conference* 2006, February 2006.

- van Veldhoven, R. H. M. van; Rutten, R. and Breems, L. J. (2008). An inverter based hybrid  $\Sigma\Delta$  modulator, IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers, (Feb. 2008), pp. (492–493).

- Vaz, A.; Solar, H.; Rebollo, I.; Gutierrez, I. and Berenguer, R. (2010). *Long range, low power UHF RFID analog front-end suitable for batteryless wireless sensors,* IEEE International Microwave Symposium Digest, (May 2010), pp.(836-839).

- Vittoz, E. A. (1994). Micropower techniques, In: Design of MOS VLSI Circuits for Telecommunications. Prentice-Hall, ISBN: 0-13-203639-8, USA.

- Vittoz, E. A. (2009). Weak Inversion for Ultra Low-Power and Very Low-Voltage Circuits, *IEEE Asian Solid-State Circuits Conference*, (November 2009), pp. (129-132).

- Wang, H.; Xu, J. and Wu, X. (2009). A high power efficiency Class AB switched-opamp for low voltage low power sigma-delta modulators. IEEE International Conference of Electron Devices and Solid-State Circuits, EDSSC 2009. Vol., No., (25-27 Dec. 2009). pp.(429-432).

- Wismar, U.; Wisland, D. & Andreani, P. (2006). A 0.2V 0.44μW 20 kHz Analog to Digital SD Modulator with 57 fJ/conversion FoM. Proceedings of the 32nd European Solid-State Circuits Conference, 2006. ESSCIRC 2006, (19-21 Sept. 2006), pp.(187-190).

- Yang, H.Y.; Sarpeshkar, R. (2005). A time-based energy-efficient analog-to-digital converter, IEEE Journal of Solid-State Circuits, Vol.40, No.8, (Aug. 2005), pp.(1590-1601).

- Yang, H.Y.; Sarpeshkar, R. (2006). A Bio-Inspired Ultra-Energy-Efficient Analog-to-Digital Converter for Biomedical Applications. IEEE Transactions on Circuits and Systems I: Regular Papers, Vol.53, No.11, (Nov. 2006), pp.(2349-2356).

- Yao, L.; Steyaert, M. S. J. & Sansen, W. (2004). A 1-V 140-IA 88-dB audio sigma-delta modulator in 90-nm CMOS, *IEEE Journal of Solid-State Circuits*, Vol. 39, No. 11, (November 2004), pp. (1809–1818).

- Yao, L.; Steyaert, M. & Sansen, W. (2006). Low-Power Low-Voltage Sigma-Delta Modulators in Nanometer CMOS. Springer. ISBN-13 978-1-4020-4139-6 (HB), The Netherlands.

- Yeknami, A.F.; Qazi, F.; Dabrowski; J.J. and Alvandpour, A. (2010). *Design of OTAs for Ultra-Low-Power Sigma-Delta ADCs in Medical Applications*. International Conference on Signals and Electronics Systems ICSES, Poland, September 2010.

#### **Energy Efficiency in Communications and Networks**

Edited by Dr. Sameh Gobriel

ISBN 978-953-51-0482-7 Hard cover, 142 pages Publisher InTech Published online 04, April, 2012 Published in print edition April, 2012

The topic of "Energy Efficiency in Communications and Networks" attracts growing attention due to economical and environmental reasons. The amount of power consumed by information and communication technologies (ICT) is rapidly increasing, as well as the energy bill of service providers. According to a number of studies, ICT alone is responsible for a percentage which varies from 2% to 10% of the world power consumption. Thus, driving rising cost and sustainability concerns about the energy footprint of the IT infrastructure. Energy-efficiency is an aspect that until recently was only considered for battery driven devices. Today we see energy-efficiency becoming a pervasive issue that will need to be considered in all technology areas from device technology to systems management. This book is seeking to provide a compilation of novel research contributions on hardware design, architectures, protocols and algorithms that will improve the energy efficiency of communication devices and networks and lead to a more energy proportional technology infrastructure.

#### How to reference

In order to correctly reference this scholarly work, feel free to copy and paste the following:

E. López-Morillo, F. Márquez, T. Sánchez-Rodríguez, C.I. Luján-Martínez and F. Munoz (2012). Achieving Energy Efficiency in Analogue and Mixed Signal Integrated Circuit Design, Energy Efficiency in Communications and Networks, Dr. Sameh Gobriel (Ed.), ISBN: 978-953-51-0482-7, InTech, Available from: http://www.intechopen.com/books/energy-efficiency-in-communications-and-networks/achieving-energy-efficiency-in-analog-integrated-circuit-design

# INTECH

open science | open minds

#### InTech Europe

University Campus STeP Ri Slavka Krautzeka 83/A 51000 Rijeka, Croatia Phone: +385 (51) 770 447

Fax: +385 (51) 686 166 www.intechopen.com

#### InTech China

Unit 405, Office Block, Hotel Equatorial Shanghai No.65, Yan An Road (West), Shanghai, 200040, China 中国上海市延安西路65号上海国际贵都大饭店办公楼405单元

Phone: +86-21-62489820 Fax: +86-21-62489821 © 2012 The Author(s). Licensee IntechOpen. This is an open access article distributed under the terms of the <u>Creative Commons Attribution 3.0</u> <u>License</u>, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.