Open access • Proceedings Article • DOI:10.1109/FUSION.2003.1426670

# Active filter hardware design & performance for the DIII-D plasma control system — Source link

D. Sellers, J.R. Perron, M.L. Walker, J.D. Broesch Institutions: General Atomics Published on: 01 Oct 2003 - IEEE/NPSS Symposium on Fusion Engineering Topics: Bessel filter, Chebyshev filter, Active filter, Filter (signal processing) and Control system

#### Related papers:

- Digital filter design techniques in the frequency domain

- Analog means of shaping the frequency response characteristics of digital filter [and Doppler tracking application]

- Digital parametric filters for studio mixing desk

- · Hybrid filter for high-power converter systems

- · Regular-sampled current measurement in AC drives using delta-sigma modulators

GA-A24469

i.

л:,

201 10 10

ю.

## ACTIVE FILTER HARDWARE DESIGN & PERFORMANCE FOR THE DIII-D PLASMA CONTROL SYSTEM

by D. SELLERS, J.R. FERRON, M.L. WALKER and J.D. BROESCH

**MARCH 2004**

### DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

GA-A24469

), j

ř

## ACTIVE FILTER HARDWARE DESIGN & PERFORMANCE FOR THE DIII-D PLASMA CONTROL SYSTEM

## by D. SELLERS, J.R. FERRON, M.L. WALKER and J.D. BROESCH

This is a preprint of a paper presented at the 20th IEEE/NPSS Symposium on Fusion Engineering, San Diego, California, October 14–17, 2003 and to be published in *Fusion Science and Technology*.

Work supported by the U.S. Department of Energy under Contract No. DE-AC03-99ER54463

GENERAL ATOMICS PROJECT 30033 MARCH 2004

### Active Filter Hardware Design & Performance for the DIII–D Plasma Control System

D. Sellers, J.R. Ferron, M.L. Walker, J.D. Broesch General Atomics, P.O. Box 85608, San Diego, California 92186-5608

Abstract. The digital plasma control system (PCS), currently in operation on the DIII-D tokamak, requires inputs from a large number of sensors. Due to the nature of the digitizers and the relative noisy environment from which these signal are derived, each of the 32 signals must be conditioned via an active filter. Two different types of filters, Chebyshev and Bessel with fixed frequencies: 100Hz Bessel was used for filtering the motional Stark effect diagnostic data. 800 Hz Bessel was designed to filter plasma control data and 1200 Hz Chebyshev is used with closed loop control of choppers. The performance of the plasma control system is greatly influenced by how well the actual filter responses match the software model used in the control system algorithms. This paper addresses the various issues facing the designer in matching the electrical design with the theoretical.

#### I. INTRODUCTION

This paper will cover the hardware side of designing an active filter. The characteristics of analog filter circuits are subject to drift and are dependent on temperature. Active filters do not suffer from these problems, and are extremely *stable* with respect both to time and temperature. Unlike their passive counterparts, active filters can handle *low frequency signals* accurately. One of the critical requirements of the PCS filters was low frequency noise 10 Hz and below, at 0 Hz primary.

Design of accurate filters for the plasma control systems (PCS), depends not only on stable electrical values selected for filter frequency, but on the printed circuit board (PCB) layout techniques to add to or correct any anomalies that the fabrication may create. The design and analysis of active filter circuits can be very complex. Many equations, design charts, and computer programs have been created to produce optimum design for various filter performances. Symbols and scales are defined in Table I.

#### II. DESIGN PROCESS

A passive low-pass filter circuit consists of a resistor and a capacitor. The filter load  $(Z_L)$  is connected in parallel with the capacitor. This illustrates a major problem for passive

| TABLE I     |

|-------------|

| DEFINITIONS |

| Symbol    | Definition                                |

|-----------|-------------------------------------------|

| PCB       | Printer Circuit Board                     |

| 6U        | 6.3 inch x 9.175 PCB board                |

| fC        | Corner Frequency                          |

| $Q^{f_C}$ | Quality Factor<br>10 <sup>-12</sup> Farad |

| pF        | $10^{-12}$ Farad                          |

| nF        | 10 <sup>-9</sup> Farad                    |

| μF        | 10 <sup>-6</sup> Farad                    |

| ESR       | Equivalent series resistance              |

| POD       | Adjustable Resistor                       |

filters: unless  $Z_L$  is much larger than  $X_C$  the load is likely to affect the filter performance [1]. Additional PCB traces can make it possible to add resistance and or board capacitance. Connecting a voltage follower to the circuit eliminates the load problem and converts the circuit into an active filter. Active filters have very high input impedances and very low output impedances. This makes their response essentially independent of source and load impedance and their changes.

Device selection was a very critical process. Resistor and capacitor values selected must have very low tolerances. The resistors must have tolerance of < 1%. All of the resistors used, theoretically, should be identical in values so that only the capacitors varied the needed frequency.

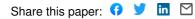

To minimize the possible changes of  $f_C$  and Q, NPO (stable with temperature) (COG) ceramic capacitors were used if possible. NPO capacitors hold their nominal values over a wide temperature and voltage range (Fig. 1). The other various ceramics capacitor types are X7R, Z5U and Y5V. COG-type ceramic capacitors are the most precise. Their values range from 0.5 pF to 47 nF [2]. NPO capacitors were not available in the ranges needed for a large amount of the desired filter frequencies, so X7R-type ceramic capacitors were used where needed and range from 100 pF to 2.2 µF with initial tolerance over temperature of  $< \pm 10\%$  ( $\pm 20\%$  is normal for most ceramic capacitors). Tantalum electrolytic capacitors with equivalent series resistance (ESR) were used for power management and decoupling. Tantalum capacitors placed on the filter power supply offer stability and improved ability to withstand high inrush currents high ripple current. Sensitivity is the measure of the limitation of the filters performance to change in component values. The most important filter parameters to consider are the corner frequency and quality factor,  $f_C$  and Q.

The format of the filter boards is the PCI form factor "6U." A number of off-the-shelf racks and enclosures to support the filter cards are available in CPI format and are designed for low noise, redundant power supplies. This was

Fig. 1. Change in capacitors values (%) over temperature and voltage.

ideal in that development did not have to focus on mounting hardware and interface issues.

#### III. SCHEMATICS AND PCB

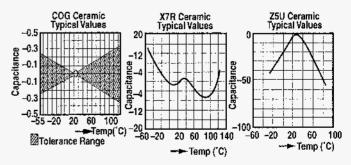

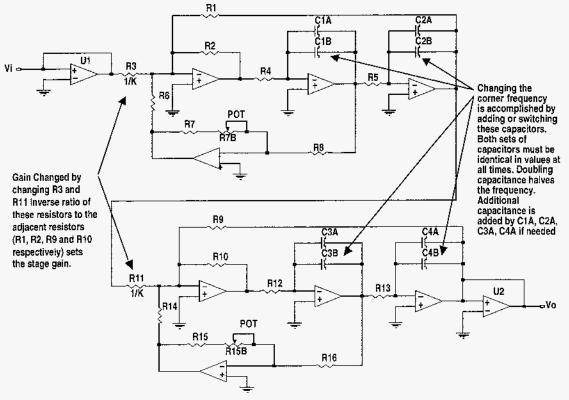

Schematic design and PCB layout were created using OrCad capture and OrCad layout software tools (Fig 2). The filter schematic was designed with 32 identical filter blocks per filter card. Channels 1 to 3 in the schematics included test points, placed before and after each active order section of the design for testing and verification of the design including extra I/O connectors for addional testing without use of SCSI-3 I/O (Fig. 3).

Testing and tuning each of the 32 filter channel included the option to add and remove additional values to each filter channel. This was needed since capacitors and resistors are not made in every numerical numbers and our calculated values along with small PCB board resistance variations, makes matching very difficult.

Schematics were designed with trim pots (R7B, R15B Fig. 2) to add resistance to adjust the filters Q, which is the inverse damping effect at the cutoff frequency. Additional capacitors placed in parallel with C1A and C2A were added as needed, adding capacitance, for fine tuning to the required frequency.

The PCB filters design can affect critical characteristics of a filter. The PCB board was designed with 10 trace layers. Multiple ground planes, plus ground (GND) copper pours (copper fills between traces) on each non-plane layer reduced ground-current resistance and inductance, and are connected to each other by GND vias. To control crosstalk, input and output signals were placed on layers 1 and 3 of the PCB board, GND planes were placed on layer 2 and 4 and a copper pour on the top layer to control signal jump between traces. The PCB board was designed with 0.005 inch traces for signals. Power and GND traces are 0.020 inch wide. Due to the 0.005 inch trace widths, the PCB board top and bottom copper layer were increased to 2 oz. thickness to keep the traces from being damaged during assembly and for long term reliability (Figs. 4 and 5).

Traces between each cascading section of the active filters were designed to have identical internal trace lengths. Minimizing trace lengths and keeping input circuits as far as possible from output circuits was also a design goal. The input and output traces were not a concern due to the voltage followers U1 and U2. With the use of null (0  $\Omega$ ) resistors, additional trace lengths were added to the design to correct the trace lengths on filter channel blocks.

#### IV. TUNING

Design issues and the larger number of devices needed for each of the 32 channels on one filter board made adjustments and tuning to the proper filter value very difficult. The capability for placement of additional parts and possible adjustments on key points of the design was very helpful when testing.

A change in frequency can be completed by varying R4, R5, R12, R13, but all four of the resistors values must be identical at all times. The design calculation was done with the use of stable matching 10 K resistors, so the frequency was adjusted by adding additional capacitance on C1B, C2B, C3B,

Fig. 2. Single filter channel schematics.

Fig. 3. Channel 1 included test headers before and after each filter pole. Adjustable resistors (Potentimeter) were used to tune in each channel and later replaced by a fixed value.

Fig. 4. Front side of 32 channel filter PCB in 6U PCI format.

Fig. 5. Back side of 32 channel PCB.

C4B or changing the value of C1A, C2A, C3A, and C4A. With the use of NPO capacitors, additional capacitance was added where needed.

#### V. BESSEL FILTER TUNING

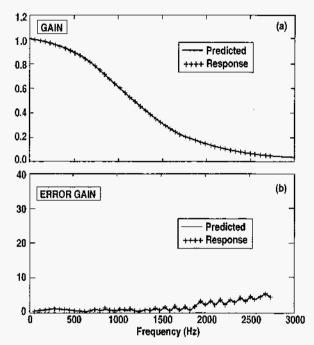

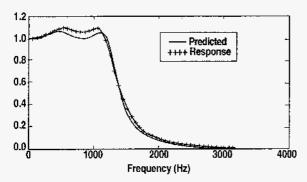

The 800Hz Bessel filters required capacitor values of 0.0138  $\mu$ F (0.012  $\mu$ F + 0.0018  $\mu$ F) for the 1st and 2nd stage 0.01239  $\mu$ F (0.012  $\mu$ F + 0.00039  $\mu$ F) for the 3rd and 4th stage. The test results producing low error were due to matching capacitor values (calculated versus real world values) and low tolerance devices used for this particular filter frequency (Fig. 6).

Fig. 6. (a) Bessel filter tuning frequency response. (b) Bessel filter tuning error response.

#### VI. CHEBYSHEV FILTER TUNING

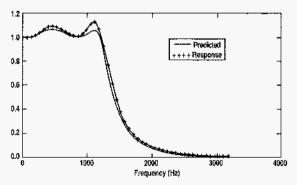

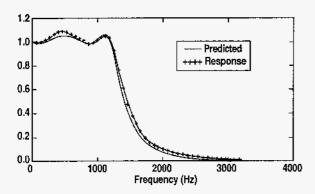

Calculated values needed were 0.02219  $\mu$ F for C1 and C2, 0.01286  $\mu$ F for C3 and C4. Fig. 7 shows the response with 0.022  $\mu$ F for C1, C2 and 0.012  $\mu$ F for C3 and C4. Additional capacitors were installed to correct the "real values" with the calculated values (180pF = C1A, C2A and 82pF = C3A, C4A). Figs. 7 and 8 show the frequency plots before and after these additions. To adjust the underdamped response adjustable resistor R7B was adjusted as necessary (Fig. 9).

Fig. 7. Chebyshev filter tuning using nominal values of  $0.022 \ \mu\text{F}$  for C1, C2 and  $0.012 \ \mu\text{F}$  for C3 and C4.

Fig. 8. Chebyshev filter tuning after compensation capacitors added, 180pF = C1A, C2A, 02pF = C3A and C4A.

Fig. 9. Chebyshev filter tuning using compensated capacitors and adjusting R7B.

#### VII. CONCLUSION

Optimizing PCB layout for best active filters can be summarized in a few simple rules:

- Keep input and output lines as far apart as possible, within the constraint of keeping components close to all other devices in that filter channel.

- Solid ground planes between trace layers,

- Copper pours on each PCB layer.

- Add additional tuning capability:

- Potentiometers

Additional footprints

- Use <1% matching resistors, <5% tolerance capacitors (very critical)

- Future design approaches:

- Check for manufactured filter blocks

- Use of X2Y capacitors

#### ACKNOWLEDGMENT

Work supported by U.S. Department of Energy Contract No. DE-AC03-99ER54463.

#### REFERENCES

- [1] D.A Bell "Operational Amplifiers" Englewoodd Cliffs, New Jersey, Prentice Hall (1990) p266 -267.

- [2] D. Lancaster "Active Filter Cookbook." Jordan Hill, Oxford: Synergetics Press (1975).