# Adaptively-Biased Capacitor-Less CMOS Low Dropout Regulator with Direct Current Feedback

Yat-Hei Lam

Wing-Hung Ki

Chi-Ying Tsui

Department of EEE Hong Kong University of Science & Technology Hong Kong SAR, China e-mail: hylas@ee.ust.hk Department of EEE Hong Kong University of Science & Technology Hong Kong SAR, China e-mail: eeki@ee.ust.hk Department of EEE Hong Kong University of Science & Technology Hong Kong SAR, China e-mail: eetsui@ee.ust.hk

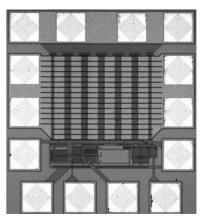

Abstract — A capacitor-less low dropout regulator (LDR) with direct current feedback is proposed. A symmetrically-matched voltage mirror in sensing the load current is employed, and gives excellent line and load regulations. The dynamic biasing results in an LDR with pole-tracking that extends the bandwidth of the loop gain at high load currents. The LDR was fabricated in a 0.35µm CMOS process with an active area of 0.11mm², and measurement results corroborated well with both analysis and simulation.

## I. Introduction

Embedding a low dropout regulator (LDR, also known as LDO) into an IC chip for on-chip power regulation can reduce the circuit board area, but bulky off-chip capacitors are usually unavoidable for adequate filtering. In addition, on-chip compensation capacitors are usually needed and this takes up valuable silicon area.

The performance of the LDR depends much on the design of the error amplifier in the voltage feedback loop. To increase the gain and bandwidth of the loop, and to eliminate the output capacitor, multi-stage amplifier with a rather sophisticated compensation scheme was proposed [1]. However, an on-chip compensation capacitor of even a few pF occupies a large silicon area, and it is better if they could further be reduced, or even eliminated. An LDR needs a large biasing current for the high-gain high-speed error amplifier for control, especially when the load current is high. It would be advantageous if the bias current of the LDR is adaptive to the load, such that at light load, the bias current is low for high efficiency, and at heavy load, the bias current is high for high speed control.

## II. LDR WITH DIRECT CURRENT FEEDBACK

The first LDR with a dynamically biased voltage buffer was proposed in 1998 [2] but a BiCMOS process is needed and accurate current sensing was achieved due to the difference in  $|V_{ds}|$  between the sensing transistor and the power transistor.

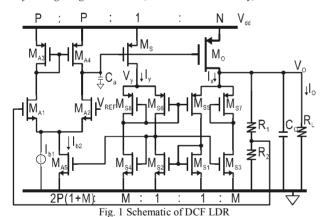

Fig. 1 shows our proposed LDR that employs an accurate current sensor using a symmetrically-matched (SM) voltage mirror [3, 4]. Two feedback loops can be identified. The scaled output voltage is compared to the reference voltage  $V_{\rm ref}$  through an error amplifier that is simply a differential pair, and the output of which drives the pass transistor  $M_o$  to supply the load cuurent. This is the voltage feedback loop. The current feedback loop consists of the SM voltage mirror that provides a bias current  $I_{b2}$  for the error amplifier that drives  $M_o$  to complete the loop. The error amplifier is biased by  $M_{\rm S5}$  and it sinks a current of [2P/N]× $I_{\rm do}$  which is the feedback current generated by the current sensor. The fed back bias current is accurately proportional to  $I_o$ , and we coined this action as direct current feedback (DCF). The drain current of the power transistor  $M_o$  bears a square relation with the gate overdrive voltage:

$$I_{do} = \frac{1}{2} \mu_p C_{ox} (W/L)_{M_o} (|V_{gso}| - |V_{tp}|)^2 (1 + |\lambda_p V_{dso}|)$$

(1)

Suppose the drain current of  $M_{o}$  increases to  $I_{do}\text{+}i_{do}$  due to an

This research is in part supported by Research Grant Council CERG HKUST 6311/04E.

increase in load current. To accommodate this change, the gate overdrive voltage  $|V_{gso}| - |V_{tp}|$  has to increase according to equation (1) to keep the output voltage constant. Now, with the ratio assignment of Fig. 1, the drain current of  $M_{A3}$  increases from  $(P/N)I_{do}$  to  $(P/N)(I_{do}+i_{do})$ , providing just the correct overdrive voltage for  $M_{A4}$  and thus,  $M_o$ . Consequently, an excellent load regulation is obtained.

For stability and bandwidth, we note that the proposed LDR has two high impedance nodes related to the feedback loops. The first one is at the output of the error amplifier Va, and is the dominant pole  $p_a = 1/(C_aR_a)$ , where  $C_a$  is mainly the very large gate capacitance of  $M_o$ , and  $R_a$  is the output resistance at  $V_a$ . The second pole is at the output of the regulator  $V_0$ , with  $p_0 = 1/(C_0 R_0) \propto I_0$ , where  $C_0$  is the drain capacitance of  $M_0$  plus the parasitic capacitance of the packaging, and  $R_o = r_{do} ||R_L|| (R_1 + R_2) \propto 1/I_o$ . Since the proposed LDR has no output filtering capacitor, po is much larger than p<sub>a</sub>. Now, the criteria of design is to make sure that p<sub>o</sub> is higher than the unity gain frequency  $\omega_t$  due to the single pole roll-off of  $p_a$ , and  $\omega_t = bg_{mA1}g_{mo}R_o/C_a$ .  $M_{A1}$  and  $M_{A2}$  are designed to work in weak inversion region at light to medium load such that  $g_{mA1} \propto I_o$  [5]. At light load,  $M_0$  works in weak inversion region also and  $g_{mo} \propto I_0$ , giving  $\omega_t \propto I_o$ . The unity gain bandwidth tracks with  $p_o$ . At medium load,  $M_0$  works in strong inversion region such that  $g_{mo} \propto \sqrt{I_0}$ , while  $M_{A1}$  and  $M_{A2}$  are designed to stay in weak inversion region, thus  $\omega_t$  $\propto \sqrt{I_o}$ . The bandwidth  $\omega_t$  is still extending with the load current but at a slower rate. At heavy load, MAI, MA2 and Mo work in strong inversion region, and  $g_{mA1}$ ,  $g_{mo} \propto \sqrt{I_o}$ , giving  $\omega_t$  independent of  $I_o$ . Separation between  $\omega_t$  and  $p_o$  becomes larger as  $I_o$  increases. As a result, if the LDR is stable at a light load current, it is guaranteed to be stable at a higher load current.

## III. SIMULATION AND MEASUREMENT RESULTS

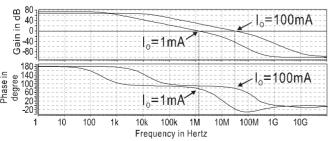

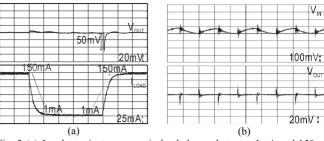

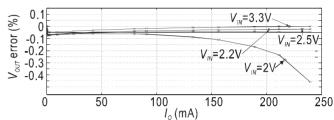

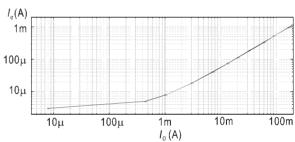

The direct current feedback low dropout regulator was fabricated in a 0.35µm CMOS process. Fig.2 shows the simulated loop gain response. Pole tracking is evident as both p<sub>a</sub> and p<sub>o</sub> move to higher frequencies at a high load current, with po moves faster than pa, and the unity gain bandwidth is extended. Fig.3(a) shows the measured load transient response of the DCF LDR with a current step of 1mA to 150mA. For a load change from high to low, the initial large bias current gives a fast response and the ripple is small, only 4mV, and is even smaller than 0.5% of the output voltage. For a load change from low to high, the initial bias current of the error amplifier is small and the response is slow and leads to a larger glitch of 50mV at the output. As the bias current increases with the load current, the bandwidth increases and the output voltage is stabilized very quickly. The 1% settling time (18mV of 1.8V) is less than 200ns. Fig.3(b) shows the rejection of switching noise. In this measurement, the LDR is cascaded to a switching converter. Low frequency ripples are filtered out effectively and high frequency glitches are attenuated by approximately 14dB. Fig.4 shows the measured output voltage vs the load current and the supply voltage. For a load current that changes from 0 to 240mA at  $V_{dd}$  = 2.2V, the load regulation is only  $2.77\mu V/mA$  (664 $\mu V$  in total). Note that for a conventional LDR, the output voltage decreases monotonically as the load current increases, but for the proposed DCF LDR, the output voltage increases initially at light load current, which is due to the current feedback mechanism using the symmetrically-matched voltage mirror, and the load regulation is not solely controlled by the gain of the error amplifier. Fig.5 shows the measured quiescent current  $I_q$  vs the load current  $I_q$ . The quiescent current includes the currents consumed by the error amplifier, the voltage mirror and the feedback resistors. At light loads,  $I_q$  is closed to  $I_{b1}$  (a very small bias current in case the load current goes to zero) plus the current of the potential divider, but as  $I_q$  is larger than ImA,  $I_q$  increases linearly, which implies that the current sensor works properly. Table 1 summarizes the specifications of the proposed DCF LDR. Fig.6 shows the chip micrograph.

### IV. Conclusions

We demonstrated a working low dropout regulator that employed adaptive biasing and symmetrical matching techniques. Remarkable performance in both load transient response and load regulation are shown in the measurement results. The resultant LDR needs no filtering and compensation capacitors, and fabrication cost could be much reduced. Therefore, it is suitable for system-on-chip (SOC) applications and as an on-chip power regulator.

#### REFERENCES

- K. N. Leung and P. Mok, "A capacitor-free CMOS low-dropout regulator with damping-factor-control frequency compensation," *IEEE J. of Solid-State Ckts.*, Vol.38, No.10, pp.1691-1702, Oct. 2003.

- [2] G. A. Rincon-Mora and P. E. Allen, "A low-voltage, low quiescent current, low drop-out regulator," *IEEE J. of Solid-State Ckts.*, Vol.33, No.1, pp.36–44, Jan. 1998.

- [3] Y. H. Lam, W. H. Ki, C. Y. Tsui and D. Ma, "Integrated 0.9V charge-control switching converter with self-biased current sensor," IEEE Int'l Midwest Symp. on Ckts. & Sys., Hiroshima, Japan, pp.305–308, July 2004.

- [4] Y. H. Lam, W. H. Ki and C. Y. Tsui, "Symmetrically matched voltage mirrors and applications therefor," US Patent Application No. 11/185,294, July 20, 2005.

- [5] P. R. Gray, P. J. Hurst, S. H. Lewis and R. G. Meyer, Analysis and design of Analog Integrated Circuits, 4<sup>th</sup> ed. New York: Wiley, 2001.

Fig. 2 Loop gain simulation of DCF LDR

Fig. 3 (a) Load transient response in load change between 1mA and 150mA (2µs/div) and (b) Line ripple rejection with high frequency switching noise

Fig. 4 Load regulation of the DCF LDR

Fig. 5 Quiescent current versus load current

TABLE 1 SPECIFICATIONS OF THE DCF LDO REGULATOR

| Technology                                                            | 0.35µm CMOS process     |

|-----------------------------------------------------------------------|-------------------------|

| Chip area (including pads)                                            | 0.32 mm <sup>2</sup>    |

| Chip area (active circuit area)                                       | 0.11mm <sup>2</sup>     |

| $V_{dd}$                                                              | 2-3.6V                  |

| V <sub>0</sub>                                                        | 1.8V                    |

| Maximum I <sub>0</sub>                                                | 240 mA                  |

| Quiescent Current @ I₀=0mA                                            | 3 μΑ                    |

| Quiescent Current @ I₀=200mA                                          | 1.03 mA                 |

| Load regulation @ V <sub>dd</sub> =2.2V, I <sub>O</sub> =0mA to 240mA | 2.77μV/mA (664μV total) |

| Line regulation @ $V_{dd}$ =2V to 3.6V, $I_O$ =100mA                  | <0.8mV/V (1.28mV total) |

| Line ripple rejection @ 10kHz                                         | >40 dB                  |

| Output impedance @ 1MHz (I <sub>o</sub> =100mA)                       | 200mΩ                   |

Fig. 6 Chip micrograph of the DCF LDR