# **ARTICLE**

https://doi.org/10.1038/s41467-019-13176-4

OPFN

# All WSe<sub>2</sub> 1T1R resistive RAM cell for future monolithic 3D embedded memory integration

Maheswari Sivan<sup>1</sup>, Yida Li<sup>1\*</sup>, Hasita Veluri<sup>1</sup>, Yunshan Zhao<sup>1</sup>, Baoshan Tang<sup>1</sup>, Xinghua Wang<sup>1</sup>, Evgeny Zamburg <sup>1</sup>, Jin Feng Leong<sup>1</sup>, Jessie Xuhua Niu<sup>1</sup>, Umesh Chand<sup>1</sup> & Aaron Voon-Yew Thean <sup>1\*</sup>

3D monolithic integration of logic and memory has been the most sought after solution to surpass the Von Neumann bottleneck, for which a low-temperature processed material system becomes inevitable. Two-dimensional materials, with their excellent electrical properties and low thermal budget are potential candidates. Here, we demonstrate a low-temperature hybrid co-integration of one-transistor-one-resistor memory cell, comprising a surface functionalized 2D WSe<sub>2</sub> p-FET, with a solution-processed WSe<sub>2</sub> Resistive Random Access Memory. The employed plasma oxidation technique results in a low Schottky barrier height of 25 meV with a mobility of 230 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, leading to a 100x performance enhanced WSe<sub>2</sub> p-FET, while the defective WSe<sub>2</sub> Resistive Random Access Memory exhibits a switching energy of 2.6 pJ per bit. Furthermore, guided by our device-circuit modelling, we propose vertically stacked channel FETs for high-density sub-0.01  $\mu$ m<sup>2</sup> memory cells, offering a new beyond-Si solution to enable 3-D embedded memories for future computing systems.

1

<sup>&</sup>lt;sup>1</sup>Department of Electrical and Computer Engineering, National University of Singapore, 4 Engineering Drive 3, Singapore 117583, Singapore. \*email: li.yida@nus.edu.sg; Aaron.Thean@nus.edu.sg

merging non-von Neumann architectures with intensive in-memory computing like next-generation deep learning and neuromorphic chips will demand high-density integration of embedded memory. Three-dimensional monolithic (sequential) multilayer stacking of transistors and memory among interconnects may allow us to expand the on-chip memory density. Such architectures will not only overcome the two-dimensional (2D) die limitations but also enable new three-dimensional (3D) computation systems, where logic and memory elements are intimately co-located, to significantly improve the memory access bandwidth and energy<sup>1</sup>. However, to fully realize such 3D systems, there are fundamental technology challenges to overcome. Among which, transistorinterconnect thermal budget incompatibility poses a major road block. Advanced low-resistivity copper interconnect with low-k dielectric interlayer cannot tolerate thermal exposure above 400 °C<sup>2</sup>. Since the thermal activation of dopants in Sibased devices are typically between 600 and 1000 °C, Si transistor formation below such temperature results in device performance and reliability degradations<sup>3</sup>. This low thermal budget technology barrier calls for both material and process integration breakthroughs, to enable new platforms for 3D integration.

Carbon nanotubes (CNTs) field-effect transistor (FETs) and 2D semiconducting van der Waal-layered crystals (2DMat) have drawn immense attention as transistor channel material, due to their intrinsic performance that rivals silicon, as well as upcoming successors like germanium, silicon germanium, and III-V compound semiconductors at sub-nanometer channel thickness regime<sup>4</sup>. More importantly, the potential of such nanomaterials for low-temperature, large-area transfer and integration, independent of their material synthesis<sup>5,6</sup>, puts them in an advantageous position to be co-integrated additively with metal interconnects on CMOS (complementary metal-oxide-semiconductor) chips (Supplementary Table 1). The feasibility of 3D integration with CNTs has already been demonstrated by Shulaker et al.1, but that of 2DMat has only started to gain traction<sup>7</sup>. 2DMat, with their intrinsic nanolayer structures and variety of electronic structures are expected to add more functionalities for process temperature-limited technologies like sequential/monolithic 3D chips<sup>8</sup> and highperformance flexible electronics<sup>9</sup>.

In this work, we demonstrate the feasibility of hybrid cointegration of a surface-engineered WSe2-based thin film transistor (TFT) and resistive random access memories (ReRAM) to realize a 1 transistor-1 resistor (1T1R) memory cell. This is done through integrating WSe2 of different morphologies (single crystalline for TFT, and polycrystalline for ReRAM) processed through different synthesis technique, to address the conflicting charge transport attributes required for logic and memory. As TFT should be optimized for high performance and low leakage, the high-quality mechanically exfoliated WSe2 is utilized as the transistor channel. On the other hand, ReRAM should be optimized for low-voltage defect-enabled switch ability, for which solution-processed WSe2 is employed. Despite WSe2 2DMat being well investigated for future logic application, its application for 1T1R memory cell by hybrid co-integration is yet to be investigated. Moreover, our proposed processes are room temperature based, offering compelling compatibility with temperature-limited 3D monolithic process integration and flexible electronics processing. Furthermore, we propose through calibrated compact device modeling and circuit simulations that sub-0.01 µm<sup>2</sup> 1T1R cells with good read/write margins are feasible by stacking 2D nanosheets to realize a multiple-stacked 2D TFTs to drive the 2D ReRAMs.

## Results

WSe<sub>2</sub> select transistor material. With a large bandgap, a reasonably high intrinsic thin-channel carrier mobility  $^{10}$ , and n-ppolarity that can be easily modulated by contact Schottky barrier metal<sup>11</sup>, WSe<sub>2</sub> offers great potential for low leakage and performant CMOS logic gates<sup>12</sup>. The low on-state resistance and offstate leakage potential of the WSe<sub>2</sub> transistor also makes them a good select transistor candidate for 1T1R memories, which calls for minimization of voltage loss across the transistor during memory cell set/reset and the off-state sneak current in the array, respectively. Despite the favorable intrinsic attributes, WSe<sub>2</sub> transistors are still challenged by extrinsic degradations in mobility and high contact resistance. The reports of WSe2 exhibiting high mobility at low temperatures 13 suggest the detrimental role played by various scattering sources, such as phonons, Coulomb impurities (CI), and intrinsic defects in mobility degradation. Although passivation methods based on dielectric deposition, including atomic layer-deposited high-k encapsulation<sup>14</sup>, have been pursued, the process uniformity remains challenging due to undesired grain boundary nucleation<sup>15</sup>. Thus, it becomes necessary to investigate other strategies including uniform native oxide passivation solution as well.

In addition, minimizing transistor access resistance is essential to translate the performance gains from channel carrier mobility. While heavy source/drain (S/D) doping is the most preferred method for improving contact resistance in conventional Si devices, such substitutional doping in 2DMat comes at the expense of increased defect density<sup>16</sup>. For 2DMat, several approaches ranging from material modification to the cointegration of graphene electrodes<sup>17</sup> have been proposed. However, they present new challenges in stability and workfunction limitations. For example, the semiconducting 2H phase to metallic 1T phase modification 18 can improve contact resistance significantly, but the low-temperature stability and Fermi level to conduction band alignment limits its utilization for p-FETs<sup>14</sup>. Graphene contacts, due to its Fermi level alignment close to the conduction band, would also lead to undesirable electron injection for p-FETs<sup>17</sup>. In this work, we concurrently address strategies for hole carrier doping, mobility enhancement, Schottky barrier, and contact resistance reduction through a single-step process that overcomes the issues of stability and p-contact work-function alignment. We developed a selflimiting single-step, low-temperature WO<sub>3</sub> formation on channel surface and under the S/D contacts by post-contact remote plasma oxidation. This process simultaneously enhances the WSe<sub>2</sub> TFT mobility by almost 76 times and reduces the contact resistance by a hundred-fold. By implementing Ag-WO<sub>3</sub>-WSe<sub>2</sub> metal-insulator-semiconductor (MIS) contact, we achieved an ultra-low Schottky barrier height (SBH) of 25 meV with respect to the WSe<sub>2</sub> valence band, significantly enhancing hole injection.

Low-temperature surface layer plasma oxidation for WSe<sub>2</sub> FET. For 2D transition metal dichalcogenides (TMDs), the thickness is

a critical parameter influencing their electronic and optical properties. Although mechanical exfoliation results in high-quality WSe<sub>2</sub> flakes, the approach does not allow for precise thickness control. Considerable amount of research has been devoted to realizing a thickness reduction strategy, such as the use of focused ion beam<sup>19</sup>, ozone treatment<sup>20,21</sup>, XeF<sub>2</sub> vapors<sup>22</sup>, plasma oxidation<sup>23</sup>, thermal oxidation<sup>24</sup>, and so on. However, these approaches can induce minor<sup>22</sup> as well as major damage to the crystallinity of the WSe<sub>2</sub> material with resultant negative impact to its electrical performance. While the above-mentioned reports focus on oxidation as a thickness reduction strategy for mechanically exfoliated samples, we introduce a low-temperature

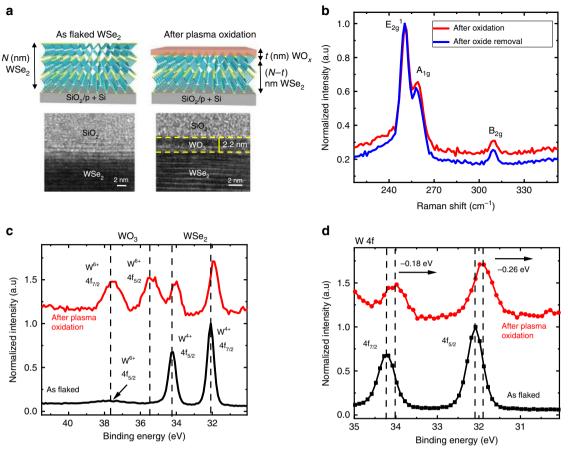

**Fig. 1** Remote plasma oxidation process and characterization. **a** Schematic representation of surface plasma oxidation and the corresponding cross-sectional transmission electron microscope (xTEM) images. The xTEM image of oxidized WSe<sub>2</sub> shows 2.2 nm of WO<sub>3</sub> upon oxidation, which is a consumption of three layers of WSe<sub>2</sub>. **b** Raman spectroscopy comparison before oxidation and after oxide removal, in order to have comparison between WSe<sub>2</sub> of same thickness. No apparent change in peak position is observed, implying no crystalline damage due to plasma oxidation. **c** X-ray photoelectron spectroscopy (XPS) comparison of as flaked WSe<sub>2</sub> and plasma-oxidized WSe<sub>2</sub>. The appearance of two additional peaks after oxidation corresponds to an *x* factor of 3 in WO<sub>x</sub>. **d** W 4f core level XPS spectrum comparison of pristine WSe<sub>2</sub> and plasma-oxidized WSe<sub>2</sub>. The observed shift to lower binding energy implies electron transfer from WSe<sub>2</sub> to WO<sub>3</sub>

remote plasma oxidation process (Methods section) and study the utility of the formed oxide as a MIS contact and encapsulation layer using detailed material and electrical characterization. We show that gentle plasma oxidation can create a layer of surface  $WO_x$ , which do not damage the underlying  $WSe_2$  structure. Figure 1a shows the cross-sectional transmission electron microscope (xTEM) image of the  $WSe_2$  flake before and after the remote plasma oxidation, from which the presence of  $WO_x$  and the quality of exposed  $WSe_2$  are confirmed. The thickness of the formed  $WO_x$  is ~2.2 nm for a consumption of three layers of  $WSe_2$ , as confirmed by xTEM. Irrespective of oxidation time, the  $WO_x$  formation is found to be self-limiting as well (Supplementary Fig. 1). The same oxide thickness has been validated for  $WSe_2$  of different starting area and thicknesses under the same oxidation condition.

Raman spectroscopy and X-ray photoelectron spectroscopy (XPS) analysis were done to determine the nature of  $WO_x$  formed by this process. As the vibrational and optical properties strongly vary with thickness, a comparison of "oxidized WSe<sub>2</sub>" and "oxide-removed WSe<sub>2</sub>" has been performed. The oxide removal process, which is selective to WSe<sub>2</sub>, is done using KOH solution (Methods section). From the Raman spectrum in Fig. 1b, we observe the typical out-of-plane  $A_{1g}$  mode, in plane  $E_{2g}$  mode and the bulk,  $B_{2g}$  mode for two prepared four-layer WSe<sub>2</sub> samples; one with WO<sub>x</sub> (after oxidation) and one

without  $WO_x$  (after oxide removal). No apparent Raman peak shift is detected between the two samples-ruling out the presence of any plasma oxidation induced stress in WSe<sub>2</sub>. The resultant WOx appears to be amorphous due to the absence of the  $800 \,\mathrm{cm}^{-1}$  signature peak, indicating crystalline  $\mathrm{WO}_x^{25}$ (Supplementary Fig. 2). The amorphous  $WO_x$  structure is further corroborated by the xTEM images (Fig. 1a), which did not reveal any crystalline order in the WO<sub>x</sub> layer. Since there exists reports of crystalline WO3 formed through air heating at higher temperature of 400 °C<sup>25</sup>, the amorphous WO<sub>x</sub> is likely due to our low-temperature plasma oxidation process. From the XPS analysis in Fig. 1c, we confirm the stoichiometry of amorphous  $WO_x$  to be native  $WO_3$ . Specifically, peaks at 35.5 and 37.7 eV after plasma oxidation correspond to the binding energies of W<sup>6+</sup>, indicating the presence of WO<sub>3</sub><sup>25</sup>. Furthermore, we observe charge transfer mediated by WO<sub>3</sub> from the XPS spectrum after plasma oxidation. The observed decrease in binding energy of W 4f core levels (0.18 eV reduction in W4+  $4f_{7/2}$  and 0.26 eV reduction in W<sup>4+</sup>  $4f_{5/2}$ ) (Fig. 1d) suggests that there is electron transfer from WSe<sub>2</sub> to WO<sub>3</sub>. This is attributed to the high work function of WO3 consistent with other reported studies<sup>22</sup> We show here that low-temperature plasma oxidation, capable of self-limiting to ~2.2 nm amorphous WO<sub>3</sub>, produces an ultra-thin hole donor layer that is also gentle to WSe<sub>2</sub>.

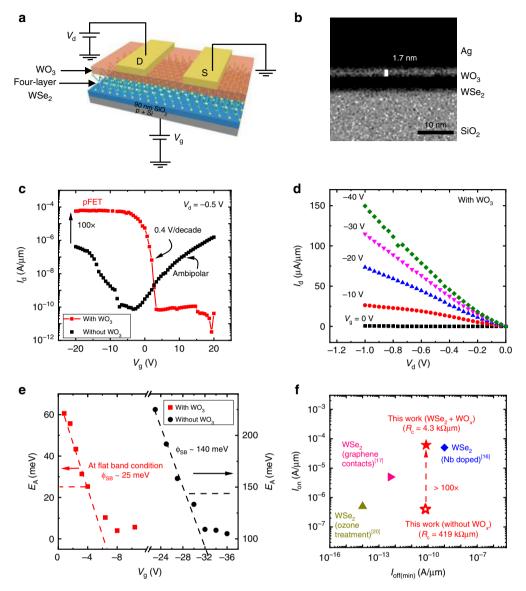

**Fig. 2** Surface plasma-oxidized WSe<sub>2</sub> TFT and electrical characterization. **a** Device schematic showing a four-layer WSe<sub>2</sub> and 2.2 nm WO<sub>3</sub> on SiO<sub>2</sub>/p + Si layer with gate length ( $L_g$ ) = 1.80 μm and width (W) = 2.05 μm. **b** Transmission electron microscopy image of the device contact region, after post-contact plasma oxidation, revealing the presence of WO<sub>3</sub> underneath the metal contacts. **c**  $I_d$ -V $_g$  plots for four-layer thick device with and without WO<sub>3</sub>. **d**  $I_d$ -V $_d$  characteristics after plasma oxidation for different gate voltages. **e** Effective Schottky barrier height extraction from low-temperature transfer characteristics and Arrhenius plot. At flat band condition, the curve deviates from linearity and the corresponding activation energy becomes the Schottky barrier. **f** Benchmark plot showing the performance of plasma-oxidized p-FET versus other reported data.  $I_{on}$  is determined at  $V_d$  = -0.5 V

Figure 2a shows the schematic of the fabricated device consisting of a four-layer WSe<sub>2</sub> and three-layer WO<sub>3</sub>. The detailed fabrication procedure can be found in the Methods section. In order to realize a thinner WO<sub>3</sub> layer under the Ag S/D contacts to minimize tunneling resistance, we chose to perform post-contact plasma oxidation. The key advantage of this strategy is that the WO<sub>3</sub> growth rate under the S/D region would be moderated by the metal contact. The TEM image (Fig. 2b) confirms thinner (1.7 nm) WO<sub>3</sub> layer under the contact as opposed to the thicker (2.2 nm) oxide formation for the exposed channel, despite the common plasma oxidation process. Due to limited diffusion of O radicals at the Ag-WSe2 terminations on both ends of the electrodes, the O radicals can only propagate laterally under the Ag contacts, resulting in a reduced thinning of WSe<sub>2</sub> layer<sup>24</sup> under the contact metal as opposed to the exposed channel regions.

We characterized the resultant TFT performance by measuring the transfer and output characteristics (Fig. 2c, d). Figure 2c compares the transfer characteristics with and without post-contact plasma oxidation. The devices without WO<sub>3</sub> is unremarkable, showing ambipolar conduction, with slightly stronger n-type ( $V_{\rm g} > -5$  V) than p-type conduction ( $V_{\rm g} < -5$  V). Upon plasma oxidation, the device exhibits strong p-type conduction. Most remarkably, a  $100\times$  enhancement in the hole current is accompanied by a strong polarity change, where n-type conduction is completely suppressed. To further investigate the TFT performance improvement, we carefully characterized the influence of WO<sub>3</sub> on mobility and contact resistance.

We measured the gate inversion capacitance of the oxidized device and found it to have increased by  $2\times$  compared to the geometrical value (77 vs.  $38\,\mathrm{nF\,cm^{-2}}$ ). Details of inversion capacitance extraction are found in Supplementary Fig. 3 and

Supplementary Note 1. Since we do not observe CV frequency dispersion (Supplementary Figure 3e) that indicates significant fast or slow charge trapping/de-trapping processes, we exclude the possibility of spurious charges and disorder at WSe<sub>2</sub> bottomgate dielectric interface as reported by Pradhan et al. 13. Instead. we believe the interfacial charge transfer at the WSe<sub>2</sub>-WO<sub>3</sub> heterostructure contributed towards the capacitance increase. To ensure accurate mobility extraction, we emphasize here the need for CV measurements, instead of making capacitance assumptions based on geometry. From Fig. 2c and the measured inversion capacitance, we extracted a dramatic 76× hole fieldeffect mobility ( $\mu_{FE}$ ) increase from 3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (non-oxidized) to 230 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and observed a significant 100× reduction of contact resistance ( $R_c$ ) to 4.3 k $\Omega$ µm from our control with 420 kΩμm, which is extracted using the well-reported  $R_{\text{total}}$ - $V_{\text{g}}$ method<sup>26</sup>. The details of field-effect mobility and contact resistance extraction can be found in the Supplementary information (Supplementary Figs. 4 and 5). The  $R_c$  reduction correlates to a considerable lowering of the contact's SBH to 25 meV with respect to the SBH of 140 meV of our control sample without WO<sub>3</sub> as shown in Fig. 2e. It appears that the thin WO<sub>3</sub> under the Ag contact unpinned the contact Fermi level with respect to WSe2, closer to the valence band minimum of WSe2, owing to the high work function of WO<sub>3</sub><sup>27</sup>. This would also explain the observed suppression of electron current, as the SBH for electrons would be large. Our room temperature, low-power remote plasma oxidation treatment allows a gentler process to achieve less damage to the underlying WSe2 flake, as evident by the non-reduction of the PL signal<sup>23</sup> (Supplementary Fig. 6) as compared to other reported methods<sup>28</sup>. In addition, the plasma process allows the formation of a uniform thin layer of WO<sub>3</sub> beneath the contact, which has not been reported. The argument is supported by the observed SBH to be 10× lower than the barrier height reported from other work involving similar surface functionalization with WO<sub>3</sub><sup>20</sup>

Furthermore, we conducted an experiment, where the plasma oxidation was performed prior to contact formation, leading to a uniform thicker (2.2 nm) WO<sub>3</sub> under S/D contacts and over the channel (Supplementary Fig. 7). While the drive current slightly improved compared to non-oxidized device, the performance is weaker than the post-contact-oxidized sample due to higher contact resistance, which is comparable to the device without oxidation (Supplementary Fig. 5). This suggests the importance of controlling WO3 thickness, as a tunneling layer—the thicker WO<sub>3</sub> with pre-contact oxidation actually degrades the contact resistance due to increased tunneling resistance<sup>29</sup>. Figure 2f benchmarks selected top-performing WSe2 devices from various reports. Our work shows the strongest Ion performance for devices with sub-nA μm<sup>-1</sup>-level I<sub>off\_min</sub>, showing an extraordinary 100× drive current enhancement with respect to our non-WO<sub>3</sub> control (Supplementary Table 2).

WSe<sub>2</sub> ReRAM material, fabrication, and characterization. 2DMat-based ReRAM on multilayer hBN<sup>30,31</sup>, solution-processed multilayer 2D ReRAM<sup>32–35</sup>, MoS<sub>2</sub> phase change memristor behavior<sup>36</sup>, novel resistive switching approaches such as gate tunable non-volatile resistive switching in monolayer MoS<sub>2</sub> via atomic re-arrangement of grain boundaries<sup>37</sup>, and fast switching operation enabled by electric field-induced structural transition in MoTe<sub>2</sub> and Mo<sub>1 – x</sub>W<sub>x</sub>Te<sub>2</sub><sup>38</sup> have been demonstrated. Here, we investigate the potential of a Ag-WSe<sub>2</sub>-Ag ReRAM comprising of a solution-processed WSe<sub>2</sub> as the resistive memory element and Ag as electrodes, realized using a high-precision Aerosol Jet printing (Methods section and Supplementary Table 3). Apart from being compatible with 3D monolithic integration, the

solution-processed approach combined with the aerosol jet printing is chosen to leverage on the in situ sonication-induced modulation of defects in the switching layer through ink quality to study the device impact due to different WSe<sub>2</sub> morphologies<sup>39</sup>. Compared to traditional metal oxide-based ReRAMs, the realization of forming-free operation with lower switching voltage and current is one of the defining advantages of solution-processed WSe<sub>2</sub> ReRAM. This may be due to the defect formation and migration with respect to the flake morphology as opposed to shorted metallic conductive bridges in oxide ReRAM<sup>40</sup>. Together with the unique material properties, we demonstrate Ag/WSe<sub>2</sub>/Ag ReRAM that exhibits non-volatile, forming-free, sub-1 V switching characteristics at a set current  $\leq 5 \,\mu\text{A}$ , with a low switching energy of 2.9 pJ per bit.

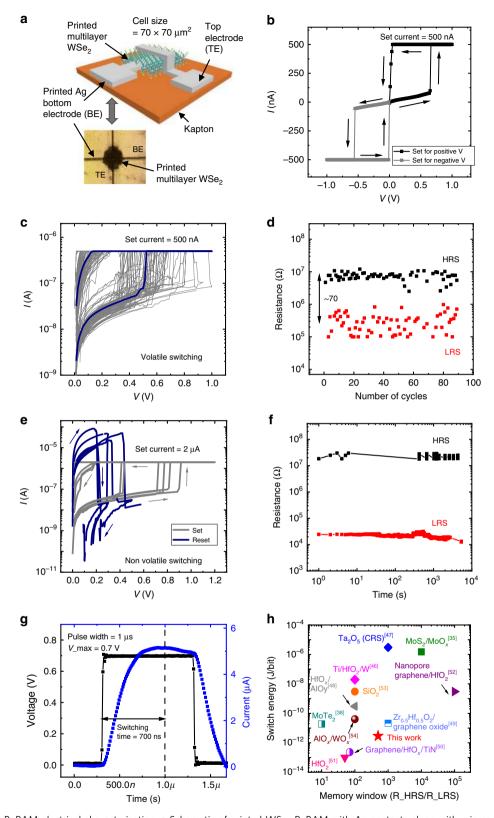

Figure 3a shows the schematic and the optical microscope image of the WSe2 ReRAM with Ag contact. We performed a detailed material characterization using scanning electron microscopy (SEM), Raman spectroscopy and X-ray diffraction (Supplementary Fig. 8). As observed from SEM images, the morphology of the as-printed WSe2 layer is highly disordered with randomly distributed clusters, significantly different from the exfoliated-transferred WSe2 for the TFT. Raman analysis shows that the E2g mode of the printed WSe2 is consistent with the exfoliated WSe<sub>2</sub>. The absence of interlayer coupling-B<sub>2g</sub> mode and the out-of-plane A<sub>1g</sub> mode is likely due to the disordered morphology of the printed WSe2. The non-orientated switching layer morphology is desired for the vertical memory element as we seek to promote volume-based vacancy or filamentary switching for our devices. Figure 3b shows the direct current (DC) sweep characteristics over a voltage range of -1 to 1 V with a set current limit to 500 nA. The device exhibits forming-free behavior, which can be set in both positive and negative polarity bias. We observe an abrupt switching at sub-1 V set voltage, indicating filamentary-based conduction. Under a set current of 500 nA, the switching characteristic is found to be volatile, that is, the low resistance state (LRS) decays quickly to high resistance state (HRS) after the bias is removed. Figure 3c shows the DC stress cycling of the device over 90 cycles, while Fig. 3d shows the repeatability of the HRS/LRS over the 90 cycles at a read voltage of 50 mV. The device achieves an average HRS/LRS window of ~70 over all the cycles tested. When the set current is increased to 2 μA, the device transitions to a non-volatile switching state. We believe that with the larger set current, the filament thickens and remains stable without external bias<sup>41</sup>. The ReRAM exhibits a unipolar switching behavior where set and reset voltages share the same polarity. As observed in many of the unipolar ReRAM, the reset operation is dominated by the thermophoresis effect<sup>42</sup>, where joule heating ruptures the filament, thus returning the device to the HRS state. The reset voltage ranges from 0.2 to 0.3 V, while the reset current lies in between 80 and 100 μA, as shown in Fig. 3e. The observation of the unipolar switching characteristics is concomitant with that of chemical vapor depositiongrown WSe<sub>2</sub> reported by Ge et al<sup>43</sup>. We observe a larger memory window of 103 when the set current is increased to 5 µA and achieves a retention time of  $>10^4$  s (Fig. 3f).

We have confirmed that the switching is not due to Ag ion diffusion in  $WSe_2$  by comparing the ReRAM switching behavior of otherwise identical devices with inert carbon-based electrodes (Supplementary Fig. 9 and Supplementary Discussion 1), which show similar abrupt switching characteristics. This indicates that the switching mechanism is intrinsic to the  $WSe_2$  switching layer, likely due to selenium vacancies, thus ruling out the possibility of Ag metal ion conductive-bridge-based mechanism. The switching time, as calculated by applying a voltage pulse of amplitude 0.7 V and 1  $\mu$ s width is found to be 700 ns (Fig. 3g). With the trade-off existing between programing voltage and switching time<sup>44</sup>, we

**Fig. 3** Printed WSe<sub>2</sub> ReRAM electrical characterization. **a** Schematic of printed WSe<sub>2</sub> ReRAM with Ag contacts along with microscope image of printed ReRAM. **b** The device sets from HRS to LRS for both positive and negative voltages. **c** Stress cycling data for 90 cycles at a smaller set current of 500 nA, where volatile behavior is observed. **d** Endurance properties of ReRAM at read voltage of 50 mV and a set current of 500 nA. **e** Set and reset operation with a larger set current of  $2 \mu$ A, exhibiting non-volatile behavior. **f** Retention plot showing LRS and HRS stability till  $10^4$  s at a read voltage of 50 mV and set current of  $5 \mu$ A. **g** Switching time characterization with an AC pulse of 0.7 V amplitude and  $1 \mu$ s pulse width. **h** Benchmark plot of switching energy per bit vs. memory window of printed WSe<sub>2</sub> ReRAM with other representative non-volatile resistive switching publications

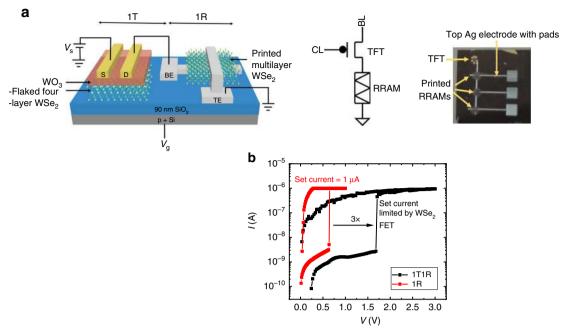

**Fig. 4** 1T1R configuration and characterization. **a** 3D schematic view of 1T1R structure with flaked WSe<sub>2</sub> transistor and printed WSe<sub>2</sub> ReRAM and the corresponding circuit representation. The photo image of 3× WSe<sub>2</sub> ReRAMs printed using low-temperature aerosol jet printing method, which is linked up to the fabricated WSe<sub>2</sub> TFT on a single chip is also shown. **b** *I-V* switching plot for 1T1R configuration, where the switching current is limited by the transistor drive current

have chosen to limit the programming voltage to achieve low set power, which results in slower switching time of 700 ns. From the material/structural point of view, controlling the flake size and thickness of the switching layer would be areas that could potentially offer improvement in switching speed<sup>45</sup>. Our devices show one of the lowest reported switching energy (Supplementary Fig. 10, Supplementary Table 4, and Supplementary Note 2) relative to other 2DMat<sup>35,38</sup> and other oxide-based ReRAMs<sup>46-54</sup>, as illustrated in the Fig. 3h with endurance comparable to other reported 2DMat ReRAMs (Supplementary Table 5). We suspect that the low switching energy is promoted by the excess defects and grain boundaries in our printed WSe2 layer. We performed repeatability check for ReRAM devices fabricated across several batches at different times, where we observed consistent switching characteristics, as shown in the cumulative probability distribution plot for set voltage, reset voltage, and ReRAM resistance (Supplementary Fig. 11). We believe that there is still significant opportunity for improvement with respect to ReRAM endurance and other metrics by engineering the flake sizes with the solutionprocessed approach.

Although Aerosol jet printing technique allows additive deposition of inks with a wide range of viscosities to realize quick prototyping of devices at relaxed dimensions (down to  $10\,\mu m$  feature size), it is not a suitable method for industrial-scale production because of the low throughput and large feature size achievable. Except for the low thermal budget of our process, we do not believe that our additive approach would significantly change the device conclusions for the solution-deposited and subtractive methods like solution spin coating, compatible with large-scale dense circuit integration.

# All WSe<sub>2</sub> 1T1R memory cell integration and characterization.

The approaches of in-memory and neuromorphic computing based on embedded memory have recently garnered great momentum, with growing interests to apply ReRAM<sup>55</sup>. However, high-density cross-bar ReRAM array suffers from current cross-talk interference due to sneak currents<sup>56</sup>, resulting in misreading

and unintended disturbance of memory states as well as undesirable increase in memory standby power consumption. By employing a select transistor to isolate the selected ReRAM cell from unselected cells, a 1T1R architecture can be implemented to circumvent these problems<sup>57,58</sup>. Since the 1T1R cell leakage is gated by the select transistor off-state leakage, it is necessary for the select transistor bandgap to be appropriately wide to limit S/D band-to-band leakage current due to the memory operating voltage. WSe<sub>2</sub> possess suitable bandgap in the range of 1.2 eV (bulk) to 1.6 eV (monolayer), limiting the transistor minimum off-state leakage to be in the order of  $pA\,\mu m^{-1}$  for operating voltages in the range of 0.8-1.5 V. On the other hand, the maximum on-state drive current of the select transistor should support the set voltage and reset current of the ReRAM. However, the low intrinsic drive current of 2D TMD-based TFT makes it difficult to drive the ReRAM. Therefore, we propose to utilize the performance enhancement in plasma-oxidized WSe<sub>2</sub> to mitigate this issue.

We integrated the TFT and the ReRAM on the same chip to study the co-integration and its functionality (Fig. 4a), where the WSe<sub>2</sub> ReRAM is printed after the WSe<sub>2</sub> TFT fabrication. The measured 1T1R circuit configuration is as depicted in Fig. 4a. Figure 4b shows the successful switching of the WSe<sub>2</sub> ReRAM by the WSe<sub>2</sub> TFT. As expected, the TFT's on-state resistance increased the memory cell switching voltage to 1.7 V, which is almost 3× larger than that of the ReRAM alone. This clearly highlights the gating impact of the select transistor performance for the memory cell. It is necessary to decrease the TFT on-state resistance while maintaining low off-state leakage to limit sneak current. This becomes increasingly challenging with decreasing cell size where TFT area is constrained. In the next section, we investigate the cell design with the use of material-calibrated compact models and circuit simulations, which would allow us to project for scaled-up memory array implementation.

Material-device-circuit co-design of 1T1R memory cell. In order to evaluate the memory cell for scaled technologies and to

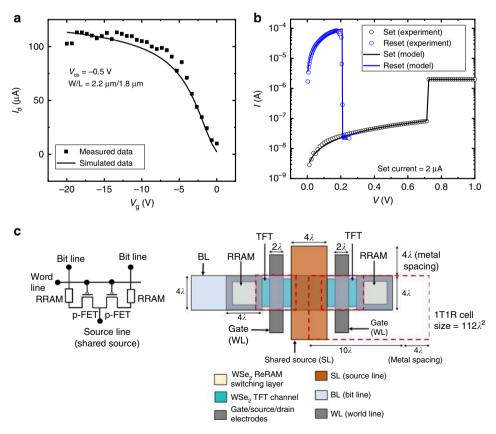

project for future 1T1R technology, we investigate the materialsystem co-design using detailed circuit modeling and study the disruptive impact of material properties on the system design considerations. A BSIM-IMG compact circuit model<sup>59</sup> description of the TFT has been calibrated to experiment-based longchannel devices and known WSe<sub>2</sub> material parameters. Shortchannel effects such as velocity saturation, GISL (gate-induced source leakage) and GIDL (gate-induced drain leakage) has been taken into account for the scaled devices through modeling. A hysteron-based compact model, as reported by Garcia-Redondo et al.<sup>60</sup>, has been calibrated to the WSe<sub>2</sub> ReRAM. Guided by experimental data, we applied these models largely behaviorally, given that the physics of these devices are not well described yet. Despite this, we expect these models to be accurate for our SPICE circuit analysis. Figure 5a, b show the compact model behavior for WSe<sub>2</sub> TFT and ReRAM, respectively, which correlates well with the experimental data.

We project scaled technology performance by calibrating our device and circuit models with intrinsic long-channel mobility and contact resistance enhancement salient to our 2D WSe<sub>2</sub> approach. Our aim is to provide a first-order comparison between different material systems and their potential system impact, without the distraction of subjective details specific to scaled device design (such as interface trap density, S/D tunneling, etc. as explained in Supplementary Fig. 12 and Supplementary Discussion 2) and other more complex technology factors. We recognize that detailed technology factors related to scaled transistor/memory device behavior, interconnect properties, physical layout, and process integration approaches would be useful to refine the system view in the future. Here, we analyze the 1T1R cell scaling using  $\lambda$ -based design rule description, where

$F = 4\lambda = \text{minimum metal } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{T1R cell size is limited by } \frac{1}{2} \text{ pitch and } 1\text{ pitch and } 1\text$ the select transistor size (min. cell area =  $112\lambda^2$ )<sup>61</sup>. The layout of such a shared-source 1T1R cell is shown in Fig. 5c. As the 1T1R memory cell is scaled down, the selector drive current degrades with the linear reduction of width ( $W = 4\lambda$ ), whereas the ReRAM switching current is largely insensitive to the cell size due to filamentary switching<sup>43</sup>. This would raise concern over the ability of the select transistor to set and reset the ReRAM, for smaller cells. For shorter channel length, as the drive current scales with width (W) and  $C_{ox}$  as per the relation,  $I_{sd,sat}$  =  $V_{\rm sat}WC_{\rm ox}(V_{\rm sg}-|V_{\rm tp}|-V_{\rm sd,sat})$ , increasing TFT gate capacitance  $(C_{ox})$ , with thinner high-k gate dielectrics (to increase carrier charge density) may compensate for the current degradation due to width scaling<sup>62</sup>. However, our analysis shows that, even with aggressive scaling of high-k gate oxide as per industry standards for low-power devices<sup>62,63</sup>, we would still suffer a 2.2× drop in current as the width is reduced 5× (from gate length of 65 to 13 nm in Fig. 6b).

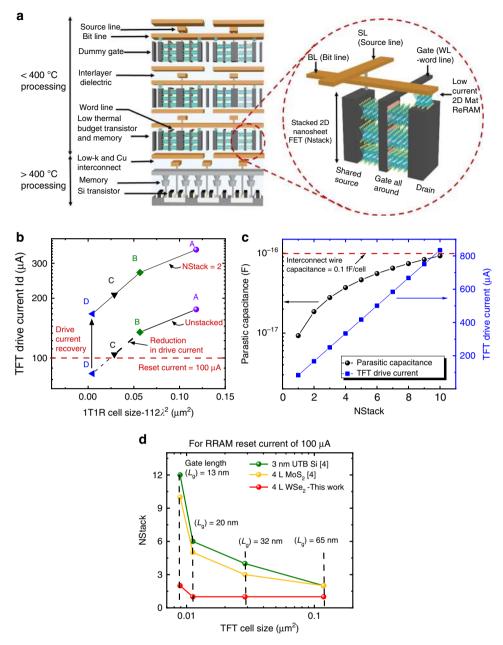

One way to address the issue of weak select transistor would be to rely on smaller ReRAM set current, but at the expense of reduced HRS/LRS ratio (Supplementary Fig. 13). Hence, to mitigate the drive current degradation, without compromising on the memory window, we propose increasing the effective width by vertical stacking of 2DMat nanosheet TFT channels. This would allow for TFT drive current recovery, without sacrificing the 1T1R cell footprint. The conceptual representation of such a 3D monolithic stacking of CMOS logic and 2D multiple-stacked WSe<sub>2</sub> TFTs is shown in Fig. 6a. While thin WO<sub>3</sub> is still utilized as hole doping layer, an additional gate dielectric with a metal gate wrapped around the nanosheet could be employed, to realize the proposed gate all around (GAA) vertically stacked WSe<sub>2</sub> TFT.

Fig. 5 Compact modeling and circuit simulations. **a**  $I_d$ – $V_g$  of SPICE TFT model vs. measured WSe<sub>2</sub> p-FET. **b** I–V of SPICE ReRAM model vs. measured for SET and RESET process. **c** Circuit representation and layout of shared SL 1T1R structure, with the 1T1R cell size indicated (BL—bit line; WL—word line; SL—shared-source line)

**Fig. 6** 3D monolithic stacking of TFT and memory. **a** Conceptual illustration of 3D monolithic stacking of CMOS logic and 2D multiple-stacked WSe<sub>2</sub> TFTs with ReRAM with thermal budget indicated for various levels (not to scale). **b** Transistor drive current (at  $V_{sg} = 2$  V) variation with respect to 1T1R cell size as per λ design rule. The specifications for the legends are, A:  $L_g = 65$  nm,  $W_{ch} = 130$  nm, EOT = 2.3 nm, k = 4.5; B:  $L_g = 45$  nm,  $W_{ch} = 90$  nm, EOT = 2.2 nm, k = 4.5; C:  $L_g = 32$  nm,  $W_{ch} = 64$  nm, EOT = 2.1 nm, k = 4.5; D:  $L_g = 13$  nm,  $W_{ch} = 26$  nm, EOT = 1.1 nm, k = 25. We observe -2.25× drop in drive current as the width is scaled 5× (130-26 nm). Stacked-channel devices showing the recovery of drain current with NStack = 2, to support the ReRAM reset current of 100 μA. **c** Change in TFT drive current and parasitic capacitance (self-capacitance due to stacking) vs. NStack (number of 2DMat nanosheet stacking layer) at  $V_{sg} = 2$  V. **d** Comparison of NStack (number of nanosheet TFT stacked) for different feature sizes among WSe<sub>2</sub>, MoS<sub>2</sub>, and UTB Si to support ReRAM reset current of 100 μA

Accordingly, as shown in Fig. 6b, an NStack (number of 2DMat nanosheet TFT channels) of 2 would more than compensate for the drive current loss due to geometric width scaling, to support ReRAM reset current of  $100\,\mu\text{A}$ .

Although stacking of channel layers would result in boosted drive current per footprint, the parasitic capacitance arising from the self-capacitance due to stacking including gate to S/D capacitance and other fringing components could lead to increased switching delays and slowing down of circuit operation. Hence, it is necessary to evaluate the trade-off between the number of stacking layers and the cell switching delay due to

transistor capacitance vs. wiring interconnect parasitic. The increase in parasitic capacitance with the number of stacking layers for  $L_{\rm g}=13$  nm is shown in Fig. 6c. With a metal wire pitch of 52 nm and assuming aspect ratio to be 2, the capacitance of the wire is 1.045 fF  $\mu$ m<sup>-1</sup> <sup>64</sup>. Accordingly, the interconnect capacitance for a 1T1R cell, considering the metal line length to be  $14\lambda$ , is 0.1 fF per cell. The simulated transistor parasitic capacitance due to stacking reveals that the interconnect capacitance induced by long word line/bit line would be the more dominant factor and that the stacking-induced self-capacitance is not expected to pose a serious concern for NStack  $\leq$ 10. The necessity for having a high

performant stacking channel layer becomes even more critical, to restrict the NStack below 10. With GAA nanosheet FETs being regarded as a potential candidate for sub-3 nm technology node, the key research areas that require improvements are fine-tuning of nanosheet width optimization with extreme ultraviolet lithography<sup>65</sup>, optimization of inner spacers<sup>66</sup>, advancement in metrology, and inspection to measure the buried channel, process control, and other fabrication challenges in gate stack integration.

Furthermore, we have compared the number of stacking layers that would be required for other 2D materials such as MoS<sub>2</sub> as well as conventional ultrathin Si from other reported works with respect to the WSe<sub>2</sub> device reported in this work. Our analysis shows that the enhanced WSe2 device requires a fewer number of channel stacking layers as compared to other materials, to support the maximum reset current of 100 µA of our low-voltage ReRAM (Fig. 6d). This is due to WSe2's higher mobility at sub-5 nm channel thickness, compared to MoS<sub>2</sub> and ultrathin Si. Specifically, only two 2D WSe<sub>2</sub> TFT channel stacks (NStack = 2) are required for cell sizes below 0.01  $\mu$ m<sup>2</sup>. These findings imply that, apart from thermal budget limitation, the large number of stacking layers required for ultrathin Si transistors and MoS2 at sub-5 nm channel thickness increases the complexity of fabrication and the stacking-induced parasitic capacitance.

While smaller effective mass  $(m^*)$  of WSe<sub>2</sub> allows for higher mobility and high performance in sub-10 nm gate length  $(L_{\rm g})$ , the enhanced S/D tunneling due to lower  $m^*$  is the down side<sup>67,68</sup>. Hence, to further reduce the footprint of each device, we recommend greater width scaling rather than  $L_{\rm g}$  scaling, without increasing the standby power. However, the width scaling will come at the expense of lower drive current per TFT. In this case, channel stacking of TFT becomes even more necessary to recover the required drive current and is an essential control knob to enable dense 1T1R cell.

# Discussion

In this work, a low-thermal-budget hybrid (solution-processedexfoliated) integration of 2D material-based 1T1R is demonstrated for the first time. We highlight the importance of different material morphology for logic and memory operation. The select transistor needs to be single crystalline with enhanced drive for scaled 1T1R cells, while it is desired for the memory device to be polycrystalline with defects that enable low-voltage switching. We show by post-contact plasma oxidation, a simple low-thermalbudget method to enhance the multilayer WSe2 transistor for this purpose; achieving significant hole mobility  $(230 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1})$ , reduction of contact resistance (to 4.3 kΩμm) and Schottky barrier (to 25 meV). This culminates in a 100× drive enhancement with respect to our control devices. In addition, we report an allprinted WSe<sub>2</sub>-based ReRAM using a low-temperature, aerosol jet process. The ReRAM exhibits sub-1 V non-volatile unipolar switching with a low switching energy of 2.9 pJ per bit. We demonstrated the TFT-ReRAM 1T1R hybrid co-integration, which guided our accurate device-circuit models and enabled us to investigate material-system memory cell co-design for scaled technologies. This led us to the proposed stacked TFT channels for the memory cell to achieve high-density 1T1R memory array for future dense monolithic 3D memory systems.

# Methods

Remote plasma oxidation. The plasma chamber source to sample distance is limited to 10 cm. The oxidation is performed at room temperature with a plasma power of 11 W and chamber pressure of 20 mTorr (100 sccm of  $O_2$  and 20 sccm of Ar) for 2 min to

form  $2.2 \text{ nm WO}_3$ . For some of the material characterization, the WO<sub>3</sub> is removed by dipping in 1 M KOH solution for 30 s.

TFT device fabrication and characterization. WSe $_2$  flakes were mechanically exfoliated on p + Si with 90 nm SiO $_2$  layer, followed by electrode patterning using electron beam lithography. The length and width of the device are characterized and validated by AFM. Ag (10 nm) contacts capped with Au (90 nm) was deposited by electron beam evaporator followed by lift off to form source and drain contacts. The device is then subjected to an annealing procedure (200 °C for 1 h in N $_2$ -H $_2$  ambient, followed by vacuum annealing at 250 °C for 0.5 h), to remove the photoresist residue and other gaseous adsorbates. After which, the plasma oxidation, as explained in the previous step is performed to form WO $_3$  above the channel and also underneath the S/D contacts. The electrical measurements were collected by Agilent parameter analyzer B1500A.

Aerosol ink printing method for WSe<sub>2</sub> ReRAM. WSe<sub>2</sub> flakes suspended in ethanol forms the ink (concentration 0.1 mg/ml, from 2D semiconductor) that is ultrasonically atomized and deposited by the Optomec AJ5X Aerosol Jet 5-axis Printer<sup>69</sup>. The bottom and top Ag electrodes are printed via the pneumatic atomizer followed by an 830 nm laser sintering process (Kapton) or a 150 °C, 30 min baking process (SiO<sub>2</sub>/Si substrate). Due to the low concentration of WSe<sub>2</sub> in the ink, the ReRAM WSe<sub>2</sub> layer has to be deposited over multiple passes. We deposited ~400 nm average thickness of WSe<sub>2</sub> (printed over 30 passes) for our ReRAM devices, with more details provided in the Supplementary Information (Supplementary Table 3 and Supplementary Fig. 8a). A final step of baking the entire sample at a temperature of 100 °C for 30 min is done to ensure conductivity of the printed Ag electrodes.

# Data availability

All data supporting the findings of this study are available from the corresponding author on request.

Received: 18 April 2019; Accepted: 11 October 2019; Published online: 15 November 2019

#### References

- Shulaker, M. M. et al. Monolithic 3D integration: a path from concept to reality. In Proc. 2015 Design, Automation & Test in Europe Conference & Exhibition 1197–1202 (EDA Consortium, 2015).

- Fox, R. et al. High performance k = 2.5 ULK backend solution using an improved TFHM architecture, extendible to the 45nm technology node. In Electron Devices Meeting, 2005. IEDM Technical Digest. IEEE International 81–84 (IEEE 2005)

- Batude, P. et al. 3D sequential integration opportunities and technology optimization. In *IEEE International Interconnect Technology Conference* 373–376 (IEEE, 2014).

- Iannaccone, G., Bonaccorso, F., Colombo, L. & Fiori, G. Quantum engineering of transistors based on 2D materials heterostructures. *Nat. Nanotechnol.* 13, 183 (2018).

- Fu, Y., Qin, Y., Wang, T., Chen, S. & Liu, J. Ultrafast transfer of metalenhanced carbon nanotubes at low temperature for large-scale electronics assembly. Adv. Mater. 22, 5039–5042 (2010).

- Castellanos-Gomez, A. et al. Deterministic transfer of two-dimensional materials by all-dry viscoelastic stamping. 2D Mater. 1, 11002 (2014).

- Wang, C.-H. et al. 3D monolithic stacked 1T1R cells using monolayer MoS<sub>2</sub> FET and hBN RRAM fabricated at low (150 °C) temperature. In 2018 IEEE International Electron Devices Meeting (IEDM) 22–25 (IEEE, 2018).

- 8. Batude, P. et al. 3D sequential integration: application-driven technological achievements and guidelines. In 2017 IEEE International Electron Devices Meeting (IEDM) 1–3 (IEEE, 2017).

- Akinwande, D., Petrone, N. & Hone, J. Two-dimensional flexible nanoelectronics. *Nat. Commun.* 5, 5678 (2014).

- Fang, H. et al. High-performance single layered WSe<sub>2</sub> p-FETs with chemically doped contacts. Nano Lett. 12, 3788–3792 (2012).

- Resta, G. V. et al. Polarity control in WSe<sub>2</sub> double-gate transistors. Sci. Rep. 6, 29448 (2016).

- Das, S., Dubey, M. & Roelofs, A. High gain, low noise, fully complementary logic inverter based on bi-layer WSe<sub>2</sub> field effect transistors. *Appl. Phys. Lett.* 105, 83511 (2014).

- Pradhan, N. R. et al. Hall and field-effect mobilities in few layered p-WSe<sub>2</sub> field-effect transistors. Sci. Rep. 5, 8979 (2015).

- Liu, W. et al. Role of metal contacts in designing high-performance monolayer n-type WSe<sub>2</sub> field effect transistors. *Nano Lett.* 13, 1983–1990 (2013).

- Shokouh, S. H. H. et al. High-performance, air-stable, top-gate, p-channel WSe<sub>2</sub> field-effect transistor with fluoropolymer buffer layer. *Adv. Funct. Mater.* 25, 7208–7214 (2015).

- Chuang, H.-J. et al. Low-resistance 2D/2D ohmic contacts: a universal approach to high-performance WSe<sub>2</sub>, MoS<sub>2</sub>, and MoSe<sub>2</sub> transistors. *Nano Lett.* 16, 1896–1902 (2016).

- Chuang, H.-J. et al. High mobility WSe<sub>2</sub> p- and n-type field-effect transistors contacted by highly doped graphene for low-resistance contacts. *Nano Lett.* 14, 3594–3601 (2014).

- Kappera, R. et al. Phase-engineered low-resistance contacts for ultrathin MoS<sub>2</sub> transistors. Nat. Mater. 13, 1128 (2014).

- Castellanos-Gomez, A. et al. Laser-thinning of MoS<sub>2</sub>: on demand generation of a single-layer semiconductor. *Nano Lett.* 12, 3187–3192 (2012).

- Yamamoto, M., Nakaharai, S., Ueno, K. & Tsukagoshi, K. Self-limiting oxides on WSe<sub>2</sub> as controlled surface acceptors and low-resistance hole contacts. *Nano Lett.* 16, 2720–2727 (2016).

- Pudasaini, P. R. et al. High-performance multilayer WSe<sub>2</sub> field-effect transistors with carrier type control. Nano Res. 11, 722–730 (2018).

- Zhang, R., Drysdale, D., Koutsos, V. & Cheung, R. Controlled layer thinning and p-type doping of WSe<sub>2</sub> by vapor XeF<sub>2</sub>. Adv. Funct. Mater. 27, 1702455 (2017)

- Li, Z. et al. Layer control of WSe<sub>2</sub> via selective surface layer oxidation. ACS Nano 10, 6836–6842 (2016).

- Liu, Y. et al. Thermal oxidation of WSe<sub>2</sub> nanosheets adhered on SiO<sub>2</sub>/Si substrates. Nano Lett. 15, 4979–4984 (2015).

- Liu, B. et al. High-performance WSe<sub>2</sub> field-effect transistors via controlled formation of in-plane heterojunctions. ACS Nano 10, 5153-5160 (2016).

- Roy, T. et al. Field-effect transistors built from all two-dimensional material components. ACS Nano 8, 6259–6264 (2014).

- Meyer, J. et al. Transition metal oxides for organic electronics: energetics, device physics and applications. Adv. Mater. 24, 5408–5427 (2012).

- Yamamoto, M. et al. Self-limiting layer-by-layer oxidation of atomically thin WSe<sub>2</sub>. Nano Lett. 15, 2067–2073 (2015).

- Lee, S., Tang, A., Aloni, S. & Philip Wong, H.-S. Statistical study on the Schottky barrier reduction of tunneling contacts to CVD synthesized MoS<sub>2</sub>. Nano Lett. 16, 276–281 (2015).

- Pan, C. et al. Coexistence of grain-boundaries-assisted bipolar and threshold resistive switching in multilayer hexagonal boron nitride. Adv. Funct. Mater. 27, 1604811 (2017).

- Qian, K. et al. Hexagonal boron nitride thin film for flexible resistive memory applications. Adv. Funct. Mater. 26, 2176–2184 (2016).

- Hao, C. et al. Liquid-exfoliated black phosphorous nanosheet thin films for flexible resistive random access memory applications. Adv. Funct. Mater. 26, 2016–2024 (2016).

- Son, D. et al. Colloidal synthesis of uniform-sized molybdenum disulfide nanosheets for wafer-scale flexible nonvolatile memory. Adv. Mater. 28, 9326–9332 (2016).

- Tan, C., Liu, Z., Huang, W. & Zhang, H. Non-volatile resistive memory devices based on solution-processed ultrathin two-dimensional nanomaterials. *Chem. Soc. Rev.* 44, 2615–2628 (2015).

- Bessonov, A. A. et al. Layered memristive and memcapacitive switches for printable electronics. *Nat. Mater.* 14, 199 (2015).

- Cheng, P., Sun, K. & Hu, Y. H. Memristive behavior and ideal memristor of 1T phase MoS<sub>2</sub> nanosheets. *Nano Lett.* 16, 572–576 (2015).

- Sangwan, V. K. et al. Gate-tunable memristive phenomena mediated by grain boundaries in single-layer MoS<sub>2</sub>. Nat. Nanotechnol. 10, 403 (2015).

- Zhang, F. et al. Electric-field induced structural transition in vertical MoTe<sub>2</sub> and Mo<sub>1-x</sub>W<sub>x</sub>Te<sub>2</sub>-based resistive memories. *Nat. Mater.* 18, 55 (2019).

- Tao, H. et al. Scalable exfoliation and dispersion of two-dimensional materials

—an update. Phys. Chem. Chem. Phys. 19, 921–960 (2017).

- Tsai, T.-L., Chang, H.-Y., Jiang, F.-S. & Tseng, T.-Y. Impact of post-oxide deposition annealing on resistive switching in HfO<sub>2</sub>-based oxide RRAM and conductive-bridge RAM devices. *IEEE Electron Device Lett.* 36, 1146–1148 (2015).

- Wang, M. et al. Robust memristors based on layered two-dimensional materials. Nat. Electron. 1, 130 (2018).

- 42. Strukov, D. B., Alibart, F. & Williams, R. S. Thermophoresis/diffusion as a plausible mechanism for unipolar resistive switching in metal–oxide–metal memristors. *Appl. Phys. A* **107**, 509–518 (2012).

- 43. Ge, R. et al. Atomristor: nonvolatile resistance switching in atomic sheets of transition metal dichalcogenides. *Nano Lett.* **18**, 434–441 (2017).

- Luo, Q. et al. Super non-linear RRAM with ultra-low power for 3D vertical nano-crossbar arrays. Nanoscale 8, 15629–15636 (2016).

- Raghavan, N. Performance and reliability trade-offs for high-κ RRAM. Microelectron. Reliab. 54, 2253–2257 (2014).

- Cheng, L. et al. Reprogrammable logic in memristive crossbar for in-memory computing. J. Phys. D 50, 505102 (2017).

- Breuer, T. et al. Realization of minimum and maximum gate function in Ta<sub>2</sub>O<sub>5</sub>-based memristive devices. Sci. Rep. 6, 23967 (2016).

- Huang, P. et al. Reconfigurable nonvolatile logic operations in resistance switching crossbar array for large-scale circuits. Adv. Mater. 28, 9758–9764 (2016).

- Yan, X. et al. Highly improved performance in Zr<sub>0.5</sub>Hf<sub>0.5</sub>O<sub>2</sub> films inserted with graphene oxide quantum dots layer for resistive switching non-volatile memory. J. Mater. Chem. C 5, 11046–11052 (2017).

- Lee, S., Sohn, J., Jiang, Z., Chen, H.-Y. & Wong, H.-S. P. Metal oxideresistive memory using graphene-edge electrodes. *Nat. Commun.* 6, 8407 (2015).

- 51. Govoreanu, B. et al.  $10 \times 10 \text{ nm}^2 \text{ Hf/HfO}_x$  crossbar resistive RAM with excellent performance, reliability and low-energy operation. In *Electron Devices Meeting (IEDM), 2011 IEEE International* 31–36 (IEEE, 2011).

- Zhao, X. et al. Confining cation injection to enhance CBRAM performance by nanopore graphene layer. Small 13, 1603948 (2017).

- Shih, C.-C. et al. Ultra-low switching voltage induced by inserting SiO<sub>2</sub> layer in indium-tin-oxide-based resistance random access memory. *IEEE Electron Dev. Lett.* 37, 1276–1279 (2016).

- 54. Song, Y. L. et al. Low reset current in stacked AlO<sub>x</sub>/WO<sub>x</sub> resistive switching memory. *IEEE Electron Dev. Lett.* **32**, 1439–1441 (2011).

- Ielmini, D. & Wong, H.-S. P. In-memory computing with resistive switching devices. Nat. Electron. 1, 333 (2018).

- Zhou, J., Kim, K.-H. & Lu, W. Crossbar RRAM arrays: selector device requirements during read operation. *IEEE Trans. Electron Dev.* 61, 1369–1376 (2014).

- 57. Wang, X. P. et al. Highly compact 1T-1R architecture (4F<sup>2</sup> footprint) involving fully CMOS compatible vertical GAA nano-pillar transistors and oxide-based RRAM cells exhibiting excellent NVM properties and ultra-low power operation. In *Electron Devices Meeting (IEDM), 2012 IEEE International* 20–26 (IEEE, 2012).

- Chen, P.-Y. & Yu, S. Compact modeling of RRAM devices and its applications in 1T1R and 1S1R array design. *IEEE Trans. Electron Dev.* 62, 4022–4028 (2015).

- Chauhan, Y. S. et al. BSIM compact MOSFET models for SPICE simulation. In Mixed Design of Integrated Circuits and Systems (MIXDES), 2013 Proceedings of the 20th International Conference 23–28 (IEEE, 2013).

- Garcia-Redondo, F., Gowers, R. P., Crespo-Yepes, A., López-Vallejo, M. & Jiang, L. SPICE compact modeling of bipolar/unipolar memristor switching governed by electrical thresholds. *IEEE Trans. Circuits Syst. I* 63, 1255–1264 (2016).

- Yeh, C.-W. S. & Wong, S. S. Compact one-transistor-N-RRAM array architecture for advanced CMOS technology. *IEEE J. Solid-State Circuits* 50, 1299–1309 (2015).

- Robertson, J. High dielectric constant gate oxides for metal oxide Si transistors. Rep. Prog. Phys. 69, 327 (2005).

- Lee, B. H., Oh, J., Tseng, H. H., Jammy, R. & Huff, H. Gate stack technology for nanoscale devices. *Mater. Today* 9, 32–40 (2006).

- Li, H. et al. Device and circuit interaction analysis of stochastic behaviors in cross-point RRAM aArrays. *IEEE Trans. Electron Dev.* 64, 4928–4936 (2017).

- Barraud, S. et al. Performance and design considerations for gate-all-around stacked-nanowires FETs. In 2017 IEEE International Electron Devices Meeting (IEDM) 22–29 (IEEE, 2017).

- Huang, Y.-C., Chiang, M.-H. & Wang, S.-J. Speed optimization of vertically stacked gate-all-around MOSFETs with inner spacers for low power and ultralow power applications. In 20th International Symposium on Quality Electronic Design (ISQED) 231–234 (IEEE, 2019).

- Majumdar, K., Hobbs, C. & Kirsch, P. D. Benchmarking transition metal dichalcogenide MOSFET in the ultimate physical scaling limit. *IEEE Electron Dev. Lett.* 35, 402–404 (2014).

- Cao, W., Kang, J., Sarkar, D., Liu, W. & Banerjee, K. 2D semiconductor FETs

—projections and design for sub-10 nm VLSI. *IEEE Trans. Electron Dev.* 62, 3459–3469 (2015).

- Secor, E. Principles of aerosol jet printing. Flex. Print. Electron. 3, 035002 (2018).

### **Acknowledgements**

This work has been supported in part by Singapore's National Research Foundation grant NRF-RSS2015-003, Hybrid Integrated Flexible Electronic Systems (HiFES) Prog. (hifes.nus.edu.sg), E6Nanofab, and the Center for Advanced 2D Materials at the National University of Singapore. Many thanks to Ms. Zhang Yang for TEM sample preparation, and to Dr. Gong Xiao and his team for assisting us on the low-temperature measurement.

#### **Author contributions**

A.V.-Y.T., Y.L., and M.S. conceived the project and designed the experiments. M.S. and Y.L. performed the device fabrication, electrical measurements, and analysis. H.V. performed the modeling and circuit simulations. Y.Z. carried out the TEM experiments. B.T. prepared the ink for solution processing. X.W performed XRD. E.Z., J.F.L., U.C., and J.X.N. contributed towards discussion and data interpretation. M.S, Y.L, and A.V.-Y.T. co-wrote the paper, and all authors are involved in the discussions and preparation of the manuscript.

#### **Competing interests**

The authors declare no competing interests.

#### **Additional information**

**Supplementary information** is available for this paper at https://doi.org/10.1038/s41467-019-13176-4.

Correspondence and requests for materials should be addressed to Y.L. or A.-Y.T.

**Peer review information** *Nature Communications* thanks Giovanni Resta and the anonymous reviewer/s for their contribution to the peer review of this work.

Reprints and permission information is available at http://www.nature.com/reprints

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation,

distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <a href="http://creativecommons.org/licenses/by/4.0/">http://creativecommons.org/licenses/by/4.0/</a>.

© The Author(s) 2019