# An 11-bit, 12.5-MHz, Low-Power, Low-Voltage, Continuous-Time Sigma-Delta Modulator in 0.13 µm CMOS Technology

vorgelegt von

Diplom-Ingenieur

Eugenio Di Gioia

aus Agrigent (Italien)

Von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften – Dr.-Ing. –

genehmigte Dissertation

#### Promotionsausschuss:

Vorsitzender: Prof. Dr.-Ing. Roland Thewes Gutachter: Prof. Dr.-Ing. Heinrich Klar

Gutachterin: Prof. Dr. rer. nat. Doris Schmitt-Landsiedel

Tag der wissenschaftlichen Aussprache: 20.12.2010

Berlin 2011

### **Abstract**

The trend of the last years in the industry of integrated circuits has shifted more and more from the analog toward the digital world. Thanks to the CMOS technology an impressive miniaturization of the electronic active elements has been made possible, which allows for low cost and mass production of complex circuits on a single chip. The natural candidates for very large-scale integration (VLSI) technologies are digital circuits since these can be relatively easily scaled down with large improvements in the operating speed. On the other hand virtually all natural signals are of analog nature, requiring dedicated circuits converting these signals in the digital form, in order to process them with the digital circuitry. Such circuits are named analog-to-digital converters (ADC) and find wide diffusion in all devices dealing with natural signals like images, sound, temperature, radio signals, etc. In order to reduce the equipment cost the integration of the ADC on the same chip containing the digital circuits is highly desirable. Actually, modern highly miniaturized CMOS technologies are not very suitable for analog circuits, as they feature rather poor analog electrical properties. To cope with this, particular ADC topologies are required which are robust enough to be implemented in CMOS technology with a feature size in the order of 100 nanometers. One of the most promising architecture for CMOS processes is the continuous-time sigma-delta ( $\Sigma\Delta$ ) modulator. This achieves very large accuracy and performance by optimally using the main advantage of the modern CMOS technology: high speed. In this work a study of low-power, high-speed continuous time  $\Sigma\Delta$  modulators is presented. A possible application of this class of modulators is represented by high-speed portable communication devices of the next generation. The author focuses on design strategies at architectural and transistor level in order to keep to power consumption to a very low amount without sacrificing the modulator resolution.

The modulator proposed in this work is based on a  $0.13~\mu m$  CMOS process and achieves an effective resolution of 11 bits at a signal bandwidth of 12.5 MHz dissipating 11.4 mW of power. It is shown how to compensate for the unavoidable excess loop delay which degrades the performance achievable, applying this technique to a resonator-based continuous-time loop filter. A model is illustrated enabling the design of RC-integrators based on two-stage Miller compensated operational amplifiers. Furthermore a resistor-based feed-forward loop filter topology is implemented to reduce the power consumption of the filter. Another low-power benefit is achieved by merging two DAC into a single DAC without altering the functionality of the modulator.

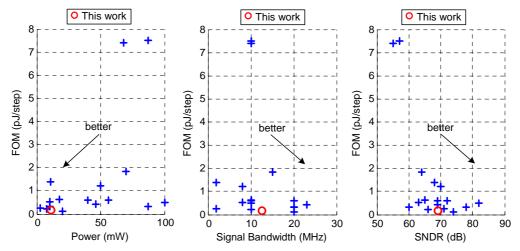

The proposed modulator obtains a very good figure of merit according to post-layout simulation results when compared to the literature state-of-the-art.

# Zusammenfassung

Der Trend der letzten Jahre in der Industrie der integrierten Schaltungen hat sich immer mehr von der analogen zur digitalen Welt verschoben. Dank der CMOS Technologie ist eine beeindruckende Miniaturisierung der aktiven elektronischen Bauelemente möglich gewesen, welche eine Reduzierung der Herstellungskosten sowie die Massenproduktion von komplexen Schaltungen auf einem einzigen Chip ermöglicht. Die natürlichen Kandidaten für Technologien mit sehr hohem Integrationsgrad (VLSI) sind Digital-Schaltungen, da diese einfach verkleinert werden können mit erheblicher Erhöhung relativ Betriebsgeschwindigkeit. Andererseits sind geradezu alle natürlichen Signale analog und benötigen dedizierte Schaltungen für deren Umwandlung in die digitale Form, um diese Signale mit Digital-Schaltungen weiter verarbeiten zu können. Diese Schaltungen werden Analog-Digital-Umwandler genannt (ADC) und finden in praktisch allen Geräten Anwendung, welche sich mit natürlichen Signalen wie Bildern, Ton, Temperatur, Radiofrequenz-Signalen, etc. befassen. Um die Kosten der Geräte zu minimieren, ist die Integration der ADC auf demselben Chip, welcher die Digital-Schaltungen enthält, höchst wünschenswert. Moderne hochminiaturisierte CMOS-Technologien sind aber nicht sehr geeignet für Analogschaltungen, da sie bescheidene analoge elektrische Eigenschaften aufweisen. Um dies zu meistern, werden besondere ADC-Topologien benötigt, welche genügend robust sind, um in einer CMOS-Technologie mit einer Strukturgröße von ca. 100 Nanometern implementiert zu werden. Eine vielversprechende Architektur für CMOS-Prozesse ist der zeitkontinuierliche Sigma-Delta-Modulator ( $\Sigma\Delta$ ). Diese Architektur erzielt große Genauigkeit und Performance, indem der Hauptvorteil moderner CMOS-Technologien ausgenutzt wird: die hohe Geschwindigkeit. In dieser Arbeit wird eine Studie über leistungsarme zeitkontinuierliche  $\Sigma\Delta$ -Modulatoren mit hoher Geschwindigkeit präsentiert. Diese Klasse von Modulatoren findet eine mögliche Anwendung in tragbaren breitbandfähigen Mobilfunkgeräten der nächsten Generation. Der Autor konzentriert sich auf die Design-Strategien auf Architektur- und Transistorebene mit dem Ziel, die Verlustleistung des Modulators ohne Beeinträchtigung dessen Auflösung zu reduzieren.

Der in dieser Arbeit präsentierte Modulator basiert auf einem 0.13 µm CMOS-Prozess und erzielt eine effektive Auflösung von 11 Bits bei einer Signal-Bandbreite von 12.5 MHz und einer Verlustleistung von 11.4 mW. Es wird gezeigt, wie das unvermeidbare Excess-Loop-Delay, welches die erzielbare Performance verschlechtert, kompensiert werden kann. Diese Technik wird auf ein resonator-basiertes, zeitkontinuierliches Schleifenfilter angewendet. Ein Modell für das Design von RC-Integratoren, welche auf zweistufigen Miller-kompensierten Operationsverstärkern basieren, wird erläutert. Ferner wird eine widerstandsbasierte Feed-Forward Filterarchitektur implementiert, um die Verlustleistung des Schleifenfilters zu reduzieren. Ein zusätzlicher Vorteil bezüglich der Verlustleistung ist erzielt worden, indem zwei verschiedene DAC-Stufen, welche Bestandteile des Modulators sind, in einem einzelnen DAC zusammengefasst werden ohne die Funktionalität des Modulators zu verändern.

Der vorgeschlagene Modulator erzielt gemäß Post-Layout-Simulationen im Vergleich mit dem heutigen Stand der Technik einen sehr guten Gütefaktor.

# **Contents**

| Ab | Abstract                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |  |  |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

| Zu | ısammenfassung                                                                                                                                                                                                                                                                                                                                                                | 4                                                                          |  |  |  |  |

| Ac | cknowledgments                                                                                                                                                                                                                                                                                                                                                                |                                                                            |  |  |  |  |

| 1. | Introduction                                                                                                                                                                                                                                                                                                                                                                  | 9<br>9<br>10                                                               |  |  |  |  |

| 2. | 2.1. Analog-to-digital conversion 2.2. Performance metrics 2.2.1. Static metrics 2.2.2. Dynamic metrics 2.3. Linearized model 2.4. Oversampling 2.5. Sigma-Delta ADC 2.5.1. Linear model 2.5.2. 1st order modulator 2.5.3. 2nd order modulator 2.5.4. L-th order modulator 2.5.5. Stability analysis                                                                          | 11<br>11<br>13<br>13<br>15<br>16<br>18<br>19<br>20<br>22<br>24<br>25<br>27 |  |  |  |  |

|    | 2.5.6. Zero spreading  2.6. Quasi-linear model  2.7. Single loop / Cascaded  2.8. Discrete time / continuous time loop filter  2.8.1. Discrete time filter  2.8.2. Continuous time filter  2.8.3. DT-CT equivalence  2.8.4. Circuit noise  2.8.5. Jitter error  2.8.6. Excess loop delay  2.8.7. Summary of pros and cons of CT and DT modulators  2.9. Single-Bit / Multibit | 30<br>31<br>32<br>34<br>38<br>42<br>45<br>48<br>51<br>52<br>53             |  |  |  |  |

| <b>3.</b> | Low-power high-speed CT $\Sigma\Delta$ modulator: system level design       |                       |  |  |  |  |                              |                                 |

|-----------|-----------------------------------------------------------------------------|-----------------------|--|--|--|--|------------------------------|---------------------------------|

|           | 3.1. Specifications                                                         |                       |  |  |  |  |                              |                                 |

|           | 3.2. Architecture choice and loop filter synthesis                          |                       |  |  |  |  |                              |                                 |

|           | <ul><li>3.3. High level simulations of the prototype DT modulator</li></ul> |                       |  |  |  |  |                              |                                 |

|           |                                                                             |                       |  |  |  |  |                              |                                 |

|           |                                                                             |                       |  |  |  |  |                              | 3.5.1. CIFF and CIFB topologies |

|           |                                                                             |                       |  |  |  |  |                              |                                 |

|           |                                                                             |                       |  |  |  |  |                              |                                 |

|           | 3.5.3. Resonator for zero spreading and architectural modification          |                       |  |  |  |  |                              |                                 |

|           | 3.6. Excess Loop Delay compensation                                         |                       |  |  |  |  |                              |                                 |

|           | 3.7. Coefficient scaling                                                    |                       |  |  |  |  |                              |                                 |

|           | 3.8. Circuit implementation                                                 |                       |  |  |  |  |                              |                                 |

|           |                                                                             |                       |  |  |  |  | 3.10. High-level simulations | 76                              |

|           |                                                                             |                       |  |  |  |  | 3.10.1. Finite opamp gain    |                                 |

|           |                                                                             | 3.10.2. DAC jitter    |  |  |  |  |                              |                                 |

|           |                                                                             |                       |  |  |  |  |                              |                                 |

| 4.        | 4. Low-power high-speed CT $\Sigma\Delta$ modulator: integrated circu       | uit design 81         |  |  |  |  |                              |                                 |

|           | 4.1. Used technology and supply voltage                                     | _                     |  |  |  |  |                              |                                 |

|           | 4.2. Loop filter operational amplifiers                                     |                       |  |  |  |  |                              |                                 |

|           | 4.2.1. Standard design approach                                             |                       |  |  |  |  |                              |                                 |

|           | 4.2.2. New design approach                                                  |                       |  |  |  |  |                              |                                 |

|           | 4.2.3. Dimensioning of the 1 <sup>st</sup> integrator                       |                       |  |  |  |  |                              |                                 |

|           | 4.2.4. Dimensioning of the 2 <sup>nd</sup> integrator                       | 93                    |  |  |  |  |                              |                                 |

|           | 4.2.5. Dimensioning of the 3 <sup>rd</sup> integrator                       | 93                    |  |  |  |  |                              |                                 |

|           | 4.2.5. Difficultioning of the 5 integrator                                  |                       |  |  |  |  |                              |                                 |

|           | 4.3. Loop filter passive components                                         |                       |  |  |  |  |                              |                                 |

|           | 4.3.1. Capacitors                                                           |                       |  |  |  |  |                              |                                 |

|           | 4.3.2. Resistors                                                            |                       |  |  |  |  |                              |                                 |

|           |                                                                             |                       |  |  |  |  |                              |                                 |

|           | 4.5. Main DAC                                                               |                       |  |  |  |  |                              |                                 |

|           | 4.5.1. Mismatch                                                             |                       |  |  |  |  |                              |                                 |

|           | 4.5.2. Signal-depending DAC non-linearity                                   |                       |  |  |  |  |                              |                                 |

|           | 4.5.3. Dynamic behavior of the DAC                                          |                       |  |  |  |  |                              |                                 |

|           | 4.5.4. Bias circuit                                                         | 104                   |  |  |  |  |                              |                                 |

|           | 4.5.5. Layout                                                               |                       |  |  |  |  |                              |                                 |

|           | 4.5.6. DAC circuit noise                                                    | 105                   |  |  |  |  |                              |                                 |

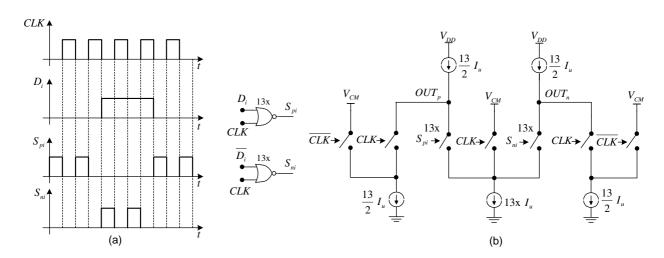

|           | 4.6. Secondary RZ DAC                                                       |                       |  |  |  |  |                              |                                 |

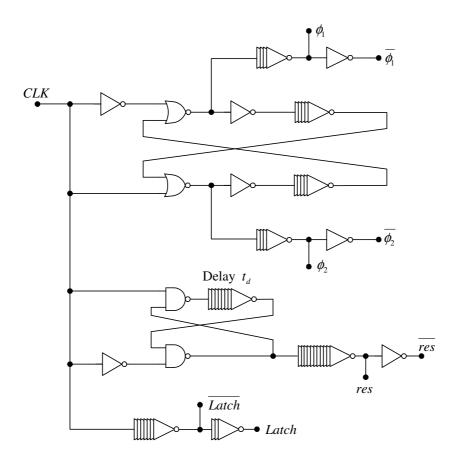

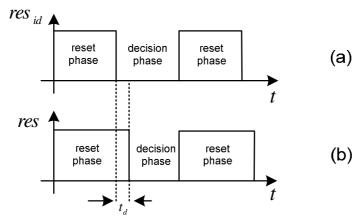

|           | 4.7. Clock generation                                                       | 4.7. Clock generation |  |  |  |  |                              |                                 |

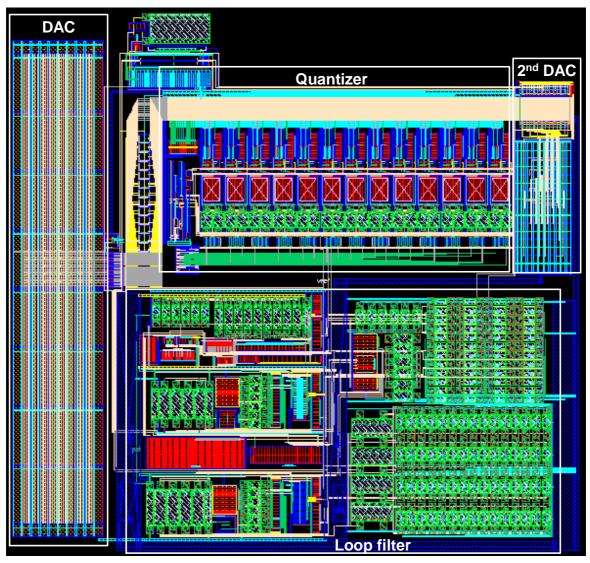

|           | 4.8. Modulator layout                                                       |                       |  |  |  |  |                              |                                 |

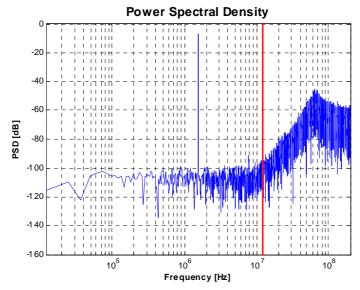

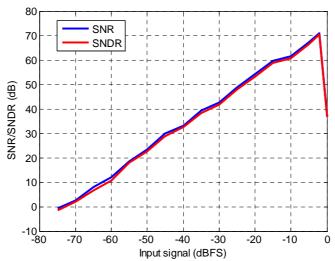

|           | 4.9. Post-layout simulation results                                         |                       |  |  |  |  |                              |                                 |

|           | 4.10. Corner simulations                                                    |                       |  |  |  |  |                              |                                 |

|           | 4.11. Estimated total circuit noise                                         |                       |  |  |  |  |                              |                                 |

|           | 7.11. Estimated total circuit hoise                                         |                       |  |  |  |  |                              |                                 |

| <b>=</b>  | 5 Conclusions and future work                                               |                       |  |  |  |  |                              |                                 |

| 5.        |                                                                             |                       |  |  |  |  |                              |                                 |

|           | 5.1. FOM and comparison with state of the art                               |                       |  |  |  |  |                              |                                 |

|           | 5.2. Future work: DEM or DAC analog calibration                             |                       |  |  |  |  |                              |                                 |

|           | 5.3. Publications                                                           |                       |  |  |  |  |                              |                                 |

| Appendix A: Calculation of the DT equivalent transfer function with the aid of the IIT | 115 |

|----------------------------------------------------------------------------------------|-----|

| A.1 Main DAC                                                                           |     |

| A.2 Auxiliary DAC                                                                      | 118 |

| A.3 DT equivalent                                                                      | 119 |

| Appendix B: Calculation of the INL of the DAC                                          | 120 |

| Bibliography                                                                           | 123 |

### Acknowledgments

I wish to express my deep gratitude to my research advisor, Prof. Heinrich Klar, for helping me in the realization of this research work, for giving me many advices and suggestions in the field of analog electronics and guiding me into all important aspects of circuit design. I thank him for his kindness and helpfulness under the professional and human aspect.

I am grateful to Prof. Doris Schmitt-Landsiedel for serving on my qualifying exam committee.

A special thank goes to my colleagues Stephan Leuschner and Norman Wolf who supported me throughout all these years, helped me into manage many design issues and offered me a precious source of inspiration for my research in the many discussions we had.

I would like also to thank Werner Eschenberg, Rene Hartmann and Uwe Voss from our Department of Microelectronics for their willingness to solve all technical problems efficiently and fast and for their kindness.

I express sincere gratitude to my parents Alessandro e Mariangela and to my sister Daniela for their support and love all over my life.

Sincere thanks to my friends, who allowed me to have relaxing moments and encouraged me all these years.

Finally I deeply thank my companion in life, Henrike, for encouraging me in the difficult moments, for her love and her patience and for always giving me an optimistic view of life.

# **Chapter 1**

### Introduction

#### 1.1. Motivation

The trend of the last decades clearly shows that the implementation of devices for signal processing in every possible field, such as telecommunications, video, audio, medical equipment is moving toward the digital world. This is because of the large number of advantages, which digital devices offer: high integration, simple size scaling, robustness toward noise and other sources of disturbance, programmability. Hence the famous motto "the world goes digital". Nevertheless the world is analog in all its aspects, therefore devices are needed, which allow an interface between the analog world and the digital devices. This interface consists in the analog-to-digital converters and their counterpart, the digital-toanalog converters. The domination of digital circuits in the semiconductor market has led to a technology optimization primarily toward this sort of circuits. Because of its good suitability for digital circuits the CMOS technology has nowadays the largest market share. This technology provides considerable advantages toward other technologies, such as MOS selfalignment, which enables the fabrication of extremely small components and low static power dissipation, a precondition for the implementation of low-power devices. The most important aspect taken into consideration from the industry so far is the miniaturization of the transistors, maximizing the number of components on the same area hence minimizing the cost of the equipment. On the other size the continuous scaling of the dimensions of the transistors has led to a worsening of the analog electrical properties of these fundamental elements. Going into detail, we can observe that the progressive reduction of the transistor channel length has led to a reduction of the maximum available gain, the so called transistor self-gain  $g_m/g_{ds}$ , i.e. the ratio of the transconductance to the output conductance. Furthermore, the continuous reduction of the oxide thickness has put stringent limits on the maximum available supply voltage. This reduces in turn the maximum available signal amplitude, hence limiting, considering the circuit thermal noise constant, the maximum achievable SNR. To counteract this trend, the thermal noise must be reduced, which is obtained increasing the power consumption.

Another issue of modern sub- $\mu$ m CMOS technologies is represented by the difficulty in reducing the threshold voltage  $V_T$  at the same rate as the supply voltage [Ito08]. This is desirable to enable low-voltage analog circuits to generate large signal swing. A bound in the scaling of the threshold voltage is represented by the leakage currents of transistors which are supposed to be in the off-state, which rise exponentially when reducing  $V_T$ , hence increasing

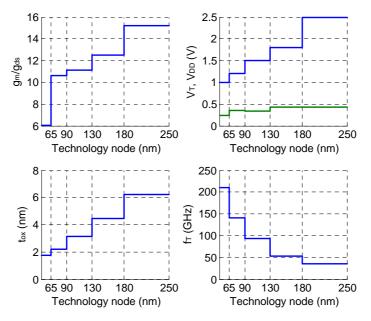

the power consumption. The trend of the most important analog parameters for different technology nodes is depicted in Fig. 1.1 [Pek04].

Fig. 1.1. Trend of the most important analog parameters for different technology nodes [Pek04]

#### 1.2. Objective and outline of this work

The objective of this research work is to show the feasibility of a low-voltage, low-power, high-speed Sigma-Delta analog-to-digital converter (ADC) for portable telecommunication devices. The proposed ADC could be employed in devices based on the mobile wireless standard WiMAX [Wim06] or for video or medical imaging. The priority is given to a low-cost device, which should be achieved using a standard CMOS technology. This writing focuses on solutions at both architectural and transistor level to reduce the power consumption without sacrificing speed and performance.

The work is articulated as in the following: chapter 2 introduces the basics of the A/D conversion and analyzes the Sigma-Delta family in particular; chapter 3 concentrates on system level considerations and on the high-level architecture of the proposed  $\Sigma\Delta$  modulator; chapter 4 describes into detail the blocks of the proposed modulator up to the layout and shows the simulation results; finally chapter 5 summarizes the achieved results comparing them with the state of the art.

# **Chapter 2**

# **Basics of analog-to-digital conversion**

#### 2.1. Analog-to-digital conversion

The analog to digital conversion is the process of converting an analog signal into a time-discrete, amplitude-discrete digital signal. The operation is performed in two steps: the sampling and the quantization. The device realizing these two operations is called analog-to-digital converter (ADC).

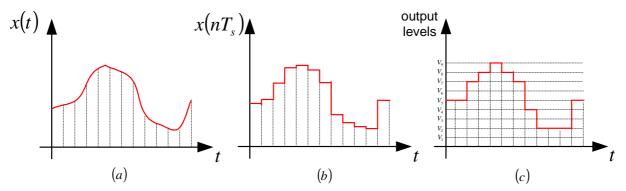

Consider a continuous-time signal x(t) as shown in Fig. 2.1a. This signal is sampled at constant time instants which are multiple of  $T_s$ . A time discrete signal is obtained  $x[k]=x(nT_s)$ . The process of ideal sampling can be mathematically seen as the product of the continuous-time signal x(t) with a Dirac comb signal x(t) with period x(t) with period x(t) with period x(t) with a Dirac comb signal x(t) with period x(t) with pe

$$x(nT_s) = x(t) \cdot p(t) = \sum_{n=-\infty}^{\infty} x(nT_s) \cdot \delta(t - nT_s)$$

(2.1)

Transforming this signal in the frequency domain by means of the Fourier transform we find:

$$X_{d}(\omega) = \frac{1}{2\pi} X(\omega) * P(\omega) = \frac{1}{T_{s}} \sum_{k=-\infty}^{\infty} X(\omega) \cdot \delta \left( \omega - \frac{2\pi k}{T_{s}} \right) = \frac{1}{T_{s}} \sum_{k=-\infty}^{\infty} X \left( \omega - \frac{2\pi k}{T_{s}} \right)$$

(2.2)

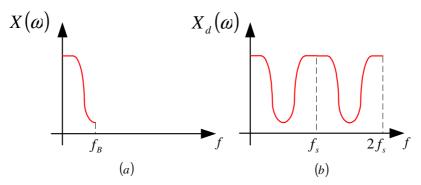

Equation (2.2) clearly shows that the spectrum  $X_d(\omega)$  of the time-discrete signal is periodic. An important consequence of this is that, as stated by the Nyquist-Shannon sampling theorem, the minimum sampling frequency  $f_s$  allowing a perfect reconstruction of a low-pass signal with a limited bandwidth  $f_B$  is  $f_s=2f_B$ . This limitation avoids the unwanted effect of aliasing, namely the superposition of "replicas" of the signal in the frequency domain which would cause signal deterioration and information loss. In order to satisfy this condition the analog signal must be bandlimited by means of a so called anti-aliasing filter.

Fig. 2.1a-b and Fig.2.2a-b show the process of sampling both in the time and in the frequency domain.

Fig. 2.1. Sampling and quantization in the time domain

Fig. 2.2. Sampling in the frequency domain

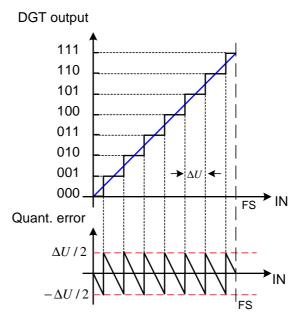

The quantization process consists in mapping the infinite possible amplitude values of the input signal into a finite set of discrete values (Fig. 2.2c). This is done by comparing the signal with a finite set of equidistant threshold values and associating the signal to the nearest threshold. This process is unavoidably associated with information loss, which is depending on the deterministic error introduced by the quantization. Assuming an N-bit quantization, hence  $2^N$  quantization levels and a signal with limited amplitude, such that the quantizer is not overloaded, the introduced quantization error  $\varepsilon_Q$  will be limited to:

$$-\frac{\Delta U}{2} \le \varepsilon_{\varrho} \le \frac{\Delta U}{2} \tag{2.3}$$

where  $\Delta U$  is the width of the quantization interval, that is the distance between two consecutives thresholds. This is equal to:

$$\Delta U = \frac{V_{FS}}{2^{N-1}} \tag{2.4}$$

$V_{FS}$  is the full-scale input signal and N again is the resolution of the quantizer in bits. Fig.2.3 depicts the input-output static characteristic of a three-bit (eight level) quantizer and the signal depending quantization error.

Fig. 2.3. Ideal ADC characteristic (above) and quantization error (below)

#### 2.2. Performance metrics

For the characterization of an analog-to-digital converter we can distinguish two categories of performance metrics: static and dynamic.

#### 2.2.1. Static metrics

All static metrics can be determined by comparison of the input-output characteristic of the ADC under test (real ADC) with that of the ideal ADC. In the following the main static parameters are described.

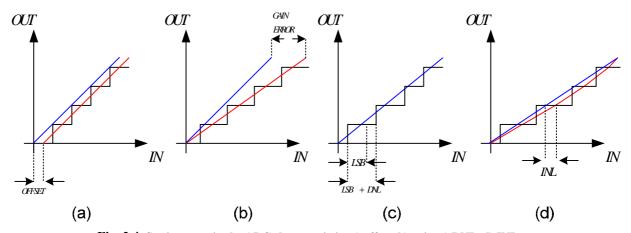

#### **Linear errors**

- The offset error (Fig 2.4a), defined as the intercept of the line interpolating the inputoutput characteristic with the horizontal axis. This error typically arises because of a shift of all reference voltages used as thresholds for the ADC, i.e. because the ground voltage is larger than zero.

- The gain error (Fig 2.5b), given by the ratio between the slope of the line interpolating the input-output characteristic of the real ADC and the slope of the ideal ADC. This error typically arises because all reference voltages are larger (or smaller) than the nominal value of the same relative amount, that is, all quantization steps are larger (or smaller) but still identical. For instance, this is the case when the threshold voltages of the ADC are generated by dividing a reference voltage by means of a resistive voltage divider and the reference voltage is larger (or smaller) than the nominal value.

#### **Non-linear errors**

These parameters are measured after removal of the two linear errors listed above and typically arise because of mismatch of the elements used in the A/D conversion, which are supposed to be identical (i.e. resistors or capacitors).

- Differential non-linearity (DNL) (Fig 2.5c), defined for each quantization step as the difference between the step width of the real ADC and the ideal quantization step  $\Delta U$  normalized to the  $\Delta U$

$$DNL(n) = \frac{V(n) - V(n-1) - \Delta U}{\Delta U}$$

(2.5)

DNL typically arises in presence of *random* mismatch of the elements used for the conversion and provides information about the *local* deviation of one step toward the ideal one.

- Integral non-linearity (INL) (Fig 2.d) is defined as the sum of the DNL of the real ADC over the whole input-output characteristic.

$$INL(n) = \sum_{1}^{k} DNL(k)$$

(2.6)

INL is the *accumulated* mismatch of the elements used in the conversion and provides information about the *maximum* (global) deviation of the real ADC characteristic toward the real one. It is also interesting to note that, while the DNL has a high-frequency spatial content, the INL has low-frequency spatial content because of the accumulation as in Eq. (2.6).

Fig. 2.4. Static errors in the ADC characteristic: a) offset, b) gain, c) DNL, d) INL

#### 2.2.2. Dynamic metrics

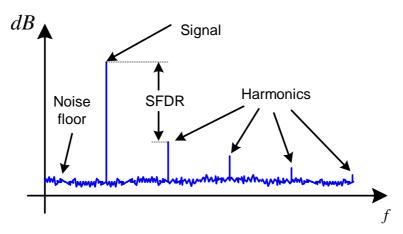

Dynamic metrics refer to the dynamic behavior of the ADC and are determined by examining the output spectrum of the ADC. The most important dynamic metrics are listed in the following:

Signal-to-noise ratio (SNR) is the ratio of the signal power to the noise power in the signal band, expressed in dB

$$SNR = 10\log\frac{P_{S}}{P_{N}} \tag{2.7}$$

Signal-to-noise-and-distortion ratio (SNDR) is the ratio of the signal power to the noise power in the signal band and the power of all signal harmonics in the signal band, expressed in dB

$$SNDR = 10\log \frac{P_S}{P_N + P_D} \tag{2.8}$$

Spurious free dynamic range (SFDR) is defined as the difference in dB between the signal amplitude and the amplitude of the largest spurious signal in the signal band

$$SFDR = 10\log\frac{P_{S}}{P_{D,\text{max}}} = P_{S,dB} - P_{D,\text{max},dB}$$

(2.9)

Total harmonic distortion (THD) is defined has the ratio of the total power of the harmonics to the signal power, expressed in dB

$$THD = 10\log \frac{\sum_{i} P_{D,i}}{P_{S}}$$

(2.10)

Fig.2.5. ADC output spectrum. Signal, harmonics and noise floor are highlighted

#### 2.3. Linearized model

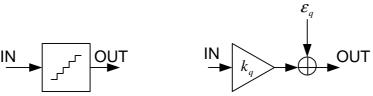

It is difficult to mathematically model the deterministic error introduced by the quantization process, since we have to cope with a nonlinear element: the quantizer. The problem can be simplified by making following assumptions:

- 1) the number of quantization levels is large;

- 2) the quantizer is not overloaded;

- 3) the input signal changes "rapidly", in such a way that successive output values are not correlated.

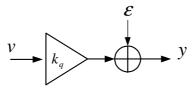

While the first two conditions are not difficult to be satisfied, the third one is hardly realized. For example just consider a constant input signal: in this case also the output will be constant and the output values are fully correlated. Nevertheless these assumptions lead to an approximate but in the reality good working model which is a very powerful instrument for designing an ADC. It can be shown that, if all three assumptions hold, the introduced quantization error presents white noise properties. We can then simplify the problem by replacing the quantizer, a strongly nonlinear block, by a linear amplifier with gain  $k_q$  and by adding white noise at its output (Fig. 2.6). The gain is given by the slope of the line interpolating the static input-output characteristic of the quantizer.

Fig. 2.6. Left: nonlinear quantizer. Right: linear model with added white noise

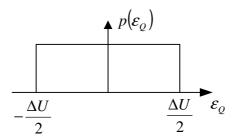

By replacing the quantization *error* by quantization *noise*, a purely deterministic process is modeled as a stochastic process. To quantify the equivalent white noise we need to calculate its variance. If condition 3) is valid, that is, the input signal changes continuously and in a non-regular way, we can assume that the probability that the signal lays somewhere between two thresholds is uniformly distributed, i.e. the probability  $p(\varepsilon_Q)$  of the quantization error is uniformly distributed in the interval  $[-\Delta U/2; \Delta U/2]$  (Fig. 2.7).

Fig. 2.7. Probability distribution of the quantization error

If assumption 2) applies no overloading of the quantizer takes place, hence the error is certainly limited to the interval  $[-\Delta U/2; \Delta U/2]$ . This means that:

$$\int_{-\frac{\Delta U}{2}}^{\frac{\Delta U}{2}} p(\varepsilon_Q) d\varepsilon_Q = 1 \tag{2.11}$$

From (2.11) and considering a uniform distribution it follows that:

$$p \cdot \Delta U = 1 \implies p = \frac{1}{\Delta U}$$

(2.12)

The variance of the zero mean random variable  $\varepsilon_Q$  is given by:

$$\sigma^{2} = \int_{-\infty}^{+\infty} p(\varepsilon_{Q}) \varepsilon_{Q}^{2} d\varepsilon_{Q} = \frac{1}{\Delta U} \int_{-\frac{\Delta U}{2}}^{\frac{\Delta U}{2}} \varepsilon_{Q}^{2} d\varepsilon_{Q} = \frac{1}{\Delta U} \left(\frac{1}{3}\varepsilon_{Q}^{3}\right) \Big|_{-\frac{\Delta U}{2}}^{\frac{\Delta U}{2}} = \frac{\Delta U^{2}}{12}$$

(2.13)

that is, the variance of the quantization noise is proportional to the square of the quantization interval. This result agrees with the intuition: a larger  $\Delta U$  means a larger quantization error, hence more "noise".

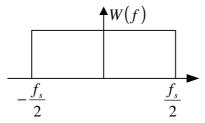

The power of the stochastic zero-mean variable  $\varepsilon_Q$  is its variance  $\sigma^2$ . Because the quantized signal is also sampled (time-discrete), the whole quantization noise power will be aliased in the frequency range  $[-f_s/2; f_s/2]$  leading to a power spectral density (PSD):

$$W(f) = \frac{\sigma^2}{f_s} = \frac{\Delta U^2}{12f_s} \tag{2.14}$$

Since the quantization noise is white, the spectral power density will be constant in the frequency range  $[-f_s/2; f_s/2]$  as depicted in Fig. 2.8.

Fig. 2.8. Power spectral density of the sampled quantization error

The signal-to-quantization noise ratio (SQNR) is defined as the SNR of the modulator when the only noise present is quantization noise, that is, all other noise sources (i.e. thermal noise, other disturbances) are assumed to be zero. The maximum SQNR is achieved with a full scale input signal because the quantization noise power is, according to the linearized model, constant and not depending on the signal. Assuming a full-scale sine input signal

$$x(t) = 2^{N-1} \Delta U \sin(\omega t) \tag{2.15}$$

the signal power is

$$P_S = \frac{1}{2} \cdot 2^{2(N-1)} \Delta U^2 \tag{2.16}$$

Hence the SQNR in dB is:

$$SQNR = 10\log\frac{P_S}{P_N} = 10\log\frac{\frac{1}{2} \cdot 2^{2(N-1)}\Delta U^2}{\frac{\Delta U^2}{12}} = 10\log\left(\frac{3}{2} \cdot 2^{2N}\right) = 1.76 + 6.02N$$

(2.17)

Eq. (2.17) shows that an SQNR improvement of 6dB is achieved by incrementing the resolution of the ADC of one bit.

Once we know the SQNR of a certain ADC we can define its effective number of bits (ENOB) as the number of bits of an ideal ADC which would have the same SQNR as the ADC we are considering. By simply rewriting (2.17) we get:

$$ENOB = \frac{SQNR - 1.76}{6.02} \tag{2.18}$$

#### 2.4. Oversampling

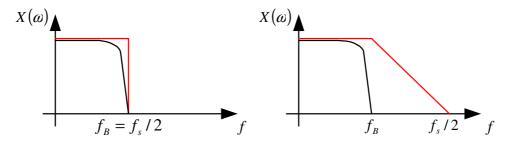

As previously seen, the minimal required sampling frequency in order to avoid aliasing is, according to the Nyquist-Shannon sampling theorem, twice the maximum signal frequency. In order to limit the signal bandwidth, a low-pass filter is required, called anti-aliasing filter. A low-pass filter has a transition frequency range between its pass-band and its stop-band, the width of this range depends on the order of the filter, that is, on the number of its poles. More precisely, the slope of the frequency response of the filter in the stop-band is equal to  $M \cdot 20$  dB/dec, where M is the filter order. In order to relax the requirements on the filter order it is useful to increase the sampling frequency  $f_s$  beyond the minimum required value. As shown in Fig. 2.9, the greater  $f_s$ , the simpler the anti-aliasing filter that can be used to limit the signal bandwidth. Aliasing will be negligible if the filter is designed to have large attenuation for larger frequencies than  $f_s/2$ , while it is not of concern if the attenuation is moderate between  $f_B$  and  $f_s/2$ .

Fig. 2.9. Amplitude response of anti-aliasing filters for  $f_s/2=f_B$  (left) and  $f_s/2>f_B$  (right)

A sampling process at frequencies above the Nyquist frequency is called oversampling. Apart from the benefits described before, oversampling has another important advantage. To analyze this we will make use of the already described linear model for an ADC. Again, considering a clocked *N*-bit quantizer and modelling the quantization error as white noise, we get following PSD for the quantization noise:

$$W(f) = \frac{\sigma^2}{f_s} = \frac{\Delta U^2}{12f_s} \tag{2.19}$$

As expected, the whole noise power will be aliased into the frequency range  $[-f_s/2; f_s/2]$  because of sampling. A substantial difference towards the Nyquist converter case can be observed: in order to calculate the SQNR of the converter we need to integrate the noise PSD in the signal band, that is, in the frequency interval  $[-f_B; f_B]$ .

This leads to a noise power

$$P_{N} = \frac{\Delta U^{2}}{12f_{s}} 2f_{B} = \frac{\Delta U^{2}}{12 \cdot OSR}$$

(2.20)

where we defined the factor

$$OSR = \frac{f_s}{2f_R} \tag{2.21}$$

This factor is called Oversampling Ratio (OSR). Note that in a Nyquist converter OSR=1 since  $f_s$ =2 $f_B$ . Following SQNR is obtained.

$$SQNR = 10\log\frac{P_{S}}{P_{N}} = 10\log\frac{\frac{1}{2} \cdot 2^{2(N-1)}\Delta U^{2}}{\frac{\Delta U^{2}}{12 \cdot OSR}} = 1.76 + 6.02N + 10\log OSR$$

(2.22)

Comparing equation (2.22) with the equation (2.17), valid for Nyquist converters, a 3-db SQNR improvement can be achieved by doubling the OSR, that is, the sampling frequency. Applying (2.18) this means an improvement of 0.5 bits of ENOB, hence we can achieve a better resolution by simply sampling faster. In other words we can trade off speed for accuracy. This result is particularly important when dealing with modern CMOS technologies: on the one side these offer, thanks to miniaturization, very high working frequencies, on the other size they allow only moderate precision of the analog parts. For this reason oversampled ADC are becoming very popular in the modern CMOS industry.

#### 2.5. Sigma-Delta ADC

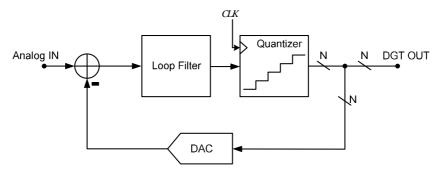

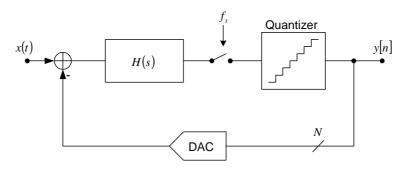

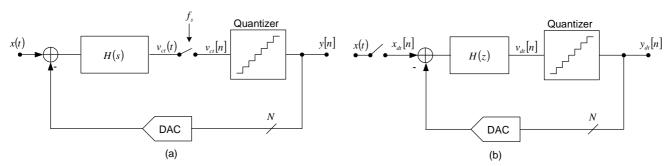

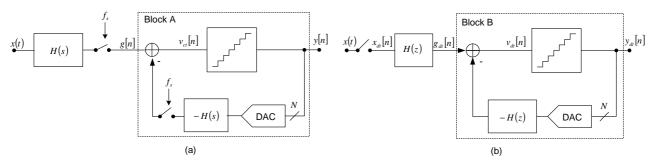

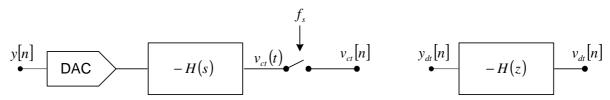

In order to further improve the resolution of the oversampled AD conversion architectural changes of the converter can be introduced. This is done by means of a Sigma-Delta modulator. The Sigma-Delta architecture joins the advantages of oversampling with those of feedback. In Fig. 2.10 we can see the general topology of such a modulator. This consists of three main blocks: a filter, called loop filter because of its position inside a loop; a clocked quantizer which is typically a comparator or an *N*-bit flash ADC; a Digital-to-Analog converter (DAC), usually a bank of switched capacitors or an array of identical current sources.

Fig. 2.10. Scheme of principle of a generic  $\Sigma\Delta$  modulator

The loop filter is constituted by one or many cascaded integrators, connected by a series of feed-forward and/or feedback paths. A strongly non-linear element is present, the quantizer, making it difficult to analyze the modulator with an exact analytical model. To understand the way this architecture works we can describe it by means of the linear model.

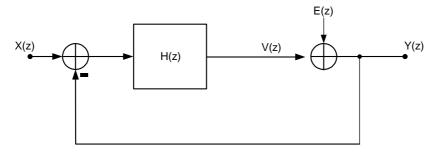

#### 2.5.1. Linear model

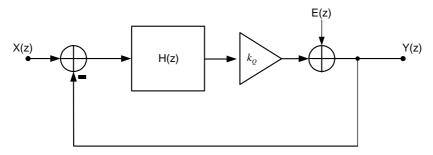

At first we will consider the DAC as ideal, namely perfectly linear and delay-free. The filter is also assumed to be linear and time invariant (LTI) and can thus be modeled by means of its transfer function H(z). At this point we assume the filter is discrete-time (DT), typically realized with switched capacitor techniques, since this allows an easier mathematical modeling. Finally, the quantizer is replaced by a gain element followed by an adder in order to take the quantization noise into account. The gain  $k_Q$  is the slope of the line interpolating the quantizer characteristic. Fig 2.11 shows the linear model of a generic Sigma-Delta modulator.

Fig. 2.11. Linear model of a generic  $\Sigma\Delta$  modulator

This linear time-invariant system has two inputs, X(z) and E(z) and one output. Assuming  $k_O=1$ , we can calculate two transfer functions:

$$STF(z) = \frac{Y(z)}{X(z)} = \frac{H(z)}{1 + H(z)}$$

(2.23)

and

$$NTF(z) = \frac{Y(z)}{E(z)} = \frac{1}{1 + H(z)}$$

(2.24)

STF is called Signal Transfer Function, NTF is the Noise Transfer Function. Equations (2.23) and (2.24) show that two different filter functions are obtained, depending on H(z), for the input signal and for the unwanted quantization noise. Using the superposition principle the output of the linear model is:

$$Y(z) = STF(z) \cdot X(z) + NTF(z) \cdot E(z)$$

(2.25)

In order to see the frequency response of STF and NTF we replace the variable z as following:

$$STF(j\omega) = STF(z)\Big|_{z=e^{j\omega T_s}} = \frac{H(e^{j\omega T_s})}{1 + H(e^{j\omega T_s})}$$

(2.26)

and

$$NTF(j\omega) = NTF(z)\Big|_{z=e^{j\omega T_s}} = \frac{1}{1 + H(e^{j\omega T_s})}$$

(2.27)

where  $T_s$  is the sampling frequency of the system. For all frequencies where

$$\left| H\left(e^{j\omega T_s}\right) >> 1 \tag{2.28}$$

we get:

$$STF(j\omega) \cong 1 \text{ and } NTF(j\omega) \cong \frac{1}{H(e^{j\omega T_s})}$$

(2.29)

By inserting (2.29) in (2.25):

$$Y(j\omega) \cong X(j\omega) + \frac{E(j\omega)}{H(j\omega)}$$

(2.30)

Therefore, if  $H(j\omega)$  is designed to have a high gain at frequencies in the signal band, the modulator output contains a replica of the non-attenuated input signal and largely attenuated quantization noise in that band.

The transfer function (TF) of the loop filter can be expressed as:

$$H(z) = \frac{N(z)}{D(z)} \tag{2.31}$$

where N(z) and D(z) are the numerator and the denominator of H(z) respectively. Both are polynomial functions of z.

By substituting (2.31) in (2.24) we obtain:

$$NTF(z) = \frac{1}{1 + H(z)} = \frac{D(z)}{D(z) + N(z)}$$

(2.32)

This equation shows that the zeros of the NTF are the poles of the loop filter.

The loop filter contains one or more integrators; the number of the integrators is called *order* of the modulator. In the following some basic topologies are shortly analyzed.

### 2.5.2. 1st order modulator

Assuming the loop filter is a forward Euler DT-integrator, that is:

$$H(z) = \frac{z^{-1}}{1 - z^{-1}} \tag{2.33}$$

following STF and NTF can be derived:

$$STF(z) = \frac{H(z)}{1 + H(z)} = z^{-1}$$

$NTF(z) = \frac{1}{1 + H(z)} = 1 - z^{-1} = \frac{z - 1}{z}$  (2.34)

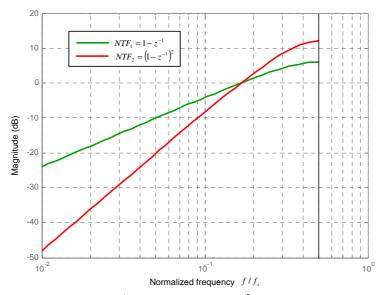

The STF is a simple delay of one clock period, while the NTF is a differentiator. A sigmadelta modulator using a single integrator as loop filter is called 1<sup>st</sup> order modulator. The NTF obtained has a zero for z=1 that is at DC (f=0) and a slope of +20dB/dec. The maximum of the NTF is achieved for z=-1, that is for  $f=f_s/2$  and is equal to 2 (6 dB). The frequency response of NTF is shown in green in Fig. 2.12.

Fig. 2.12. NTF of a 1st order (green) and 2nd order (red) modulator.

The main advantage of the sigma-delta architecture is now evident: the quantization noise is frequency *shaped*, i.e. high-pass filtered. Therefore we expect a better resolution than that of a simple oversampled ADC. To calculate the SQNR of the  $1^{st}$  order sigma-delta modulator we need to calculate the output noise power  $P_N$  together with the signal power  $P_S$ . Assuming a purely delaying STF, the latter is simply equal to the signal power at the input, namely, as shown in section 2.3, eq. (2.16):

$$P_{S} = \frac{1}{2} \cdot 2^{2(N-1)} \Delta U^{2} \tag{2.35}$$

Considering an N-bit quantizer, following input noise power spectral density (PSD) is added by the quantizer:

$$W(f) = \frac{\sigma^2}{f_s} = \frac{\Delta U^2}{12f_s} \tag{2.36}$$

the PSD at the output is:

$$W_{out}(f) = W(f)|NTF(f)|^{2} = \frac{\Delta U^{2}}{12f_{s}} \left| (1 - z^{-1})_{z=e^{j2\pi gT_{s}}} \right|^{2} = \frac{\Delta U^{2}}{12f_{s}} \left| 1 - e^{-j2\pi gT_{s}} \right|^{2}$$

$$= \frac{\Delta U^{2}}{12f_{s}} \left| e^{-j\pi gT_{s}} \left( e^{j\pi gT_{s}} - e^{-j\pi gT_{s}} \right) \right|^{2} = \frac{\Delta U^{2}}{12f_{s}} \left| \left( e^{j\pi gT_{s}} - e^{-j\pi gT_{s}} \right) \right|^{2}$$

(2.37)

By using Euler's formula:

$$\frac{e^{j\pi T_s} - e^{-j\pi T_s}}{2j} = \sin(\pi T_s) \tag{2.38}$$

$$W_{out}(f) = \frac{\Delta U^2}{12f_s} [2\sin(\pi f T_s)]^2$$

(2.39)

By integrating the PSD of the quantization noise at the modulator output in the signal band we obtain:

$$P_{N} = \int_{-f_{B}}^{f_{B}} \frac{\Delta U^{2}}{12f_{s}} \left[ 2\sin(\pi g T_{s}) \right]^{2} df \cong \frac{\Delta U^{2}}{12} \frac{\pi^{2}}{3} \left( 2f_{B}T_{s} \right)^{3} = \frac{\Delta U^{2}}{12} \frac{\pi^{2}}{3} OSR^{-3}$$

(2.40)

This result is obtained adopting the approximation:

$$\sin(\pi T_s) \cong \pi T_s \tag{2.41}$$

which is valid for  $fT_s <<1$ , that is, for frequencies which are much smaller than the sampling frequency. This is normally the case by oversampled ADCs. Looking at (2.40), the first term of the final product is the input quantization noise, the second term is a constant while the third one shows that the output noise power is inversely proportional to the  $3^{rd}$  power of the OSR.

The SQNR of a 1<sup>st</sup> order modulator is:

$$SQNR = 10\log\frac{P_{S}}{P_{N}} = 10\log\frac{\frac{1}{2}\cdot2^{2(N-1)}\Delta U^{2}}{\frac{\Delta U^{2}}{12}\frac{\pi^{2}}{3}OSR^{-3}} = 1.76 + 6.02N - 10\log\frac{\pi^{2}}{3} + 10\log OSR^{3}$$

(2.42)

Equation (2.42) shows that 9-dB SQNR improvement can be achieved by doubling the OSR, that is, an improvement of 1.5 bits of ENOB.

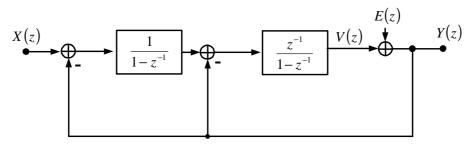

### 2.5.3. 2<sup>nd</sup> order modulator

A 2<sup>nd</sup> order sigma-delta modulator makes use of two integrators in the loop. Since each integrator causes a phase shift of -90 degrees because of its pole at DC, this structure is unsuitable for a system with feedback because of stability issues. In this case the phase margin of the modulator would be zero. An additional negative zero is required in order to improve the phase margin. As known, a negative zero causes a phase shift of +90 degrees. The zero can be introduced by means of an additional feed-forward (FF) or feedback (FB) path. Fig 2.13 shows for instance a 2<sup>nd</sup> order modulator with an additional feedback path. The 1<sup>st</sup> integrator is a backward Euler non-delaying integrator and its TF is:

$$H_1(z) = \frac{1}{1 - z^{-1}} \tag{2.43}$$

the 2<sup>nd</sup> integrator is a forward Euler delaying integrator with TF

$$H_2(z) = \frac{z^{-1}}{1 - z^{-1}} \tag{2.44}$$

The loop filter transfer function of the modulator in Fig. 2.13 is:

$$H(z) = \frac{V(z)}{Y(z)} = -\frac{z^{-1}}{(1-z^{-1})^2} - \frac{z^{-1}}{(1-z^{-1})} = \frac{-2z+1}{(z-1)^2}$$

(2.45)

where V(z) is the quantizer input. Eq. (2.45) shows the presence of a zero  $z_n$ =-1/2, which arises from the additional feedback path.

Fig. 2.13.  $2^{nd}$  order  $\Sigma\Delta$  modulator with additional feedback

By calculating the STF and the NTF we obtain now:

$$STF(z) = \frac{Y(z)}{X(z)} = z^{-1}$$

(2.46)

and

$$NTF(z) = \frac{Y(z)}{E(z)} = (1 - z^{-1})^2 = \frac{(z - 1)^2}{z^2}$$

(2.47)

As in the 1<sup>st</sup> order case, the STF is simply a delay of one clock period  $T_s$ . The NTF is now a differentiator of 2<sup>nd</sup> order, i.e. it has two zeros at DC. Its frequency response is shown in red in Fig. 2.12. The slope of the curve is now +40dB/dec while the maximum of NTF is again for z=-1 ( $f=f_s/2$ ) and equals to 4 (12 dB).

To calculate the SQNR we recognize that the signal power is the same as in the 1<sup>st</sup> order case, since we deal with a simply delaying STF. The output noise PSD is, by taking into account the new NTF (2.47):

$$W_{out}(f) = W(f)|NTF(f)|^{2} = \frac{\Delta U^{2}}{12f_{s}} \left| (1 - z^{-1})_{z=e^{j2\pi jT_{s}}}^{2} \right|^{2} = \frac{\Delta U^{2}}{12f_{s}} \left| (1 - e^{-j2\pi jT_{s}})^{2} \right|^{2}$$

$$= \frac{\Delta U^{2}}{12f_{s}} \left| \left[ e^{-j\pi jT_{s}} \left( e^{j\pi jT_{s}} - e^{-j\pi jT_{s}} \right) \right]^{2} \right|^{2} = \frac{\Delta U^{2}}{12f_{s}} \left| e^{-j2\pi jT_{s}} \left( e^{j\pi jT_{s}} - e^{-j\pi jT_{s}} \right)^{2} \right|^{2}$$

$$= \frac{\Delta U^{2}}{12f_{s}} \left| \left[ 2j\sin(\pi jT_{s}) \right]^{2} \right|^{2} = \frac{\Delta U^{2}}{12f_{s}} 16\sin^{4}(\pi jT_{s})$$

$$(2.48)$$

By integrating the PSD of the quantization noise at the modulator output in the signal band we obtain:

$$P_{N} = \int_{-f_{B}}^{f_{B}} \frac{\Delta U^{2}}{12f_{s}} 16 \sin^{4}(\pi f T_{s}) df \cong \frac{\Delta U^{2}}{12} \frac{\pi^{4}}{5} (2f_{B}T_{s})^{5} = \frac{\Delta U^{2}}{12} \frac{\pi^{4}}{5} OSR^{-5}$$

(2.49)

Again, the result is approximated and valid only for  $f \le f_s$ . In this case the output noise power is inversely proportional to the  $5^{th}$  power of the OSR.

The SQNR of a 2<sup>nd</sup> order modulator is:

$$SQNR = 10\log\frac{P_S}{P_N} = 10\log\frac{\frac{1}{2} \cdot 2^{2(N-1)} \Delta U^2}{\frac{\Delta U^2}{12} \frac{\pi^4}{5} OSR^{-4}} = 1.76 + 6.02N - 10\log\frac{\pi^4}{5} + 10\log OSR^5$$

(2.50)

Equation (2.50) shows that 15-dB SQNR improvement can be achieved by doubling the OSR, that is, an improvement of 2.5 bits of ENOB.

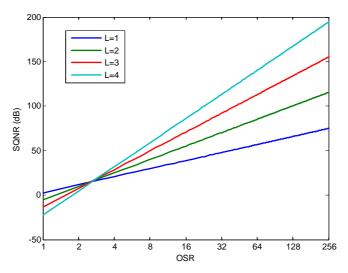

#### 2.5.4. L-th order modulator

A loop filter of L-th order is constituted by L cascaded integrators. By generalizing the calculation for a modulator of L-th order with a pure differentiating NTF in the form:

$$NTF = (1 - z^{-1})^{L} = \frac{(z - 1)^{L}}{z^{L}}$$

(2.51)

This NTF has L zeros at DC and a maximum of  $2^L$  for  $f=f_s/2$ . By calculating the output quantization noise power in the signal band solving the integral:

$$P_{N} = \int_{-f_{B}}^{f_{B}} \frac{\Delta U^{2}}{12f_{s}} |NTF(f)|^{2} df$$

(2.52)

we obtain, similarly to the previous cases:

$$SQNR = 1.76 + 6.02N - 10\log\frac{\pi^{2L}}{2L+1} + 10\log OSR^{2L+1}$$

(2.53)

This means a  $(2L+1)\cdot 3$  dB SQNR increase for each doubling of the OSR, that is, an improvement of  $(2L+1)\cdot 0.5$  bits of ENOB. Fig. 2.14 plots the theoretically achievable SQNR as a function of the OSR and the modulator order L. The number of bits of the quantizer is assumed to be 1. For each additional bit the plotted lines are simply shifted upwards by 6.02 dB (eq. 2.53).

Fig. 2.14. Achievable SQNR with 1-bit comparator for purely differentiating NTF= $(1-z^{-1})^L$

As explained later, it is not possible to realize a pure differentiating NTF of arbitrary order L, since instability issues occur. The graph above simply plots the theoretical achievable resolution.

#### 2.5.5. Stability analysis

Although the linear model proves very useful to estimate the achievable resolution of the modulator depending on the sampling frequency, the modulator order and the resolution of the quantizer, it gives not much information about the stability of the modulator.

One criterion to estimate the stability is the analysis of the root locus, that is, the position of the filter poles on the *z*-plane. Even if the filter is designed to be stable, i.e. all poles are inside the unit circle, the modulator can get instable, depending on the amplitude of the signal at the quantizer input. Here we distinguish two cases:

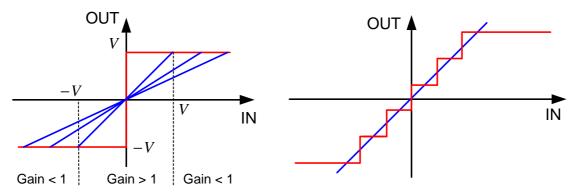

a) one-bit quantizer (i.e. a single comparator); it is not straightforward to define the gain of the quantizer in the linear model, as the straight lines interpolating the comparator characteristic are infinite (Fig. 2.15). Moreover the instantaneous gain depends on the amplitude of the input signal, since the output is limited to only two values  $\pm V$ .

Fig. 2.15. Gain of a 1-bit (left) and multibit (right) quantizer

As depicted in Fig. 2.15, when the input signal is bounded in the interval [-V,V] a gain larger than one is obtained, otherwise the gain is smaller than one (the comparator is overloaded).

[Ris94] defines the gain of the comparator as:

$$k_q = \frac{\text{cov}(v, y)}{\sigma^2(v)} \tag{2.54}$$

This is the value which minimizes the power of the quantization error sequence [Sch05]. To demonstrate this, consider the linear model of the quantizer (Fig. 2.16). The output is:

$$y = k_a v + \varepsilon \tag{2.55}$$

where v is the comparator input, y its output and  $\varepsilon$  the quantization error. Assuming a zero-mean quantization error  $\varepsilon$ , the error power is equal to its variance, namely:

$$\sigma^{2}(\varepsilon) = \sigma^{2}(y - k_{a}v) = \sigma^{2}(y) - 2k_{a}\operatorname{cov}(v, y) + k_{a}^{2}\sigma^{2}(v)$$

(2.56)

Differentiating (2.56) with respect to  $k_q$  the value of  $k_q$  minimizing the error variance is found to be the same as proposed by [Ris94] in (2.54). Equation (2.54) shows that the gain  $k_q$  can only be defined if the statistical properties of the quantizer input  $\nu$  are known.

Fig. 2.16. Linear model of the quantizer

b) multibit quantizer: in this case it is possible to define the gain as the slope of the straight line interpolating the input-output characteristic (Fig. 2.15). The larger the number of quantization levels, the better the approximation made. This model works correctly as long as the quantizer is not overloaded. If this happens, the output amplitude remains constant even when the input increases (clipping), leading to a reduction of the effective gain.

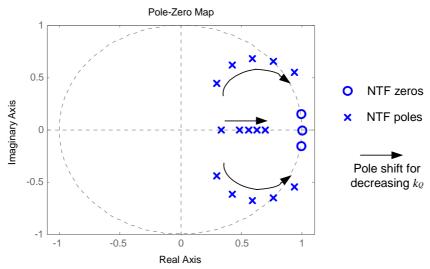

The linear model can be enhanced by taking into account a variable gain for the quantizer. We can define the point at which instability occurs, as the point where the closed loop poles, i.e. the poles of the NTF, move outside the unit circle. This can be made by plotting the closed loop poles for different gains of the amplifier which models the quantizer in the linear model. For example, Fig. 2.17 plots the root locus of a 3<sup>rd</sup> order NTF with three zeros and three poles against the quantizer gain  $k_Q$ . By decreasing  $k_Q$  the poles eventually move outside the unit circle, leading to instability of the modulator. This analysis is useful to get an insight, how far the system is from instability.

Fig. 2.17. Root locus of the NTF singularities as function of the quantizer gain

Intuitively, a smaller  $k_Q$  leads to instability and, as seen previously, this occurs if the quantizer input becomes too large, such that the quantizer is overloaded. Assuming a non overloaded multibit quantizer with unity gain as in Fig. 2.18, we can estimate the amplitude of the quantizer input, by calculating the TF between the input signal X(z) and the quantizer input V(z) and between the "quantization noise source" E(z) and V(z). Using the superposition principle we can express V(z) as the sum, of a signal and a noise contribution.

$$V(z) = V(z)_{signal} + V(z)_{noise} = STF \cdot X(z) + NTF \cdot E(z) - E(z)$$

(2.57)

Fig. 2.18. Linear model with unit quantizer gain

Typically the STF is one in the signal band and smaller than one for higher frequencies. From Eq. 2.57 we can see that V(z) contains a replica of the input signal X(z) plus high-pass filtered quantization noise. Qualitatively, two factors contribute to saturate the quantizer: the amplitude of X(z) which is replicated by V(z) and the amount of high-filtered noise which is fed back to V(z). These considerations suggest the introduction of two parameters to get a

measure of the modulator stability: a)  $NTF_{MAX}$ , the maximum of |NTF(z)|, gives information about the high-frequency gain of the NTF; b) the maximum stable amplitude (MSA) defines the maximum amplitude of the input signal, so that the modulator remains stable.

An empirical criterion based on experience and observation states that a modulator is likely to be stable for  $NTF_{MAX}<1.5^1$  [Sch05], although this condition is neither necessary nor sufficient.

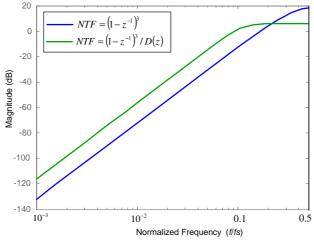

From this point of view it becomes clear that higher order purely differentiating NTFs necessarily lead to instability, since their maximum gain increases exponentially with the order L (NTF<sub>MAX</sub>= $2^L$ ). A countermeasure consists in deliberately reducing the maximum of the NTF by introducing poles in its TF [Sch05].

$$NTF_D = \frac{(z-1)^L}{D_N(z)} \tag{2.58}$$

$D_N(z)$  is a polynomial in z in the form:

$$D_{N}(z) = z^{L} + a_{I-1}z^{L-1} + \dots + a_{1}z + 1$$

(2.59)

the poles of  $NTF_D$  are usually chosen so that the NTF is a Chebyschev or Butterworth highpass maximally flat filter. The result of this operation is, as depicted in Fig. 2.19, a reduction of the high-frequency gain at the expense of an increased low-frequency gain, that is, an increase of the noise floor in the signal band. The price for a better stability is thus a worse noise suppression, hence a lower SQNR of the modulator. Since the numerator of NTF<sub>D</sub> is the same as that of the purely differentiating NTF we can calculate the increase  $\alpha$  of the noise floor, assuming the NTF poles are at much higher frequencies than  $f_B$ , as:

$$\alpha = \frac{NTF_D(z)}{NTF(z)}\Big|_{z=1} = \frac{1}{D_N(z=1)} = \frac{1}{1 + a_{L-1} + \dots + a_1 + 1}$$

(2.60)

The assumption that the poles are at much higher frequencies than  $f_B$  means a constant inband increase of NTF, which is evident in Fig. 2.19, where both curves are parallel in the lower frequency range.

Fig. 2.19. Example of reduction of NTF<sub>MAX</sub> by introducing new poles for NTF

$<sup>^{1}</sup>$  This condition is applied to modulators with binary (one-bit) comparators. Multibit modulators are more robust against instability and tolerate higher values of NTF<sub>MAX</sub>.

#### 2.5.6. Zero spreading

So far only a purely differentiating NTF was assumed, obtained with a loop filter constituted of one or more cascaded integrators. This kind of NTF does not ensure an optimal noise shaping. For a given modulator order L the optimal NTF can be found by minimizing the quantization noise power in the signal band, that is, by finding the minimum of the integral:

$$P_{N} = \int_{-f_{B}}^{f_{B}} \frac{\Delta U^{2}}{12f_{s}} |NTF(f)|^{2} df$$

(2.61)

Once the poles are chosen based on stability considerations, the solution of the problem consists in finding:

$$\min \left[ \int_{-f_B}^{f_B} |N(z)|_{e^{j2\pi f}}^2 df \right]$$

(2.62)

where N(z) is the numerator of the NTF in form of a polynomial of z of order L.

By solving (2.62) numerically, the frequency of the zeros which minimize the in-band noise and the SQNR improvement can be calculated [Nor97]. The results of the numerical calculations are shown in Tab. 2.1. The optimal NTF zeros are always located on the unit circle ( $|z_n|=1$ ), that is, the damping factor is zero. They are either at DC or complex-conjugate and cause the NTF frequency response to have a notch at the frequencies of the zeros.

| Order L of<br>NTF | Freq. of the zeros normalized to $f_B$ | Location of the zeros on the z-<br>plane | SQNR improvement (dB) |

|-------------------|----------------------------------------|------------------------------------------|-----------------------|

| 1                 | 0                                      | 1                                        | 0                     |

| 2                 | ±0.577                                 | 0.994±0.113j                             | 3.5                   |

| 3                 | 0, ±0.775                              | 1, 0.988±0.152j                          | 8                     |

| 4                 | ±0.34, ±0.861                          | 0.998±0.067j, 0.986±0.168j               | 13                    |

| 5                 | $0, \pm 0.538, \pm 0.906$              | 1, 0.994±0.106j, 0,984±0.177j            | 18                    |

Tab. 2.1. Location of the NTF zeros for optimal suppression of the quantization noise (zero spreading)

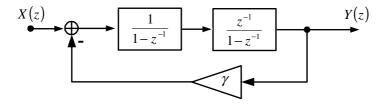

Complex-conjugate NTF zeros on the unit circle are obtained with a local feedback path across two consecutive integrators of the loop filter, forming a circuit called resonator (Fig. 2.20) with transfer function:

$$H_{res}(z) = \frac{Y(z)}{X(z)} = \frac{z^{-1}}{1 - (2 - \gamma)z^{-1} + z^{-2}}$$

(2.63)

where  $\gamma$  is the feedback coefficient.

Fig. 2.20. Resonator for generation of complex-conjugate NTF zeros (filter poles) on the unit circle.

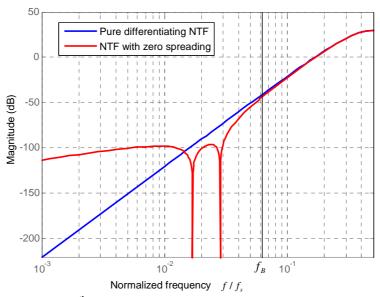

Fig 2.21 shows exemplary a NTF of 5th order with (in red) and without zero spreading (in blue). The notches are introduced by two pairs of complex-conjugate zeros on the unit circle.

Fig. 2.21. Gain response of a 5<sup>th</sup> order NTF: pure differentiating (blue) and with zero spreading (red)

The zero spreading allows stronger noise suppression in the higher signal band at the expense of lower suppression at very low frequencies. The total in-band noise power is nevertheless smaller than in the purely differential NTF.

#### 2.6. Quasi-linear model

All previous calculations of the performance of sigma-delta modulators were based on linearized models. Although these models are very simple and powerful, they are not exact and base on assumptions, which are not always true (such as the non-correlation of the input samples). Starting from these considerations, some authors have developed non-linear or quasi-linear models. These models are very complicated to apply and often become unsuitable for practical design implementations. For example [Ris94] models a 1-bit sigma-delta modulator with a technique which is known from the circuit simulation. The problem is split in two parts: a DC operating point and an AC model. Three approximations are made:

- the input signal has zero frequency (DC). This assumption is valid if the sampling frequency is much higher than the signal frequency, that is, if OSR>>1

- the mean output value of the modulator is supposed to be the same as the constant input signal. This assumption is correct if the loop gain of the modulator is very large at low frequencies, so that the output (which is fed back) can track the input. This constant output value can be seen as the operating point of the comparator, which determine its AC (small signal) parameters

- the quantization error is modeled as noise, like in the well-known linear model. The comparator is replaced by a gain element which is applied only to the AC noise and not to the DC signal

In summary the output binary flow is the sum of two components:

- the mean value is a replica of the (constant) input signal of the modulator

the variance, i.e. the AC power of the output, is the high-pass filtered noise according to the formula

$$\sigma^{2}(y) = \frac{\Delta U^{2}}{12} \int_{0}^{f_{B}} NTF_{K}(f) df = \frac{\Delta U^{2}}{12} A(k_{q})$$

(2.64)

Here  $NTF_K$  denotes the NTF of the modulator as a function of the quantizer AC-gain  $k_a$ :

$$NTF_K = \frac{1}{1 + k_q H} \tag{2.65}$$

where  $k_q$  is the comparator gain defined as in (2.54).

This quasi-linear modeling allows to get information about the stability of the modulator and to predict non-linear phenomena like limit cycles but will not be used in the present work.

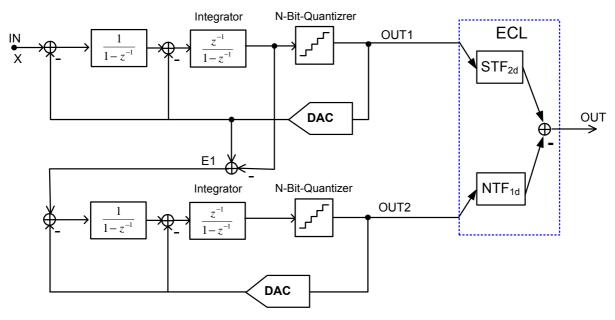

#### 2.7. Single loop / Cascaded

It was shown that the maximum of the NTF gives an indication about the stability behavior. In particular, larger values of  $NTF_{MAX}$  denote a modulator which is more prone to instability. Apart from the technique already shown, consisting in the introduction of poles in the NTF to lower the maximum NTF gain at the expense of less noise suppression, another solution is possible. The idea is to process the quantization noise in more than one loop, making a more aggressive noise shaping possible without sacrificing the stability of the modulator. Fig. 2.22 shows the main blocks of such architecture. Two ore more loops are cascaded: the first loop processes the input signal while the latter threat the quantization noise introduced by the first loop. The digital outputs of the single stages are processed by a digital block called Error Correction Logic (ECL). This logic block filters the digital inputs with appropriate transfer functions.

In the following an example of a 2-2 cascaded modulator (Fig. 2.2) is explained: the modulator consists of two identical DT  $2^{nd}$  order sigma delta modulators. The digital outputs of the modulators are:

$$OUT_1 = STF_1 \cdot X + NTF_1 \cdot E_1$$

$$OUT_2 = STF_2 \cdot E_1 + NTF_2 \cdot E_2$$

(2.66)

where  $STF_1$ ,  $STF_2$  are the signal transfer functions,  $NTF_1$ ,  $NTF_2$  the noise transfer functions and  $E_1$ ,  $E_2$  the quantization noise of the 1<sup>st</sup> and 2<sup>nd</sup> stage respectively. Digitally filtering both  $OUT_1$  and  $OUT_2$  and summing them, following output signal is provided by the ECL:

$$OUT = OUT_1STF_{2d} - OUT_2NTF_{1d}$$

(2.67)

Substituting (2.66) in (2.67) the digital output is:

$$OUT = STF_1STF_{2d}X + NTF_1STF_{2d}E_1 - STF_2NTF_{1d}E_1 - NTF_2NTF_{1d}E_2$$

(2.68)

Fig. 2.22. A 2-2 cascaded DT sigma-delta modulator

By choosing:

$$STF_{2d} = STF_2 = z^{-1}$$

(2.69)

and

$$NTF_{1d} = NTF_1 = (1 - z^{-1})^2 (2.70)$$

we obtain:

$$OUT = STF_1STF_{2d}X - NTF_2NTF_{1d}E_2 = z^{-2}X - (1 - z^{-1})^4E_2$$

(2.71)

We see that the digital output is the sum of the input signal delayed by two clock periods plus the  $4^{th}$  order shaped quantization noise of the  $2^{nd}$  stage. The quantization noise of the  $1^{st}$  stage has been completely canceled. In general the noise contained at the output is the quantization noise of the last stage, the order of noise shaping is the sum of the orders of the single stages. The other noise terms from all other stages are cancelled by the ECL. The advantage of a cascaded architecture is that we can *theoretically* achieve a noise shaping of very large order by simply cascading many stages of lower order. Moreover, we can get very stable modulators by keeping the order of the single stages low (typically  $\leq 2$ ).

On the other hand this architecture suffers from a major issue: mismatch between analog and digital part of the modulator. In fact, we need a perfect cancelling of the analog generated TF with the digitally generated ones. This is not possible in a real implementation of the circuit: while the digital filters behave ideally, the analog NTF and STF of the analog loop depend on circuit non-idealities like integrator gain, bandwidth, settling error, etc. and therefore deviate from the ideal form. In the 2-2 modulator, for example, a residuum  $\alpha \cdot E_I$  of the unwanted noise of the first stage leaks to the output worsening the modulator resolution (SQNR):

$$OUT = STF_1STF_{2d}X + \alpha E_1 - NTF_2NTF_{1d}E_2$$

(2.72)

For this reason seldom more than two stages are cascaded, since the leakage noise eventually dominates the other noise terms and further cascading would have no more benefits.

#### 2.8. Discrete time / continuous time loop filter

Another important distinction in the family of sigma-delta modulators concerns the implementation of the loop filter. There are basically two categories of loop filers: discrete time (DT) and continuous time (CT) filters.

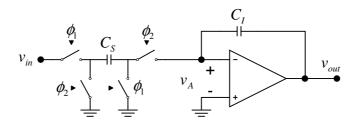

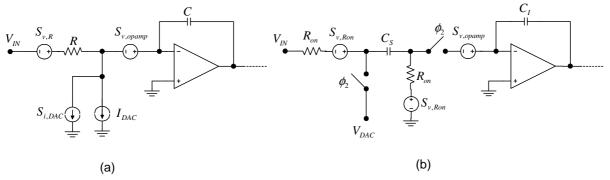

#### 2.8.1. Discrete time filter

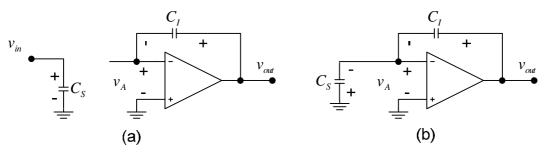

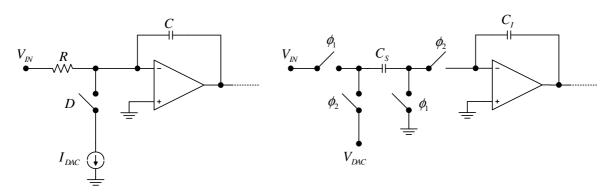

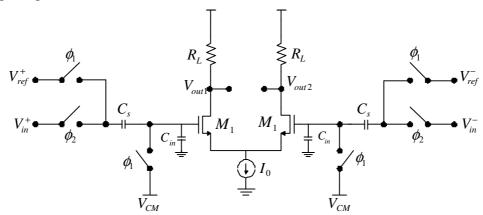

Discrete time filters are implemented by means of switched capacitor (SC) circuits. These circuits are constituted by operational amplifiers (opamp), capacitors and switches. Additionally, two clock phases are necessary to switch the capacitors. A typical SC integrator is depicted in Fig. 2.23.

Fig. 2.23. Discrete time, switched capacitor integrator

We can distinguish two operation phases: a sampling phase, when  $\varphi_I$  is high and  $\varphi_2$  is low, where the input voltage is sampled on the capacitor  $C_S$ ; an integration phase when  $\varphi_2$  is high and  $\varphi_I$  is low, where the charge stored in  $C_S$  is transferred into  $C_I$ . The ideal opamp forces the voltage  $v_A$  to stay at zero (virtual ground). The output voltage in the time domain is:

$$v_{out}[n] = v_{out}[n-1] + v_{in}[n-1] \frac{C_s}{C_I}$$

(2.73)

By z-transforming both terms of equation (2.73):

$$V_{out} = V_{out} z^{-1} + V_{in} z^{-1} \frac{C_s}{C_t}$$

(2.74)

that is:

$$H(z) = \frac{V_{out}}{V_{in}} = \frac{z^{-1}}{1 - z^{-1}} \frac{C_S}{C_I}$$

(2.75)

namely the TF of a forward Euler integrator. The gain coefficient of the integrator is the ratio  $C_S/C_I$ . The most important advantage of SC circuits is that sensitive circuit parameters can be made dependant on capacitor ratios. This peculiarity proves useful in integrated circuits were large process-related variations affect the *absolute* values of the components. In contrast to this, the *relative* variations of elements of the same type, which are physically contiguous on the chip are relatively small. Hence, even a large variation of the absolute value of the

capacitors  $C_S$  and  $C_I$  in (2.75) has a very small influence on the capacitor ratio. SC-based integrated circuits can achieve a precision of up to 0.1% despite fluctuations of the absolute values in the order of  $\pm 20\%$ .

#### 2.8.1.1. Errors in the TF because of non-idealities

Deviations from the ideal TF are caused by non-idealities of the analog circuit realizing the DT integrator:

- mismatch of the capacitors  $C_S$  and  $C_I$

- finite DC-gain of the opamp

- finite bandwidth of the opamp

- slew rate of the opamp

The effect of capacitor mismatch is straightforward and, according to (2.75), a gain error in the integrator TF is introduced. This error is limited, thanks to the good matching properties of capacitors which are contiguous on the layout and is typically on the order of 0.1%.

Let us consider an opamp with finite DC-gain  $A_{DC}$ . Now a non-zero voltage  $v_A$  is present at the opamp inputs (Fig. 2.23):

$$v_A = -\frac{v_{out}}{A_{DC}} \tag{2.76}$$

Analyzing the DT-integrator in the time domain we can calculate the total charge Q in the capacitors according to the polarity shown in Fig. 2.24. When  $\varphi_I$  is high (Fig. 2.24a):

$$Q[n-1] = v_{in}[n-1]C_S + (v_{out}[n-1] - v_A[n-1])C_I = v_{in}[n-1]C_S + v_{out}[n-1](1 + \frac{1}{A_{DC}})C_I$$

(2.77)

where *n* denotes the discrete time point considered. When  $\varphi_2$  is high (Fig. 2.24b), noting that capacitor  $C_S$  is turned upside down because of the switching, the time-domain equation is:

$$Q[n] = -v_A[n]C_S + (v_{out}[n] - v_A[n])C_I = v_{out}[n]\frac{C_S}{A_{DC}} + v_{out}[n]\left(1 + \frac{1}{A_{DC}}\right)C_I$$

(2.78)

Rearranging the terms:

Fig. 2.24. Switched capacitor integrator: sampling phase (a) and integration phase (b)

$$Q[n] = v_{out}[n] \cdot \left[ \left( 1 + \frac{1}{A_{DC}} \right) C_I + \frac{C_S}{A_{DC}} \right]$$

(2.79)

Equating (2.77) and (2.79), according to the principle of charge conservation:

$$Q[n-1] = Q[n] \Rightarrow v_{in}[n-1]C_S + v_{out}[n-1]\left(1 + \frac{1}{A_{DC}}\right)C_I = v_{out}[n] \cdot \left[\left(1 + \frac{1}{A_{DC}}\right)C_I + \frac{C_S}{A_{DC}}\right]$$

(2.80)

Transforming this time-domain equation into the *z*-domain:

$$V_{in}z^{-1}C_{S} + V_{out}z^{-1}\left(1 + \frac{1}{A_{DC}}\right)C_{I} = V_{out}\left[\left(1 + \frac{1}{A_{DC}}\right)C_{I} + \frac{C_{S}}{A_{DC}}\right]$$

(2.81)

Hence, the TF of the integrator will be:

$$H(z) = \frac{V_{out}}{V_{in}} = \frac{z^{-1}C_S}{\left(1 + \frac{1}{A_{DC}}\right)C_I + \frac{C_S}{A_{DC}} - z^{-1}\left(1 + \frac{1}{A_{DC}}\right)C_I}$$

(2.82)

The DC-gain of the integrator is:

$$H(z)|_{z=1} = A_{DC} (2.83)$$

which is, as expected, the same as the DC-gain of the operational amplifier used for the integrator. Furthermore, a pole shift can be observed by equating the denominator of (2.82) to zero:

$$\left(1 + \frac{1}{A_{DC}}\right)C_I + \frac{C_S}{A_{DC}} - z^{-1}\left(1 + \frac{1}{A_{DC}}\right)C_I = 0$$

(2.84)

$$z_{P} = \frac{\left(1 + \frac{1}{A_{DC}}\right)C_{I}}{\left[\left(1 + \frac{1}{A_{DC}}\right)C_{I} + \frac{C_{S}}{A_{DC}}\right]} = \frac{C_{I}}{C_{I} + \frac{C_{S}}{\left(1 + \frac{1}{A_{DC}}\right)A_{DC}}}$$

(2.85)

$$z_P \cong \frac{1}{1 + \frac{C_S}{C_I A_{DC}}} \cong 1 - \frac{C_S}{C_I A_{DC}} = 1 - \Delta_P$$

(2.86)

where the last approximation holds for large values of  $A_{DC}$ . While the pole of the ideal integrator is at DC (z=1), its location is shifted inside the unit circle by an amount  $\Delta_P$  in case of finite opamp gain.

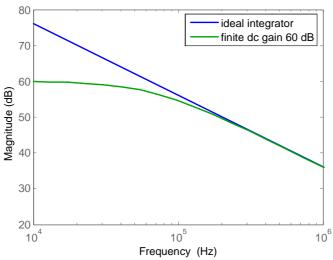

Fig. 2.25. Bode diagram of a DT-integrator with finite DC gain. The pole is not at DC like in the ideal case (blue)

This pole shift has directly an effect on the NTF of the modulator and hence on the quantization noise suppression. Remembering that the zeros of the NTF are the poles of the loop filter (sect. 2.5.1), we can deduce that a pole shift of the integrator causes a worsening of the noise suppression by shifting the zero of the NTF.

Also other opamp non-idealities modify the TF of the integrator and, in turn, worsen the suppression of the quantization noise. The finite bandwidth of the opamp, for example, slows down the process of charge transfer in the integration phase, thus causing an error on the final voltage across the integration capacitance  $C_I$ . The same happens in case of finite slew rate of the opamp with the important difference that the opamp does not work as a linear amplifier. These errors will not be examined in the present work, for an extensive explanation the reader can refer to [Fer06].

The non-idealities of the analog devices described so far directly affect the noise transfer function of the modulator introducing error terms and affecting the suppression of the quantization noise. In particular, cascaded modulators are very sensitive to the mismatch between the analog and digital TF and great attention must be paid when designing opamp for cascaded topologies.

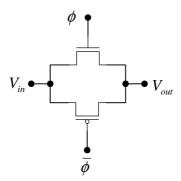

### 2.8.1.2. Switches

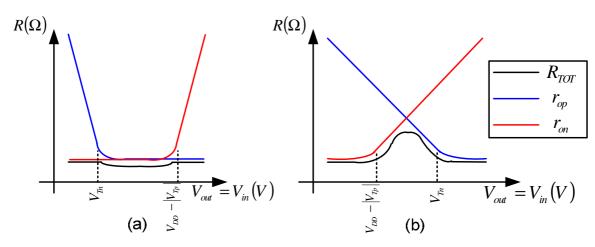

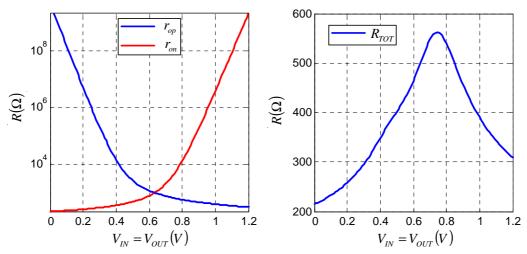

A critical aspect of DT modulators in modern sub-µm technologies is the relatively poor quality of switches, which are realized with MOS transistors. The trend of the last years [Pek04] shows that the reduction of the threshold voltage for new technology nodes has been slower than that of the supply voltage. As a consequence, the overdrive voltage which can be applied to the switches is becoming smaller, making it difficult to bias conducting switches in strong inversion. This means a progressive increase in the on-resistance of the conducting switches, hence slower sampling and also non-linearities because of the dependence of the resistance on the input signal. In order to make the on-resistance less dependent on the signal, transmission gates can be used, realized with an nmos and a pmos transistor in parallel as shown in Fig. 2.26.

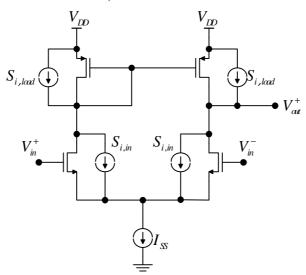

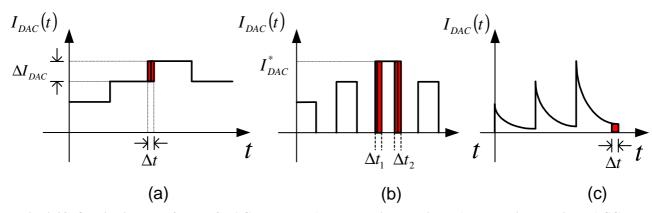

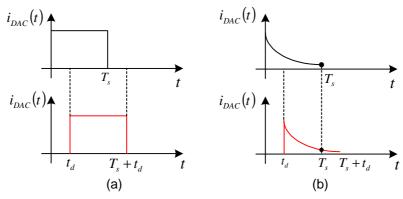

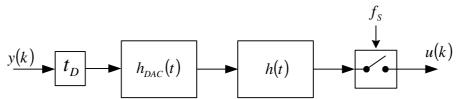

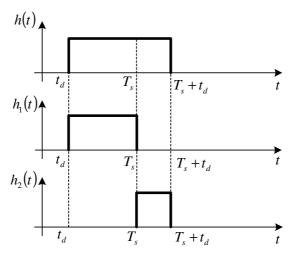

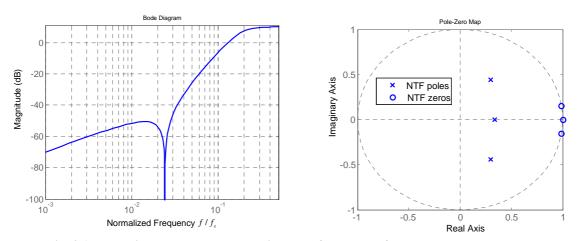

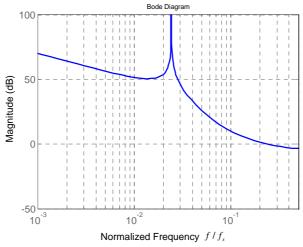

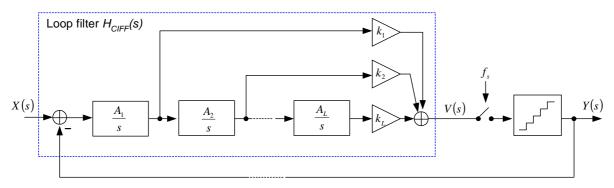

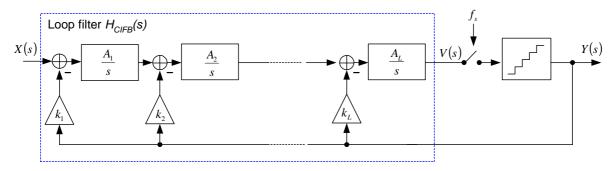

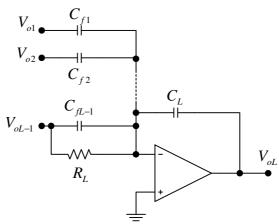

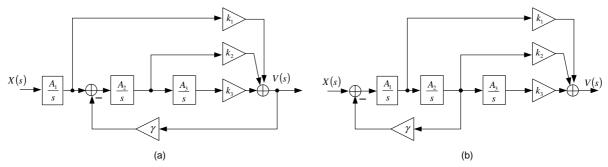

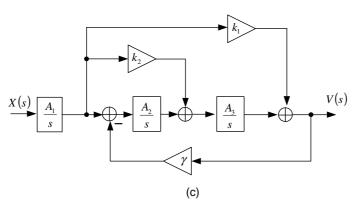

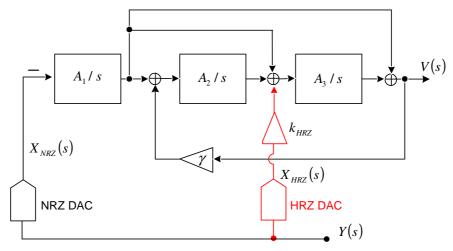

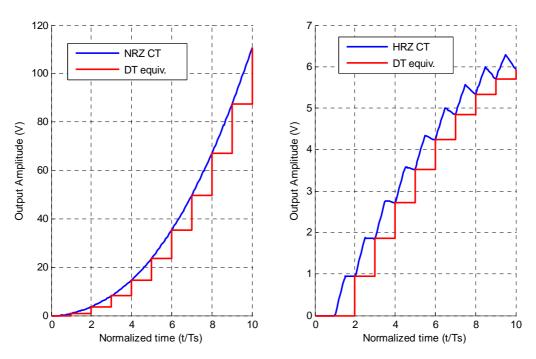

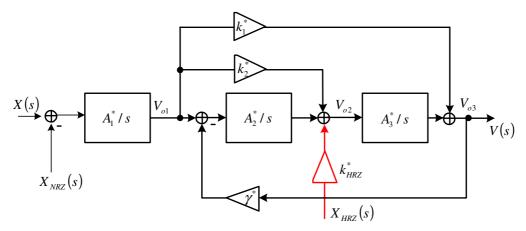

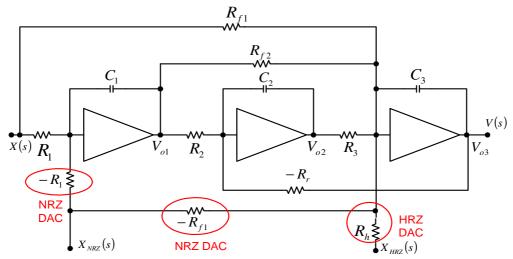

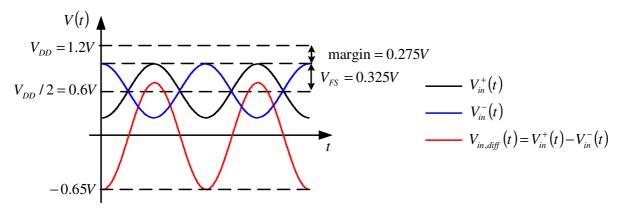

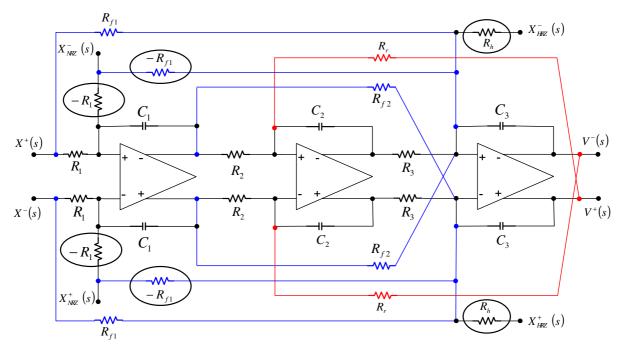

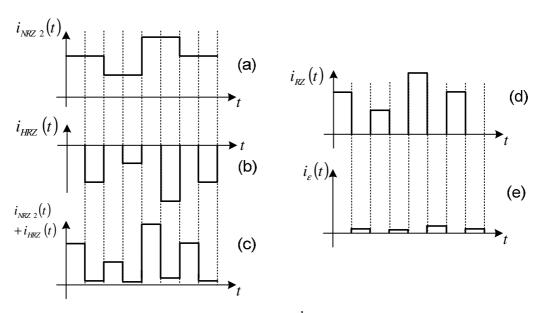

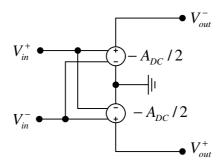

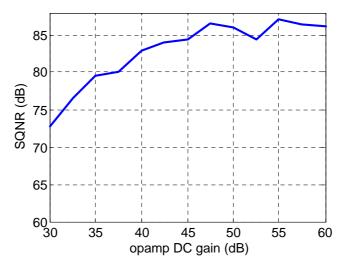

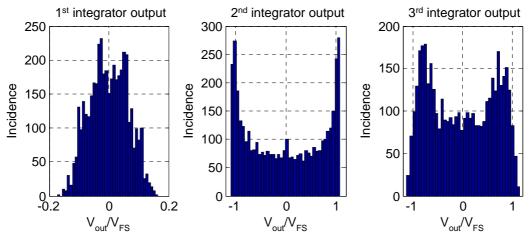

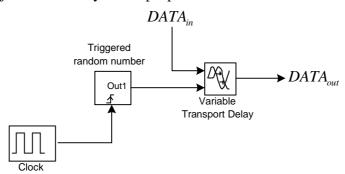

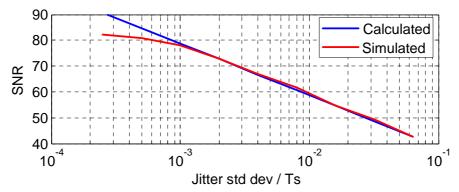

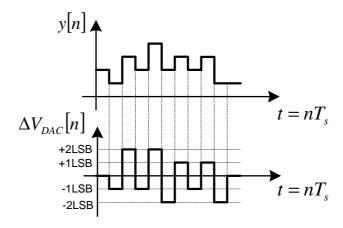

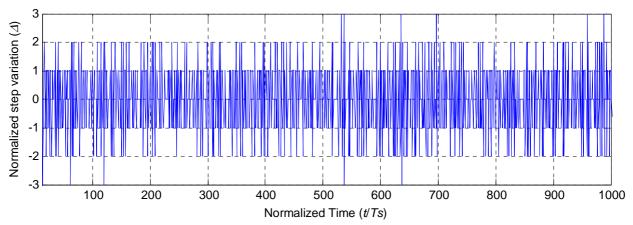

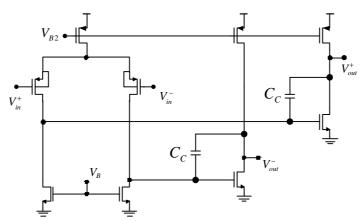

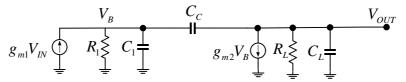

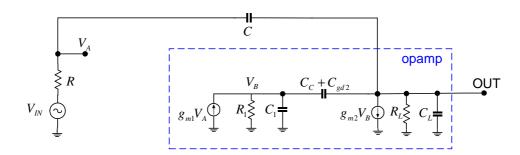

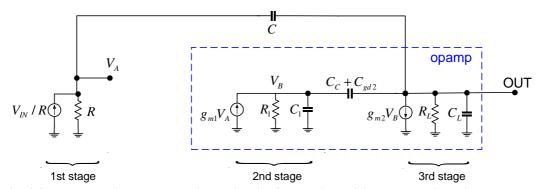

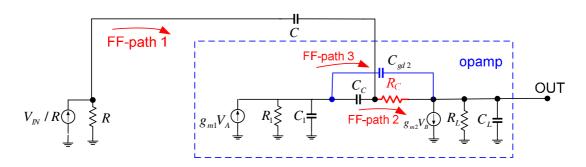

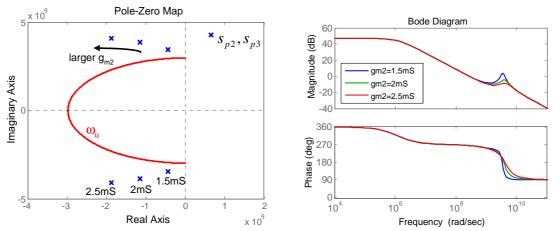

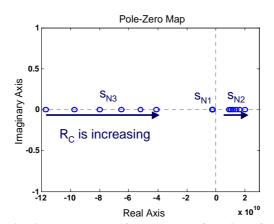

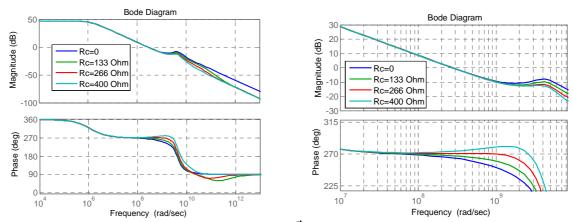

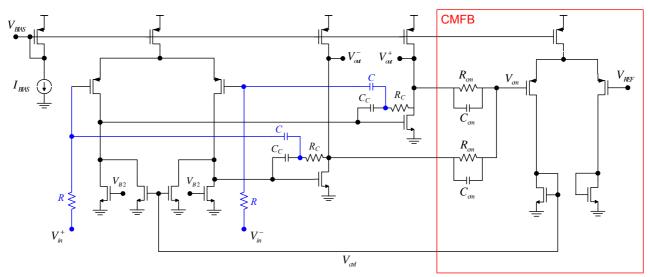

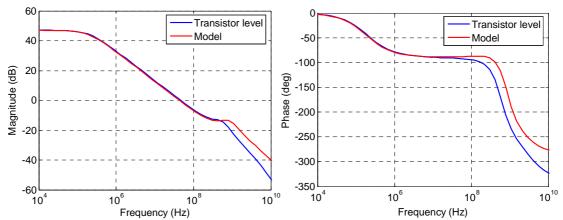

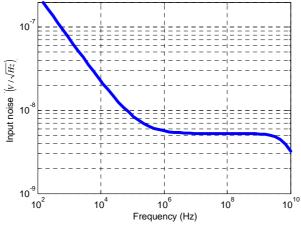

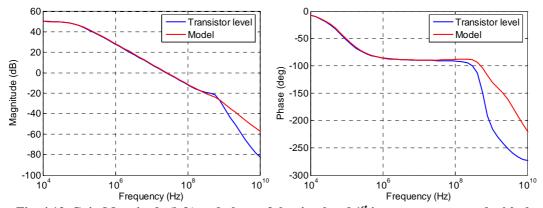

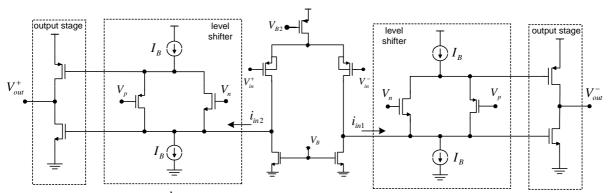

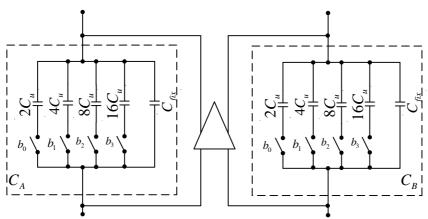

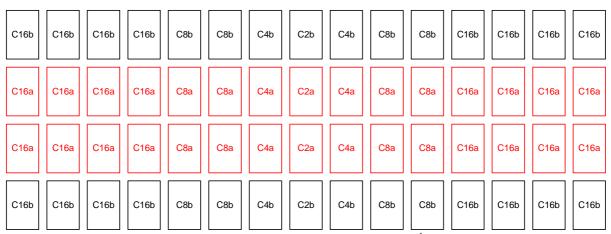

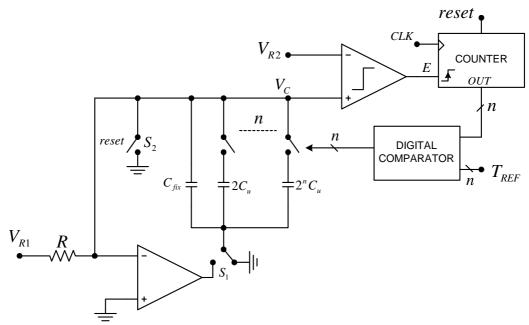

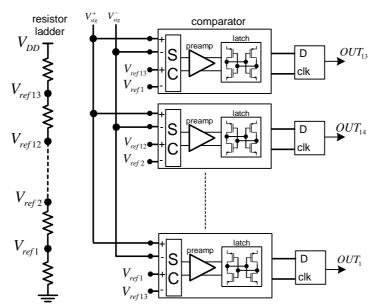

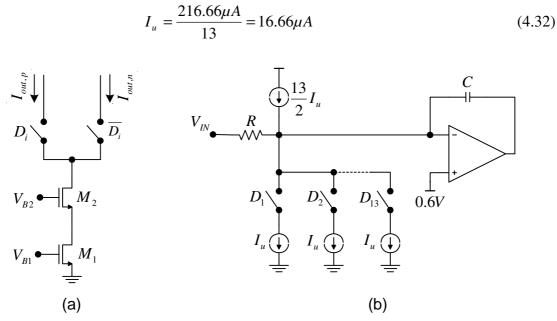

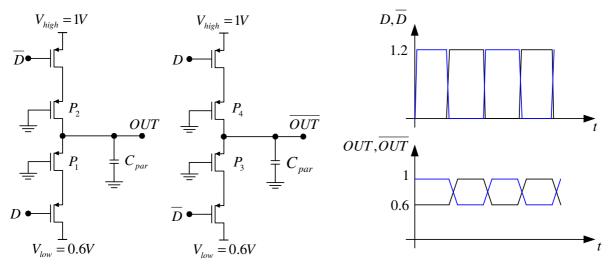

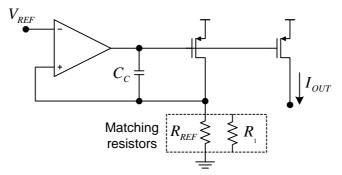

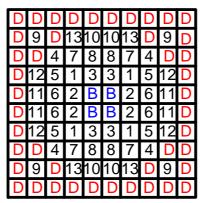

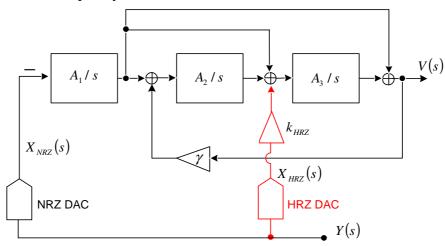

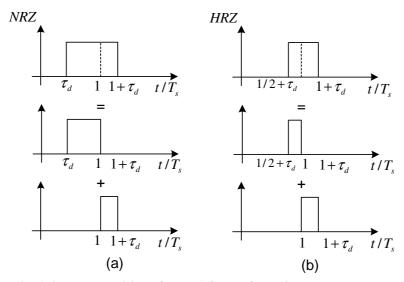

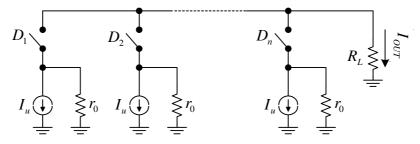

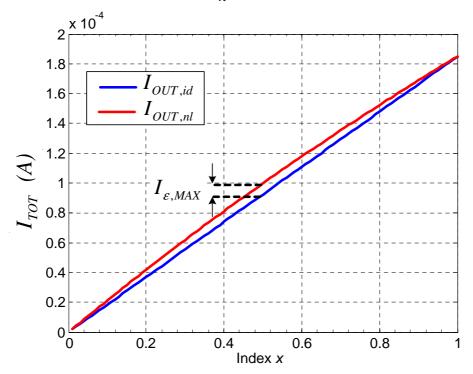

Fig. 2.26. Transmission gate schematic