## An Analysis on a Pseudo-Differential Dynamic Comparator with Load Capacitance Calibration

M<sub>13</sub>

Mo

Department of Physical Electronics, Tokyo Institute of Technology Daehwa Paik, Masaya Miyahara, and Akira Matsuzawa paik@ssc.pe.titech.ac.jp

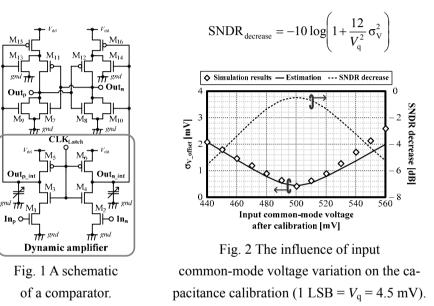

Abstract This paper analyzes a pseudo-differential dynamic comparator with a dynamic pre-amplifier as shown in figure 1. The transient gain of a dynamic pre-amplifier is derived and well matched with the simulation results. Based on the calculated gain, a load capacitance calibration method is analyzed. This analysis well estimates input-referred compensated voltage of each digital calibration code. The influence of PVT variation is also figured out. This analysis shows a dynamic comparator is sensitive to input common-mode voltage variation as shown in figure 2. The analyzed comparator uses 90-nm CMOS technology as an example.

Acknowledgments This work was partially supported by MIC, CREST in JST, NEDO, Berkeley Design Automation for the use of the Analog FastSPICE(AFS) Platform, and VDEC in collaboration with Cadence Design Systems, Inc.