### University of Texas at El Paso DigitalCommons@UTEP

**Open Access Theses & Dissertations**

2013-01-01

## Anasic Design And Test Methodology For An Undergraduate Design And Fabrication Project

Arun Joseph Kurian University of Texas at El Paso, akurian@miners.utep.edu

Follow this and additional works at: https://digitalcommons.utep.edu/open\_etd Part of the <u>Computer Engineering Commons</u>, and the <u>Electrical and Electronics Commons</u>

**Recommended** Citation

Kurian, Arun Joseph, "Anasic Design And Test Methodology For An Undergraduate Design And Fabrication Project" (2013). Open Access Theses & Dissertations. 1856. https://digitalcommons.utep.edu/open\_etd/1856

This is brought to you for free and open access by DigitalCommons@UTEP. It has been accepted for inclusion in Open Access Theses & Dissertations by an authorized administrator of DigitalCommons@UTEP. For more information, please contact <a href="https://www.uee.org">www.uee.org</a> UTEP. It has been accepted for inclusion in Open Access Theses & Dissertations by an authorized administrator of DigitalCommons@UTEP. For more information, please contact <a href="https://www.uee.org">www.uee.org</a> UTEP. It has been accepted for inclusion in Open Access Theses & Dissertations by an authorized administrator of DigitalCommons@UTEP. For more information, please contact <a href="https://www.uee.org">www.uee.org</a> UTEP. For more information, please contact <a href="https://www.uee.org">www.uee.org</a> Utep://www.uee.org</a>

# ANASIC DESIGN AND TEST METHODOLOGY FOR AN UNDERGRADUATE

## DESIGN AND FABRICATION PROJECT

Arun Joseph Kurian, MSCE

Department of Electrical and Computer Engineering

APPROVED:

Eric MacDonald, Ph.D.

John Moya, Ph.D.

Ryan B. Wicker, Ph.D.

Benjamin C. Flores. Dean of the Graduate School Copyright ©

by

Arun Joseph Kurian

2012

Dedication

To My Parents and Friends

## AN ASIC DESIGN AND TEST METHODOLOGY FOR AN UNDERGRADUATE DESIGN AND FABRICATION PROJECT

by

Arun Joseph Kurian, MSCE

#### THESIS

Presented to the Faculty of the Graduate School of

The University of Texas at El Paso

in Partial Fulfillment

of the Requirements

for the Degree of

#### MASTER OF SCIENCE

Department of Electrical and Computer Engineering

THE UNIVERSITY OF TEXAS AT EL PASO

DECEMBER 2012

#### ACKNOWLEDGEMENTS

I would like to thank my graduate thesis advisor Dr. Eric MacDonald for giving me the opportunity to work in the field I am most passionate about: Digital Circuit Design. I could have never asked for a better major advisor. Dr. MacDonald has not only expanded my skills in VLSI area but has elevated my confidence to do well in my professional endeavors. Thank you Dr. MacDonald, I will always be grateful for everything you have done for me.

Also, I would like to extend my most humble gratitude to my team inIntelFolsom, California who gave me an opportunity for internship. This was a great motivating experience to complete my studies and get back to working again.

Additionally, I wish to give my sincere thanks to members of UTEP's ASICS Lab for their support and interest in this research. In particular, I would to thank Praveen Palakurthi not only for his welcomed suggestions and endless assistance, but for making me feel I was not alone in the intricate but rewarding field of Digital Circuit Design.

I am also compelled to recognize that without the assistance of the UNIX systemadministrators and the staff from the ECE Dept. I would have never completed my work.

ToDr. Moya, I am obliged for his academic instruction, for his professional advice, and for motivating me to never quit. ToDr. Wicker I am truly grateful for taking a sincere interest in my thesis topic and for highlighting areas of improvement.

Finally, I would like to thank my family and friends who have always believed that I can accomplish my goals. My parents, and my brotherTharunare everything to me and I would never be here, without their support.

#### ABSTRACT

During the 1990's the main focus of chip design methodologies was on the timings and area constraints. Power consumption was considered significant only after a drastic increase of device densities from 130nm on as well as dramatic increases in sub threshold leakage. As technology advanced from 130nm to 90nm and below there was a significant increase in leakage current due to lower threshold voltage and the influence of the deep submicron effects. High power consumption causes different problems such as increasing the cost of the product, reducing the reliability, reducing the battery life among others. Therefore EDA tools were designed to maximize the speed while minimizing area and only recently focused on improving power.

The main objective of this thesis is to complete a study of an ASIC (Application Specific Integrated Circuit) design and test flow to establish a full design methodology for an undergraduate class chip design and fabrication project from Verilog RTL to GDS2 for fabrication. The tools includeSynopsys Design Compiler to generate a netlist of the physical design and Synopsys IC Compiler to perform the placement and optimization followed by clock tree synthesis, routing and lastly corechecking. The core is then inserted and connected with the chip pad frame using Synopsys Custom Designer. The final chip GDS generated will be sent to Mosis for fabrication. The Verification of the final chip design will be done usingCadenceVirtuoso. This project gives an overview of different steps in the development of an ASIC, front end and back end design using Synopsys Design Compiler and IC compiler flow. In this thesis a simple 8 bit counter is considered as an example.

This Thesis will provide the students with familiarity with the current industry standard tools from vendors like Synopsys and Cadence and thestudents will be well versed with acomprehensive ASIC design flow. The final design will be sent to Mosis for fabrication and the student teams will have working silicon in their hands with five packaged chip per project the demonstration of which will be beneficial when interviewing for a job in the chip industry.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                  | V    |

|---------------------------------------------------|------|

| ABSTRACT                                          | VI   |

| TABLE OF CONTENTS                                 | VIII |

| LIST OF FIGURES                                   | X    |

| CHAPTER 1: INTRODUCTION                           | 1    |

| 1.1 WHAT IS AN ASIC?                              | 1    |

| 1.2 Types of ASICs:                               | 1    |

| 1.2.1 Full Custom ASICs:                          | 2    |

| 1.2.2 Semi-Custom ASICs:                          | 3    |

| 1.2.3 Standard Cell ASICs:                        | 3    |

| 1.2.4 Gate Array ASICs:                           | 3    |

| 1.2.5 Programmable ASICs:                         | 5    |

| 1.3 CHAPTER ORGANIZATION                          | 7    |

| CHAPTER 2: BACKGROUND AND MOTIVATION              | 8    |

| 2.1 DIGITAL CIRCUIT DESIGN:                       | 8    |

| 2.3 DIGITAL LOGIC BASICS                          | 9    |

| 2.4 IMPLEMENTATION OF GATES                       | 9    |

| 2.5 PROPAGATION DELAYS:                           |      |

| 2.6 POWER CONSUMPTION IN DIGITAL CIRCUITS         | 11   |

| 2.7 Low Power Synthesis:                          | 12   |

| 2.8PLACEMENT ALGORITHMS:                          |      |

| 2.9 Static Timing Analysis:                       |      |

| 2.10 Power Estimation and Reduction:              | 14   |

| CHAPTER 3: LOGIC SYNTHESIS                        | 15   |

| 3.1 IMPORTANT DC PARAMETERS:                      | 16   |

| 3.2 DESIGN OBJECTS:                               | 17   |

| 3.3 Design Entry                                  |      |

| 3.4 TECHNOLOGY LIBRARY:                           | 19   |

| 3.5 DESIGN ATTRIBUTES AND CONSTRAINTS:            | 19   |

| 3.5.1 Design Attributes:                          | 20   |

| 3.5.2 Design Constraints:                         |      |

| CHAPTER 4: SYNTHESIS OPTIMIZATION TECHNIQUES      | 24   |

| 4.1 MODEL OPTIMIZATION:                           | 24   |

| 4.1.1 Resource Allocation:                        | 24   |

| 4.1.2 Common sub-expressions and Common factoring |      |

| 4.1.3   | Removing Redundant Code                         |    |

|---------|-------------------------------------------------|----|

| 4.1.4   | 0                                               |    |

| 4.1.5   | 0                                               |    |

| 4.1.6   |                                                 |    |

| 4.2     | OPTIMIZATIONS USING DESIGN COMPILER:            |    |

| 4.2.1   | Compile the design                              |    |

| 4.2.2   | Flattening and structuring                      |    |

| 4.2.3   | Removing hierarchy                              |    |

| 4.2.4   | Optimizing for Area                             |    |

| 4.3     | TIMING ISSUES:                                  |    |

| 4.3.1   | Compilation with map_effort high                |    |

| 4.3.2   | Group critical paths and assign a weight factor |    |

| 4.3.3   | Register balancing                              |    |

| 4.3.4   | Choose a specific implementation for a module   |    |

| 4.3.5   | Balancing heavy loading Designs                 |    |

| СНАРТЕ  | R 5: IC COMPILER                                |    |

| 5.1     | Floor Planning:                                 |    |

| 5.2     | Concept of Flattened Verilog Netlist            |    |

| 5.3     | PLACEMENT                                       | 45 |

| 5.4 Clo | OCK TREE SYNTHESIS                              |    |

| 5.5     | ROUTING                                         | 49 |

| СНАРТЕ  | R 6: FULL METHODOLOGY                           | 51 |

| 6.1     | Design Compiler                                 | 51 |

| 6.2     | IC_COMPILER:                                    |    |

| 6.3     | Custom designer:                                | 61 |

| СНАРТЕ  | R 7: CONCLUSION AND FUTURE WORK                 | 75 |

| REFERE  | NCES                                            | 76 |

| APPEND  | DIX B SYNTHESIS TCL SCRIPT                      |    |

| APPENE  | DIX C PLACE AND ROUTE TCL SCRIPT                |    |

| VITA    |                                                 |    |

## LIST OF FIGURES

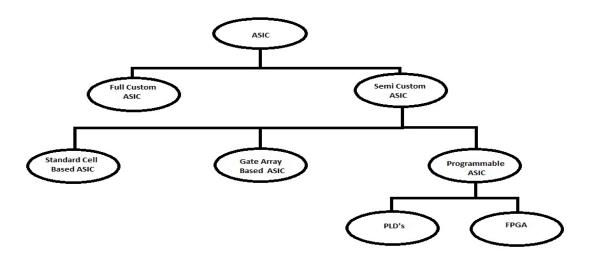

| FIGURE 1: TYPES OF ASICS                             | 2  |

|------------------------------------------------------|----|

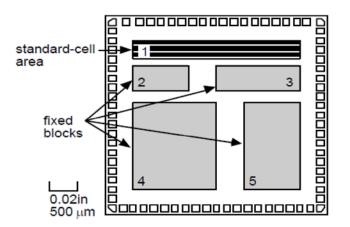

| FIGURE 2: STANDARD CELL BASED ASIC                   | 3  |

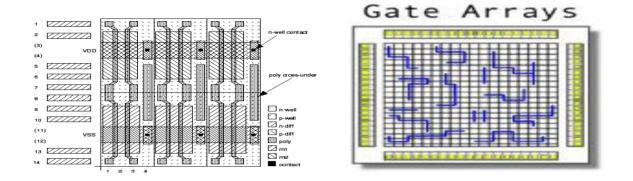

| FIGURE 3: GATE ARRAY ASIC                            | 4  |

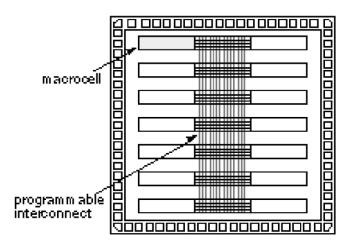

| FIGURE 4: PLD                                        | 5  |

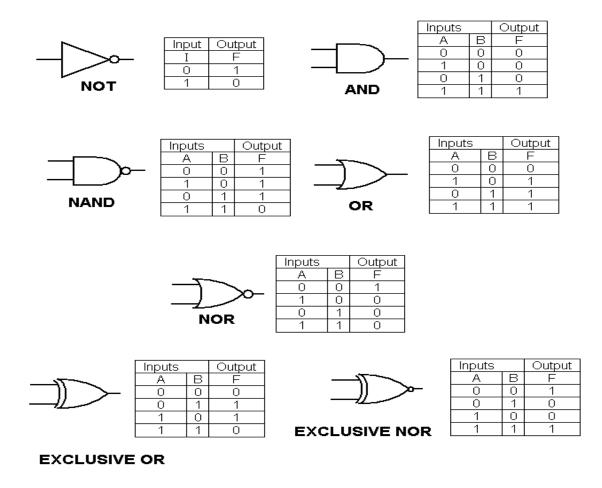

| FIGURE 5: GATE TRUTH TABLE                           | 9  |

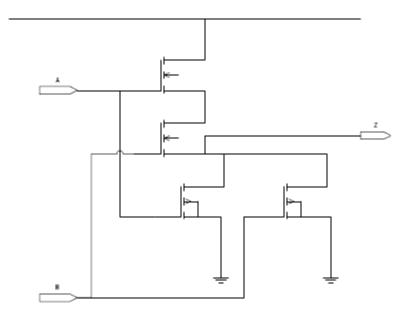

| FIGURE 6: NOR GATE USING TRANSISTORS                 |    |

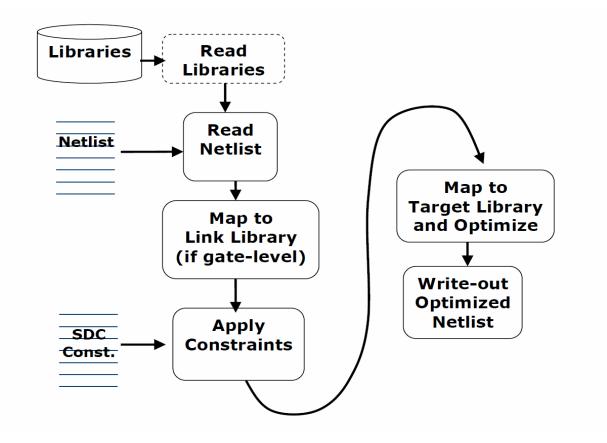

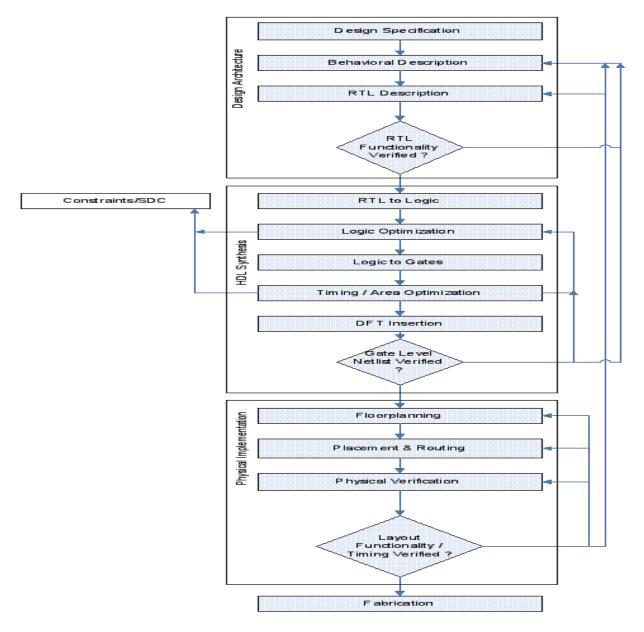

| FIGURE 7: SYNTHESIS FLOW                             | 16 |

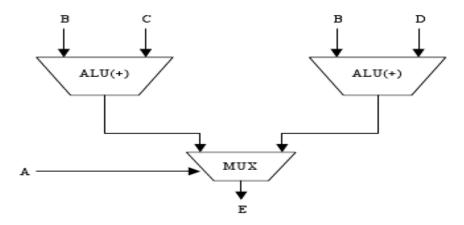

| FIGURE 8: BAD RESOURCE ALLOCATION                    | 25 |

| FIGURE 9: GOOD RESOURCE ALLOCATION                   |    |

| FIGURE 10: SYNTHESIS WITHOUT PARENTHESIS             |    |

| FIGURE 11: SYNTHESIS WITH PARENTHESIS                |    |

| FIGURE 12: SETUP AND HOLD TIMES                      |    |

| FIGURE 13: ASIC DESIGN FLOWCHART                     |    |

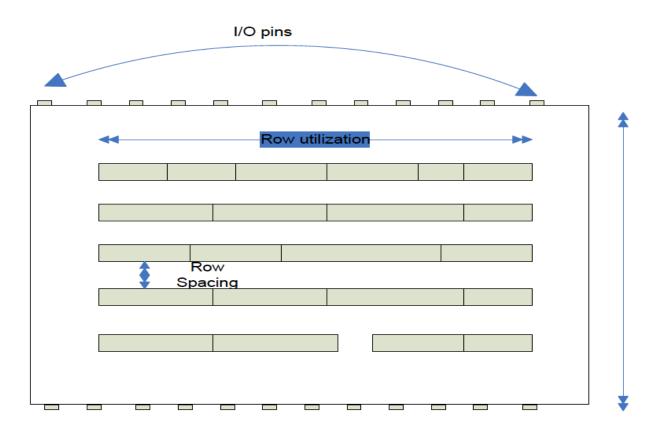

| FIGURE 14: FLOOR PLAN EXAMPLE                        |    |

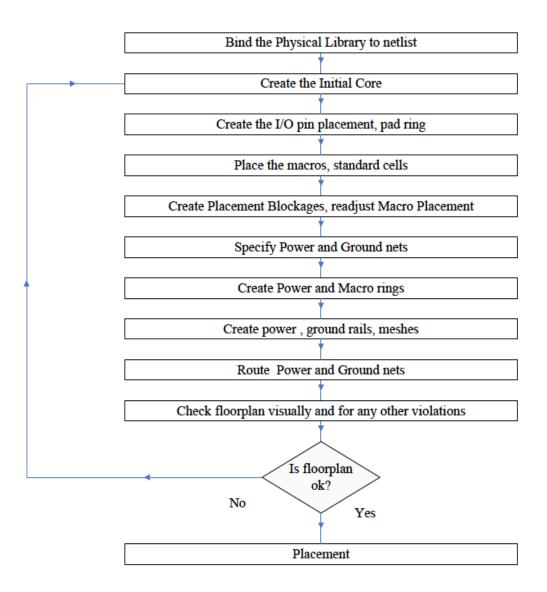

| FIGURE 15: FLOOR PLANNING FLOWCHART                  | 45 |

| FIGURE 16: CLOCK TREE SYNTHESIS STRATEGY             | 47 |

| FIGURE 17: CLOCK DISTRIBUTION LEVELS                 |    |

| FIGURE 18: WAVEFORM 1                                |    |

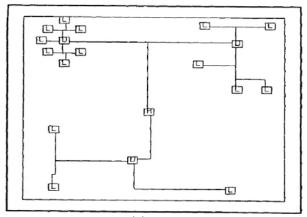

| FIGURE 19: FLOOR PARTITIONED INTO GCELLS             |    |

| FIGURE 20: DESIGN COMPILER INVOKE                    | 51 |

| FIGURE 21: IC COMPILER DESIGN IMPORT                 |    |

| FIGURE 22: FLOOR PLAN CREATION                       | 53 |

| FIGURE 23: POWER RING CREATION                       | 54 |

| FIGURE 24: : METAL LAYERS                            | 55 |

| FIGURE 25: PLACEMENT OF CELLS                        | 56 |

| FIGURE 26: ADDING POWER STRAPS                       |    |

| FIGURE 27: INSERTING CLOCK TREE                      |    |

| FIGURE 28: ROUTING                                   | 59 |

| FIGURE 29: ADDING FILLS                              | 60 |

| FIGURE 30: CREATING NEW LIBRARY                      | 61 |

| FIGURE 31: COPYING CONTENTS TO NEWLY CREATED LIBRARY |    |

| FIGURE 32: ADDING THE PAD FRAME TO THE NEW LIBRARY   | 63 |

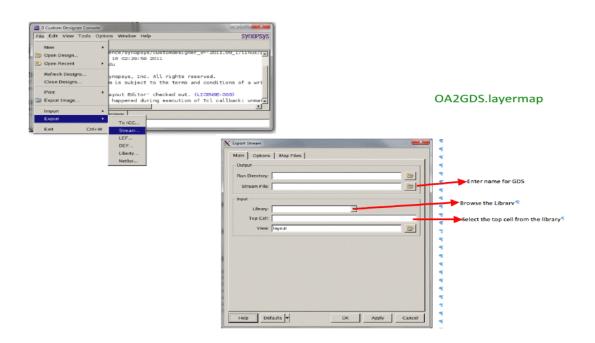

| FIGURE 33: IMPORT GDS (MAIN)                         | 64 |

| FIGURE 34: IMPORT GDS (LAYER MAP FILE)               | 64 |

| FIGURE 35: CREATING SYMBOL AND SCHEMATIC (MAIN)      | 65 |

| FIGURE 36: CREATING SYMBOL AND SCHEMATIC (OPTIONS)   | 66 |

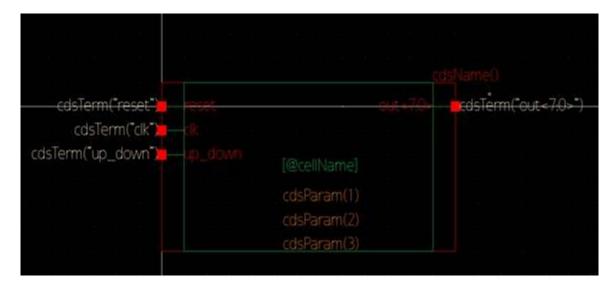

| FIGURE 37: SYMBOL CREATED                            |    |

| FIGURE 38: SCHEMATIC CREATED                         |    |

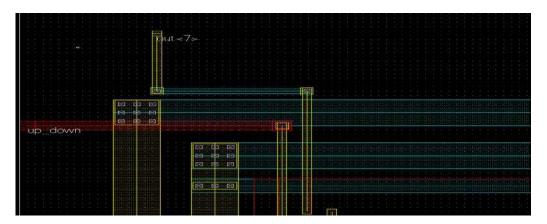

| FIGURE 39: CORE PORTS                                | 68 |

| 9 |

|---|

| 0 |

| 1 |

| 1 |

| 2 |

| 3 |

| 4 |

| ( |

#### **CHAPTER 1: INTRODUCTION**

#### 1.1 What is an ASIC?

Integrated circuits are usually fabricated on silicon wafers with the wafer containing hundreds of dicestructures. ASIC stands for Application Specific Integrated Circuit and an IC designed for a specific application while using standard cell library is referred to an ASIC. Examples of ASICS include chips designed for satellites, chips designed for automotive systems, and chips designed as interfaces between memory and CPU on a personal computer. Examples of IC's which are not ASIC include memories, microprocessors etc.

#### 1.2 Types of ASICS

ASICS are categorized based on the technology used for manufacture. The various types are full-custom ASICS and semi-custom and semi-custom can be further classified as standard cell based ICs (CBICs), Gate Array (GA) type.

Figure 1: Types Of ASICS

#### 1.2.1 FULL CUSTOM ASICS

The mask layers are customized in a full-custom ASIC where a majority of the design is done at the transistor level in terms of layout and simulation. Full custom ASICS are designed if there are no standard libraries available or when particular care is required to meet performance or power requirements of an application. The full custom methodology offers the highest performance with the disadvantages of increased design time, complexity, design expense, and highest risk. Microprocessors are generally full-custom, but designers are increasingly turning to semicustom ASIC techniques in this area as well. Other examples of full-custom ASICS are high-voltage automobile, analog/digital (communications), or sensors and actuators.

The disadvantages of full custom ASIC are:

- 1. Design complexity

- 2. Lack of automation in the tools

- 3. Substantial design time

#### 1.2.2 SEMI-CUSTOM ASICS

Semi-custom ASICS are ASICS that are customized in one or two areas. A semi-custom ASIC is manufactured with the masks for the diffused layers already fully defined, so the transistors and other active components of the circuit are already fixed. The customization of the final ASIC product to the intended application is done by varying the masks of the interconnection layers, e.g., the metallization layers.

#### 1.2.3 STANDARD CELL ASICS

A standard cell-based ASIC uses standard cells which are predesigned logic cells (AND gates, OR gates, multiplexers, and flip-flops, for example). The standard-cell areas (also called flexible blocks) in a Standard Cell Based ASIC are built of rows of standard cells. The standard-cell areas may be used in combination with larger predesigned cells like memories or analog circuits.

Figure 2:Standard Cell Based ASIC

#### 1.2.4 GATE ARRAY ASICS

Gate array ASICS are partially finished with rows of transistors and resistors required but the transistors are unconnected. The chip is completed by connecting the required transistors and

resistors with the back-end metal layers. The Gate array is made of "basic cells", where individual cells contain some number of transistors and resistors depending on the vendor. Using a cell library (gates, registers, etc...) and a macro library (more complex functions), the customer designs the chip and the vendor's software generates the interconnection masks.

These final masking stages are less costly than those associated with designing a full-custom ASIC from scratch.

A gate array circuit is a prefabricated circuit with no particular function in which transistors, standard logic gates, and other active devices are placed at regular predefined positions and manufactured on a wafer, usually called **Master Slice**. Creation of a circuit with a specified function is achieved by connecting the required elements using metal layers at the time of manufacture and this can be done on wafers that have already been fabricated with complete transistors (front end) and thus eliminate the amount of time between completing the design and obtaining silicon. The gate array drawbacks are low density and low performance as compared to full custom or standard cell ASICS.

Figure 3: Gate Array ASIC

#### 1.2.5 **PROGRAMMABLE ASICS**

a) PLDs are programmable logic devices that can be used to perform complex functions. PLDs can be programmed for specific applications. PLDs use different technologies to allow programming of the device.

PLDs are having these common features:

- No customized mask layers or logic cells

- Fast design turnaround

- A single large block of programmable interconnect

• A matrix of logic macro cells that usually consist of programmable array logic

followed by a flip-flop or latch.

Figure 4:PLD

b) FPGA (Field Programmable Gate Array) are first developed in the mid of 80's by Xilinx. FPGAs are better in terms of functionality in comparison with PLDs and can be used for more complex and denser designs.

FPGAs are composed of logic blocks instead of unwired transistors.

The core of the FPGA is an array for logic cells that can perform combinational and sequential logic

FPGAs have the following features:

- Less dense than custom mask

- Higher unit cost

- Ready to be used out the box

- Reprogrammable

• In this project, in which a methodology is established to be used in an undergraduate design project, which ends with a free 0.5 micron CMOS fabrication, an FPGA-based emulation process is used to evaluate and validate a design written in Verilog – similar to the approach taken by industry. This significantly reduces the risk of the chip design being fabricated that is wrong.

Application Specific Integrated Circuits (ASICS) and Field Programmable Gate Arrays (FPGAs) are different types of custom chips, which differ in their properties, cost, and manufacturing process. The choice of which to use depends on the required application and its requirements and in some applications, FPGAs are used to prototype a design given the low NRE expense, but are replaced in production by ASICS to improve the per device costs [2].

Older style ASICS were of gate array type which consisted of unconnected transistors. The most common type of ASIC currently used is the standard cell based ASIC which accounts for most digital logic fabricated today. Many electronics companies with a core competency outside of the chip industry (e.g. routers, cell phones, graphics processing) can design customized chips with the

standard cell library and fabricate the chips at a silicon foundry. Examples of such fab-less companies include NVidia or Qualcomm and this business model is gaining popularity given the huge costs associated with silicon manufacturing and the availability of reliable and inexpensive foundry services. The most popular foundry services are now located in Taiwan and China with companies like the Taiwanese Semiconductor Manufacturing Company or Universal Manufacturing Company. Companies like IBM and Texas Instruments in the USA also provide these services generally providing better performance but at an increased cost per die [2].

#### **1.3 Chapter Organization**

The focus of this thesis is to develop a methodology to generate chips at an education level for undergraduatesusing standard industry EDA tools by vendors like Synopsys and Cadence. The remainder of this thesis is organized as follows:In chapter 2 the main focus is on how this new ASIC design methodology has made the whole process of chip production fast, easy and efficient. The chapter also discusses digital logic basics defining terms like propagation delays with a brief description of the power consumption in digital circuits. Chapter 3focuses mainly on the tool Design Compiler (DC) by Synopsys used for the synthesis of RTL. Chapter 4 mainly talks about the synthesis optimization techniques that could be used for improving area and speed of the final chip.Chapter5 describes focuses on the tool IC Compiler by Synopsys which is used mainly for the place and route operation to generate the final core of the chip in design. Inchapter 6 the methodology used is discussed.Chapter 7 provides the conclusion and future work. Appendix A lists the Verilog code for the simple 8 bit counter used to test the methodology. Appendix B shows the synthesis TCL script that was used. Appendix C lists the IC Compiler TCL script that was used for design place and route operation.

#### **CHAPTER 2: BACKGROUND AND MOTIVATION**

The main motivation behind this project was to provide the undergraduate students with a familiarity with the chip design process to help the students complete the entire chip design process starting from writing the RTL to fabricating the silicon. The finals designs will be sent to MOSIS for fabrication and with the final silicon in hand will be a great asset for discussion in job interviews and securing a job or finding future research opportunities depending on their interests. Power of the designed and fabricated chips will be evaluated in a subsequent semester upon arrival of the silicon hardware.

#### 2.1 Digital Circuit Design

Digital circuit design prior to the last two decades involved developing schematics for the required functions, which required selecting the right gates and making the required connections. This method is slow, tedious and prone to error. An alternative that was developed was to use a Hardware Descriptive language (HDL) to describe the behavior or a design - the two most commonly used HDLs are VHDL and Verilog. The designs can be created much more rapidly, and the only errors are likely to be with the logic design, as opposed to the implementation – such as incorrectly connected gates.HDLs can be compiled using compilers for simulation and testing requirements. Once the design is believed to function correctly synthesis is performed to get a form required by the FPGA or ASIC. The resulting output is analyzed for real time performance and can be refined and recompiled for a better design in the future. This process can be iterative.

#### 2.3 Digital Logic Basics

While most of the optimization is done by the synthesis tools, knowledge of the basic logic gates is still required to understand the synthesis process and optimization methods.

Figure 5: Gate truth Table

#### 2.4 Implementation of gates

Individual gates are built using transistors and the characteristics of the gate depend on the type and configuration of transistors used. For example, the CMOSimplementation of a NOR gate could be represented by figure:

Figure 6: NOR Gate using transistors

Since these circuits are built from transistors, logic gates inherit a number of characteristics that areimportant to digital design:

• Transistors have capacitance which affects the speed and power dissipation of the device [2].

• Transistors consume current through their input transitions and provide a limited amount of power at the output pins [2]. Therefore the drive strength is limited. This number referred to asthe fan-out of the gate and is usually less than 20.

#### 2.5 Propagation delays

In response to changes to the inputs, outputs of the logic gates change after a certain time known as the propagation delay. This is caused due to the time taken to charge and discharge the internal and load capacitances and different transistor configurations also give different delays.

In a large circuit there are a large number of gates and the propagation delay will be the sum of the propagation delays of the gates thorough which the signal passes. The path that has the highest delay is known as the critical path for the circuit. Optimizing this path is the central objective of Static Timing Analysis (STA) which is the critical feedback mechanism for logic synthesis as well as a final check required before fabrication [2].

#### 2.6 Power Consumption in Digital Circuits

Power consumption is an important issue while designing chips. Increased power consumption may result in thermal challenges. From a commercial stand point, the lower power consuming products are more competitive particularly in terms battery life in portable applications. Two main categories of power consumption are:

- Static power: This is the power used by a logic gate when the logic is held constant. Leakage current is the component contributing to subthreshold as well as gate oxide tunneling current. This component is becoming a larger and larger fraction of the total power as the threshold voltage of the transistors is decreasing (leakage increases 10x for 70mV drop in the threshold voltage) to match the decreases in the supply voltage. The gate oxides are dropping below 25 angstroms in thickness thus allowing for additional Fowler Nordheim Tunneling resulting in additional leakage current [2].

- **Dynamic power:** This is the power consumed by the logic gate when anode changes states. This Dynamic power is caused due to the switching current generating the change and due to the charging and discharging of the gates capacitance to generate the required modification in voltage level [2].

Dynamic power is more significant and can be influenced by the logic design. Minimizing the number of transistors will minimize the power consumptionas well as reducing the functionality of the chip. There are other ways in which this can be attempted:

- **Disabling unused parts of the circuit:** An AND gate can be provided at the inputs with one input connected to an enable signal. The entire circuit can be kept static with the enable signal kept low by reducing input transitions [2].

- **Reducing glitches in a circuit:** A glitch is a temporary change in the signal level before the final value is reached. These can be avoided by using the right logical arrangement and timing can reduce power consumption. Glitches are normal and not a functional concern as long as static timing requirements are met [2].

#### 2.7 Low Power Synthesis

The advent of portable devices has made low power circuit design an important research area. High power consumption increases heat dissipation and reduces the reliability of complex modern circuits with high transistor counts and fast clock rates. In CMOS the large portion of power dissipation is due to dynamic power consumption [18]. Till now power reduction has been mainly dealt with by reducing the gate switching frequency. But in reality gates have delay resulting in glitch transition that contributes to about 30% of the power consumption [5].

Typical approach in low power synthesis is to first generate a multilevel AND-OR or NAND-NOR representation of logic function. Next this representation is optimized for power. AND-XOR logic is more compact than their boolean counterparts in terms of layout area. However conventional optimization of XOR yield poor results [6].

Primary method used to reduce power is by voltage reduction. However voltage reduction below 1 volt begins to create problems. Under these situations the design and automation tools play a crucial role. In the past decades wide variety of solutions have been come up with to solve these this problem which includes RTL power management and multiple voltage assignment, to poweraware logic synthesis and physical design, to memory and bus interface design [7].

#### 2.8 Placement Algorithms

The general nature of CMOS technology encourages the use of "gate-matrix" or "strip based" layout design style. In this style the cells are formed by two horizontal strips of diffusion with vertical poly silicon strips running between them. In a well fit design the source of one FET will become the drain of the next with the diffusion unbroken. If the circuit used different nets for the FETs then it is necessary to isolate them with a gap. To minimize the area the number of gaps need to be reduced. This is a difficult problem because search-space of possible FET ordering is large [8].

The automated tools that do the placement operation play a crucial role in transforming the circuit description into a physical description. Placement operation is divided into an initial placement phase followed by an iterative placement improvement phase. The objective of the initial placement phase is to minimize the area and wire length. An iterative placement phase is required to optimize placement as all the information is not available during the initial placement phase [9].

Placement algorithms are classified into two categories: Constructive and iterative types. Constructive algorithm takes in modules and a netlist defining the interconnection between the modules. The input to the iterative algorithm is the initial placement phase [10].

#### 2.9 Static Timing Analysis

Due to aggressive technology scaling and limits on the optical lithography the gap between the design phase and fabrication phase is increasing leading to performance offsets between the designed and fabricated specifications. Static Timing Analysis (STA) helps in determining the circuit performance so that the circuit can be designed for extreme conditions [11].

Traditional static timing analysis is becoming insufficient to accurately evaluate the process variation impact on designs performance considering increase in the variable parameters like power supply voltage temperature corners. The use of a novel approach called statistical static timing analysis helps to overcome these issues with traditional STA. However this novel approach needs costly additional data such as an accurate process variation information, and a statistical standard cell library characterization. STA tools can be used to estimate path delays. This helps in finding the worst case path in a circuit which is a critical information governing the speed of a circuit. There are various techniques to determine this information. During this calculation false paths in a design must be eliminated and only delays of true paths must be calculated using the various proposed methods [12].

#### 2.10 Power Estimation and Reduction

Power estimation and reduction is becoming a critical area for ASIC designers. Reducing both the leakage and dynamic power is important to make the product more commercially viable. Major power reductions are only possible at RTL and system levels. At this level sequential modifications can be made via techniques like sequential clock gating, power gating, voltage/frequency scaling and other micro-architectural techniques [15]. Without accurate power estimation power reduction cannot be done at optimal levels. Various RTL power estimation tools have been proposed. The increase in circuit sizes and complex effects introduced due to deep submicron designs make the task of power estimation very challenging [14].

#### **CHAPTER 3:LOGIC SYNTHESIS**

The Design Compiler [DC] is the synthesis tool from Synopsys. DC takes a RTL [Register Transfer Logic] hardware description [design written in either Verilog/VHDL], and standard cell library as input and outputs a technology dependent gate-levelnetlist. The gate-levelnetlist is the structural representation of only standard cells based on the cells in the standard cell library. The synthesis tool internally performs many steps, which are listed below. Also below is the flowchart of synthesis process.

1) DC reads in technology libraries, DesignWare libraries, and symbol libraries. During the synthesis process, DC translates the RTL description to components extracted from the technology library and DesignWare library. The technology library consists of basic logic gates and flip-flops. The DesignWare library contains more complex cells for example adders and comparators. DC can automatically determine when to use Design Ware components and then efficiently synthesize these components into gate-level implementations.

2) Reads the RTL hardware description written in either Verilog/VHDL.

3) The synthesis tool thenperforms many steps including high-level RTL optimization, RTL to un-optimized boolean logic, technology independent optimizations, and finally technology mapping to the available standard cells in the technology library, known as the target library. This resulting gate-levelnetlist also depends on constrains given by the designer. Constraints are the designer's specification of timing and environmental restrictions [area, power, process etc.] under which synthesis is to be performed.

4) After the optimization process, the design is ready for DFT [design for test/ test synthesis].DFT is test logic that designers can integrate into design during synthesis. This helps the designer to

test for issues early in the design cycle and also can be used for testing the chip once back from fabrication.

5) After test synthesis, the design is ready for the place and route. The place and route tools place and physically interconnect cells in the design. Based on the physical routing, the designer can back-annotate the design and can use Design Compiler again to resynthesize the design for more accurate timing analysis.

Figure 7: Synthesis Flow

#### **3.1 Important DC Parameters**

are:

There are four important parameters that should be setup before one can start using the tool

- **search\_path:** This parameter is used to specify to the synthesis tool the paths that should be searched when looking for a synthesis technology libraryduring synthesis.

- target\_library: The parameter specifies the file that contains the logic cells that should be used for mapping during synthesis.

- **symbol\_library:** This parameter points to the library that contains the "visual" information on the logic cells in the synthesis technology library. Logic cells have a symbolic representation and information about these symbols is stored in this library.

- **link\_library:** This parameter points to the library that contains information about the logic gates in the synthesis technology library. The tool uses this library solely for reference but does not use the cells present for mapping as in the case of target\_library.

#### 3.2 Design Objects

There are eight different types of objects categorized by Design Compiler:

- Design: The design corresponds to the circuit description that performs some logical function. The design may be stand-alone or may include other sub-designs. The sub design can be treated as a different design.

- **Cell**: The cell is the instantiated name of the sub-design in the design. In Synopsys terminology, there is no differentiation between the cell and an instance. They are treated as a cell.

- **Reference**: This is the definition of the original design to which the cell or instance refers.

- **Ports**: These are the primary inputs, outputs of the design.

- Pin: The pin corresponds to the inputs, outputs of the cells in the design.

- Net: These are the signal names, i.e., the wires that connect the design together by connecting ports to pins and/or pins together.

- **Clock**: The port or pin that is identified as a clock source.

- Library: Corresponds to the collection of technology specific cells that the design is targeting for synthesis, or linking for reference.

#### 3.3 Design Entry

Before synthesis, the design must be entered into the Design Compiler (referred to as DC from now on) in the RTL format. DC provides the following two methods of design entry:

- Readcommand

- Analyze& elaborate commands

The analyze & elaborate commands are two different commands, allowing designers to initially analyze the design for syntax errors and RTL translation before building the generic logic for the design. The generic logic or GTECH components are part of Synopsys generic technology independent library. The generic logicis an unmapped representation of boolean functions and serves as placeholders for the technology dependent library.

The **analyze** command also stores the result of the translation in the specified design library that maybe used later. So a design analyzed once need not be analyzed again and can be merely elaborated, thus saving time. Conversely **read** command performs the function of **analyze** and **elaborate** commands but does not store the analyzed results, therefore making the process slow by comparison.

The commands used for the methods in DC are as given below:

#### Read command:

dc\_shell>read -format < format>< list of file names>

#### Analyze and Elaborate commands:

dc\_shell>analyze -format <format><list of file names> .syn file is the file in which the analyzed information of the design analyzed is stored. EX: The adder entity in the adder.vhd has a generic parameter "width" which can be specified during elaboration.

#### 3.4 Technology Library

Technology libraries contain the information that the synthesis tool needs to generate a netlist for a design based on the desired logical behavior and constraints on the design. The tool referring to the information provided in a particular library would make appropriate choices to build a design. The libraries contain information regarding the area of the cell, the input-to-output timing of the cell, constraints on fanout of the cell, and the timing checks that are required for the cell. Other information stored in the technology library may be the graphical symbol of the cell for use in creating the netlist schematic.

The target\_library, link\_library, and symbol\_libraryparameters in the startup file are used to set the technology library for the synthesis tool.

#### 3.5 Design Attributes and Constraints

A designer, in order to achieve optimum results, has to methodically constrain the design, by describing the design environment, target objectives and design rules. The constraints contain timing and/or area information, usually derived from the design specifications. The synthesis tool uses these constraints to perform synthesis and tries to optimize the design with the aim of meeting these constraints.

#### **3.5.1 DESIGN ATTRIBUTES**

Design attributes set the environment in which a design is synthesized. The attributes specify the process parameters, I/O port attributes, and statistical wire-load models. The most common design attributes and the commands for their setting are given below:

Load:Each output can specify the drive capability that determines how many loads can be driven within a particular time. Each input can have a load value specified that determines how slow a particular driver is. Signals that are arriving later than the clock can have an attribute that specifies this fact. The load attribute specifies how much capacitive load exists on a particular output signal. The load value is specified in the units of the technology library in terms of picofarads or standard loads, etc... The command for setting this attribute is given below:

#### set\_load<value><object\_list>

#### EX:dc\_shell>set\_load 1.5 x\_bus

**Drive:** The drive specifies the drive strength at the input port, usually specified as a resistance value. This value controls how much current a particular driver can source. The larger a driver isi.e. 0 resistance, the faster a particular path will be, but a larger driver will take more area, so the designer needs to trade off speed and area for the best performance. The command for setting the drive for a particular object is given below

#### set\_drive<value><object\_list>

EX:dc\_shell>set\_drive 2.7 ybus

#### 3.5.2 DESIGN CONSTRAINTS

Design constraints specify the goals for the design. The twoimportant constraints are area and timing. Depending on how the design is constrained the DC/DA tries to meet the set objectives. Realistic specification is important, because unrealistic constraints might result in excess area, increased power and/or degrading in timing. The basic commands to constrain the design are:

set\_max\_area: This constraint specifies the maximum area a particular design should have. The value is specified in units used to describe the gate-level macro cells in the technology library.

#### EX:dc\_shell>set\_max\_area 0

Specifying a 0 area willresult in the tool prioritizing size over power or performance.create\_clock: This command is used to define a clock object with a particular period and waveform. The –period option defines the clock period, while the –waveform option controls the duty cycle and the starting edge of the clock. This command is applied to a pin or port, object types.

Following example specifies that a port named CLK is of type "clock" that has a period of 40 ns, with 50% duty cycle. The positive edge of the clock starts at time 0 ns, with the falling edge occurring at 20 ns. By changing the falling edge value, the duty cycle of the clock may be altered.

#### EX:dc\_shell>create\_clock -period 40 -waveform {0 20} CLK

• set\_don't\_touch\_network: This is a very important command, usually used for clock networks and resets. This command is used to set a dont\_touchproperty on a port, or on the net. Note setting this property will also prevent DC from buffering the net. In addition, a gate coming in contact with the "don't\_touch" net will also inherit the attribute.

#### EX:dc\_shell>set\_dont\_touch\_network {CLK, RST}

set\_don't\_touch: This is used to set a dont\_touch property on the current\_design, cells, references, or nets. This command is frequently used during hierarchical compilation of blocks for preventing the DC from optimizing the don't\_touch object.

#### EX:dc\_shell>set\_don't\_touchcurrent\_design

• **current\_design**is the variable referencing the current working design. This variable can be set using the **current\_design**command as follows

#### dc\_shell>current\_design<design\_name>

• **set\_input\_delay**: This command specifies the input arrival time of a signal in relation to the clock. This parameter specifies the time taken for the data to be stable after the clock edge. The timing specification of the design usually contains this information, as the setup/hold time requirements for the input signals. From the top-level timing specifications the sub-level timing specifications may also be extracted.

#### EX:dc\_shell>set\_input\_delay -max 23.0 -clock CLK {datain}

#### dc\_shell>set\_input\_delay -min 0.0 -clock CLK {datain}

The CLK has a period of 30 ns with 50% duty cycle. For the above given specification of max and min input delays for the datain with respect to CLK, the setup-time requirement for the input signal datain is 7ns, while the hold-time requirement is 0ns.

• **set\_output\_delay**: This command is used at the output port, to define the time taken for the data to be available before the clock edge. This information is usually is provided in the timing specification.

#### EX:dc\_shell>set\_output\_delay - max 19.0 -clock CLK {dataout}

The CLK has a period of 30 ns with 50% duty cycle. For the above given specification of max output delay for the dataout with respect to CLK, the data is valid for 11 ns after the clock edge.

• set\_max\_delay: This command defines the maximum delay required in terms of time units for a particular path. In general used for blocks that contains combination logic only.

However can also be used to constrain a block that is driven by multiple clocks, each with a different frequency. This command has precedence over DC derived timing requirements.

### EX:dc\_shell>set\_max\_delay 5 - from all\_inputs() - to\_all\_outputs()

• **set\_min\_delay**: This defines the minimum delay required in terms of time units for a particular path. Opposite of the set\_max\_delay command this command has precedence over DC derived timing requirements.

EX:dc\_shell>set\_max\_delay 3 - from all\_inputs() - to\_all\_outputs()

#### **CHAPTER 4: SYNTHESIS OPTIMIZATION TECHNIQUES**

An optimized design is a design that has satisfied the timing and area requirements. This can be done in two stages; one at the code level and the other during synthesis. The code level optimization involves modifications to the RTL and is required to avoid inconsistencies between simulation results before and after modifications.

#### 4.1 Model Optimization

Model optimizations are important as the logic that is generated by the synthesis tool is sensitive to the RTL code that is provided as input. Different RTL codes generate different logic depending on the synthesis tool. The changes made to the RTL can result in an increase or decrease in the number of synthesized gates and change timing characteristics. A logic optimizer results in different endpoints for best area and best speed depending on the starting point provided by a netlist. The different starting points are obtained by modifying the same HDL code using different constructs. Some of the optimizations that are options for a better design are as follows:

#### 4.1.1 **RESOURCE ALLOCATION**

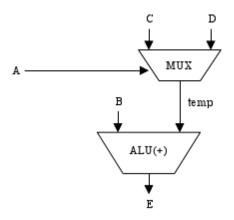

Thefollowingmethod refers to the process of sharing a hardware resource. Consider the following *if* statement:

if A = '1' then E = B + C; else E = B + D; end if; The code above would generate two ALUs one for the addition of B+C and other for the addition B + D.A single ALU can be shared for both the addition operations. The above code would synthesize as follows:

Figure 8: Bad resource allocation

The code above can be rewritten as follows :

if A = '1' then

temp= C; // A temporary variable introduced.

else

temp=D;

end if;

E = B + temp;

Figure 9: Good resource allocation

From the figure above we can see that one ALU has been removed and only one ALU being shared for both the addition operations. However a multiplexer is introduced at the input to the ALU that contributes to path delay. Earlier only the multiplexercontributed to the delay.Withresource allocation the multiplexer and ALU contribute to the delay. Therefore due to resource sharing the area of the design has decreased but the delay is increased. This is the trade-off that the designer has to decide on. No resource sharing is generally performed for timing-critical designs.

#### 4.1.2 COMMON SUB-EXPRESSIONS AND COMMON FACTORING

Identifying common sub expressions and reusing the pre computed values wherever possible is a good practice. A simple example is given below.

B= R1 + R2; C <= R3 - (R1 + R2);

If the sub expression R1 + R2 in the signal assignment for C is replaced with B as given below, only one adder will be generated for the computation instead of two.

$C \le R3 - B;$

Such changes if made by the designer can cause the tool to synthesize better logic and also enable the tool for better optimizations.

#### 4.1.3 **REMOVING REDUNDANT CODE**

Cases exist where the value of an expression might not change within a loop. The synthesis tool handles the loop statement by repeating the loop a specified number of times. In such cases redundant code getsgeneratedcausing additional logic to be synthesized. This can be avoided by moving the expression outside the loop, thus optimizing the design. An example is given below:

C = A + B;

for C in range 0 to 5 loop

T = C - 6;

Assumption: *C* is not assigned a new value within the loop, thus the above expression would remain constant on every loop iteration.

end loop;

The above code would generate six subtracters for the expression when only one is necessary. Thus by modifying the code as given below we could avoid the generation of unnecessary logic.

C = A + B;

temp: = C - 6; // A temporary variable is introduced

for c in range 0 to 5 loop

T = temp;

Assumption: C is not assigned a new value within the loop, thus the above expression would remain constant on every iteration of the loop.

end loop;

#### 4.1.4 CONSTANT FOLDING AND DEAD CODE ELIMINATION

Designer might accidentally leave expressions that are constant in value.

EX:

Y = 2 \* C;

Assigning the value of Y as 8 within the code can avoid the above unnecessary code. This method is called constant folding. Dead code elimination refers to certain code sections that never get executed.

EX: A: = 2; B: = 4; if (A > B) then end if;

The *if* statement would never be executed and can be eliminated from the code. The logic optimizer performs these optimizations automatically but the optimization time can be reduced if the designer keeps account of the above factors while designing.

## 4.1.5 FLIP-FLOP AND LATCH OPTIMIZATIONS

The designer should try to remove the unnecessary flip-flop and latch elements in the design. Only the clock sensitive signals should be placed in positive edge statements to avoid unnecessary flip-flops. Latches can be eliminated by specifying an else statement for if statements.

## 4.1.6 USING PARENTHESES

The correct parenthesis usage is critical to generate a well-timed design.

EX:

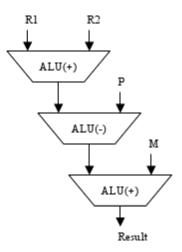

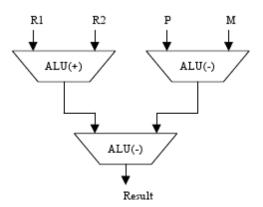

Result  $\leq R1 + R2 - P + M;$

The hardware generated for the above code is as given below in Figure

# Figure 10: Synthesis without parenthesis

If the expression has been written using parentheses as given below, the hardware synthesized would be as given in Figure.

Result  $\leq = (R1 + R2) - (P - M);$

Figure 11: Synthesis with parenthesis

Therefore using parentheses the timing path for the datapath has been reduced as it does not need to go through one more ALU as in the earlier case.

## 4.2 Optimizations using Design Compiler

For obtaining an optimized design a lot of experimentation and synthesis iterations are required.For optimization, changing of HDL code may affect other blocks in the design. For this reason, HDL code modification is generally avoided.

#### **Resolving multiple instances:**

Before proceeding for optimization, one needs to resolve multiple instances of sub-blocks in the design. This is a necessary step as DC does not permit compilation until multiple instances are resolved.

EX: Let's say module A has been synthesized. Now moduleB that has two instantiations of module A - namely U1 and U2. The compilation will error out with a message stating that module A is instantiated 2 times in moduleB. This can be resolved as follows:

Use the**dont\_touch**attribute on moduleA before synthesizing moduleB, or **uniquify**moduleB. **Uniquify**command creates unique definitions of multiple instances. So for the above case synthesizer will generate moduleA\_u1 and moduleA\_u2, corresponding to instance U1 and U2 respectively.

## Various DC optimization commands are given below:

#### 4.2.1 COMPILE THE DESIGN

The compilation process translates the HDL code to gates from the target library. This is done through the **compile** command. The syntax is given below:

compile -map\_effort<low | medium | high>

-incremental\_mapping

-in\_place

-no\_design\_rule | -only\_design\_rule

-scan

The default compile option is -map\_effort medium. This produces good results for most of the designs. The map\_effort high should only be used, if target objectives are not met through default compile. The -incremental\_mapping is used to improve timing of the logic.

# 4.2.2 FLATTENING AND STRUCTURING

Flattening means reducing the design to an equivalent two level AND/OR form. This helps in optimizing the design by removing the intermediate variables. This option is set to "false" by default. There are two stages to this optimization. The first stage consists of flattening and structuring and the second stage consists of mapping of the resulting design to actual gates using optimization techniques.

Flattening reduces the number of logic levels between the input and output. This results in faster logic but is generally recommended for unstructured designs. He flattened design can then be structured during optimization. Flattening has a significant impact on the areareduction. In general one should compile the design using default settings (flatten and structure are set as false). If there are timing violations flattening and structuring should be employed. If the design is still failing apply only flattening without structuring.

The command for flattening is given below:

set\_flatten<true | false>

-design <list of designs>

-effort <low | medium | high>

-phase <true | false>

31

The –phase option if set to true enables the DC to compare inverted and non- inverted form of the logic equations. The default setting for structuring is "true".

For example: Before structuring after structuring P = ax + ay + cP = aI + cQ = x + y + z Q = I + zI = x + y

The command for structuring is given below.

set\_structure<true | false>

-design <list of designs>

-boolean<low | medium | high>

-timing <true | false>

# 4.2.3 **REMOVING HIERARCHY**

Hierarchy is a logic boundary that prevents DC from optimizing across this boundary. Unnecessary hierarchy leads to cumbersome designs that are very difficult to optimize across boundaries and only optimizing within the boundary. To allow DC to optimize across these boundaries we can use the following commands.

dc\_shell>current\_design <design name>

# dc\_shell>ungroup -flatten -all

This allows the DC to optimize the logic separated by boundaries as one logic resulting in

better timing and a more optimized solution.

### 4.2.4 **OPTIMIZING FOR AREA**

DC by default does optimizations for timing. Designs that are not critical on timing can be optimized for area. Usage of the dont\_touch attribute on the high drive strength gates will result in better area due to gate elimination. Once the design is mapped to gates the design should be recompiled with the new constraints. Incremental compile ensures that the design doesn't change much from initial stage bloating unnecessary logic.

#### 4.3 Timing Issues

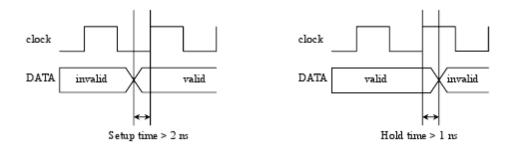

There are two kinds of timing issues that are important in a design- setup and hold timing violations:

- Setup Time: The time for which the input data should not change before the clock edge is referred to as set time. Input change during this period is going to result in a setup time violation. Figure illustrates an example with setup time equal to 2 ns. This means that signal DATA must be valid 2 ns before the clock edge; i.e. the data should not change during this 2ns period before the clock edge.

- Hold Time: The time for which the data should be held constant after the clock edge is referred to as hold time. Change of data during this period would trigger a hold timing violation. Figure illustrates an example with-hold time equal to 1 ns. This means that signal DATA must be held valid 1 ns after the clock edge; i.e. the data should not change during the 1 ns period after the clock edge.

Figure 12: Setup and Hold times

The synthesis tool automatically checks for setup and hold time violations on the paths that have timing constraints imposed. The following are the equations used to check for these violations:

Tprop + Tdelay<Tclock - Tsetup (1)

Tdelay + Tprop>Thold (2)

Tprop is the propagation delay from input clock to output of the device, Tdelay is the propagation delay across the combinational logic through which the input arrives, Tsetup is the setup time requirement of the device, Tclock is clock period and Thold is the hold time requirement of the device.

So if the propagation delay across the combinational logic, Tdelay is such that the equation (1) fails i.e. Tprop + Tdelay is more than Tclock – Tsetup then a setup timing violation is reported. Similarly if Tdelay + Tpropis greater than Thold then a hold timing violation is reported. The input data arriving late due to large combinational circuit delay Tdelay can result in a setup time violation as the flip-flop doesn't get enough time to read the data. In case of hold time violation the data arrives faster than usual (insufficient Tdelay+Tprop) and the flip flop doesn't get enough time to store the data.

Various synthesis commands can be used for optimizing the design to avoid timing violations:

a) Compilation with a map\_effort high option

b) Group critical paths together and assigning a weight factor

- c) Register balancing

- d) Choose a specific implementation for a module

- e) Balancing heavy loading

#### 4.3.1 COMPILATION WITH MAP\_EFFORT HIGH

The default compilation option for map\_effort is medium. This usually gives the best results with flattening and structuring options. The map\_effort high option should be used in case of violations with the default option. This usually takes a long time to run and thus is not used as the first option. This compilation could improve design performance by about 10%.

# 4.3.2 GROUP CRITICAL PATHS AND ASSIGN A WEIGHT FACTOR

The group\_path command can be used to assign weight factor to certain paths indicating the effort that is needed for specified paths. The weight factor dictates the effort needed to spend on a path for optimization.

group\_path -name <group\_name> -from <starting\_point> -to <ending\_point> -weight

<value>

#### 4.3.3 **REGISTER BALANCING**

This command is more useful for pipelined designs. The command reshuffles the logic from one pipeline stage to another by moving extra logic from overly constrained pipeline stages to less constrained ones with additional timing. The command is balance\_registers.

#### 4.3.4 CHOOSE A SPECIFIC IMPLEMENTATION FOR A MODULE

Depending upon the map\_effort option set, DC will automatically choose different implementations for a functional module. For example the adder has the following kinds of implementation.

- a) Ripple carry rpl

- b) Carry look ahead –cla

- c) Fast carry look ahead –clf

- d) Simulation model –sim

Implementation types rpl, cla, and clf are for synthesis; clf is the faster implementation followed by cla; the slowest being rpl. If compilation of map\_effort low is set the designer can manually set the implementation using the set\_implementation command. If the map\_effort is set to medium the design compiler would automatically choose the appropriate implementation depending upon the optimization algorithm.

# 4.3.5 BALANCING HEAVY LOADING DESIGNS

A large load cannot be driven by a single net. This leads to unnecessary delays and thus timing violations. The**balance\_buffers**commandsolves this problem. When used DC will create buffer trees to drive a large fanout thus balancing the heavy load.

# **CHAPTER 5: IC COMPILER**

IC compiler is a tool from Synopsys that is used for physical implementation. Following is a detailed flowchart for the ASIC design process.

Figure 13: ASIC Design Flowchart

The physical implementation consists of three steps:

A)Floor planningB)PlacementC) Clock Tree Synthesis (CTS)D)Routing

# 5.1 Floor Planning

At the floor planning stage, thenetlist describes the design and the various blocks of the design and the interconnection between the different blocks. The netlist is the logical description of the ASIC and the floor plan is the physical description of the ASIC. Floor planning is the process of mapping the logical description of the design to the physical description. The main objectives of floor planning are to minimize

a. Area

b. Timing (delay)

During floor planning, the following are done:

- The size of the chip is estimated.

- The various blocks in the design, are arranged on the chip.

- Pin assignment is done.

- The I/O and power planning are done.

- The type of clock distribution is decided

# Figure 14: Floor Plan Example

The final timing and quality of the chip depends on the floor plan design. The three basic elements of chip are:

- 1. Standard Cells: The design is made up of standard cells.

- 2. I/O cells: These cells connect the chip to the outside world.

3. Macros (Memories): Sequential storage elements like flip flop take up a lot of area. Therefore special memory elements are used which store the data efficiently and also do not occupy much space on the chip. These memory cells are called macros. Examples of memory cells include 6T SRAM (Static Dynamic Access Memory), DRAM (Dynamic Random Access Memory) etc.

The above figure shows a basic floor plan. The following are the basic floor planning steps (and terminology):

• Aspect ratio (AR): Aspect Ratio is defined as the ratio of the width and length of

the chip. From the figure, we can say that aspect ratio is x/y. The aspect ratio should take into account the number of routing resources available. If there are more horizontal layers, then the rectangle should be long and width should be small and vice versa if there are more vertical layers in the design.

Normally, METAL1 is used up by the standard cells. Usually, odd numbered layers are horizontal layers and even numbered layers are vertical. So for a 5 layer design, AR = 2/2 = 1.

For a 6 layer design, AR = 2/3 = 0.66.

- **Concept of Rows**: The standard cells for a particular design are placed in rows. The rows have equal height and spacing between. The width of the rows can vary. VDD and ground rails are placed on either side of the cell rows. Power for the cells in the rows can be derived from these voltage rails.

- **Core**: Core is defined as the inner block, which contains the standard cells and macros. There is an outer block which covers the inner block. The I/O pins are placed on the outer block.

- **Power Planning**: Power supply is required for a chip to work. A power ring is designed around the core. The power ring contains the VDD and VSS rings. Once the ring is placed, a power mesh is designed such that the power reaches the cells easily. The power mesh is nothing but horizontal and vertical lines on the chip. One needs to assign the metal layers through which the power needs to be routed. The VDD and VSS rails also have to be defined.

- **I/O Placement**: There are two types of I/O's.

- i. **Chip I/O:** TheI/O placement consists of the placement of I/O pins and the I/O pads.

- ii. **Block I/O:** The core consists of several blocks.Eachblock has block I/O pins which communicate with other blocks in the chip.

- **Concept of Utilization**: Utilization is defined as the percentage of area that has been utilized in the chip. In the initial stages of the floor plan design, if the size of the chip is unknown, then the starting point of the floor plan design is utilization. There are three different kinds of utilizations.

- i. **Chip Level utilization:** Chip level utilization is the ratio of the area of standard cells, macros and the pad cells with respect to area of chip.

## Area (Standard Cells) + Area (Macros) + Area (Pad Cells)

Area (chip)

ii. **Floor plan Utilization**: Floor plan utilizationis defined as the ratio of the area of standard cells, macros, and the pad cells to the area of the chip minus the area of the sub floor plan.

Area (Standard Cells) + Area (Macros) + Area (Pad Cells)

Area (Chip) – Area (sub floor plan)

iii. **Cell Row Utilization**: Cell row utilization is defined as the ratio of the area of the standard cells to the area of the chip minus the area of the macros and area of blockages.

#### Area (Standard Cells)

Area (Chip) - Area (Macro) – Area Region Blockages)

• Macro Placement: During floor planning the initial placement of macros in the core is performed first. Depending on the placement of macros standard cells are place in the core. Blockages should be put in the areas where two macros are placed close by. This helps prevent tool from placing standard cells in those small areas and

avoid congestion. Few of the different kinds of placement blockages are:

- i. **Standard Cell Blockage**: The tool does not put standard cells in the area specified by the standard cell blockage.

- ii. Non Buffer Blockage: The tool can place only buffers in the area specified by the non-buffer blockage.

- Blockages below power lines: Blockages should be created under power lines, so that congestion problems don't occur later. If there are lot of errors post routing, use of placement blockages can ease congestion.

- I/O Cells in the Floor plan: The I/O cells are the cells which help the internal blocks of the chip to communicate with the outside world. The I/O cells provide voltage to the core. There are a lot of resistances and capacitances due to the different elements in the I/O construction. Due to this, the voltage may need to be higher outside so that the correct voltage can be provided to the cells inside.

So now the next question is how the chips can communicate between different voltages?

The answer is provided by the I/O cells. These I/O cells are basicallylevel shifters. Level shiftersconvert the voltage from one level to another. The input I/O cells reduce the voltage coming from the outside to that of the voltage needed inside the chip and output I/O cells increase the voltage which is needed outside of the chip. The I/O cells also act like buffers.

#### 5.2 Concept of Flattened Verilog Netlist

Verilognetlist is usually in the hierarchical form. In a hierarchical design the design is broken down into sub modules. This greatly simplifies the design process. Hierarchical netlist is good only until physical implementation. During placement and routing, flattened netlist is a better option. In a flattened netlist the blocks have been basically opened up and there are no more sub blocks. There is just one top block. This helps in achieving better routing and good quality optimization. Conventional hierarchical flow can lead to sub-optimal timing for critical paths traveling through the blocks and for critical nets routed around the blocks.

The following gives an example of a netlist in the hierarchical mode as well as the flattened netlist mode:

#### **Hierarchical Model:**

```

module top (a,out1)

input a;

output out1;

wire n1;

SUB1 U1 (.in (a), .out (n1))

SUB1 U2 (.in (n1), .out (out1))

endmodule

module SUB1 (b,outb)

input b;

outputoutb;

wire n1, n2;

INVX1 V1 (.in (b), .out (n1))

INVX1 V2 (.in (n1), .out (n2))

INVX1 V3 (.in (n2), .out (outb))

endmodule

```

In verilog, the instance name of a module is unique. In the flattened netlist, the instance name would be the top level instance name/lower level instance name etc... Also the input and output ports of the sub modules get lost. In the above example the input and output ports a, out1, b and outb get lost.

The above hierarchical model, when converted to the flattened netlist, will look like this:

# Flattened Model:

module top (in1, out1)

input in1;

output out1;

wire topn1;

INVX1 U1/V1 (.in (in1), .out (V1/n1) INVX1 U1/V2 (.in (V1/n1), .out (V2/n2) INVX1 U1/V3 (.in (V2/n2), .out (topn1) INVX1 U2/V1 (.in (n1), .out (V1/n1) INVX1 U2/V2 (.in (V1/n1), .out (V2/n2) INVX1 U2/V3 (.in (V2/n2), .out ( out1 ) endmodule

The following is chart for the floorplanning process:

Figure 15: Floor planning flowchart

#### 5.3 Placement

Placement is the step in the physical implementation process where place for the standard cells are allocated on the row. Space is set aside for interconnect to each logic/standard cell. Once the placement process is complete we can get accurate estimates of the capacitive loads that each standard cell has to drive. The tool places these cells based on the algorithms used internally.

The main objectives of the placement algorithm are:

- Making the chip as dense as possible (Area Constraint)

- Minimize the total wire length (reduce the length for critical nets). The number of horizontal/vertical wire segments crossing a line.

Constraints for doing the above are:

- The placement should be routable (no cell overlaps; no density overflow).

- Timing constraints are met

There are different algorithms to do placement. The most popular ones are as follows:

- a. **Constructive algorithms:** This type of algorithm uses a set of rules to arrive at the optimized placement. Example: Cluster growth, min cut, etc.

- b. **Iterative algorithms:** Intermediate placements are modified to achieve a better design. Already constructed placements are used initially and iterates on that to get a better placement.

Example: Force-directed method.

c. Nondeterministicapproaches: simulated annealing, genetic algorithm, etc.

# 5.4 Clock Tree Synthesis

Clock tree synthesis is a layout technique used to provide balanced buffer distribution to clock pins in an attempt to minimize the clock skew [19]. The following figure shows balancing effect between various connections and wire lengths:

Figure 16: Clock Tree Synthesis Strategy

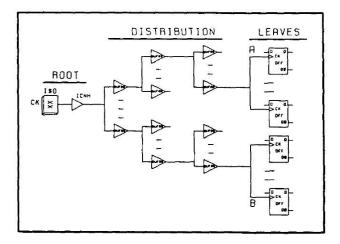

In Figure 16 the point 'R' is termed as the root point for clock distribution. The root drives the distribution macros 'D'. The distribution macros will drive the leaves 'L' which are clock inputs to sequential macros or another level of distribution macros as illustrated in Figure 17.

Figure 17: Clock Distribution Levels

The tree in Figure 17 is said to have three levels. The function of the distribution level is to achieve balanced loading when driving the leaves.

Figure 18 shows three waveforms. The waveform labeled CK is the input to the root CK in Figure 17.Waveforms A and B are the clock inputs to two sequential elements (D type flip-flops) on different branches. The time t1 and t2 are termed as clock insertion delays which is the time required to propagate through the clock distribution. The difference between t1 and t2 is termed as clock skew.

Figure 18 : Waveform 1

Interconnect and loading capacitances are the largest effect of balancing [19]. There are various aspects like metal capacitance for each routing level, their individual capacitance effects, fringing and parallel plate, and the physical size difference of macros which cannot be controlled by the designer [19]. The only aspects controlled by the designer are the choice of macros and buffer distribution. The factors influencing balancing are the layout tool, the size of the array, and the existence of large blocks [19].

The capability if the layout tool is fixed. The designer has to use the command appropriately to get the best out of the tool. The layout tool has difficulty placing and routing the blocks that is driven by the root. The larger the area the more difficult it will be finding the center of gravity points for all the destination inputs [19]. The existence of large blocks can disturb the balancing process by making the layout tool work around these blocks.

The strength of the root macro is very critical as it determines the skew and insertion delays [19]. Best results can be achieved by using larger buffers at the root followed by medium strength buffers at the distribution level that drives the leaves [19]. Usually the last level contains the most number of distribution buffers [19]. Therefore using low drive strength buffers here will prevent

excessive power dissipation still conforming to the clock skew requirements [19].

# 5.5 ROUTING

Next step after floor planning and placement is routing. Routing is the process of connecting various placed blocks. Until now, the blocks were only just placed on the chip.

Routing also is spilt into two steps:

1. **Global routing**: Global router plans the routing between different blocks placed. The main objective here is to minimize the total interconnect length and critical path delay.

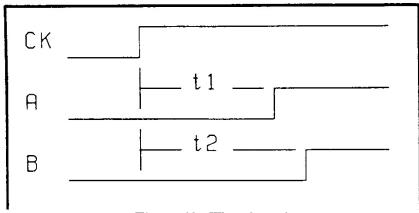

The chip is divided into small blocks called routing bins. The size of the routing bin depends on the algorithm the tool uses. Each routing bin is also called a gcell. Each gcell has a finite number of horizontal and vertical tracks. Global routing assigns nets to specific gcells but does not define the specific tracks for the nets. The global router connects two different gcells from the center point of each gcell.

The global router keeps track of the total number of interconnections going in each direction. This is called the routing demand. The number of routing layers available depends on the design. Each routing layer has a minimum width spacing rule, and routing capacity.

EX: Consider a 5 metal layer design. If metals 1,4,5 are used for intercell connection, pin, vdd, vss connections then only metals 2 and 3 are available for routing. The routing demand going over the routing supply results in congestion causing DRC errors.

2. **Detailed Routing**: In this step the nets are connected. Actual via and metal connections are created. The main objective in this step is to minimize the total area, wire length, delay in the critical paths. Each layer has its own routing grid, rules. During the final routing, the width, layer, and exact location of the interconnection are decided.

Figure 19: Floor partitioned into gcells

After detailed routing is complete, the exact length and the position of each interconnect for every net in the design is known. The actual delay estimation is now performed by extracting the parasitic capacitance and resistance. The parasitic extraction is done by extraction tools. This information is used by the static timing analysis tools to generate accurate timing statistics. After timing is met and verification is performed such as DRC and LVS the design is sent to the foundry to manufacture the chip.

# CHAPTER 6: FULL METHODOLOGY

# 6.1 Design Compiler

Invoke the script with "dc\_shell-t -f synthesis.tcl" after modifying the script for your design. You will need to update the script for your design and library locations. Comments are included.

2) After synthesis, you will have a post\_synth netlist and a sdc file constraining your

timing.

| Terminal                                                                           |         |

|------------------------------------------------------------------------------------|---------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>T</u> erminal Ta <u>b</u> s <u>H</u> elp |         |

| bash-3.2\$ csh                                                                     | <u></u> |

| source of /etc/system.cshrc                                                        |         |

| [101]cdsemac_eepc23> dc_shell-t -f synthesis.tcl                                   |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    |         |

|                                                                                    | ×       |

Figure 20: Design Compiler Invoke

# 6.2 IC\_Compiler

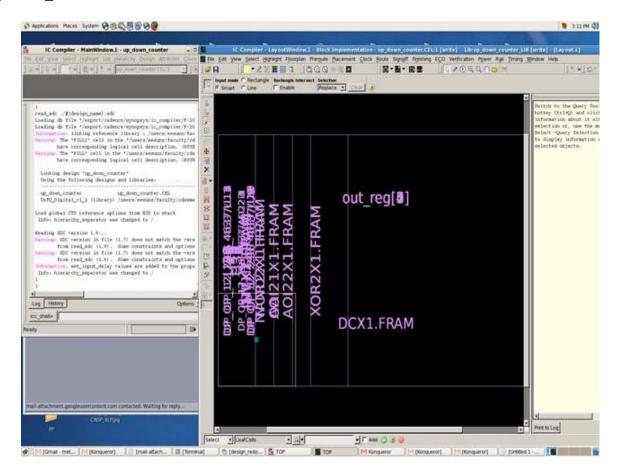

1) Change the directory to the directory with the startupICCscript(icc\_ONC5\_version3.tcl).

Execute the following on the command line: icc\_shell -gui -f

icc\_ONC5\_version3.tcl

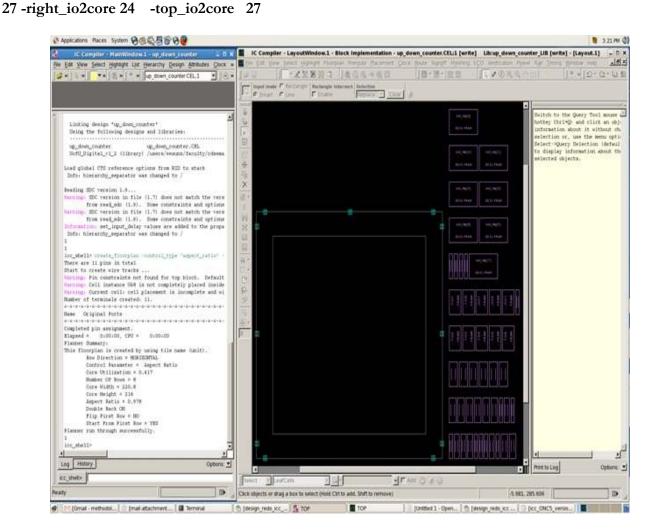

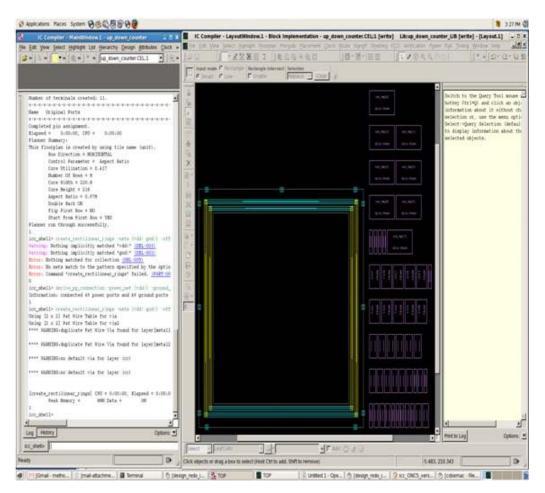

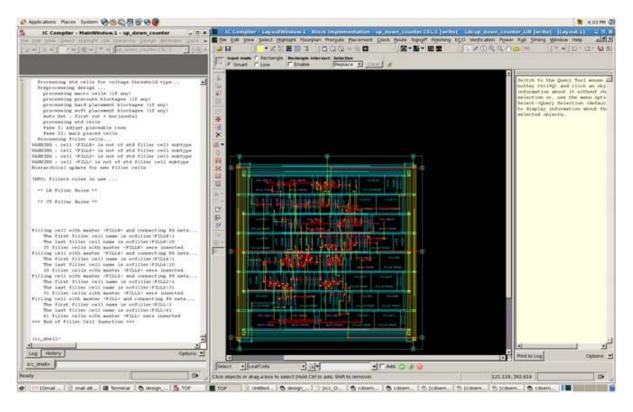

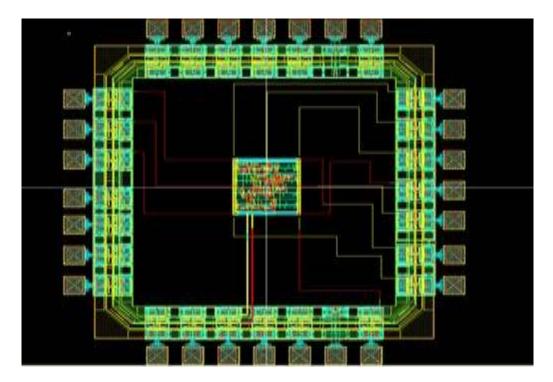

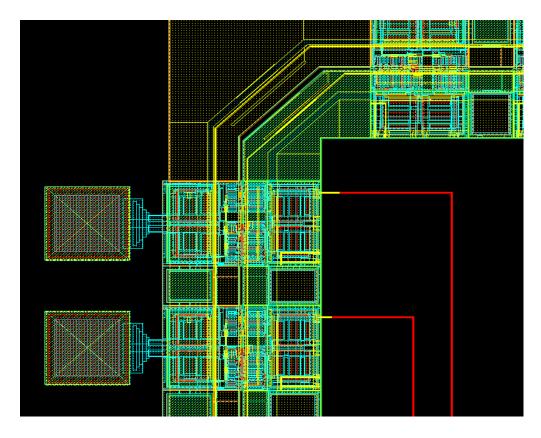

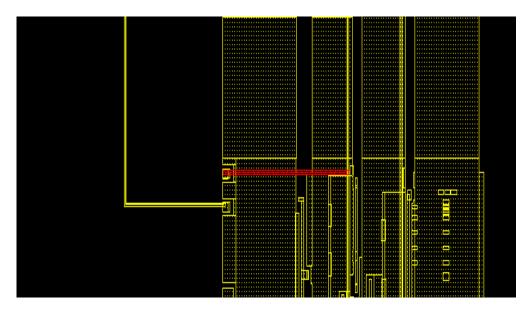

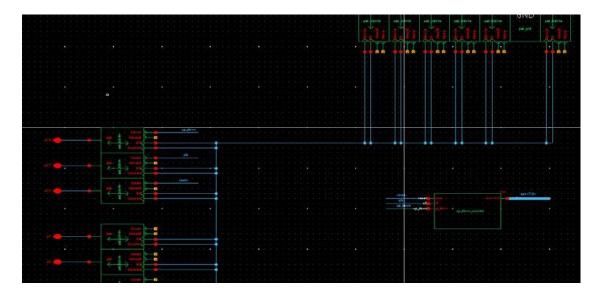

Figure 21: IC compiler design import

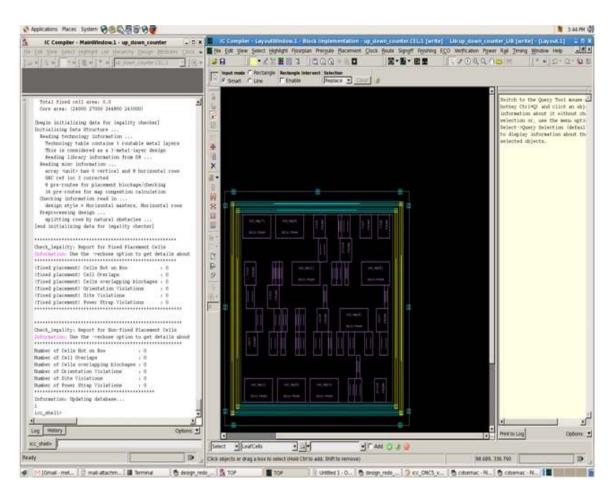

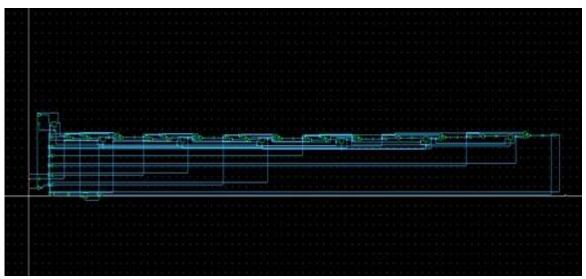

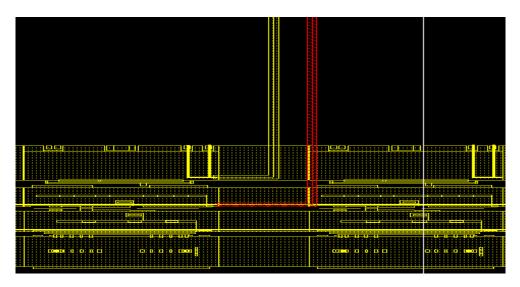

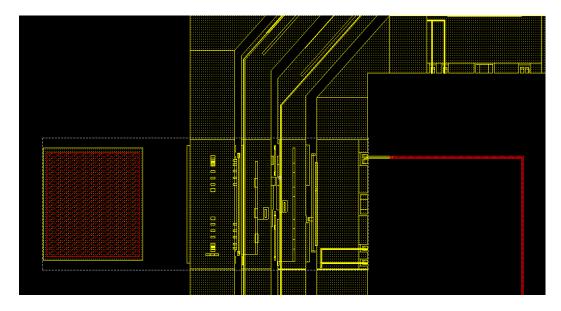

3) The following command will allocate space for the chip and place the pins evenly on the border. The purple boxes on the right are the unplaced cells. The core\_utilization will determine how dense the design will be at the expense of routability later. create\_floorplan -control\_type "aspect\_ratio" -core\_aspect\_ratio "1" core\_utilization "0.4" -row\_core\_ratio "1" -start\_first\_row -left\_io2core 24 -bottom\_io2core

Figure 22: Floor Plan creation