# NANO EXPRESS

# An Early Detection Circuit for Endurance Enhancement of Backfilled Contact Resistive Random Access Memory Array

Yun-Feng Kao<sup>®</sup>, Jiaw-Ren Shih, Chrong Jung Lin and Ya-Chin King<sup>\*</sup>

# Abstract

As one of the most promising embedded non-volatile storage solutions for advanced CMOS modules, resistive random access memory's (RRAM) applications depend highly on its cyclability. Through detailed analysis, links have been found between noise types, filament configurations and the occurrence of reset failure during cycling test. In addition, a recovery treatment is demonstrated to restore the cyclability of RRAM. An early detection circuit for vulnerable cells in an array is also proposed for further improving the overall endurance of an RRAM array. Lifetime of RRAM can be extended to over 10 k cycles without fail bits in an array.

Keywords: RRAM, Variability, Stochastic model, Monte Carlo Simulation, Trap-assisted tunneling

# Introduction

In recent years, RRAM with advantages of simple structure, superior scalability and high compatibility to advanced CMOS processes has become one of the core technologies for realizing embedded non-volatile memory modules [1–8]. RRAM featuring high cyclability can extend its applications to systems which required to update non-volatile data more frequently, such as computing-in-memory and neuromorphic systems [9–15].

Switching of states in RRAM films is believed to be attained by generation/recombination of oxygen vacancies ( $V_o$ ) to further control construction/destruction of conductive filaments (CF) [16–22]. Many studies have shown that stochastic mechanisms in the formation of CFs during set/reset operations have been found as one of root causes for bit failure during cycling tests [23–27]. In a fail-to-set cell, excess  $V_o$  recombined during reset operations widens the tunneling gap between the residual CFs and the top electrode, which weakens the electric field in the gap region, leading to low  $V_o$

\*Correspondence: ycking@ee.nthu.edu.tw

Microelectronics Laboratory, Institute of Electronics Engineering, National Tsing Hua University, Hsinchu 300, Taiwan

generation [24]. On the other hand, excess  $V_0$  generated during set operation, leading to CF over-growth. This is believed to be the main cause of reset failures [24, 28]. Also, unexpected depletion of oxygen ions during cycling is found to be responsible for the closing of the resistance window [23, 28]. Several schemes for mitigating the effect of the stochastic process in  $V_{o}$  generation/annihilation have been reported in various studies [23, 24, 28–30]. Pulse with large rising and falling time was found to, respectively, reduce  $V_0$  generation in set operation and consumption of oxygen ion in reset process [23]. To obtain good controllability of  $V_0$ , Chen et al. also suggest a tuning-pulse amplitude method for balancing set/reset operations [29]. Aside from pulse conditioning [23, 29], strong set/reset electrical recovery treatments on devices after endurance failure are found that cells can be restored and cycled again [24, 28, 30]. It is also revealed that increased frequency of recovery operations pushes the overall cycling endurance performance higher [24]. Periodic recovery on the whole array during cycling costs high power overhead and implementation challenges in real memory modules. Therefore, find the weak cells, which are at the brink of cycle failure, is essential to the implementation

© The Author(s) 2021. **Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

of a selective and timely recovery. This can enable the improvement of cyclability without wasting unnecessary treatments on healthy cells.

In our previous work, cells with low reset efficiency were found to correlate to its CF topography. Furthermore, random telegraphic noises are linked to the CF types, which also reflect the change of CF after cycling stress [31]. In this work, new circuits for early detection of weak devices in an array by its read current characteristics have been proposed. A reset recovery operation is also introduced for preventative strengthening of vulnerable cells identified by the detection method. Applying the method of early detection and selective CF strengthen operations, significant improvement in the set/reset cyclability has been successfully demonstrated.

# Methods

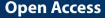

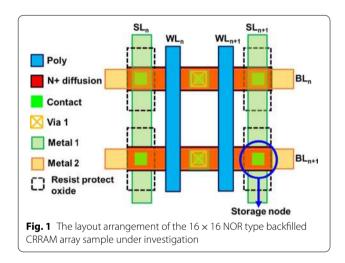

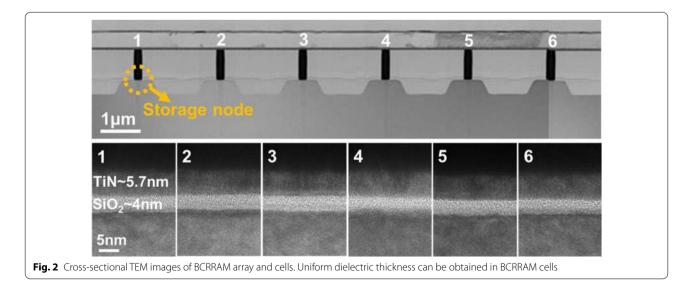

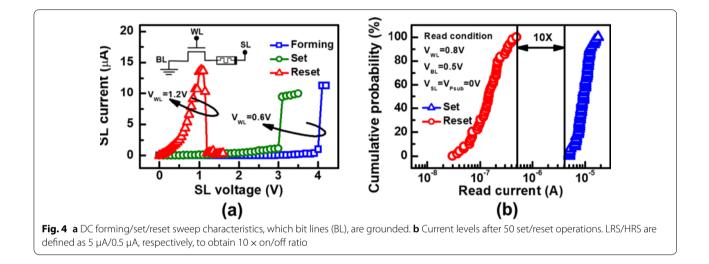

Statistical analysis on endurance of RRAM is collected from a  $16 \times 16$  backfilled contact resistive random access memory (BCRRAM) array, which is fabricated by 0.18 µm CMOS logic process [32, 33]. As shown on layout in Fig. 1, storage node of BCRRAM is connected in series with a n-channel transistor for cell selection in a NOR-type array. To in-depth investigate the physical properties of TMO layer of BCCRAM, the transmission electron microscopic (TEM) analysis is carried out by JEOL JEM-2800 transmission electron microscopic with energy 200 keV. The cross-sectional TEM images of BCRRAM array along source line (SL) direction are shown in Fig. 2. Because of the better control of the backfilled dielectric film thickness, uniform transition metal oxide (TMO) layer can be achieved. The relative element compositions along the depth of RRAM film are provided in energy-dispersive X-ray (EDX) spectroscopy analysis in Fig. 3, where TMO film of BCRAM cell is found to be composed of TiN/TiON/SiO<sub>2</sub> [32, 33]. The electrical analysis is completed by a semiconductor parameter analyzer and a pulse generator. DC forming/ set/reset characteristics of BCRRAM are demonstrated in Fig. 4a. Note that high SL voltage in forming/set operations are required to trigger the soft breakdown process. Low word line (WL) voltage 0.6 V on the gate of the select transistor clamps the surge current and prevents to overset into irreversible resistance states. As a BCR-RAM device under the unipolar mode, higher  $V_{WL}$  of 1.2 V is chosen to supply high enough current to enhance the diffusion of oxygen ion and recombination with  $V_{o}$ , favoring the switching back to HRS [34-37]. As shown in Fig. 4b,  $10 \times$  read current window can be maintained under 50 DC set/reset cycles, which low resistance state

(LRS)/high resistance state (HRS) are set to 5  $\mu$ A/0.5  $\mu$ A, respectively.

# **Results and Discussion**

## **Cyclability and Reset Recovery Scheme**

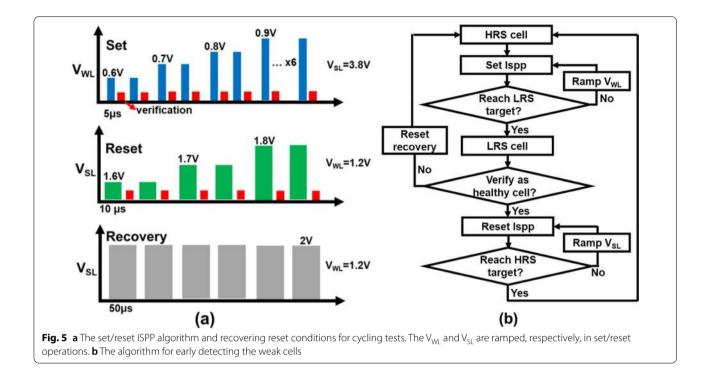

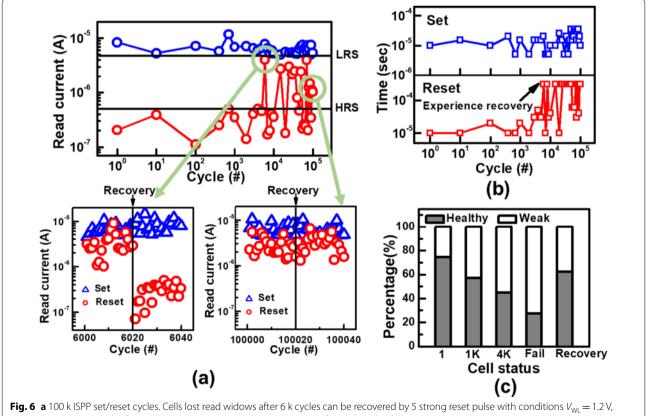

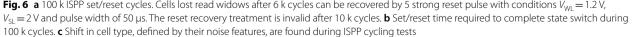

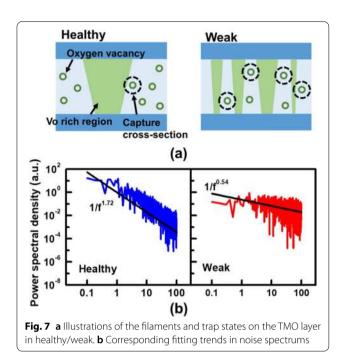

Cycling endurance of BCRRAM is examined by an optimized incremental step pulse programming (ISPP) algorithm shown in Fig. 5a. After each stress pulse, the states of BCRRAM are then verified to determine whether  $V_{\rm WL}/V_{\rm SL}$  needs to be increased for the next set/reset operations [38]. As displayed in Fig. 6a, stable read current window can be obtained within 20 µs set/reset time, see in Fig. 6b, for 1k cycles. Experimental data show that reset time required to reach the target HRS gradually increases when the number of cycles passes 1000. Data also reveal that most cells eventually stuck at LRS even after raising reset time to 60 µs. To investigate the root cause of reset degradation during cycling, low frequency noise (LFN) found in the read current is investigated and is reported as an index reflecting the properties of CFs [39-41]. In our previous work [31], cells with different densities of CFs inside its TMO layers exhibit distinct noise spectrum in its read current. As depicted in Fig. 7a, cells can be categorized into two groups based on characteristics of the LFN spectrum in their read current, in Fig. 7b. Cells with low density of CFs, labeled "healthy," are found to be more robust and are expected to endure more cycling stress. Cells containing multiple tiny CFs, named "weak," are believed to be more vulnerable to stress. To study the main failure mechanisms for cells under cycling tests, LFN of BCRRAM devices are monitored. As summarized in Fig. 6c, a strong correlation between cell types and number of cycles is found in BCRRAM array. Portion of weak cells with multiple conductive paths in TMO layers significantly increases after cycling, which is believed to cause less efficient heating

in a dispersed CF, slowing down reset process [31]. As a result, endurance failure on reset operation is attributed to the generation of multiple conductive paths. In addition to ISPP tests, different kinds of CFs generations after the constant voltage stresses were also reported [27, 28]. Unnecessary CFs generated by fixed set/reset operation conditions was believed to be one of reasons, causing cells to gradually lose their capabilities on switching back to HRS. To revive cells after reset failure, unnecessary CFs inside their TMO layers need to be trimmed through strong reset recovery pulses with conditions in Fig. 5a,  $V_{WL}$ =1.2V,  $V_{SL}$ =2V and pulse width of 50 µs, as demonstrated in Fig. 6a. With the proper reset recovery treatment, the read current window as well as its cyclability can be restored. However, as shown in Fig. 6b, the reset recovery pulses are needed more frequently on cells that experienced more than 10 k cycles. Data in Fig. 6a also indicate that reset recovery operations may become useless for some cells after long cycling stress, suggesting that the CFs in these cells are damaged to beyond repair.

The shift in cell's noise feature observed in Fig. 6c implies that cell types are useful index for repairing a vulnerable cell before it reaches complete failure. Therefore, distinguishing cell types by its noise features during operation is a crucial factor in realizing early interventions for strengthening CFs.

## **Early Detection Circuit**

For cells with more CFs inside TMO layers, its read current fluctuates between multiple resistance states. On the contrary, cells with one dominant CFs in RRAM films, current repeatedly jump between two distinct states, which can be used as the indices of the healthy cells [31]. As a result, number of middle states in read current can help us identify the vulnerable cells before it fails completely. Therefore, in the algorithm shown in Fig. 5b, to early detect a vulnerable cell and revive it before completely losing its cycling capability, the sampling current of cells is fed to the detection circuit. Once diagnosed restoration operations are performed on the confirmed weak cells. Hence, two circuits for detecting these weak cells are introduced and discussed in the following sections.

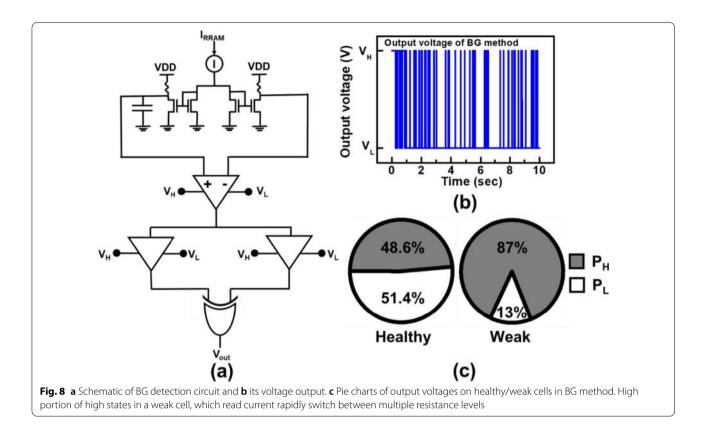

The first detection circuit by the buffer gate (BG) method, is illustrated in Fig. 8a. First, sampling current from BCRRAM cells is mirrored and filtered by a capacitor to set an average level. Next, the difference between the two sides is amplified. The amplified difference of middle states still slightly fluctuates between 0.55 V and 0.45 V. On the other hand, cell with one dominant CF, where the read current is found to jump between bi-levels; when it passes through the detector circuit, the output can be push to the high/low voltage levels. As shown in Fig. 8b, different logic states are generated by the two BGs with proper transition voltages and the XOR logic gate. For cells exhibiting middle-state RTN, the output voltage  $(V_{out})$  becomes latch at high voltage states  $(V_{H})$ instead of low voltage states ( $V_{\rm L}$ ). The ratio between the probability of output in  $V_{\rm H}$  ( $P_{\rm H}$ ) versus that in  $V_{\rm L}$  ( $P_{\rm L}$ ) of the XOR output on cells first categorized by their LFN as healthy/weak cells are summarized in Fig. 8c. For cells with multiple current levels in read current levels, a larger portion of XOR output remains in high states when the weak cells are put into the detection circuit. On the other hand, healthy cells with a single dominant CF and distinct resistance levels are more likely to put the XOR output at the low voltage states.

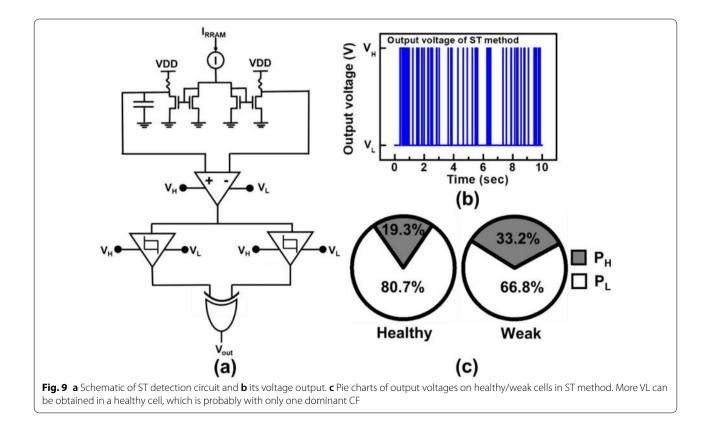

The second circuit proposed here for screening out vulnerable cells, named as Schmitt trigger (ST) method, is illustrated in Fig. 9a. Two Schmitt triggers, which upper/lower triggers are designed to be 0.65 V/0.35 V and 0.55 V/0.45 V, respectively, are used instead to find out the probability of the read current in its middle state. Output voltage, shown in Fig. 9b, becomes high when the read current is in its middle state. From the ST method, the percentages of high/low levels on the XOR output are summarized in Fig. 9c. The detection outputs are more likely to stay in  $V_{\rm H}$  for weak cells than that for healthy ones.

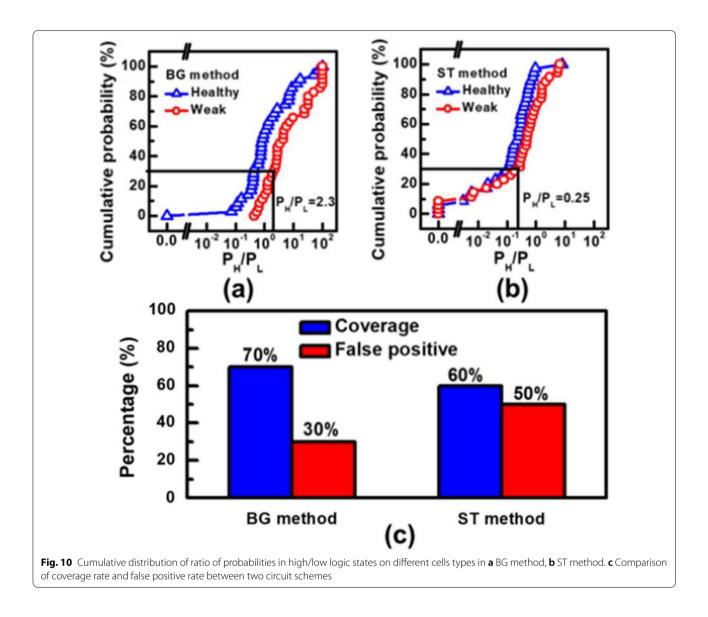

To investigate the success rate of the detection in identifying the weak cells, the ratio of high states from the detector output for the two groups of cells firstly categorized by LFN characteristics are compared in Fig. 10a, b.

For the BG detection circuit, we defined a weak cell by having a  $P_{\rm H}/P_{\rm L}$  ratio above 2.3. With this criterium, 70% of the weak cells can be successfully caught while leading to 30% false positive. For ST method, when the select criterium is set at a  $P_{\rm H}/P_{\rm L}$  ratio > 0.25, the coverage rate can reach 60%, while the false positive can be as high as 50%. This makes ST method a less effective screen method. As compared in Fig. 10c, higher coverage rate and lower chances of false-positive are demonstrated by the BG method.

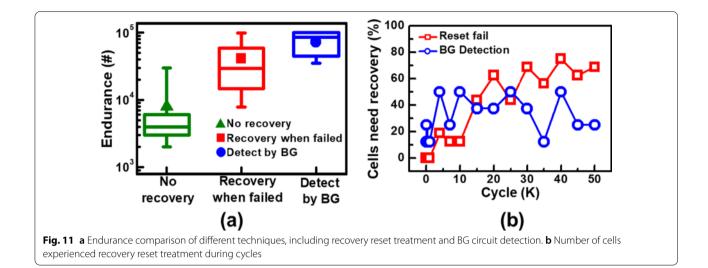

Due to high coverage rate provided by BG method, it is employed for the detection of vulnerable cells with high risk of endurance failure for the initiation of early interventions. The cycling characteristics of cells experiencing different types of recovery interventions are compared in Fig. 11a. Cells are found to sustain only 2 k cycles when no intervention is taken during cycling tests. Lifetime of BCRRAM can be extended by several thousand of cycles when reset recovery pulses are applied after reset failure. However, most of the revived cells cannot pass 8 k of cycling. Through the early detection circuit with BG scheme, weak cells in an array before cycling failure can be detected. With a recovery pulse applied on a weak cell detected, endurance of most BCRRAM cells can be significantly extended to more than 40 k cycles. The 15% cells in an 16 × 16 memory array required reset recovery treatment in different methods are compared in Fig. 11b. Although more cells need to be recovered before 10 k cycles in BG detection method, its percentage of cells is relatively stable throughout a 50 k cycling test. However,

in comparison group, where devices are restored after reset failure, proportion of cells needed recovery interventions increases with cycling stress, which suggests heavier operation overhead on both speed and power.

Thanks to detection circuit and reset recovery, the cycling lifetime of BCRRAM can be extended effectively. Even though the coverage rate of the BG detection circuit reaches 70%, some vulnerable cells are not identified. As a result, we believe that improving the coverage rate is one of the pathways for further enhancing the overall endurance of BCRRAM arrays. The settings of the detection circuit can be further adjusted for decreasing the false negative rate, enhancing the coverage rate. Besides, the reset recovery reset can be optimized for better reviving BCRRAM to its cycling capabilities.

# Conclusions

In this study, correlations of LFNs, topographies of CFs and reset failure during cycling are established. Besides, a recovery reset treatment is implemented in BCRRAM array for restoring reset failure. Two detection circuits, BG method and ST method, are proposed and investigated to screen out the vulnerable cells for early recovery interventions. In addition, the proposed BG method with a higher coverage rate is employed on a BCRRAM array to improve endurance. With the newly proposed BG detection circuits and early detection initiated reset recovery operation, significant improvement of cycling endurance for over 10 k times has been demonstrated.

#### Acknowledgements

The authors would like to thank the support from the Ministry of Science and Technology (MOST), Taiwan.

#### Authors' contributions

Kao carried out the device characterization. Shih supported TEM and EDX analysis. Lin and King supervised this study and modified manuscript. All authors read and approved the final manuscript.

#### Funding

This study is supported by the Ministry of Science and Technology (MOST), Taiwan.

#### Availability of data and materials

The datasets supporting the conclusions of this article are included in the article.

#### Declarations

#### **Competing interests**

The authors declare they have no competing interests.

Received: 26 July 2020 Accepted: 25 June 2021 Published online: 05 July 2021

#### References

- Bazzi H, Harb A, Aziza H, Moreau M (2018) Novel RRAM CMOS non-volatile memory cells in 130 nm technology. In: International conference on computer and applications (ICCA), pp 390–393

- Hsieh MC, Liao YC, Chin YW, Lien CM, Chang TS, Chih YD, Natarajan S, Tsai MJ, King YC, Lin CJ (2013) Ultra high density 3D via RRAM in pure 28 nm CMOS process. In: 2013 IEEE international electron devices meeting, pp 10.3.1–10.3.4

- Ielmini D (2016) Resistive switching memories based on metal oxides: mechanisms, reliability and scaling. Semicond Sci Technol 31(6):063002

- Jagath AL, Leong CH, Kumar TN, Almurib HF (2019) Insight into physicsbased RRAM models—review. J Eng 2019(7):4644–4652

- Mei CY, Shen WC, Wu CH, Chih YD, King YC, Lin CJ, Tsai M, Tsai K, Chen FT (2013) 28-nm 2T high-K metal gate embedded RRAM with fully compatible CMOS logic processes. IEEE Electron Device Lett 34(10):1253–1255

- Shen WC, Mei CY, Chih YD, Sheu SS, Tsai MJ, King YC, Lin CJ (2012) High-K metal gate contact RRAM (CRRAM) in pure 28 nm CMOS logic process. In: 2012 International electron devices meeting, pp 31.6.1–31.6.4

- Wong HP, Lee H, Yu S, Chen Y, Wu Y, Chen P, Lee B, Chen FT, Tsai M (2012) Metal–Oxide RRAM. Proc IEEE 100(6):1951–1970

- Zhu L, Zhou J, Guo Z, Sun Z (2015) An overview of materials issues in resistive random access memory. J Materiom 1(4):285–295

- Puglisi FM, Pacchioni L, Zagni N, Pavan P (2018) Energy-efficient logicin-memory I-bit full adder enabled by a physics-based RRAM compact model. In: 2018 48th European solid-state device research conference (ESSDERC), pp 50–53

- Zhou Y-X, Li Y, Su Y-T, Wang Z-R, Shih L-Y, Chang T-C, Chang K-C, Long S-B, Sze SM, Miao X-S (2017) Non-volatile reconfigurable sequential logic in a HfO<sub>2</sub> resistive random access memory array. Nanoscale 9(20):6649–6657

- Wang Z, Li Y, Su Y, Zhou Y, Cheng L, Chang T, Xue K, Sze SM, Miao X (2018) Efficient implementation of boolean and full-adder functions with 1T1R RRAMs for beyond von neumann in-memory computing. IEEE Trans Electron Devices 65(10):4659–4666

- 12. Wang Z, Su Y, Li Y, Zhou Y, Chu T, Chang K, Chang T, Tsai T, Sze SM, Miao X (2017) Functionally complete boolean logic in 1T1R resistive random access memory. IEEE Electron Device Lett 38(2):179–182

- Moon K, Lim S, Park J, Sung C, Oh S, Woo J, Lee J, Hwang H (2019) RRAM-based synapse devices for neuromorphic systems. Faraday Discuss 213:421–451

- Hong X, Loy DJ, Dananjaya PA, Tan F, Ng C, Lew W (2018) Oxidebased RRAM materials for neuromorphic computing. J Mater Sci 53(12):8720–8746

- Ielmini D (2018) Brain-inspired computing with resistive switching memory (RRAM): devices, synapses and neural networks. Microelectron Eng 190:44–53

- Raghavan N, Pey KL, Liu W, Wu X, Li X, Bosman M (2011) Evidence for compliance controlled oxygen vacancy and metal filament based resistive switching mechanisms in RRAM. Microelectron Eng 88(7):1124–1128

- 17. Kumar D, Aluguri R, Chand U, Tseng TY (2017) Metal oxide resistive switching memory: materials, properties and switching mechanisms. Ceram Int 43:S547–S556

- Yu S (2014) Overview of resistive switching memory (RRAM) switching mechanism and device modelling. In: IEEE international symposium on circuits and systems (ISCAS), pp 2017–2020

- Chang T-C, Chang K-C, Tsai T-M, Chu T-J, Sze SM (2016) Resistance random access memory. Mater Today 19(5):254–264

- Tsai Y-T, Chang T-C, Huang W-L, Huang C-W, Syu Y-E, Chen S-C, Sze SM, Tsai M-J, Tseng T-Y (2011) Investigation for coexistence of dual resistive switching characteristics in DyMn<sub>2</sub>O<sub>5</sub> memory devices. Appl Phys Lett 99(9):092106

- Bersuker G, Gilmer DC, Veksler D, Kirsch P, Vandelli L, Padovani A, Larcher L, McKenna K, Shluger A, Iglesias V, Porti M (2011) Metal oxide resistive memory switching mechanism based on conductive filament properties. J Appl Phys 110(12):124518

- Waser R, Dittmann R, Staikov G, Szot K (2009) Redox-based resistive switching memories–nanoionic mechanisms, prospects, and challenges. Adv Mater 21(25–26):2632–2663

- Lu Y, Chen B, Gao B, Fang Z, Fu YH, Yang JQ, Liu LF, Liu XY, Yu XY, Kang JF (2012) Improvement of endurance degradation for oxide based resistive switching memory devices correlated with oxygen vacancy accumulation effect. In: 2012 IEEE international reliability physics symposium (IRPS), pp MY.4.1–MY.4.4

- 24. Huang P, Chen B, Wang YJ, Zhang FF, Shen L, Liu R, Zeng L, Du G, Zhang X, Gao M, Kang JF, Liu XY, Wang XP, Weng BB, Tang YZ, Lo G, Kwong D (2013) Analytic model of endurance degradation and its practical applications for operation scheme optimization in metal oxide based RRAM. In: 2013 IEEE International electron devices meeting, pp 22.5.1–22.5.4

- Balatti S, Ambrogio S, Wang Z, Sills S, Calderoni A, Ramaswamy N, Ielmini D (2015) Voltage-controlled cycling endurance of HfOx-based resistiveswitching memory. IEEE Trans Electron Devices 62(10):3365–3372

- 26. Balatti S, Ambrogio S, Wang Z, Sills S, Calderoni A, Ramaswamy N, Ielmini D (2014) Pulsed cycling operation and endurance failure of metal-oxide

resistive (RRAM). In: 2014 IEEE international electron devices meeting, pp 14.3.1–14.3.4  $\,$

- Kang JF, Huang P, Chen Z, Zhao YD, Liu C, Han RZ, Liu F, Liu XY, Wang YY, Gao B (2016) Physical understanding and optimization of resistive switching characteristics in oxide-RRAM. In: 2016 46th European solid-state device research conference (ESSDERC), pp 154–159

- Chen B, Lu Y, Gao B, Fu YH, Zhang FF, Huang P, Chen YS, Liu LF, Liu XY, Kang YF, Wang YY, Fang Z, Yu XY, Li X, Wang XP, Singh N, Lo GQ, Kwong DL (2011) Physical mechanisms of endurance degradation in TMO-RRAM. In: 2011 International electron devices meeting, pp 12.3.1–12.3.4

- Chen YY, Govoreanu B, Goux L, Degraeve R, Fantini A, Kar GS, Wouters DJ, Groeseneken G, Kittl JA, Jurczak M, Altimime L (2012) Balancing SET/ RESET pulse for >10<sup>10</sup> endurance in HfO<sub>2</sub>\Hf 1T1R bipolar RRAM. IEEE Trans Electron Devices 59(12):3243–3249

- You Z, Hu F, Huang L, Liu P, Kuang J, Li S (2016) A long lifetime, low error rate RRAM design with self-repair module. J Semicond 37(11):115004

- Kao YF, Lin CJ, King YC (2020) Reset variability in backfilled resistive random access memory and its correlation to low frequency noise in read. IEEE J Electron Devices Soc 8:465–473

- Chen HY, Chen HH, Kao YF, Chen PY, King YC, Lin CJ (2016) A new manufacturing method of CMOS logic compatible 1T-CRRAM. In: 2016 International symposium on VLSI technology, systems and application (VLSI-TSA), pp 1–2

- Chen HY, Chen HH, King YC, Lin CJ (2016) Investigation of set/reset operations in CMOS-logic-compatible contact backfilled RRAMs. IEEE Trans Device Mater Reliab 16(3):370–375

- Yu S, Wu Y, Wong HSP (2011) Investigating the switching dynamics and multilevel capability of bipolar metal oxide resistive switching memory. Appl Phys Lett 98(10):103514

- 35. Yu S, Wong HP (2010) A phenomenological model for the reset mechanism of metal oxide RRAM. IEEE Electron Device Lett 31(12):1455–1457

- Russo U, lelmini D, Cagli C, Lacaita AL (2009) Self-accelerated thermal dissolution model for reset programming in unipolar resistive-switching memory (RRAM) devices. IEEE Trans Electron Devices 56(2):193–200

- Russo U, Lelmini D, Cagli C, Lacaita AL, Spiga S, Wiemer C, Perego M, Fanciulli M (2007) Conductive-filament switching analysis and selfaccelerated thermal dissolution model for reset in NiO-based RRAM. In: IEEE international electron devices meeting, pp 775–778

- Kao YF, Lin CJ, King YC (2019) Stochastic filament formation on the cycling endurance of backfilled contact resistive random access memory cells. In: 2019 International symposium on VLSI technology, systems and application (VLSI-TSA), pp 1–2

- Chai Z,Ma J, Zhang W, Govoreanu B, Simoen E, Zhang JF, Ji Z, Gao R, Groeseneken G, Jurczak M (2016) RTN-based defect tracking technique: experimentally probing the spatial and energy profile of the critical filament region and its correlation with HfO2 RRAM switching operation and failure mechanism. In: IEEE symposium on VLSI technology, pp 1–2

- 40. Hsieh ER, Lu PY, Chung SS, Ke SS, Yang CW, Tsai CT, Yew TR (2015) The RTN measurement technique on leakage path finding in advanced high-k metal gate CMOS devices. In: 2015 IEEE 22nd international symposium on the physical and failure analysis of integrated circuits, pp 154–457

- Ambrogio S, Balatti S, Cubeta A, Calderoni A, Ramaswamy N, Ielmini D (2014) Statistical fluctuations in HfOx resistive-switching memory: part II: random telegraph noise. IEEE Trans Electron Devices 61(8):2920–2927

## Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.