# An Effective Gate Resistance Model for CMOS RF and Noise Modeling

Xiaodong Jin, Jia-Jiunn Ou, Chih-Hung Chen\*, Weidong Liu, M. Jamal Deen\*, Paul R. Gray, and Chenming Hu

Department of Electrical Engineering and Computer Sciences, University of California, Berkeley \*Integrated Devices and Circuits Lab., Simon Fraser University, British Columbia, Canada Email: xjin@eecs.berkeley.edu Fax: 510-643-2636

# Abstract

A physics-based effective gate resistance model representing the non-quasi-static (NQS) effect and the distributed gate electrode resistance is proposed for accurately predicting the RF performance of CMOS devices. The accuracy of the model is validated with 2-D simulations and experimental data. In addition, the effect of the gate resistance on the device noise behavior has been studied with measured data. The result shows that an accurate gate resistance model is essential for the noise modeling.

# Introduction

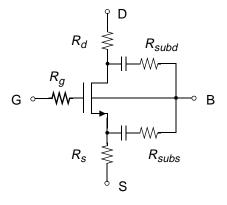

The continuous scaling of CMOS has made this technology a candidate for RF applications. CMOS technology is attractive because of low cost, high integration, and easy access to the technology. However, the accuracy of the existing CMOS compact model at RF is not satisfactory. Recently, several CMOS RF models based on BSIM3v3 have been proposed [1]-[3]. All of them add a gate resistance  $(R_{o})$  and a substrate coupling network to the core BSIM3v3. Fig. 1 shows one example with a particularly simple substrate network. In those models,  $R_g$  was obtained by curve fitting the measured input impedance data. As a result, it was difficult to model  $R_o$ as a function of device geometry and bias conditions making the accurate simulation of small signal circuits difficult and large signal circuits impossible. In this paper, a physical effective gate resistance model incorporating the first-order non-quasi-static (NQS) effect as well as the distributed gate electrode resistance is proposed. The proposed model can accurately predict not only the high frequency ac behavior but also the noise performance of CMOS devices.

## Model

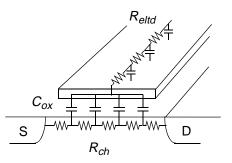

$R_g$  consists of two parts: the distributed gate electrode resistance ( $R_{geltd}$ ) and the distributed channel resistance seen from the gate ( $R_{gch}$ ), as shown in Fig. 2,

$$R_g = R_{geltd} + R_{gch}.$$

(1)

Since  $R_{geltd}$  is insensitive to bias and frequency, its value can

Fig. 1 A MOSFET RF model based on BSIM3v3.

be obtained from the gate electrode sheet resistance  $(R_{eltd})$ ,

$$R_{geltd} = R_{eltd} (\alpha W/L + \beta) , \qquad (2)$$

where  $\alpha$  is 1/3 when the gate terminal is brought out from one side, and 1/12 when connected on both sides.  $\beta$  models the external gate resistance. There are two mechanisms involved in  $R_{gch}$ : one is the static channel resistance ( $R_{st}$ ), which accounts for the dc channel resistance; the other is the excess-diffusion channel resistance ( $R_{ed}$ ) due to the change of chan-

Fig. 2 Illustration of distributed nature of gate electrode resistance  $R_{eltd}$ , channel resistance  $R_{ch}$ , and gate capacitance  $C_{ax}$ .

nel charge distribution by ac excitation of the gate voltage.  $R_{st}$  and  $R_{ed}$  together determine the time constant of the non-quasistatic effect.  $R_{st}$  is modeled by integrating the resistance along the channel under quasi-static assumption,

$$R_{st} = \int dR = \int dV / I_d$$

sion current as

$=V_{ds}/I_d \text{ in triode region; or} (3)$ = $V_{dsat}/I_d \text{ in saturation region,} (4)$ where  $V_{dsat}$  is the saturation drain voltage. Both  $I_d$  and  $V_{dsat}$ are available in BSIM3v3.  $R_{ed}$  can be derived from the diffu-

$$R_{ed} = \frac{qL}{\eta W \mu C_{ax} kT} , \qquad (5)$$

where  $\eta$  is a technology-dependent constant. The overall channel resistance seen from the gate is

$$\frac{1}{R_{gch}} = \gamma \left( \frac{1}{R_{st}} + \frac{1}{R_{ed}} \right) , \qquad (6)$$

where  $\gamma$  is a parameter accounting for the distributed nature of the channel resistance and  $C_{ox}$  (see Fig. 2).  $\gamma$  equals to 12 if the resistance is uniformly distributed along the channel. Since this assumption is not valid in the saturation region,  $\gamma$  is left as a fitting parameter.

#### Verification by Simulation and Experiment

To extract  $R_g$ , two-port s-parameters are converted to yparameters and the input resistance is

$$R_{in} = \operatorname{real}(1/Y_{11}) \tag{7}$$

where gate is connected to port 1 and drain to port 2.  $R_{in}$  includes  $R_g$  and the source/drain resistance  $(R_s/R_d)$ . Since  $R_s/R_d$  is known from dc measurement, the value of  $R_g$  can be extracted from  $R_{in}$ .

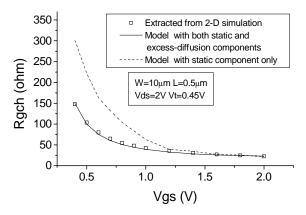

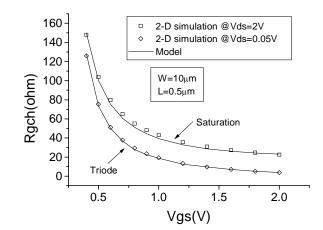

Fig. 4 The effective  $R_g$  model agrees well with 2-D simulation. Inclusion of the excess-diffusion channel resistance is necessary for accuracy in the moderate and weak inversion regions.

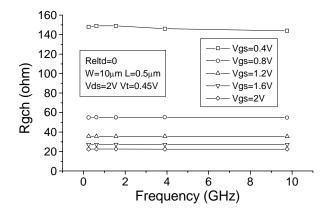

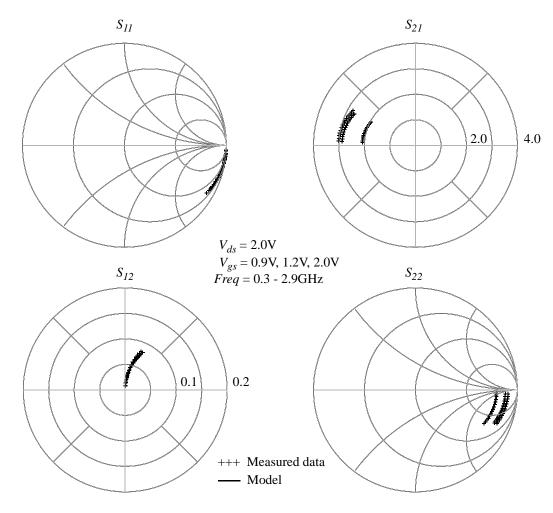

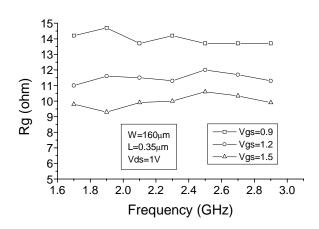

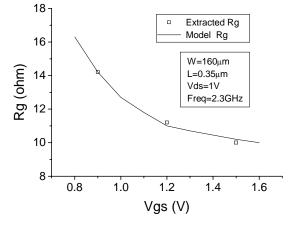

In order to verify the physical model for  $R_{gch}$ , 2-D simulation of  $Y_{11}$  was carried out with  $R_{eltd}$  set to zero. Fig. 3 shows the simulation results of a 10/0.5 NMOS with different bias and frequencies. Essentially  $R_{ech}$  is independent of frequency but sensitive to bias. The result is rearranged in Fig. 4 to emphasize the bias dependency of  $R_{gch}$ . Good agreement between 2-D simulation and the proposed model is observed with  $\eta=1$  and  $\gamma=14$  . Note the model will deviate from data at low  $V_{gs}$  if  $R_{ed}$  is ignored. Fig. 5 shows the good agreement both in triode and saturation regions. RF device test patterns were designed and fabricated with a 0.35µm process. Fig. 6 shows the s-parameters of a 160/0.35 NMOS, both the measured data and the BSIM3v3 RF model in [3] with the proposed effective gate resistance model. Fig. 7 shows the measured  $R_g$  at various bias and frequency. Fig. 8 shows an excellent agreement between the data and the model. In this case  $R_{geltd}$  contributes less than 1 $\Omega$  of the total effective  $R_{g}$ .

Fig. 3 2-D simulation of effective channel resistance  $R_{gch}$  extracted from  $Y_{11}$ . Gate electrode sheet resistance  $R_{eltd}$  is set to zero.

Fig. 5 Effective  $R_g$  model agrees well with 2-D simulations both in triode and saturation regions.

Fig. 6 s-parameters of a 160/0.35 NMOS with 16 fingers at three  $V_{gs}$ . The model agrees with data well.

Fig. 7  $R_g$  extracted from s-parameter data of a 16-finger NMOS.

Fig. 8 Effective  $R_g$  model agrees well with measured data at various  $V_{gs}$ . The gate electrode resistance  $R_{geltd}$  contributes less than 1 $\Omega$  of the overall  $R_g$ .

The gate resistance plays a very significant role in RF noise modeling because  $R_g$  not only affects the input impedance but also contributes to the thermal noise. The overall thermal noise consists of three parts: one is the noise from  $R_g$ ; another is the noise from the physical resistance  $R_d$ ,  $R_s$ ,  $R_{subd}$ , and  $R_{subs}$  (see Fig. 1). The third component is the channel thermal noise current which can be described by its power spectral density as [4]

$$S_{I_d} = \frac{4k}{L_{eff}^2 \cdot I_D} \int_0^{V_{DS}} T_e(V) \left( \mu_{eff} W Q_I(V) - \frac{I_D}{E_c} \right)^2 dV \quad , \tag{8}$$

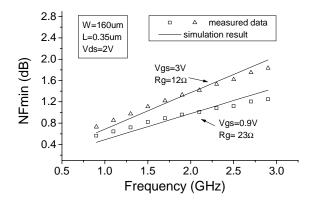

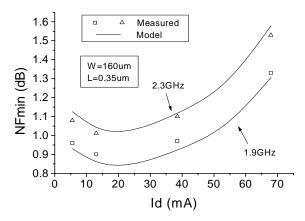

where  $T_e$  is the electron temperature accounting for the hot electron effect,  $\mu_{eff}$  is the effective carrier mobility,  $Q_I$  is the inversion layer charge density, and  $E_c$  is the critical electrical field when carriers reach the saturation velocity, which is used to model the velocity saturation effect. To get the overall noise of a device, the direct calculation method [5] is employed. Fig. 9 shows good agreement between the measured and the modeled minimum noise figure ( $NF_{min}$ ) at various bias and frequency. Fig. 10 shows  $NF_{min}$  vs. bias current with fixed  $V_{ds}$ . A minimum  $NF_{min}$  is observed at a particular bias condition, an important fact for RF circuits such as lownoise amplifiers (LNA). These comparisons show the proposed effective gate resistance model accurately predicts the device noise behavior in addition to the input impedance of CMOS devices.

## Conclusion

A physical effective gate resistance model is proposed for CMOS RF models with significant impact on the input impedance and the noise performance of CMOS devices. With this physics-based bias-dependent  $R_g$  model, now it becomes possible to simulate RF circuits with a unified RF/ noise model. The accuracy of the proposed model has been evaluated with both 2-D simulations and experimental data and good agreement has been observed.

#### Acknowledgment

This work is supported by SRC 98-SJ-417 and California MICRO. The authors would like to thank STMicroelectronics for wafer fabrication and BTA for assistance on dc model extraction.

Fig. 9  $NF_{min}$  prediction by the effective  $R_g$  model agrees well with data at two different  $V_{gg}$ .

Fig. 10 Comparison of  $NF_{min}$  between the measured data and the model. A minimum  $NF_{min}$  is observed at a particular bias.

#### References

[1] W. Liu, et al., "RF MOSFET modeling accounting for distributed substrate and channel resistance with emphasis on the BSIM3v3 SPICE model," in *IEDM Tech. Dig.*, pp. 309-312, Dec. 1997.

[2] D. R. Pehlke, et al., "High frequency application of MOS compact model and their development for scalable RF model libraries," *Proc. of CICC*, pp. 219-222, May 1998.

[3] J.-J. Ou, et al., "CMOS RF modeling for GHz communication IC's," VLSI Symp. on Tech., Dig. of Tech. Papers, pp. 94-95, June 1998.

[4] A. van der Ziel, *Noise in Solid State Devices and Circuits*, New York, Wiley, 1986.

[5] C.-H. Chen, et al.,"Direct calculation of the MOSFET high frequency noise parameters," *Proc. of the 14th International Conference on Noise and Physical Systems and 1/f Fluctuations*, pp. 488-491, July 1997.