**ALGOS**ALGorithms for Optimization and Simulation

# An Efficient Low Power Multiple-value Look-up Table Targeting Quaternary FPGAs

Cristiano Lazzari<sup>1</sup>, Jorge Fernandes<sup>2</sup>, Paulo Flores<sup>2</sup> and *José Monteiro*<sup>2</sup>

<sup>1</sup>INESC-ID Lisbon, Portugal lazzari@inesc-id.pt

<sup>2</sup>INESC-ID / IST, TU Lisbon Lisbon, Portugal {jrf,pff,jcm}@inesc-id.pt

- Motivation

- Binary vs Quaternary Lookup Tables

- New Quaternary-to-Binary Decoder

- Results

- Conclusions and Future Work

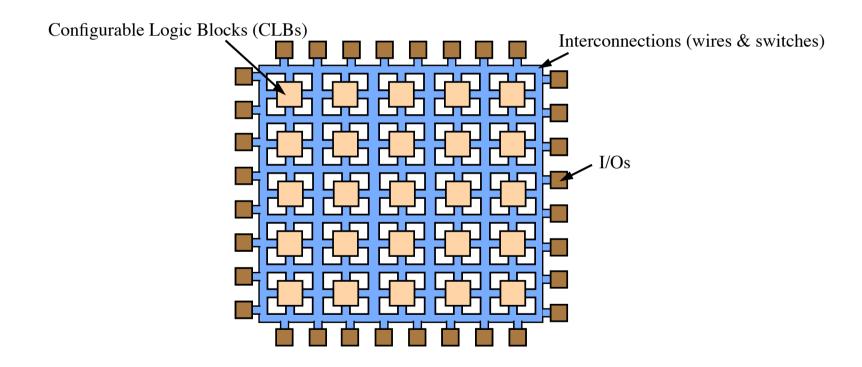

### **Motivation – Field Programmable Gate Arrays**

- Interconnections play crucial role in FPGAs

- They severely impact on power and area (Singh, Sadowska; 2002)

- Up to 90% chip area are interconnections (Cunha, Boudinov, Carro; 2006)

Major limiting factor for developing efficient FPGA designs!

### Introduction – Multiple-Valued Logic (MVL)

Multiple-valued Logic uses more than two logic values

– MVL (quaternary)

### Introduction – Multiple-Valued Logic (MVL)

- Compacting the information with MVL

- Reduced number of wires to represent the same information

- Reduced number of logic blocks to operate over data

- Reduced wire lengths to connect logic blocks

- As a consequence

- Smaller Area due to interconnection reduction

- Power consumption and delay reduction

- reduced load capacitance

- Physical implementation of the interconnects are the same in the binary logic and the MVL

- We are left with the implementation of the logic blocks

### **Multiple-Valued Logic – Early Work**

Multiple-valued logic is not new

| — 1993        | FPGA       | (Zilic, Vranesic)    |  |

|---------------|------------|----------------------|--|

| <b>- 1995</b> | Multiplier | (Hanyu, Kameyama)    |  |

| <b>- 1998</b> | Adder      | (Gonzalez, Mazumder) |  |

1998 Lookup tables (Sheikholeslami, Yoshimura, Gulak)

- Logic is implemented using current-mode devices

- Excessive power consumption

- Complex Design

### A Voltage-Mode MVL Device

- A voltage-mode MVL device has been recently proposed

- Data is represented by quaternary values

- Deals with the power dissipation problem

- Based on standard CMOS circuits

- Requires transistors with different V<sub>th</sub>s

(Cunha, Boudinov, Carro; 2006)

- Multiple V<sub>th</sub>s demand process modifications

- More process steps

- Increased production costs

### **Contributions of This Work**

# Implementation of a new MVL LUT

Voltage-mode device

No additional process steps are required

Competitive with the binary LUTs

### **Binary & Quaternary Lookup Tables**

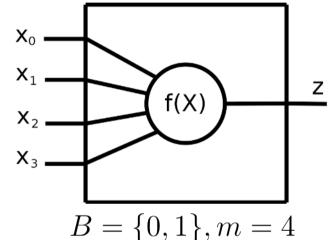

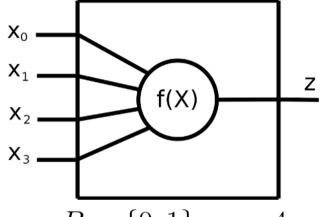

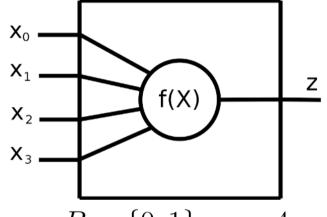

### **BLUT**

$$f:B^m\to B$$

$$X = (x_0, \dots, x_i, \dots, x_{m-1})$$

$Y = (y_0, \dots, y_i, \dots, y_{n-1})$

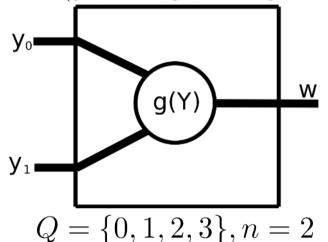

$$g:Q^n \to Q$$

QLUT

$$Y=(y_0,\cdots,y_i,\cdots,y_{n-1})$$

$y_0$

$$Q=\{0,1,2,3\}, n=2$$

$$|Q| = 2 \times |B|$$

### **Binary & Quaternary Lookup Tables**

### BLUT

$$f:B^m\to B$$

$$X = (x_0, \cdots, x_i, \cdots, x_{m-1})$$

$$B = \{0, 1\}, m = 4$$

$$g:Q^n \to Q$$

QLUT

$$X = (x_0, \dots, x_i, \dots, x_{m-1})$$

$Y = (y_0, \dots, y_i, \dots, y_{n-1})$

$$|Q| = 2 \times |B|$$

### **Binary & Quaternary Lookup Tables**

**BLUT**

$$f: B^m \to B$$

$$X = (x_0, \cdots, x_i, \cdots, x_{m-1})$$

$$B = \{0, 1\}, m = 4$$

$$g:Q^n \to Q$$

QLUT

$$X = (x_0, \dots, x_i, \dots, x_{m-1})$$

$Y = (y_0, \dots, y_i, \dots, y_{n-1})$

$$y_0$$

$$f_0(Y)$$

$$W$$

$$y_1$$

$$|Q| = 2 \times |B|$$

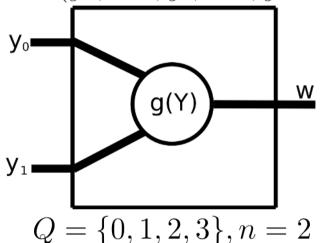

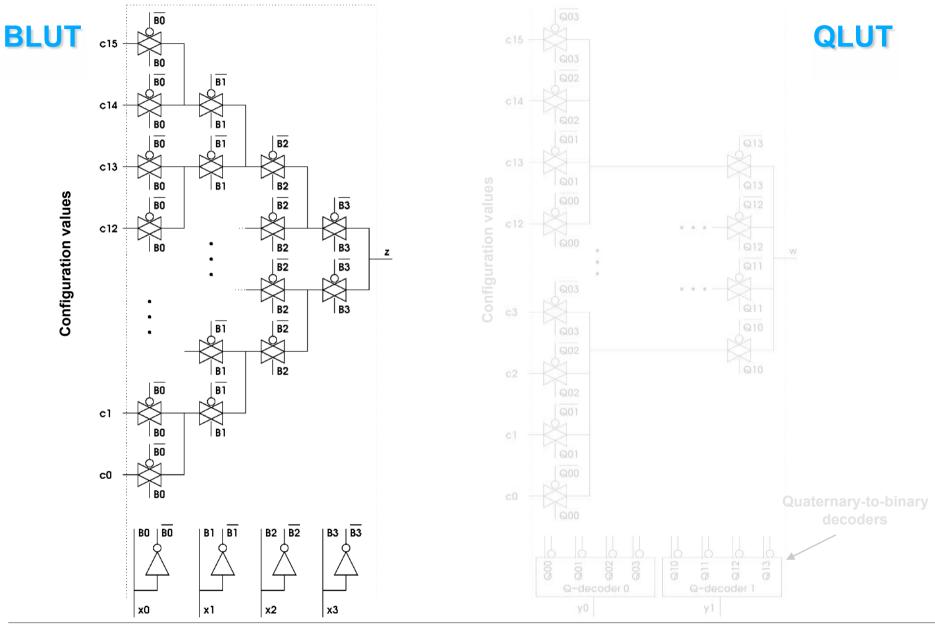

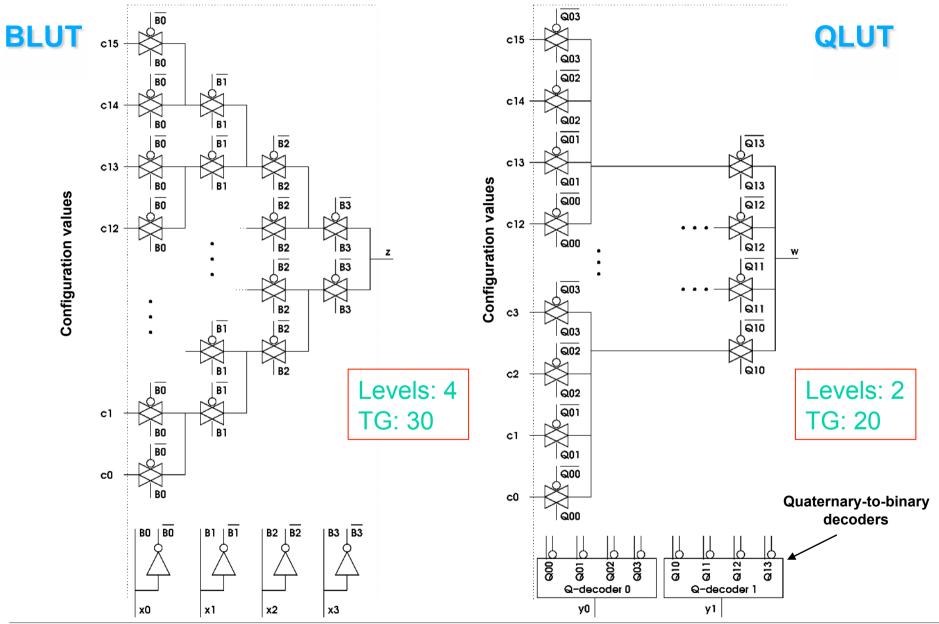

# **Binary & Quaternary LUTs Implementation**

## **Binary & Quaternary LUTs Implementation**

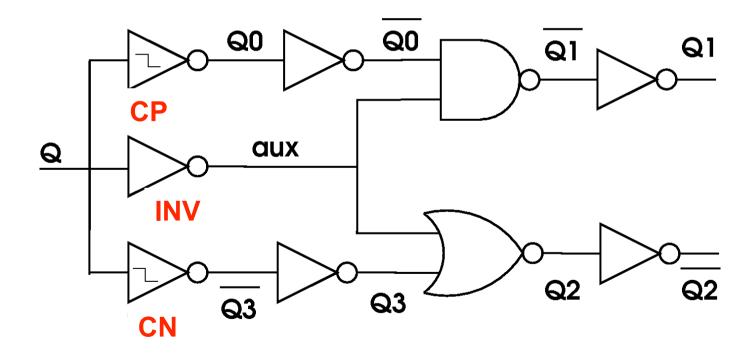

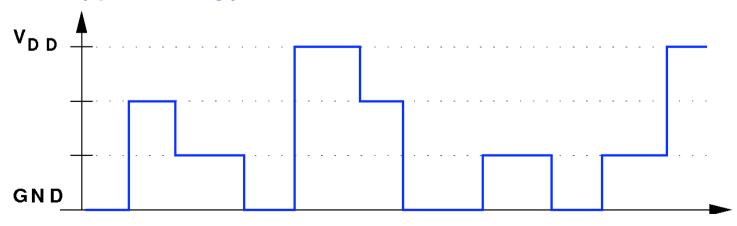

# **Quaternary-to-binary Decoder**

| Q     | $Q_0$ | $Q_1$ | $Q_2$ | $Q_3$ |

|-------|-------|-------|-------|-------|

| $0_4$ | $1_2$ | 0     | 0     | 0     |

| 14    | 0     | $1_2$ | 0     | 0     |

| $2_4$ | 0     | 0     | $1_2$ | 0     |

| $3_4$ | 0     | 0     | 0     | $1_2$ |

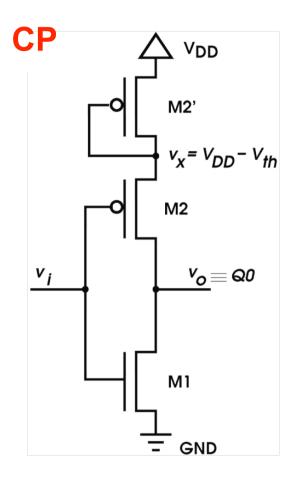

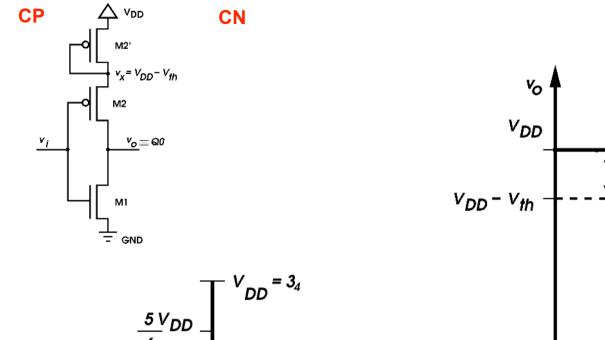

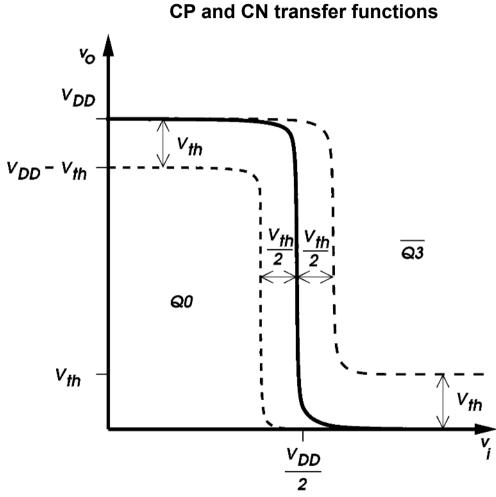

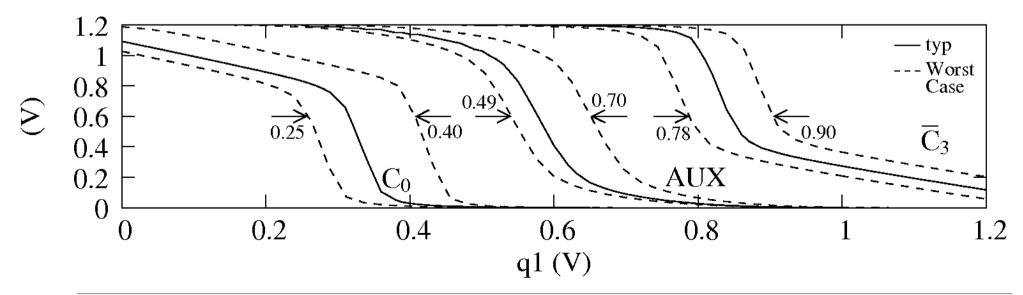

## **Quaternary Comparators**

CN

Output is GND when Vi >= '1'

Output is GND when Vi > '2'

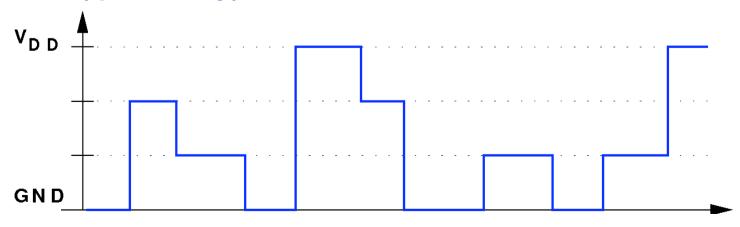

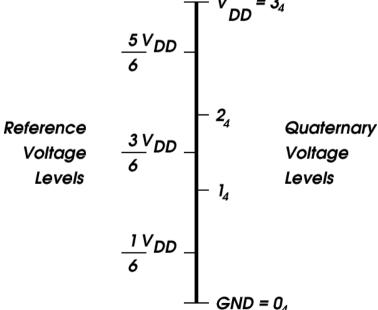

## **Quaternary Logic Levels**

# **Q-decoder Signals Waveforms**

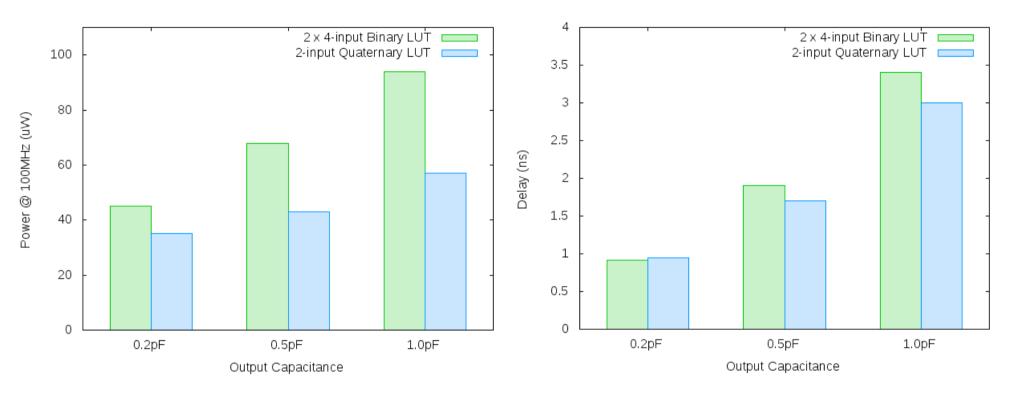

### **Experimental Results**

- UMC 130nm technology (Cadence Virtuoso)

- Vdd = 1.2V, Vth~400mV

- Quaternary LUTs present power gains ranging from 22% to 39%

- Larger gains for larger loads

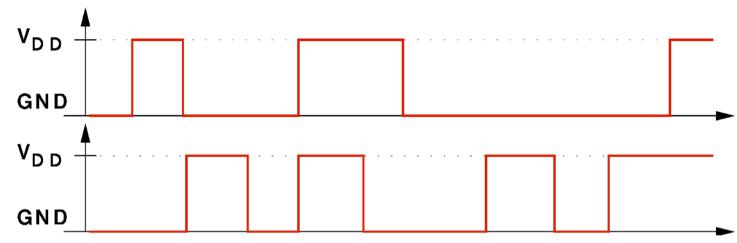

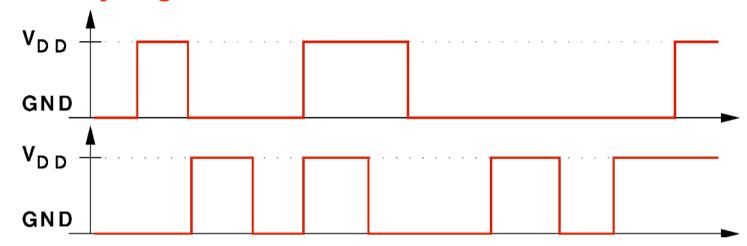

### **Voltage Swing**

On average, the voltage swing is V<sub>DD</sub>/2

### Binary Logic

MVL (quaternary)

## **Process Variability and Noise Margin**

- Process variability and reduced noise margin are important challenges on the development of MVL circuits

- We performed a Monte Carlo simulation

- Considering random process and mismatch variations

- Observed decision levels voltage variations were < 90mV</li>

- A 100mV gap between logic levels is still available

### **Conclusions**

- We propose a new design for a quaternary lookup table

- This design allows for voltage discretization outside the reach of binary logic

- Results show that the proposed technique is competitive with binary FPGAs

- Fabricated chip using 130nm technology is under test

- We are developing a complete FPGA structure

- Logic blocks, switch matrix, etc