## An Electrothermal Model for AlGaN/GaN Power HEMTs Including Trapping Effects to Improve Large-Signal Simulation Results on High VSWR

Olivier Jardel, Fabien De Groote, Tibault Reveyrand, Jean-Claude Jacquet, Christophe Charbonniaud, Jean-Pierre Teyssier, Didier Floriot, and Raymond Quéré, *Senior Member, IEEE*

# Published in IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, VOL. 55, NO. 12, DECEMBER 2007, pp. 2660-2669

© 2007 IEEE Personal use of this material is permitted. However, permission to reprint/republish or redistribute this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

# An Electrothermal Model for AlGaN/GaN Power HEMTs Including Trapping Effects to Improve Large-Signal Simulation Results on High VSWR

Olivier Jardel, Fabien De Groote, Tibault Reveyrand, Jean-Claude Jacquet, Christophe Charbonniaud, Jean-Pierre Teyssier, Didier Floriot, and Raymond Quéré, Senior Member, IEEE

Abstract—A large-signal electrothermal model for AlGAN/GaN HEMTs including gate and drain related trapping effects is proposed here. This nonlinear model is well formulated to preserve convergence capabilities and simulation times. Extensive measurements have demonstrated the impact of trapping effects on the shapes of I(V) characteristics, as well as load cycles. It is shown that accurate modeling of gate- and drain-lag effects dramatically improves the large-signal simulation results. This is particularly true when the output loads deviate from the optimum matching conditions corresponding to real-world simulations. This new model and its modeling approach are presented here. Large-signal simulation results are then reported and compared to load–pull and large-signal network analyzer measurements for several load impedances at high voltage standing wave ratio and at two frequencies.

${\it Index~Terms} \hbox{\it --} AlGaN/GaN~HEMTs~modeling,~drain~lag,~gate~lag,~large-signal~network~analyzer,~trapping~effects.}$

#### I. INTRODUCTION

THANKS TO their very high breakdown voltages and their high sheet carrier densities, AlGaN/GaN HEMTs are a very promising solution for high-power and high-frequency applications. The progress made on their technology over the last few years now make them usable in systems, and hence, there is a need for electrical models. Many topologies and solutions to extract models are reported in the literature [1]–[4]. Here we propose a complete nonlinear model, including the thermal effects and taking into account the electrical anomalies due to the trapping effects. Indeed, the latter have a strong impact on

the electrical performances of these components, and it is hard today to imagine that they will be completely removed soon, even if solutions exist to reduce them.

We will show that modeling the trapping effects dramatically improves the large-signal simulation results, and that this is particularly true when the output loads deviate from the optimum matching conditions.

Thus, such designed models can prove interesting for wideband application designs in which devices cannot be optimally loaded on the whole bandwidth, or also to have an idea of the shapes of the load cycles when the devices are submitted to electrical perturbations (in order, for example, to check if destructive operating modes are reached or not). Considering this last point, this model was also designed to be able to reach high compression levels, i.e., the equations used are well formulated to preserve good convergence capabilities.

This paper is organized as follows. In Section II, the nonlinear model used is described with particular emphasis on the way trapping effects are taken into account. In Section III, the extraction procedure based on pulsed I(V) and pulsed S-parameters is described [5]. It is shown how the time constants of the traps are evaluated, and the results are evaluated for a variety of dc and pulsed I(V) characteristics. In Section IV, classical load–pull measurements, as well as time-domain large-signal measurements, are extensively used to validate the proposed model. Those measurements were performed at two different frequencies, namely, 5 and 10 GHz, and for several load impedances at high voltage standing-wave ratio (VSWR).

#### II. DESCRIPTION OF THE NONLINEAR MODEL

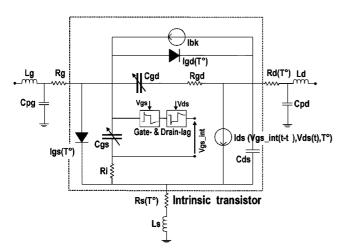

Fig. 1 shows the topology of the complete equivalent circuit we use to model the devices. All the parts of this schematic are described in the following.

#### A. Current Source

The main current source of the model is described by modified Tajima's equations [3], [4]. Both diodes  $D_{\rm GD}$  and  $D_{\rm GS}$  have classical forms.

Manuscript received April 10, 2007; revised July 2, 2007. This work was supported in part by the European Defence Agency under Korrigan Workpackage 3.3 (RTP 102.052) and by the Commissariat à l'Énergie Atomique/Direction des Applications Militaires–Île de France under Contract SL-DAM-O4-010.

O. Jardel, F. De Groote, T. Reveyrand, J.-P. Teyssier, and R. Quéré are with the XLIM  $C^2S^2$ –Unité Mixte de Recherche, Centre National de la Recherche Scientifique, Université de Limoges, 19100 Brive, France (e-mail: olivier. jardel@brive.unilim.fr; degroote@brive.unilim.fr; tibault.reveyrand@xlim.fr; jean-pierre.teyssier@brive.unilim.fr; quere@xlim.fr).

J.-C. Jacquet and D. Floriot are with the Alcatel/Thalès III–V Laboratory, 91460 Marcoussis, France (e-mail: jean-claude.jacquet@3-5lab.fr; didier.floriot@3-5lab.fr).

C. Charbonniaud is with AMCAD Engineering, ESTER Technopole, 87069 Limoges, France (e-mail: christophe.charbonniaud@amcad-engineering.com).

Fig. 1. Structure of the nonlinear model used. Ids equation is given in [5] and charge equations are given in [6]. The extrinsic parameters are assumed constant. Ids, Igs, Igd, Rs, and Rd depend on the temperature.

The equations of the main current source are

$$\begin{split} Id &= Id_t \cdot \gamma_{md} \\ \gamma_{md} &= 1 + \beta gm \cdot (V \text{ds} + V dm) \\ & \cdot (1 + \tanh(\alpha gm \times (V \text{gs\_int} - V gm))) \\ Id_t &= \frac{I_{\text{DSS}}}{1 - \frac{1}{m}(1 - e^{-m})} \left[ V_{\text{GSN}} - \frac{1}{m}(1 - e^{-mV_{\text{GSN}}}) \right] \\ & \cdot \left[ 1 - e^{-V_{\text{DSN}}(1 - aV_{\text{DSN}} - bV_{\text{DSN}}^2)} \right] \\ V_{\text{GSN}} &= 1 + \frac{V_{\text{gs\_int}}(t - \tau) - V\phi}{V_P} \\ V_{\text{DSN}} &= \frac{V_{\text{DS}}}{V_{\text{DSP}} \left( 1 + w \frac{V_{\text{gs\_int}}(t - \tau)}{V_P} \right)} \end{split}$$

and  $V_P = V_{P0} + pV_{DSP} + V\phi$ . The equations of the diodes are

$$ID_{\mathrm{gd}} = I\mathrm{sgd} \cdot e^{\frac{q \cdot V\mathrm{gd}}{k \cdot T \cdot \mathrm{sgd} \cdot N\mathrm{gd}}} \quad ID_{\mathrm{gs}} = I\mathrm{sgs} \cdot e^{\frac{q \cdot V\mathrm{gs}}{k \cdot T \cdot \mathrm{sgs} \cdot N\mathrm{gs}}}.$$

#### B. Trapping Effects

The circuits used here to model the gate- and drain-lag effects and the methods to extract their associated parameters have been described in [7]. Such circuits modeling trapping effects are necessary in advanced modeling of HEMTs, and different solutions have been studied, particularly in [8]–[10].

Here, the effect of the traps is presented as a contribution to the command voltage Vgs. Indeed, the trapping effects induce that Ids = f(Vgs, Vds, Vbias, time), whereas Ids = f(Vgs, Vds) in the ideal case. In the model presented, Ids is unchanged, but the command voltage is modified to take into account the trapping effects. We then have here Ids = f(Vgs, Vds) and Vgs = f(Vbias, time).

Thus, these subcircuits, mounted in series between the gate resistance and the current source (cf. Fig. 1), modify the command voltage of the current source (called Vgs\_int) by adding

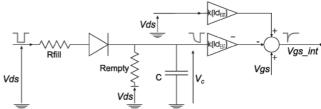

Fig. 2. Schematic of the drain-lag model.

transients to  $V {

m gs.}$  These transients are related to the capture or the emission of charges by the traps.

The drain-lag subcircuit topology, considering only one trap level, is shown at Fig. 2. The gate-lag subcircuit is based on the same architecture, but the input voltage is V g s, and the diode direction and the sign of k are changed.

The capture time constant is given by

$$\tau_{\rm fill} \approx R_{\rm fill} \cdot C$$

(as  $R_{\rm empty} \gg R_{\rm fill}$ ).

The emission time constant is given by

$$\tau_{\text{empty}} = R_{\text{empty}} \cdot C$$

.

In a mathematical form, the circuit gives

$$Vgs\_int = k(Ids_{EST}) \cdot [Vds - V_C] + Vgs$$

with

$$k(Ids_{EST}) = k_{rel} \cdot Ids_{EST}(Vgs) \cdot A_{DL}$$

where  $A_{DL}$  is a fitting factor in Amp<sup>-1</sup>.

The amplification factor k is linked to the amplitude of the trap and we assume that it is linearly dependent on the output current. This current, noted  $I_{\rm dSEST}$ , is an estimate of the total drain current, which is calculated in a very simple fashion, depending only on  $V_{\rm gS}$  (linearly or with a tanh-based law), to preserve the convergence properties of the model. It is then provided by a different source from the one describing the full nonlinear channel current. We will show that this simple description gives, however, accurate results.

Thus, four parameters have to be extracted, i.e., C, Rcmpty, Rfill, and k. It should be noted that, by examining the circuit of Fig. 2 and taking into account the dissymmetry between the two time constants, the level of the control voltage Vgs\_int is mainly determined by the high level of the drain voltage in pulsed conditions.

#### C. Nonlinear Capacitances

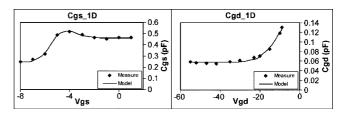

Both capacitances Cgs and Cgd are 1-D [6]. In order to keep them depending on their own terminal voltages (i.e., Vgs for Cgs and Vgd for Cgd), they are extracted along an estimated load line corresponding approximately to the optimum load cycle locus. Modeling them that way is very practical in terms of simplicity of modeling. The impact of such simplification will be quantified in Section III-C.

#### D. Breakdown Model

The breakdown is simply described by exponential increases of the gate and drain currents when the breakdown voltage  $\mathrm{BV}_{\mathrm{GD}}$  is reached. A soft quasi-exponential function is used to keep an expression well suited for convergence [5] as follows:

$$I_{bk} = I_{bkDG} \cdot \exp \operatorname{soft}(\alpha_{DG} \cdot V_{DS})$$

with

$$\exp$$

soft = if  $(x < \max$ arg) then  $\exp(x)$ ,

else  $\max$   $\exp \cdot (x + 1 - \max$ arg)

$\max$ arg =  $\ln(\max$ exp)  $\max$ exp =  $10^{99}$ .

#### E. Thermal Dependence

The self-heating effects have an exponential behavior versus time when the power changes abruptly and, hence, can be reproduced by *RC* cells in an electrical simulator. The input of the circuit is the dissipated power calculated in the following way:

$$P_{\text{DISS}} = I_G \cdot V_{\text{GS}} + I_D \cdot V_{\text{DS}}$$

.

The output of the thermal circuit is a voltage corresponding to the temperature elevation. By adding the room temperature to this voltage, we obtain the device temperature.

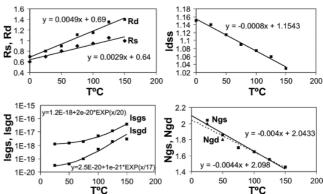

The measurements show that the calculated temperature has an impact on the current source parameters Idss and P [5], the values of the access resistances Rs and Rd, the ideality factors ( $N_{\rm GD}$  and  $N_{\rm GS}$ ) of the diodes  $D_{\rm GD}$  and  $D_{\rm GS}$  linearly, and on the saturation currents (Isgs and Isgd) of the diodes exponentially. Thus, we have

$$X = X_0 + X_T \cdot T$$

where X represents Idss, P, Rs, Rd, Ngs, or <math>Ngd

$$Y = Y_0 + Y_T \cdot e^{(T/Ta)}$$

where Y represents Isgs or Isgd.

III. PULSED  $I\!-\!V$  AND PULSED S-PARAMETERS CHARACTERIZATIONS: EXTRACTION OF THE PARAMETERS

The measurements were performed on a 600- $\mu$ m (8  $\times$  75  $\times$  0.25  $\mu$ m) Al<sub>0.27</sub>Ga<sub>0.73</sub>N/GaN HEMT from Thalès–Tiger grown by MOCVD on an SiC substrate.

#### A. Trapping Circuits Parameters

The parameter extraction is obtained by measuring the current transients during voltage pulses for which traps emit their charges. The form of these transients can be fitted by a few exponential terms. In the current case, two terms (i.e., two trapping levels) were chosen for both gate- and drain-lag circuits. This choice represents a tradeoff between the accuracy of the fit and the complexity of the circuit. However, it is not worth obtaining an excellent fit, as the trapping time constants strongly depend on the temperature, which is not taken into account in the model. On the other hand, it is important to avoid "parasitic"

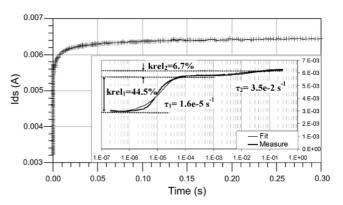

Fig. 3. Measurement of a drain-lag related current transient.  $V{\rm gs}$  is kept at a fixed value equal to  $-6{\rm \,V}$ , whereas  $V{\rm \,ds}$  is pulsed from 30 to 20 V. Self-heating effects are negligible in this case. The fit of the transient and the parameters extracted are also displayed.

exponential terms due to self-heating during the measurements. That means that the thermal state of the device needs to remain: 1) the same before and during the pulse and 2) close to the one of the bias point of the spotted application because of the thermal dependence of the emission time constants.

In order to obtain the drain-lag related emission time constants,  $V{\rm ds}$  was pulsed from 30 to 20 V and  $V{\rm gs}$  fixed close to pinchoff in order to obtain a very low drain current to avoid thermal effects (the dissipated power variation is less than 0.05 W), and the temperature of the chuck was set to 110 °C in order to make the device work approximately in the same thermal state as for the foreseen application in class AB. The current transient, and also the curve modeling it by a sum of two exponential terms, are shown at Fig. 3. The main extracted parameters are also displayed on this figure.

Gate-lag related emission time constants are less precisely obtained, thermal transients being harder to avoid during measurements. We pulse the gate-source voltage in a short range near of  $V_{\rm SS\_bias}$  with  $V_{\rm CS\_bias}$  equal to  $V_{\rm CS\_bias}$ . This implies that the temperature is close to that of the application.

The capture time constants are not extracted from measurements, as they are too fast to be measured in this case, and generally in most devices. However, it is worth noting that the key point to obtain good results in continuous wave (CW) large-signal applications is the asymmetry between short capture time constants and large emission time constants. Thus, the values are fixed to a few nanoseconds.

#### B. Pulsed I–V Measurements and Current Sources Parameters Extraction

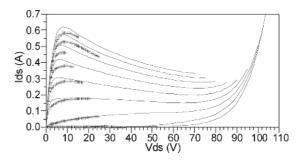

In order to obtain the static characteristics of the device and to extract the current source parameters, pulsed I-V measurements are performed at the room temperature. The current source parameters are extracted from pulsed I-V measurements at a quiescent bias point of V gs0 = 0 V and V ds0 = 0 V (case 1). This quiescent bias point is chosen in order to: 1) obtain a quasi-isothermal measurement as pulses are very short (400 ns) and 2) to avoid trapping effects. Indeed, for this quiescent bias point configuration, the classical I-V curves measurement implies that V gs is pulsed down and V ds is pulsed up. Hence, the

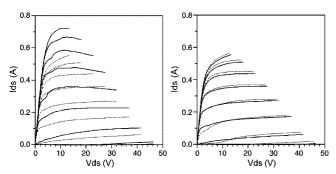

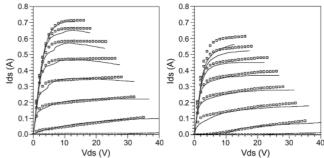

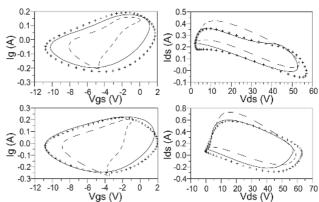

Fig. 4. 400-ns pulsed-IV measurements (with V gs from -8 to 1 V) on the  $8 \times 75~\mu m$  transistor at three different quiescent bias points. (left) V gs0 = 0 V and V ds0 = 0 V (case 1): continuous lines; V gs0 = -8 V and V ds0 = 0 V (case 2): dashed lines. (right) V gs0 = -8 V and V ds0 = 0 V (case 2): continuous lines; V gs0 = -8 V and V ds0 = 20 V (case 3): dashed lines. The differences on the left are attributed to gate-lag effects, whereas they are attributed to drain-lag effects on the right.

gate- and drain-lag related traps are filling. Considering that this filling phenomenon is very fast compared to pulse duration, the traps state is given by the voltage levels during the pulses.

The parameters of the diodes and the breakdown generator are also extracted from this measurement configuration.

Other quiescent bias point choices allow us to observe the trapping effects and even to separate gate- and drain-lag effects. Such types of measurements will also be useful to validate the trapping circuit parameters extraction. We can focus on the two following configurations [11].

- 1) If the quiescent bias point is, for example, V gs0 = -8 V (when the device is pinched off) and V ds0 = 0 V (case 2), the gate— and drain—source voltages are pulsed up during the measurement. Hence, the traps commanded by drain—source voltage are filling (fast), and the traps commanded by gate—source voltage are emptying (slowly). We can conclude that inside the pulse, the traps commanded by gate—source voltage remain in the state they had at quiescent bias point, and the state of the traps commanded by the drain—source voltage has changed and is now given by the drain—source voltage level inside the pulse.

- 2) If the quiescent bias point is, for example, V gs0 = -8 V (pinched off) and V ds0 = 20 V (case 3), the drain–source voltage is pulsed down for the measurement points where V ds < 20 V and pulsed up for V ds > 20 V.

Considering that the traps' discharge is very slow compared to the duration of the pulses, the state of the traps inside a pulse is that of the quiescent bias point for  $V \, \mathrm{ds} < 20 \, \mathrm{V}$ , and that of the drain–source voltage for  $V \, \mathrm{ds} > 20 \, \mathrm{V}$ .

Superimposed on Fig. 4 are three pulsed I(V) networks corresponding to the three cases of quiescent biases described earlier. The current is approximately 1.25 A/mm. We note that the current dispersion, for this device, is mainly due to the gate-lag effects. The drain-lag effects induce an increase of the knee voltage, especially manifest at low current.

This device presents an unusual behavior of the drain lag, as the saturation current is higher when  $V ds\_bias = 20 \text{ V}$  than when  $V ds\_bias = 0 \text{ V}$ . However, the difference is weak and was not observed on the other measured devices.

Fig. 5. Measured and simulated pulsed I–V networks at Vgs0 = 0, Vds0 = 0 and at Vgs0 = -8 V, Vds0 = 20 V on the  $8 \times 75 \,\mu \mathrm{m}$  transistor for Vgs from -8 to +1 V (continuous lines: measurements, squares: simulations).

Fig. 6. 1-D nonlinear forms of  $C\mathrm{gs}$  and  $C\mathrm{gd}$  with equations based on hyperbolic tangents. The points correspond to values extracted along the estimated load cycle, the lines correspond to the model.

It has to be noted that we took care to maintain the output current equal to 0 A at the quiescent bias points and that we chose the length of the pulses as short as possible to avoid thermal effects and their influence on output current.

The simulated pulsed I-V characteristics are shown and compared to measurements at Fig. 5. We note that the proposed model can take into account the value of the quiescent bias, thus dramatically increasing the range of validity of the model. However, small discrepancies remain at high  $V \, {\rm gs}$  voltages (around  $V \, {\rm gs} = 1 \, {\rm V}$ ). This can be due to: 1) the relative simplicity of the trapping circuits and/or 2) to a slight difference between several measured devices.

## C. Pulsed S-Parameters Measurements and Frequency-Dependent Parameters Extraction

The pulsed S-parameters are measured for each point of the I(V) networks [5]. The extrinsic parameters are extracted from these S-parameters and then the intrinsic elements are calculated for each measured point. This multibias S-parameters extraction gives, in particular, the values of Cgs and Cgd for the points measured along the estimated load line. Very precise fits are obtained along the latter with tanh-based equations [6], as is shown at Fig. 6.

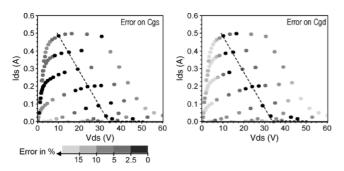

The errors made by using such 1-D forms are shown on Fig. 7 on a whole  $I\!-\!V$  network. These errors remain weak on a large area for  $C\mathrm{gs}$ , while they rapidly increase for low values of  $V\mathrm{ds}$  for  $C\mathrm{gd}$ . However, those capacitance models ensure a very robust behavior of the model even at high compression levels.

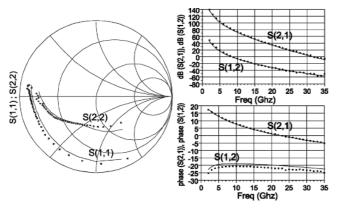

Other intrinsic parameters, i.e., Rgd, Ri, Cds, and  $\tau$ , are kept constant (18.5  $\Omega$ , 0.65  $\Omega$ , 139 fF, and 1.88 ps<sup>-1</sup>, respectively).

Fig. 7. Error made on capacitance values by using 1-D equations. (left) Cgs. (right) Cgd. From black to light gray points, error is respectively inferior to 2.5%, between 2.5%–5%, between 5%–10%, between 10%–15%, and superior to 15%. The dashed lines represent the estimated load lines.

Fig. 8. Measured and modeled pulsed S-parameters at a quiescent bias point of  $V{\rm gs0}=-4$  V,  $V{\rm ds0}=25$  V and a pulse level at  $V{\rm gs0}=-4$  V,  $V{\rm ds0}=24$  V on the 8  $\times$  75  $\mu{\rm m}$  transistor (measurements: points, model: continuous lines).

Fig. 8 shows a comparison between measured and modeled S-parameters at the bias point for a characterization at a quiescent bias point equal to the bias point of the spotted application.

#### D. Thermal Circuit Parameters and Thermal Dependence

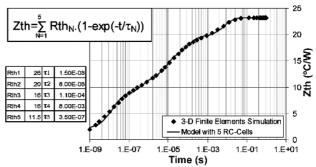

The thermal circuit is obtained by fitting the hot spot temperature transient obtained by 3-D finite-element simulations. Fig. 9 shows the self-heating obtained by applying a dissipated power of 7 W/mm, and also the fit obtained by modeling it with five *RC* cells.

Measurements have been performed on these devices to confirm the values obtained from the 3-D simulation and a relatively good agreement has been found for the thermal resistance. However, time constants of trapping and thermal effects mix together and are very difficult to separate. Thus, we relied on the 3-D simulation (validated in [12]) to derive the dynamical thermal subcircuit, as shown at Fig. 9.

*Note*: Fig. 9 shows that the self-heating is not negligible after 400 ns, which corresponds to the typical pulse duration during pulsed I(V) measurements. However, it is difficult to obtain shorter pulses considering the voltage and current ranges applied. Moreover, the temperature modeled is that of the point located at the center of the channel, having the fastest heating.

Fig. 9. Extraction of the thermal impedance versus time of the modeled device. Simulations are performed with a 3-D model of the transistor in the software ANSYS. The points correspond to the simulated self-heating for a dissipated power of 7 W/mm, the continuous lines corresponds to the values given by the electrical model with five *RC* cells.

Fig. 10. Thermal dependence of parameters of the model: the access resistances Rs and Rd, the parameter of the Tajima's current source Idss, and the ideality factors of the diodes Ngs and Ngd, linearly dependent on the temperature; the saturation currents of the diodes, exponentially dependent on the temperature (points: extracted values, continuous lines: model, excepted for Ngd (dashed line).

Fig. 11. Measured and modeled dc I(V) curves for Vgs from -8 to +1 V. The modeled breakdown locus is also showed (measurements: crosses, model: continuous lines).

The thermal dependence of the current source parameters is obtained by fitting quasi-isothermal pulsed I(V) networks measured at several chuck temperatures (typically from  $-60\,^{\circ}\text{C}$  to  $200\,^{\circ}\text{C}$ ): the values of most parameters remain the same, but they have to be changed for some of them (cf Section II-E). The variations obtained in this case are shown at Fig. 10.

A comparison between dc I(V) measurements and simulations is given at Fig. 11 (the modeled breakdown locus is also

Fig. 12. Measured and modeled load impedances at 10 GHz on the 8  $\times$  75  $\mu m$  transistor. The VSWR values are calculated with respect to  $Z{\rm opt}$ .

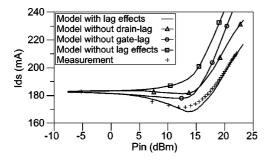

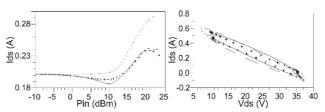

Fig. 13. Measured (crosses) and modeled average output current in different conditions: by taking into account any trapping effect, by modeling only gate lag, by modeling only drain lag, and by modeling gate and drain lag, at the optimum load impedance.

shown). The quite good correlation validates the method of thermal modeling, despite the approximations made: the "hot spot" temperature is not fully representative of the temperature of the transistor, but extracting it from the simulator in order to model the self-heating is the most practical way in terms of easiness and time. Moreover, and for example, we remarked that it is not worth modeling the thermal impedance of several representative points in the device structure [13] (in the access areas for Rs and Rd, in the active area for the other parameters), as the gain in precision on the electrical simulations is negligible, even if it allows knowing more precisely the temperature at each of these points.

# IV. VALIDATION OF THE MODEL AGAINST LARGE-SIGNAL MEASUREMENTS: SIMULATIONS ON SEVERAL LOAD IMPEDANCES

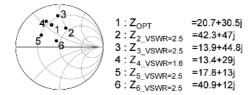

Load-pull measurements were performed at a drain bias of 25 V (dc) in class AB and at 10 GHz (CW) for several load impedances, shown at Fig. 12. These load impedances correspond to a VSWR of 2.5, except for a point at a VSWR of 1.6 (load 4).

### A. Load—Pull Measurements/Simulations on the Optimum Load Impedance

First, large-signal simulations were performed on the optimum load impedance (load 1 in Fig. 12). A maximum power of 2.5 W (4 W/mm) was measured with a small-signal gain of 15.5 dB and a maximum power-added efficiency (PAE) of 39%. The comparison between measurements and simulations is given at Figs. 13 and 14, and demonstrates the improvement brought by the new model. The impact of trapping effects on the

Fig. 14. Measured and modeled power characteristics (gain, output power, PAE, magnitude and phase of the input reflection coefficient, versus input power (measurements: points, simulations: continuous lines) at the optimum load impedance at 10 GHz.

average current is particularly obvious, and both effects have an influence on it. The current decrease with increasing power is a significant consequence of the asymmetric nature of the traps capture and emission processes and cannot be attributed to the thermal effects, which are also modeled. Indeed, the traps state is determined by the peak values of  $V \rm gs$  and  $V \rm ds$ , which increase when the input power increases.

## B. Load–Pull Measurements/Simulations on Output Impedance Mismatches

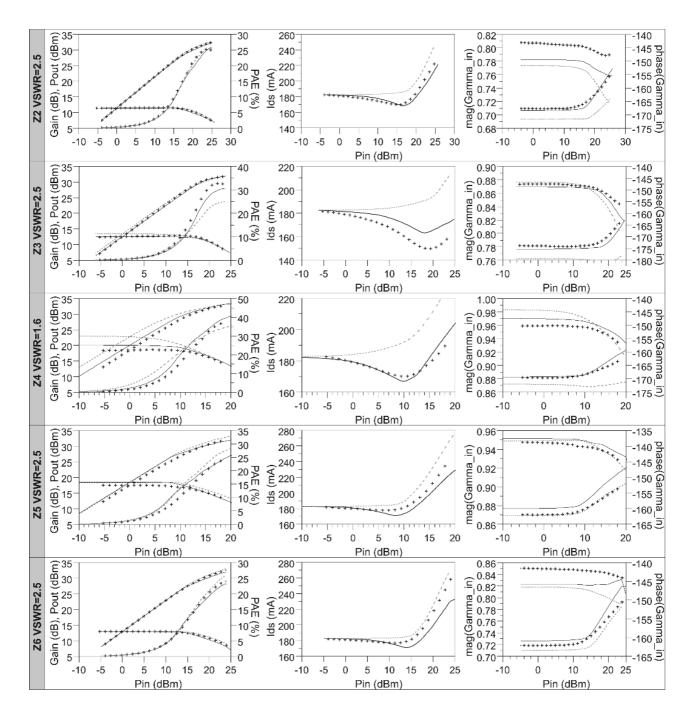

The large-signal simulation results on other load impedances are shown in Fig. 15 in the numbering order given in Fig. 12.

These results of simulations with trapping effects included are better for all the impedances contouring the optimum load, and especially the mean output current and PAE. They validate the fact that the model is able to reproduce the large-signal characteristics on a wider range of load impedances when the trapping effects are taken into account.

We can note that the influence of the trapping effects on the output current depends on the load impedance and, therefore, on the forms of the load cycles and voltages excursions. On  $Z_2, Z_3$ , and  $Z_4$ , the trapping effects are significant, leading to bad behavior of the model without trapping subcircuits. On  $Z_5$  and particularly on  $Z_6$ , the trapping effects have less influence (the current do not decrease strongly before the compression), and the characteristics could be fairly well reproduced without modeling the trapping effects. However, these cases are isolated, and the characteristics are all better reproduced when the trapping effects are taken into account, even if they are quite simply modeled.

Fig. 15. Comparison between measurements and simulations for the load impedances 2–6 with the model including trapping effects and the model not including them (crosses: measurements, continuous lines: model with trapping effects, dashed gray lines: model without trapping effects).

It has to be noted that the input reflection coefficient ( $\gamma_{\rm in}$ ) is also better modeled when the trapping effects are taken into account. This is important to predict instabilities or to adapt the devices inputs.

This proves that modeling the traps is very important for these types of devices, as the models which do not include the trapping effects show their limitations when the load impedance is modified. This is all the more true as the transistors mounted in amplifiers cannot be loaded on the optimum impedance in many cases. An example is the case of wideband amplifiers, for which the matching is often chosen for the most critical frequency in terms of power, and represents a compromise in order to meet the specifications on the entire bandwidth. Another example is the case of systems terminated by antennas, which can receive RF power and then transmit it to the outputs of the transistors, thus modifying their load impedances. Such behavior deserves a

Fig. 16. Measured and modeled load impedances at 5 GHz on the  $8\times75~\mu\mathrm{m}$  transistor. The line delimits the stability area at 5 GHz.

Fig. 17. Comparison between measurements and simulations (with and without trapping effects included) at the optimum load impedance (Z=47.7+j.43.5). Waveforms are shown at 5-dB compression (crosses: measurements, continuous lines: simulations with trapping effects, dashed lines: simulations without trapping effects).

more detailed analysis, which can be performed through simulations and time domain load–pull measurements, as presented in Section V.

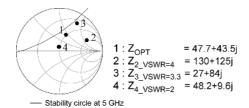

# V. LARGE-SIGNAL NETWORK ANALYZER (LSNA) MEASUREMENTS AND SIMULATIONS ON SEVERAL LOAD IMPEDANCES

Load–pull measurements with an LSNA [14], [15] were performed at 5 GHz on a transistor of the same process and the same development, but fabricated on another wafer. The model was, however, unchanged and simulations were performed in the same conditions as for measurements. Our LSNA load–pull setup allows reconstructing the time-domain waveforms with a cutoff frequency of 20 GHz. Thus, we are able to measure the four first harmonics at 5 GHz, which allows a good precision on the waveforms even at high compression levels. Measurements have been performed on several load impedances, located on a Smith chart in Fig. 16 and numbered from 1 to 4. Optimum load could not be encircled, as the device became unstable (the simulated stability circle at 5 GHz is also shown). From Figs. 17–19, results of simulations are compared to these measurements and will be commented upon.

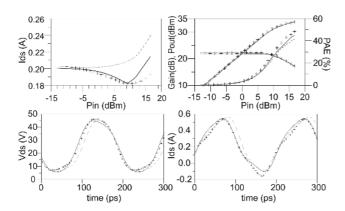

On the optimum load impedance (Fig. 17), we note that both models (with and without trapping effects) give good power results, except for the dc output current form, where the model with traps gives better results. However, the waveforms (here at 5-dB compression) are better described when trapping effects are activated.

Fig. 18. Comparison between measurements and simulations (with and without trapping effects included) of the extrinsic input and output load cycles at load impedance 2 (Z=130+j.125) at 4.6-dB compression for the top graphs, and at load impedance 3 (Z=27+j84) at 7-dB compression for the bottom graphs (crosses: measurements, continuous lines: simulations with trapping effects, dashed lines: simulations without trapping effects).

Fig. 19. Comparison between measurements and simulations (with and without trapping effects included) of the dc output current and the extrinsic output load cycle at load impedance 4(Z=48.1+j.9.6) at 8-dB compression (crosses: measurements, continuous lines: simulations with trapping effects, dashed lines: simulations without trapping effects).

In Fig. 18, the measured and simulated input and output extrinsic load cycles are shown for load impedances 2 and 3 (at 4.6- and 7-dB compression, respectively). We remark that the input load cycles are better described when trapping effects are activated. It shows particularly well the importance of the capacitances C g s and C g s on the extrinsic waveforms at the input: these are swept differently, as the output current is better modeled when trapping circuits are activated. The output load cycles are also better described, but we can note that the maximum value of V d s is never reached by the models, which may be due to the relative imprecision of the current source at low current, and the strong impact of the trap levels on the buffer conduction at pinchoff.

In Fig. 19, the measured and simulated (with and without trapping effects) dc output current and output load cycle for load impedance 4 are shown. Measurements were driven at a very high level of compression (8 dB). It is interesting to note that the model with activated trapping effects is able to simulate quite well the output load cycle (and particularly the increase of the knee voltage due to the trapping effects), and the abrupt collapse of the dc current when the input power reaches 20 dBm.

#### VI. CONCLUSION

A nonlinear model for AlGaN/GaN HEMTs was proposed especially for high power amplifier design, and then the most im-

portant nonlinearities, i.e., the nonlinear capacitances C g s and C g d, thermal effects, and trapping effects were taken into account. They have been described in a simple fashion in order to keep a good tradeoff between the accuracy of the simulation results and the convergence, simulation times, and extraction procedure duration.

We have demonstrated here that including trapping effects in a nonlinear model has a significant impact on large-signal results, especially the output loads that deviate from the optimum matching conditions.

The design of the lag subcircuits has two main advantages: only one parameter has to be changed to reproduce the variations of the lag amplitudes, as it is often the case among several transistors of a wafer, and adding them do not require modifying the topology of the main current source. Hence, they can be separately implemented in other nonlinear models.

Many simplifications were done in the description of the trapping effects, and the most interesting way of improvement seems to take into account the thermal dependence of the trapping time constants, and to describe the amplitude of the traps as not only depending on the current. However, these improvements should be reserved for specific studies, as they will undoubtedly have a strong impact on the convergence of the model.

The simulations performed with this model are fast, and we did not notice convergence problems. Activating/deactivating the lag subcircuits multiplies the simulation times in harmonic balance by an approximate factor of 1.5.

#### ACKNOWLEDGMENT

The authors wish to acknowledge the European Defense Agency (EDA), Brussels, Belgium, and the Commissariat à l'Énergie Atomique/Direction des Applications Militaires (CEA/DAM)–Île de France, Bruyère-le-Châtel, France, and Dr. D. E. Root, Agilent Technologies, Santa Rosa, CA, for his valuable advice and comments.

#### REFERENCES

- [1] I. Angelov, V. Desmaris, K. Dynefors, P. Å. Nilsson, N. Rorsman, and H. Zirath, "On the large-signal modelling of AlGaN/GaN HEMTs and SiC MESFETs"," in *Gallium Arsenide and Other Semiconduct. Applicat. Symp.*, Oct. 3–4, 2005, pp. 309–312.

- [2] T. J. Brazil, "A universal large-signal equivalent circuit for GaAs MESFET," in *Proc. 21st Eur. Microw. Conf.*, Stuttgart, Germany, 1991, pp. 921–926.

- [3] Y. Tajima and P. D. Miller, "Design of broad band power GaAs FET amplifiers," *IEEE Trans. Microw. Theory Tech.*, vol. MTT-32, no. 3, pp. 261–267, Mar. 1984.

- [4] J. P. Teyssier, J. P. Viaud, and R. Quéré, "A new nonlinear I(V) model for FET devices including breakdown effects," IEEE Microw. Guided Wave Lett., vol. 4, pp. 104–106, Apr. 1994.

- [5] J. P. Teyssier, P. Bouysse, Z. Ouarch, D. Barataud, T. Peyretaillade, and R. Quéré, "40-GHz/150-ns versatile pulsed measurement system for microwave transistor isothermal characterization," *IEEE Trans. Microw. Theory Tech.*, vol. 46, no. 12, pp. 2043–2052, Dec. 1998.

- [6] S. Forestier, T. Gasseling, P. Bouysse, R. Quéré, and J. M. Nebus, "A new nonlinear capacitance model of millimeter wave power PHEMT for accurate AM/AM–AM/PM simulations," *IEEE Microw. Wireless Compon. Lett.*, vol. 14, no. 1, pp. 43–45, Jan. 2004.

- [7] O. Jardel, F. De Groote, C. Charbonniaud, T. Reveyrand, J. P. Teyssier, R. Quéré, and D. Floriot, "A drain-lag model for AlGaN/GaN power HEMTs," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Honolulu, HI, Jun. 2007, pp. 601–604.

- [8] M. S. Shirokov, R. E. Leoni, III, J. Bao, and J. C. M. Hwang, "A transient SPICE model for digitally modulated RF characteristics of ion-implanted GaAs MESFETs," *IEEE Trans. Electron Devices*, vol. 47, no. 8, pp. 1680–1681, Aug. 2000.

- [9] K. Kunihiro and Y. Ohno, "A large-signal equivalent circuit model for substrate-induced drain–lag phenomena in HJFET's," *IEEE Trans. Electron Devices*, vol. 43, no. 9, pp. 1336–1342, Sep. 1996.

[10] W. R. Curtice, J. H. Benett, D. Suda, and B. A. Syrett, "Modeling of

- [10] W. R. Curtice, J. H. Benett, D. Suda, and B. A. Syrett, "Modeling of current lag in GaAs IC's," in *IEEE MTT-S Int. Microw. Symp. Dig.*, 1998, vol. 2, pp. 603–606.

- [11] C. Charbonniaud, S. De Meyer, R. Quéré, and J. P. Teyssier, "Electrothermal and trapping effects characterization of AlGaN/GaN HEMTs," in 11th GAAS Symp., Munich, Germany, Oct. 6–7, 2003, pp. 201–204.

- [12] R. Aubry, J. C. Jacquet, J. Weaver, O. Durand, P. Dobson, G. Mills, M. A. Di Forte Poisson, S. Cassette, and S. L. Delage, "SThM temperature mapping and non-linear thermal resistance evolution with bias on AlGaN/GaN HEMT devices," *IEEE Trans. Electron Devices*, vol. 54, no. 3, pp. 385–390, Mar. 2007.

- [13] J. C. Jacquet, R. Aubry, H. Gérard, E. Delos, N. Rolland, Y. Cordier, A. Bussutil, M. Rousseau, and S. L. Delage, "Analytical transport model of AlGaN/GaN HEMT based on electrical and thermal measurement," in *Proc. 12th GaAs Symp.*, Amsterdam, The Netherlands, Oct. 11–15, 2004, pp. 235–238.

- [14] F. De Groote, O. Jardel, J. Verspecht, D. Barataud, J. P. Teyssier, and R. Quéré, "Time domain harmonic load–pull of an AlGaN/GaN HEMT," presented at the 66th ARFTG, Washington, DC, Dec. 2005.

- [15] D. Barataud, C. Arnaud, B. Thibaud, M. Campovecchio, J. M. Nebus, and J. P. Villotte, "Measurements of time-domain voltage/current waveforms at RF and microwave frequencies based on the use of a vector network analyzer for the characterization of nonlinear devices-application to high efficiency power amplifiers and frequency-multipliers optimization," *IEEE Trans. Instrum. Meas.*, vol. 47, no. 5, pp. 1259–1264, Oct. 1998.

Olivier Jardel was born in Poitiers, France, in November 1981. He received the Engineer degree from the Aix-Marseille I University, Marseille, France, in 2004, and is currently working toward the Ph.D. degree in electrical engineering at the common laboratory between the XLIM Laboratory, Université de Limoges and Alcatel/Thalès III–V Laboratory, France.

His main research interests include the characterization and modeling of semiconductor microwave power devices and their related electrical defects.

Fabien De Groote was born in Limoges, France, in 1981. He received the Master Research degree and Engineer degree from the Université de Limoges, Limoges, France, both in 2004, and is currently working toward the Ph.D. degree at Université de Limoges.

He is currently with the XLIM Laboratory, High Frequency Components Circuits Signals and Systems Department, Université de Limoges. His main interests are nonlinear time-domain analysis and pulsed power measurements of microwave active devices.

**Tibault Reveyrand** was born in Paris, France, in 1974. He received the Ph.D. degree from Université de Limoges, Limoges, France, in 2002.

From 2002 to 2004, he was Post-Doctoral Scientist with the Centre National d'Etudes Spatiales (CNES) (French Space Agency). In 2005, he became a Contractual Engineer with the Centre National de la Recherche Scientifique (CNRS), XLIM [formerly the Institut de Recherche en Communications Optiques et Microondes (IRCOM)], Limoges, France. His main research interests include the characteriza-

tion and modeling of RF and microwave nonlinear components.

**Jean-Claude Jacquet** received the Engineer degree from the Ecole Supérieure d'Optique, Orsay, France, in 1990.

He subsequently joined the Central Research Laboratory of Thalès, as a Research Staff Member, where he was involved with spintronic devices. He focused his efforts on the giant magnetoresistive effect and found a new physical effect called the magnetorefractive effect. Since 1999, he has been involved with GaInP HBT and GaN HEMT microwave power devices. He is in charge of the optimization of thermal

and breakdown aspects with the Alcatel/Thalès III–V Laboratory, Marcoussis, France. He is also involved in vacuum cold electrons emission projects.

Christophe Charbonniaud was born in Limoges, France, in 1972. He received the Master Research degree from Université de Limoges, Limoges, France, in 2001, and the Ph.D. degree from the Research Institute on Microwave and Optical Communications XLIM [formerly the Institut de Recherche en Communications Optiques et Microondes (IRCOM)], Université de Limoges, in 2005.

He is a cofounder of AMCAD Engineering, ESTER Technopole, Limoges, France, where he

is involved with power devices measurements and modeling.

**Jean-Pierre Teyssier** was born in Brive, France, in 1963. He received the Master and Ph.D. degrees from the Université de Limoges, Limoges, France, in 1990 and 1994, respectively.

Since 1995, he has been a Researcher with the XLIM [formerly the Institut de Recherche en Communications Optiques et Microondes (IRCOM)] Laboratory and Teacher with Université de Limoges, Limoges, France. His research topics include computer science, programming (C++), database (SQL), embedded systems, real time systems, and

data networks. His main research interests include RF nonlinear measurements, designs of new time-domain and pulsed systems, embedded software for bench equipments, bench control, and modeling software.

**Didier Floriot** was born in Paris, France, in 1967. He received the Electrical Engineering degree from Supelec, Gif-sur-Yvette, France, in 1992, and the M.S. and Ph.D. degrees from Paris VI University, Paris, France, in 1993 and 1995, respectively.

He then joined the Thales Research Center, where he was involved with the development of the power InGaP/GaAs HBT technology for radar and space applications and on the integration of this technology inside demonstrators. He has also been involved with the electrical robustness, reliability aspects, and

thermal management of this technology for high-power applications. He is currently Team Leader with the Alcatel/Thalès III–V Laboratory, Marcoussis, France, a joint research group involved with III–V optomicrowave devices and power semiconductors. His fields of interest cover modeling, characterization, and design of power devices including III–V and III–N semiconductors. He is Scientific Advisor for Thalès on the integration of new technologies inside radar programs. He is also Co-Director of the common laboratory between Alcatel/Thalès III–V Laboratory and the XLIM [formerly the Institut de Recherche en Communications Optiques et Microondes (IRCOM)] Laboratory, Centre National de la Recherche Scientifique (CNRS), where his research is focused on the modeling and design of high nonlinear devices.

Raymond Quéré (M'88–SM'99) received the Electrical Engineering degree and French agrégation degree in physics from ENSEEIHT-Toulouse, Toulouse, France, in 1976 and 1978, respectively, and the Ph.D. degree in electrical engineering from the University of Limoges, Brive, France, in 1989.

In 1992, he became a Full Professor with the University of Limoges, where he currently heads the research group on high-frequency nonlinear circuits and systems with the Institut de Recherche en Communications Optiques et Microondes (IRCOM),

Centre National de la Recherche Scientifique (CNRS), Toulouse, France. He is mainly involved in nonlinear modeling and design of microwave devices and circuits. He is involved in a number of Technical Program Committees and serves as a reviewer for several journals.

Dr. Quéré was appointed general chairman of European Microwave Week, Paris, France, in 2005.