Delft University of Technology

## An Energy-Efficient 3.7-nV/√ Hz Bridge Readout IC With a Stable Bridge Offset **Compensation Scheme**

Jiang, Hui; Nihtianov, Stoyan; Makinwa, Kofi A.A.

DOI 10.1109/JSSC.2018.2885556

**Publication date** 2019 **Document Version** Final published version

Published in IEEE Journal of Solid State Circuits

#### Citation (APA)

Jiang, H., Nihtianov, S., & Makinwa, K. A. A. (2019). An Energy-Efficient 3.7-nV/√ Hz Bridge Readout IC With a Stable Bridge Offset Compensation Scheme. *IEEE Journal of Solid State Circuits*, *54*(3), 856-864. [8588386]. https://doi.org/10.1109/JSSC.2018.2885556

#### Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

#### Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

# 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

# An Energy-Efficient 3.7-nV/√Hz Bridge Readout IC With a Stable Bridge Offset Compensation Scheme

Hui Jiang<sup>®</sup>, Student Member, IEEE, Stoyan Nihtianov<sup>®</sup>, Senior Member, IEEE, and Kofi A. A. Makinwa<sup>®</sup>, Fellow, IEEE

Abstract—This paper describes an energy-efficient bridge readout IC (ROIC), which consists of a capacitively coupled instrumentation amplifier (CCIA) that drives a continuous-time delta-sigma modulator ( $CT\Delta\Sigma M$ ). By exploiting the CCIA's ability to block dc common-mode voltages, the bridge's bias voltage may exceed the ROIC's supply voltage, allowing these voltages to be independently optimized. Since bridge output is typically much smaller than bridge offset, a digital to analog converter (DAC) is used to compensate this offset before amplification and thus increase the CCIA's useful dynamic range. Bridge loading is reduced by using a dual-path positive feedback scheme to boost the CCIA's input impedance. Furthermore, the CCIA's output is gated to avoid digitizing its output spikes, which would otherwise limit the ROIC's linearity and stability. The ROIC achieves an input-referred noise density of 3.7 nV//Hz, a noise efficiency factor (NEF) of 5, and a power efficiency factor (PEF) of 44, which both represent the state of the art. A pressure sensing system, built with the ROIC and a differential pressure sensor (AC4010), achieves 10.1-mPa (1 $\sigma$ ) resolution in a 0.5-ms conversion time. The ROIC dissipates about 30% of the system's power dissipation and contributes about 6% of its noise power. To reduce the sensor's offset drift, a temperature compensation scheme based on an external reference resistor is used. After a two-point calibration, this scheme reduces bridge offset drift by 80x over a 50 °C range.

Index Terms—Beyond the rails, bridge offset compensation, bridge sensor, capacitively coupled (CC) chopper, CC instrumentation amplifier (CCIA), continuous-time delta–sigma modulator (CT $\Delta\Sigma$ M), energy efficient, readout IC (ROIC), temperature compensation.

#### I. INTRODUCTION

WHEATSTONE bridges are widely used to read out impedance sensors that monitor physical parameters such as temperature, pressure, and humidity [1]–[12]. As shown in Fig. 1, their output can be digitized by a readout IC (ROIC), which consists of an instrumentation amplifier (IA) and an analog to digital converter (ADC). To maximize the accuracy of the resulting sensing system, the ROIC should have low input-referred noise, low-temperature drift, high

Manuscript received July 30, 2018; revised September 27, 2018 and October 29, 2018; accepted November 26, 2018. Date of publication December 25, 2018; date of current version February 21, 2019. This work was supported by the ECSEL Joint Undertaking Project. This paper was approved by Associate Editor Piero Malcovati. (*Corresponding author: Hui Jiang.*)

The authors are with the Electronic Instrumentation Laboratory, Microelectronics Department, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: jianghuithu@gmail.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2018.2885556

R - r = R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R + r R +

Fig. 1. Precision sensing systems.

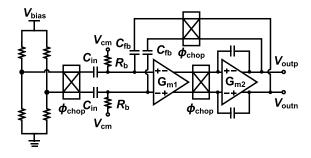

Fig. 2. Bridge readout using a CCIA.

input impedance, high linearity, and high common-mode rejection ratio (CMRR) [2], [13]. It should also have high energy efficiency to facilitate its use in battery-powered applications and in precision mechatronic systems where self-heating may be an issue [14].

An ROIC's energy efficiency will usually be determined by its IA, since this sets its input-referred noise. Recently, capacitively coupled (CC) IAs have been shown to be particularly energy efficient [3]. As shown in Fig. 2, a CCIA consists of an input chopper, which up-modulates differential input voltages to a chopping frequency,  $f_{chop}$ , allowing them to be amplified by an inverting amplifier with capacitive feedback elements. Since they only require one noise-critical input stage, CCIAs are generally more energy efficient than three-Opamp and current-feedback (CF) IAs [15]. Moreover, their input capacitors naturally block common-mode (CM) input voltages, allowing them to handle CM levels much larger than their supply voltages [4]. In bridge readout applications, this means that the bridge and the ROIC can be powered from different voltage supplies, allowing the ROIC's supply voltage to be optimized for energy efficiency. Last but not the least,

0018-9200 © 2018 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

since CCIAs are inherently chopped, their 1/f noise and offset are also quite low.

A major drawback of CCIAs is that they generate output spikes at their chopping transitions, i.e., at  $2f_{chop}$  [3]. These should not be digitized since their amplitude is usually not a linear function of the input signal. In the case of a discretetime ADC, this can be readily achieved by sampling the output of the CCIA just before the chopping transitions [3]. The CCIA's bandwidth then needs to be wide enough to ensure complete settling, which increases noise aliasing and thus degrades the ROIC's overall energy efficiency [5]. Furthermore, the ADC's sampling frequency  $f_s$  is now the same as  $2f_{chop}$ , which limits design flexibility. In [6], a dynamic filter has been used to limit the noise bandwidth while maintaining settling accuracy, but at the expense of increased design complexity.

This paper describes a pressure sensing system that consists of an energy-efficient ROIC and a bridge-type pressure sensor [16]. The ROIC uses a gated continuous-time delta-sigma modulator (CT $\Delta \Sigma M$ ) to digitize the CCIA's output while avoiding its output spikes. To maximize the CCIA's useful dynamic range, the bridge offset is compensated by a passive digital to analog converter (DAC) referred to the bridge biasing voltage. This ratio-metric approach ensures that the compensating signal only depends on capacitor and resistor ratios, and so is stable over temperature and bias voltage variations. Implemented in a standard CMOS 180-nm process, the ROIC achieves a state-of-the-art noise efficiency factor (NEF) of 5. It dissipates about 30% of the system's power and contributes about 6% of its noise power, resulting in a resolution of 10.1 mPa (rms) with a range of  $\pm 100$  Pa in a 0.5-ms conversion time.

The rest of this paper is organized as follows. Section II discusses the main techniques used in the ROIC to achieve high energy efficiency and high precision. Section III describes the implementation details of the ROIC, while the experimental results of the ROIC and pressure sensing system with temperature calibration are presented in Section IV. Section V provides the conclusion.

#### II. SYSTEM DESIGN OF THE ROIC

Differential pressure sensors with a range of  $\pm 100$  Pa are required in air gages for industrial applications [7]. The AC4010 is a high-resolution bridge-type piezo-resistive pressure sensor that can cover this range. To achieve a resolution of 10 mPa (rms) over 1-kHz bandwidth, its biasing voltage  $V_{\text{bias}}$  should be at least 5 V, thus resulting in a sensitivity of about 45  $\mu$ V/Pa. However, this will be superimposed on a bridge offset of about 100 mV, due to the mismatch of its piezo-resistive elements (nominally 3.7 k $\Omega$  each), to ensure that the ROIC does not limit the sensor's performance, it should be designed to meet the specifications in Table I.

#### A. Dual-Supply Sensing System

Conventionally, the supply voltage of an ROIC must be somewhat larger than the bridge's CM level, despite the fact that the bridge's output is quite small [2], [9], [10], [17]. This

TABLE I TARGET SPECIFICATIONS OF THE ROIC

| Specifications      | Value                                                             |  |  |  |  |  |

|---------------------|-------------------------------------------------------------------|--|--|--|--|--|

| Input noise density | $4 \text{ nV}/\sqrt{\text{Hz}}$ (~ 1 k $\Omega$ )                 |  |  |  |  |  |

| Conversion time     | 0.5 ms                                                            |  |  |  |  |  |

| Input CM level      | 2.5 V                                                             |  |  |  |  |  |

| Input range         | $\pm$ 100 mV (offset), $\pm$ 10 mV (signal)                       |  |  |  |  |  |

| Gain                | pprox 100                                                         |  |  |  |  |  |

| Input impedance     | $> 370 \text{ k}\Omega \text{ (for } < 0.1\% \text{ gain error)}$ |  |  |  |  |  |

| Offset drift        | < 10 µ/ °C                                                        |  |  |  |  |  |

| Power dissapation   | < 6.8 mW                                                          |  |  |  |  |  |

| INL                 | < 50 ppm                                                          |  |  |  |  |  |

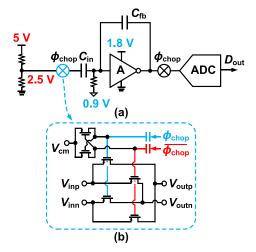

Fig. 3. (a) Proposed dual-supply sensing system (single-ended representation). (b) CCIA's CC input chopper.

constraint leads to a tradeoff between bridge sensitivity and ROIC power dissipation.

One way of avoiding this tradeoff is to exploit the beyondthe-rails capability of a CCIA. As shown in Fig. 3(a), the bridge can then be powered from a 5-V supply, while the ROIC can be powered from a 1.8-V supply voltage. The only active components exposed to the bridge's 2.5-V CM voltage are the switches of the CCIA's CC input chopper [Fig. 3(b)], which can be realized with deep n-well CMOS (DMOS) transistors or I/O devices [18]. The CCIA's input capacitors can be implemented by metal–insulator–metal (MIM) capacitors, which, in most processes, are capable of handling even higher voltages.

#### B. Compensating the Bridge Offset

Due to bridge mismatch, however, increasing  $V_{\text{bias}}$  will also increase bridge offset. Since this can be quite large, it will limit the IA's useful output range, and hence its gain. As a result, the succeeding ADC will need to have a wider dynamic range and lower input-referred noise, both of which will result in increased power dissipation.

To avoid this problem, bridge offset should be compensated before amplification. This can be done by using: 1) an external offset compensation network to trim the bridge [19] and 2) a current DAC to inject a programmable current into the bridge [20]. However, the bridge and the compensation

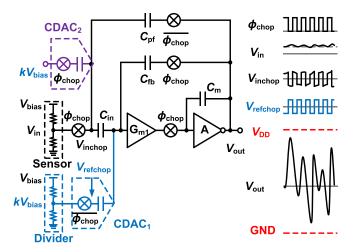

Fig. 4. Block diagram of the CCIA illustrating the operation of the bridge offset compensation and dual-path input impedance boosting loops.

circuitry will inevitably have different temperature dependencies, leading to significant temperature drift.

In this paper, the CCIA is used to implement a ratio-metric offset-compensation scheme (Fig. 4). The bridge output  $V_{in}$  is added to an offset-compensating signal generated by a capacitive DAC (CDAC<sub>1</sub>), which is referred to  $V_{bias}$  via a resistive divider. By implementing both  $C_{in}$  (input capacitor of the CCIA) and CDAC<sub>1</sub> with MIM capacitors, both the bridge output  $V_{in}$  and the divider's output  $kV_{bias}$  will respond in the same way to temperature and  $V_{bias}$  variations.

Note that the residual bridge offset and bridge sensitivity will still drift over temperature. As shown in Fig. 1, such errors can be absorbed by an overall system calibration. However, the proposed bridge offset compensation minimizes the errors contributed by the ROIC, ensuring that the overall system accuracy is mainly limited by the bridge sensor.

#### C. Dual-Path Input Impedance Boosting Scheme

A known drawback of CCIAs is that they output spikes at twice the chopping frequency  $(2 f_{chop})$  [3]. This is because  $C_{in}$  must be rapidly charged and discharged at the chopping transitions. To reduce the amplitude of these spikes, most of the required charge can be provided from the output of the CCIA via a positive feedback path [3] or by an auxiliary pre-charge path [6], which also boosts the CCIA's input impedance. Although the boosting effect of a positive feedback path is limited by parasitic capacitors and stability considerations [3], it is more appealing in this design, as a precharge path requires active buffers which would compromise the CCIA's beyond-the-rails capability.

As shown in Fig. 4, a positive feedback path can be realized with an extra capacitor  $C_{pf}$  which should provide a compensation charge  $Q_{com}$  [3], given by

$$Q_{\rm com} = C_{\rm pf} V_{\rm out} \approx C_{in} V_{\rm in} = Q_{\rm in} \tag{1}$$

where  $V_{in}$  consists of two parts, the useful bridge signal  $V_{sig}$ and the bridge offset  $V_{os}$ . However, in the proposed design (Fig. 4),  $V_{os}$  will be partially canceled by CDAC<sub>1</sub> before amplification. To still provide a charge proportional to the compensated offset, a capacitive DAC (CDAC<sub>2</sub>) is added, and

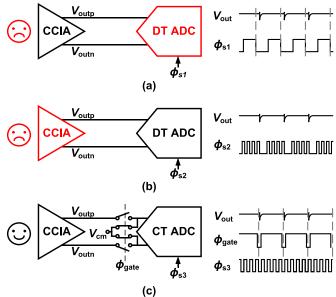

Fig. 5. Different ways to avoid digitizing the spikes of a CCIA by (a) using  $f_s = 2f_{chop}$ , (b) oversampling at quiet moments, and (c) using gated continuous-time integration.

driven by the same code as  $CDAC_1$ . The total compensation charge is now given by

$$Q_{\rm com} = C_{\rm pf} V_{\rm out} + Q_{\rm DAC}$$

$$\approx C_{\rm in} (V_{\rm sig} + V_{\rm off}) = Q_{\rm in}.$$

(2)

#### D. Gating the Output of the CCIA

The CCIA's residual output spikes can be avoided by using a discrete-time  $\Delta \Sigma$  modulator (DT $\Delta \Sigma M$ ) to synchronously sample the CCIA's output. The modulator's sampling frequency  $f_s$  will then be equal to  $2f_{chop}$ , as shown in Fig. 5(a) [3], [5]. Assuming that the CCIA is a single pole system without slew rate limitations, a minimum bandwidth BW is needed to achieve sufficient settling [21]

$$BW \ge 2 \cdot (m+1) \cdot f_{s} \cdot \ln 2 \tag{3}$$

where *m* is the target resolution of the ROIC in bits. Due to the sampling process, noise within a bandwidth of  $\pi/2 \cdot BW$  will fold back to baseband, increasing the CCIA's in-band noise power density. This significantly decreases the ROIC's energy efficiency [5]. A dynamic *RC* filter can be used to limit the noise bandwidth before sampling [Fig. 5(b)] at the expense of increased design complexity [6].

In this design, the CCIA's residual spikes are avoided by gating the input of a CT $\Delta \Sigma M$  [4]. As shown in Fig. 5(c), the input of the CT $\Delta \Sigma M$  is connected to the CM voltage for the duration of the spikes, after which it is connected to the output of the CCIA. In this way, the errors associated with the CCIA's spikes are reduced without noise fold back. Compared to a switched-capacitor (SC) load, the resistive load presented by the modulator significantly relaxes the requirements on the CCIA's driving capability and thus further improves the ROIC's energy efficiency. Since the CCIA's output is effectively duty cycled, these benefits are acquired at the expense of a small reduction (2.5%) in its effective gain.

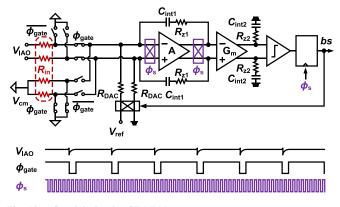

Fig. 6. Simplified circuit diagram of the bridge ROIC.

Fig. 7. Schematic of the CCIA main amplifier with demodulating chopper. (Bias circuits and CM feedback loop circuits are not shown.)

#### **III. ROIC IMPLEMENTATION DETAILS**

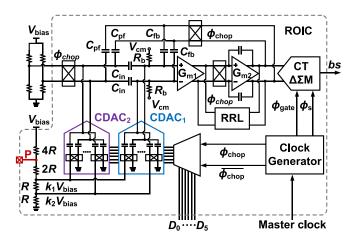

A simplified circuit diagram of the proposed ROIC is shown in Fig. 6. It consists of a CCIA with bridge offsetcompensation circuitry and a gated  $CT\Delta\Sigma M$ . In this section, the implementation of these blocks will be discussed in detail.

### A. CCIA

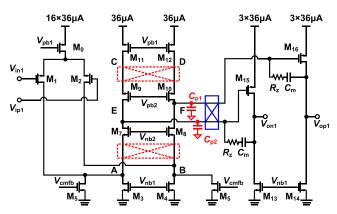

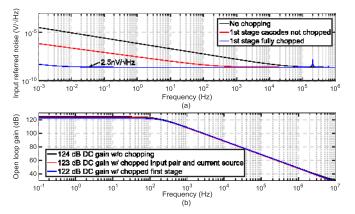

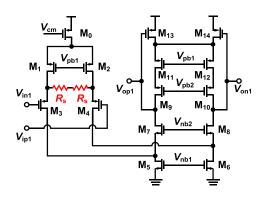

The gain of the CCIA is set at 40 dB. To achieve high linearity, the CCIA is built around a two-stage Miller compensated amplifier, with a dc gain of about 124 dB. The bridge has an equivalent source resistance of 3.7 k $\Omega$ , corresponding to a noise density of 7.8 nV/ $\sqrt{Hz}$ . The CCIA's input-referred noise should then be lower than this, which is quite challenging. The first stage consists of a chopped folded-cascode amplifier with a very large PMOS input pair (1280  $\mu$ m/0.2  $\mu$ m) that is biased in weak inversion to efficiently realize a trans-conductance of about 6.7 mS. As shown in Fig. 7, the input pair consuming most of the current of the amplifier. To mitigate the noise gain penalty due to the input pair's parasitic capacitance (1.3 pF), the CCIA's input capacitors  $C_{in}$  were set to 10 pF [3].

In this design, the offset and 1/f noise of the 1st stage is mitigated by chopping, while that of the 2nd stage is suppressed by the gain of the 1st stage. Often [2], [22], and [23], the demodulating chopper (drawn with dotted lines in Fig. 7) is located at nodes A and B and C and D. In this case,

Fig. 8. Simulation results. (a) Amplifier's input-referred noise PSD. (b) Amplifier's open-loop gain.

Fig. 9. Simplified circuit diagram of the offset compensation DAC.

the cascodes are not chopped and their 1/f noise becomes dominant, as shown in Fig. 8(a).

This can be addressed by moving the chopper to the output of the 1st stage, i.e., nodes E and F in Fig. 7. As shown in Fig. 8(a), chopping at 200 kHz results in a simulated 3.2 mHz 1/*f* noise corner. However, the chopped parasitic capacitors ( $C_{p1,2}$ ) at these nodes will form an SC resistance, which, in turn, will reduce the gain of the 1st stage. To mitigate this, the cascode transistors were made relatively small ( $M_{7,8}$ : 24 µm/1.8 µm and  $M_{9,10}$ : 60 µm/1.2 µm), and the layout was optimized. In this way, chopping only reduces the open-loop gain by 2 dB [Fig. 8(b)].

To minimize their noise contribution, the CCIA's bias resistors  $R_b$  should be in excess of 250 M $\Omega$ . To conserve area, they are implemented as SC resistors to achieve good linearity and stability over process and temperature variations [18]. The input chopper consists of capacitively driven DMOS transistors, allowing the input of the CCIA to handle bridge CM voltages up to 3.3 V (limited by the ESD-protection diodes) while operating from a 1.8-V supply.

#### B. Offset Compensation DAC

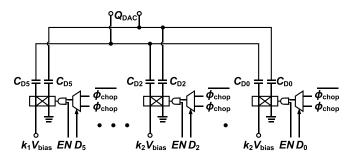

The bridge offset-compensation circuit consists of a 5-bit  $(D_{5-1})$  binary weighted DAC with a redundant LSB  $(D_0)$  and a bank of chopper switches (Fig. 9). It is controlled by an external trimming code  $(D_{5-0})$ . The DAC compensates the bridge offset by effectively adding a scaled and chopped version of  $V_{\text{bias}}$  to the output of the bridge.

The total DAC capacitance should be kept small to minimize its impact on the CCIA's noise gain [18]. With a 5-V bias, a  $\pm 100$ -mV bridge offset can be expected. To bring the

Fig. 10. Gated 2nd-order  $CT\Delta \Sigma M$ .

offset into the input range of the CCIA, two references,  $k_1V_{\text{bias}}$  (1.25 V for  $D_{5-3}$ ) and  $k_2V_{\text{bias}}$  (0.625 V for  $D_{2-0}$ ), are derived from  $V_{\text{bias}}$  by a resistive divider. In this way, the DAC capacitance is reduced from 1.6 to 0.87 pF, 11.4× smaller than  $C_{\text{in}}$ , ensuring that the divider's noise contribution is much less than the CCIA. The unity capacitances are 49.1 fF for  $D_{5-1}$  and 35.6 fF for  $D_0$  (the smallest in the process).

The resistive divider has a total resistance of 36 k $\Omega$ , and is made from polysilicon resistors, which can handle bridge bias voltages up to 6.6 V. The chopper switches are protected by connecting the node P to an ESD-protected pad to ensure that the chopper gates are not exposed to voltages above the supply (Fig. 6). The polarity of the compensating signal can be inverted via the choppers, so the CCIA's output can be expressed as  $(V_{in}C_{in}\pm Q_{DAC1})/C_{fb}$ . The simulations show that the CCIA, including the DAC, achieves an input-referred noise density of 3.4 nV/ $\sqrt{Hz}$  and a 1/f noise corner of 18 mHz.

#### C. Gated $CT\Delta \Sigma M$

As shown in Fig. 10, the CT $\Delta \Sigma M$  employs an energyefficient 2nd-order feedforward topology. It consists of a gated *RC* integrator (1st stage), a  $G_m-C$  integrator (2nd stage), a 1-bit quantizer, and a resistive feedback DAC. The modulator's sampling frequency  $f_s = 2$  MHz, which is enough to achieve the target resolution.

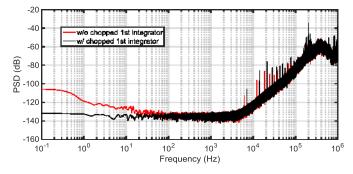

The 1st integrator, consuming about 190  $\mu$ A, employs a folded-cascode OTA (A) with an 82-dB dc gain and a trans-conductance of about 0.86 mS.  $R_{in}$  and  $R_{DAC}$ , each 200 k $\Omega$ , are the main thermal noise sources of the CT $\Delta \Sigma M$ .  $R_{Z1}$  (0.74 k $\Omega$ ) is added, in series with  $C_{int1}$  (35 pF), to compensate the right-half plane zero of OTA-based *RC* integrator. The 1st integrator is also chopped to reduce the impact of its 1/*f* noise on the ROIC's input-referred noise. Its chopping frequency is set at  $f_s$  to minimize quantization noise fold back [24]–[26]. Although this is much higher than the 1st integrator's 1/*f* corner, the associated drawbacks, such as reduced input impedance, reduced output impedance, and increased residual offset, are suppressed by the gain of the preceding CCIA.

The 1st integrator is gated by periodically swapping its input between the CCIA's output and the CM voltage. For linearity, the associated switches are located at the integrator's virtual ground to ensure that their ON-resistance is signal independent. As shown in Fig. 10, the gating scheme ensures that the

Fig. 11. Source degenerated OTA of the 2nd integrator.

CCIA's output is always loaded by the input resistors  $R_{in}$ , and thus minimizes gating transients. In this paper, the gating period is 2.5% of each chopping phase, resulting in a proportional decrease in the CCIA's equivalent gain. This gain is well-defined as  $\phi_{gate}$ ,  $\phi_{chop}$ , and  $\phi_s$  are derived from a 16-MHz external clock.

As shown in Fig. 11, the 2nd integrator employs a Gm–C topology based on a 310 source degenerated OTA (Gm in Fig. 10). The 2nd integrator employs a  $G_m$ –C topology based on a source degenerated OTA (Gm in Fig. 10). Since the 2nd integrator's noise will be suppressed by the gain of the 1st, the OTA only draws 20  $\mu$ A.

The feedforward path of the 2nd-order  $\Delta \Sigma M$  is realized by adding  $R_{z2}$  (110 k $\Omega$ ) in series with integration capacitor  $C_{int2}$  (8 pF), with the value of the coefficient being well-defined by the ratio between the degeneration resistors  $R_s$  (100 k $\Omega$ ) and the feedforward resistors  $R_{z2}$ . Thus, the transfer function H(s) from the input to the output of 2nd integrator can be expressed as

$$H(s) = g_{m2} \left( R_{Z2} + \frac{1}{sC_{int2}} \right) \approx \frac{R_{Z2}}{R_s} + \frac{1}{sR_sC_{int2}}$$

(4)

where  $g_{m2}$  is the transconductance of the OTA  $G_m$  shown in Fig. 10.

The jitter of the sampling clock will translate into inputreferred noise, thus degrading the signal-to-noise ratio (SNR) of the CT $\Delta \Sigma M$ . However, the jitter requirement is relaxed by the relatively narrow signal band. The SNR<sub>jdac</sub> determined by the sampling clock jitter  $\sigma_{jdac}$  is given by [1]

$$SNR_{jdac} = 10 \cdot \log\left(\frac{1}{16 \cdot OSR \cdot f_b^2 \cdot \sigma_{jdac}^2}\right)$$

(5)

where over sampling ratio (OSR) is 1000, and  $f_b$  is 1 kHz. Assuming 10-ps (rms) jitter, SNR<sub>jdac</sub> is 118 dB, which is sufficient for bridge readout. In the worst case, 42-ps (rms) jitter would result in a noise level close to that of the ROIC. However, this noise power contribution, caused by clock jitter, to the pressure sensing system is less than 6%.

Similarly, the jitter of the gating clock  $\sigma_{jgate}$  in the 1st integrator also degrades the modulator's in-band noise performance. SNR<sub>jgate</sub> determined by this jitter is given by [27]

$$SNR_{jgate} = 10 \cdot \log\left(\frac{1}{4 \cdot \left(V_{IAO}/V_{ref}\right)^2 \cdot f_b \cdot f_{gate} \cdot \sigma_{jgate}^2}\right) (6)$$

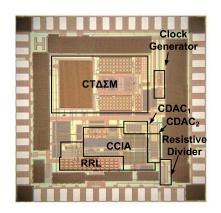

Fig. 12. Micrographs of the ROIC.

Fig. 13. Measured PSD of the ROIC's bitstream with  $2 \times 10^7$  samples. (8× averaging was applied, and the residual offset was subtracted.)

where  $V_{\text{IAO}}$  is the CCIA output signal, and  $f_{\text{gate}}$  is 400 kHz. In the worst case, when  $V_{\text{IAO}}$  is  $\pm 1$  V, the resulted SNR<sub>jgate</sub> with 10-ps (rms) jitter is 133 dB, 15 dB lower than the SNR<sub>jdac</sub>.

#### **IV. MEASUREMENT RESULTS**

The ROIC was implemented in a 180-nm standard CMOS technology and has an active area of 0.73 mm<sup>2</sup> (Fig. 12). The core of the ROIC, including the CCIA,  $CT\Delta \Sigma M$ ,  $CDAC_1$ ,  $CDAC_2$ , and clock generator, consumes 1.2 mA from a 1.8-V supply. The on-chip resistive divider is supplied by the bridge bias voltage  $V_{\text{bias}}$ , which may be as high as 6.6 V.

The performance of the ROIC and that of the entire pressure sensing system have been characterized experimentally. The digital processing of the calibration has been done in MATLAB. The results will be described in Sections IV-A and IV-B.

#### A. Electrical Measurements

The fast Fourier transform (FFT) plots of the ROIC's output bitstream, based on  $2 \times 10^7$  samples, is shown in Fig. 13. It can be seen that the modulator's 1st integrator must, indeed, be chopped to ensure that the ROIC's noise spectrum becomes flat from 0.1 Hz to 2 kHz. The spectrum corresponds to a 3.7-nV/ $\sqrt{\text{Hz}}$  noise level. By decimating the ROIC's output with an off-chip sinc<sup>3</sup> filter and then acquiring  $2 \times 10^8$  samples of the filter's output over 100 s, its 1/f corner frequency was found to be about 0.04 Hz.

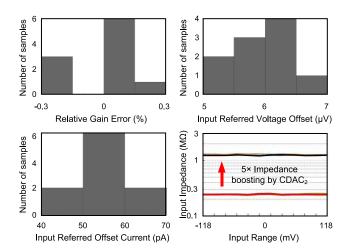

Fig. 14. Measured relative gain error, offset voltage, offset current, and the input impedance of the ROIC.

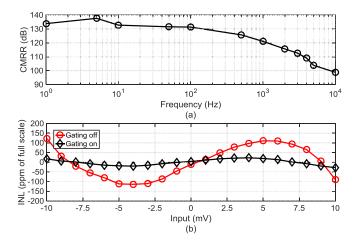

Fig. 15. Measured CMRR of (a) ROIC and (b) INL.

Measurements on 10 samples show that the ROIC achieves 0.3% relative gain error and 7- $\mu$ V voltage offset (Fig. 14). Enabling CDAC<sub>2</sub> reliably boosts its input impedance by a factor of 5 (Fig. 14). The CMRR of the ROIC is shown in Fig. 15(a).

To test the effectiveness of the gating technique, a 118-mV signal with 2-k $\Omega$  source impedance was applied to the inputs of the ROIC when the resistive voltage divider was biased at 6 V. Gating the CT $\Delta\Sigma$ M reduces the ROIC's gain temperature drift from 74.6 to 8.9 ppm/°C, and reduces its offset temperature drift from 105 to 12.5 nV/°C. As shown in Fig. 15(b), gating the CT $\Delta\Sigma$ M also improves the ROIC's INL from 105 to 28 ppm.

The ROIC's performance is summarized in Table II and compared with the state of the art. It achieves both high accuracy and energy efficiency for  $\pm 10$ -mV bridge signals, while accommodating up to 3.3-V input CM voltage. With a 3.7-nV/ $\sqrt{\text{Hz}}$  input-referred noise PSD, it achieves an NEF (in [28]) of 5 and a power efficiency factor (PEF) (in [29]) of 44.

#### B. System Measurements and Temperature Calibration

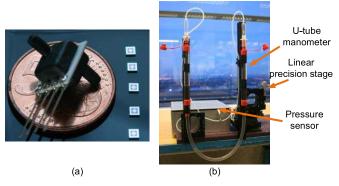

The ROIC was combined with an AC4010 pressure sensor to realize a pressure sensing system. As shown in Fig. 16(b),

|                                      | This work       | JSSC<br>2016 [1]   | JSSC<br>2012 [2]                                                        | ISSCC<br>2018 [5]                                                       | JSSC<br>2017 [6]                                                        | ISSCC<br>2011 [8] | ESSCIRC<br>2012 [9] | VLSI<br>2017 [10] | L-SSC<br>2018 [11]  |

|--------------------------------------|-----------------|--------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------|---------------------|-------------------|---------------------|

| Architecture                         | CCIA +<br>CTΔΣΜ | 3-Opamp<br>+ DTΔΣM | $\frac{\text{CFIA} + \text{DT}\Delta\Sigma M}{\text{DT}\Delta\Sigma M}$ | $\frac{\text{CCIA} + \text{DT}\Delta\Sigma M}{\text{DT}\Delta\Sigma M}$ | $\frac{\text{CCIA} + \text{DT}\Delta\Sigma M}{\text{DT}\Delta\Sigma M}$ | SHA +             | Gm-C<br>CTΣΔM       | CC-<br>CTΣΔΜ      | CC-           CTΣΔΜ |

| Input stage                          | PMOS            | PMOS               | PMOS                                                                    | PMOS                                                                    | NMOS                                                                    | PMOS              | PMOS                | PMOS              | PMOS                |

| Technology (nm)                      | 180 nm          | 180 nm             | 700 nm                                                                  | 130 nm                                                                  | 180 nm                                                                  | 350 nm            | 700 nm              | 40 nm             | 180 nm              |

| Active area (mm <sup>2</sup> )       | 0.73            | 0.5                | 6                                                                       | 0.88                                                                    | 0.53 <sup>2</sup>                                                       | 1.2               | 3                   | 0.06              | 0.75                |

| Supply Voltage (V)                   | 1.8             | 1.55               | 5                                                                       | 3                                                                       | 3.3                                                                     | 3.3               | 5                   | 1.2               | 1.8                 |

| Supply Current (mA)                  | 1.2             | 1.56               | 0.27                                                                    | 0.326 <sup>1</sup>                                                      | 0.075 <sup>2</sup>                                                      | 2                 | 0.24                | 0.0175            | 1.2                 |

| DC CMRR (dB)                         | 134             |                    | 140                                                                     | 124                                                                     | 109                                                                     |                   | 120                 |                   | 137                 |

| CM Input Range (V)                   | 0-3.3           |                    | 0-2.5                                                                   |                                                                         | 0–3                                                                     | 0–3               | 0–2.5               |                   | 0-3.3               |

| INL (ppm)                            | 28              |                    | 5                                                                       |                                                                         | 5                                                                       |                   | 15                  | 79 <sup>3</sup>   | 15                  |

| Gain Drift (ppm/ °C)                 | 8.9             |                    | 0.7                                                                     |                                                                         | 0.81                                                                    |                   |                     |                   | 7.7                 |

| Offset (µV)                          | 7               |                    | 0.05                                                                    | 2.4                                                                     | 1.8                                                                     |                   | 1                   | 300               | 72                  |

| Offset Drift (nV/°C)                 | 12.5            |                    | 6                                                                       |                                                                         | 70                                                                      |                   |                     |                   | 12.3                |

| Input noise density $(nV/\sqrt{Hz})$ | 3.7             | 8.2                | 16.2                                                                    | 16                                                                      | 19                                                                      | 6.7               | 20                  | 140               | 4.5                 |

| NEF <sup>4</sup> /PEF <sup>5</sup>   | 5.0/44          | 12.5/242           | 10.4/541                                                                | 11.1/372                                                                | 6.41/136                                                                | 11.6/444          | 12/720              | 22.6/613          | 6.1/67              |

TABLE II State-of-the-Art ROICs

1. Without taking account the current consumption of 1.5V supply. 2. Without taking account the ADC. 3. Estimated from THD. 4. NEF= $\nu_n v_n (2 \cdot I_{tot} / \pi \cdot U_T \cdot 4 K T \cdot B W)$ . 5. PEF=NEF<sup>2</sup>\* $V_{DD}$ .

Fig. 16. (a) AC4010. (b) Differential pressure measurement setup.

the water-level difference in a U-tube manometer was precisely controlled by a linear stage to create a well-defined differential pressure [30].

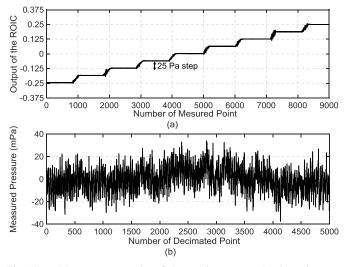

Moving the right leg of the U-tube manometer relative to the left one by  $\pm 10$  mm with a 2.5-mm step, then results in  $\pm 100$ -Pa pressure change. The real-time response of the sensing system is shown in Fig. 17(a). The pressure sensing system has a pressure sensitivity of 0.0025 (1/Pa). To evaluate the system's resolution, the inputs of the differential pressure sensor were shorted to avoid mechanical interference from the environment. The pressure resolution, obtained from the standard deviation of 5000 samples (decimated by sinc<sup>3</sup> filter with a length of 1000), is found to be 10.1 mPa

Fig. 17. Measurement results of the sensing system. Decimated output of the ROIC (a) with swept pressure input (the residual offset has been subtracted) and (b) with zero pressure input (shorted, the residual offset has been subtracted).

with a 0.5-ms conversion time for each decimated sample [Fig. 17(b)].

In practice, the temperature drift of a bridge sensor can be corrected by system calibration (Fig. 1). This usually involves exposing the bridge sensor to at least two well-defined temperature levels and measuring its output. The sensor's drift can then be corrected if the ambient temperature is known,

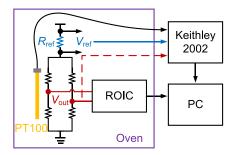

Fig. 18. Bridge sensor with reference resistor for temperature calibration.

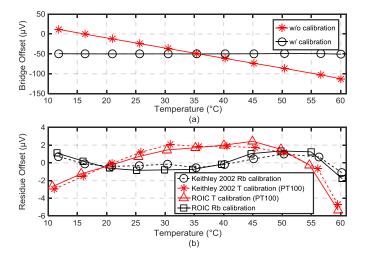

Fig. 19. Measured bridge offset drift (a) before and after calibrations and (b) residual offset drift.

e.g., by realizing a temperature sensor in the ROIC. However, the accuracy of this approach is limited by bridge self-heating, which can create temperature differences between the bridge and temperature sensor.

A more accurate approach is to use the bridge itself as a temperature sensor, by measuring its temperature-dependent resistance. To calibrate the bridge resistance over temperature, both the bridge sensor and the ROIC were placed in an oven-stabilized aluminum block next to a PT100 thermometer (Fig. 18). A reference resistor (100  $\Omega$ , ±3 ppm/°C [31]) was placed in series with the bridge as a shunt current sensor. The voltage across the reference resistor was read out by Keithley 2002. In this way, the bridge resistance, and thus, the temperature on the bridge can be measured.

The effectiveness of the resulting calibration was tested by measuring the bridge sensor's offset drift over temperature. After a two-point calibration, the offset drift decreases from 244  $\mu$ V over a 50 °C range, to about 3  $\mu$ V [Fig. 19(a)].

To compare the results of both methods and the output of the bridge is measured by both the ROIC and a Keithley 2002 (Fig. 18). As shown in Fig. 19(b), the residual offset with monitoring the bridge resistance (red curves) is about  $2\times$ better than that obtained by monitoring the bridge temperature using PT100 thermometer (black curves). The residual errors obtained by the ROIC (solid curves) are in good agreement with that obtained by the Keithley 2002 (dashed curves).

#### V. CONCLUSION

An energy-efficient ROIC for a differential pressure sensing system has been presented. To maximize bridge sensitivity with high energy efficiency, the beyond-the-rails capability of a CCIA is exploited to allow the bridge biasing voltage to exceed the ROIC's supply voltage. A bridge offset compensation is implemented in a ratio-metric manner, which is robust to variations in temperature and bridge biasing voltage. A dual positive feedback path scheme is used to boost the input impedance of the ROIC. A gated-input  $CT\Delta \Sigma M$  is proposed to digitize the amplified signal and avoid the error caused by the output spikes of the CCIA. Measurements show that the ROIC achieves both precision and energy efficiency with an NEF of 5, which represents the state of the art. The ROIC was tested together with a piezo-resistive differential pressure sensor. The experimental results show that the applied techniques are effective. The resulting pressure sensing system achieves 10.1-mPa (1 $\sigma$ ) resolution with a 0.5-ms conversion time. The ROIC dissipates about 30% of the system's power dissipation and contributes about 6% of its noise power. Moreover, a temperature calibration, to reduce the bridge temperature dependence, has shown a factor of 80× improvement on the system's offset drift over a 50 °C range.

#### ACKNOWLEDGMENT

The authors would like to thank Acuity Inc., Fremont, CA, USA, for providing sensor samples and the helpful suggestions. They would also like to thank Z.-Y. Chang, L. Pakula, R. van Puffelen, and S. Pan for their assistance in building measurement setup.

#### REFERENCES

- M. Maruyama, S. Taguchi, M. Yamanoue, and K. Iizuka, "An analog front-end for a multifunction sensor employing a weak-inversion biasing technique with 26 nVrms, 25 aCrms, and 19 fArms input-referred noise," *IEEE J. Solid-State Circuits*, vol. 51, no. 10, pp. 2252–2261, Oct. 2016.

- [2] R. Wu, J. H. Huijsing, and K. A. A. Makinwa, "A 20-b±40-mV range read-out IC with 50-nV offset and 0.04% gain error for bridge transducers," *IEEE J. Solid-State Circuits*, vol. 47, no. 9, pp. 2152–2163, Sep. 2012.

- [3] Q. Fan, F. Sebastiano, J. H. Huijsing, and K. A. A. Makinwa, "A 1.8 W 60 nV Hz capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1534–1543, Aug. 2011.

- [4] H. Jiang, K. A. A. Makinwa, and S. Nihtianov, "An energy-efficient 3.7 nV√Hz bridge-readout IC with a stable bridge offset compensation scheme," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2017, pp. 171–173.

- [5] J. Jun, C. Rhee, M. Kim, J. Kang, and S. Kim, "A 21.8b sub-100 μHz 1/f Corner 2.4 μV-offset programmable-gain read-out IC for bridge measurement systems," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2018, pp. 330–331.

- [6] H. Wang, G. Mora-Puchalt, C. Lyden, R. Maurino, and C. Birk, "A 19 nV/√ Hz noise 2-μV Offset 75-μA capacitive-gain amplifier with switched-capacitor ADC driving capability," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3194–3203, Dec. 2017.

- [7] M. Sogard and S. Lee, "Air gauges comprising dual-range differential pressure sensor," WO Patent 063 104 A1, May 2, 2013.

- [8] C. D. Ezekwe, J. P. Vanderhaegen, X. Xing, and G. K. Balachandran, "A 6.7 nV<sub>4</sub>Hz sub-mHz-1/f-corner 14b analog-to-digital interface for rail-to-rail precision voltage sensing," in *IEEE ISSCC Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2011, pp. 246–248.

- [9] G. Singh, R. Wu, Y. Chae, and K. A. A. Makinwa, "A 20 bit continuoustime ΣΔ modulator with a Gm-C integrator, 120 dB CMRR and 15 ppm INL," in *Proc. ESSCIRC*, Sep. 2012, pp. 385–388.

- [10] C.-C. Tu, Y.-K. Wang, and T.-H. Lin, "A 0.06 mm<sup>2</sup>  $\pm 50$  mV range -82 dB THD chopper VCO-based sensor readout circuit in 40 nm CMOS," in Proc. Symp. VLSI Circuits, Kyoto, Japan, 2017, pp. C84-C85,

- [11] H. Jiang, C. Ligouras, S. Nihtianov, and K. A. A. Makinwa, "A 4.5 nV///Hz capacitively coupled continuous-time sigma-delta modulator with an energy-efficient chopping scheme," IEEE Solid-State Circuits Lett., vol. 1, no. 1, pp. 18-21, Jan. 2018.

- [12] S. Pan, H. Jiang, and K. A. A. Makinwa, "A CMOS temperature sensor with a 49fJK2 resolution FoM," in Proc. Symp. VLSI Circuits, Kyoto, Japan, 2017, pp. C82-C83.

- [13] P. Horowitz and W. Hill, The Art of Electronics. New York, NY, USA: Cambridge Univ. Press, 2016.

- [14] R. Yang, M. A. P. Pertijs, and S. Nihtianov, "A precision capacitanceto-digital converter with 16.7-bit ENOB and 7.5-ppm/°C thermal drift," IEEE J. Solid-State Circuits, vol. 52, no. 11, pp. 3018-3031, Nov. 2017.

- [15] H. Jiang and K. A. A. Makinwa, "Energy-efficient bridge-to-digital converters," in Proc. IEEE Custom Integr. Circuits Conf. (CICC), San Diego, CA, USA, Apr. 2018, pp. 1-7.

- [16] Acuity Series AC401X 10 to 500 MBAR Packaged Sensor Die, Acuity Incorp., Fremont, CA, USA, 2015.

- [17] B. J. van den Dool and J. K. Huijsing, "Indirect current feedback instrumentation amplifier with a common-mode input range that includes the negative roll," IEEE J. Solid-State Circuits, vol. 28, no. 7, pp. 743-749, Jul. 1993.

- [18] Q. Fan, J. H. Huisjing, and K. A. A. Makinwa, Capacitively-Coupled Chopper Amplifiers. Cham, Switzerland: Springer, 2017. [19] J. Williams, "Bridge circuits," Linear Technol. Corp., Milpitas,

- CA, USA, Appl. Note AN43, 1990.

- [20] A. Donida et al., "A 0.036 mbar circadian and cardiac intraocular pressure sensor for smart implantable lens," in IEEE ISSCC Dig. Tech. Papers, San Francisco, CA, USA, Feb. 2015, pp. 392-393.

- [21] M. Pelgrom, Analog-to-Digital Conversion. Cham, Switzerland: Springer, 2017.

- [22] T. Denison, K. Consoer, A. Kelly, A. Hachenburg, and W. Santa, "A 2.2  $\mu$ W 94 nV $\sqrt{Hz}$ , chopper-stabilized instrumentation amplifier for EEG detection in chronic implants," in IEEE ISSCC Dig. Tech. Papers, San Francisco, CA, USA, Feb. 2007, pp. 162-594.

- [23] J. F. Witte, J. H. Huijsing, and K. A. A. Makinwa, "A current-feedback instrumentation amplifier with 5  $\mu$ V offset for bidirectional highside current-sensing," in IEEE J. Solid-State Circuits, vol. 43, no. 12, pp. 2769–2775, Dec. 2008.

- [24] F. Sebastiano, R. H. M. van Veldhoven, and S. Ersoy, "Modulator with high signal to noise ratio," Europe Patent 2919388 A1, Sep. 16, 2015.

- [25] S. Billa, A. Sukumaran, and S. Pavan, "A 280 µW 24 kHz-BW 98.5 dB-SNDR chopped single-bit CT  $\Delta \Sigma M$  achieving <10 Hz 1/f noise corner without chopping artifacts," in IEEE ISSCC Dig. Tech. Papers, San Francisco, CA, USA, Jan./Feb. 2016, pp. 276-277.

- [26] H. Jiang, B. Gönen, K. A. A. Makinwa, and S. Nihitanov, "Chopping in continuous-time sigma-delta modulators," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2017, pp. 1-4.

- [27] R. Schreier, S. Pavanand, and G. C. Temes, Understanding Delta-Sigma Data Converters. Hoboken, NJ, USA: Wiley, 2017.

- [28] M. S. J. Steyaert and W. M. C. Sansen, "A micropower low-noise monolithic instrumentation amplifier for medical purposes," IEEE J. Solid-State Circuits, vol. 22, no. 6, pp. 1163-1168, Dec. 1987.

- [29] R. Muller, S. Gambini, and J. M. Rabaey, "A 0.013 mm<sup>2</sup>, 5  $\mu$ W, DC-coupled neural signal acquisition IC with 0.5 V supply," IEEE J. Solid-State Circuits, vol. 47, no. 1, pp. 232-243, Jan. 2012.

- [30] H. Jiang, J. G. Vogel, and S. Nihtianov, "A power-efficient readout for wheatstone-bridge sensors with COTS components," IEEE Sensors J., vol. 17, no. 21, pp. 6986-6994, Nov. 2017.

- [31] MINIOHM (5E10) Precision Wirewound Resistor, Rhopoint Components Ltd., East Grinstead, U.K., 2003.

Hui Jiang (S'14) received the master's degree in integrated circuit engineering from Tsinghua University, Beijing, China, in 2013.

He is currently a Ph.D. Researcher with the Electronic Instrumentation Laboratory, Delft University of Technology, Delft, The Netherlands. His research work involves the design of energy-efficient readout ICs (ROICs) for piezo-based sensors and capacitive displacement sensors. His research has resulted in several patents and publications in JSSC, ISSCC, and VLSI.

Mr. Jiang was a recipient of the ISSCC Student Travel Grant in 2015, the third prize of the Benelux Student Chip Design Competition in 2016, and the IEEE Solid-State Circuits Society Predoctoral Achievement Award in 2018. He is a Committee Member of the SSCS Young Professionals and serves as a reviewer for the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, the IEEE SENSORS JOURNAL, the IEEE TRANSACTIONS ON INSTRUMENTATION AND MEASUREMENT, IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, and the Sensors and Actuators A: Physical.

Stoyan Nihtianov (M'93-SM'98) is currently with the Electronic Instrumentation Laboratory, Microelectronics Department, TU Delft, The Netherlands, where he is an Associate Professor leading the Research Group on Industrial Electronic Instrumentation. He is also a Senior Research Fellow with the high-tech company ASML, Veldhoven, The Netherlands. He has authored or co-authored over 160 peerreviewed scientific papers, five books and book chapters, in the field of sensors and sensor interface electronics. He holds 26 patents.

Kofi A. A. Makinwa (M'97-SM'05-F'11) received the B.Sc. and M.Sc. degrees from Obafemi Awolowo University, Ife, Nigeria, in 1985 and 1988, respectively, the M.E.E. degree from the Philips International Institute, Eindhoven, The Netherlands, in 1989, and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2004.

From 1989 to 1999, he was a Research Scientist with the Philips Research Laboratories, Eindhoven, where he worked on interactive displays and digital

recording systems. In 1999, he joined the Delft University of Technology, where he is currently an Antoni van Leeuwenhoek Professor and the Head of the Microelectronics Department. He has co-authored or edited 15 books, as well as over 250 technical papers, and holds 30 patents. His research interests include the design of mixed-signal circuits, sensor interfaces and smart sensors.

Dr. Makinwa is a member of the Royal Netherlands Academy of Arts and Sciences and an Editorial Board Member of the PROCEEDINGS OF THE IEEE. For his doctoral research, he received the 2005 Simon Stevin Gezel Award from the Dutch Technology Foundation. At the 60th anniversary of ISSCC, he was recognized as a top-10 contributor. He is the Analog Subcommittee Chair of the International Solid-State Circuits Conference (ISSCC). He is also on the program committees of the VLSI Symposium, the European Solid-State Circuits Conference (ESSCIRC), and the Advances in Analog Circuit Design (AACD) Workshop. He has been a Guest Editor of the Journal of Solid-State Circuits (JSSC) and has served as a Distinguished Lecturer and Elected AdCom Member for the IEEE Solid-State Circuits Society. He was a co-recipient of 15 best paper awards from the JSSC, ISSCC, VLSI, ESSCIRC, and Transducers.