# An Energy-Efficient, Resistor-Based Smart Temperature Sensor

Delft University of Technology Kianoush Souri

**Delft University of Technology**

**Faculty of EEMCS**

# DELFT UNIVERSITY OF TECHNOLOGY DEPARTMENT OF ELECTRICAL ENGINEERING

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled An Energy-Efficient, Resistor-Based Smart Temperature Sensor

by

Kianoush Souri

in partial fulfilment of the requirements for the degree of

MASTER OF SCIENCE MICROELECTRONICS

Dated: 29<sup>th</sup> August, 2013

Supervisor:

Prof. Dr. Kofi A.A. Makinwa

Committee Members:

Dr. Ing. Leo de Vreede

Dr. Ir. Michiel Pertijs

# An Energy-Efficient, Resistor-Based Smart Temperature Sensor

Submitted to the Office of Graduate Studies of the Delft University of Technology In partial fulfillment of the requirements for the degree of MASTER OF SCIENCE

> Kianoush Souri 4181212 August 29th, 2013

Supervisor: Prof. Dr. K. A. A. Makinwa

# **Contents**

# CHAPTER 1: INTRODUCTION

| 1.1 Introduction                                                         |

|--------------------------------------------------------------------------|

| 1.2 MEMS Frequency References                                            |

| 1.3 Temperature Sensors in CMOS Technology                               |

| 1.3.1 BJT-Based Temperature Sensor                                       |

| 1.3.2 ETF-Based (Electro-Thermal Filter) Temperature Sensor              |

| 1.3.3 Temperature-Dependent-Delay-Line (TDDL-Based) Temperature Sensor 4 |

| 1.3.4 Resistor-Based Temperature Sensor                                  |

| 1.3.5 Comparison                                                         |

| 1.4 Energy-Efficiency Comparison                                         |

| 1.4.1 Resistor-Based Sensing                                             |

| 1.4.1 BJT-Based Sensing7                                                 |

| 1.4.2 Conclusion                                                         |

| 1.5 Conclusion7                                                          |

| 1.6 Thesis Organization                                                  |

| CHAPTER 2: TEMPERATURE SENSING PRINCIPLE                                 |

| 2.1 Introduction                                                         |

| 2.2 Existing Resistor-Based Temperature Sensors                          |

| 2.2.1 Temperature-Dependent RC Oscillator                                |

| 2.2.2 Auto-Balanced RC-Network                                           |

| 2.3 Phase-Domain Temperature-Sensing Principle                           |

| 2.3.1 Phase-Extraction Methodology                                       |

| 2.3.1.2 Phase Extraction Linearity                                       |

| 2.3.2 Noise Sources Employing the Phase-Domain Principle | 15 |

|----------------------------------------------------------|----|

| 2.4 Considerations for the Filter's Implementation       | 16 |

| 2.4.1 Low Pass Filter (LPF)                              | 17 |

| 2.4.1.1 1 <sup>st</sup> -order LPF Noise                 | 18 |

| 2.4.1.1 Temperature-to-Phase Conversion                  | 18 |

| 2.4.2 High Pass Filter (HPF)                             | 20 |

| 2.4.2.1 Temperature-to-Phase Conversion                  | 20 |

| 2.4.3 Band Pass Filter                                   | 20 |

| 2.4.3.1 Phase-to-Temperature Sensitivity                 | 20 |

| 2.4.3.1 2 <sup>nd</sup> -order BPF Noise                 | 21 |

| 2.4.3.2 Temperature-to-Phase Conversion                  | 23 |

| 2.4.4 Conclusion                                         | 23 |

| 2.4.5 Implemented RC Filter                              | 24 |

| 2.4.6 Conclusion                                         | 24 |

| 2.5 Available Resistors in CMOS                          | 25 |

| 2.5.1 Non-Linear Temperature-Dependence                  | 25 |

| 2.5.2 Parasitic Effects                                  | 25 |

| 2.5.3 Voltage Dependency                                 |    |

| 2.5.4 Conclusion                                         | 26 |

| 2.6 Temperature Sensing Resolution                       | 27 |

| 2.6.1 Temperature Sensitivity                            | 27 |

| 2.6.1 BPF Noise Analysis                                 |    |

| 2.6.2 Temperature Sensing Resolution                     | 29 |

| 2.7 Conclusion                                           | 29 |

|                                                          |    |

# CHAPTER 3: FIRST TEST CHIP

| 3.1 Ir | ntroduction                                     |    |

|--------|-------------------------------------------------|----|

| 3.2 P  | rior PDSDM Implementations                      |    |

| 3.3 F  | ïrst Test Chip                                  |    |

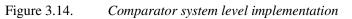

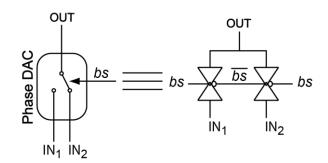

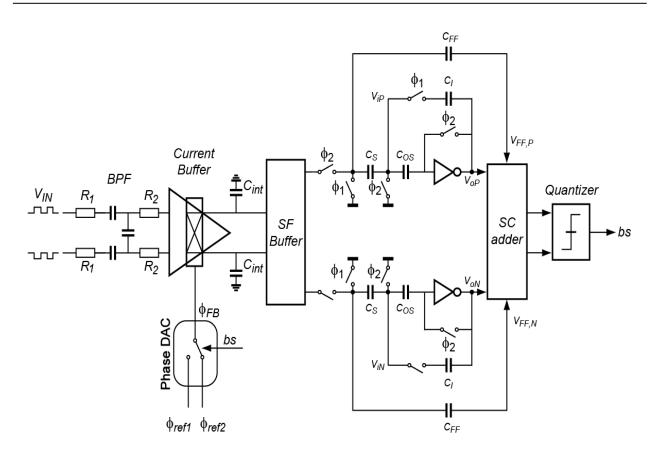

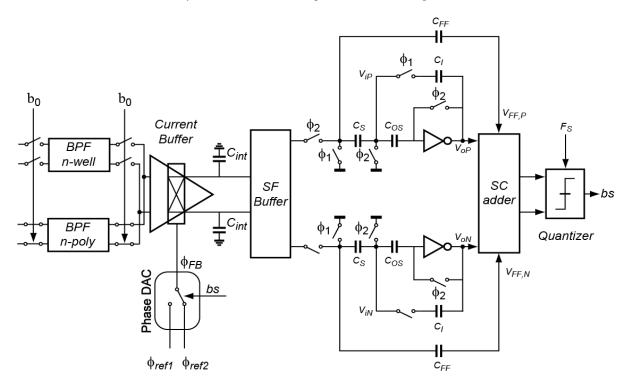

| 3.3.1  | PDSDM system level architecture                 |    |

| 3.3.2  | 1 <sup>st</sup> order PDSDM system-level design |    |

| 3.3.2  | 2.2 Charge-balancing scheme in PDSDM            |    |

| 3.3.2  | 2.3 Considerations of Wien-bridge Interfacing   |    |

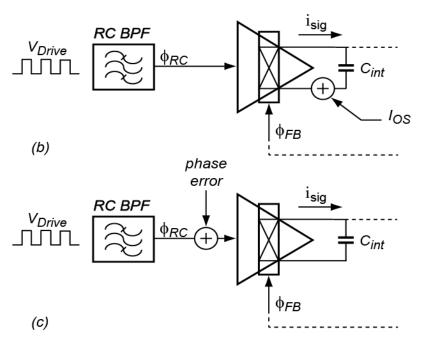

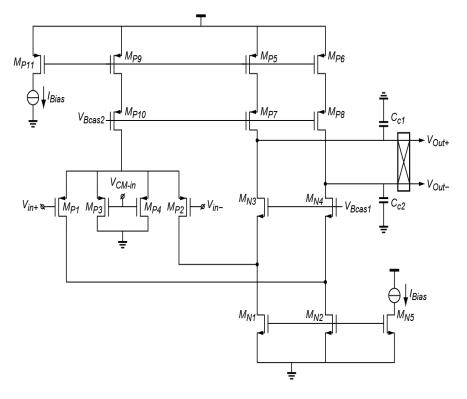

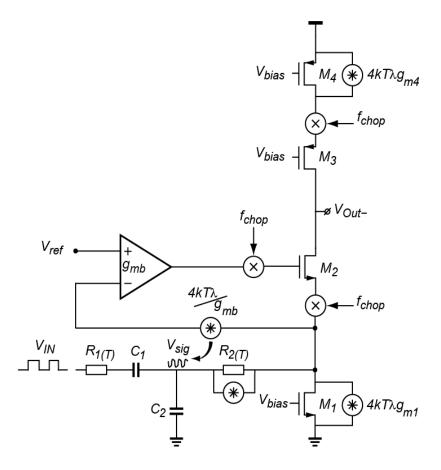

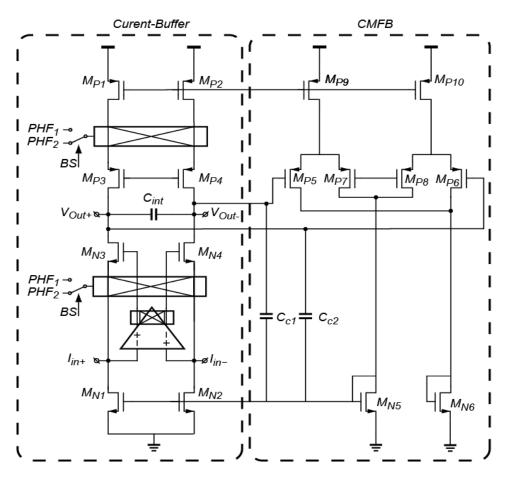

| 3.4 P  | DSDM Circuit Design                             |    |

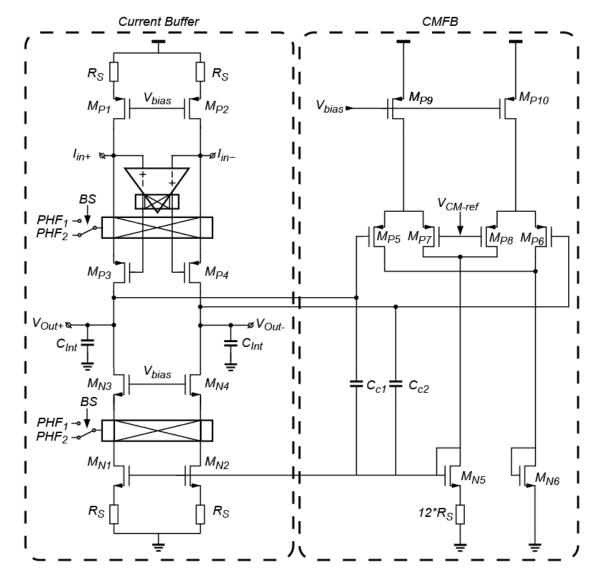

| 3.4.1  | Current-buffer Implementation                   |    |

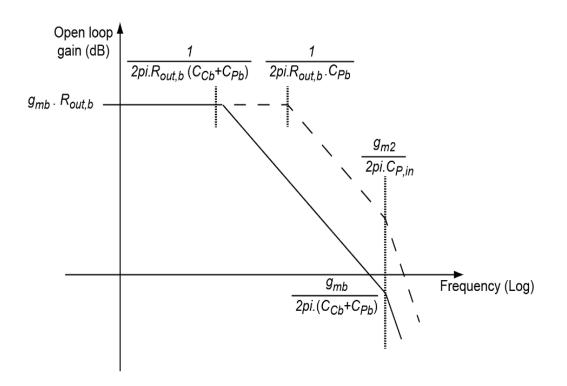

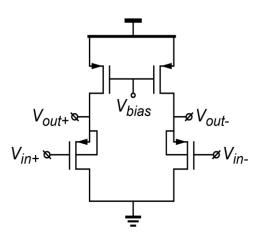

| 3.4.   | 1.2 Gain booster                                |    |

| 3.4.   | 1.3 Compensation                                |    |

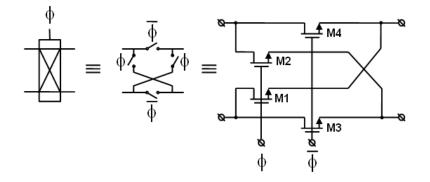

| 3.4.   | 1.4 Mixer Implementation & Considerations       |    |

| 3.4.   | 1.5 Readout Noise                               |    |

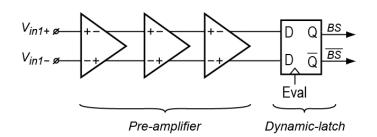

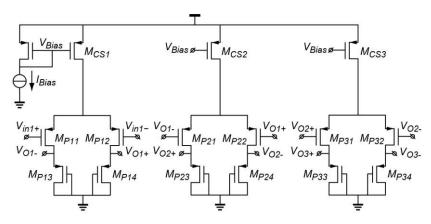

| 3.4.2  | Comparator                                      |    |

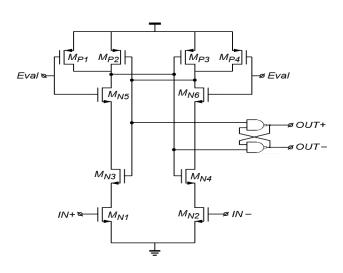

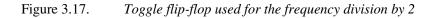

| 3.4.3  | Phase Generator Block                           |    |

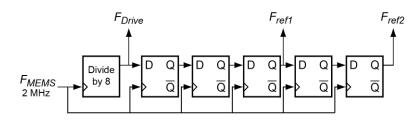

| 3.4.4  | Phase DAC                                       |    |

| 3.4.5  | Jitter and synchronization                      |    |

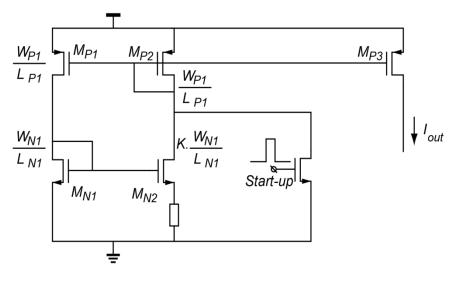

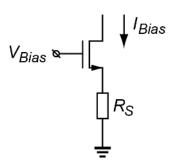

| 3.4.6  | Constant-Gm Bias Circuit                        |    |

| 3.5 E  | Expected Performance                            |    |

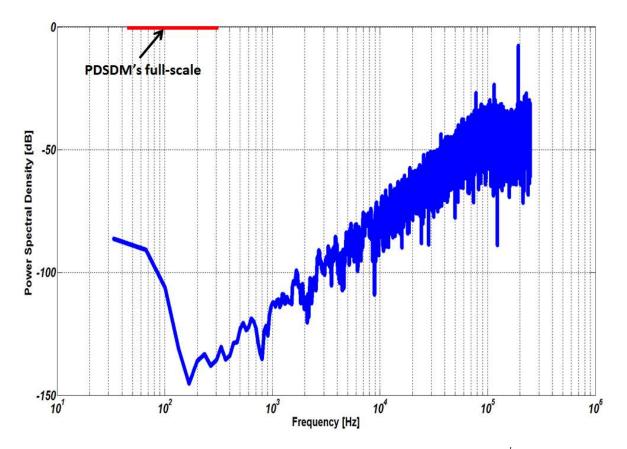

| 3.5.1  | Readout noise                                   |    |

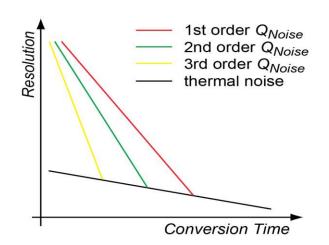

| 3.5.2  | Quantization Noise                              |    |

| 3.5.3  | Total Noise                                     |    |

| 3.6 N  | leasurement Results                             |    |

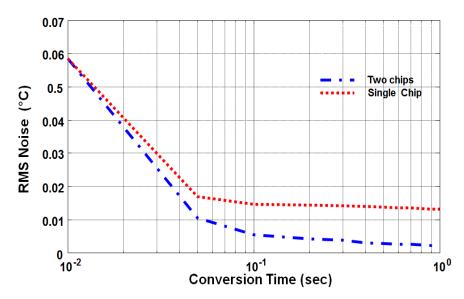

| 3.6.2  | Resolution vs. Conversion Time                  | 50 |

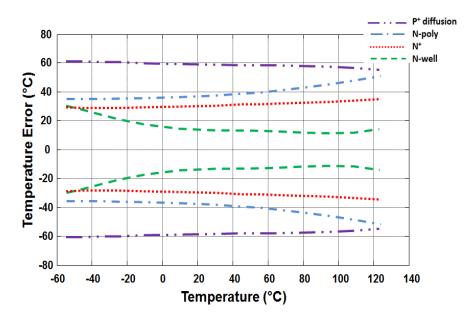

| 3.6.3 Temperature Inaccuracy Associated with Resistor         | 51 |

|---------------------------------------------------------------|----|

| 3.7 Conclusion                                                | 53 |

| CHAPTER 4: SECOND TEST CHIP                                   |    |

| 4.1 Introduction                                              | 55 |

| 4.2 PDSDM requirements                                        |    |

| 4.3 First design weaknesses                                   | 57 |

| 4.3.1 Thermal Noise                                           | 57 |

| 4.3.1.2 Source Degeneration                                   |    |

| 4.3.2 Power Reduction                                         |    |

| 4.3.3 Voltage Dependency                                      |    |

| 4.3.4 Supply Noise                                            | 60 |

| 4.3.5 Conclusion                                              | 61 |

| 4.4 2 <sup>nd</sup> -order "Hybrid Sigma-Delta"               | 61 |

| 4.4.1 System Implementation                                   | 62 |

| 4.5 Circuit Implementation                                    | 64 |

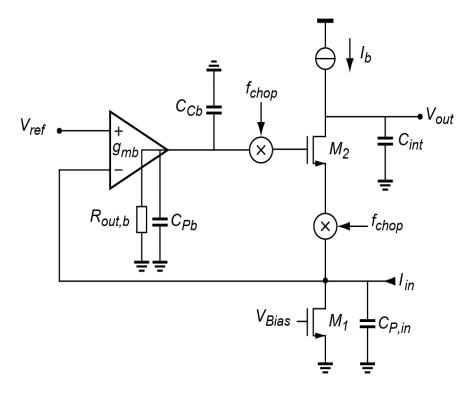

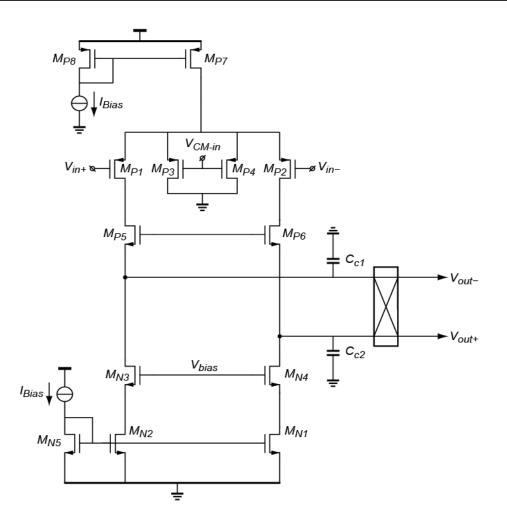

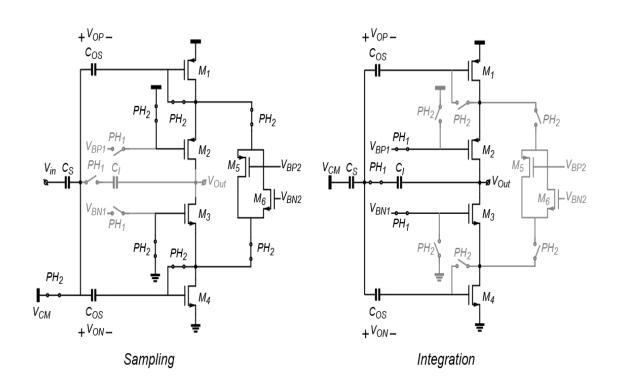

| 4.5.1 First Integrator                                        | 64 |

| 4.5.1.2 Gain Booster                                          | 66 |

| 4.5.2 1 <sup>st</sup> & 2 <sup>nd</sup> Integrator Connection | 67 |

| 4.5.3 Second Integrator                                       | 68 |

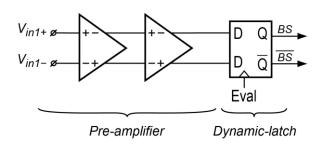

| 4.5.4 Comparator Implementation                               | 69 |

| 4.6 Simulation Results                                        | 70 |

| 4.7 Chip Implementation                                       | 70 |

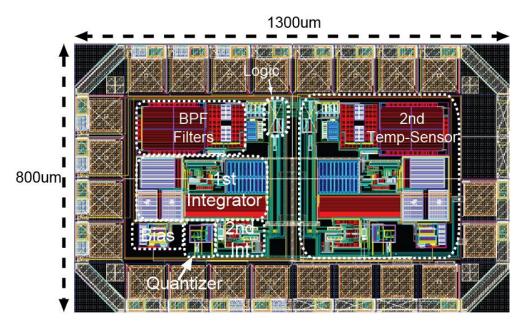

| 4.7.2 Layout                                                  | 72 |

| 4.8 Expected Performance                                      | 72 |

| 4.9 Conclusion                                                | 74 |

## CHAPTER 5: CONCLUSION

| 5.1 | Conclusion & Future Work | 77 | 7 |

|-----|--------------------------|----|---|

|-----|--------------------------|----|---|

# ACKNOWLEDGMENT

Foremost, I would like to express my sincere gratitude to my advisor Prof. Kofi Makinwa for the continuous support of my M.Sc. study and research, for his patience, motivation, enthusiasm, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis.

Besides my advisor, I would like to thank the rest of my thesis committee: Dr. Michiel Pertijs, and Dr. Leo de Vreede for attending my M.Sc. defense.

Last but not least, I would like to thank my family: my parents, my brothers (Kamran & Kamyar), my sisters in law (Sara & Zohreh), also my friends: Ali Fekri, Saleh Heydari, Shahab Shariat and all the rest who are not mentioned in here. Without your continuous support and friendship it was not possible to catch this point, I wish all the best for you all.

Kianoush,

Delft,

29<sup>th</sup> August 2013

# 1 Introduction

# **1.1** Introduction

Temperature is a critical operating parameter of most electrical, mechanical, magnetic, chemical, radiant, and biological systems [1]. This is because such systems often exhibit some sort of temperature dependency, which in turn necessitates temperature measurement and control in many systems [2-8].

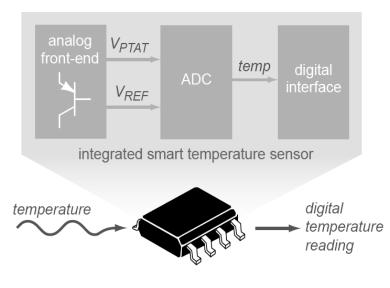

Smart temperature sensors output a digital code representing ambient temperature. As shown in Fig. 1.1, the first step involves using a sensor to convert temperature into an electrical signal. This signal is then processed by an analog front-end and digitized by an on-chip analog-to-digital converter [9, 10]. The sensor's digital output then can be readily transmitted to other digital building blocks of a system [11], in a robust manner.

The goal of this project is to design an energy-efficient, high-resolution (sub-mK) and highly accurate temperature sensor (<0.1°C) for the compensation of frequency references based on micro electro-mechanical systems (MEMS). In the following, a brief introduction to MEMS frequency references will be given and the requirements for this application will be further discussed. Then, the energy-efficiency of existing CMOS temperature sensors is discussed, and a number of promising temperature sensing techniques are identified.

# **1.2 MEMS Frequency References**

Frequency references are widely used in electronic systems, where they often set limits to the obtainable performance, functionality, power consumption, size and cost [13, 14]. MEMS-based oscillators are being actively developed as sources of highly stable reference frequencies [15], with the small form-factor needed in hand-held wireless devices, and comparable power consumption than the original quartz-crystal-based frequency references [16].

Figure 1.1. Integrated smart sensor block diagram [9].

Compared to quartz-crystal-based references, MEMS frequency references suffer from significantly inferior accuracy both in terms of temperature stability and manufacturing tolerance [15, 17]. As a result, an important research focus is on improving this [18, 19].

Process spread impacts the accuracy of MEMS resonators. This can be improved with more advanced lithography and multi-point (3-to-6 point) trimming. However, the large native temperature-coefficient of frequency (TCF) of MEMS resonators, typically ~30 ppm/°C, causes a drift of more than 5000 ppm across the military temperature range (-55°C to 125°C) [15]. Since many applications require variations of less than ±50ppm and even ±1ppm, temperature compensation becomes necessary for MEMS oscillators [20, 8]. Which in turn, in order to achieve a frequency-instability of a few ppms, the temperature sensor's inaccuracy should be less than 0.1°C [8].

In a recent publication [8], it has been shown that for high performance applications, the temperature sensor's noise should be less than  $170\mu K$  (rms). Because of that the temperature sensor's noise will then determine the output jitter of the MEMS oscillator.

Lastly, to be able to track ambient temperature variations, the temperature sensor's conversion rate should be less than 100msec, while satisfying all the above mentioned requirements.

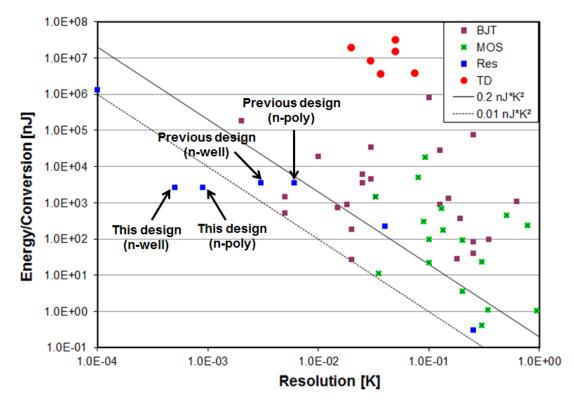

Since frequency references are widely used in portable, battery-powered devices, energyefficiency is a key requirement. The relative energy-efficiency of smart temperature sensors can be assessed with the help of a resolution figure of merit (FOM) defined as the product of energy per conversion and square of resolution [22]:

$$Resolution FOM = Energy (per conversion) \times Resolution^{2}.$$

(1.1)

| Table 1.1.Target specifications of this work. |                     |  |  |

|-----------------------------------------------|---------------------|--|--|

| Parameter                                     | Value               |  |  |

| Power consumption                             | <30uW               |  |  |

| Analog core area                              | <0.1mm <sup>2</sup> |  |  |

| Conversion time                               | 100msec             |  |  |

| Resolution (RMS)                              | <1mK                |  |  |

| Inaccuracy $(3\sigma)$                        | <0.1°C              |  |  |

| Calibration points #                          | 3 to 6              |  |  |

| Resolution FOM                                | <2pJ°K <sup>2</sup> |  |  |

TT 1 1 1 1 c .1 .

State-of-the-art temperature sensors achieve a resolution FOM about 10pJ°K<sup>2</sup>, however, only a few can also achieve mK-level resolution in a conversion time of 100msec [8, 9]. The aim of this work is to achieve a significant improvement in both energy efficiency and resolution. As discussed, multi-point trimming is required for MEMS frequency references, therefore, the integrated temperature sensor without any cost overhead. Table 1.1 summarizes the target specification of a temperature sensor for MEMS resonator compensation.

There are numerous temperature-sensing devices available in CMOS technology and consequently different manners of measuring temperature, each of which leads to a certain maximum energy-efficiency. To make the most energy-efficient temperature sensor, an appropriate choice should first be made as to the temperature-sensing device. In the next section, some existing temperature sensing methods are briefly investigated.

#### 1.3 **Temperature Sensors in CMOS Technology**

In this section, four temperature sensing methods in CMOS are briefly discussed, and in the next section, their performance is compared.

#### 1.3.1 **BJT-Based Temperature Sensor**

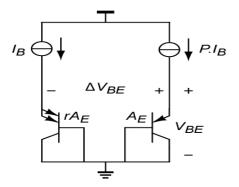

Figure 1.2 illustrates two bipolar transistors with emitter areas  $A_E$  and  $r.A_E$ , configured in a "diode connected" fashion, and biased by currents  $I_1$  and  $pI_1$ , respectively [23, 24]. Two different temperature dependent signals with negative and positive temperature coefficients can then be generated. The base-emitter voltage  $V_{BE}$  has a complementary-to-absolutetemperature (CTAT) behavior with a temperature coefficient of  $\approx$  -2mV/°C. The difference in base-emitter voltages  $\Delta V_{BE}$ , on the other hand, has a proportional-to-absolute-temperature (PTAT) behaviour over temperature with a temperature coefficient of  $\approx 100 \ \mu V/^{\circ}C$  [12]. An appropriate linear combination of PTAT and CTAT voltages provides a temperature independent band-gap reference voltage [9]. The PTAT ratio  $\mu$  in Eqn. 1.2, which represents the temperature, can then be readily determined by means of an analog-to-digital converter (ADC) [12].

$$\mu = \frac{V_{PTAT}}{V_{REF}} = \frac{\alpha \Delta V_{BE}}{\alpha \Delta V_{BE} + V_{BE}}$$

(1.2)

Figure 1.2. The core of the BJT-based smart temperature sensor [12].

A state-of-the-art BJT-based temperature sensor achieves an energy-efficiency of 11  $pJ^{\circ}K^{2}$ , and 5mK resolution in a 100msec conversion time. Moreover, this sensor obtains  $\pm 0.15^{\circ}C$  inaccuracy over the military temperature range after a one point calibration and trim at room temperature [9].

# **1.3.2** ETF-Based (Electro-Thermal Filter) Temperature Sensor

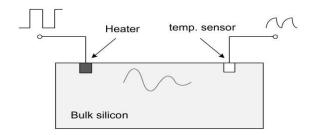

Silicon's *Thermal Diffusivity* is defined as the rate at which heat diffuses through a silicon substrate. Recent research has shown that the thermal diffusivity D of silicon is a well-defined parameter, as the silicon wafer used for IC fabrication is a highly pure material [25]. The thermal diffusivity of bulk silicon is strongly temperature dependent:  $D \approx 1/T^{1.8}$  [26]. Fig. 1.3 shows the structure of an electro-thermal filter (ETF), which uses a heater to generate heat pulses, and a thermopile (at a distance *S* from the heater), which converts the received temperature variations into a voltage signal. An ETF behaves like a low-pass filter in the thermal domain. Driving this filter at a certain frequency results in a temperature dependent phase shift which can then be digitized by an ADC. A state-of-the-art ETF-based temperature sensor achieves an energy-efficiency of  $0.7\mu J^{\circ}K^{2}$ , and 20mK resolution in a 6.2sec conversion time. Also, after batch calibration, it achieves  $\pm 0.2^{\circ}C$  inaccuracy over the military temperature range [27].

Figure 1.3. Electro-Thermal Filter in CMOS technology [31].

# **1.3.3** Temperature-Dependent-Delay-Line (TDDL-Based) Temperature Sensor

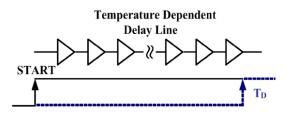

The time delay associated with an inverter is temperature dependent. It can then be measured and digitized by a time-to-digital converter (TDC) [28]. A temperature-dependent delay line consists of an even number of inverters (or equivalent delay buffers) as shown in Fig. 1.4. As the sensor's dynamic range is defined in the time-domain, the longer the inverter

chain is, the more resolution can be achieved. This temperature dependent delay is a function of channel's mobility, threshold voltage, and supply voltage, which results in poor supply dependency. A state-of-the-art TDDL-based temperature sensor achieves an energy-efficiency of  $160nJ^{\circ}K^{2}$ , and 91mK resolution in a 500msec conversion time. It also achieves  $\pm 0.6^{\circ}C$  inaccuracy over a  $0^{\circ}C$  to  $90^{\circ}C$  temperature range after two point trimming [28].

Figure 1.4. Temperature dependent delay line implementation in CMOS.

# **1.3.4** Resistor-Based Temperature Sensor

Resistors have been widely used as temperature sensors [8, 29, and 30]. In CMOS technology, their temperature-coefficient is a function of resistor type, with temperature coefficients ranging between  $0.1\%/^{\circ}$ C and  $0.4\%/^{\circ}$ C. There are different ways of reading out a resistor. One way is to make a half-Wheatstone bridge using resistors with different temperature coefficients [29]. The bridge is then balanced by a feedback loop based on a successive approximation algorithm. This work achieves an energy-efficiency of 19pJ°K<sup>2</sup>, and 250mK resolution in a 12.5µsec conversion time. It also achieves ±0.5°C inaccuracy over a 0°C to 100°C temperature range after one point trimming [29]. Another way of reading out a resistor is by incorporating it in a voltage divider together with a switched-capacitor (SC) resistor. A feedback loop tries to balance the two impedances by regulating the SC resistor's effective impedance via its switching frequency. The required frequency then represents the temperature [8]. This work achieves an energy-efficiency of 13pJ°K<sup>2</sup>, and 0.1mK resolution in a 100msec conversion time. It also achieves ±0.03°C inaccuracy over a -40°C to 85°C temperature range, but this is after 6 point trimming [8].

# 1.3.5 Comparison

Table 1.2 compares four temperature sensing topologies. It can be seen that the TDDLbased approach results in poor inaccuracy and exhibits a relatively high supply dependency. It also has poor energy-efficiency compared to resistor- and BJT-based sensors. In the case of ETF-based sensors, although good accuracy can be achieved, their inherently high power consumption prohibits their use in applications where energy-efficiency is vital. Resistorbased and BJT-based temperature sensors both have better energy-efficiency than the other two candidates.

Examination of Table 1.2 shows that resistor-based temperature sensors are less accurate than BJT-based ones. However, the multi-point trimming commonly used in MEMS resonator applications can also be re-used to improve their accuracy. In order to make a final choice between resistor and BJT-based temperature sensors, the fundamental limits on their energy-efficiency must be examined more carefully. This will be investigated in the following section.

| Table 1.2. State-oj-the-art temperature sensors. |                       |                                        |                                      |                                            |

|--------------------------------------------------|-----------------------|----------------------------------------|--------------------------------------|--------------------------------------------|

| Parameter                                        | Resistor[29]          | BJT[9]                                 | ETF[27]                              | TDDL[28]                                   |

| Technology                                       | 0.18µm                | 0.16µm                                 | 0.16µm                               | 0.35µm                                     |

| Supply voltage                                   | 1.2 to 2V             | 1.5V to 2V                             | 5V                                   | 3.3V                                       |

| Supply current                                   | 20μΑ                  | 3.4µA                                  | 700µA                                | 12µA                                       |

| Supply sensitivity                               | 0.625°C/V             | 0.5°C/V                                |                                      | 33°C/V                                     |

| Temperature<br>range                             | 0°C<br>to 100°C       | -55°C<br>to 125°C                      | -70°C<br>to 170°C                    | 0°C<br>to 90°C                             |

| Inaccuracy<br>(Trim method)                      | ±0.5°C<br>(one point) | 0.15°C(3σ)<br>(voltage<br>calibration) | ±0.4°C(3σ)<br>(batch<br>calibration) | $\pm 0.6^{\circ}C(3\sigma)$<br>(two point) |

| Resolution<br>(conversion time)                  | 0.25K<br>(12.5µsec)   | 0.005K<br>(100msec)                    | 0.04K<br>(6.25sec)                   | 0.091K<br>(500msec)                        |

| Resolution energy<br>efficiency                  | 19 pJ°K <sup>2</sup>  | 11pJ°K <sup>2</sup>                    | $4.8 \mu J^{\circ} K^2$              | 160nJ°K <sup>2</sup>                       |

Table 1.2.State-of-the-art temperature sensors.

# 1.4 Energy-Efficiency Comparison

As concluded in the previous section, both resistor-based and BJT-based temperature sensors are suitable candidates for energy-efficient applications. To make the best choice, their energy-efficiency should be compared. This is the subject of the following sections.

#### 1.4.1 Resistor-Based Sensing

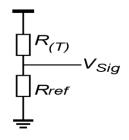

A resistor-based temperature sensing technique is shown in Fig. 1.5 [8]. The temperaturesensitive-voltage signal is produced by making a voltage divider in which  $R_{(T)}$  is a temperature dependent resistor and  $R_{ref}$  is a reference resistor assumed to be quite stable over temperature. The temperature sensitivity of the shown voltage divider then can be calculated as follows, while assuming  $V_{DD} = 1.8V$ ,  $R_{ref} = R_{(T)}$ , and finally a typical temperature coefficient of 0.3%/K for available resistors in CMOS [8]:

$$\Delta V_{Sig} \approx \frac{1}{4} \left( \frac{\Delta R_{(T)}}{R_{(T)}} \right) V_{DD} = 1.44 m V /^{\circ} \text{C}.$$

(1.3)

Figure 1.5. *Resistor-based temperature sensing* [8].

The noise associated with the voltage divider shown in Fig. 1.5, while drawing 1µA from a 1.8V supply (which means  $R = R_{Ref} = R_{(T)} = 900k\Omega$ ) in a 5Hz bandwidth is equal to:

$$v_{n,Tot} = \sqrt{2 \times (4KT/R) \cdot (\frac{R}{2})^2 \cdot BW} = 189nV.$$

(1.4)

by combining this with the previously calculated sensitivity of the voltage divider together with its noise, then the temperature-sensing resolution can be calculated as follows:

$$\sigma_{T,Resistor} = \frac{v_{n,Tot}}{s_T^{\Delta V_{BE}}} = \frac{189nV}{1.44 \ mV/K} = 131 \mu K.$$

(1.5)

#### 1.4.1 BJT-Based Sensing

The PTAT ratio  $\mu$  in Eqn. 1.2, which represents the temperature, can be mapped into a reading in degrees Celcius by linear scaling:

$$D_{out} = A.\,\mu + B,\tag{1.6}$$

where  $A \cong 600$  and B = -273. The temperature-sensing resolution of the BJT-based temperature sensor elaborated in [12] is as follows:

$$\sigma_{T,bip} = \frac{A}{V_{REF}} \alpha \sqrt{\frac{2kT(1-\mu)}{g_{m1} \cdot t_{conv}}},$$

(1.7)

where  $g_{m1}$  is the transconductance of the transistor biased with the smaller bias current. Consequently, using A  $\cong 600$ ,  $V_{REF} = 1.2$ V and  $\mu = 0.5$  (which represents the bit density at room temperature), Eqn. 1.7 can be re-written as:

$$\sigma_{T,bip} \cong (5.1 \cdot 10^{-9} \text{ KC}^{0.5}) \cdot \alpha \sqrt{\frac{1}{I \cdot t_{conv}}}, \qquad (1.8)$$

where if  $t_{conv} = 100$  msec (5Hz bandwidth),  $\alpha = 20$ , and  $I = 1\mu A$ , the output-referred noise will be:

$$\sigma_{T,bip} \cong 320 \mu \text{K},\tag{1.9}$$

## 1.4.2 Conclusion

If the energy/conversion is assumed to be the same for both resistor and BJT-based approaches, then comparing Eqns. 1.5 and 1.9 and using Eqn. 1.1 reveals that the ultimate resolution FoM of resistor-based temperature sensors is about 6x better than the BJT-based FoM. This is because resistors can provide 2.5x more resolution.

# **1.5** Conclusion

It can be concluded that resistors are the best candidates for on-chip temperature sensing as far as energy-efficiency is concerned. However, designing an energy-efficient smart temperature sensor also requires energy-efficient readout circuitry. In order to prevent excessive power from being wasted either in the sensor part or readout part, the readout circuitry noise-performance should be roughly the same as that of the sensor.

A literature study shows that in practice temperature sensor resolution is often limited by the noise of the readout circuitry. A resistor-based temperature sensor achieves  $100\mu$ K in a 100msec conversion time, while its ultimate resolution should be  $16\mu$ K under these conditions [8]. Also, a BJT based temperature sensor achieves 5mK with a 100msec conversion time, instead of the potentially achievable 0.2mK [9, 12]. This means that in these designs, the noise from the readout circuitry is still much higher than that of the sensor, thus there is still enough room to improve their energy-efficiency.

# **1.6** Thesis Organization

This thesis is organized as follows. A new resistor readout technique, called the "*Phase-Domain*" technique, is discussed in Chapter 2. Moreover, the sensor's design and implementation will be elaborated. In Chapter 3, the design of an energy-efficient temperature-sensing topology is presented. Furthermore, the circuit implementation and considerations of a first test chip are described. This chapter also includes the measurement results of the first test chip with a brief discussion on the weaknesses and potential points for improvement. In Chapter 4, the last chapter, the weaknesses of the first test chip will be addressed while a new ADC implementation based on the concept of a "*Hybrid Sigma-Delta Modulator*" is developed to address the previously mentioned requirements. This chapter ends with conclusion and a discussion of future work that can be done to further improve performance.

#### References

- [1] "National Semiconductor Temperature Sensor Handbook," National Semiconductor, <u>www.national.com</u>.

- [2] Kneezel et al., "Ink jet printer having temperature sensor for replaceable print heads," U.S. Patent 5 85 825, Dec. 17, 1996.

- [3] Victor Alexandrovich Kalinin et al., "Saw torque and temperature sensor," EP1882169 B1, Apr. 29, 2009.

- [4] L.M. Johnson, "Integrated optical temperature sensor," Applied physics letters, pp. 134-136, Jun. 2009.

- [5] K. Sundaresan, P. E. Allen and F. Ayazi, "Process and temperature compensation in a 7-MHz CMOS clock oscillator," IEEE J. Solid-State Circuits, pp. 433-442, Feb. 2006.

- [6] F. Fiori and P. S. Crovetti "A new compact temperature-compensated CMOS current reference," IEEE Trans. Circuits Syst. II, Expr. Briefs, vol. 52, no. 11, pp.724-728, 2005.

- [7] D.-S. Min et al., "Temperature-compensation circuit techniques for high-density CMOS DRAMs," in Proc. Digest of Technical Papers VLSI Circuits 1991 Symp., 1991, pp. 125-126.

- [8] M. H. Perrott et al., "A temperature-to-digital converter for a MEMS-based programmable oscillator with < ±0.5-ppm frequency stability and < 1-ps integrated jitter," IEEE J. Solid-State Circuits, vol. 48, pp. 276-291, Dec. 2012.

- [9] K. Souri, Y. Chae and K. A. A. Makinwa, "A CMOS temperature sensor with a voltagecalibrated inaccuracy of ±0.15°C (3σ) from -55 to 125°C," IEEE J. Solid-State Circuits, vol. 48, no. 1, pp. 292-301, Jan. 2013.

- [10] M. A. P. Pertijs, K. A. A. Makinwa and J. H. Huijsing, "A CMOS temperature sensor with a 3s inaccuracy of ±0.1°C from -55°C to 125°C," IEEE J. Solid-State Circuits, vol. 40, no. 12, pp. 2805-2815, Dec. 2005.

- [11] Y. W. Li et al., "A 1.05V 1.6mW 0.45°C  $3\sigma$ -resolution  $\Delta\Sigma$ -based temperature sensor with parasitic-resistance compensation in 32nm CMOS," ISSCC Dig. Tech. Papers, pp. 340-341, Feb. 2009.

- [12] M. A. P. Pertijs and J. H. Huijsing, "Precision Temperature Sensors in CMOS Technology", Springer, 2006.

- [13] H. M. Lavasani, R. Abdolvand and F. Ayazi, "A 500 MHz low phase noise AlN-on-silicon reference oscillator," in Proc. IEEE CICC, 2007, pp. 599-602.

- [14] B. P. Harrington, M. Shahmohammadi and R. Abdolvand, "Toward ultimate performance in GHz MEMS resonators: Low impedance and high Q," in Proc. IEEE Micro Electro Mechanical Systems Conf., 2010, pp.707-710.

- [15] H. M. Lavasani et al. "Electronic temperature compensation of lateral bulk acoustic resonator reference oscillators using enhanced series tuning technique," IEEE J. Solid-State Circuits, vol. 47(6), pp. 1381-1393, May 2012.

- [16] M. A. Hopcroft et al., "A high-stability MEMS frequency reference," in Proc. 14th Int. Conf. Solid State Sens., Actuators, Microsyst. (Transducers), 2007, pp.1307-1310.

- [17] F. Ayazi, "MEMS for integrated timing and spectral processing," in Proc. IEEE CICC, 2009, pp. 65-72.

- [18] G. Stemme, "Resonant silicon sensors," J. Micromech. Microeng, vol. 1, no. 2, pp. 113-125, 1991.

- [19] S. Pourkamali, A. Hashimura, R. Abdolvand, G. K. Ho, A. Erbil and F. Ayazi, "High-Q single-crystal silicon HARPSS capacitive beam resonators with self-aligned sub-100-nm transduction gaps," J. Microelectromech. Syst., vol. 12, no. 4, pp.487-496, 2003.

- [20] T. Mattila et al., "A 12 MHz micromechanical bulk acoustic mode oscillator," Sens. Actuators A, Phys., vol. 101, no. 1, pp. 1-9, 2002.

- [21] S. Pourkamali, G. K. Ho and F. Ayazi, "Low-impedance VHF and UHF capacitive silicon bulk acoustic wave resonators—Part I: Concept and fabrication," IEEE Trans. Electron Devices, vol. 54, no. 8, pp. 2017-2023, 2007.

- [22] K. A. A. Makinwa, "Smart Temperature Sensor Survey," [Online]. Available: http://ei.ewi.tudelft.nl/docs/TSensor\_survey.xls

- [23] "TMP102 Data Sheet," Texas Instruments Inc., Oct. 2008, <u>www.ti.com</u>.

- [24] "ADT 7301 Data Sheet," Analog Devices Inc., Aug. 2004, www.analog.com.

- [25] P. Turkes, "An ion-implanted resistor as thermal transient sensor for the determination of the thermal diffusivity in silicon," Physica Status Solidi A, vol. 75, no. 2, pp. 519-523, Feb. 1983.

- [26] M. Kashmiri, "Thermal-diffusivity-based frequency references in standard CMOS," Ph.D. dissertation, Faculty of EEMCS, Delft University of Technology, the Netherlands.

- [27] C. P. L. van Vroonhoven, D. d'Aquino and K. A. A. Makinwa "A thermal-diffusivity-based temperature sensor with an untrimmed inaccuracy of ±0.2°C (3σ) from -55 to 125°C," ISSCC, Digest of Technical Papers, pp. 314-315, Feb. 2010, San Francisco.

- [28] P. Chen et al. "A time-domain SAR smart temperature sensor with curvature compensation and a 3s inaccuracy of -0.4C to +0.6 cover a 0C to 90C range," IEEE J. Solid-State Circuits, vol. 45, no. 3, pp. 600-609, Mar. 2010.

- [29] C.-K. Wu et al., "A 80kS/s 36µW resistor-based temperature sensor using BGR-free SAR ADC with a unevenly-weighted resistor string in 0.18µm CMOS," in Proc. Digest of Technical Papers VLSI Circuits 2011 Symp., pp. 222-223.

- [30] D. Ruffieux, F. Krummenacher, A. Pezous and G. Spinola-Durante, "Silicon resonator based 3.2μW real time clock with ±10 ppm frequency accuracy," IEEE J. Solid-State Circuits, vol. 45, no. 1, pp.224-234, 2010.

- [31] S. Heydari, "Thermal-diffusivity-based temperature sensor for microprocessors," M.Sc. dissertation, Faculty of EEMCS, Delft University of Technology, the Netherlands.

# **2** Temperature Sensing Principle

# 2.1 Introduction

As previously discussed, than BJT-based temperature sensors, resistor-based temperature sensors are potentially more energy-efficient. In addition, an inaccuracy comparable with their BJT-based counterparts can be achieved by taking advantage of the multi-point trimming already used in the manufacture of MEMS frequency references [1-4].

As found in the literature and in a commercially available product, resistor-based temperature sensors have been used for MEMS resonator temperature compensation [1-7]. In this chapter some of the already existing readout principles, such as the use of RC oscillators [2] and an auto-balanced RC network [1], will be briefly described. Following that, a new approach based on measuring the temperature-dependent phase shift of an RC filter, called the phase-domain temperature sensing principle, will be presented [7]. This phase-shift can then be digitized by means of a phase-domain sigma-delta modulator (PDSDM) [8, 9]. This chapter continues with the requirements and design considerations related to the sensor's frontend. In the following chapter the requirements of the PDSDM for interfacing the RC filter will be discussed. Furthermore, the circuit implementation and considerations will be elaborated.

# 2.2 Existing Resistor-Based Temperature Sensors

The temperature information associated with a resistor's temperature-dependency can be extracted via different signals: voltage, current, phase, frequency, etc. As a result, widely different readout topologies can be used to extract this information. In the following some of the already existing temperature sensing methods used for MEMS resonator compensation is elaborated briefly.

# 2.2.1 Temperature-Dependent RC Oscillator

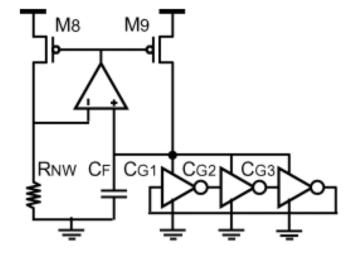

One way to read out a resistor is to bias it at a well-defined voltage and use the resulting temperature-dependent current to drive an oscillator [2]. Figure 2.1 shows a system-level implementation of this approach. This circuit consists of a temperature-dependent resistor  $R_{NW}$ , an operational transconductance amplifier (OTA), and an inverter-based ring-oscillator with an odd number of stages *i* and a total gate capacitance  $C_G = \sum C_{G,i}$ . The temperature dependent current flowing through the ring oscillator changes its output frequency. The dynamic equation which relates the current and frequency in the ring-oscillator can be expressed as follows [10]:

$$I = f \cdot C_G \cdot V, \tag{2.1}$$

Where *I* is the current flowing through the ring-oscillator,  $C_G$  is the gate capacitance, *V* is the supply voltage, and finally *f* is the logic's operational frequency. By using Ohm's law together with Eqn. 2.1, it can be shown that the oscillator's operational frequency will be proportional to  $\frac{1}{R_{NW}}$ .  $C_G$ , which in turn is a temperature dependent frequency [2].

It should be noted that the output frequency of a ring-oscillator is also supply-dependent [11]. This problem is mitigated by driving the inverters with a current source and also using a decoupling capacitor  $C_F$  to filter out high-frequency supply noise [2, 11-12]. In this design, the oscillator's phase-noise is dominated by the flicker-noise of the current sources and the opamp [11] which degrades the potentially high resolution achievable by using a resistor. This temperature sensor, after a one point trim, achieves  $\pm 3^{\circ}$ C inaccuracy over a temperature range of 0°C to 100°C. It also achieves a resolution of 40mK in a 7.5msec conversion time while drawing 30µA from a 1V supply voltage, resulting a resolution-FoM of 36pJ°K<sup>2</sup> [2]. However, this performance is still two orders of magnitude worse than the resistor's ultimate energy-efficiency.

Figure 2.1. Temperature sensing principle using the RC ring-oscillator [2].

Figure 2.2. Auto-balanced RC network readout principle [1].

# 2.2.2 Auto-Balanced RC-Network

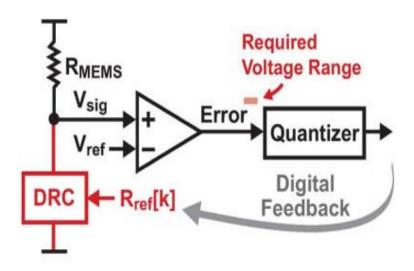

Another way of reading out a resistor is to embed the resistor in an auto-balancing voltage divider. Fig. 2.2 shows a system-level implementation of this approach [1]. It consists of a voltage divider, followed by an amplifier, and then a quantizer which digitally balances the reference impedance which is a part of the voltage divider. The voltage divider consists of a temperature dependent MEMS-resistor  $R_{MEMS}$  (0.3%/K) and a tuneable temperature independent reference impedance (implemented by stable capacitors over temperature). The voltage divider's output is then compared to a reference voltage by the following amplifier. The amplified error is then applied to a quantizer whose output will be fed back to tune the reference impedance. The task of the auto-balancing loop is to make the amplifier's output error zero. It is noticeable that the temperature-to-digital converter's (TDC) noise at low frequencies is dominated by the amplifier's flicker-noise, although windowed chopping technique is used. Whereas at high frequencies, the quantization noise associated with the quantizer is dominated. This readout technique achieves an energy-efficiency of 13  $pJ^{\circ}K^{2}$ , and 0.1mK resolution in a 100msec conversion time while the resolution of the sensing element is  $16\mu$ K. Moreover, after 6 point trim, this approach achieves  $\pm 0.02^{\circ}$ C inaccuracy over a -40°C to 85°C temperature range [1].

# 2.3 Phase-Domain Temperature-Sensing Principle

A digital temperature measurement requires a temperature-dependent signal and a temperature-independent signal as reference [13]. However, there is no accurate reference resistor in CMOS technology. Fortunately, in the context of MEMS frequency references a well-defined frequency is available [1-4]. So a well-defined SC resistor can be made, as discussed above. Alternatively, by translating the desired temperature-dependent signal into the time-domain, this frequency can be directly used as the desired reference signal [7].

One way of generating a temperature-dependent signal in time-domain is to exploit the fact that the phase-shift of an RC-filter is temperature dependent. So by driving an RC-filter at a fixed frequency the required temperature-dependent phase shift can be extracted. Since

metal-insulator-metal (MIM) capacitors and/or fringe capacitors are comparatively quite stable over temperature, the filter's phase shift will then be mainly a function of the resistor's temperature dependency. A point to be noted is that the RC-filter can be driven by a square-wave signal, which can be readily generated by digital circuits.

In the following sections, first, the way that an RC filter's phase-shift can be extracted will be elaborated. Then, since a high resolution temperature sensor is targeted, noise sources associated with the phase-domain temperature sensing principle are mentioned. The rest of this chapter is mainly devoted to the design and choice of the desired filter which converts the temperature information into the phase-domain.

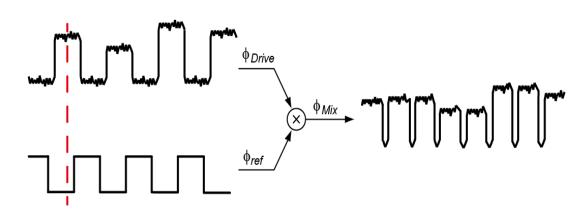

# 2.3.1 Phase-Extraction Methodology

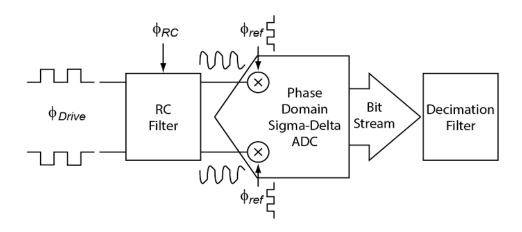

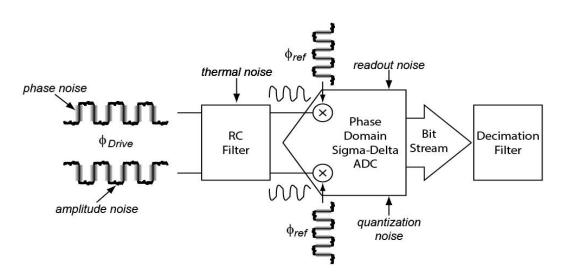

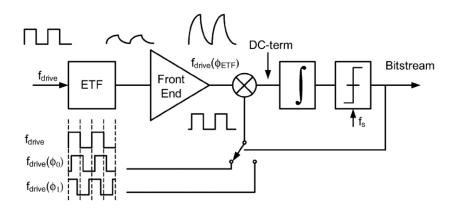

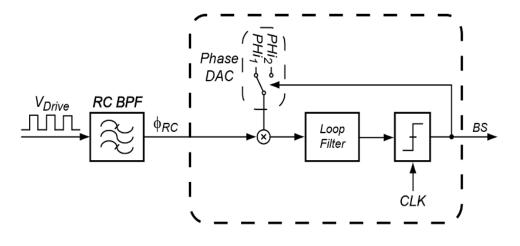

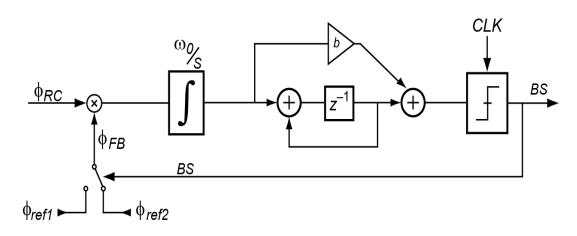

In order to extract the temperature-dependent phase shift associated with the RC-filter, phase demodulation can be employed [8-9]. This involves mixing the filter's output with a signal with the same frequency as the filter's driving signal but with a known phase. The mixer outputs an AC signal which is superimposed on a DC signal (see Eqn. 2.6). The mixer could be incorporated into a phase domain sigma-delta modulator (PDSDM) which then digitizes the phase-shift associated with the RC-filter [8, 9]. Figure 2.3 shows a system level implementation of a temperature sensor in the phase domain. A mathematical analysis of this system is described below.

Considering only the main tone of the filter's square-wave driving signal and assuming a phase shift of zero, the input to the RC filter can be expressed as:

$Signal_{drive} = A \times \cos(2\pi f + 0^{\circ}).$ (2.2)

The RC-filter's output then can be derived as:

$$Signal_{RC,Out} = A \times |TF_{RC}| \cos(2\pi f + \varphi_{RC}).$$

(2.3)

The mixing signal can be modelled by a cosine function, whose phase shift is defined relative to the driving signal:

$Signal_{Mixing} = B \times \cos(2\pi f + \varphi_{Mix}). \tag{2.4}$

The mixed signal can then be calculated by using Eqn. 2.5:

$$Signal_{Mixer-out} = Signal_{Mixing} \times Signal_{RC-Out},$$

(2.5)

Substituting Eqns. 2.3 and 2.4 into Eqn. 2.5 results in:

$$\text{Signal}_{\text{Mixer-out}} = \frac{\text{AB}}{2} \times |\text{TF}_{\text{RC}}| [\cos(\varphi_{\text{RC}} - \varphi_{\text{Mix}}) + \cos(4\pi f + \varphi_{\text{Mix}} + \varphi_{\text{RC}})], \quad (2.6)$$

Where A is the amplitude of driving signal, B is the mixing signal's amplitude,  $|TF_{RC}|$  is the magnitude of the filter's transfer-function, f is the filter's driving frequency,  $\varphi_{RC}$  is the phase shift associated with the filter, and finally,  $\varphi_{Mix}$  is the phase shift of the mixing signal.

Figure 2.3. System level implementation of a smart temperature-sensor in the phasedomain.

### 2.3.1.2 Phase Extraction Linearity

In order to achieve the best accuracy, the temperature-to-phase mapping should be done in a linear manner, i.e. the mixer should be operated in its most linear region. From Eqn. 2.6, the DC signal bearing the temperature information is a cosine function, which can be linearized as follow if  $(\phi_{RC} - \phi_{Mix}) \sim 90$  degrees:

$$\text{Signal}_{\text{Mixer,DC}} = \frac{\text{AB}}{2} \times |\text{TF}_{\text{RC}}| \times (\phi_{\text{RC}} - \phi_{\text{Mix}}). \tag{2.7}$$

# 2.3.2 Noise Sources Employing the Phase-Domain Principle

The noise sources associated with the phase-domain temperature sensing technique can be classified as follows, (also see Fig. 2.4):

- 1) Thermal noise of the filter

- 2) Readout circuitry noise (thermal & flicker noise)

- 3) Amplitude noise of the filter's driving signal

- 4) Phase noise of the filter's driving signal

The first two noise sources introduce only thermal noise, while the readout circuitry also causes flicker noise. It should be noted that lowering thermal noise usually requires more power. In order to be energy-efficient, while neglecting the flicker noise, the thermal noise contribution of the filter and the PDSDM should be the same at the filter's driving frequency Furthermore, the thermal noise should be much higher than the amplitude and phase noise introduced by the filter's driving signal. The effect of these noise sources are briefly elaborated below.

The noise of the filter's driving signal's amplitude could result in a noisy digital output, and depending on the ADC's operation principle and bandwidth, the output referred noise can then be calculated. The effect of this noise source will be discussed further in the next chapter.

Figure 2.4. Noise sources associated with the phase-domain approach.

The phase noise of the MEMS frequency reference, ultimately limits the achievable resolution in the phase domain. The jitter performance of a state-of-the-art MEMS frequency reference is less than 1psec over a 20 kHz to 20MHz frequency range [1, 5]. This could be translated into a temperature-sensing resolution if the filter's phase-to-temperature sensitivity is known.

It should be mentioned that all the above discussions are based on the assumption that the quantization noise associated with the readout circuitry is much lower than the thermal noise of the whole system. This argument will be discussed in detail in the following chapter.

# 2.4 Considerations for the Filter's Implementation

While designing an RC-filter for temperature sensing application, several factors should be carefully considered, namely:

- 1) Phase-to-temperature sensitivity

- 2) Thermal noise of the filter

- 3) Amplitude of the driving signal

- 4) Phase-to-temperature linear-conversion

- 5) Filter's driving frequency

Below each of the aforementioned factors are introduced in detail:

With the purpose of making an energy efficient sensor, the most important factor to be considered is the sensor's phase-to-temperature sensitivity together with its noise; i.e. for a given noise floor, a higher temperature-sensitivity results in a higher signal-to-noise ratio (SNR). Phase-to-temperature sensitivity for three different types of filters, namely low-pass-filter (LPF), high-pass-filter (HPF), and band-pass-filter (BPF) will be discussed in this chapter.

While assuming the filter's thermal noise dominates all other noise-sources, the RC-filter phase-to-temperature sensitivity together with the filter's thermal-noise defines the sensor's

signal-to-noise ratio (SNR). To get the most resolution out of an RC-filter, while comparing sensitivity of different filters, the thermal-noise associated with each of them should also be considered. Moreover, the SNR associated with each of the aforementioned filters will be extracted.

From Eqn. 2.6, it can be concluded that the signal's change over temperature is proportional to the amplitude of the driving signal. Consequently, the higher the driving signal's amplitude, the better the achievable resolution will be. As a result, a rail-to-rail driving signal should be chosen.

Ideally, the temperature-to-phase mapping should be a linear function. However, the attenuation factor of an RC-filter causes high order systematic gain error. The effect of the non-linearity associated with the  $|TF_{RC}(T)|$  is shown in Eqn. 2.8:

$$Signal_{Mixer-out} = \frac{AB}{2} \times |TF_{RC}(T)| \times (\phi_{RC} - \phi_{Mix}).$$

(2.8)

While investigating the filter's structure, this non-linear gain error should be taken into account. The residual gain error, after the intended multi-point trimming, should be much lower than the targeted inaccuracy, in order to prevent the need for more trimming points. In the following sections, phase-to-temperature mapping is discussed for the previously mentioned filters.

In order to choose the driving frequency of the RC-filter there are numerous considerations which should be taken into account. Since a high resolution temperature sensor is targeted, the first consideration is the flicker noise associated with the readout circuitry which dominates the noise performance in DC measurements. However, there are some other considerations such as parasitic effects and voltage dependency which restricts the choice of the filter's driving frequency. These factors should be taken into account while choosing the filter's driving frequency. Finally, a general remark to be noted is that implementing an RC filter regardless of its type in a differential topology gives 0.5bit more resolution compared to its single-ended counterpart. This is because, while signal power is 4x larger, noise power is only 2x greater. In addition, differential systems are more robust to external noise sources, since the noise appears as common-mode noise that can be mitigated by the differential system's common-mode rejection property.

## 2.4.1 Low Pass Filter (LPF)

The transfer function and phase of a 1<sup>st</sup>-order low-pass filter in the frequency-domain is expressed by Eqns. 2.9 and 2.10, respectively:

$$TF(T,j\omega) = \frac{1}{1+R_{(T)}Cj\omega}$$

(2.9)

$$\varphi_{\text{RC}-\text{LP}}(\mathbf{T}, \mathbf{j}\omega) = -\tan^{-1}(\mathbf{R}_{(\text{T})}\mathbf{C}\omega), \qquad (2.10)$$

where  $R_{(T)}$  is the temperature dependent resistor and C is the implemented capacitor value. Resistor temperature dependency changes the filter's time constant over the temperature. This variation can be modelled as a change in driving frequency while the time

constant is fixed. From Eqn. 2.10 it can be seen that the phase shift is also a function of frequency. Thus, the optimum driving frequency to achieve the maximum phase shift can be calculated. To do so, Eqn. 2.11 expresses the phase derivative as a function of angular frequency:

$$\frac{\mathrm{d}(\varphi_{\mathrm{RC-LP}}(\mathrm{T},\omega))}{\mathrm{d}\omega} = -\frac{\mathrm{R}_{\mathrm{(T)}}\mathrm{C}}{1 + \left(\mathrm{R}_{\mathrm{(T)}}\mathrm{C}\omega\right)^2} \tag{2.11}$$

Equation 2.11 reveals that for  $\omega = \pm \infty$ , the phase change due to the frequency change is zero. Since Eqn. 2.11 is a 2<sup>nd</sup>-order function, it will have a maximum at which the second derivative becomes equal to zero:

$$\frac{d^{2}(\frac{-R_{(T)}C}{1+(R_{(T)}C\omega)^{2}})}{d\omega} = 0 \rightarrow \left(3R_{(T)}^{4}C^{4}\omega^{4} + 2R_{(T)}^{2}C^{2}\omega^{2} - 1\right) = 0 \rightarrow \omega = 1/R_{(T)}C.$$

(2.12)

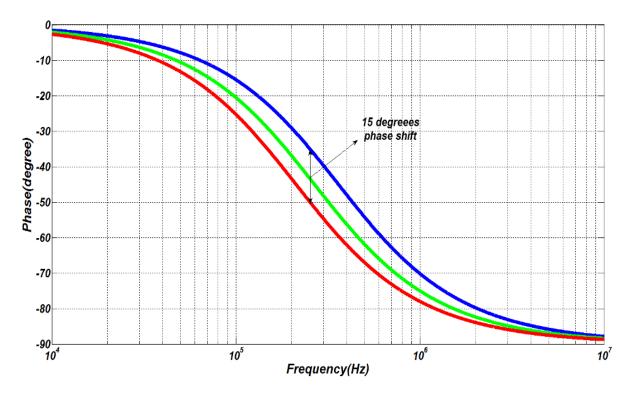

From Eqn. 2.12, it can be concluded that the second derivative becomes equal to zero at the filter's  $f_{.3dB}$  frequency which is equal to  $1/(2\pi . R_{(T)}. C)$ . Assuming a resistor with a temperature-coefficient of 0.3%/K, while driving the LPF at its  $f_{-3dB}$ , the filter's phase-shift will change by 15 degrees over the military temperature range. This is shown intuitively in Fig. 2.5.

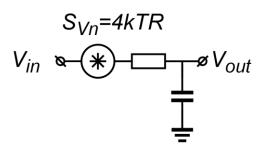

# **2.4.1.1** 1<sup>st</sup>-order LPF Noise

An LPF noise model is shown in Fig. 2.6 and its output-referred voltage noise power-spectral-density (PSD) is equal to:

$$S_{V_n,Out} = 4kTR \times |TF(T,j\omega)|^2, \qquad (2.13)$$

where k is Boltzmann's constant, T is temperature, R is resistor value, and finally  $|TF(T, j\omega)|$  is the magnitude of the filter's transfer function. Driving the filter at its  $f_{-3dB}$  frequency to get maximum phase shift, results in an attenuation of  $|TF(T, f_{-3db})| \approx 0.7$ . As a result, the filter's noise PSD at  $f_{-3dB}$  is:

$$S_{V_n,Out} = 4kTR \times \frac{1}{2},\tag{2.14}$$

#### 2.4.1.1 Temperature-to-Phase Conversion

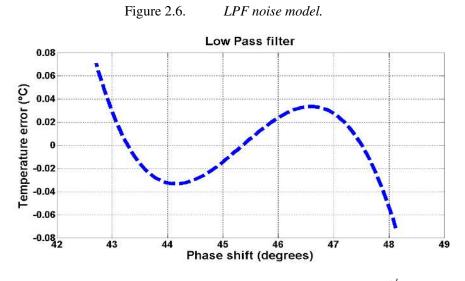

The temperature-error associated with the temperature-to-phase conversion, after 3-point trim, should be much lower than the targeted inaccuracy. While using an ideal resistor with a constant linear temperature coefficient of 0.15%/K simulation result shows that, for an LPF a temperature inaccuracy of about 0.07°C could be achieved, after a 2<sup>nd</sup>-order polynomial fit (3-point trim) and over the industrial temperature range. Figure 2.7 shows the simulated temperature error of an LPF, which can be seen that an LPF could not satisfy the desired inaccuracy.

Figure 2.5. *LPF phase change over the military temperature range modelled in the frequency domain.*

Figure 2.7. Non-linearity associated with a 1st-order LPF after a 2<sup>nd</sup>-order fitting

#### 2.4.2 High Pass Filter (HPF)

Another possible filter implementation is a high-pass-filter. The transfer function and the phase response of a 1<sup>st</sup>-order HPF in the frequency domain is expressed by Eqns. 2.15 and 2.16, respectively:

$$TF(T,j\omega) = \frac{R_{(T)}Cj\omega}{1+R_{(T)}Cj\omega}$$

(2.15)

$$\varphi_{\rm RC-LP}(T,j\omega) = \frac{\pi}{2} - \tan^{-1}(R_{(T)}C\omega),$$

(2.16)

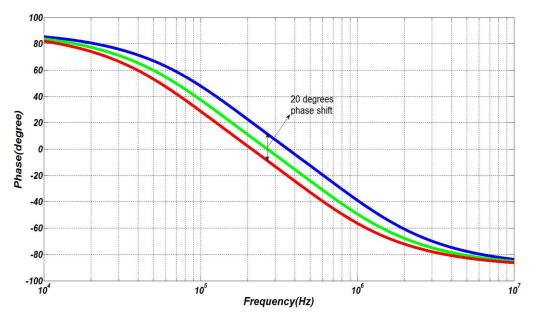

where  $R_{(T)}$  is the temperature-dependent resistor and C is the implemented capacitor. The phase-to-temperature sensitivity of an HPF will be exactly the same as an LPF under the previously determined condition for the LPF. As a result, assuming a resistor with a temperature-coefficient of 0.3%/°C, while driving the LPF at its  $f_{-3dB}$ , the filter's phase-shift will change by 15 degrees over the military temperature range. Moreover, for the same resistor value and filter's time constant, the noise PSD of an HPF at its  $f_{-3dB}$  will be the same as the LPF. Consequently, the only difference between the HPF and LPF could be their temperature-to-phase conversion which is elaborated below.

#### 2.4.2.1 Temperature-to-Phase Conversion

The temperature-error associated with the temperature-to-phase conversion, after 3-point trimming, should be much lower than the targeted inaccuracy of less than 0.1°C. While using an ideal resistor with a constant linear temperature coefficient of 0.15%/K, simulation result for an HPF shows a temperature inaccuracy of about 0.07°C, after a 2<sup>nd</sup>-order polynomial fit (3-point trim) and over the industrial temperature range, which is exactly the same as LPF.

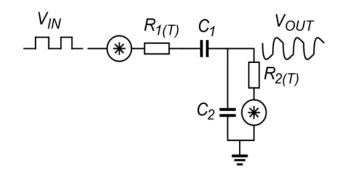

#### 2.4.3 Band Pass Filter

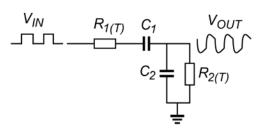

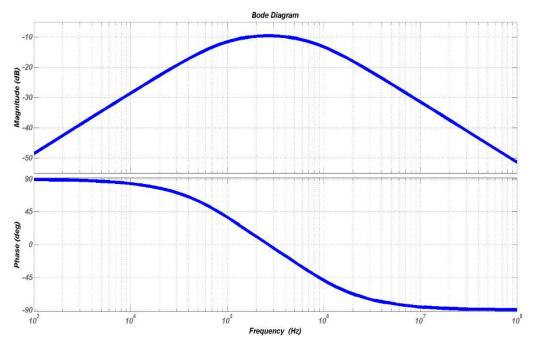

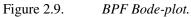

In order to have a better understanding of how a BPF behaves in the time domain and frequency domain, Fig. 2.9 shows a BPF's square-wave response in the time domain, and Fig. 2.10 shows a 2<sup>nd</sup>-order BPF's Bode-plot, which consists of an LPF and an HPF. The BPF to be used for phase-domain approach should have the low pass filter's cut-off frequency to be the same as the HPF's stop band frequency. In this way the phase falls down over frequency with a constant slope of 90 degrees per decade, without any flat band in between. This could be done by choosing  $R_{1(T)} = R_{2(T)}$  and  $C_1 = C_2$ .

#### 2.4.3.1 Phase-to-Temperature Sensitivity

The same analysis done for the previous filter types could be repeated, in order to find the optimum filter's driving frequency to get the maximum phase change over temperature. To do so, first the filter's transfer function and phase response should be extracted. Equations 2.19 and 2.20 show the transfer function and phase response of the 2<sup>nd</sup>-order BPF sketched in Fig. 2.8:

$$TF(T,j\omega) = \frac{R_{(T)}Cj\omega}{\left(1 - R_{(T)}^2 C^2 \omega^2\right) + 3R_{(T)}Cj\omega}$$

(2.19)

$$\varphi_{RC-BPF}(T,j\omega) = -tan^{-1} \frac{(R_{(T)}^2 C^2 \omega^2 - 1)}{3R_{(T)} C\omega}.$$

(2.20)

Assuming that resistors used in the  $2^{nd}$ -order BPF have the same temperature coefficient as the ones used in the LPF and HPF, then the resistor change results in a change of filter's time constant. Since phase shift is frequency dependent, there should be an optimum frequency which brings the most achievable phase shift. To calculate the optimum frequency, Eqn. 2.21 extracts the phase derivative over the frequency:

$$\frac{d(\varphi_{RC-BPF}(T,j\omega))}{d\omega} = -\frac{(3R_{(T)}C\omega)^2 \times (R_{(T)}^2C^2\omega^2 + 1)}{\omega \times [(3R_{(T)}C\omega)^2 + (R_{(T)}^2C^2\omega^2 - 1)^2]}.$$

(2.21)

Equation 2.21 reveals that for  $\omega = \pm \infty$  the phase variation caused by the frequency change is zero. Since Eqn. 2.21 is a 4<sup>th</sup>-order function, it will have a maximum, at which the second derivative becomes zero. Equation 2.22 shows the 2<sup>nd</sup> derivative of the BPF phase response.

$$\frac{d^2 \left(\frac{-R_{(T)}C}{1+(R_{(T)}C\omega)^2}\right)}{d\omega} = 0 \to \left(R_{(T)}^2 C^2 \omega^2 - 1\right) = 0 \to \omega = 1/R_{(T)}C.$$

(2.22)

From Eqn. 2.22 it can be seen that the phase change is maximum at filter's center frequency. Assuming a resistor with temperature coefficient of 0.3%/K (the same as for the LPF and HPF), and driving the BPF at its center frequency, 20 degrees phase shift could be extracted over the military temperature range. This is shown intuitively in Fig. 2.10.

# 2.4.3.1 2<sup>nd</sup>-order BPF Noise

A noise model for a BPF is shown in Fig. 2.11. Then, the filter's output-referred voltage noise PSD is equal to:

$$S_{V_n,Out} = 4kT \times R_{Total,Out}(j\omega, T), \qquad (2.23)$$

where  $R_{Total,Out}$  is the filter's output resistance. The filter's output resistance is frequency dependent. While driving the filter at its center frequency,  $R_{Total,Out}$  is equal to  $\frac{2R}{3}$ . It can be seen that the BPF noise PSD is 1.33x higher than that of the LPF or HPF (while resistor values are the same in both cases) while, the phase-to-temperature sensitivity of the BPF is about 1.33x greater. It can be concluded that the BPF's SNR is roughly the same as the LPF and HPF's SNR. Eqn. 2.24 mathematically proves that the SNR of a BPF in a certain bandwidth is about the same as that of its LPF (or HPF) counterpart.

$$\frac{SNR_{BPF}}{SNR_{HPF}} = \frac{\frac{10log\frac{(20 \text{ deg})^2}{4kTR \times \frac{2}{3} \times BW}}{10log\frac{(15 \text{ deg})^2}{4kTR \times \frac{1}{2} \times BW}} = 1.047,$$

(2.24)

Figure 2.8. BPF implementation and its square-wave response.

Figure 2.10. *BPF phase shift over the military temperature range*

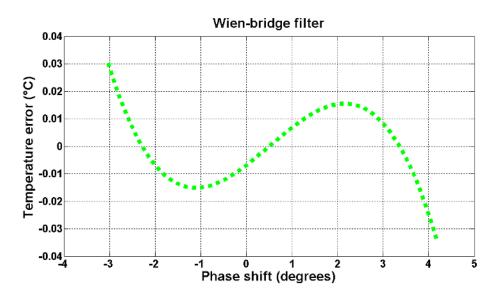

#### 2.4.3.2 Temperature-to-Phase Conversion

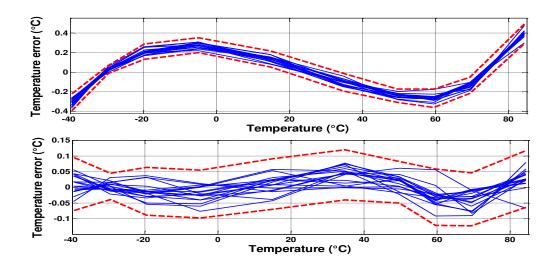

As discussed before, the temperature-error associated with the temperature-to-phase conversion should be much lower than the targeted inaccuracy of less than  $0.1^{\circ}$ C after a  $3^{nd}$ -order fitting. While using an ideal resistor with a constant linear temperature coefficient of 0.15%/K, simulation result for a BPF, show that the temperature inaccuracy after a  $2^{nd}$ -order polynomial fit (3-point trim) and over the industrial temperature range is about  $0.03^{\circ}$ C (see Fig 2.12) which is in line with the desired inaccuracy.

#### 2.4.4 Conclusion

Looking at Table 2.1, it can be seen that neither the LPF nor the HPF could satisfy the targeted inaccuracy due to their systematic high-order non-linear temperature-dependence. However, that of a BPF is about 0.03°C which is in line with the targeted specification. This is due to the fact that the combination of an LPF with a HPF results in less non-linear temperature dependent gain error, while brings more phase change. On top of this, the BPF achieves a slightly higher SNR, which makes the BPF the best candidate of these three types of filters.

Figure 2.11. *BPF noise model*

Figure 2.12. Non-linearity of a  $2^{nd}$ -order Wien-bridge after a  $2^{nd}$ -order fitting.

| Filter Type | Phase sensitivity<br>(Degree/°C) | Normalized thermal noise  | Systematic temperature<br>error (3 point-trim) | SNR (normalized to LPF) |

|-------------|----------------------------------|---------------------------|------------------------------------------------|-------------------------|

| LPF         | 83m                              | $4kTR \times \frac{1}{2}$ | 0.07°C                                         | 1                       |

| BPF         | 110m                             | $4kTR \times \frac{2}{3}$ | 0.03°C                                         | 1.047                   |

| HPF         | 83m                              | $4kTR \times \frac{1}{2}$ | 0.07°C                                         | 1                       |

Table 2.1.Characteristic of different type of filters

Figure 2.13. BPF implementation: current output (top); voltage output (bottom).

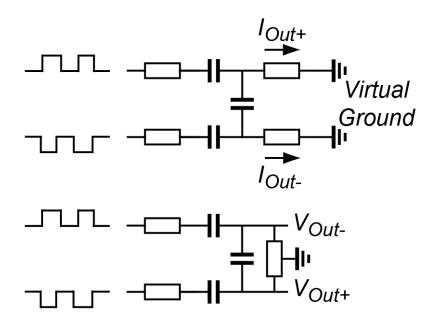

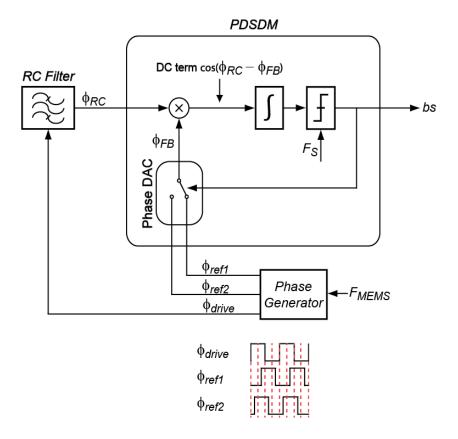

## 2.4.5 Implemented RC Filter

The BPF could be designed in such a way that its output can be in the voltage domain or in the current domain; both situations are shown in Fig. 2.13. The systematic temperatureerror associated with them, are both equal to 0.01°C after a 3<sup>rd</sup>-order fitting. However, while considering the implemented readout circuit characteristics, one of them should be chosen. In the fabricated design, the band pass filter outputs a temperature dependent current which this filter is called Wien-bridge RC filter. The reason for this choice is motivated in Chapter 3 while discussing the readout implementation.

## 2.4.6 Conclusion

So far, it is shown that the Wien-bridge RC filter performs much better than the HPF and LPF, both in terms of systematic temperature-error and SNR. On top of this, an argument of how the SNR is related to the value of the implemented resistor was elaborated. However, in order to design the filter, characteristics of different type of resistors, available in the design kit, should be investigated, in order to satisfy the previously mentioned requirements. Next section discusses the characteristics of available resistors.

## 2.5 Available Resistors in CMOS

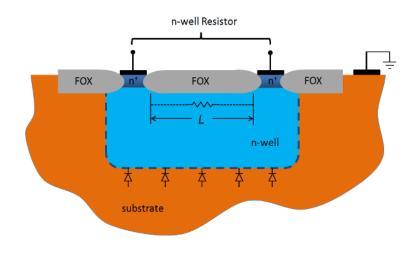

In order to make an energy efficient temperature sensor, the resistor's temperature coefficient must be as high as possible, so that a larger *SNR* could be extracted. In CMOS technology, there are different types of resistors available, each of which having different temperature coefficient. They also have different resistivities, parasitic capacitances, and voltage dependencies. Available resistors in CMOS could be mainly classified into 3 main branches:

- 1) Resistors with doped silicide

- 2) Resistors without doped silicide

- 3) N-well resistors

The resistors with doped silicide and the n-well resistors have the highest temperature coefficients. Although resistors with silicide have a high temperature coefficient, their unit sheet resistance is about two orders of magnitude lower than that of the other resistors. This characteristic makes the silicide resistors unsuitable, when large resistance is required.

Resistors without silicide have 2x lower temperature coefficient (except for the P<sup>+</sup> doped polysilicon resistor, which is 10x lower) than the other resistors, which results in 2x less resolution for the same resistor value. This drawback could be neglected by their relatively high resistivity when compared to silicide resistors. Thus, resistors without silicide (except P<sup>+</sup> poly-silicon) could be good candidates.

So far, the resistors without silicide (except  $P^+$  Polysilicon) and n-well resistors look suitable for the targeted application. However, still some other considerations should be accounted for when using them as sensors. These considerations could be classified as: nonlinear temperature dependence, voltage dependency, parasitic effects and area, which are all discussed in the following sections.

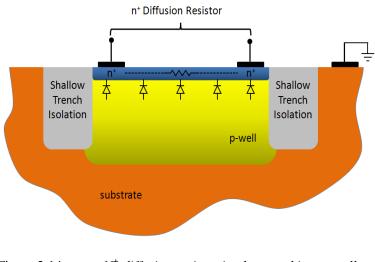

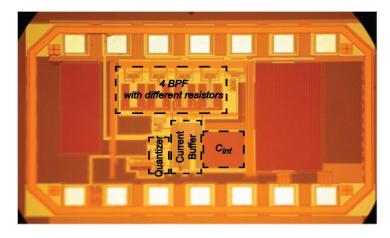

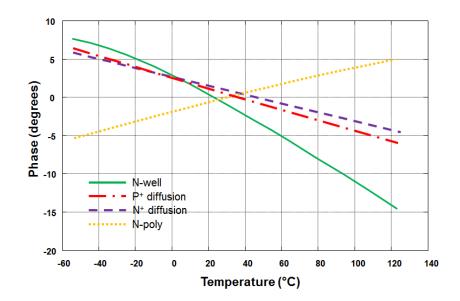

## 2.5.1 Non-Linear Temperature-Dependence

Since multi-point trim could be applied during trimming/calibration process, resistors' high-order non-linear behavior can be easily removed. However, in order to simulate and fairly judge the inaccuracy of different types of resistors and after a high-order fitting, resistors' high-order temperature coefficients are desired. Since these coefficients are not provided in the design kit, in the first design fabrication, four different RC filters using different types of resistors (N<sup>+</sup> diffusion, P<sup>+</sup> diffusion, n-poly and n-well under shallow trench isolation (STI)) are implemented.

## 2.5.2 Parasitic Effects

As previously discussed, the driving frequency of the filter should be higher than the flicker-noise corner frequency associated with the readout circuitry. This driving frequency could be translated into a certain time-constant for the implemented filter which is a function of the RC product. Parasitic effects should be considered since they could change the desired filter's transfer function. In the case of an  $N^+$  diffusion resistor, the presence of the junction capacitance associated with the reverse-biased diode formed by the  $N^+$  region and p-well

(shown in Fig. 2.14) results in a distributed RC network. To maintain the desired filter transfer function, the parasitic zeros and/or poles should preferably be separated by more than two orders of magnitude from the zeros and/or poles of desired filter. Consequently, the resistor and capacitor values should be chosen in such a way to satisfy this requirement.

## 2.5.3 Voltage Dependency

Resistors implemented in CMOS technology are voltage dependent. As a result the output of a resistor-based temperature sensor will also be voltage dependent. Moreover, the previously discussed junction parasitic capacitors are exponentially voltage-dependent. This problem can be tackled by biasing the resistors such that the junction diodes are deeply reverse-biasing, and thus have the minimum parasitic capacitance. In order to compete with other types of sensors, the targeted specification for the voltage dependency is less than  $1^{\circ}$ C/V.

## 2.5.4 Conclusion

As mentioned before, the promising resistors to be used as temperature sensing element, are  $N^+$  diffusion,  $P^+$  diffusion, n-poly and n-well. However, while implementing these resistors, the driving frequency of the filter should be chosen while considering temperature-sensing resolution and temperature-inaccuracy associated with the filter. As flicker noise dominates the noise performance in DC measurement, while assuming that chopping technique could be employed in order to mitigate it, a driving frequency higher than the flicker noise corner frequency is required. It should be mentioned that MOS devices in CMOS technology, typically have a flicker noise corner frequency about 100kHz. Moreover, the higher the driving frequency the faster the phase extraction loop converges. However, parasitic effects and voltage dependency associated with resistors, place an upper limit for the filter's driving frequency. Simulation results show that having a driving frequency higher than 250kHz, parasitic effects start to change the desired transfer function associated with the Wien-bridge filter.

Figure 2.14.  $N^+$  diffusion resistor implemented in a p-well

## 2.6 Temperature Sensing Resolution

As concluded above, a driving frequency of 250kHz is required for the Wien-bridge RC filter. The aforementioned driving frequency represents an RC time constant defining the centre frequency of the implemented Wien-bridge which is a function of RC product. However, in order to achieve a sub-mK resolution in a 5Hz bandwidth, resistor value should be chosen appropriately, while the temperature sensitivity of the implemented Wien-bridge is taken into account. A Wien-bridge exploiting the phase-domain temperature sensing approach is shown in Fig. 2.15.

#### 2.6.1 Temperature Sensitivity

In order to calculate the desired resistor value, the temperature sensitivity of the Wienbridge should be first extracted. From Eqn. 2.20, the phase shift of a Wien-bridge RC filter is a function of driving frequency together with the RC time constant. As the frequency is chosen to be 250kHz, the phase-to-temperature sensitivity is a function of the temperature dependency of the resistor, which can be calculated as follows:

$$\frac{d(\varphi_{RC-WB}(R_{(T)},\omega))}{d(R_{(T)})} \times \frac{d(R_{(T)})}{dT} = -\frac{(3R_{(T)}C\omega)^2 \times (R_{(T)}^2C^2\omega^2 + 1)}{R_{(T)} \times [(3R_{(T)}C\omega)^2 + (R_{(T)}^2C^2\omega^2 - 1)^2]} \times \frac{d(R_{(T)})}{dT}.$$

(2.25)

While substituting the temperature coefficient of the previously discussed resistors into Eqn. 2.25, phase-to-temperature sensitivity of the implemented Wien-bridge and for different resistors could be extracted. Table 2.2 shows the calculated phase-to-temperature sensitivity for different type of resistors. This phase-to-temperature sensitivity could be translated into a current-to-temperature sensitivity of the DC output current, by using Eqn. 2.26:

$$I_{\text{DC,WB}} = \frac{V}{2R_{(\text{T})}} \cdot |TF_{RC-WB}| \cdot \cos(90 - \varphi_{RC})$$

(2.26)

Where V is the amplitude of the driving signal equal to 1.8V,  $|TF_{RC-WB}|$  is the attenuation factor of the Wien-bridge at its center frequency which is equal to 1/3. Then, Eqn. 2.26 could be simplified as:

$$I_{\rm DC,WB} \cong \frac{300 \text{mV}}{\text{R}_{(T)}} \cdot \varphi_{RC-WB}(\text{T})$$

(2.27)

Assuming a first-order temperature dependence for the resistors,  $R_{(T)} = R_{(T_0)}(1 + \alpha \Delta T)$ , and using the previously calculated phase-to-temperature sensitivity, the current-to-temperature sensitivity could be calculated as follows:

$$S_{T}^{I_{DC,out}} = \frac{d(I_{DC,WB})}{d(T)} = 300 \text{mV} \cdot \frac{\frac{d(\varphi_{RC-WB}(R_{(T)},\omega)}{d(T)} \cdot R_{(T)} - \frac{d(R_{(T)})}{d(T)} \cdot \varphi_{RC-WB}(R_{(T)},\omega)}{(R_{(T)})^{2}}.$$

(2.28)

Figure 2.15. single ended Wien-bridge RC-filter exploiting phase domain temperature sensing approach

| Resistor type            | DC current-change $\left(\frac{mV/^{\circ}C}{R}\right)$ | Phase change<br>(mradian/°C) |  |

|--------------------------|---------------------------------------------------------|------------------------------|--|

| N-poly                   | 0.57                                                    | 55                           |  |

| P <sup>+</sup> diffusion | 0.74                                                    | 72                           |  |

| N <sup>+</sup> diffusion | 0.74                                                    | 72                           |  |

| N-well under STI         | 1.2                                                     | 116                          |  |

| N-well under OD          | 1.42                                                    | 138                          |  |

Table 2.2.BPF DC current-change for the implemented resistors.

Substituting the previously calculated phase-to-temperature sensitivity together with the temperature coefficient of the n-well resistor, the output current sensitivity could be calculated as follows:

$$S_T^{I_{DC,out}} = \frac{d(I_{DC,WB})}{d(T)} = \frac{1.2 \text{ mV/}^{\circ}\text{C}}{R}.$$

(2.28)

Then, the current-to-temperature sensitivity for different type of resistors is also shown in Table 2.2.

#### 2.6.1 BPF Noise Analysis

In order to calculate the resolution, the output referred current noise PSD of the Wienbridge at its centre frequency should be calculated, which determines noise floor at DC when mixing action takes place. Looking at Fig. 2.15, the noise of the resistor  $R_1$  will be low-pass filtered, while the noise of the resistor  $R_2$  will be high-pass filtered. Then, the filter's output-referred current noise PSD at its centre frequency and in a single-ended configuration could be calculated as follows:

$$S_{I_{n},Out} = \frac{1}{|TF_{WB,IN}|^{2}} \times \frac{4kTR_{1}}{R_{2}^{2}} + \frac{1}{|TF_{WB,Out}|^{2}} \times \frac{4kTR_{2}}{R_{2}^{2}} \xrightarrow{R=R_{1}=R_{2}}{\approx} \frac{4kT}{2R/3}.$$

(2.29)

Consequently, the integrated noise in a 5Hz bandwidth is as follows:

$$\sigma_{I_n,Out} = \sqrt{\frac{6kT}{R} \times 5Hz}.$$

(2.30)

#### 2.6.2 Temperature Sensing Resolution

The temperature sensing resolution, while the sensitivity of the n-well resistor is taken into account, could be calculated as follows:

$$\sigma_{\mathrm{T,WB}} = \frac{\sigma_{\mathrm{I_{n},Out}}}{S_{T}^{I_{DC,out}}} = \frac{\sqrt{\frac{6\mathrm{kT}}{\mathrm{R}} \times 5\mathrm{Hz}}}{\frac{1.2\mathrm{mV}/^{\circ}\mathrm{C}}{\mathrm{R}}} = \frac{\sqrt{6\mathrm{kT}\cdot\mathrm{R}\cdot5\mathrm{Hz}}}{1.2\mathrm{mV}/^{\circ}\mathrm{C}}.$$

(2.30)

In order to achieve a resolution of better than  $250\mu$ K in the 5Hz bandwidth and for the aforementioned n-well resistor, the resistor value should have a value lower than 150K $\Omega$ . Moreover, in order to satisfy the desired time constant, a capacitor value equal to 4pF is desired. This resolution represents an SNR of more than 120dB in the 5Hz bandwidth. In order to reach a signal-to-quantization-noise (SQNR) of higher than 120 dB, an appropriate PDSDM should be implemented, which is discussed in next chapters.

## 2.7 Conclusion

A band-pass-filter is selected in order to play the role of the temperature sensing element. The BPF brings a systematic non-linearity error of about 20mK after a 2nd-order fitting over the military temperature range which satisfies our targeted specification. A driving frequency of 250kHz has been chosen which defines the centre frequency of the Wien-bridge. In order to achieve sub-mk resolution while satisfying all the other considerations such as parasitic effects and voltage dependency, the Wien-bridge incorporates a 135k $\Omega$  resistor and a 4.4pF capacitor. The implemented Wien-bridge achieves a resolution of few hundreds  $\mu$ K in a bandwidth of a 5Hz, while using the aforementioned resistors available in CMOS technology. This signal can then be digitized by implementing a phase domain sigma-delta modulator. Next chapter, Chapter 3, first covers the system level design of the PDSDM. Afterwards, the circuit implementations and design considerations, in order to interface the Wien-bridge filter, will be further discussed.

#### References

- M. H. Perrott et al., "A temperature-to-digital converter for a MEMS-based programmable oscillator with < ±0.5-ppm frequency stability and < 1-ps integrated jitter," IEEE J. Solid-State Circuits, vol. 48, pp. 276-291, Dec. 2012.

- [2] D. Ruffieux, et al. "Silicon resonator based 3.2μW real time clock with ±10 ppm frequency accuracy," IEEE J. Solid-State Circuits, vol. 45, no. 1, pp.224-234, 2010.

- [3] R. Tabrizian, M. Pardo, and F. Ayazi, "A 27 MHz Temperature Compensated MEMS Oscillator with Sub-ppm Instability," IEEE International Conference on Micro Electro Mechanical Systems (MEMS 2012), Paris, France, Jan. 2012, pp. 23-26.

- [4] G. K. Ho, K. Sundaresan, S. Pourkamali and F. Ayazi "Micromechanical IBARs: Tunable high-Q resonators for temperature-compensated reference oscillators", J. MEMS, vol. 19, no. 3, pp.503 -515 2010

- [5] "SiT5003 Data Sheet," SiTime Corporation., <u>www.sitime.com</u>.

- [6] "SiT5301 Data Sheet," SiTime Corporation., <u>www.sitime.com</u>.

- [7] M. Shahmohammadi, K. Souri, K. A. A. Makinwa, "A Resistor-based Temperature sensor for MEMS Frequency References," to be presented at European solid state circuits conference (ESSCIRC) 2013

- [8] M. Kashmiri, "Thermal-diffusivity-based frequency references in standard CMOS," Ph.D. dissertation, Faculty of EEMCS, Delft University of Technology, the Netherlands.

- [9] C. P. L. van Vroonhoven, D. d'Aquino and K. A. A. Makinwa "A thermal-diffusivity-based temperature sensor with an untrimmed inaccuracy of ±0.2°C (3σ) from -55 to 125°C," ISSCC, Digest of Technical Papers, pp. 314-315, Feb. 2010, San Francisco

- [10] J. M. Rabaey, et al., "Digital integrated circuits", 2<sup>nd</sup> edition, Prentice Hall, 2003.

- [11] A. Abidi, "Phase Noise and Jitter in CMOS Ring Oscillator," IEEE J. Solid-State Circuits, vol. 41, no. 8, pp.1803-1816, 2006.

- [12] A. Hajimiri, et al. "A General Theory of Phase Noise in Electrical Oscillator," IEEE J. Solid-State Circuits, vol. 33, no. 2, pp.179-194, 1998.

- [13] M. A. P. Pertijs and J. H. Huijsing, "Precision Temperature Sensors in CMOS Technology", Springer, 2006.

# 3 First Test Chip

## **3.1** Introduction

An energy-efficient, high-resolution phase domain analog-to-digital converter (ADC) is required for the targeted application. A sigma-delta ADC is the best choice for high-resolution applications since it only makes modest demands on the accuracy of its analog components [1, 2]. Oversampling is used to spread the quantization noise over a wider bandwidth and also it shapes quantization noise outside the signal band [5].

The aim of the first test chip is to determine the inaccuracy associated with each type of resistors, while exploiting a phase domain sigma-delta modulator (PDSDM). In order to be able to achieve an inaccuracy of less than 0.1°C, the resolution of the implemented PDSDM should be much lower than the targeted inaccuracy [5]. On top of this, the non-linear temperature dependence of the PDSDM should be much lower than what resistors have.

In this chapter, some of the prior PDSDM implementations are first briefly discussed. Then, the PDSDM implementation in order to satisfy the aforementioned requirements, together with the system level considerations is elaborated. In the following, the circuit level implementation of the first test chip will be presented. This chapter will be concluded with briefly discussing the weaknesses and possible improvement points, which will be then dealt with in more detail in next chapter.

## **3.2 Prior PDSDM Implementations**

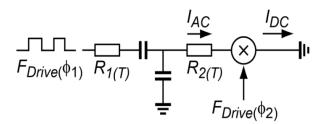

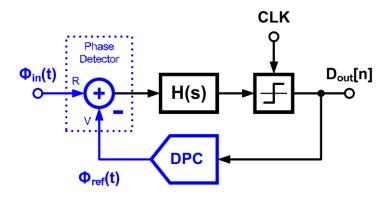

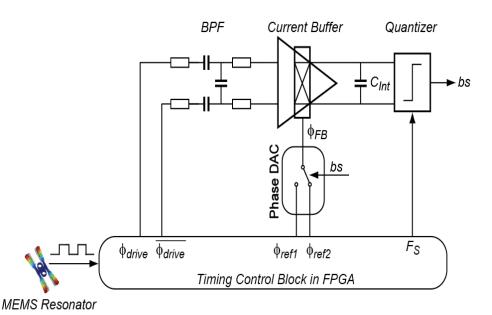

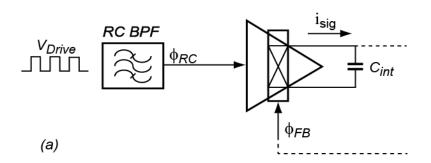

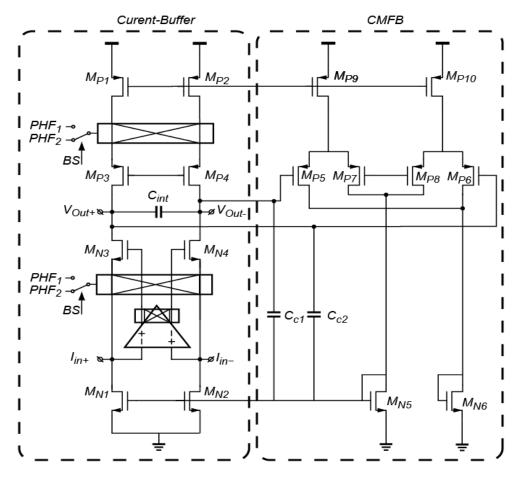

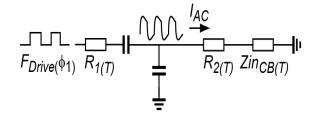

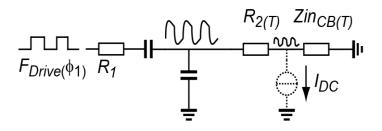

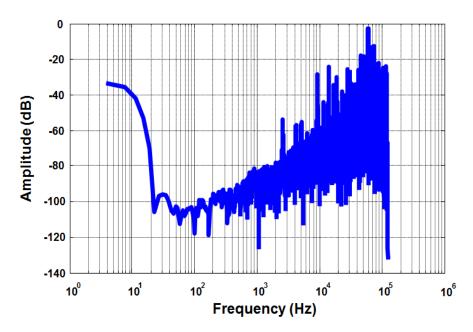

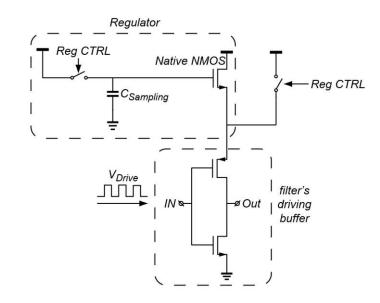

A 1<sup>st</sup>-order continuous-time (CT) PDSDM incorporating a synchronous chopper demodulator which extracts the input phase signal is presented in [2]. The aim of this design was to extract the phase shift associated with an electro-thermal filter (ETF). The PDSDM incorporates a passive  $G_m$ -C integrator which constitutes an ADC (see Fig. 3.1) with a thermal noise floor of lower than -80dB while burning about130µA from a 5V supply.

Figure 3.1. *I<sup>st</sup>-order CT PDSDM incorporating Gm-C integrator* [2]

Figure 3.2. *Charge balancing scheme used in 2<sup>nd</sup>-order CT PDSDM [3]*