# An Improved Family of ZVS-PWM Active-Clamping DC-to-DC Converters

Cláudio Manoel C. Duarte, Member, IEEE, and Ivo Barbi, Senior Member, IEEE

Abstract—A new family of dc-to-dc converters featuring clamping action, PWM modulation and soft-switching (ZVS) in both active and passive switches, is proposed to overcome the limitations of clamped mode dc-to-dc converters. The new family of converters is generated and the new circuits are presented. As the resonant circuits absorb all parasitic reactances, including transistor output capacitance and diode junction capacitance, these converters are suitable for high-frequency operation.

Principle of operation, of Boost converter, theoretical analysis, simulation and experimental results are presented, taken from a laboratory prototype rated at 1600 W, input voltage of 300 V, output voltage of 400 V, and operating at 100 kHz. The measured efficiency at full load was 98%.

Index Terms—Active-clamping, dc-to-dc converters, soft-switching.

#### I. INTRODUCTION

THE objective of high frequency operation in dc-dc converters is the reduction of reactive components size and cost. As in any power application, high efficiency is essential, and hence the increasing of frequency can be problematic because of the direct dependence of switching losses on frequency. The use of soft-switching techniques [1], [2], ZVS and ZCS, is an attempt to substantially reduce switching losses, and hence attain high efficiency at increased frequency.

Different techniques has been proposed to operate dc-dc converters in high frequency [3]–[7]. The active clamping technique [8], [9] has the advantages of PWM modulation, soft-commutation (ZVS) on main switches and low voltage stresses due to the clamping action. Besides operating at constant frequency and with reduced commutation losses there is no significant increasing on circulating reactive energy that would cause large conduction losses.

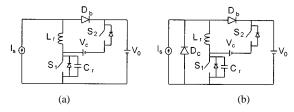

The parasitic ringings caused by the interaction of the junction capacitance of the rectifier, in the clamped mode Boost converter [Fig. 1(a)], [10], and the resonant inductor are eliminated by the inclusion of an auxiliary clamping diode [11], as shown in Fig. 1(b), limiting the voltage stress on the rectifier to the output voltage. It is important to note that to simplify the analysis, in all figures in the paper, the input filter inductance is assumed large enough to be considered as a current source  $(I_s)$  and the capacitor  $C_c$  is selected to have a large capacitance so that the voltage

Manuscript received December 22, 1999; revised July 25, 2001. Recommended by Associate Editor J. Oian.

C. M. C. Duarte is with the Catholic University of Pelotas, Pelotas 96010-000, Brazil (e-mail: cmcd@atlas.ucpel.tche.br).

I. Barbi is with the INEP, Power Electronics Institute, Federal University of Santa Catarina, Florianópolis (SC) 88040-970, Brazil (e-mail: ivo@inep.ufsc.br).

Publisher Item Identifier S 0885-8993(02)02166-X.

Fig. 1. Clamped mode converters: (a) without diode  $D_{\rm c}$  and (b) with diode  $D_{\rm c}$ .

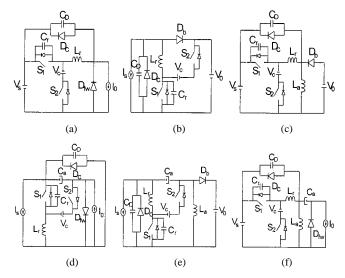

Fig. 2. New family of converters: (a) Buck, (b) Boost, (c) Buck-boost, (d) Cuk, (e) Sepic, and (f) Zeta.

$V_c$ , across the capacitor  $C_c$ , could be considered as a constant one. Although the voltage stress on the rectifier has been eliminated, by this approach, both  $D_b$  and  $D_c$  diodes still present hard switching commutation and the voltages across these devices still rise in a high dv/dt rate, which means compatibility electromagnetic problems and switching losses.

This paper presents an improved family of dc-dc converters featuring clamping action, PWM modulation and soft-switching (ZVS) in both active and passive switches. The inclusion of capacitor  $C_D$  and clamping diode  $D_c$ , in the Boost converter, as shown in Fig. 2(b), results in reduced voltage dv/dt and soft-switching conditions for all switching devices, including diodes  $D_c$  and  $D_b$ . Therefore all parasitic reactances are absorbed, including transistor output capacitance and diode junction capacitance, resulting in high efficiency at high frequency operation without significant increasing in voltage and current stresses on switches.

All basic dc-to-dc converters (Buck, Boost, Buck-boost, Cuk, Sepic, and Zeta) are generated from the same commutation cell

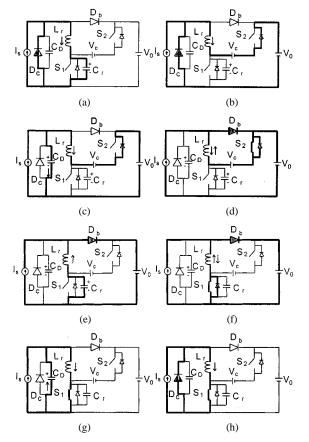

Fig. 3. Topological stages of Boost converter.

(one switch and one diode). Therefore, if the concept of commutation cell were applied to the proposed Boost converter, shown in Fig. 1(b) with addition of capacitor  $C_D$ , a new commutation cell can be found. This cell is formed by  $S_1, D_b$  or  $D_{fw}, S_2, V_c, C_r, L_r, D_c$ , and  $C_D$ , and from it basic dc-to-dc topologies are generated, the converters shown in Fig. 2. Thus, these six converters present the same behavior, in terms of commutation, and the same transfer energy principle when compared to the basic dc-to-dc converters.

#### II. OPERATION AND ANALYSIS OF THE BOOST CONVERTER

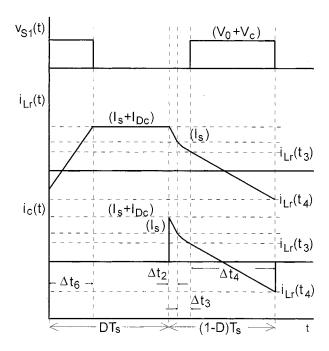

The eight topological stages and key waveforms of the proposed Boost converter, to one switching cycle, are shown in Figs. 3 and 4, respectively. Where  $i_{S_1}(t)$  represents current through  $S_1$ .

From Figs. 3 and 4 it can be seen that the two switches are switched in a complementary way and soft-switching is achieved for all switches and diodes. The main switch  $S_1$  is turned off at  $t = t_0$ , when the switching cycle starts.

#### A. Stage 1 $[t_0, t_1]$ ; Resonant Stage, Fig. 3(a)

Prior to  $t_0$ , the main switch  $S_1$  is on, the auxiliary switch is off and the clamping diode  $D_c$  is conducting. When  $S_1$  is turned off, at  $t = t_0$ , the first resonant stage has started, as shown in Fig. 3(a). The capacitor  $C_r$  is charged in a resonant way. When  $v_{C_r}(t)$  reaches  $V_c + V_0$ , the antiparallel diode of  $S_2$  starts conducting and this stage ends with voltage  $v_{C_r}(t)$ clamped at  $V_c + V_0$ .

Fig. 4. Theoretical waveforms of Boost converter.

This stage is described by

$$i_{L_r}(t) = i_{L_r}(t_0)\cos\omega_1 t \tag{1}$$

$$v_{C_D}(t) = 0 (2)$$

$$v_{C_r}(t) = \sqrt{\frac{L_r}{C_r}} i_{L_r}(t_0) \operatorname{sen} \omega_1 t$$

(3)

where

$$\omega_1 = \frac{1}{\sqrt{L_x C_x}} \tag{4}$$

$$\omega_1 \Delta t_1 = \operatorname{sen}^{-1} \left[ \frac{(V_0 + V_c)}{i_{L_r}(t_0) \sqrt{L_r/C_r}} \right]$$

(5)

where

$$\Delta t_1 = t_1 - t_0 \tag{6}$$

$$\Delta t_1 = t_1 - t_0 \tag{6}$$

$$i_{L_r}(t_1) = \sqrt{i_{L_r}^2(t_0) - \frac{(V_0 + V_c)^2}{L_r/C_r}}. \tag{7}$$

#### B. Stage 2 $[t_1, t_2]$ ; Linear Stage [Fig. 3(b)]

In this stage, the  $L_r$  current ramps down until reaches  $I_s$ , when the clamping diode  $D_c$  becomes reversibly biased and diode  $D_b$  starts conducting.

The state equations to this stage are

$$i_{L_r}(t) = -\frac{(V_c + V_0)}{L_r}t + i_{L_r}(t_1)$$

(8)

$$v_{C_D}(t) = 0 (9)$$

$$v_{C_r}(t) = (V_0 + V_c) (10)$$

and

$$\Delta t_2 = \frac{(i_{L_r}(t_1) - I_s)}{(V_c + V_0)} L_r \tag{11}$$

where

$$\Delta t_2 = t_2 - t_1 \tag{12}$$

$$i_{L_r}(t_2) = I_s. (13)$$

#### C. Stage 3 $[t_2, t_3]$ ; Resonant Stage [Fig. 3(c)]

When the clamping diode  $D_c$  ends conducting, the current through  $L_r$  decreases and the capacitor  $C_D$  is charged in a resonant way. When  $v_{C_D}(t)$  reaches  $V_0$ , the diode  $D_b$  becomes forward biased and starts conducting.

The equations that describe this stage are

$$i_{L_r}(t) = I_s - \frac{(V_c + V_0)}{\sqrt{L_r/C_D}} \sin \omega_2 t$$

(14)

$$v_{C_D}(t) = (V_c + V_0)(1 - \cos \omega_2 t)$$

(15)

$$v_{C_r}(t) = (V_c + V_0) (16)$$

where

$$\omega_2 = \frac{1}{\sqrt{L_r C_D}} \tag{17}$$

$$\omega_2 \Delta t_3 = \cos^{-1} \left[ \frac{V_c}{V_c + V_0} \right] \tag{18}$$

where

$$\Delta t_3 = t_3 - t_2 \tag{19}$$

$$i_{L_r}(t_3) = I_s - \frac{V_0\sqrt{1 + 2V_c/V_0}}{\sqrt{L_r/C_D}}.$$

(20)

### D. Stage 4 $[t_3, t_4]$ ; Linear Stage [Fig. 3(d)]

The  $L_r$  current ramps down, because  $C_c$  is considered as a constant voltage source, until it reaches zero, when it changes its direction and rises again. When the antiparallel diode of  $S_2$  is conducting, the auxiliary switch  $S_2$  should be switched on to

achieve a loss-less turn-on. This stage ends when  $S_2$  is turned off at  $t=t_4$ .

This stage is described by

$$i_{L_r}(t) = -\frac{V_c}{L_r}t + i_{L_r}(t_3)$$

(21)

3

$$v_{C_D}(t) = 0 (22)$$

$$v_{C_r}(t) = (V_0 + V_c) (23)$$

and

$$\Delta t_4 = (1 - D)T_s - (\Delta t_1 + \Delta t_2 + \Delta t_3 + \Delta t_5)$$

(24)

where

$$\Delta t_4 = t_4 - t_3$$

and  $\Delta t_5 = t_5 - t_4$  (25)

$$i_{L_r}(t_4) = -\frac{V_c}{L_r} \Delta t_4 + i_{L_r}(t_3).$$

(26)

E. Stage 5  $[t_4, t_5]$ ; Resonant Stage [Fig. 3(e)]

The voltage across  $C_r$  falls, due to the resonance between  $L_r$  and  $C_r$ , until it reaches zero at  $t=t_4$ . This stage ends when  $v_{C_r}(t)$  becomes null and the antiparallel diode of  $S_1$  begins conducting [see (27)–(31) at the bottom of the page].

F. Stage 6  $[t_5, t_6]$ ; Resonant Stage [Fig. 3(f)]

In stage 6,  $S_1$  is turned on without switching losses, in a ZVS way, because  $v_{C_r}(t)$  became null. The current through  $L_r$  changes its polarity and ramps up to reaches  $I_s$  at  $t=t_6$ . Then the diode  $D_b$  becomes reversibly biased and turns off.

The state equations are

$$i_{L_r}(t) = \frac{V_0}{L_r}t + i_{L_r}(t_5) \tag{32}$$

$$v_{C_D}(t) = V_0 \tag{33}$$

$$v_{C_r}(t) = 0 (34)$$

and

$$\Delta t_6 = \frac{(I_s - i_{L_r}(t_5))}{V_0} L_r \tag{35}$$

where

$$\Delta t_6 = t_6 - t_5 \tag{36}$$

$$i_{L_r}(t_6) = I_s. (37)$$

$$i_{L_r}(t) = -\frac{V_c}{\sqrt{L_r/C_r}} \sin \omega_1 t - i_{L_r}(t_4) \cos \omega_1 t \tag{27}$$

$$v_{C_D}(t) = V_0 \tag{28}$$

$$v_{C_r}(t) = V_0 + V_c \cos \omega_1 t - \sqrt{\frac{L_r}{C_r}} i_{L_r}(t_4) \sin \omega_1 t \tag{29}$$

and

$$\omega_1 \Delta t_5 = \cos^{-1} \left\{ \frac{V_0 V_c + \sqrt{\left[i_{L_r}^2(t_4) L_r/C_r\right] \cdot \left[V_c^2 - V_0^2 + i_{L_r}^2(t_4) L_r/C_r\right]}}{\left[V_c^2 + i_{L_r}^2(t_4) L_r/C_r\right]} \right\}$$

(30)

$$i_{L_r}(t_5) = -\frac{V_c}{\sqrt{L_r/C_r}} \sqrt{1 - \cos^2 \omega_1 \Delta t_5} - i_{L_r}(t_4) \cos \omega_1 \Delta t_5$$

(31)

#### G. Stage 7 [ $t_6$ , $t_7$ ]; Resonant Stage [Fig. 3(g)]

When diode  $D_b$  is turned off, capacitor  $C_D$  and inductor  $L_r$  begins resonate. The voltage across  $C_D$  reduces to zero and current through  $L_r$  rises. This stage ends when voltage across  $C_D$  becomes null and the clamping diode  $D_c$  becomes forward biased

$$i_{L_r}(t) = \frac{V_0}{\sqrt{L_r/C_D}} \sin \omega_2 t + I_s \cos \omega_2 t \tag{38}$$

$$v_{C_D}(t) = V_0 \cos \omega_2 t - \sqrt{L_r/C_D} I_s \sin \omega_2 t \tag{39}$$

$$v_{C_r}(t) = 0 (40)$$

and

$$\omega_2 \Delta t_7 = tg^{-1} \left[ \frac{V_0}{I_s \sqrt{L_r C_D}} \right] \tag{41}$$

$$\Delta t_7 = t_7 - t_6 \tag{42}$$

$$i_{L_r}(t_7) = i_{L_r}(t_0) = I_s \sqrt{(V_0^2 C_D / L_r I_s^2) + 1}.$$

(43)

#### H. Stage 8 $[t_7, t_8]$ ; Resonant Stage [Fig. 3(h)]

At  $t=t_7$ , the diode  $D_c$  is conducting and the current through  $L_r$  is clamped at  $I_s+I_{D_c}$ . The diode  $D_b$  is reversibly biased and power is not transferred to the load. This stage ends when  $S_1$  is turned off at the end of the switching cycle:

$$i_{L_r}(t) = i_{L_r}(t_7) = i_{L_r}(t_0)$$

(44)

$$v_{C_D}(t) = 0 (45)$$

$$v_{C_{-}}(t) = 0$$

(46)

and

$$\Delta t_8 = DT_s - (\Delta t_7 + \Delta t_6) \tag{47}$$

where

$$\Delta t_8 = t_8 - t_7 \tag{48}$$

$$i_{L_r}(t_8) = i_{L_r}(t_0).$$

(49)

#### III. CURRENT THROUGH DIODE $D_c$

The exceeding storage energy in  $L_r$  (responsible by the increasing of its current beyond  $I_s$ ) is equal to storage energy in capacitor  $C_D$  during one operation cycle  $(E_{C_D})$ , because during stage 7,  $C_D$  transfers its whole energy to  $L_r$ , resulting in decreasing of input voltage from  $V_s$  to zero and increasing of  $i_{L_r}(t)$  from  $I_s$  to  $I_s + I_{D_c}$ . Therefore, we have

$$E_{C_D}(t_6) = \frac{1}{2}C_D V_0^2 = \frac{1}{2}L_r I_{D_c}^2$$

(50)

$$I_{D_c} = \frac{V_0}{Z_{02}} \tag{51}$$

where

$$Z_{02} = \sqrt{\frac{L_r}{C_D}}. (52)$$

Thus, from (51), it may be noted that the peak value of current through  $D_c$  depends directly on  $C_D$ . Therefore, as greater is  $C_D$  greater will be this current and peak current through main switch  $S_1$ .

Fig. 5. Main simplified waveforms.

## IV. $D_c$ Voltage Conversion Ratio and $D_c$ Voltage Clamping Ratio

As we can see from the waveforms of Fig. 4 and mathematical expressions from Section II, the behavior of this new boost converter is quite different respect to boost-buck-boost converter presented in [10]. However, using suitable approximations, it is possible to derive useful relations which can greatly simplify the design procedure.

Thus, considering that the duration of intervals  $(t_1, t_2)$  and  $(t_4, t_5)$  are very small compared to switching cycle, as can be seen from Fig. 5, we have from the current balance on  $C_c$

$$\int_{0}^{\Delta t_{2}} \left[ -\frac{(V_{c} - V_{0})}{L_{r}} t + i_{L_{r}}(t_{1}) \right] dt + \int_{0}^{\Delta t_{3}} \left[ I_{s} - \frac{(V_{c} - V_{0})}{Z_{2}} \sin \omega_{2} t \right] dt + \int_{0}^{\Delta t_{4}} \left[ -\frac{V_{c}}{L_{r}} t + i_{L_{r}}(t_{3}) \right] dt = 0.$$

(53)

By assuming  $I_{L_1} = (I_s + I_{D_c})$  and

$$\Delta t_4 = (1 - D)T_s - \frac{1}{\omega_2} \cos^{-1} \left(\frac{\beta}{1 + \beta}\right) - 2\delta \tag{54}$$

where  $\delta$  represents the dead time and  $\beta = V_c/V_0$ , and solving (53), we have

$$I_{0n} = \frac{1}{\omega_2 T_s} \left[ \frac{1 + \frac{\beta}{2} (\omega_2 \Delta t_4)^2 + \sqrt{(1 + 2\beta)} \omega_2 \Delta t_4}{\frac{1}{(1+\beta)} + \cos^{-1} \left(\frac{\beta}{1+\beta}\right) + \omega_2 \Delta t_4} \right]$$

(55)

where

$$\Delta t_2 = \frac{1}{\omega_2} \frac{V_0}{(V_0 + V_c)} = \frac{1}{\omega_2 T_s} \frac{\beta}{(1+\beta)}$$

(56)

$$\Delta t_3 = \frac{1}{\omega_2} \cos^{-1} \left( \frac{\beta}{1+\beta} \right) \tag{57}$$

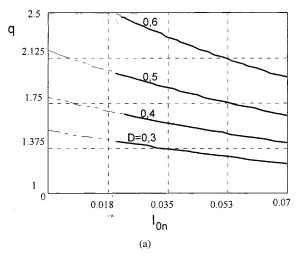

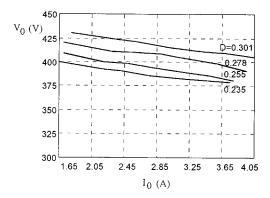

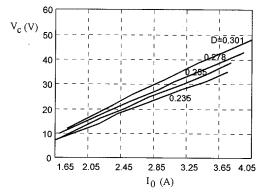

Fig. 6. (a) Voltage conversion ratio; (b) Voltage clamping ratio.

$$i_{Lrn}(t_4) = -\frac{\beta}{T_s} \Delta t_4 + i_{Lrn}(t_3)$$

(58)

$$I_{0n} = I_{sn} = \frac{L_r I_s}{V_0 T_s} = \frac{L_r I_0}{V_s T_s}.$$

(59)

As the average current through inductor  $L_r$  must be null in one switching cycle, we have

$$V_0 + V_c = V_s + V_{S_2} (60)$$

and, as the average voltage across  $S_2$  is

$$V_{S_2} = D(V_0 + V_c) (61)$$

so, equating (60) with (61) gives

$$q = \frac{V_0}{V_s} = \frac{1}{(1 - D)(1 + \beta)}. (62)$$

Note that  $\beta$  and  $V_c$  cannot be solved analytically and are  $I_{0n}$  dependent, and  $I_{0n}$  is the normalized load current. However, based on (55) and (62), design curves can be generated for design purposes.

A set of design curves showing the relationship between voltage conversion ratio q and normalized load current  $I_{0n}$ , for different values of duty cycle D ( $\omega_2 T_s = 48$ ) is shown in Fig. 6(a). It can be seen that for a given value of D, a larger  $I_{0n}$  gives a lower voltage conversion ratio. This behavior is similar to that of boost-buck-boost converter [10].

In Fig. 6(b) we can see a set of design curves showing the relationship between voltage clamping ratio  $\beta$  and normalized load current  $I_{0n}$ , for different values of duty cycle D. It can be seen that for a given value of D, a larger  $I_{0n}$  gives a larger voltage clamping ratio, consequently a larger  $V_c$ . In the same way, this behavior is similar to that of boost-buck-boost converter [10].

The mathematical model developed here holds while  $i_{L_r}(t_3)$  is greater then zero. Therefore, from (20), we have the following constraint:

$$I_{0n} \ge \frac{1}{\omega_2 T_s} \sqrt{1 + 2\beta}.\tag{63}$$

This constraint is shown in Fig. 6(a).

#### V. ZERO VOLTAGE CONDITIONS

In order to achieve zero voltage turn-on for  $S_1$ , there must be sufficient energy stored in the resonant inductor  $L_r$  to completely discharge the resonant capacitor  $C_r$  at  $t_5$ . Thus we have

$$\frac{1}{2}L_r i_{L_r}^2(t_4) \ge \frac{1}{2}C_r(V_c + V_0)^2 \tag{64}$$

then

$$I_{0n} \ge \frac{(\beta+1)}{\sqrt{\frac{C_D}{C_r}\omega_2 T_s}} + \frac{\sqrt{1+2\beta}}{\omega_2 T_s} + (1-D)\beta$$

$$-\frac{\beta}{\omega_2 T_s} \cos^{-1}\left(\frac{\beta}{\beta+1}\right) - 2\beta \frac{\delta}{T_s}. \quad (65)$$

Equation (65) gives another constraint on  $I_{0n}$ . Which means that there is a minimum value of load current in CCM where ZVS turn-on for  $S_1$  is kept, and it depends directly on  $L_r$ .

#### VI. EXPERIMENTAL RESULTS OF THE BOOST CONVERTER

The new Boost converter was implemented, with the following specifications: output power  $P_0=1600~\rm W$ ; input voltage  $V_s=300~\rm V$ ; output voltage  $V_0=400~\rm V$ ; switching frequency  $f_s=100~\rm kHz$ . The power stage consists of the following parameters:

—switches  $S_1$  and  $S_2$ : power MOSFET's IRFP460;—diode  $D_b$ : APT30D60;—diode  $D_c$ : APT15D100k—extern resonant capacitor  $C_D$ :1000 pF/1.6 kV—extern resonant capacitor  $C_{\rm rext}$ : 1000 pF/1.6 kV;—capacitor  $C_c$ : 1.0  $\mu$ F/200 V;—output filter  $C_f$ : 4 capacitors (100  $\mu$ F/250 V) in series and parallel ( $C_{f\, \rm total} = 100 \ \mu$ F);—resonant inductor  $L_r$ : 37  $\mu$ H, core (E-45/15)-Thornton;—input filter  $L_f$ : 600  $\mu$ H, core (E-55)

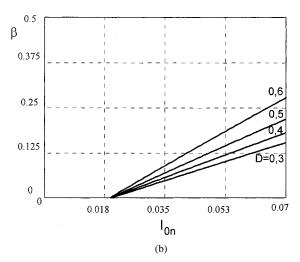

Experimentally obtained waveforms of the switches current and drain-to-source voltages and the resonant inductor current and voltage across the resonant capacitor are shown in Fig. 7.

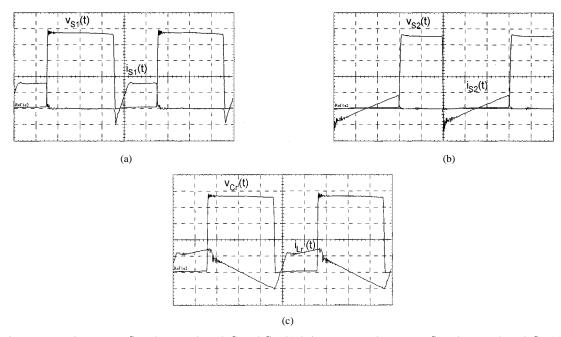

The voltage across diodes  $D_b$  and  $D_c$  and the current through those diodes are shown in Fig. 8. These waveforms agree with those predicted theoretically, and as it can be noted from the waveforms shown in Fig. 7, the main switches  $(S_1 \text{ and } S_2)$  present ZVS commutation with clamped voltages. From Fig. 7,

Fig. 7. (a) Drain-to-source voltage across  $S_1$  and current through  $S_1$  and  $C_r$ ; (b) drain-to-source voltage across  $S_2$  and current through  $S_2$ ; (c) voltage across  $C_r$  and current through  $L_r$ . (voltage: 100 V/div; current: 5 A/div; time scale: 2  $\mu$ s/div).

Fig. 8. (a) Voltage across  $D_b$  and current through  $D_b$  (voltage: 100 V/div; current: 5 A/div; time scale: 2  $\mu$ s/div); (b) voltage across  $D_c$  and current through  $D_c$  (voltage: 100 V/div; current: 2 A/div; time scale: 2  $\mu$ s/div).

Fig. 9. Output voltage with different load conditions and duty cycle.

Fig. 10. Voltage across the clamping capacitor with different load conditions and duty cycle.

it is possible to note that the diodes present ideal commutation conditions.

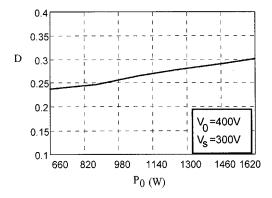

In Fig. 9, the output voltage as a function of output current is shown, for different duty cycles, and in Fig. 10, the voltage across clamping capacitor for the same conditions can be noted.

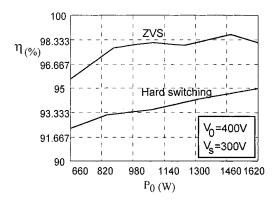

In Fig. 11 it is shown the efficiency measurement of the ZVS-PWM Active-Clamping Boost Converter as a function of

the output power, in comparison with the conventional Hard-switching PWM Boost converter's efficiency, at the same input and output data, and operating at the same switching frequency (100 kHz). The experimentally obtained efficiency from the new ZVS-PWM boost converter is equal to 98%, and from the conventional Hard-switching boost converter is equal

Fig. 11. Experimental efficiency curve with constant output and input voltage.

Fig. 12. Duty cycle variation to keep output voltage constant with different load conditions.

to 95%, for rated load. The duty cycle necessary to keep the output voltage at 400 V, is shown in Fig. 12.

#### VII. CONCLUSION

A new family of dc-to-dc converters featuring clamping action, PWM modulation and soft-switching (ZVS) in both active and passive switches, is proposed to overcome the limitations of clamped mode dc-to-dc converters. As the resonant circuits absorb all parasitic reactances, including transistor output capacitance and diode junction capacitance, these new converters operate with favorable switching conditions in all switching devices. Therefore, these converters are suitable for high-frequency operation.

#### REFERENCES

K. H. Liu and F. C. Lee, "Resonant switches—A unified approach to improve performance of switching converters," in *Proc. INTELEC*, 1984, pp. 344–351.

- [2] —, "Zero-voltage switching techniques in dc/dc converter circuits," in *Proc. PESC*, 1986, pp. 58–70.

- [3] K. W. Liu, R. Oruganti, and F. C. Lee, "Quasiresonant converters—Topologies and characteristics," *IEEE Trans. Power Electron.*, vol. PEL-2, pp. 62–71, Jan. 1987.

- [4] M. F. Tabisz and F. C. Lee, "Zero-voltage switching multi-resonant technique—A novel approach to improve performance of high-frequency quasiresonant converters," in *Proc. PESC*, 1988, pp. 9–17.

- [5] I. Barbi, J. C. Bolacell, D. C. Martins, and F. B. Libano, "Buck quasiresonant converter operating at constant frequency: Analysis, design and experimentation," *IEEE Trans. Power Electron.*, vol. 5, pp. 276–283, July 1990.

- [6] G. Hua, C. S. Leu, and F. C. Lee, "Novel zero-voltage-transition PWM converters," in *Proc. PESC*, 1992, pp. 55–61.

- [7] G. Hua, X. Yang, Y. Jiang, and F. C. Lee, "Novel zero-current-transition PWM converters," in *Proc. PESC*, 1993, pp. 538–544.

- [8] R. Watson, F. C. Lee, and G. C. Hua, "Utilization of an active-clamp circuit to achieve soft switching in flyback converters," in *Proc. PESC*, 1994, pp. 909–916.

- [9] C. M. C. Duarte and I. Barbi, "A family of ZVS-PWM active-clamping dc-to-dc converters: Synthesis, analysis, design, and experimentation," in *Proc. INTELEC*, 1995, pp. 502–509.

- [10] —, "A new family of ZVS-PWM active-clamping dc-to-dc boost converters: Synthesis, analysis, and experimentation," in *Proc. INTELEC*, 1996, pp. 305–312.

- [11] M. Jovanovic, "A technique for reducing rectifier reverse-recovery-related losses in high-voltage, high-power boost converters," in *Proc.* APEC, 1997, pp. 1000–1007.

Cláudio Manoel C. Duarte (M'98) was born in Pelotas, Rio Grande do Sul, Brazil, in 1960. He received the B.S. degree from the Catholic University of Pelotas, Brazil, in 1982 and the M.S. and Ph.D. degrees from the Federal University of Santa Catarina, Florianópolis, Brazil, in 1993 and 1997, respectively, all in electrical engineering.

Since August 1983, he has been Assistant Professor in the Engineering School, Catholic University of Pelotas. His research interests are in the areas of dc-dc converters and power factor

correction. He is the Vice-Rector of the Catholic University of Pelotas.

**Ivo Barbi** (SM'80) was born in Gaspar, Santa Catarina, Brazil in 1949. He received the B.S. and M.S. degrees in electrical engineering from the Federal University of Santa Catarina, Florianópolis, Brazil, in 1973 and 1976, respectively, and the Ph.D. degree from the Institute National Polytechnique de Toulouse, France, in 1979.

He founded The Brazilian Power Electronics Society and the Power Electronics Institute, Federal University of Santa Catarina. Currently, he is a Professor of the Power Electronics Institute.

Dr. Barbi has been an Associate Editor of the Power Converters Section, IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, since January 1992.