# An Improved Small-Signal Parameter-Extraction Algorithm for GaN HEMT Devices

Ronan G. Brady, Student Member, IEEE, Christopher H. Oxley, and Thomas J. Brazil, Fellow, IEEE

Abstract—A highly efficient and accurate extraction algorithm for the small-signal equivalent-circuit parameters of a GaN high electron-mobility transistor device is presented. Elements of the extrinsic equivalent-circuit topology are evaluated using a modified "cold field-effect transistor" approach whereby the undesirable need to forward bias the device's gate terminal is avoided. Intrinsic elements are determined based on a circuit topology, which identifies, for the first time, a time delay in the output conductance of GaN-based devices. The validity of the proposed algorithm has been thoroughly verified with excellent correlation between the measured and modeled S-parameters up to 50 GHz.

*Index Terms*—Gallium nitride (GaN), heterojunction field-effect transistor (HFET), high electron-mobility transistor (HEMT), parameter extraction, small-signal modeling.

# I. INTRODUCTION

ECENT publications on GaN-based high electron-mobility transistor (HEMT) technology have demonstrated superior performance capabilities over more traditional GaAs/ InP/SiGe-based counterparts [1]–[3]. The large bandgap energy  $(E_q)$ , typically of the order of 3.4 eV, results in higher breakdown fields ( $E_{\rm br} = 4$  MV/cm) permitting much larger voltage swing across the output of the device [4]. Fabrication of the device on a high thermal conductivity (k) substrate [5], e.g., SiC (k = 4.5 W/cm · K) will enable improved power-handling capabilities and increased thermal stability under adverse temperature operating conditions [6]. Furthermore, enhanced carrier-confinement processes, whereby both piezoelectric and spontaneous polarizations contribute to the 2-DEG layer formation, induce improved sheet carrier densities in excess of  $2 \times 10^{13}$  e/cm<sup>2</sup> [7] when compared with GaAs, typically  $2 \times$ 10<sup>12</sup> e/cm<sup>2</sup>. Monte Carlo simulations have also predicted saturation velocities of the order of  $v_{\rm sat} = 2.5 \times 10^7$  cm/s [8]. Taking all these factors into consideration, GaN-based transistor technologies have undoubtedly become an ideal candidate for high-power and high-frequency microwave circuitries for applications in many areas including aerospace, military, and wireless communications.

Over the last few decades, the development of an accurate device model has proven to be a vital step in the "first-pass"

C. H. Oxley is with the Computing Science and Engineering Department, De Monfort University, Leicester LE1 9BH, U.K. (e-mail: choxley@dmu.ac.uk).

Digital Object Identifier 10.1109/TMTT.2008.925212

design approach when designing monolithic microwave integrated circuits (MMICs). Models provide a valuable tool for predicting the large-signal performance of a device when simulated with complex modulation schemes like wideband code division multiple access (W-CDMA). An electrical equivalent circuit is one such device model. It provides a means of describing the electrical properties of the device-under-test (DUT) by linking elements of the equivalent circuit directly to the physical structure of the device. Complete characterization of a device's large-signal performance warrants an accurate evaluation of this underlying equivalent circuit under small-signal conditions.

During the last decade, a number of papers have presented different approaches for extracting the small-signal model (SSM) parameters of GaN-based transistors. An LDMOS modeling technique [9] has been proposed for the GaN heterostructure field-effect transistor (HFET) [10], whereby all eight parasitic elements are evaluated solely from the DUT in an off state. However, the present authors are of the view that, for some devices, extraction of the elements of the parasitic network using a single bias state can be problematic. In particular, the data required for series element extraction can be quite noisy and certain network parameters may exhibit an undesirable dependence with frequency. A 22-element distributed model proposed in [11] requires the estimation of initial element values for a bi-directional optimization technique. However, the process of acquiring these initial estimates involves the use of several empirical and algebraic assumptions, which may not suit all device structures. A low gate bias model extraction technique [12] has demonstrated an efficient SSM evaluation. All elements are determined without forward biasing the gate of the device. Nonetheless, the procedure can only be applied to devices where the equivalent drain-source capacitance  $C_{ds}$ is negligible. As will be highlighted in this paper,  $C_{ds}$  is, in general, not negligible and can be particularly high under certain cold field-effect transistor ("cold-FET") bias conditions. The existence of a significant  $C_{ds}$  effect has been addressed in a recent GaN "cold-FET" extraction approach [13]. In spite of this, an iterative procedure is required to determine a suitable forward biasing condition that is high enough to suppress the channel resistance, but low enough not to cause significant current flow through the gate terminal that could otherwise permanently degrade the future performance of the device. Furthermore, a certain level of modeling experience is required to identify the appropriate frequency ranges over which the Z-parameters can be used to evaluate the parasitic resistances.

Several publications [14], [15] have identified the existence of time delays in the output conductance element  $(g_{ds})$  of

Manuscript received January 18, 2008; revised April 16, 2008. First published June 13, 2008; last published July 9, 2008 (projected). This work was supported by the Science Foundation Ireland under the Principal Investigator Award at University College Dublin, Dublin, Ireland.

R. G. Brady and T. J. Brazil are with the School of Electrical, Electronic and Mechanical Engineering, University College Dublin, Dublin 4, Ireland (e-mail: ronan.brady@ucd.ie; tom.brazil@ucd.ie).

the standard small-signal equivalent circuit of FET devices. Without modifications to the conventional intrinsic circuit topology [16], this feature can be misinterpreted as bias-dependant drain and source access resistances. In extreme cases, these resistances may even appear negative [14], the plausibility of which is questionable from a physical point-of-view, while they can also create problems with implementation in simulators. The increased phase delay in  $g_{ds}$  at higher frequencies has been attributed to this phenomenon [17]. Based on this observation, an additional time dependence has been introduced into the  $g_{ds}$  element of a conventional equivalent circuit [18], [19]. In this study, similar phase delays in  $g_{ds}$  are identified for the first time in GaN-based HEMTs. Utilizing the circuit topology proposed in [18] issues regarding the physical consistency of the extracted access resistances are resolved.

A complete extraction procedure of all equivalent-circuit elements in a GaN HEMT device is presented in this paper. All extrinsic parasitic elements are evaluated under "cold-FET" conditions without forward biasing the gate terminal, as there is no requirement for the channel resistance to be small. Using a straightforward optimization procedure and utilizing a selection of well-established analytical expressions, values for the intrinsic equivalent-circuit elements can be accurately determined. The robustness and efficiency of this novel approach clearly distinguishes this study from previous extraction methodologies. This is demonstrated by the fact that elements are determined in a step-by-step noniterative procedure, which requires minimal intervention or experience on the part of the model developer. The validity of the proposed small-signal modeling methodology is discussed and the reliability of the evaluated SSM parameters is rigorously demonstrated.

# **II. DEVICE STRUCTURE**

The SSM has been determined for an AlGaN/GaN HEMT transistor fabricated at QinetiQ Ltd., Hampshire, U.K. It consists of a double cell "pi" structure with a 0.29- $\mu$ m gate length, as measured by focused ion beam cross sectioning. The gate metallization is a "T profile" in order to minimize the parasitic gate resistance. The total gatewidth is 100  $\mu$ m, consisting of two unit gatewidths of 50  $\mu$ m, and the gate-to-drain spacing is approximately 1.8  $\mu$ m. The layer structure consists of 28-nm AlGaN (26%),  $\approx$ 1 nm of aluminum nitride (AlN), and 1.2- $\mu$ m insulating GaN on a 4-H vanadium-doped silicon carbide (SiC) substrate. The AlN layer has the effect of increasing the mobility and is expected to reduce real space transfer into the AlGaN layer at high electric fields [20].

## **III. EXTRACTION PROCEDURE**

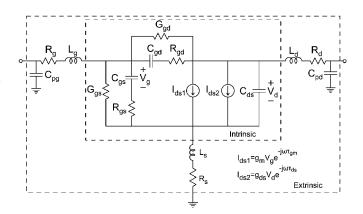

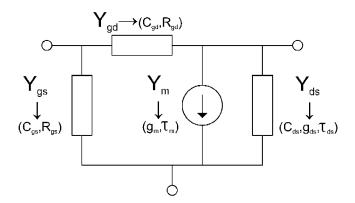

The complete small-signal circuit proposed for this device is shown in Fig. 1. Lumped components of the intrinsic topology represent the first-order linearization of nonlinear elements in the equivalent-circuit model including a pair of parallel current sources. Both of these are derived from a single nonlinear current source, the first representing a standard transconductance, whereas the second represents a generalized conductance

Fig. 1. Complete small-signal equivalent circuit for a GaN HEMT including intrinsic and extrinsic circuit topologies.

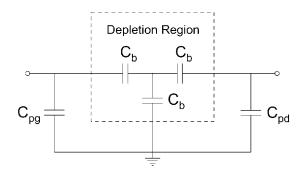

Fig. 2. Reduced equivalent-circuit topology for a "pinched-off" GaN HEMT.

with possible delay. Time delays, indicative of the observed frequency dependence in each of these conductances, are specified with reference to the intrinsic terminal voltages, as depicted in Fig. 1. The extrinsic parasitics include bias-independent elements  $R_g$ ,  $R_d$ ,  $R_s$ ,  $C_{pg}$ ,  $C_{pd}$ ,  $L_g$ ,  $L_d$ , and  $L_s$ . Assuming that the parasitics are evaluated and deembedded correctly, the remaining bias-dependant intrinsic elements can be evaluated using both the analytical expressions presented in [16] plus the straightforward fitting routine described in this paper. The following outlines the novel procedure for the correct extraction of the entire set of circuit elements.

## A. Parasitic Pad Capacitance Extraction

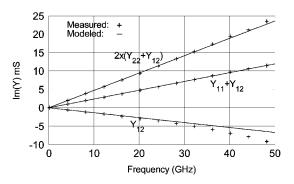

Parasitic gate and drain pad capacitances of GaN HEMT are generally extracted from conventional "cold-FET" techniques,  $V_{\rm DS} = 0.0$  V, using S-parameter measurements below pinched-off bias conditions, namely,  $V_{\rm GS} < V_p$ . Under these conditions, channel conductivity is negligible and the now passive device exhibits a purely capacitive behavior under low to medium frequencies [21]. For our GaN HEMT, under the pinchoff bias of  $V_{\rm GS} = -8.0$  V, the equivalent-circuit topology of Fig. 2 was deemed to be an adequate electrical representation of the device in this bias state [9]. The star-connected network of gate capacitance elements  $C_b$  exploits the symmetrical behavior of the depletion capacitance under the gate [22]. Linear regression fits to the various algebraic Y-parameter quantities,

Fig. 3. Measured and modeled Y-parameters (0.2–50 GHz) for a 2 × 50  $\mu$ m GaN HEMT under a "cold-FET" bias condition of  $V_{\rm GS}$  = -8.0 V and  $V_{\rm DS}$  = 0.0 V.

TABLE I

Extracted "Cold-FET" Pinched-Off Elements

|               | ,(IF) |

|---------------|-------|

| 16.63 16.18 6 | 4.03  |

as illustrated in Fig. 3, provide values for the individual elements according to the following mathematical expressions:

$$\operatorname{Im}(Y_{12}) = -\omega \frac{C_b}{3} \tag{1}$$

$$\operatorname{Im}(Y_{11} + Y_{12}) = \omega \left( C_{\text{pg}} + \frac{C_b}{3} \right) \tag{2}$$

$$Im(Y_{22} + Y_{12}) = \omega \left( C_{pd} + \frac{C_b}{3} \right).$$

(3)

As one can see, the highly linear behavior of the measured admittances justifies the reduced circuit topology of Fig. 2 over the lower frequency band. The extracted capacitances are presented in Table I.

It may be noted that a possible parasitic feedback capacitance between the gate and drain terminals has been omitted in the circuit of Fig. 2. In fact, based on geometrical data, estimates of this capacitance indicate values that are a factor of ten down on the pad capacitances, thereby permitting its omission from the equivalent circuit of Fig. 1, and subsequently, Fig. 2. This assumption will be further justified by the observed frequency independence of the extracted intrinsic parameters presented later in this paper. Furthermore, the authors acknowledge that the assumption of intrinsic symmetries, as inferred by Fig. 2, does not necessarily hold for all devices [23]. Certain device structures may also exhibit nonnegligible feedback capacitances [24]. A more generalized extraction approach would be to utilize open dummy structures, as demonstrated on the GaN HEMT in [12] and [13]. However, such structures were not available to the present authors, but techniques of this type should be used whenever these structures are available.

## B. Parasitic Inductance and Resistance Extraction

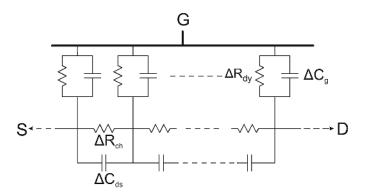

Having evaluated the parasitic pad capacitances, an accurate means of characterizing the series access regions of the device was sought. Under open channel conditions, a distributed

Fig. 4. Distributed gate network for a  $2 \times 50 \ \mu m$  GaN HEMT under open channel bias condition of  $V_{\rm GS} = 0.0$  V and  $V_{\rm DS} = 0.0$  V.

*RC* network has been proposed to characterize the electrical behavior of an FET device [25]. However, this model fails to account for any drain-source capacitance associated with the channel, arising from the separation of high electron concentration access regions at the drain and source [17]. Under low  $V_{\rm DS}$ bias conditions, this separation becomes small and, thus, a significant increase in  $C_{\rm ds}$  at  $V_{\rm DS} = 0.0$  V can be expected. Therefore, a more suitable distributed circuit topology is proposed, as illustrated in Fig. 4. Here,  $\Delta R_{\rm ch}$  and  $\Delta C_{\rm ds}$  represent the distributed elements of the drain-source channel resistance and capacitance, respectively, while  $\Delta C_g$  and  $\Delta R_{dy}$  account for the equivalent impedance under the Schottky barrier, as described by Dambrine *et al.* in [25]. From transmission line theory, the impedance matrix of this two-port network is given by

$$Z = \begin{bmatrix} \frac{Z_0}{\tanh(\gamma L)} & \frac{Z_0(\cosh(\gamma L) - 1)}{\sinh(\gamma L)} \\ \frac{Z_0(\cosh(\gamma L) - 1)}{\sinh(\gamma L)} & \frac{2Z_0(\cosh(\gamma L) - 1)}{\sinh(\gamma L)} \end{bmatrix}.$$

(4)

$Z_o$  represents the characteristic impedance and  $\gamma L$  is the product of the transmission line coefficient and gate length of the gate's equivalent transmission line network. These quantities can be determined from an analysis of the distributed equivalent circuit of Fig. 4, and are given by the following:

$$Z_0 = \sqrt{\frac{R_{\rm ch}//C_{\rm ds}}{G_{dy} + j\omega C_g}} \tag{5}$$

$$\gamma L = \sqrt{(R_{\rm ch}//C_{\rm ds})(G_{dy} + j\omega C_g)} \tag{6}$$

where  $G_{dy} = (R_{dy})^{-1}$ . Under microwave frequencies  $|(\gamma L)^2| \ll 1$  and, thus, the equivalent intrinsic impedance matrix simplifies to the following:

$$Z = \begin{bmatrix} \frac{\frac{1}{3}R_{\rm ch}}{1+j\omega C_{\rm ds}R_{\rm ch}} + \frac{R_{dy}}{1+j\omega C_{g}R_{dy}} & \frac{\frac{1}{2}R_{\rm ch}}{1+j\omega C_{\rm ds}R_{\rm ch}} \\ \frac{\frac{1}{2}R_{\rm ch}}{1+j\omega C_{\rm ds}R_{\rm ch}} & \frac{R_{\rm ch}}{1+j\omega C_{\rm ds}R_{\rm ch}} \end{bmatrix}_{(7)}$$

Deembedding the extracted pad capacitances from the equivalent circuit of Fig. 1, the complete Z-parameter representation of the measured device, under unbiased "cold-FET" conditions, becomes

$$Z_{11} = R_g + R_s + j\omega(L_g + L_s) + \frac{\frac{1}{3}R_{\rm ch}}{1 + j\omega C_{\rm ds}R_{\rm ch}} + \frac{R_{dy}}{\frac{1}{1 + j\omega C_{\rm ds}R_{\rm ch}}}$$

(8)

$$\frac{1}{2}R_{\rm ch}$$

$$Z_{12} = R_s + \frac{2}{1 + j\omega C_{\rm ds} R_{\rm ch}} + j\omega L_s \tag{9}$$

$$Z_{22} = R_d + R_s$$

$$+\frac{R_{\rm ch}}{1+j\omega C_{\rm ds}R_{\rm ch}}+j\omega (L_d+L_s).$$

(10)

Previous extraction methodologies [26], [27] that avoid the forward gate biasing techniques describe a similar set of equations for the DUT, though without the apparent complication of the drain-source capacitance  $C_{ds}$ , as shown in (8)–(10). Therefore, with reference to (8)–(10), the direct extraction approach for the remaining parasitic elements can no longer be applied here. However, the interaction of  $C_{ds}$  in parallel with the channel resistance introduces a favorable dispersive behavior into the measured series resistances. Therefore, despite increasing the complexity of the analysis,  $C_{ds}$  effectively permits the distinction of the channel resistance from the parasitic resistances, as can be mathematically inferred from (8)–(10). Hence, by incorporating this system of equations into a least squares (LS) fitting routine, one can evaluate unique and consistent values for the remaining parasitic elements. The general error function of such an LS fitting routine is given by

$$E_{xy}|_{\substack{x = 1, 2 \\ y = 1, 2}} = \sum_{i}^{N} \left\{ \left[ \operatorname{Re} \left( Z_{xy}^{\operatorname{sim}}(\omega_{i}) - Z_{xy}^{\operatorname{meas}}(\omega_{i}) \right) \right]^{2} + \left[ \operatorname{Im} \left( Z_{xy}^{\operatorname{sim}}(\omega_{i}) - Z_{xy}^{\operatorname{meas}}(\omega_{i}) \right) \right]^{2} \right\}.$$

(11)

The following algorithm now details each step of the proposed novel extraction procedure.

Step 1) To improve the efficiency of the LS fitting process, individual impedance elements of the  $Z_{22}$ -parameter can be estimated as follows:

$$R_{\rm ch} \approx \operatorname{Re}(Z_{22}|_{f_L} - Z_{22}|_{f_H}) \tag{12}$$

$$R_d + R_s \approx \operatorname{Re}(Z_{22}|_{f_H}) \tag{13}$$

$$C_{\rm ds} \approx \frac{1}{\omega_M R_{\rm ch}} \left( \frac{R_{\rm ch}}{{\rm Re}(Z_{22}|_{f_M} - Z_{22}|_{f_H})} - 1 \right)^{\frac{1}{2}}$$

(14)

$$L_d + L_s \approx \frac{1}{\omega_H} \operatorname{Im} \left( Z_{22} |_{f_H} - \frac{R_{\mathrm{ch}}}{1 + j\omega_H C_{\mathrm{ds}} R_{\mathrm{ch}}} \right) \quad (15)$$

where  $\omega = 2\pi f$  and quantities subscripted with L, M, and H denote parameters measured at the lowest, intermediate, and highest frequencies of 0.2, 25.0 and 50.0 GHz, respectively. The estimates given by (12)–(14) are based on an analysis of

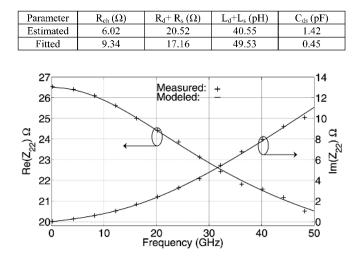

TABLE II EXTRACTED  $Z_{22}$ -Parameters

Fig. 5. Measured and modeled real and imaginary parts of the  $Z_{22}$ -parameter (0.2–50 GHz) for an unbiased "cold-FET" 2 × 50  $\mu$ m GaN HEMT.

the real parts of  $Z_{22}$ , which are dominated by the interaction of  $C_{\rm ds}$  with the channel resistances  $R_{\rm ch}$ over the entire measured frequency range. At the highest frequencies, both the drain inductance  $L_d$ and source inductances  $L_s$  begin to dominate the imaginary part of the measured series impedance and are appropriately estimated by (15). An LS fit of (10) to the measured complex  $Z_{22}$ -parameter over the measured frequency range reveals the optimum values of these estimated quantities. Table II outlines values for both the estimated and fitted quantities for this step. A comparison of the measured and modeled results of both the real and imaginary components of  $Z_{22}$  is given in Fig. 5. This graph also highlights the significant reduction in the measured series output resistance over frequency due to  $C_{\rm ds}$ , as described earlier. The fitted  $R_{\rm ch}$  and  $C_{\rm ds}$  values can now be fixed for the remainder of the extraction process.

Step 2) The source resistance  $R_s$  and source inductance dominate the real and imaginary parts of  $Z_{12}$  at the highest frequencies and can be estimated as follows:

$$R_s \approx \operatorname{Re}(Z_{12}|_{f_H}) \tag{16}$$

$$L_s \approx \frac{1}{\omega_H} \operatorname{Im} \left( Z_{12} |_{f_H} - \frac{\frac{1}{2} R_{\mathrm{ch}}}{1 + j \omega_H C_{\mathrm{ds}} R_{\mathrm{ch}}} \right).$$

(17)

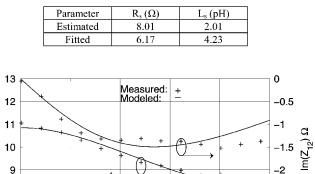

A similar LS fit of (9) to the measured complex  $Z_{12}$ -parameter reveals the final values of these quantities. The estimated and fitted values are given in Table III. Furthermore, a comparison of the measured and modeled  $Z_{12}$ -parameter for this step is shown in Fig. 6.

C

-2.5

-3

50

TABLE III EXTRACTED  $Z_{12}$ -Parameters

Re(Z<sub>12</sub>) Ω

8

7

0

10

Fig. 6. Measured and modeled real and imaginary parts of the  $Z_{12}$ -parameter (0.2–50 GHz) for an unbiased "cold-FET"  $2 \times 50 \,\mu$ m GaN HEMT.

Frequency (GHz)

30

40

20

Step 3) Finally, estimates of the equivalent impedance parameters of the  $Z_{11}$ -parameter are made as follows:

$$C_g \approx -\frac{1}{\omega_L} \operatorname{Im} \left( Z_{11} |_{f_L} - \frac{\frac{1}{3} R_{\mathrm{ch}}}{1 + j \omega_L C_{\mathrm{ds}} R_{\mathrm{ch}}} \right)^{-1}$$

(18)

$$R_{dy} \approx \frac{1}{(\omega_L C_g)^2} \operatorname{Re} \left( Z_{11} |_{f_L} - \frac{\frac{1}{3} R_{\mathrm{ch}}}{1 + j \omega_L C_{\mathrm{ds}} R_{\mathrm{ch}}} \right)^{-1}$$

(19)

$$R_g + R_s \approx \operatorname{Re}(Z_{11}|_{f_H}) \tag{20}$$

$$L_g + L_s \approx \frac{1}{\omega_H} \operatorname{Im} \left( \begin{array}{c} Z_{11} |_{f_H} - \frac{\frac{1}{3} R_{\mathrm{ch}}}{1 + j \omega_H C_{\mathrm{ds}} R_{\mathrm{ch}}} \\ - \frac{R_{dy}}{1 + j \omega_H C_g R_{dy}} \end{array} \right).$$

(21)

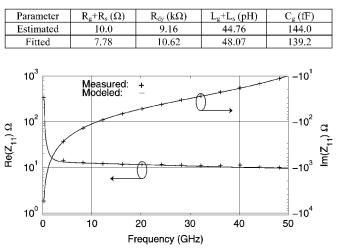

Under the lower frequencies, the complex impedances presented by the gate leakage resistance  $R_{dy}$ and gate capacitance  $C_q$  are prevalent. Using the fitted  $R_{\rm ch}$  and  $C_{\rm ds}$  values from Step 1) and rearranging (8), reasonable estimates of these intrinsic parameters are made according to (18) and (19). Series gate parasitics begin to dominate the measured impedances at the highest frequencies and are estimated according to (20) and (21). A final LS fit of the complex  $Z_{11}$ -parameter to (8) provide the optimum values for these quantities, the results of which are shown in Table IV. A graph of this fit is presented on a log scale in Fig. 7 to clearly highlight the outstanding correlation between the measured and modeled results over the measured frequency range.

TABLE IV EXTRACTED  $Z_{11}$ -Parameters

Fig. 7. Measured and modeled real and imaginary parts of the  $Z_{11}$ -parameter (0.2–50 GHz) for an unbiased "cold-FET"  $2 \times 50 \,\mu$ m GaN HEMT.

TABLE V EXTRACTED SERIES PARASITIC ELEMENTS

| L <sub>g</sub> (pH) | L <sub>d</sub> (pH) | L <sub>s</sub> (pH) | $R_{g}(\Omega)$ | $R_{d}\left(\Omega ight)$ | $R_{s}(\Omega)$ |

|---------------------|---------------------|---------------------|-----------------|---------------------------|-----------------|

| 43.85               | 45.30               | 4.23                | 1.60            | 10.98                     | 6.17            |

At this stage, all the data required for the complete characterization of the device's parasitic network has been obtained. Where necessary, values for each individual parasitic element can be determined by performing algebraic operations on the fitted data from Tables II-IV. Table V now outlines the final values for each individual parasitic element, which will be used to determine the measured intrinsic parameters of the device.

# C. "Hot-FET" Intrinsic Element Extraction

Values determined for the extrinsic elements can be deembedded from the measured data by a series of straightforward mathematical operations to reveal the measured intrinsic Y-parameters of the device [25]. Traditionally, equations described in [16] can be used to determine the remaining elements of the intrinsic circuit [26]-[28]. However, the introduction of the drain conductance delay parameter gives an overdetermined system of equations. This problem is depicted in the general equivalent circuit of Fig. 8, which is a simplified form of the intrinsic topology described in Fig. 1. Mathematically unique values can be extracted for a maximum of two intrinsic elements or parameters from each admittance quantity at each measured frequency. This is not so in the case of  $Y_{ds}$ , which is now described in terms of three parameters as follows:

$$Y_{\rm ds} = g_{\rm ds} \exp(-j\omega\tau_{\rm ds}) + j\omega C_{\rm ds}.$$

(22)

Therefore, a final fitting routine to (22) is required to evaluate the equivalent values of these parameters at each bias point.

Fig. 8. Generalized equivalent intrinsic topology of a GaN HEMT device showing the lumped complex admittance quantities in each limb and their associated equivalent-circuit parameters.

Fig. 9. Real and imaginary parts of the measured (+) and modeled (-) S-parameters (0.2–50 GHz) for  $2 \times 50 \,\mu$ m GaN HEMT at  $V_{\rm GS} = 0.0$  V and  $V_{\rm DS} = 0.0$  V.

Having outlined a detailed algorithm for extracting the SSM of a GaN HEMT, Section IV will now provide a thorough validation of this proposed approach.

#### **IV. RESULTS AND DISCUSSION**

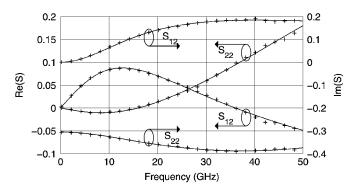

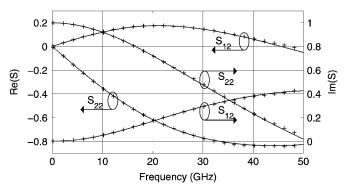

In Section III, the extraction algorithm for the extrinsic parasitics under "cold-FET" conditions was presented. To evaluate the accuracy of the extracted parasitic elements, Figs. 9 and 10 now compare a selection of the measured and modeled S-parameters of the device under both of these "cold-FET" bias conditions. Real and imaginary components of these quantities are plotted separately to highlight the excellent correlation between the measured and modeled results over the measured frequency range. These results provide a good indication of the accuracy of the extracted parasitic values thus far.

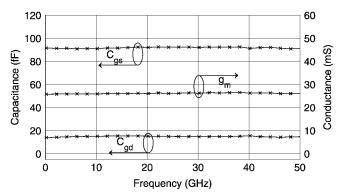

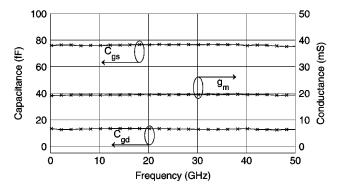

Deembedding all bias independent parasitic components from the measured data, the intrinsic elements were then determined under active multibias conditions. In the case where elements could be evaluated by direct analytical expressions, their unique values were determined over the entire measured frequency range. A selection of these elements extracted over frequency for two different bias points is shown in Figs. 11 and 12. Ignoring measurement errors, it is quite apparent that the extracted elements exhibit clear frequency independence over the measured frequency range. Similar results were observed for the majority of bias points across the bias plane. This result further validates both the chosen topology and the accuracy

Fig. 10. Real and imaginary parts of the measured (+) and modeled (-) S-parameters (0.2–50 GHz) for  $2 \times 50 \ \mu m$  GaN HEMT at  $V_{\rm GS} = -8.0$  V and  $V_{\rm DS} = 0.0$  V.

Fig. 11. Extracted intrinsic elements of  $C_{\rm gs},\,C_{\rm gd},\,{\rm and}\,g_m$  versus frequency (0.2–50 GHz) for a  $2\times50~\mu{\rm m}$  GaN HEMT at  $V_{\rm GS}=-0.6$  V and  $V_{\rm DS}=12.5~$  V.

Fig. 12. Extracted intrinsic elements of  $C_{\rm gs},\,C_{\rm gd},\,{\rm and}\,g_m$  versus frequency (0.2–50 GHz) for a  $2\times50~\mu{\rm m}$  GaN HEMT at  $V_{\rm GS}=-7.0$  V and  $V_{\rm DS}=20.0\,$  V.

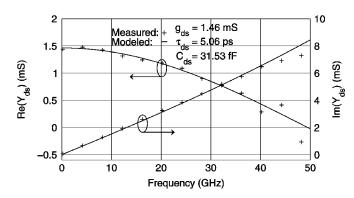

of the proposed extraction technique. The real and imaginary parts of  $Y_{\rm ds}$  for these bias points are also shown in Figs. 13 and 14, highlighting the appropriateness of the output conductance time delay approach.

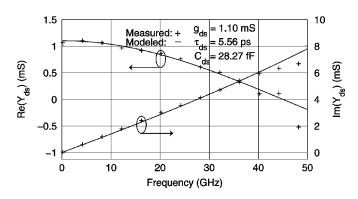

To verify the small-signal behavior of the model, the proposed circuit topology of Fig. 1 was simulated with the extracted values determined using this novel procedure for our GaN HEMT. Table VI outlines a selection of the extracted values for three different bias points over the range of  $V_{\rm GS}$  (-5-0 V). The ability of the model to accurately reproduce the measured data at these varying bias extremes is demonstrated in Fig. 15. Calculation of the error between the measured and

Fig. 13. Measured (+) and modeled (-) intrinsic output conductance  $Y_{\rm ds}$  (0.2–50 GHz) and associated fitting parameters of  $g_{\rm ds}$ ,  $\tau_{\rm ds}$ , and  $C_{\rm ds}$  for a  $2 \times 50 \,\mu{\rm m}$  GaN HEMT at  $V_{\rm GS} = -6.0$  V and  $V_{\rm DS} = 12.5$  V.

Fig. 14. Measured (+) and modeled (-) intrinsic output conductance  $Y_{\rm ds}$  (0.2–50 GHz) and associated fitting parameters of  $g_{\rm ds}$ ,  $\tau_{\rm ds}$ , and  $C_{\rm ds}$  for a  $2 \times 50 \,\mu$ m GaN HEMT at  $V_{\rm GS} = -7.0$  V and  $V_{\rm DS} = 20.0$  V.

TABLE VI EXTRACTED INTRINSIC ELEMENTS FOR  $2\times50\,\mu\,\mathrm{m}$  Gan Hemt

|                      | $V_{GS} = 0.0 V$ | $V_{GS} = -3.0V$  | $V_{GS} = -5.0 V$ |

|----------------------|------------------|-------------------|-------------------|

|                      | $V_{DS} = 8.0 V$ | $V_{DS} = 20.0 V$ | $V_{DS} = 6.0 V$  |

| $C_{gs}$ (fF)        | 101.0            | 120.0             | 103.0             |

| $R_{gs}(\Omega)$     | 16.4             | 12.2              | 3.4               |

| $C_{gd}(fF)$         | 32.0             | 13.0              | 19.0              |

| $R_{gd}(\Omega)$     | 53.8             | 145.0             | 54.0              |

| $g_{m}$ (mS)         | 11.0             | 18.8              | 26.3              |

| $\tau_{gm}$ (ps)     | 1.01             | 1.53              | 0.82              |

| g <sub>ds</sub> (mS) | 4.69             | 1.25              | 2.23              |

| $\tau_{ds} (ps)$     | 3.59             | 5.71              | 4.9               |

| $C_{ds}$ (fF)        | 36.0             | 31.0              | 38.6              |

| $G_{gs}(\mu S)$      | 4.25             | 40.57             | 7.86              |

| $G_{gd}(\mu S)$      | 1.62             | 3.80              | 5.11              |

modeled results is determined from the following generalized error expression [29]:

where M and N denote the number of bias and frequency points, respectively.

Fig. 15. Measured (×) and modeled (-) S-parameters (0.2–50 GHz) for  $2 \times 50 \ \mu m$  GaN HEMT for bias points (a)  $V_{\rm GS} = 0.0$  V and  $V_{\rm DS} = 8.0$  V, (b)  $V_{\rm GS} = -3.0$  V and  $V_{\rm DS} = 20.0$  V and (c)  $V_{\rm GS} = -5.0$  V and  $V_{\rm DS} = 6.0$  V.

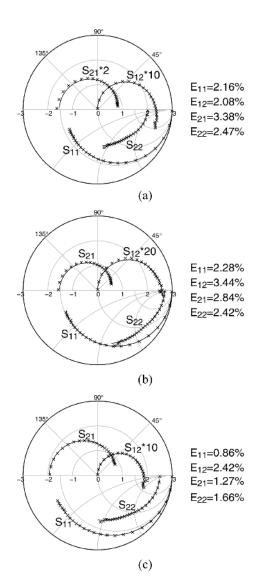

In Fig. 16, the variation of all intrinsic parameters over the bias plane is presented, in particular, the drain-source capacitance  $C_{ds}$  in Fig. 16(c). In saturation the high-field channel region extends towards the drain, separating the highly doped source and drain access regions in an electrostatic sense, and a resulting  $C_{ds}$  develops [30]. Under decreasing  $V_{DS}$  bias and increasing  $V_{\rm GS}$  bias, this separation becomes smaller, thus reducing this separation and giving rise to a sudden spike in the extracted  $C_{ds}$ , particularly around  $V_{GS} = 0.0$ , as shown. In retrospect, the behavior of the extracted  $C_{ds}$  around the "cold-FET" bias point of  $V_{\text{GS}} = 0.0$  V and  $V_{\text{DS}} = 0.0$  V highlights the requirement of the improved extraction methodology presented in this paper. The extracted capacitance at this bias is of the order of 15 times the magnitude of that extracted in the saturation region and, thus, its inclusion in the presented distributed topology of Fig. 4 is well justified. Overall, the behavior of the all-extracted elements is generally smooth over the bias plane, which

Fig. 16. Extracted intrinsic elements for  $2 \times 50 \ \mu m$  GaN HEMT over the measured bias plane.

is a favorable feature tending to verify the reliability of values determined by optimization-based extractions. These results are also consistent with those presented in previous publications on similar devices [11], [13].

A physical explanation of the drain time delay can be inferred from an analysis of its behavior over the bias plane. At biases exceeding the saturation voltage, the edges of the depletion layer are no longer largely confined to the region beneath the gate contact. In particular, the drain side of the depletion region extends steadily toward the drain terminal under increasing drain voltage. Correspondingly, a similar monotonic increase in the extracted drain delay can be observed in Fig. 16(e). Hence, one can postulate that it represents a delay in the drain current's response to the drain voltage arising from delays associated with the partially depleted high-field region. This essentially constitutes a transmission line effect, which, from a compact equivalent-circuit point-of-view, justifies the form of (22). Nonetheless, a more detailed explanation, particularly from researchers within the physical modeling community, may be warranted. The effectiveness of  $\tau_{ds}$ , in terms of modeling accuracy, can be demonstrated by a comparison of the error in  $S_{22}$  with and without its inclusion in the circuit of Fig. 1. Applying (23) to all the measured and modeled  $S_{22}$ -parameters across the entire bias plane, the authors have found that the error is reduced from 11.2% down to 3.5%.

Several accounts have detailed bias dependencies in the access resistances  $R_d$  and  $R_s$  of GaN-based transistors [31], [32]. Their importance and subsequent impact on the linearity performance in terms of the measured transconductance and cutoff frequency has been demonstrated [33], [34]. It should be noted that the access resistances extracted for this device were bias independent. The values determined under "cold-FET" conditions were found to be highly sufficient in reproducing the measured S-parameters of our device. Furthermore it is quite clear from Figs. 11 and 12 that the extracted intrinsic elements remained independent of frequency over the active bias plane. This is a clear indication of the accuracy of the model parasitics and, therefore, the use of bias-independent access resistances appears to be well founded. Although it can be argued that the inclusion of a time delay in the output conductance could be "masking" nonlinearities in the access resistances, the authors found that its omission resulted in negative resistances, which is both inconsistent with device physics and unsuitable for implementation in large-signal simulation environments.

The efficiency of the proposed extraction algorithm is demonstrated by the fact the entire small-signal performance of the device across the I-V plane (125 bias points) was determined in under 30 s. The accuracy and closeness of the parameter estimates, as highlighted in Tables II–IV, and the overall systematic approach of the extraction procedure contributes to its efficiency. Simulations were performed in a MATLAB simulation environment on a 1.65-GHz computer.

Our technique has recently been applied to another  $2 \times 50 \,\mu\text{m}$ GaN HEMT from a separate development process. Modeling accuracy, comparable to that presented in this paper, has been observed for this device including identification of almost identical delay phenomena in the output conductance. Straightforward scaling rules, similar to those proposed in [35], have permitted the extension of the proposed extraction methodology to wider device structures. Preliminary fitting results from a  $2 \times 125 \,\mu\text{m}$  GaN HEMT have been very promising, indicating the robustness of the proposed extraction methodology.

# V. CONCLUSION

A highly accurate and robust small-signal parameter extraction algorithm has been presented for a  $2 \times 50 \ \mu m$  GaN HEMT device. All parasitics have been evaluated using traditional "cold-FET" techniques that utilize a modified distributed channel model, which accounts for the significant drain-source capacitance observed under these bias conditions. Furthermore, the requirement to suppress the channel resistance by forward biasing the gate terminal is avoided. Straightforward expressions are introduced to estimate these parasitic quantities and subsequently improve the efficiency of the systematic optimization procedure. A time dependency in the output conductance has been introduced into the equivalent-circuit topology. It effectively represents a time delay at the output and accounts for the observed increase in phase delay at higher frequencies. A simple optimization procedure has been described to evaluate its behavior across the bias plane. The extracted intrinsic elements have also shown appropriate frequency independence over the entire measured frequency range. The validity of all extracted values has been verified with excellent correlation between the measured and modeled S-parameters up to 50 GHz.

# ACKNOWLEDGMENT

The authors would like to sincerely thank Dr. M. Uren and D. Hayes, both with QinetiQ Ltd., Hampshire, U.K., for supplying the measured small-signal parameter data.

#### REFERENCES

- S. N. Mohammad, A. A. Salvador, and H. Morkoç, "Emerging gallium nitride based devices," *Proc. IEEE*, vol. 83, no. 10, pp. 1306–1355, Oct. 1995.

- [2] S. T. Sheppard, K. Doverspike, W. L. Pribble, S. T. Allen, J. W. Palmour, L. T. Kehias, and T. J. Jenkins, "High-power microwave GaN/ AlGaN HEMT's on semi-insulating silicon carbide substrates," *IEEE Electron Device Lett.*, vol. 20, no. 4, pp. 161–163, Apr. 1999.

- [3] Q. Chen, J. W. Yang, M. A. Kahn, A. T. Ping, and I. Adesida, "High transconductance AlGaN/GaN hetrostructure field effect transistor on SiC substrates," *IEEE Electron. Lett.*, vol. 33, no. 16, pp. 1413–1415, Jul. 1997.

- [4] R. J. Trew, "Wide bandgap semiconductor transistors for microwave power amplifiers," *IEEE Micro*, vol. 1, pp. 46–54, Aug. 1996.

- [5] C. Lee, P. Saunier, J. Yang, and M. Asif Khan, "AlGan–GaN HEMT's on SiC with CW performance of e > 4 Watt/mm and 23% PAE at 35 GHz," *IEEE Electron Device Lett.*, vol. 24, no. 10, pp. 616–618, Oct. 2003.

- [6] R. Gaska, Q. Chen, J. W. Yang, A. Osinsky, M. Asif Khan, and M. S. Shur, "High temperature performance of AlGaN/GaN HFET's on SiC substrates," *IEEE Electron Device Lett.*, vol. 18, no. 10, pp. 492–494, Oct. 1997.

- [7] L. Shen et al., "AlGaN/AlN/GaN high-power microwave HEMT," IEEE Electron Device Lett., vol. 22, no. 10, pp. 457–459, Oct. 2001.

- [8] U. V. Bhadkar and M. S. Shur, "Monte Carlo calculations of the velocity-field characteristics of Wurtzite GaN," J. Appl. Phys., vol. 82, no. 4, pp. 1649–1655, 1997.

- [9] R. Gaddi, P. J. Tasker, and J. A. Plá, "Direct extraction of LDMOS small signal parameters from off-state measurements," *Electron. Lett.*, vol. 36, no. 23, pp. 1964–1966, Nov. 2000.

- [10] S. Nuttinck, E. Gebara, J. Laskar, J. Shealy, and M. Harris, "Improved RF modeling techniques for enhanced AlGaN/GaN HFETs," *IEEE Trans. Microw. Wireless Compon. Lett.*, vol. 13, no. 4, pp. 140–142, Apr. 2003.

- [11] A. Jarndal and G. Kompa, "A new small-signal modeling approach applied to GaN devices," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 11, pp. 3440–3448, Nov. 2005.

- [12] G. Chen, V. Kumar, R. S. Schwindt, and I. Adesida, "A low gate bias model extraction technique for AlGaN/GaN HEMTs," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 7, pp. 2949–2953, Jul. 2006.

- [13] G. Crupi *et al.*, "Accurate multibias equivalent-circuit extraction for GaN HEMTs," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 10, pp. 3616–3622, Oct. 2006.

- [14] D. M. Brookbanks, "Self consistent modeling of PHEMT device for millimeter wave small signal, noise and power applications," in *Proc. GaAs Applicat. Symp.*, Paris, France, Oct. 2000, 4 pp.

- [15] G. Kim, Y. Shimizu, B. Murakami, M. Goto, K. Ueda, T. Kihara, T. Matsuoka, and K. Taniguchi, "Accurate small-signal modeling of FD-SOI MOSFET," *IEICE Trans. Electron.*, vol. E89-C, no. 4, pp. 517–519, Apr. 2006.

- [16] M. Berroth and R. Bosch, "High frequency equivalent circuit of GaAs FET's for large signal applications," *IEEE Trans. Microw. Theory Tech.*, vol. 39, no. 2, pp. 224–229, Feb. 1991.

- [17] P. Roblin and H. Rohdin, *High-Speed Hetrostructure Devices*. Cambridge, U.K.: Cambridge Univ. Press, 2001.

- [18] M. A. Magerko and K. Chang, "Modeling of Gunn domain effects in the output conductance of the high-frequency small-signal GaAs MESFET equivalent circuit," *Microw. Opt. Technol. Lett.*, vol. 5, no. 14, pp. 748–752, Dec. 1992.

- [19] W. Struble, A. Platzker, S. Nash, and J. Plá, "A new small signal MESFET and HEMT model compatible with large signal modeling," in *IEEE MTT-S Int. Microw. Symp. Dig.*, San Diego, CA, May 1994, pp. 1567–1570.

- [20] T. Li, R. P. Joshi, and R. D. del Rosario, "Requirements for low intermodulation distortion in GaN–AlxGa1–xN high electron mobility transistors: A model assessment," *IEEE Trans. Electron Devices*, vol. 49, no. 9, pp. 1511–1518, Sep. 2002.

- [21] F. Diamant and M. Laviron, "Measurement of the extrinsic series elements of a microwave MESFET under zero current conditions," in *Proc. 12th Eur. Microw. Conf.*, Helsinki, Finland, Sep. 1982, pp. 451–456.

- [22] P. M. White and R. M. Healy, "Improved equivalent circuit for determination of MESFET and HEMT parasitic capacitances from 'coldFET' measurements," *IEEE Microw. Guided Wave Lett.*, vol. 3, no. 12, pp. 453–453, Dec. 1993.

- [23] Y.-L. Lai and K.-H. Hsu, "A new pinched-off cold-FET method to determine parasitic capacitances of FET equivalent circuits," *IEEE Trans. Microw. Theory Tech.*, vol. 49, no. 8, pp. 1410–1418, Aug. 2001.

- [24] N. Rorsman, M. Garcia, C. Karlsson, and H. Zirath, "Accurate smallsignal modeling of HFET's for millimeter-wave applications," *IEEE Trans. Microw. Theory Tech.*, vol. 44, no. 3, pp. 432–437, Mar. 1996.

- [25] G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, "A new method for determining the FET small-signal equivalent circuit," *IEEE Trans. Microw. Theory Tech.*, vol. 36, no. 7, pp. 1151–1159, Jul. 1988.

- [26] R. Tyrani, J. E. Gerber, T. Daniel, R. S. Pengelly, and U. L. Rhode, "A new and reliable direct parasitic extraction method for MESFETs and HEMTs," in *Proc. 23rd Eur. Microw. Conf.*, Madrid, Spain, Sep. 1993, pp. 451–453.

- [27] V. I. Cojocaru and T. J. Brazil, "Parasitic resistance extraction errors with their implications for FET model accuracy around  $V_{\rm cls} = 0$ ," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Denver, CO, Jun. 1997, pp. 1599–1602.

- [28] K. Shirakawa *et al.*, "An approach to determining an equivalent circuit for HEMT's," *IEEE Trans. Microw. Theory Tech.*, vol. 43, no. 3, pp. 499–503, Mar. 1995.

- [29] M. Pirazzini *et al.*, "A preliminary study of different metrics for the validation of device and behavioral models," in *Proc. 65th ARFTG Conf.*, Long Beach, CA, Jun. 2005, pp. 1–8.

- [30] H. Rohdin et al., "0.1 μm gate-length AlInAs/GaInAs/GaAs MODFET MMIC process for applications in high-speed wireless communications," *Hewlett-Packard J.*, vol. 49, pp. 1–37, Feb. 1998.

- [31] C. H. Oxley, "Method for measuring source resistance R<sub>s</sub> in saturation region of GaN HEMT device over bias conditions (V<sub>gs</sub>, V<sub>ds</sub>)," *Electron. Lett.*, vol. 40, no. 5, pp. 334–346, Mar. 2004.

- [32] R. J. Trew, Y. Liu, G. L. Bilbro, W. Kuang, R. Vetury, and J. B. Shealy, "Nonlinear source resistance in high-voltage microwave AlGaN/GaN HFETs," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 5, pp. 2061–2067, May 2006.

- [33] T. Palacios et al., "Influence of the dynamic access resistance in the gm and ft linearity of AlGaN/GaN HEMTs," IEEE Trans. Electron Devices, vol. 52, no. 10, pp. 2117–2123, Oct. 2005.

- [34] D. W. DiSanto and C. R. Bolognesi, "At-bias extraction of access parasitic resistances in AlGaN/GaN HEMTs: Impact on device linearity and channel electron velocity," *IEEE Trans. Electron Devices*, vol. 53, no. 12, pp. 2914–2929, Dec. 2006.

- [35] J. Wood and D. E. Root, "Bias-dependant linear scalable millimeterwave FET model," *IEEE Trans. Microw. Theory Tech.*, vol. 48, no. 12, pp. 2352–2360, Dec. 2000.

**Ronan G. Brady** (S'07) was born in County Cavan, Ireland, in 1982. He received the B.E. degree in electronic engineering from University College Dublin (UCD), Dublin, Ireland, in 2003, and is currently working toward the Ph.D. degree in characterization and modeling of microwave devices at UCD.

He is currently with the RF and Microwave Research Group, UCD. His research interests include device characterization and nonlinear modeling with an emphasis on the accurate prediction of dispersion phenomena in GaN-based devices.

**Christopher H. Oxley** received the B.Sc. degree in physics from the University of London, London, U.K., in 1969, and the Ph.D. degree from De Monfort University, Leicester, U.K., in 2005.

In 1969, he joined the Allen Clark Research Centre, Caswell, U.K. He recently joined the faculty of the Computing Science and Engineering Department, De Montfort University, Leicester, U.K. He has authored or coauthored over 70 scientific papers. He holds four patents. Throughout his career, he has been involved in the area of microwave

devices/circuits. His current interests include thermal imaging of electronic devices, electrical characterization/modeling of III–V and III nitride devices and electrical properties of conducting fabrics.

Dr. Oxley is a Fellow of the Institution of Engineering and Technology (IET).

**Thomas J. Brazil** (M'86–SM'02–F'04) received the B.E. degree in electrical engineering from University College Dublin (UCD), Dublin, Ireland, in 1973, and the Ph.D. degree in electronic engineering from the National University of Ireland, Dublin, Ireland, in 1977.

He then joined Plessey Research, Caswell, U.K., where he was involved with microwave subsystem development prior to returning to UCD in 1980. He is currently a Professor of electronic engineering and holds the Chair of Electronic Engineering at UCD.

His research interests are in the fields of nonlinear modeling and characterization techniques at the device, circuit, and system levels. He also has interests in nonlinear simulation algorithms and several areas of microwave subsystem design and applications. He has authored or coauthored numerous publications in the international scientific literature in these fields.

Prof. Brazil is a Fellow of Engineer Ireland and a Member of the Royal Irish Academy. From 1998 to 2001, he was an IEEE Microwave Theory and Techniques Society (IEEE MTT-S) Worldwide Distinguished Lecturer in high-frequency computer-aided design (CAD) applied to wireless systems. He is currently a member of the IEEE MTT-1 Technical Committee on CAD.