# An Interleaving Track & Hold with 7.6 ENOB @ 1.6 GS/s in 0.12 µm CMOS<sup>1</sup>

Simon M. Louwsma, Ed J.M. van Tuijl, Maarten Vertregt\*, Peter C.S. Scholtens\*, Bram Nauta

IC-Design Group, MESA+ Research Institute, University of Twente, Enschede, the Netherlands

\*Philips Research, Eindhoven, the Netherlands

S.M.Louwsma@utwente.nl

Abstract—A 1.6 GS/s Track and Hold circuit that produces 16 interleaving, 100 MS/s voltage buffered output signals is presented. The achieved SFDR for a 950 MHz full scale input signal is 50 dB. Phase alignment is 0.4 ps RMS and aperture uncertainty is 1 ps RMS. The chip includes two Analog to Digital Converters and a Switching Matrix to accommodate measurement of all sampled output signals and their timing relation. Chip area is 0.14 mm² excluding the AD Converters. The chip is made in a 0.12  $\mu m$ , 1.2 V CMOS Process. Power consumption of the interleaving T/H circuit is 32 mW.

*Keywords*—AD-converter; track and hold; sample and hold; interleaving; jitter

#### I. INTRODUCTION

For analog to digital conversion at samplerates above 1 GS/s, typically flash [1] converters are used. The resolution of these converters is limited, because each extra bit would require 4 to 8 times more gate area resulting in excessive input capacitance and power consumption. embedded For applications converters are therefore practically limited to 6 bits of accuracy; however for applications like cable-TV, higher resolutions are needed. For lower speeds, alternative architectures are widely available (like pipeline converters) which enable higher resolutions and have a higher efficiency. If accuracy of more than 6 bits is needed, combined with samplerates in the GS/s-range, interleaving multiple (pipeline) ADCs is a good option. In [2] an 8 bit 20 GS/s ADC is reported, consisting of 80 interleaved pipeline converters. Although performance is impressive, the power consumption of 10 W is too high for embedded applications. An important part of an interleaving ADC is the front-end T/H. In [3] and [4] GS/s-range track and hold circuits are presented, but they are all in bipolar technology, do not accommodate interleaving, and can not be embedded in

standard CMOS. In this paper we present a 1.6GS/s interleaving track and hold with only 32 mW of power consumption for application in a 16 times interleaved ADC architecture aiming at 8 bit performance.

### II. ARCHITECTURE

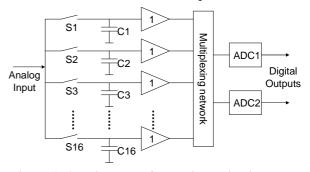

A schematic overview of the architecture of our testchip is shown in Figure 1. The circuit consists of 16 separate track and hold (T/H) circuits. Because analog off-chip measurement is difficult, a switching network and 2 ADC's are integrated to enable on-chip analog measurement. The switching network can connect each of the 16 T/H outputs to each of the ADC's. In this way linearity, offset, gain and time (phase) accuracy of the individual T/H circuits can be verified. The measurement method will be explained in section 5.

Figure 1: Architecture of the chip realization

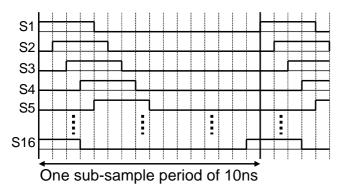

To create an interleaving T/H, the switches have to be opened one after another. The timing diagram is shown in Figure 2. The arrow at the bottom indicates one subsample period that contains 16 clockperiods of the 1.6 GHz sample clock. The track time is 4 clock periods (2.5 ns), while the hold time is 12 clock periods (7.5 ns). The asymmetry between the track and the hold time is chosen because a longer hold time, relaxes the ADC requirements. Furthermore, at each moment in time only 4 instead of 8 sample capacitors are connected to the input, which results in less input load capacitance and increases the input bandwidth. Decreasing the track time even further would result in incomplete settling.

<sup>&</sup>lt;sup>1</sup> Part of this work was presented at [6]

During each clock period one T/H circuit is switched into the hold mode (e.g. T/H1) and another is switched into the track mode (in this case T/H5). This last event generates a voltage spike at the input, because a capacitor with a previously sampled value is connected to the input. To avoid the influence of this spike (on T/H1), the switches in trackmode close after the switches in holdmode have been opened.

Figure 2: Timing of the switches in a 16 times

#### III. CIRCUIT DESIGN / IMPLEMENTATION

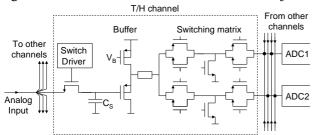

A single ended version of a complete channel is shown in Figure 3. The switches are implemented using a single NMOST without bootstrapping. Although bootstrapping would result in a lower and more constant ON-resistance, it is not needed in order to reach the target accuracy of 8 bit. The sampling capacitors are 100fF to limit kT/C noise, but also to limit distortion as will be described later in this section.

The chip has a differential clock input to decrease crosstalk and reject ground bounce. The clock lines are terminated on-chip with 50  $\Omega$  to ground. The clock-buffer consists of an N-type differential pair with current mirror followed by three inverters to generate steep edges in order to minimize the effects of circuit jitter.

Figure 3: A single ended T/H channel

Each differential T/H output can be connected to each of the two ADCs. As shown in Figure 3, this is accomplished by switching blocks consisting of two transmission gates and a switch to ground. This switch is included to prevent capacitive crosstalk between the channels. The matrix is controlled by an external bus

signal. The timing of the ADCs can also be controlled. When for example the next sampler is selected, to keep pace the ADC timing must be delayed by one clockperiod.

The ADCs are well-proven pipeline converters which were available in an analog library. They have a resolution of 10 bits which is enough to measure the accuracy of the T/H. The ADCs will not be discussed further, because they only serve the measurement purpose. The digital outputs are Low Voltage Differential Signalling (LVDS) buffers to minimize crosstalk from the digital outputs. Due to proper pin layout the crosstalk to the input pins is small and only common mode.

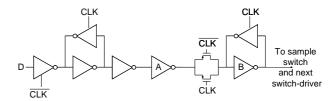

# A. Switch-driver

With a sample-rate fs of 1.6 GS/s, the switches have to be opened 625 ps after each other. When the timing is not accurate, distortion products at multiples of fs/16 around the frequency of the input signal will appear, degrading the SINAD. To accomplish accurate timing, the circuit shown in Figure 4 is used. The circuit is a modified master/slave flipflop. The digital input D dictates whether the sample switch should be opened or closed on the next rising edge of the clock. Jitter of this signal does not influence the moment of the switch transition, because it is re-clocked by the master-clock running at fs. With this circuit it is possible to generate the clock scheme with Linterleaving and non-equal sample- and holdtimes. The critical, jitter generating path from clock-edge to sampling switch is kept as short as possible, minimizing aperture uncertainty due to noise and matching accuracy. As discussed in the previous section, some delay is needed when going from track- to holdmode. This is accomplished by varying the ratio of the PMOST and NMOST of the transmission gate and of the inverters A and B.

Figure 4: Switch-driver circuit

To generate the clock scheme as shown in Figure 2, a circuit generating a 4-out-of-16 signal is connected to the D input of switchdriver 1. The output of switchdriver 1 has the same shape as the input, but is delayed by one clockperiod. This signal is connected to the D input of switchdriver 2 and so on.

# B. 3.2 Buffer

The hold buffer is shown in Figure 3. It consists of a PMOST source follower, because this simple circuit has a large bandwidth and still enough linearity for 8 bit. The external biasing of the PMOST current sources is common to all buffers. A source follower has a DC level shift between its input and output. Offsets between the buffers result in distortion components in the combined digital output stream. The offsets should be smaller than half an LSB, which is 1 mV for 8 bits of accuracy. For the 0.12  $\mu m$  technology the required gate area would be 352  $\mu m^2$  per buffer (3 $\sigma$  value).

Due to the nonlinear input capacitance of the buffer harmonic distortion is generated. To reduce this distortion the total capacitance can be linearized by connecting a linear (plate) capacitor in parallel. Simulation shows that this capacitance has to be about 5 times larger than the gate capacitance in order to get enough linearity for 8 bit. This would result in a load of about 0.7 pF \* 5 per T/H, making the total input load 14pF. As the input is terminated with a 50  $\Omega$  resistor onchip, the resulting input bandwidth would be limited to 270 MHz. This is far below the target, and therefore another solution is chosen. Much smaller source followers are used, which do not meet the matching criteria. The offsets must then be calibrated, which is feasible [2] and is expected to have low power consumption, because only a DC calibration is needed. In this design the calibration is not yet implemented. The resulting input bandwidth including all parasitics is 3.5 GHz.

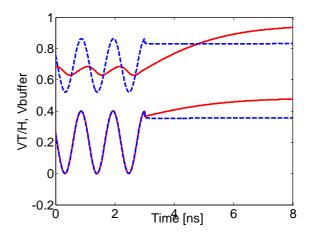

When the bandwidth of the buffer is a few times larger than the input frequency, the output of the buffer will follow the input. With the load of the ADC, which can be as high as 2 pF, this would result in a huge power consumption. However for correct operation of the T/H and ADC such a high bandwidth is not needed, because the samplerate of the ADC is the input samplerate divided by the interleaving factor. Choosing the bandwidth of the buffer much lower than the maximum input frequency saves a lot of power. This has however some consequences: when sampling a high frequency input signal the output can not follow the input signal completely. After the sampling moment the output settles to its final value. Thus after the sampling, the voltage over capacitor C<sub>GS</sub> of the source follower changes, which results in charge redistribution. This changes the voltage on the sampling capacitor and the final output value of the buffer, which introduces distortion due to the nonlinearity of C<sub>GS</sub>. A simulation result showing this behaviour is shown in Figure 5 with the straight red lines. A poly-Si resistor is placed between the buffer and the output load (the ADC input), increasing the bandwidth of the buffer. Now the output can follow the input of the buffer and the distortion is reduced. This is shown in Figure 5 with the blue dashed lines.

Figure 5: Simulation result showing the behaviour of adding the resistor. Straight lines: without resistor, dashed lines: with resistor. Upper lines: Output voltage of buffer, Lower lines: Input voltage of buffer.

All circuits are quasi-differential so each T/H circuit contains 2 channels in a symmetrical layout. This symmetry and the choice of PMOS transistors (source connected to the N-well) in the source followers guarantees a good rejection of the common mode (ground) bounce.

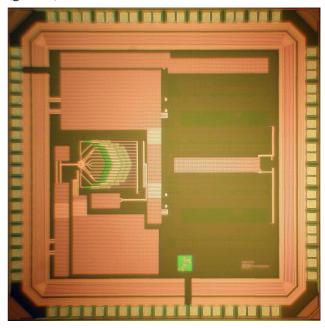

Figure 6: Photograph of the complete test chip. Dimensions: 2.2 mm x 2.2 mm

#### IV. LAYOUT

In Figure 7 a photograph of the complete chip is shown. On the left hand side in the middle the T/H-core is located an on the right hand side the two ADC's are laid-out, but they are not visible, because of metal-6 tiling. The rest of what is visible is mostly decoupling capacitance.

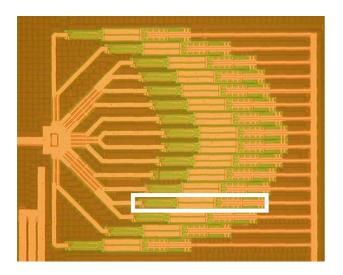

Matching properties between the different T/Hs have to be good. Differences in phase, gain or timing will be depicted as tones related to multiples fs/16. To accomplish good matching a symmetrical bus structure is used as shown on the chip photograph in Figure 7. From the central point in the middle on the left, 16 busses with exactly the same length are connected to the T/H circuits. A layout of one of the T/H circuits is shown in Figure 8. The circuits all have the same orientation to minimize mismatch.

Figure 7: Chip photograph showing the T/H core. Dimensions:  $400 \ \mu m \times 350 \ \mu m$

Figure 8: Layout of a single T/H channel

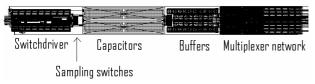

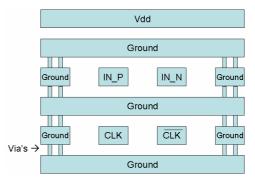

A cross section of the bus is shown in figure 9. The bus does not only contain the differential input signal, but also the differential clock signal and the supplies of the buffer that drives the switch. Differences in these are minimized and sampling time offsets are reduced. Another advantage of the bus structure is that both the clock and the input signals are shielded, lowering crosstalk between these two.

Figure 9: Cross section of the bus structure

# V. EXPERIMENTAL RESULTS

The T/H is designed for a 2 GHz sampling frequency, implying a subsampling frequency of 125 MHz. The integrated ADCs however are limited to 100 MS/s, so testing was limited to 1.6 GS/s. Most measurements however were performed at 1.28 GS/s in order to get an ENOB of 9.2 of the converters instead of 7.7 at 1.6 GS/s.

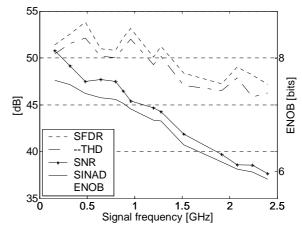

The performance of a single channel of the distributed T/H is determined by connecting it to one of the ADCs. In figure 10 SFDR, -THD, SNR and SINAD/ENOB are shown as a function of the input frequency at a samplerate of 1280 MS/s. The input amplitude at the chip is  $0.5V_{PP,\ Differential}$  but varies slightly due to cable losses. This is visible as a ripple in SFDR and -THD.

Figure 10: SFDR, SNR, -THD, SINAD and ENOB of one T/H for different input frequencies. Fs = 1.28 GHz

The effective resolution bandwidth (ERBW) is 1 GHz, starting from an initial 7.6 ENOB performance at 100 MHz signal frequency. Beyond the ERBW, gradual and graceful degradation is observed up to 2.4 GHz. Similar performance is measured for different channels and different samples. At high frequencies the SNR drops due to the influence of clock-jitter and at low frequencies the SNR is dominated by circuit noise. From calculations it follows that the jitter is about 1 ps RMS.

This jitter stems from the external clock generator, the external signal generator, and from the T/H circuit. The jitter of the clock and signal generators is specified at 0.5 ps RMS, so the jitter contribution of the circuit is small.

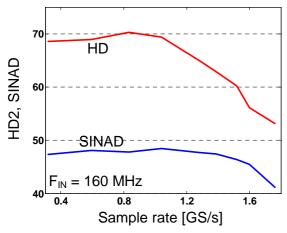

In Figure 11 another single channel measurement is shown. In this measurement the input signal frequency is constant at 160 MHz, while the sample rate is swept from 200 MS/s to 1.76 GS/s. Up to 1.3 GS/s the performance is constant, while for higher sample-rates the SINAD starts dropping due to second order distortion. Because the front-end has a very large bandwidth as can be concluded from Figure 10, this distortion can only be caused by the AD-converters, which in this case limit the performance.

In order to determine the voltage offsets between the channels, all different T/H channels were measured with the same ADC. The measured offsets are within  $\pm$  4 LSBs at 8 bit level. These are as expected, so offset calibration is needed. With this setup also the gain difference between the channels can be determined. The gain matching between the channels is  $\pm$  0.37dB, which is worse than expected. The cause of this is still under investigation.

Figure 11: SINAD and HD2 of one T/H for different sample frequencies. Fin = 160 MHz

The time alignment of the different channels was measured using the following setup. E.g. ADC1 is connected to T/H1 and ADC2 connected to T/H9. For good measurement accuracy an input signal close to the Nyquist frequency is used. From the outputs of both ADCs FFT's were calculated and the phase difference between the input signals was determined. Subtracting the phase differences due to the interleaving, the phase error and therefore the time-error can be calculated. Calculation of this phase error is very accurate because it is the average over 16,000 samples in an FFT, so the phase error due to jitter is averaged out. The RMS value

of all channel offsets is 0.4 ps. Compared to the 1.0 ps jitter this is acceptable. Measurements on other samples give comparable results.

In general a T/H consumes a large part of the total power of a complete ADC. To be able to place the power consumption of this interleaving T/H in perspective, a Figure of Merit is calculated in a similar way as for ADCs:

$$FoM = \frac{P}{2^{ENOB} 2 \times ERBW}$$

When leaving the gain and voltage offsets out of consideration, the FoM for this T/H is 0.1 pJ/Conversion. ADCs with samplerates in the order of 2 GS/s have a FoM of well over 1 pJ/C. Combined with 16 moderate speed ADCs, which can have a FoM below 1 pJ/C [5] this can result in a power efficient, high speed, moderate resolution ADC.

#### VI. CONCLUSIONS

In this paper an interleaving T/H is presented. It consumes 32mW of power, has an ENOB of 7.6 bits and an ERBW of 1 GHz. The capacitive input load is smaller than 1pF and the FoM is 0.1 pJ/C.

Combining this interleaving T/H with efficient moderate speed converters can result in a power efficient, high speed, moderate resolution ADC, making it very attractive for embedding in future applications.

# VII. ACKNOWLEDGEMENTS

The authors would like to thank Hendrik van der Ploeg for his assistance and Philips Research for fabrication of the chip.

# REFERENCES

- [1] P. Scholtens, et al., "6-bit 1.6-Gsample/s flash ADC in 0.18- $\mu$ m CMOS Using Averaging Termination," IEEE J. Solid-State Circuits, vol 37 pp. 1599 1609, December 2002.

- [2] K. Poulton, et al., "A 20GS/s 8b ADC with a 1MB Memory in 0.18  $\mu m$  CMOS", ISSCC Digest of Technical Papers, Feb. 2003.

- [3] J. C. Jensen, et al., "A Broadband 10-GHz Track-and-Hold in Si/SiGe HBT Technology", IEEE J. Solid-State Circuits, vol 37 pp. 325-330, March 2001

- [4] A. Boni, et al., "A 1-GS/s 2.7-V Track-and-Hold Amplifier with 10-b Resolution at Nyquist in SiGe BiCMOS", ESSCIRC, September 2001, pp 451-454.

- [5] J. Mulder, et al., "A 21mW 8b 125MS/s ADC Occupying 0.09mm² in 0.13 $\mu$ m CMOS", ISSCC Digest of Technical Papers, Feb. 2004.

- [6] S.M. Louwsma, et al., "A 1.6 GS/s, 16 Times Interleaved Track & Hold with 7.6 ENOB in 0.12  $\mu m$  CMOS," Proceeding of the 30<sup>th</sup> European Solid-Sate Circuits Conference, September 2004.