# **UC Irvine**

# **ICS Technical Reports**

### **Title**

An optimal clock period selection method based on slack minimization criteria

### **Permalink**

https://escholarship.org/uc/item/79212829

### **Authors**

Chang, En-Shou Gajski, Daniel D. Narayan, Sanjiv

### **Publication Date**

1996-01-08

Peer reviewed

Notice: This Material may be protected by Copyright Law (Title 17 U.S.C.) SL BAR Z 699 C3 no. 95-57

# An optimal clock period selection method based on slack minimization criteria

En-Shou Chang Daniel D. Gajski Sanjiv Narayan

Technical Report #95-57 January 8, 1996

Department of Information and Computer Science University of California, Irvine Irvine, CA 92717-3425 (714) 824-8059

echang@ics.uci.edu

#### Abstract

An important decision in synthesizing a hardware implementation from a behavioral description is selecting the clock period to schedule the datapath operations into control steps. Prior to scheduling, most existing behavioral synthesis systems either require the designer to specify the clock period explicitly or require that the delays of the operators used in the design be specified in multiples of the clock period. An unfavorable choice of the clock period could result in operations being idle for a large portion of the clock period, and consequently, affect the performance of the synthesized design. In this paper, we demonstrate the effect of clock slack on the performance of designs and present an algorithm to find a slack-minimal clock period. We prove the optimality of our method and apply it to several examples to demonstrate its effectiveness in maximizing design performance.

Notice: This Material may be protected by Copyright Law (Title 17 U.S.C.)

# 1 Introduction

In recent years, logic synthesis has come to be recognized as an integral part of the design process, and this recognition has led to an evolutionary change in design methodology into a describe-and-synthesize[1, 2] approach. The advantage of this new methodology is that it allows us to specify a design in a purely behavioral form, devoid of any implementation details. For example, we can describe a design using Boolean equations, finite-state, etc. An implementation for the design can be generated by automatic synthesis tools, instead of manual design, which is usually tedious.

Behavioral synthesis involves the transformation of a design specification into a set of interconnected RTcomponents[2] which satisfy the behavior and some specified constraints, such as the number of functional units, performance etc. Three major synthesis tasks are applied during the transformation[2]: allocation, scheduling and binding. The purpose of allocation is to determine the number of resources, such as registers, buses, and functional units, that will be used in the implementation. The task of scheduling is intended to partition the behavioral description into time intervals, called control steps. During each control step, which is usually one clock-cycle long, data will be fetched from a register, transformed y a functional unit, and written back to a register. All register transfers in any given control step will be executed concurrently. The binding task assigns variables to storage units and operations to functional units, as

well as making sure that there is a distinct communication path or bus assigned for each transfer of data between the storage and functional units.

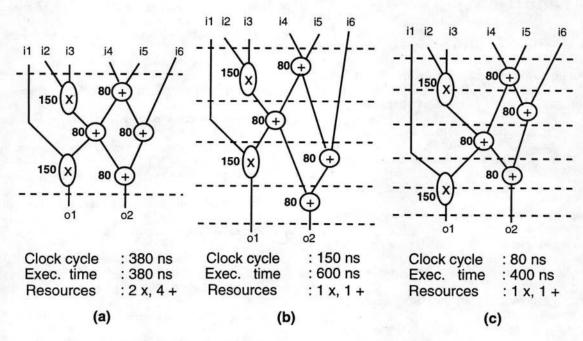

Another major task in behavioral synthesis is the selection of the clock period that will be used for implementing the design. Selecting clock period before performing synthesis tasks is important, since the choice of clock period could affect the execution time and the resources required to implement the design. For example, consider using three different clock periods (380) ns, 150 ns and 80 ns) for implementing the dataflow graph in Figure 1. In Figure 1(a), clock period 380 ns allows the fastest possible execution time but requires 2 multipliers and 4 adders to implement the design (the multiplier and adder have a delay of 150 ns and 80 ns, respectively). On the other hand, a clock period of 150 ns in Figure 1(b) requires only one adder and one multiplier, but results in a total execution time of 600 ns. The most efficient implementation, in terms of performance per resource, is obtained with an 80 ns clock period, as shown in Figure 1(c). Its execution time is comparable to that of the first implementation, and it requires the same minimal number of resources required by the second implementation.

In most synthesis tools[3, 4, 5, 6, 7], the clock period must be specified by the designer before synthesis—either the clock period is specified explicitly or the delays of components are expressed in multiple of the clock period. Designer-specified clock period is applicable when the design is developed as a part of a larger

Figure 1: Effect of the clock period on execution time and resources required

system. In this case, the clock period used for some of the standard components in the system is known and can be used for the remainder of the design. In some other cases, where the clock period is not specified, clock period selection assume great importance. It is evident from Figure 1 that the choice of a particular clock period has a strong impact on the quality of the design both in terms of hardware size and its performance. Thus, it is essential that clock period selection become an integral part of synthesis tools, which should provide the designer with feedback as to how various clock periods could possibly affect the design quality.

Some synthesis tools[8, 9, 10] equate the clock period with the delay of the slowest functional unit in the design. However, this scheme leads to under-utilization

of the faster functional units. The reason for low utilization of faster units is that in the presence of a slower functional unit such as a multiplier, which has a large delay, the clock period will be at least as long as the multiplier delay, and faster functional units implementing other operations (such as an addition) will be idle for a significant portion of the clock cycle. Hence, longer execution times can be expected for a design using the maximum-operator-delay clock.

In order to improve the performance of the design, we need to minimize the time that operations are idle (i.e. slack time) in any given control step. In this paper, we will present a method to compute the clock period for implementing a given behavioral description with a view to eliminating or minimizing the idle time associated with datapath operations.

An overview of existing approaches for estimating the clock period is presented in Section 2. We will explain our design model in Section 3. Section 4 presents a formulation of the clock estimation problem. We formally prove some properties of zero-slack clock period in relation to the delays of the functional units that will be used in the design in Section 5 In cases where its not possible to entirely eliminate the slack associated with design operations, we present an algorithm to determine a slack-minimal clock period. idle time of the functional units in Section 6. Experimental results on several benchmarks are shown in Section 7. Finally, we present our conclusions in Section 8.

## 2 Previous Work

A few synthesis tools [8, 9, 10] have incorporated clock estimation techniques which are used to either examine area-time trade-off in the design or to guide synthesis tasks such as scheduling.

In MAHA [8], the critical path in the dataflow graph is determined first. The maximum delay of any operator in the critical path is chosen as the clock period.

The clocking scheme proposed in [9] computes a lower bound for the clock period of a multi-stage system to be the longest stage time. Since the longest stage time is at least as long as the longest operator delay, this scheme computes a clock period greater than or equal to the longest operator delay.

A model for area-time estimation is presented in [10]. The dataflow graph is divided into a number of time steps. The critical path delay and the number of time steps are used to compute the lower bound on the clock as given in the following equation:

$$CLK = MAX \begin{bmatrix} Critical \ Path \ Delay/Time \ Steps, \\ MAX[Operator \ Delay] \end{bmatrix}$$

$$(1)$$

Each of the above approaches assume that each operation must be executed within one clock cycle. Multi-cycle operations, where an operation could be scheduled in two or more control steps, are not permitted. Consequently, they are similar to each other in one respect — the clock period calculated by each of the above methods is at least as long as the largest operator delay. We shall refer to these clock estimation methods as the maximum-operator-delay methods. The advantage of the above methods is that they are simple to implement and their algorithmic complexity is linear with respect to the number of different operation types that will be used to implement the design.

Let the clock period computed by these methods be denoted by  $CLK_{MOD}$ . Let  $Delay(oper_i)$  denote the delay of operation type  $oper_i$ . From the above analysis of maximum-operator-delay methods,

$$CLK_{MOD} \ge MAX [Delay(oper_i)],$$

$$for all operator types t_i \qquad (2)$$

However, using the maximum-operator-delay clock period will lead to under-utilization of the functional units in cases where the delays differ widely. Consequently, the performance of the design (start to finish execution time) is slower that cases where the idle time was somehow minimized. Incorporating the effect of clock period on the idle times of operations, during clock selection, forms the main motivation of the slack minimization method presented in this paper.

# 3 Design model

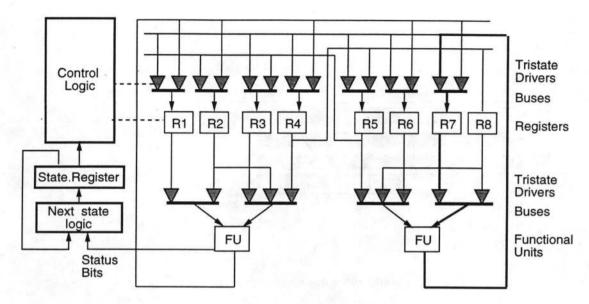

The design model for which the clock calculation is based on is shown in Fig 2. A two level bus structure is assumed for the interconnection across the registers and functional units. This model allows for easy analysis of the performance issues since the delay of the tristate driver can be considered to be constant with respect to the number of the tristate drivers driving a bus. We also assume, that for each operation in the design, there is exactly one functional unit which implements it.

Operations can be executed over several clock cycles. Thus, if a functional unit has a delay of 90 ns and the clock period is 50 ns, then the functional unit will take two clock cycles to execute the operation. A typical register-to-register transfer involves operands being read from registers, an operation performed on the operands, and the results stored in another register. Therefore, the delay delay(oper<sub>i</sub>) associated with operation type oper<sub>i</sub> of register-to-register transfer is the following:

$$delay(oper_i) = 2 * T_{tristate\_driver} + T_{setup} + T_{prop} + OpDelay(oper_i)$$

(3)

where  $T_{setup}$  and  $T_{prop}$  be the register setup and propagation delays,  $T_{tristate\_driver}$  be the delay of the tristate driver and  $OpDelay(oper_i)$  be the delay of the functional unit of type  $oper_i$ .

The operator delays used in the following sections are the values  $delay(oper_i)$  computed above, since the delay of the tri-state drivers and the registers can be counted as a constant.

# 4 The slack minimization criteria

In this section, we will present a new approach to guiding clock period selection based on a slack minimization criteria. We first define a few terms that will be used frequently throughout this paper:

**DFG** completion time: It represents the execution time of a DFG (Data Flow Graph). If the DFG is scheduled into C control steps with a clock period clk, then the completion time of the DFG,  $T_{DFG}$ , is defined as:

$$T_{DFG} = C \times clk \tag{4}$$

Operator Occurrences: This represents the number of occurrences of an operation type  $oper_i$  in a given behavioral description or its corresponding DFG, and is denoted by  $occur(oper_i)$ .

clock slack[1]: For a given clock period, the clock slack associated with an operation (or its corresponding functional unit) is defined as the difference between the operation delay and the next higher multi-

Figure 2: Design Model for Clock Calculation

ple of clock cycle. In other words, the clock slack is equivalent to the time that the functional unit would be idle, if it were scheduled into a control step. For a given clock period clk and operation type oper<sub>i</sub>, the clock slack, denoted by slack(clk, oper<sub>i</sub>), is computed using the following equation:

$$slack(clk, oper_i) = (\lceil delay(oper_i) \div clk \rceil \times clk)$$

$$- delay(oper_i) \qquad (5)$$

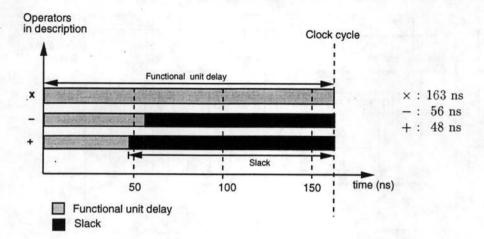

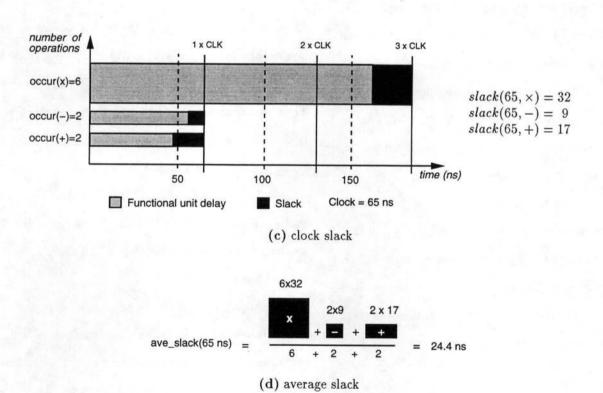

Figure 3 shows the clock slack associated with three types of operations. In this example, the clock period is determined by the maximum-operator-delay method. The lightly shaded regions represent the delays of three operation types. The clock slacks are represented by the dark regions.

average slack: For a given clock period clk, the average slack, denoted by ave\_slack(clk), is defined as the average clock slack of each operation in the design.

Let  $occur(oper_i)$  represent the number of occurrences of operation type  $oper_i$  in the design, then the average slack is defined as:

$$ave\_slack(clk) = \frac{\sum_{i} \{occur(oper_i) \times slack(clk, oper_i)\}}{\sum_{i} occur(oper_i)}$$

(6)

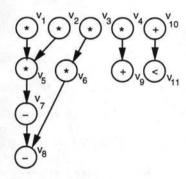

Let's consider the example shown in Figure 4, which graphically depicts the clock slack associated with the different operations in HAL[4], a second-order differential equation example. The components used are from the VDP100 datapath library[11]. Figure 4(a) shows the dataflow graph for this design. Figure 4(b) shows the occurrences and the delays of each operation type. In Figure 4(c), the delay of each operation type is shown graphically as the length of the lightly shaded regions along the X-axis. The number of occurrences of the operations in the behavior is the height of the shaded region along the Y-axis. The dark shaded regions represent the clock slack for each operation type.

Figure 3: Functional unit clock slack with clock period 163 ns

The average slack for a design of clock period 65 ns is 24.4 ns, graphically shown in Figure 4(d).

We now formulate the Slack Minimization problem. The main objective of the slack minimization problem is to minimize the clock slack in each clock cycle with the assumption that a smaller clock slack on the average will decrease the execution time of the given behavior. The clock period that produces minimum average slack, within a certain clock range, is selected as the slack-minimal clock period. Thus, the problem is defined as follow:

Find

$$clk \ge clkmin$$

which

Minimizes  $ave\_slack(clk)$  (7)

where *clkmin* is the lower bound of the clock period. *clkmin* can be determined by the designer or physical restrictions. For example, a component library usually specifies the shortest clock period at which the clock input of a bistate circuit may be driven with stable transitions of logic levels.

# 5 Computing a zero-slack clock

Obviously, "zero slack" is a lower bound of the clock slack. In this section, we will introduce two extended definitions of common divisor and greatest common divisor (GCD) and then demonstrate how a clock period is selected to obtain zero slack.

Definition 1 A common divisor in the domain of real numbers is defined as:

A real number r is a common divisor of a set of real numbers  $\{t_1, t_2, \ldots, t_n\}$

$\equiv \exists$  positive integer  $k_i \ni rk_i = t_i, \forall i$

Definition 2 A greatest common divisor (GCD) in the domain of real numbers is defined as:

GCD: set of  $R \to R$   $GCD\{t_1, t_2, \ldots, t_n\}$   $\equiv$  the largest common divisor associated with  $\{t_1, t_2, \ldots, t_n\}$

| operation type | occurrences | delay  |

|----------------|-------------|--------|

| add            | 2           | 48 ns  |

| subtract       | 2           | 56 ns  |

| multiply       | 6           | 163 ns |

(b) Occurrences and Delays of each operation type

(a) Dataflow Graph for the HAL differential Equation example.

Figure 4: Clock slack and average slack for HAL differential equation with clock period 65 ns

Whenever we select a common divisor for the delays of all the operation types used in the design to be the system clock period, it is directly induced from Definition 1 that all the operations can be executed completely in one or more clock cycles without any clock slack. We prove this property formally below:

**Theorem 1** A given clock period causes no clock slacks for a given set of operations  $\{oper_1, oper_2, ..., oper_n\}$  if and only if the clock period is a common divisor of the delay time  $\{t_1, t_2, ..., t_n\}$  of those operations.

### Proof:

First, we prove the necessity. Let the delays of the operation types be  $\{t_1, t_2, \ldots, t_n\}$  and the given clock period be a common divisor r of them. According to Definition 1, there are corresponding positive integers  $\{k_1, k_2, \ldots, k_i\}$  such that  $rk_i = t_i$  for all i, i.e., an operation of type  $oper_i$  can be executed exactly in  $k_i$  clock cycles with no slack.

Second, we prove the sufficiency. Assume that the delays of the operation types are  $\{t_1, t_2, \ldots, t_n\}$  and that there are corresponding positive integers  $\{k_1, k_2, \ldots, k_i\}$ such that an operation of type  $oper_i$  can be executed exactly in  $k_i$  clock cycles with no slack, then the clock period r satisfies Definition 1:  $\exists$  positive integer  $k_i$

$$\ni rk_i = t_i, \forall i$$

П

Since a clock period that causes zero-slack should be a common divisor of the delays of those operation types, it is trivial to infer the next theorem: **Theorem 2** The longest clock period which causes no clock slack for a given set of operations is the GCD of the delays of these operations.

From Theorem 2, we can see that if we select the GCD of the delays of all the operation types used in the design to be the clock period, there will be no idle portion in all of the clock cycles, no matter what operations are executed in each clock cycle. i.e. the longest clock period for which we will have a zero clock slack for all operation types is the GCD of their delays.

# 6 Slack minimization method

Although using the GCD of the all the operation delays as the clock period will result in zero clock slack, it is sometimes too small to be practically implemented. Thus, we need a method to select a good clock period with the smallest average slack within the feasible range, when the GCD is not applicable.

Consider the definition of the slack minimization problem (Eq.(7)). To find out the properties of Eq.(7), we shall expand the equation into a formula of primary terms, shown in Eq.(8).

Since we are minimizing Eq.(8) over a range of clock period values, terms in the equation that are invariant regardless of the specific clock period value being considered (clk) can be treated as constants. Thus, the problem can be further simplified into Eq.(9).

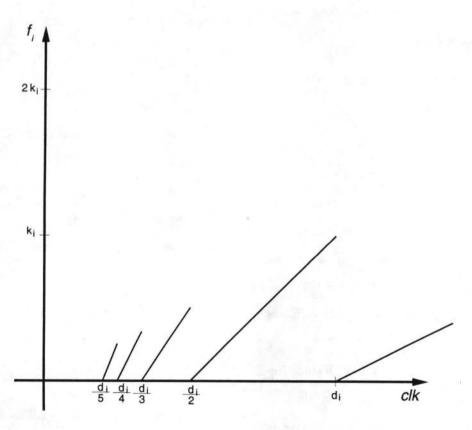

Let  $f_i(clk)$  denote a single term of Eq.(9), we can obtain the following equation.

$$f_i(clk) = k_i \times ((\lceil d_i \div clk \rceil \times clk) - d_i) \tag{10}$$

Find  $clk \geq clkmin$  which

Minimizes

$$\frac{\sum_{i} \{occur(oper_i) \times ((\lceil delay(oper_i) \div clk \rceil \times clk) - delay(oper_i))\}}{\sum_{i} occur(oper_i)}$$

(8)

Find

$$clk \geq clkmin$$

which Minimizes  $\sum_{i} \{k_i \times ((\lceil d_i \div clk \rceil \times clk) - d_i)\}$

where both  $k_i = \frac{occur(oper_i)}{\sum_{i} occur(oper_i)}$  and  $d_i = delay(oper_i)$  are constants under various  $clk$ .

Figure 5:  $f_i(clk) = k_i \times ((\lceil d_i \div clk \rceil \times clk) - d_i)$

$$= \begin{cases} k_i \times (clk - d_i) \\ \text{where } d_i \leq clk \\ k_i \times (m \times clk - d_i) \\ \text{where } \frac{1}{m} d_i \leq clk < \frac{1}{m-1} d_i , \\ \forall \text{ integer } m > 1 \end{cases}$$

For example,

when  $\frac{1}{2}d_i \leq clk < d_i$ ,  $f(clk) = k_i \times 2 \times clk - d_i$ ; when  $\frac{1}{3}d_i \leq clk < \frac{1}{2}d_i$ ,  $f_i(clk) = k_i \times 3 \times clk - d_i$ ; when  $\frac{1}{4}d_i \leq clk < \frac{1}{3}d_i$ ,  $f_i(clk) = k_i \times 4 \times clk - d_i$ . Figure 5 graphically depicts the function Eq.(10). Therefore, we observe three useful properties on Eq.(10):

- A discontinuous point (break point) of this function is created if and only if it is on  $clk = \frac{d_1}{m}$ , where m is a positive integer.

- The gradient between any two adjacent discontinuous points is fixed.

- A minimal value is generated if and only if it is on a discontinuous point.

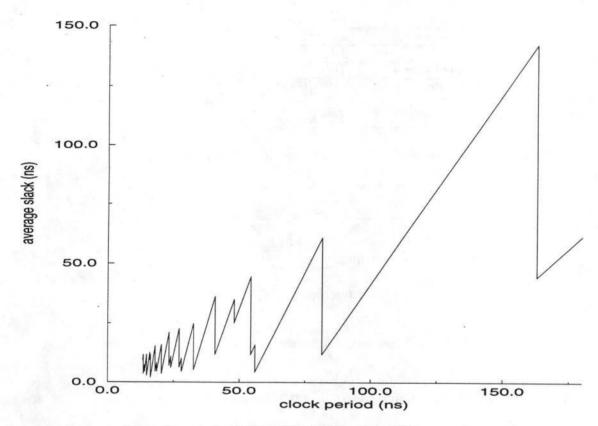

Since Eq.(9) is a summation of Eq.(10), it inherits these properties from Eq.(10). These properties of Eq.(9) can be seen clearly in Figure 6, an example of function diagram of Eq.(9) which is computed from the HAL Second-Order Differential Equation example [4]. With these properties, we can derive the minimal average slack by examining all the discontinuous points and the boundary, clkmin.

The slack minimization algorithm, which computes the clock period with the minimum average slack, is outlined in Figure 7. First, we follow the definition of operator occurrences to compute  $occur(oper_i)$  of each operation type  $oper_i$ . Then, we search all the discontinuous points of the function  $ave\_slack(clk)$  defined in Eq.(6) to find the clock period min\_slack\_clk that will cause minimum average slack within the clock range specified. The value clkmin is the lower bound of the clock range.

The time complexity of computing operator occurrences is O(n), where n is the number of nodes in the DFG provided. The time complexities of computing function  $ave\_slack(clk)$  is O(m), where m is the number of the operation types used. The number of points searched is

$$\sum_{i} \lfloor \frac{delay(oper_i)}{clkmin} \rfloor + 1 \tag{11}$$

which is O(m). Thus, the overall time complexity is  $O(n+m^2)$ .

# 7 Experimental result

To verify the accuracy of the slack minimization criteria and to prove that the clock period selected by the slack minimization algorithm can produce significantly improved design performance, the Slack Minimization method was applied to several well-known benchmarks, the HAL second order differential equation [4], a fifth order elliptical filter [12], a AR lattice filter [10], and a linear phase B-spline interpolated filter [13]. We use the resource-constrained scheduler of BdA [14] to perform the scheduling.

The datapath elements we used, shown in Table 1(a), are taken from VLSI Technology Inc. VCC4DP3 Datapath Library[15]. Computed by Eq.(3), the delay(operi)

Figure 6:  $ave\_slack(clk) = \sum_i f_i(clk)$  of the HAL example

Figure 7: The slack minimization algorithm

| datapath component | VCC4DP3 cell name | delay time    |

|--------------------|-------------------|---------------|

| adder              | DPADD001H         | 26.90 ns      |

| multiplier         | DPMLT020M         | 84.10 ns      |

| subtractor         | DPSUB001H         | 27.40 ns      |

| tristate buffer    | DPBUF0011         | 0.78 ns       |

| register           | VDP3DFF001        | setup 3.12 ns |

|                    |                   | hold 2.06 ns  |

| control buffer     | DPCLKGLO1-4       | 2.54 ns       |

(a) Datapath elements used in the designs

| operation type | delay    |  |

|----------------|----------|--|

| add            | 33.70 ns |  |

| subtract       | 34.20 ns |  |

| multiply       | 90.90 ns |  |

(b) delay(operi) we used

Table 1: Operation delays derived from the VCC4DP3 Datapath Library

we used are shown in Table 1(b). The minimum clock period *clkmin* is 2.54 ns, which is determined by the speed of the global control input non-inverting buffer of the VCC4DP3 Library.

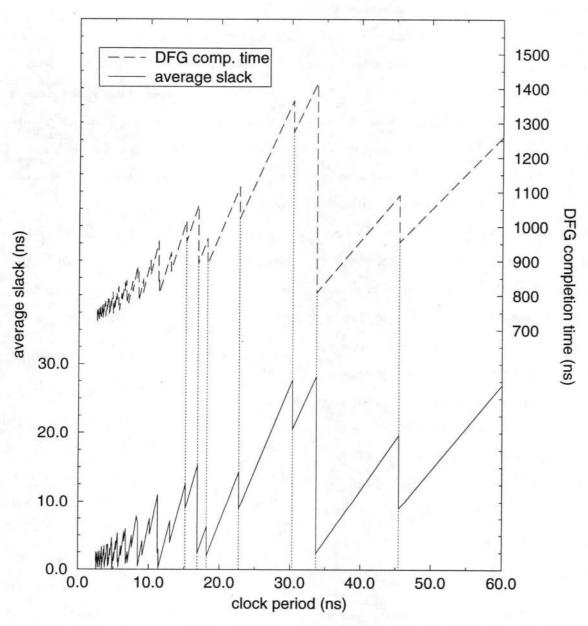

# 7.1 Relation between average slack and DFG completion time

Figure 8 illustrates the correlation between the average clock slack and the execution time for the entire behavior. Using an allocation of two functional units for each operation type, the DFG completion time and the average slack are plotted over a clock range for the fifth order digital elliptical filter[12].

From this figure, we can clearly find the relationship between DFG completion time and the average slack: smaller average slack is associated with shorter

DFG completion time in a range wherever the functions are continuous. This property is true regardless of the behavior being synthesized, the resources allocated, or the scheduler involved. When we shrink the clock period, as long as it doesn't change the number of clock cycles needed to execute each operation type, it doesn't change the number of total clock cycles needed to execute the behavior. Under such conditions, not only is the average slack reduced but the DFG completion time is shortened too. However, when the clock period is shrunk such that it changes the number of clock cycles needed to execute one of the operation types, the clock slack for the operation type will jump up one clock period and consequently the average slack will increase. This accounts for the discontinuous point of the average slack function. At the

Figure 8: Relation between average slack and DFG completion time: using the fifth order elliptical filter as example

same time, owing to the change in the number of clock cycles required to perform an operation of a specific type, it may change the schedule and consequently change the number of total clock cycles required to execute the behavior. Thus, a discontinuous point of the DFG completion time function is also created at the same clock period.

Since there is a strong relationship between the average slack and DFG completion time, the clock period with the smallest average slack is an ideal metric to be used while estimating the clock period that will result in the shortest DFG completion time. Thus, we can obtain the best performance of the design if we select the clock period with the smallest average slack.

Moreover, we can find the clock period that results in the fastest DFG completion time by scheduling the DFG with every clock period at which the average slack function is discontinuous, and then selecting the one with the shortest DFG completion time. According to the properties of Eq.(6) discussed in Section 6, this approach guarantees the optimal solution. However, this approach is impractical, since repetitive scheduling is computationally expensive.

#### 7.2 Benchmark Results

Table 2 shows the experimental results of four benchmarks using three approaches: the maximum-operator-delay method, the slack minimization method, and the optimal clock period. The optimal clock period is found by using exhausted search declared in Section 7.1.

In Table 2, the third column is the clock period selected by each method. The forth column is the average slack computed by Eq.(6). The fifth column is the DFG completion time after we scheduled each benchmarks with the clock period selected by each method. We schedule them with allocating two functional units of each operation type. Finally, the sixth column shows the slow-down factors of two clock estimation methods: the maximum-operator-delay method and the slack minimization method. The slow-down factor is calculated by Eq.(12).

From this table, we can see that the DFG completion time for the clock period selected by the slack minimization method is very close to the DFG completion time for the optimal clock period.

# 7.3 Effects of Varying Allocation

In Table 3, we examine the fact of whether the clock period selected by the slack minimization method can achieve the DFG completion time which is closed to the DFG completion time for the optimal clock period, regardless of the final allocation of functional units used to implement the design. We scheduled the DFG of the fifth order digital elliptical filter[12] with different allocations for the clock period selected by the three approaches and compared their DFG completion time.

Similar to the results in Section 7.2, we can see that the DFG completion time for the clock period selected by the slack minimization method is very close to the DFG completion time for the optimal clock period re-

| example      | clock period<br>selection<br>method | clock<br>period<br>( ns ) | average<br>slack<br>( ns ) | DFG<br>comp.<br>time(ns) | slow<br>down |

|--------------|-------------------------------------|---------------------------|----------------------------|--------------------------|--------------|

| HAL          | max. operator delay                 | 90.900                    | 22.780                     | 363.600                  | 15.3%        |

| differential | slack minimization                  | 3.134                     | 0.212                      | 316.582                  | 0.4%         |

| equation[4]  | optimal clock period                | 2.674                     | 0.322                      | 315.475                  | _            |

| digital      | max. operator delay                 | 90.900                    | 43.741                     | 1454.400                 | 100.7%       |

| elliptic     | slack minimization                  | 3.370                     | 0.021                      | 731.288                  | 0.9%         |

| filter[12]   | optimal clock period                | 2.597                     | 0.048                      | 724.602                  | _            |

| AR           | max. operator delay                 | 90.900                    | 24.514                     | 909.000                  | 5.0%         |

| lattice      | slack minimization                  | 2.597                     | 0.027                      | 916.790                  | 5.9%         |

| filter[10]   | optimal clock period                | 4.784                     | 1.960                      | 865.942                  | _            |

| B-spline     | max. operator delay                 | 90.900                    | 35.200                     | 636.300                  | 81.5%        |

| interpolated | slack minimization                  | 3.370                     | 0.035                      | 353.849                  | 0.9%         |

| filter[13]   | optimal clock period                | 2.597                     | 0.039                      | 350.614                  |              |

Table 2: Result of four benchmarks scheduled with allocating two functional units of each operation type

$$slow\_down = \frac{\text{DFG completion time for the clock estimation method}}{\text{DFG completion time for the optimal clock period}} - 1$$

(12)

| allocated               | clock period         | clock  | DFG      | slow   |

|-------------------------|----------------------|--------|----------|--------|

| resources               | selection            | period | comp.    | down   |

|                         | method               | ( ns ) | time(ns) |        |

| 2 adder                 | max. operator delay  | 90.900 | 1454.400 | 100.7% |

| 2 multiplier            | slack minimization   | 3.370  | 731.288  | 0.9%   |

|                         | optimal clock period | 2.597  | 724.602  | -      |

| 4 adder                 | max. operator delay  | 90.900 | 1272.600 | 84.2%  |

| 2 multiplier            | slack minimization   | 3.370  | 697.588  | 1.0%   |

|                         | optimal clock period | 2.597  | 690.839  | -      |

| 2 adder<br>3 multiplier | max. operator delay  | 90.900 | 1454.400 | 107.4% |

|                         | slack minimization   | 3.370  | 707.698  | 0.9%   |

|                         | optimal clock period | 2.597  | 701.228  | -      |

Table 3: Result of the fifth order elliptical filter scheduled with allocating different number of functional units

gardless of the allocation used for finally implementing the design.

# 8 Conclusion

In this paper, we presented a new approach for clock period selection, based on a clock slack minimization criteria. They provide both designers and synthesis tools with useful method for the clock period selection.

We proved that the longest clock period which produces no slack for the functional units used in each clock cycle, is the extended GCD defined in Section 5.

In some cases, the extended GCD may be too small to be practically implementable. When the extended GCD is not applicable, a method of finding the clock period with the smallest average slack in any given range was presented. Experimental results shows that the DFG completion time for the clock period selected by the method we proposed is very close to the optimal solution.

# References

- [1] D. Gajski, F. Vahid, S. Narayan, and J. Gong, Specification and design of embedded systems. New Jersey: Prentice Hall, 1994.

- [2] D. Gajski, N. Dutt, C. Wu, and Y. Lin, High-Level Synthesis: Introduction to Chip and System Design. Boston, Massachusetts: Kluwer Academic Publishers, 1991.

- [3] M. Balakrishnan and P. Marwedel, "A synthesis approach for design space exploration," in Pro-

- ceedings of the Design Automation Conference, pp. 68-74, 1989.

- [4] P. Paulin, J. Knight, and E. Girzyc, "HAL: A multi-paradigm approach to datapath synthesis," in Proceedings of the Design Automation Conference, 1986.

- [5] P. Paulin and J. Knight, "Algorithms for highlevel synthesis," in *IEEE Design & Test of Com*puters, Dec. 1989.

- [6] R. Walker and R. Camposano, A Survey of High-Level Synthesis Systems. Kluwer Academic Publishers, 1991.

- [7] M. McFarland and T. Kowalski, "Incorporating bottom-up design into hardware synthesis," IEEE Transactions on Computer-Aided Design, September 1990.

- [8] A. Parker, T. Pizzaro, and M. Mlinar, "MAHA: A program for datapath synthesis," in *Proceedings* of the Design Automation Conference, 1986.

- [9] N. Park and A. Parker, "Synthesis of optimal clocking schemes," in *Proceedings of the Design* Automation Conference, 1985.

- [10] R. Jain, M. Mlinar, and A. Parker, "Area-time model for synthesis of non-pipelined designs," in Proceedings of the International Conference on Computer-Aided Design, 1988.

- [11] VLSI Technologies Inc., VDP100 1.5 Micron CMOS Datapath Cell Library, 1988.

- [12] S. Kung, H. Whitehouse, and T. Kailath, VLSI and Modern Signal Processing. Prentice-Hall, 1985.

- [13] D. Pang and L. Ferrari, "Unified approach to general IFIR filter design using the B-spline function," in Proceedings of Asilomar Conference on Signals, Systems & Computers, 1989.

- [14] L. Ramachandran and D. Gajski, "Behavioral design assistant (bda) user's manual." UC Irvine, Dept. of ICS, Technical Report 94-36,1994.

- [15] VLSI Technologies Inc., 0.8-Micron Datapath Library (VCC4DP3), 1992.