## **Aalborg Universitet**

### An Overview of Capacitive DC-Links-Topology Derivation and Scalability Analysis

Wang, Haoran; Wang, Huai; Zhu, Guorong; Blaabjerg, Frede

Published in:

I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2019.2920257

Publication date: 2020

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA): Wang, H., Wang, H., Zhu, G., & Blaabjerg, F. (2020). An Overview of Capacitive DC-Links-Topology Derivation and Scalability Analysis. *I E E Transactions on Power Electronics*, *35*(2), 1805-1829. [8727513]. https://doi.org/10.1109/TPEL.2019.2920257

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: August 28, 2022

# An Overview of Capacitive DC Links-Topology Derivation and Scalability Analysis

Haoran Wang, Member, Huai Wang, Senior Member, IEEE, Guorong Zhu, Senior Member, IEEE, and Frede Blaabjerg, Fellow, IEEE

Abstract—Capacitive DC links are widely used in Voltage Source Converters (VSC) for power balance, voltage ripple limitation, and short-term energy storage. A typical solution which uses Aluminum Electronic Capacitors (E-cap) for such applications is assumed to be one of the weakest links in power electronic systems, therefore, also becoming one of the lifetime bottlenecks of power electronic systems. Various passive and active capacitive DC-link solutions have been proposed intending to improve the reliability of the DC links qualitatively, making great effort to diverting the instantaneous pulsating power into extra reliable storage components. In this publication, a generic topology derivation method for single-phase power converters with active capacitive DC link integrated has been proposed, which can derive all existing topologies, and identify a few new topologies. According to the synthesis results, the main achievements in research on capacitive DC-link solutions are reviewed and presented chronologically as well as thematically ordered. Further more, the reliabilityoriented design procedure is applied to size the chip area of active switching devices and the passive components to fulfill a specific lifetime target and system specification, as well as compare the overall capacitive energy storage, energy buffer ratio, and the cost of different solutions. The cost comparisons are performed with a scalable lifetime target and power rating. It reveals that different conclusions can be drawn with different lifetime targets in terms of cost-effectiveness.

#### I. INTRODUCTION

Capacitive DC links are widely used in Voltage Source Converters (VSC) for power balancing, voltage ripple limitation, and short-term energy storage. E-cap bank is the good candidate to buffer the pulsating power between the DC and AC side in industry applications due to their relatively high

This work was supported by the Innovation Fund Denmark through the Advanced Power Electronic Technology and Tools Project and the National Natural Science Foundation of China under Grant (No. 51777146).

Partial results of this manuscript have been presented at the IEEE Energy Conversion Congress and Exposition (ECCE) 2016 and IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia) 2016, sponsored by power electronics society.

Haoran Wang, Huai Wang and Frede Blaabjerg are with Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (hao@et.aau.dk, hwa@et.aau.dk and fbl@et.aau.dk)

Guorong Zhu is with School of Automation, Wuhan University of Technology, China (zhgr\_55@whut.edu.cn).

energy density and low cost [1]. However, because of the significant Equivalent Series Resistance (ESR) in the capacitor, the ripple current flowing pass will introduce higher thermal stress which will accelerate the degradation process of the E-cap. They are assumed to be one of the weakest links in power electronic systems, and therefore also becoming one of the lifetime bottlenecks in power electronic systems [2–5].

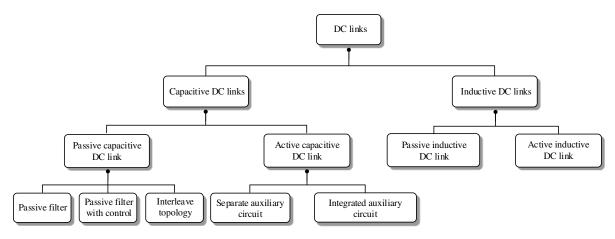

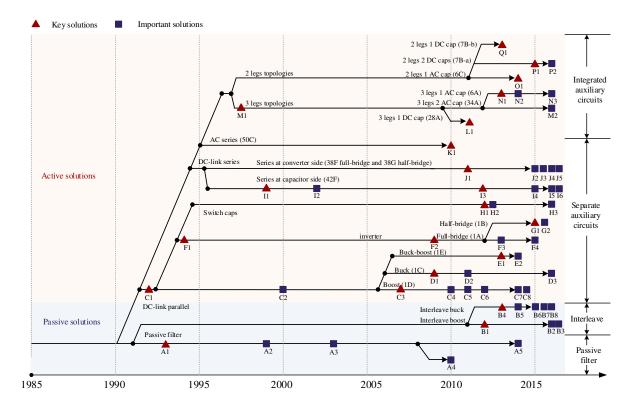

Research efforts have been made to either reduce the capacitor ripple current stresses or relaxing the required DClink capacitances. The different categories of the capacitive DC links is shown in Fig. 1, and can be classified into passive and active solutions. Passive capacitive DC-link solutions include passive filters (e.g., additional resonant passive filter to absorb the ripple) [6–12], the control strategies for two stage capacitive DC-link systems, which is relied on a specific relationship in the operating frequency between the converters connected, and the interleave structures based passive filter control methods [13-28]. Active capacitive DC links introduce the additional separate circuit to the existing DC-link. Therefore, extra circuit paths including separate auxiliary circuit and integrated auxiliary circuit are provided to process the pulsating power, which otherwise would be fully processed by the DC-link capacitors. The separate auxiliary circuit could be DC-DC converter [29-52], DC-AC converter [53-65], or other structures [66-92] The integrated auxiliary circuits are novel single-phase topologies with integrating the active DC link, such as [93–114].

Recently, some review papers have been published to make an overview and comparisons on these capacitive DC links. [115] reviews the power decoupling techniques to release DC links for micro-inverters in PV (Photovoltaics) application qualitatively and it is mainly focusing on the isolated topologies. Different from that, from the aspect of development and construction laws of power decoupling topologies, [116] reviews the topologies with integrated active DC link in both current source and voltage source converter. It classified these solutions into independent and dependent topologies and found out several independent topologies can be derived from dependent topologies by sharing the common switches and passive components. The latest publication [117] presents a comprehensive overview which covers the isolated and nonisolated cases, voltage and current source, and considering control and circuits. While the review papers on the active DC links have the above potential benefits, there are the following limitations of the existing studies on active capacitive DC-links

1) Even though [115], [116], and [117] have reviewed and

2

- 2) There is still a lack of quantitative reliability analysis of the system with active DC link. The reliability improvement of the DC-link capacitor itself (i.e., by reducing its ripple current stress or replacement by a more reliable alternative) does not necessarily imply the improvement of the overall system, since active switches and other components are added with the active capacitive DC links. The lifetime of other components may therefore be changed.

- 3) It is still an open question to conclude, which active capacitive DC link is the most promising one. Existing comparative studies are based on either the number of components used, different case studies, or different criteria to size the components [115–117]. No assessment of the existing active capacitive DC links based on a specific case is done for a given lifetime target and the same component sizing criteria.

In order deeply to investigate the original ideas of these capacitive DC-link solutions, this paper proposes a generic topology derivation method to synthesis single-phase converter with integrated auxiliary circuit, which can review all the existing single-phase topologies with active DC link integrated [118]. Based on the synthesis results, the main achievements in research on capacitive DC-link solutions are reviewed and presented chronologically and thematically ordered, so as to clearly understand the development trend of the capacitive DClink solutions. Moreover, an assessment approach of active capacitive DC links is proposed based on the overall cost of the respective solution to fulfill the same specifications in terms of functionality and lifetime [119]. The methods studied will be also applicable also to three-phase systems with unbalanced grids or loads [120] (i.e., there will be lowfrequency harmonics, requiring large size capacitors).

The structure of this paper is as follows: Section II discusses the generic topology derivation method and the cases studied, followed by the summary of the main achievements in Section III. Section IV presents the proposed cost-benchmarking based on a reliability-oriented component sizing procedure; then, the cost-benchmarking and scalability analysis are presented in Section V. The performance factors assessment is shown in Section VI, followed by the conclusions in Section VII.

# II. GENERIC TOPOLOGY DERIVATION METHOD FOR SINGLE-PHASE CONVERTER WITH CAPACITIVE ACTIVE DC LINKS

Through the power flow analysis, four general structures for decoupling the pulsating power at AC and DC sides can be obtained to provide an additional power flow path from the main circuit to the active energy storage elements. Based on the general structures, four synthesis modes to combine the main circuit and auxiliary circuit are presented, followed by enumerating all the possible topologies. In order to reduce the component count, the main circuit and the active capacitive DC-link circuit could share common elements in some of the derived topologies, which will be discussed later with examples.

#### A. Power Flow Analysis

The AC voltage  $v_{\rm ac}(t)$  and current  $i_{\rm ac}(t)$  are assumed to be sinusoidal with unity power factor, as shown in the following equations

$$v_{\rm ac}(t) = V_{\rm m} \sin(\omega t) \tag{1}$$

$$i_{\rm ac}(t) = I_{\rm m} \sin(\omega t)$$

(2)

where  $V_{\rm m}$  and  $I_{\rm m}$  are the amplitude of AC voltage and current, respectively; and  $\omega$  is the supply angular frequency. Limit in the discussion to low-frequency harmonics, the power of the AC side can be expressed as follows:

$$p_{\rm ac}(t) = v_{\rm ac}(t)i_{\rm ac}(t) = \frac{V_{\rm m}I_{\rm m}}{2} - \frac{V_{\rm m}I_{\rm m}}{2}\cos(2\omega t)$$

(3)

There are two parts in (3), the first part is the DC power supplied by the DC source  $P_{\rm dc}$  and the second part is the instantaneous unbalanced power  $p_{2\omega}(t)$  which needs a storage component to buffer, such as inductor, capacitor and source (battery).

- Capacitor: Such as film capacitor and ceramic capacitor, which is widely used for power decoupling because of the great current capability [3].

- Inductor: Magnetic components are much more reliable and feature low failure rates that are more than one order of magnitude lower than those of the other power devices. But the high power loss and large volume/weight limit its extensive use [2].

- Source: Battery can also be used for power decoupling and long hold-up time support.

Focus in this paper is on the capacitor as the energy storage element in order to buffer the pulsating power. Inductor and battery as storage component can replace the film capacitor for specific DC-link applications with similar design procedure, which is not discussed in this paper.

For passive capacitive DC links, E-caps are usually used to filter low-frequency ripple current components, and additional capacitors with higher resonant frequency (e.g., film capacitors, ceramic capacitors) are usually used to assist the filtering of the high-frequency ripple current components. The one used for low-frequency ripple current filtering is the dominant one in terms of capacitance. An alternative solution is to use single-type of capacitors, such as film capacitors, or ceramic capacitors to filter both low-frequency and high-frequency ripple current components. For active DC-link solutions, additional active circuits (or modulation schemes) are mainly used to supply or absorb low-frequency power components due to the limitation of controller bandwidth. Capacitors for high-frequency ripple components filtering are still required in the DC link of the power electronic converter.

#### B. General Structure

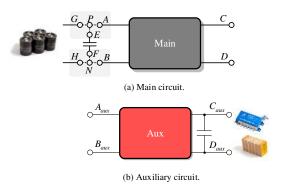

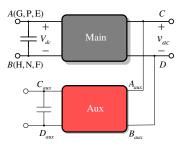

Fig. 2 defines the terminals of the main circuit of a single-phase power converter and the auxiliary circuit used for the active capacitive DC link. There are ports AB and CD for the main circuits, and  $A_{\rm aux}B_{\rm aux}$  and  $C_{\rm aux}D_{\rm aux}$  for the auxiliary circuits. AB and CD could either be alternating current (AC) or direct current (DC), depending on the applications. For

Fig. 1. Categorization of DC links in power electronic systems.

Fig. 2. Basic module for the main circuit and the auxiliary circuit.

illustration, Fig. 2 shows an inverter application case. EF and GH are the terminals of the DC-link capacitor and the input of the main circuit, respectively. Typically, without any auxiliary circuit, G, E, A are connected to P and the same to the terminal H, F, B, N.

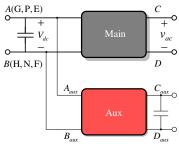

By analyzing the possible flowing paths of the pulsating power, the general structures for a single-phase system with an auxiliary circuit can be divided into four types: DC series, DC parallel, AC series, and AC parallel.

1) DC Series: In the DC series structure, the auxiliary circuit and the main circuit are connected in series at the DC side in order to compensate the voltage distortion of the DC-link capacitor. From the basic module shown in Fig. 2, it can be seen that there are three ways to connect the auxiliary circuit in series with the DC port of the main circuit. Taking the positive side terminals as an example, the three connected locations are PA at converter side, PE at the capacitor side and PG at the input side as shown in Fig. 3 (a), (b) and (c) separately in order to keep each side constant. It is worth to mention that two auxiliary circuits are required at PA and PG if it is necessary to limit the voltage ripples at both the input side and the converter side.

With the responsibility to decouple the unbalanced power, the auxiliary circuit can either be the AC/DC, which contains only AC component at the  $A_{\rm aux}B_{\rm aux}$  or the DC/DC and DC/AC converter which contain both DC and AC components.

In such AC/DC auxiliary circuit application, the voltage across  $A_{\rm aux}B_{\rm aux}$  has the inverse ripple component of the DC-link capacitors in single-phase system, so the average DC-link voltage of the single-phase system is constant. However, in DC/DC and DC/AC applications, except for an AC component, there will be a DC component in the  $A_{\rm aux}B_{\rm aux}$  port of auxiliary circuit.

- 2) DC Parallel: This structure inserts an auxiliary circuit connected in parallel to the DC-link capacitors, which will introduce a new flowing path for the ripple current at the DC link. The voltage of the input port  $A_{\rm aux}B_{\rm aux}$  of the auxiliary circuit is clamped by the DC link. Thus the auxiliary circuit can be DC/AC or DC/DC converters with a DC input. Terminal G, E, A are connected to P and the same to the terminal H, F, B, N as defined in Fig. 3 (d).

- 3) AC Series: The auxiliary circuit is connected in series with the AC side of the main circuit, as shown in Fig. 3 (e).

- 4) AC Parallel: The auxiliary circuit is connected in series with the AC side of the main circuit. It has the similar function as an active power filter in order to eliminate the harmonics at the AC side. The voltage of the  $A_{\text{aux}}B_{\text{aux}}$  port is clamped by the AC voltage of the main circuit. Thus the topologies of the auxiliary circuit is AC/DC as shown in Fig. 3 (f).

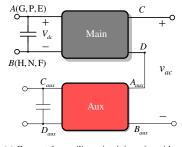

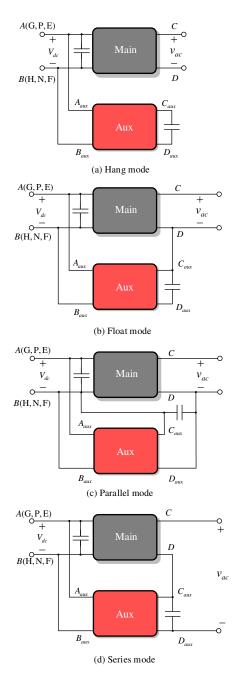

#### C. Synthesizing from General Structures

The original cells for a single-phase system with active capacitive DC links are the main circuit and the auxiliary circuit. In order to reduce the component count and derive more possible topologies with active capacitive DC-links, a topology synthesis which links the output terminals of the auxiliary circuit to the main circuit is presented. Because of some novel connections for power flowing, more possibilities to share the common cells for higher power density will be provided. Following the general structure for single-phase system with the auxiliary circuit integrated presented above, four kinds of synthesis modes are presented in Fig. 4 and this can be used for the topology derivation:

- 1) Hang mode: Hang up the  $C_{\text{aux}}D_{\text{aux}}$  port without any connection;

- 2) Float mode: Connect one terminal of the energy storage element to one of the terminals of the main circuit;

(a) Connect the auxiliary circuit in series with the (b) Connect the auxiliary circuit in series with the DC side of the main circuit (Converter side). DC side of the main circuit (Capacitor side).

B(H, N, F)

(c) Connect the auxiliary circuit in series with the DC side of the main circuit (Input side).

- (d) Connect the auxiliary circuit in parallel with the DC side of the main circuit.

- (e) Connect the auxiliary circuit in series with the AC side of the main circuit.

- (f) Connect the auxiliary circuit in parallel with the AC side of the main circuit.

Fig. 3. Structure diagrams of the auxiliary circuit connected with the main circuit.

- 3) Parallel mode: Connect two terminals of the energy storage element and two terminals of the main circuit together;

- 4) Series mode: Link the energy storage element in series with one of the terminals of the main circuit.

#### D. Topology Simplification

B(H, N, F)

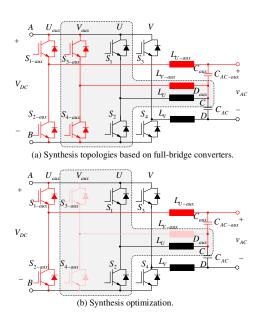

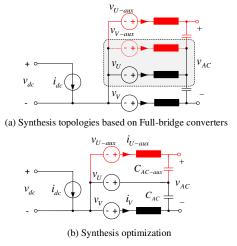

The objective of the topology simplification is to reduce the component count in synthesis structure. An example to illustrate the simplification procedure can be seen in Fig. 5 and Fig. 6. The black and red line are the main circuit and auxiliary circuit, respectively. The dashed line is shared by a common cell. A step-by-step topology simplification procedure is discussed as follows:

- 1) First, the full-bridge inverter as the main circuit with another full-bridge inverter as the auxiliary circuit are taken as an example.  $A_{\text{aux}}B_{\text{aux}}$  port of the auxiliary circuit parallelled with the DC link of the main circuit and  $C_{\text{aux}}D_{\text{aux}}$  port series with one of AC terminals of main circuit are used in this example, as shown in Fig. 4 (d).

- 2) The topology has four legs as shown in Fig. 5. Each switching leg generates a square-wave voltage from the DC link. From the average model shown in Fig. 6, it can be seen that the legs  $V_{\mathrm{aux}}$  and U have the same structure and the common DC-link input and output terminals  $CD_{\mathrm{aux}}$ .

- 3) Merge the leg  $V_{\rm aux}$  into the leg U of the main circuit. The common switching cells and filter inductors can be shared by the main circuit and the auxiliary circuit.

- 4) The AC port voltage of the single-phase conversion system is not the AC voltage of main circuit, but the sum of the output voltages of the main circuit and the auxiliary circuit. Thus, the modulation strategy for the single-phase system must

be changed, where the difference between the middle voltages of the leg  $U_{\text{aux}}$  and leg V is the AC voltage of the single-phase system.

A more general description of the topology simplification from the aforementioned analysis is as follows:

- 1) Select two topologies with one of the general structures to establish an additional power flow path for the pulsating

- 2) Check the possibility to share components (e.g., bridge legs) between the main circuit and the auxiliary circuit;

- 3) If it is applicable, integrate the components that can be shared by the main circuit and the auxiliary circuit;

- 4) Exclude the circuit topologies that do not work in principle;

- 5) Check the controllability for single-phase conversion and rebuild the modulation strategy to ensure the circuit are fully controllable.

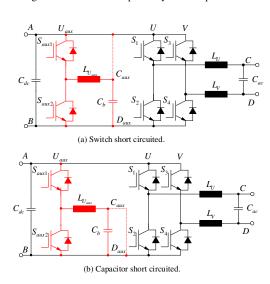

It should be noted that some topologies derived from the synthesis method do not work in principle. Two examples are shown in Fig. 7. In Fig. 7 (a), when connect terminal A and  $C_{\rm aux}$ , the energy storage element is connected in parallel with the DC link directly. The voltage of the capacitor cannot be controlled by the power semiconductors in the auxiliary circuit. Moreover, the inductor in the auxiliary circuit is a filter inductor, which has limited energy storage capability, so the  $S_{\text{aux}1}$  is short circuited. In Fig. 7 (b), the terminal  $C_{\text{aux}}$  and B are connected, which makes the energy storage capacitor short circuit.

#### E. Topology Synthesis Cases

Following the proposed topology synthesis process, the fullbridge is taken as an example for the main circuit topology.

Fig. 4. Synthesis modes for the DC parallel case shown in Fig. 3 (d).

Full-bridge, half-bridge, buck, boost and buck-boost converters are taken as the auxiliary circuits connected in parallel or series at the DC or AC side. The synthesis results of the DC parallel, DC series, AC parallel and AC series are shown below separately.

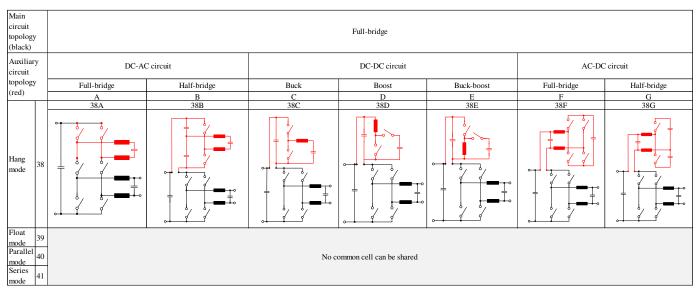

1) DC parallel: The synthesis results of the DC parallel cases are shown in Table I. There exist 20 derived topologies excluding the ones that do not work in principle. Actually, the half-bridge inverter as the main topology with these auxiliary circuits have also been taken into account, and all the topologies with component reduced have been included in the above examples.

As there are common cell in parallel with the DC link,

Fig. 5. Example of synthesis optimization based on full-bridge converters.

Fig. 6. Average model of the example of synthesis optimization.

Fig. 7. Two topology examples that do not work following the principle in synthesis procedure.

$\label{eq:table_interpolation} TABLE\ I$  Synthesis results with DC parallel mode.

| Main          | circuit topology                                                                         | /        |                                              |                                              | Full-bridge                                  |                                              |                                              |  |

|---------------|------------------------------------------------------------------------------------------|----------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|--|

| Auvilio       | (black)                                                                                  | av       | Full-bridge                                  | Half-bridge                                  | Buck                                         | Boost                                        | Buck-boost                                   |  |

| Auxilia       | ry circuit topolo<br>(red)                                                               | gy       | A                                            | B                                            | C                                            | D D                                          | E E                                          |  |

|               | ()                                                                                       |          | 1A                                           | 1B                                           | 1C                                           | 1D                                           | 1E                                           |  |

| Hang<br>mode  |                                                                                          | 1        |                                              |                                              |                                              |                                              |                                              |  |

|               | A-C <sub>aux</sub><br>A-D <sub>aux</sub>                                                 | 2        | swtich short circuit<br>swtich short circuit | cap short circuit<br>swtich short circuit    | swtich short circuit<br>1C                   | swtich short circuit<br>1D                   | swtich short circuit<br>1E                   |  |

|               | B-C <sub>aux</sub>                                                                       | 4        | swtich short circuit                         | cap short circuit                            | swtich short circuit                         | swtich short circuit                         | swtich short circuit                         |  |

|               | B-D <sub>aux</sub>                                                                       | 5        | swtich short circuit                         | swtich short circuit                         | 1C                                           | 1D                                           | 1E                                           |  |

| Float<br>mode | C-C <sub>aux</sub>                                                                       | 6        | 6A                                           | 68                                           | 6C                                           | swtich short circuit                         | swtich short circuit                         |  |

|               | C-D <sub>aux</sub>                                                                       | 7        | 6A                                           | 7B-a 7B-b                                    | IC                                           | ID                                           | ΙE                                           |  |

|               | D-C <sub>aux</sub>                                                                       |          |                                              | 6B                                           | 6C                                           | swtich short circuit                         | swtich short circuit                         |  |

|               | D-D <sub>aux</sub>                                                                       |          |                                              | 7B                                           | 1C                                           | 1D                                           | 1E                                           |  |

|               | A-C <sub>aux</sub> , B-D <sub>aux</sub>                                                  | 10<br>11 | swtich short circuit                         | cap short circuit                            | swtich short circuit                         | swtich short circuit                         | swtich short circuit                         |  |

|               | A-C <sub>aux</sub> , C-D <sub>aux</sub><br>A-C <sub>aux</sub> , D-D <sub>aux</sub>       | 12       | swtich short circuit<br>swtich short circuit | cap short circuit cap short circuit          | swtich short circuit<br>swtich short circuit | swtich short circuit<br>swtich short circuit | swtich short circuit<br>swtich short circuit |  |

| Parallel      | B-C <sub>aux</sub> , A-D <sub>aux</sub>                                                  | 13       | swtich short circuit                         | cap short circuit                            | swtich short circuit                         | swtich short circuit                         | swtich short circuit                         |  |

| mode          | B-C <sub>aux</sub> , C-D <sub>aux</sub>                                                  | 14       | swtich short circuit                         | cap short circuit                            | swtich short circuit                         | swtich short circuit                         | swtich short circuit                         |  |

|               | B-C <sub>aux</sub> , D-D <sub>aux</sub>                                                  | 15       | swtich short circuit                         | cap short circuit                            | swtich short circuit                         | swtich short circuit                         | swtich short circuit                         |  |

|               | C-C <sub>aux</sub> , A-D <sub>aux</sub><br>C-C <sub>aux</sub> , B-D <sub>aux</sub>       |          |                                              | swtich short circuit<br>swtich short circuit | swtich short circuit<br>6C                   | swtich short circuit<br>swtich short circuit | swtich short circuit<br>swtich short circuit |  |

|               | C-C <sub>aux</sub> , B-D <sub>aux</sub> 17<br>C-C <sub>aux</sub> , D-D <sub>aux</sub> 18 |          | swtich short circuit                         | 7B                                           | swtich short circuit                         | swtich short circuit                         | switch short circuit                         |  |

|               | D-C <sub>aux</sub> , A-D <sub>aux</sub> 19                                               |          | swtich short circuit                         |  |

|               | D-C <sub>aux</sub> , B-D <sub>aux</sub>                                                  | 20       | swtich short circuit                         | swtich short circuit                         | 6C                                           | swtich short circuit                         | swtich short circuit                         |  |

|               | D-C <sub>aux</sub> , C-D <sub>aux</sub>                                                  | 21       | swtich short circuit                         | 7B                                           | swtich short circuit                         | swtich short circuit                         | swtich short circuit                         |  |

|               | A-C <sub>aux</sub> , P-D <sub>aux</sub>                                                  | 22       | swtich short circuit                         |  |

|               | A-D <sub>aux</sub> , P-C <sub>aux</sub><br>B-C <sub>aux</sub> , N-D <sub>aux</sub>       | 23<br>24 | swtich short circuit<br>swtich short circuit |  |

|               | D Caux, IV Daux                                                                          | 24       | switch short circuit                         | switch short circuit                         | 25C                                          | 25D                                          | 25E                                          |  |

|               | B-D <sub>aux</sub> , N-C <sub>aux</sub> 2:                                               |          | swtich short circuit                         | swtich short circuit                         |                                              |                                              |                                              |  |

|               | E-Caux, P-Daux                                                                           | 26       | swtich short circuit                         |                                              |                                              | swtich short circuit                         | swtich short circuit                         |  |

|               | E-D <sub>aux</sub> , P-C <sub>aux</sub>                                                  | 27       | swtich short circuit                         | swtich short circuit                         | swtich short circuit                         | swtich short circuit<br>28D                  | swtich short circuit<br>28E                  |  |

| Series        | F-C <sub>aux</sub> , N-D <sub>aux</sub>                                                  | 28       | 8 swtich short circuit swtich short circuit  |                                              | 1B                                           |                                              |                                              |  |

| mode          | F-D <sub>aux</sub> , N-C <sub>aux</sub>                                                  | 29       | swtich short circuit                         |  |

|               | G-C <sub>aux</sub> , P-D <sub>aux</sub><br>G-D <sub>aux</sub> , P-C <sub>aux</sub>       | 30<br>31 | swtich short circuit<br>swtich short circuit |  |

|               | H-C <sub>aux</sub> , N-D <sub>aux</sub>                                                  | 32       | swtich short circuit                         | switch short circuit<br>switch short circuit | 25C                                          | 25D                                          | swtich short circuit<br>25E                  |  |

|               | H-D <sub>aux</sub> , N-C <sub>aux</sub>                                                  | 33       | swtich short circuit                         |  |

|               | C-Caux 34                                                                                |          | 34A                                          | 34B                                          | swtich short circuit                         | swtich short circuit                         | swtich short circuit                         |  |

|               | C-D <sub>aux</sub>                                                                       |          |                                              | swtich short circuit                         | swtich short circuit                         | swtich short circuit                         |                                              |  |

|               | D-C <sub>aux</sub><br>D-D <sub>aux</sub>                                                 | 36<br>37 | 36A<br>37A                                   | 35B<br>35B                                   | swtich short circuit                         | swtich short circuit                         | swtich short circuit                         |  |

|               | D-D <sub>aux</sub>                                                                       | 3/       | 3/A                                          | 358                                          | swtich short circuit                         | swtich short circuit                         | swtich short circuit                         |  |

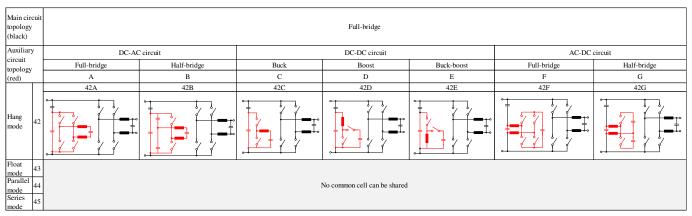

TABLE II

SYNTHESIS RESULTS WITH DC SERIES MODE.

(a) Connect the auxiliary circuit in series with the DC side of the main circuit (Converter side).

(b) Connect the auxiliary circuit in series with the DC side of the main circuit (Capacitor side).

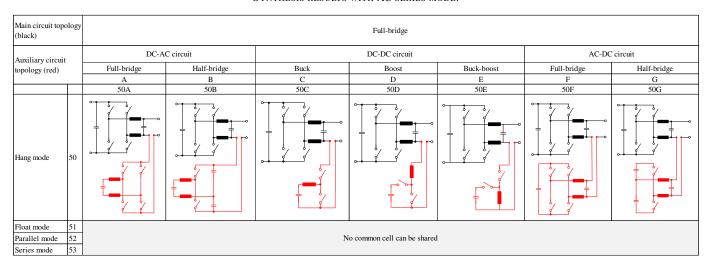

TABLE III

SYNTHESIS RESULTS WITH AC PARALLEL MODE.

| Main circuit<br>topology (blac                | k)  | Full-bridge                  |             |  |  |  |

|-----------------------------------------------|-----|------------------------------|-------------|--|--|--|

| Auxiliary circu                               | iit | Full-bridge                  | Half-bridge |  |  |  |

| topology (red)                                |     | A                            | В           |  |  |  |

|                                               |     | 46A                          | 46B         |  |  |  |

| Hang mode                                     | 46  |                              |             |  |  |  |

| Float mode 44 Parallel mode 44 Series mode 44 |     |                              |             |  |  |  |

|                                               |     | No common cell can be shared |             |  |  |  |

|                                               |     |                              |             |  |  |  |

most of the existing topologies mentioned in recent papers are belonging to this synthesis mode. As shown in Table I, the topologies 1A, 1B, 1C, 1D, and 1E include a full-bridge converter [53], a half-bridge converter [60], a buck converter [44], a boost converter [35], and a buck-boost converter [50] as the auxiliary circuit connected in parallel with the DC link, respectively. Some topologies can share the common cell between the main circuit and the auxiliary circuit, such as 6A [95], 7B [112], 6C [111] and 34A [93]. All of these typical topologies will be evaluated in following section.

2) DC series: For the converter side cases, the synthesis results can be seen in Table II (a). When the auxiliary circuit is DC/AC or DC/DC topology, besides an AC component, there will be a DC component in  $A_{\rm aux}B_{\rm aux}$ , which will lower the voltage utilization ratio of the main circuit. Here, the five auxiliary circuits with DC input are taken as examples to derive the topologies as presented in Table II. By sharing the common cells at the DC link, the topology 38A can be derived, which has been proposed in [105]. When the auxiliary circuit

TABLE IV

SYNTHESIS RESULTS WITH AC SERIES MODE.

is AC/DC topology, the voltage of  $A_{\rm aux}B_{\rm aux}$  has the inverse voltage waveform with the ripple component of the DC-link capacitor, in order to achieve a constant DC-link voltage. The full-bridge inverter for main circuit and the full-bridge and half-bridge converters for auxiliary circuits are taken as examples to synthesis single-phase topology with integrated active DC link.

Except for the hang up mode, no more single-phase topology with integrated auxiliary circuits can be obtained, because there is no common cell that can be shared at the DC link. Similar synthesis results can be found for capacitor side cases as shown in Table II (b).

- 3) AC parallel: In this case, the auxiliary circuit is connected in parallel with the AC side of the single-phase inverter [121]. The derived topologies are shown in Table III. Because no common cell can be shared, no more novel topologies can be derived.

- 4) AC series: Different from the above three modes whose AC side votlage is CD, the AC voltage of the conversion system becomes the sum of CD and  $A_{\rm aux}B_{\rm aux}$ . The derived topologies are shown in Table IV with a full-bridge inverter as the main circuit and various auxiliary circuits. In this section, the output voltage of the main circuit contains other AC or DC components besides the fundamental component. Thus, the CD port of the main circuit is different from the traditional one. The auxiliary circuit could be AC/DC topologies or DC/DC (DC/AC) topologies. One of the cases proposed in [91] connects a buck converter in series with the AC side, while the topology and modulation strategy for the main circuit need to be changed.

# III. MAIN ACHIEVEMENTS OF CAPACITIVE DC-LINK RESEARCH

In the academic community, research on the capacitive DC-link design has been performed for more than two decades and is still very popular, given the number of papers published on this topic every year. The solutions to eliminate  $p_{2\omega}(t)$

from DC and AC side can be divided into two categories: the passive solutions and active solutions as shown in Fig. 1, which depends on whether an additional auxiliary circuit is needed or not. The main achievements in capacitive DC-link research are shown in Fig. 8 chronologically as well as thematically. Key solutions indicate novel topologies or concepts and important solutions represent contributions of control and optimization for different applications, which are based on the key solutions. According to the summary of the main achievements is presented in Table. V. The first two categories are passive solutions which includes passive filter and interleave structure. The other two categories are active solutions which includes separate auxiliary circuit and integrated auxiliary circuit.

# IV. COMPONENT SIZING PROCEDURE FOR BENCHMARKING OF CAPACITIVE DC-LINK SOLUTIONS

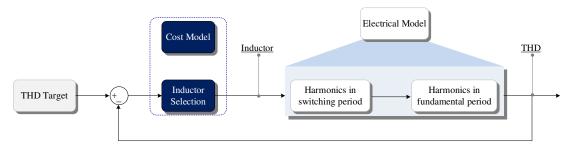

In order to keep same specification to existing solutions for benchmarking, a reliability-oriented design procedure is incorporated to size the capacitor and power semiconductor considering the same operating performance and lifetime target. For the inductor, Total Harmonic Distortion (THD) is considered to size the inductor.

#### A. Capacitor

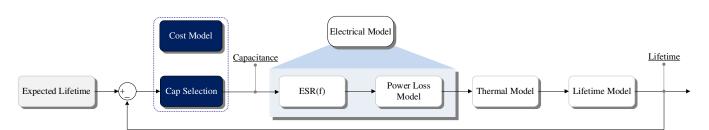

The reliability-oriented procedure to size the capacitors is shown in Fig. 9.

1) Expected Lifetime Definition: The selection of either Ecaps or film capacitors should fulfill the lifetime requirement of the overall power conversion system. It should be mentioned that it is possible to select proper E-caps to achieve different lifetime targets by derating the operation conditions. Therefore, in principle, lifetime itself is not the determining factor to decide which type of capacitors that can be used. By considering the respective advantages of E-caps and film capacitors, the type of capacitors selected in the case studies is as follows: E-caps are used for the DC-link capacitor  $C_{\rm dc}$

- A1. K. Toyama, T. Takeshita et al, LC resonant, 1993.

- A2. D. C. Hamill and P. T. Krein et al, saturable inductor, 1999.

- A3. J. C. Das, passive filter, 2003.

- A4.S. Y. Hui, et al, Passive Offline LED Driver 2010.

- A5. M. Vasiladiotis and A. Rufer, control for resonant filters, 2014.

- B1. G. R. Zhu, S.C. Tan et al, inverterleave boost, 2012.

- B2. D. B. W. Abeywardana,et al, closed-loop control for boost, 2016.

- B3. D. B. W. Abeywardana, et al, consider component tolerances, 2016. B4. I. Serban, invterleave buck, 2013.

- B5. S. Li, S. Y. Hui, et al, general interleave, 2014.

- B6. I. Serban et al, grid connected with power decoupling, 2015 B7. W. Yao, F. Blaabjerg et al, close-loop control for buck, 2016

- B8 W. Yao, F. Blaabjerg et al, robust control scheme, 2016.

- C1. H. Irie, T. Yamashita et al, 2-quadrant chopper, 1992.

- C2. Garcia, M. D. Martinez-Avial et al, harmonic reducer review, 2000. C3. A. C. Kyritsis, E. C. Tatakis, boost buffer, 2007.

- C4. M. Jang and V. G. Agelidis, battery storage, 2010.

- C5. S. Wang, X. Ruan et al, E-cap free in LED, 2011.

- C6. M. Jang, and V. Agelidis, Fuel cell system for grid connected, 2012.

- C7. W. Cai, S. Duan, et al, virtual capacitor for high efficency, 2014. C8. Y. Yang, X. Ruan, et al, Feed forward for all the harmonics, 2014.

- D1. R. Wang, F. Wanget al, buck buffer with high power density, 2009. D2. H. Li, K. Zhang, et al, continuous control, 2011.

- D3. Z. Kong, K. Zhang, et al, buck buffer for MMC submodule 2016.

- E1. K. W. Lee, T. J. Liang, et al, buck-boost buffer, 2013..

- E2. X. Cao, Q. C. Zhong, improve stability, 2014

- F1. Y. Wang, DC shunt active filter, 1994.

- F2. P. T. Krein, R. S. Balog. Three port for power decoupling, 2009.

- F3. Chi Jin, Peng Wang, et al, APF application, 2013.

- F4. Y. Tang, F. Blaabjerg et al, PQ control for power decoupling, 2015.

- G1. Y. Tang, F. Blaabjerg et al, half bridge buffer, 2014.

- G2. Y. Tang, F. Blaabjerg et al, closed-loop control, 2014.

- H1. M. Chen, K. K. Afridi et al, Stacked switched capacitor, 2012.

- H2. K. Afridi, and D. J. Perreault, Enhanced bipolar stacked, 2012.

- H3. C. McHugh et al, high power density implementation, 2016.

- II. T. Tanaka and S. Funabiki, full-bridge series with cap as dc-link, 1999.

- I2. T. Tanaka, S. Fujikawa and S. Funabiki, controller for buffer structure, 2002.

- 13. Kuang Li, Jinjun Liu, et al, application for harmonics 2006.

- S. Oin, buffer sizing and design, 2015.

- 15. V. Michal, buck buffer with dc link cap in series. 2016.

- 16. H. Wang and H. Wang. Two terminal DC-link series module, 2017.

- J1.H. Wang, H. S. H. Chung et al, series rectifier, 2011.

- J2. W. Liu, H.S.H.Chung et at, modelling and control, 2015.

- J3. Y. Qiu, Y. F. Liu et al, in LED system, 2015.

- J4. V. S. P. Cheung, H. Chung et al, scalable multiparallel, 2016.

- J5. X. Lyu, D. Cao et al, in series and in parallel buffer, 2016.

- K1. B. J. Pierquet and D. J. Perreault, series converter at ac side, 2010.

- L1. X. Liu, P. Wang et al, series inverter, 2011.

- M1. T. Shimizu et al, three legs 2 ac caps topolog, 1997.

- M2. G. Zhu, H. Wang et al, AC power decoupling 2016.

- N1. H. Li, K. Zhang et al, three legs 1 ac caps topology, 2013.

- N2. R. Chen, F. Z. Peng, modulation to reduce current stress, 2014.

- N3. H. Wu, S.-C. Wong, inductor optimization, 2016.

- O1. Q. Wenlong, W. Hui, 2 legs with an ac cap, 2014

- P1. Y. Tang and F. Blaabjerg, 2legs with 2 dc caps, 2015.

- P2. S. Li, S.-C. Tan et al, modeling and controller design, 2016.

- Q1. W. Cai, S. Duan et al, 2 legs boost inverter, 2013

Fig. 8. Main achievements in capacitive DC-link research.

Fig. 9. Capacitor reliability-oriented design to fulfill certain specification.

TABLE V

MAIN ACHIEVEMENTS SUMMARY.

| Category                                | No | Туре                | Features                                                              | Limitation                                  | Reference    |

|-----------------------------------------|----|---------------------|-----------------------------------------------------------------------|---------------------------------------------|--------------|

| Passive filters                         | A1 | Topology            | LC resonant filter for low-frequency                                  | Parameter variaration and large volume      | [6]          |

| (Easy to be                             | A2 | Topology            | Adjust the resonant frequency                                         | Large volume                                | [7]          |

| implemented                             | A3 | Topology            | Review kinds of passive filter for DC-link                            | Parameter variaration and large volume      | [8]          |

| becuase of no active<br>devices inside) | A5 | Topology<br>Control | Passive component only Controller design consider the DC-link filter  | High harmonics introduced                   | [10]<br>[12] |

| devices filside)                        | B1 | Topology            | Inverter is boost and without large E-cap                             | High voltage stress for all components      | [13]         |

|                                         | B2 | Control             | Controller design for better dynamic performance                      | riigh voltage stress for all components     | [27]         |

| Interleave structure                    |    | Control             | Controller design consider tolerance                                  |                                             | [28]         |

| (Topology born with                     | B4 | Topology            | Full bridge structure is easy to be implemented                       | Low modulation index                        | [15]         |

| power decoupling                        | B5 | Control             | Different structure with current waveform control                     |                                             | [17]         |

| capability)                             | B6 | Application         | Consider grid code and component sizing                               |                                             | [23]         |

|                                         | B7 | Control             | Close-loop control consider component tolerance                       |                                             | [26]         |

|                                         | B8 | Control             | Robust control for differential topologies                            |                                             | [64]         |

|                                         | C1 | Concept             | 2-quadrant DC chopper for ripple voltage concept                      |                                             | [30]         |

|                                         | C2 | Concept             | Review kinds of DC harmonics reducer                                  |                                             | [31]         |

|                                         | C3 | Topology (1D)       | Boost converter for DC-link with small capacitance                    | High voltage stress and much energy storage | [35]         |

|                                         | C4 | Control             | Control design for fuel cell system                                   |                                             | [36]         |

|                                         | C5 | Application         | Control design for LED system                                         |                                             | [38]         |

|                                         | C6 | Application         | Control design for fuel cell consider grid code                       |                                             | [40]         |

|                                         | C7 | Control             | Control design for high efficiency and fast response                  |                                             | [42]         |

|                                         | C8 | Control             | Feed-forward control for high accuracy ripple mitigation              |                                             | [43]         |

|                                         | D1 | Topology (1C)       | DCM buck buffer circuit                                               | Components holds DC-link voltage            | [44]         |

|                                         | D2 | Control             | CCM control for buck buffer circuit                                   |                                             | [46]         |

|                                         | D3 | Application         | Buck buffer circuit for MMC application                               |                                             | [49]         |

|                                         | E1 | Topology (1E)       | Buck-boost buffer structure                                           | Components holds DC-link votlage            | [50]         |

|                                         | E2 | Control             | Controller optimization for stability                                 |                                             | [51]         |

|                                         | F1 | Concept             | DC shunt active filter for low-frequency harmonics                    |                                             | [53]         |

|                                         | F2 | Topology (1A)       | Three port concept for power decoupling                               |                                             | [55]         |

|                                         | F3 | Application         | Full-bridge buffer for active power filter application                |                                             | [57]         |

|                                         | F4 | Control             | PQ control for full-bridge buffer circuit                             |                                             | [58]         |

|                                         | G1 | Topology (1B)       | Half-bridge buffer                                                    | High voltage stress and much energy storage | [60]         |

| Separate auxiliary                      | G2 | Control             | Close-loop control consider component tolerance                       |                                             | [61]         |

| circuit                                 | H1 | Topology            | Switched capacitors as energy buffer                                  | Control complexity and many devices         | [66]         |

| (No more change to                      | H2 | Concent             | Constal assess of switched assessitate as buffer                      | Control complexity and many devices         | [68]         |

| the main system)                        |    | Concept             | General concept of switched capacitors as buffer                      | Control complexity and many devices         |              |

|                                         | I1 | Topology (42F)      | Series full-bridge for damping harmonics                              | E-cap used in buffer circuit                | [71]         |

|                                         | I2 | Control             | Control the full-bridge as a controllable impedance                   |                                             | [73]         |

|                                         | I3 | Application         | Series full-bridge with inductor as buffer                            | Additional DC-link capacitor is needed      | [75]         |

|                                         | I4 | Control             | Control for low-frequency ripple voltage and power loss compensation  |                                             | [76]         |

|                                         | I5 | Topology (42E)      | Series buck converter as buffer                                       | Much energy storage                         | [79]         |

|                                         | I6 | Control             | Voltage control for two terminal buffer                               |                                             | [83]         |

|                                         | J1 | Topology (38F)      | Series full-bridge with the converter for voltage                     | Maka ana sida valtaga aanstant              | [85]         |

|                                         | JI | 1 opology (38F)     | compensation                                                          | Make one side voltage constant              | [83]         |

|                                         | J2 | Application         | Modeling the series module for PV application                         |                                             | [87]         |

|                                         | J3 | Application         | Control and implementation of series module for LED                   |                                             | [88]         |

|                                         | J4 | Topology (38G)      | application  Half bridge series module and its scalable multiparallel | Make one side voltage constant              | [89]         |

|                                         |    |                     |                                                                       |                                             |              |

|                                         | J5 | Application         | Series and parallel connection in buffer circuit                      |                                             | [90]         |

|                                         | K1 | Topology (50C)      | Series buck converter at AC side                                      | Change modulation strategy of main circuit  | [91]         |

|                                         | L1 | Topology (38A)      | Six-swiches converter with power decoupling capability                | Low modulation index                        | [105]        |

|                                         | M  | Tonola = (244)      | Three legs with 2 AC capacitors topology, which reuse the             | Low modultion index and much energy         | [02]         |

|                                         | M1 | Topology (34A)      | LC filter as energy buffer                                            | storage                                     | [93]         |

| (Integrated auxiliary                   | M2 | Control             | Reduce total energy storage of buffer                                 |                                             | [94]         |

| circuits)                               | N1 | Topology (6A)       | Three legs with 1 AC capacitor as buffer, which can increase          | Many switches are used                      | [95]         |

| Reduce number of                        |    | 1 opology (OA)      | energy buffer ratio                                                   | many switches are used                      |              |

| components in single-                   |    | Control             | Modulation to reduce current stress                                   |                                             | [97]         |

| phase converter with                    |    | Control             | Component sizing optimization                                         |                                             | [99]         |

| power decoupling                        | O1 | Topology (6C)       | Full-bridge with one buffer capacitors                                | Low modulation index                        | [111]        |

| capability                              | P1 | Topology (7B)       | Full-bridge with two buffer capacitors                                | Low modulation index and high current       | [112]        |

|                                         | P2 | Concept             | General structure to integrate half-birdge into full-bridge           | stress                                      | [114]        |

|                                         | Q1 | Topology (35B)      | Boost inverter with only 4 switches                                   | Swinging DC-link voltage                    | [109]        |

|                                         |    |                     | DUBLISH HEVELLET WHILL OHRY 4 SWILCHES                                | OWINSHIP LACERIER VOIGING                   | 11071        |

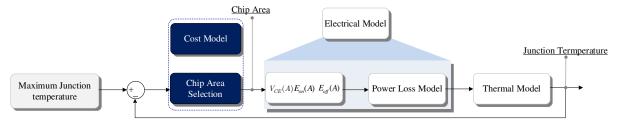

Fig. 10. Power Semiconductor reliability-oriented design procedure to fulfill the certain specification.

and film capacitors are used for the auxiliary capacitor  $C_{\rm b}$ . Such selections are based on the overall cost considerations as discussed later in cost assessment.

- 2) Capacitor Selection: Preliminary capacitor selection is done according to the electrical stress (voltage stress and current stress) and minimum required capacitance to limit the voltage ripple ratio derived from the electrical model. If the predicted capacitor lifetime is lower than the design target, another series of capacitors with longer rated lifetime or a capacitor in the same series with larger capacitance (i.e., smaller ESR) is chosen.

- 3) Electrical Stress Analysis: The electrical stress of each component is the basic for component selection. The voltage stress of DC-link electrolytic capacitor is constant, determined by the system specification. The DC-link voltage in this design is  $V_{\rm dc}$  with voltage ripple ratio of  $\alpha_{\rm v}$ . In some existing topologies, because of DC-link voltage utilization of the system is lower, the DC-link voltage is set to be another specified value. Different from that, the buffer capacitor's voltage stress is related to the capacitance of buffer capacitor. Due to the total energy storage in the capacitor determines its cost and power density at certain voltage rating, in this paper, all the cases are designed for minimum total energy storage in capacitors. Then, the electrical stresses of the capacitors can be derived.

- 4) Thermal Stress Calculation: Thermal stress is one of the critical stressors for capacitors, resulting in the reduction of capacitance and the increase of ESR due to wear out. The current ripple and ambient temperature are the contributors to the internal thermal stress of the capacitor. Towards electrolytic capacitor, the dominant degradation mechanisms are electrochemical reaction in the oxide layer and the electrolyte vaporization [3]. Both factors lead to an increase in ESR over the operating life of a capacitor. Especially, the increase of capacitor power loss causes a higher operating temperature inside the capacitor. The hot-spot temperature of the capacitor, which is affected by the current stress and ambient temperature, is derived as

$$T_{\rm h} = T_{\rm a} + R_{\rm ha} \times \sum_{i=1}^{n} [ESR(f_{\rm i}) \times I_{\rm rms}^2(f_{\rm i})]$$

(4)

where  $T_{\rm h}$  is the hot-spot temperature,  $T_{\rm a}$  is the ambient temperature,  $R_{\rm ha}$  is the equivalent thermal resistance from hot-spot to ambient,  $ESR(f_{\rm i})$  is the equivalent series resistance at frequency  $f_{\rm i}$ ,  $I_{\rm rms}(f_{\rm i})$  is the RMS value of the ripple current at frequency  $f_{\rm i}$ . The hot-spot temperature  $T_{\rm h}$  can then be estimated.

5) Lifetime Prediction: Lifetime prediction for the preliminarily selected capacitors can be done by the model which predicts the lifetime of capacitors under different operation conditions. According to the derivations in [3]

$$L = L_0 \times (\frac{V}{V_0})^{-n} \times \exp[(\frac{E_a}{K_B})(\frac{1}{T} - \frac{1}{T_0})]$$

(5)

where L and  $L_0$  are the lifetime under the use condition and testing condition, respectively. V and  $V_0$  are the voltage at use condition and test condition, respectively. T and  $T_0$  are the temperature in Kelvin at use condition and test condition, respectively.  $E_{\rm a}$  is the activation energy,  $K_{\rm B}$  is Boltzmann's constant  $8.62 \times 10^{-5} eV/K$ , and n is the voltage stress exponent. Therefore, the values of  $E_{\rm a}$  and n are the key parameters to be determined in the above model. For electrolytic capacitor and film capacitors, a simplified model from the above equation is popularly applied as follows:

$$L = L_0 \times (\frac{V}{V_0})^{-n} \times 2^{\frac{T_0 - T}{10}}$$

(6)

The model corresponds to a specific case of first equation when  $E_{\rm a}=0.94eV$  and  $T_0$  and T are substituted by 398K. For MPPF-Caps, the exponent n is from around 7 to 9.4, which is used by leading capacitor manufacturers. For electrolytic capacitors, the value of n typically varies from 3 to 5.

#### B. Power Semiconductors

The reliability-oriented procedure to size the chip area of active switches is shown in Fig. 10. The essence of selecting power semiconductor is sizing the chip area in each topology with the same loading conditions. By analyzing the power loss and thermal stress on each device, the optimal chip area can be selected for the maximum junction temperature, which is assumed to satisfy the lifetime requirement. The power semiconductor used in following analysis is IGBT. Similar sizing procedure can also be applied for MOSFET application.

1) Power Loss Calculation: The power losses in power semiconductor devices consist of the conduction loss and switching loss. If it is assumed that the current and voltage in a switching period is constant, the conduction loss in a switching period of each power device is

$$P_{\text{con}_{\text{T}}} = v_{\text{CE}}(|i_{\text{sw}}|, T_{\text{j}})|i_{\text{sw}}| \tag{7}$$

$$P_{\text{con}_{\text{D}}} = v_{\text{F}}(|i_{\text{D}}|, T_{\text{j}})|i_{\text{D}}|$$

(8)

where  $P_{\text{con}_{\text{T}}}$  is the conduction loss of the active device, and  $P_{\text{con}_{\text{D}}}$  is the conduction loss of the anti-parallel diode.  $i_{\text{sw}}$  and

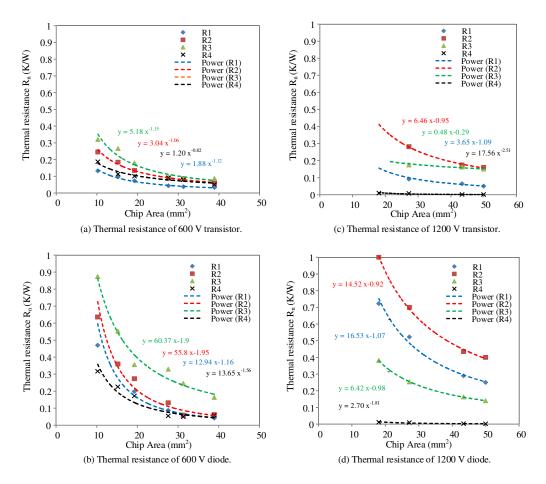

Fig. 11. Curve fitting results of thermal impedance parameters to the selected power devices.

$i_{\rm D}$  are the current flowing through the device and the diode, and  $T_{\rm j}$  is the junction temperature of the devices. The  $v_{\rm CE}$  and  $v_{\rm F}$  are related to  $i_{\rm sw}/i_{\rm D}$  and  $T_{\rm j}$  which will be further discussed later. On the other hand, the switching loss in each power device can be calculated as

$$P_{\text{sw}_{\text{T}}} = f_{\text{sw}}[E_{\text{on}}(|i_{\text{sw}}|, T_{\text{i}}, V_{\text{dc}}) + E_{\text{off}}(|i_{\text{sw}}|, T_{\text{i}}, V_{\text{dc}})]$$

(9)

$$P_{\text{sw}_{D}} = f_{\text{sw}} E_{\text{rr}}(|i_{\text{D}}|, T_{\text{i}}, V_{\text{dc}})$$

(10)

Similar as the equation above,  $P_{\rm sw_T}$  is the switching loss for the switch, and  $P_{\rm sw_D}$  is the switching loss for the freewheeling diode.  $E_{\rm on}$  and  $E_{\rm off}$  are the turn on and turn off energy dissipated by the device, while the  $E_{\rm rr}$  is the reverse recovery energy loss dissipated by the diode, which are the functions of  $i_{\rm sw}/i_{\rm D}$ ,  $T_{\rm i}$  and  $V_{\rm dc}$ .

2) Thermal Stress Analysis: The power losses of active switches induces thermal stresses. The junction temperature of IGBTs can be modeled as

$$T_{\rm j}(t) = P_{\rm tot}(t)Z_{\rm th(j-c)}(t) + T_{\rm c}(t)$$

(11)

$$T_{\rm c}(t) = T_{\rm a} + [P_{\rm totS}(t) + P_{\rm totD}(t)]$$

(12)

$\times [Z_{\rm th(c-h)}(t) + Z_{\rm th(h-a)}(t)]$

where  $P_{\rm tot}$  gives the IGBT or diode power losses.  $P_{\rm totS}$  and  $P_{\rm totD}$  are the power losses in the IGBT and the diode

respectively.  $Z_{\rm th(j-c)}$ ,  $Z_{\rm th(c-h)}$  and  $Z_{\rm th(h-a)}$  give the thermal impedance from junction to case, case to heatsink and heatsink to ambient, respectively.  $T_{\rm c}$  is the case temperature.

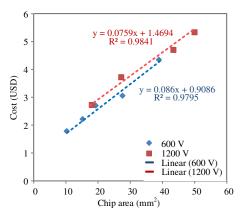

3) Sizing of the Chip Area: The power losses, thereby the thermal stresses and lifetime of the IGBTs are dependent on its chip areas. To achieve a specific lifetime target, a maximum allowable junction temperature is set in the design process, also as shown in Fig. 10. In order to size the chip area, the conduction loss model, the switching loss model, and the thermal model have to be adapted with the semiconductor chip area. The Infineon High Speed 3 (600 V and 1200 V) and Infineon IGBT Bare Die (600 V and 1200 V) have been chosen as the database because of the availability of sufficient information [122], [123]. For low voltage cases, Infineon HEXFET series (100 V and 150 V MOSFET) data are used for cost bechmarking. According to the associated data-sheets, the chip size is approximately proportional to the current rating. Moreover, the chip size determines the switch on and off energy  $E_{\text{tot}}$ ,  $V_{\text{CE}}$  and  $Z_{\text{th}}$  which have influence on the junction temperature of the devices. Based on the complete loss and thermal model including device rating information [124], the relationships can be approximately obtained by

Fig. 12. Inductor design procedure to fulfill the certain specification.

Fig. 13. Three legs single-phase structure used for the inductor design and analysis.

(a) Topology used for inductor design.

TABLE VI

PARAMETERS RELATED TO CHIP AREA BY CURVE FITTING

(SOURCE:INFINEON [122]).

| Voltage<br>Rating(V) | Parameters   | $a_0$    | $a_1$    | $a_2$    | $a_3$   |

|----------------------|--------------|----------|----------|----------|---------|

| 600                  | $V_{\rm ce}$ | 2.64     | -1.32E-1 | 7.18E-3  | 3.14E-2 |

| 600                  | $E_{ m tot}$ | 9.89E-08 | 1.71E-10 | 2.06E-10 |         |

| 1200                 | $V_{ce}$     | 2.61     | -0.0648  | 6E-3     | 4.13E-2 |

| 1200                 | $E_{ m tot}$ | 1.14E-07 | 1.12E-09 | 8.10E-10 |         |

TABLE VII

DIODE PARAMETERS RELATED TO CHIP AREA BY CURVE FITTING

(SOURCE: INFINEON [122]).

| Voltage<br>Rating (V) | Parameters       | $a_0$   | $a_1$    | $a_2$    | $a_3$  |

|-----------------------|------------------|---------|----------|----------|--------|

| 600                   | $V_{\mathrm{F}}$ | 1.7     | -4.2E-2  | 3.1E-04  | 3.3E-2 |

| 600                   | $E_{ m tot}$     | 1.3E-05 | 2.76E-05 | 6.31E-06 |        |

| 1200                  | $V_{ m F}$       | 2.5     | -0.04    | 1.3E-3   | 7.1E-2 |

| 1200                  | $E_{ m tot}$     | 3.6E-04 | 2.9E-04  | 1.1E-05  |        |

curve fitting of the equation given below.

$$\begin{cases} V_{\text{CE}}(A_{\text{chip}}, T_{\text{j}}, i_{\text{sw}}) = a_0 + a_1 A_{\text{chip}} + a_2 T_{\text{j}} + a_3 i_{\text{sw}} \\ E_{\text{tot}}(A_{\text{chip}}, T_{\text{j}}, i_{\text{sw}}, V_{\text{dc}}) = V_{\text{dc}} \times i_{\text{sw}} \times (a_0 + a_1 A_{\text{chip}} + a_2 T_{\text{j}}) \end{cases}$$

(13)

The constants  $a_0$ ,  $a_1$ ,  $a_2$ , and  $a_3$  of the specifically analyzed IGBTs are listed in Table VI. The confidence level is 95% and  $R^2$  ( $R^2$  is computed from the sum of the squares of the distances of the points from the best-fit curve determined by nonlinear regression) are higher than 0.9. Similar analytical models for diodes can be obtained by curve fitting according

to the equations below

(b) Average Model of the topolgoy used for inductor design.

$$\begin{cases} V_{\rm F}(A_{\rm chip}, T_{\rm j}, i_{\rm sw}) = a_0 + a_1 A_{\rm chip} + a_2 T_{\rm j} + a_3 i_{\rm sw} \\ E_{\rm tot}(A_{\rm chip}, T_{\rm j}, i_{\rm sw}, V_{\rm dc}) = V_{\rm dc} \times i_{\rm sw} \times (a_0 + a_1 A_{\rm chip} + a_2 T_{\rm j}) \end{cases}$$

$$(14)$$

The constants for the above equations are listed in Table VII. The thermal impedance of the power semiconductor can also be seen as a function of chip area, which is shown below

$$Z_{\text{th}}(A_{\text{chip}}) = \sum_{n=1}^{4} R_{n}(A_{\text{chip}})(1 - e^{-\frac{t}{\tau_{n}}})$$

$$= \sum_{n=1}^{4} a_{n_{0}} A_{\text{chip}}^{a_{n_{1}}} (1 - e^{-\frac{t}{\tau_{n}}})$$

(15)

where  $R_n$  is the thermal resistance for n layer RC lump of IGBT and  $\tau_n$  is the time constants. The curve fitting results for thermal resistances  $R_n(A_{\text{chip}})$  is presented in Fig. 11.

#### C. Inductor

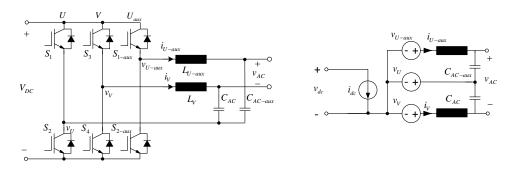

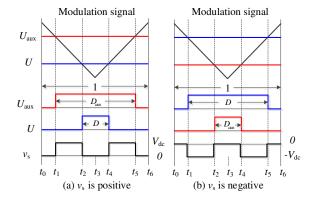

Since it is assumed that the magnetic components usually has less degradation compared to active switches and capacitors, the lifetime analysis of magnetic components is not considered in this paper. Because the modulation strategies of the single-phase systems presented above have changed, the sizing of the inductor is based on achieving the same THD of the inductor currents. The inductor design diagram can be seen in Fig. 12. An example including 3 legs is presented in Fig. 13 to illustrate the inductance design process, which can be extended to other 2 and 3 legs single-phase topologies with integrated active DC link.  $U_{\rm aux}$  and V leg are connected to AC port of single-phase converter and U leg is used for power decoupling, which seems as float ground of the capacitors.

TABLE VIII

SPECIFICATION OF THE SINGLE-PHASE SYSTEM AS A STUDY CASE.

| Parameters                              | Description                   | Value         |

|-----------------------------------------|-------------------------------|---------------|

| P(W)                                    | Power rating                  | 2200          |

| $V_{ m dc}(V)$                          | DC-link voltage               | 400<br>(800)  |

| $V_{ m m}(V)$                           | Peak voltage of AC            | $220\sqrt{2}$ |

| $I_{\mathrm{m}}(A)$                     | Peak Current of AC            | $10\sqrt{2}$  |

| $lpha_{ m v}$                           | DC-link voltage ripple ratio  | 4 %           |

| $lpha_{ m i}$                           | Inductor current ripple ratio | 20 %          |

| $f_{\rm a}(Hz)$                         | Fundamental frequency         | 50            |

| $f_{\mathrm{sw}}(Hz)$                   | Switching frequency           | 20 k          |

| $T_{\mathrm{imax}}(^{\circ}\mathrm{C})$ | Maximum Junction Temperature  | 100           |

| $T_{\mathbf{a}}(^{\circ}\mathbf{C})$    | Ambient temperature           | 50            |

| L(years)                                | Lifetime target of capacitors | 10            |

This structure is able to be transformed to several single-phase topologies with integrated active DC link from above topology derivation, such as full-bridge by deleting U leg, interleave buck converter by connecting float ground to negative terminal of DC source, topology 6A with only one buffer capacitor  $C_{\rm AC}$  and 34A, while the inductor design procedure for these cases is similar.

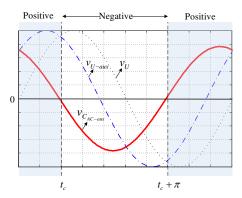

Based on the mathematical analysis, the RMS value of total harmonics over one period of the fundamental output voltage T can be obtained, which is limited to  $\alpha_{\rm i}I_{\rm AC,rms}$ .  $I_{\rm AC,rms}$  is the RMS value of the AC port current and  $\alpha_{\rm i}$  is the current ripple ratio presented in Table VIII.

$$\tilde{I}_{\text{U-aux,rms}} = \sqrt{\frac{1}{T} \left( \int_{t_{c}}^{t_{c} + \frac{T}{2}} \tilde{I}_{\text{U-aux,p}}^{2}(t) dt + \int_{t_{c} + \frac{T}{2}}^{t_{c} + T} \tilde{I}_{\text{U-aux,n}}^{2}(t) dt \right)}$$

(16)

where  $t_c$  is the crossover time of the AC current,  $\tilde{I}_{U-aux,p}^2(t)$  and  $\tilde{I}_{U-aux,n}^2(t)$  is the RMS current of leg U in a switching period. Detail analysis for parameter derivation is shown in Appendix A. Following above design procedure, the inductors for other leg can be derived and calculated by numerical computation, which can also be extended to all the cases. The analysis results for all the cases following above method have been listed in Table B.2. The inductor implementations are based on the Design software from Magnetics-2014 version [125]. The winding factor for each inductor is set to be similar for all the cases, between 35% and 40%, to keep same winding utilization.

### V. COST ASSESSMENT AND SCALABILITY ANALYSIS OF ACTIVE DC LINKS

In this section, a reliability-oriented design method for costbenchmarking is proposed, which can sizing the components with the specified lifetime target. The cost assessment and scalability analysis in terms of lifetime and power rating are studied to compare the typical capacitive DC-link solutions.

### A. Cost Assessment

The cost assessment of the existing capacitive DC links is based on the same specification as shown in Table VIII. All of them have the same design target, which is the minimum energy storage in capacitors, with the same system specification and lifetime requirement.

Fig. 14. Statistical results of power semiconductor cost which is represented as unit price for 1000 pieces ordering quantity (source: [122], [123]).

1) Power Semiconductor: The cost of the IGBT switches is modeled as the chip cost and package cost as discussed in details in [126]. The chip cost is proportional to its area and the packaging cost is a fixed one for a given packaging form. Therefore.

$$\sum_{\text{cd}} = \sum_{\text{chip}} + \sum_{\text{pack}, x} = \left(\sum_{n} \sigma_{\text{chip}, x(n)} A_{\text{chip}, n}\right) + \sum_{\text{pack}, x} (17)$$

where  $\sigma_{\mathrm{chip,x(n)}}$  is the specific cost per chip area,  $A_{\mathrm{chip,n}}$  depending on the chip technology, and  $\sum_{\mathrm{pack,x}}$  is the package cost (including chip integration and bonding). The parameter  $\sigma_{\mathrm{chip,x(n)}}$  can hence be interpreted as the sum of all processing and R & D costs for a given chip technology. The statistical results are presented in Fig. 14.

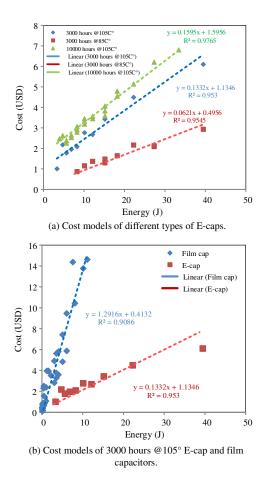

2) Capacitor: The cost of E-caps and film capacitors of certain voltage rating scales with the rated stored energy. Therefore, the cost model can be written as

$$\sum_{\text{cap}} = \sum_{\text{Energy}} + \sum_{\text{pack}} = \sum_{\text{unit}} E_{\text{cap}} + \sum_{\text{pack}} (18)$$

where  $\sum_{\rm Energy}$  is the cost for energy stored in the capacitor which can be described as the multiple of the cost for unit energy  $\sum_{\rm unit}$  and the energy requirement for circuit  $E_{\rm cap}$ . Fig. 15 (a) and (b) show the statistical results of unit cost of standard E-cap (450V rated voltage, snap-in terminals, and 20% tolerance) and polypropylene thin film capacitors from leading manufacturers.

The design results and costs for the capacitors of existing solutions are in given Table B.1 (Data supported by Digikey [123]). It is worth to note that the lifetime of DC-link capacitor in 1C with 110  $\mu F$  is 9 years which are shorter than the lifetime target. By increasing the capacitance (i.e., with lower ESR value) in the same series of products, the lifetime extends to be 11 years at 150  $\mu F$ .

3) Inductor: Based on the inductor cost model presented in [126], high flux ferrite core and solid round winding are selected in the three design cases. Inductors for converters in the considered power range are often material and labour intense, of which a simplified version can also be found in

$$\sum_{L} = \sum_{\text{mat,L}} + \sum_{\text{lab,L}}$$

(19)

Fig. 15. Statistical results of unit cost of different kinds of capacitors which are represented as unit price for 1000 pieces ordering quantity (source: [123]).

where

$$\sum_{\text{max,L}} = \sum_{\text{core,x}} + \sum_{\text{wdg,x}}^{\text{fac}} + \sum_{\text{mat,x}}^{\text{fac}}$$

$$= \sigma_{\text{core,x}} W_{\text{core}} + \sigma_{\text{wdg,x}} W_{\text{wdg}} + \sum_{\text{mat,x}}^{\text{fac}}$$

(20)

$$\sum_{\text{lab,L}} = \sigma_{\text{lab,x}} W_{\text{wdg}} + \sum_{\text{lab,x}}^{\text{fac}}$$

(21)

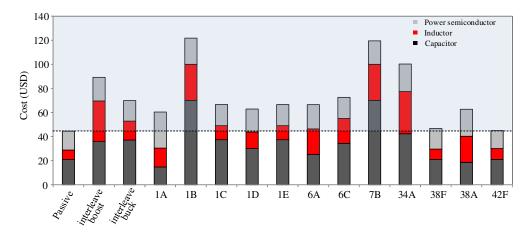

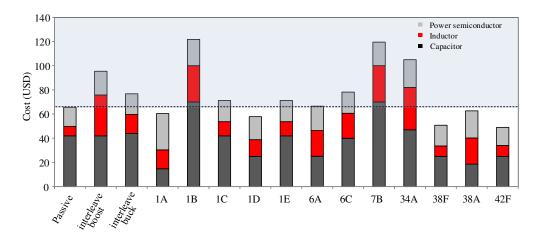

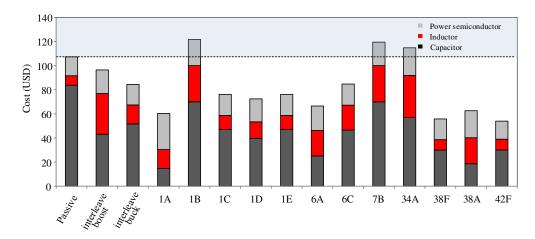

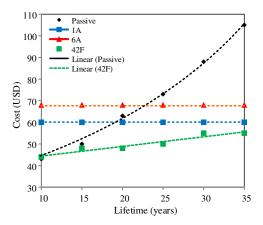

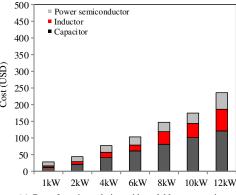

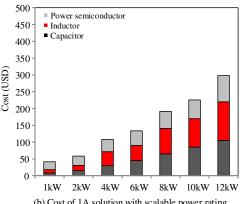

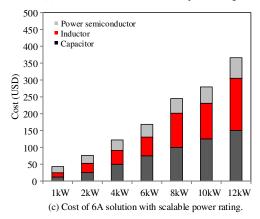

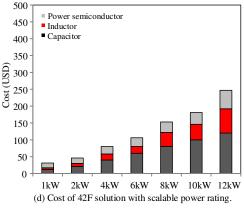

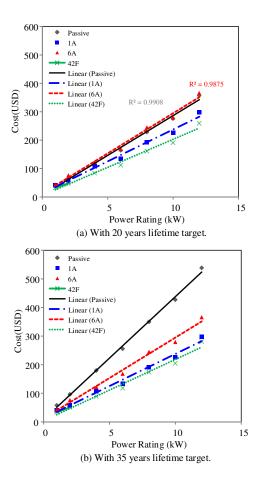

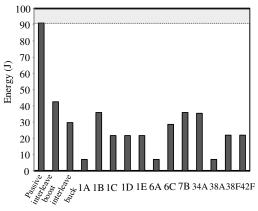

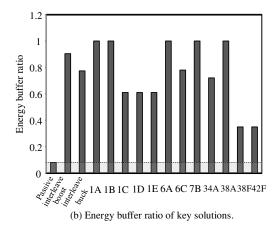

$\sigma_{\mathrm{core,x}}$ ,  $\sigma_{\mathrm{wdg,x}}$  and  $\sigma_{\mathrm{lab,x}}$  are specific costs per weight  $W_{\mathrm{core}}$ ,  $W_{\mathrm{wdg}}$  of the core and winding depending on the employed core and winding type.  $\sum_{\mathrm{mat,x}}^{\mathrm{fac}}$  and  $\sum_{\mathrm{lab,x}}^{\mathrm{fac}}$  are fixed material and labour costs (e.g. coil former, connectors). The design results of inductors' costs for the existing active power decoupling solutions are in Table B.2.