#### ASP-DAC 2014

Comprendre le monde, construire l'avenir®

## An Overview of Spin-based Integrated Circuits

Wang Kang, Weisheng Zhao, Zhaohao Wang, Jacques-Olivier Klein, Yue Zhang, Djaafar Chabi, Youguang Zhang, Dafiné Ravelosona, and Claude Chappert

IEF, Univ. Paris-Sud, CNRS, Orsay, 91405, France Electronics Engineering, Univ. Beihang, Beijing, 100191, China 1/12/2014

#### Introduction

- Spintronics fundamental

- Spin-based memory devices and circuits

- Spin-based logic devices and circuits

- Emerging computing paradigms

- Conclusion and perspectives

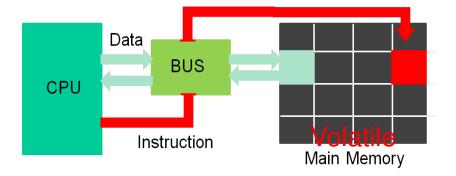

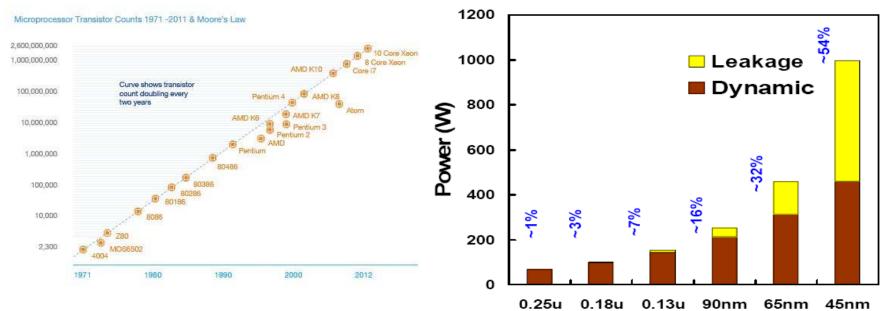

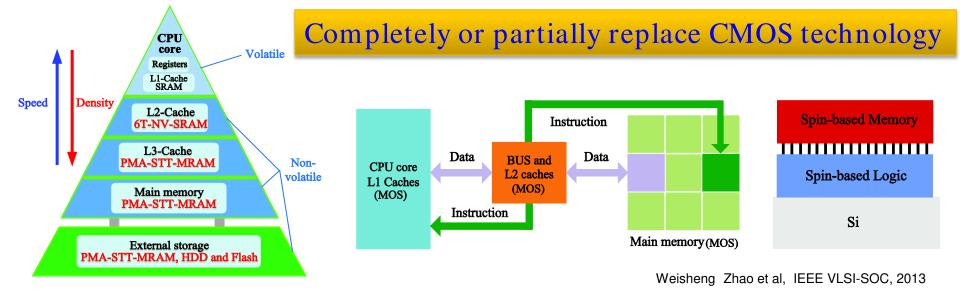

#### Moore's Law Ends?

#### • MOS Scaling Ends???

- Leakage current (static)

- Long traffic (dynamic)

- Reliability issues

Weisheng Zhao et al, IEEE VLSI-SOC, 2013

S. E. Thompson, S. Parthasarathy, Mater. Today, Vol. 9 No. 6, pp. 20-25, 2006.

2014/1/12

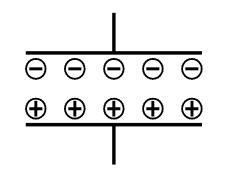

# Spintronics is Emerging!

e Spin-down

Conventional electronics: uses electrical charge Spintronics: uses spin of electrons in addition to electrical charge

- Non-volatility

- 3D integration

- fast access speed

- ultra-low power

2014/1/12

#### Introduction

- Spintronics fundamental

- Spin-based memory devices and circuits

- Spin-based logic devices and circuits

- Emerging computing paradigms

- Conclusion and perspectives

- The origins of Spintronics can be traced back to the 1970s [Julliere 1975]

- The discovery of spin valve or GMR in 1988 (Nobel Prize Physics 2007 for A. Fert and P. A. Grunberg)

- The discovery of MTJ and STT in 1995 [Moodera et al., Miyazaki et al., and Berger and Slonczewski]

- The spin-valve sensor was firstly commercialized by IBM in 1997

2014/1/12

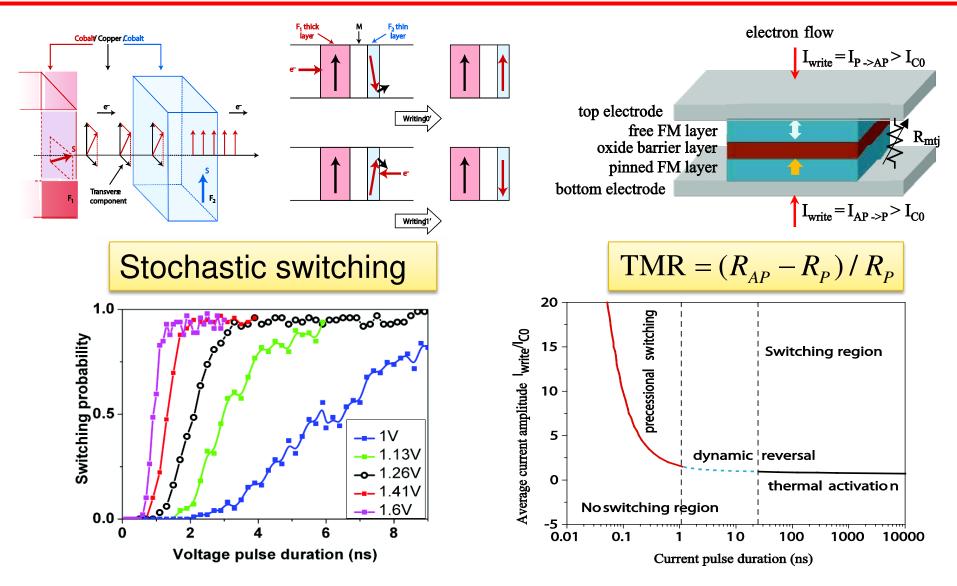

#### **STT-MTJ**

C. Chappert, A. Fert and F. Dau, Nature Mater., vol. 6, pp. 813-823, 2007. W. S. Zhao, et al, Microelectron. Reliab., vol. 52, pp. 1848-1852, 2012. 7

## STT-MTJ modeling

Critical current

$$I_{C0} = \alpha \frac{\gamma e}{\mu_B g} (\mu_0 M_s) H_K V = 2\alpha \frac{\gamma e}{\mu_B g} E$$

Precessional switching region,

$$\Pr\left(t_{pulse}\right) = 1 - \exp\left(-\frac{t_{pulse}}{\tau_1}\right), \frac{1}{\tau_1} = \left[\frac{2}{C + \ln\left(\pi^2 \Delta\right)}\right] \frac{\mu_B P}{em(1+P^2)} (I_{write} - I_{C0})$$

Thermal activation region,

$$\frac{d \mathbf{R} r t_{pulse}}{\left(1 - \mathcal{P} r\left(t_{pulse}\right)\right) dt} = \frac{1}{\tau_2}, \tau_2 = \tau_0 exp\left(\frac{E}{k_B T}\left(1 - \frac{I_{write}}{I_{C0}}\right)\right)$$

Dynamic reversal region, no explicit formulas

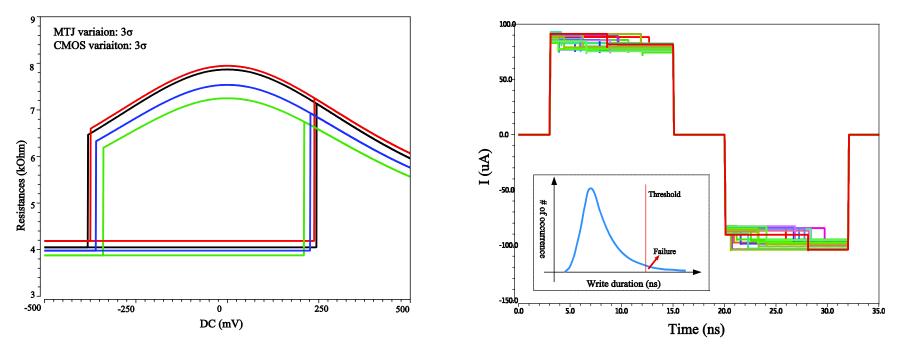

## STT-MTJ modeling (Cont.)

- Verilog-A language

- STMicroelectronics 40 nm design-kit

- DC and transient simulation

Y. Zhang et al., IEEE Trans. Electron Devices, vol. 59, no. 3, pp.819-826, 2011.

2014/1/12

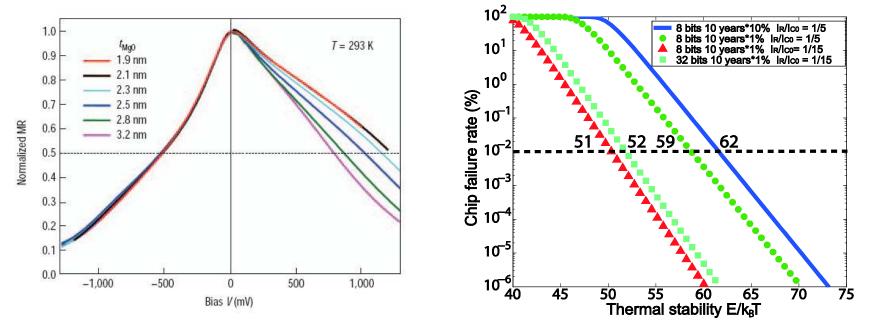

## **Reliability issues**

- STT stochastic switching—write errors

- TMR reduction—read errors

- $TMR_{real} = \frac{TMR(0)}{1 + V_{hiac}^2 / V_h^2}$

- Read disturbance—read errors  $Pr_{dis}(t_{read}) = 1 exp(-N\frac{t_{read}}{\tau_0}exp(-\Delta(1-\frac{I_{read}}{I_{c0}})))$

S.Yuasa et al, Nat. Mat. (2004)

W. S. Zhao, et al, Microelectron. Reliab., vol. 52, pp. 1848-1852, 2012.

<sup>2014/1/12</sup>

#### Introduction

- Spintronics fundamental

- Spin-based memory devices and circuits

- Spin-based logic devices and circuits

- Emerging computing paradigms

- Conclusion and perspectives

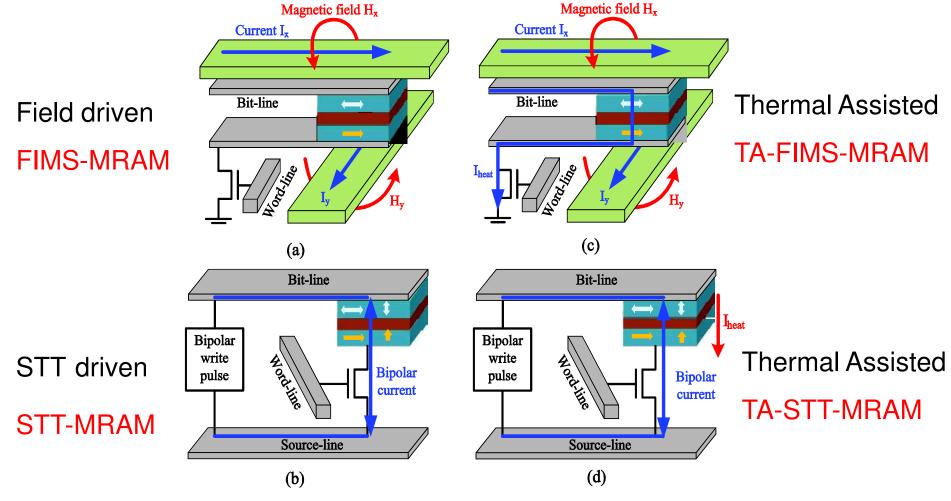

#### Magneto RAM (MRAM)

#### Mainly based on the hybrid structure, i.e. MTJ+MOS

2014/1/12

- MRAM uses MTJ as non-volatile storage element

- Read based on the TMR ratio of MTJ

- ITRS reported that STT-MRAM is one of the most promising candidates for the next generation non-volatile memory.

- Many prototypes or small-scale chips have been proposed or commercialized in markets currently

- Intrinsic anti-radiation, promising for aerospace applications

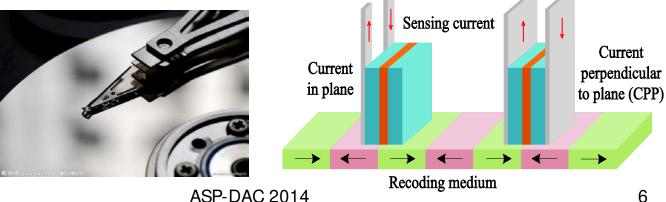

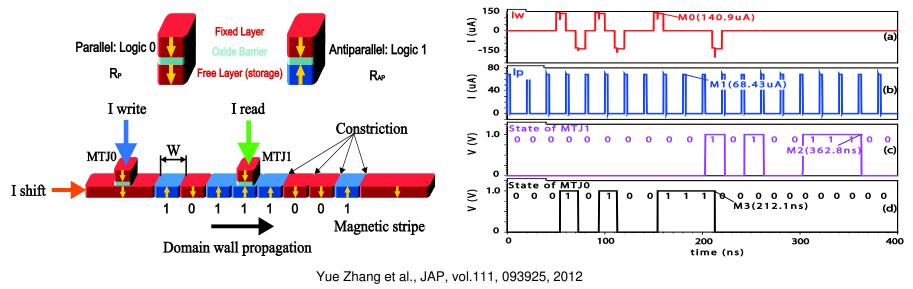

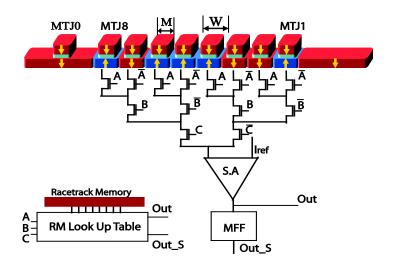

- Based on domain wall (DW) motion

- With MTJ as write and read heads

- Ultra-high storage density and low power operation

- One of the key challenges to build RM is to avoid any pinning defects in the magnetic strips

#### **Advanced Spin-based Memories**

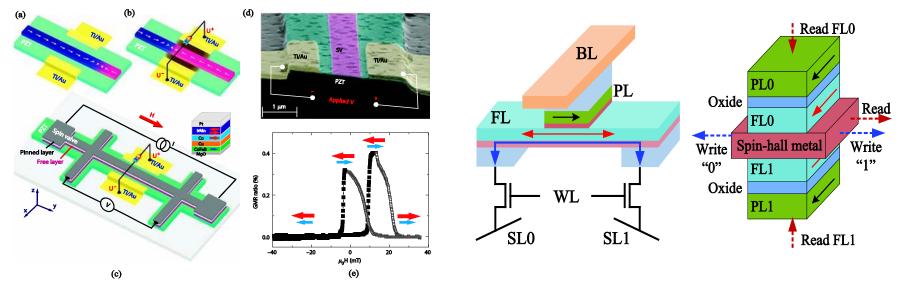

- Voltage-Controlled (DC) MRAM or DW motion

- Spin-Orbit Coupling memory devices

- Further reduce programming power VS STT

- Far away for practical applications

Na Lei et al., Nature Communications, vol.4, 1378, 2013.

#### Introduction

- Spintronics fundamental

- Spin-based memory devices and circuits

- Spin-based logic devices and circuits

- Emerging computing paradigms

- Conclusion and perspectives

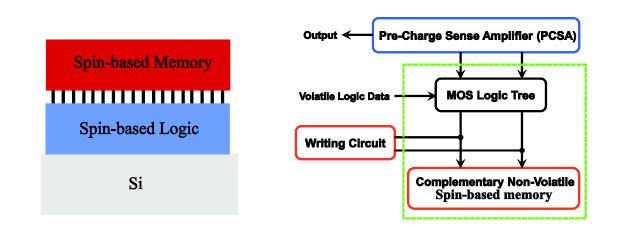

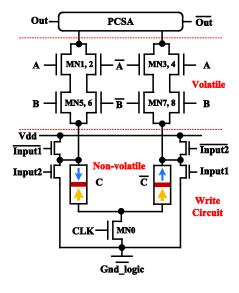

## Hybrid MTJ/CMOS Logic Circuits

- Mainly based on the logic-in-memory structure

- Inputs partly volatile, partly non-volatile

- 3D integration shortens traffic delay and power

- Low power and high speed

Erya Deng et al., IEEE Trans. Magnetics, vol.49, pp.4982-4987, 2013

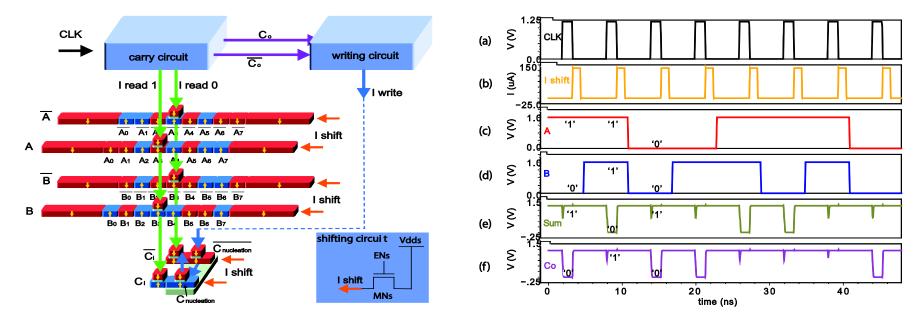

#### **Domain Wall based Logics**

- All the data inputs are stored in non-volatile states

- Area, power, delay overheads

- Same challenges as racetrack memory

- Defects in magnetic nanowires

H-P Trinh, et al., IEEE . Circuits and Systems I, vol.60, pp.1469-1477, 2013.

2014/1/12

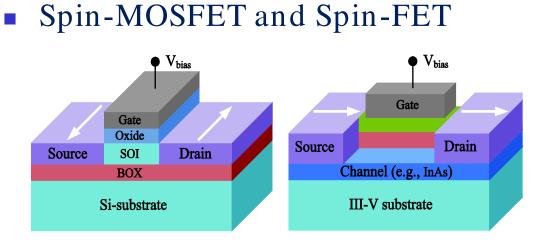

## Spin-Transistors

- Concept has been predicted early in the 1990s, but it was experimentally developed recently

- Most critical challenge for spin transistors is the "magic" material for the spin transport channel

- Graphene has been proved generally the potentiality and capability for the channel material

Sugahara S, Nitta J.Proceedings of the IEEE, 2010, 98(12): 2124-2154.

2014/1/12

$<sup>(</sup>a) \qquad (b) \qquad V_{O} \qquad (c) \qquad (c$

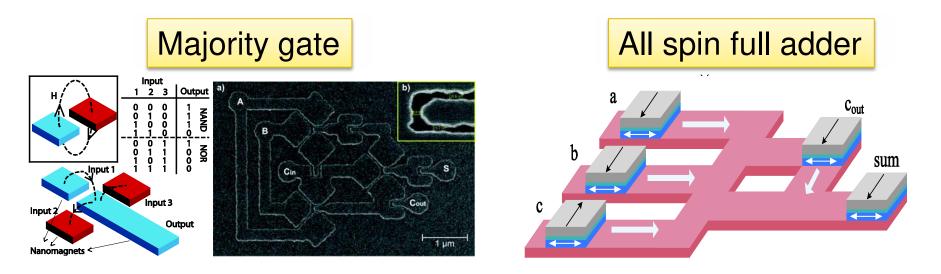

#### All-Spin Logic and Nano-Magnetic Logic

- Uses nano-magnets as digital spin capacitors to store data and spin to communicate, realizing logic gates based on the spin majority evaluation

- Ultra-low power and full spin system

- Challenges for material, fabrication and controllability

B. Behin-Aein et al, *Nature nanotech*, Vol. 5, pp. 266-270, 2010.

S. Breitkreutz, et al., IEEE Trans. on Magnetics, vol.49, pp.4464-4467, 2013.

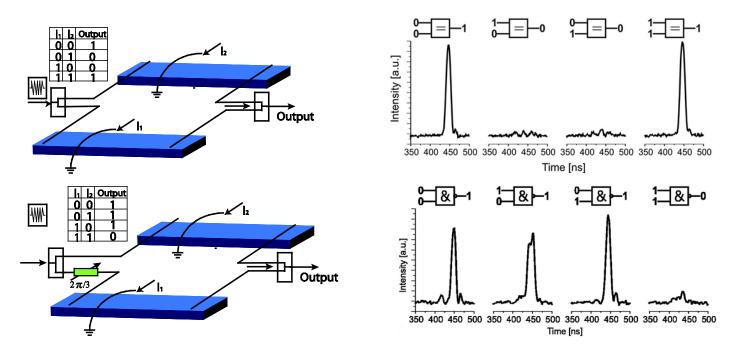

# Spin Wave Logic

- It uses magnetic films as spin conduit of wave propagation, information can be coded into a phase or amplitude of the propagating spin wave

- Challenges: Spin wave amplitude decay and low spin wave phase velocity

T. Schneider et al, Appl. Phys. Letters, vol.92, pp. 022505, 2008.

#### Introduction

- Spintronics fundamental

- Spin-based memory devices and circuits

- Spin-based logic devices and circuits

- Emerging computing paradigms

- Conclusion and perspectives

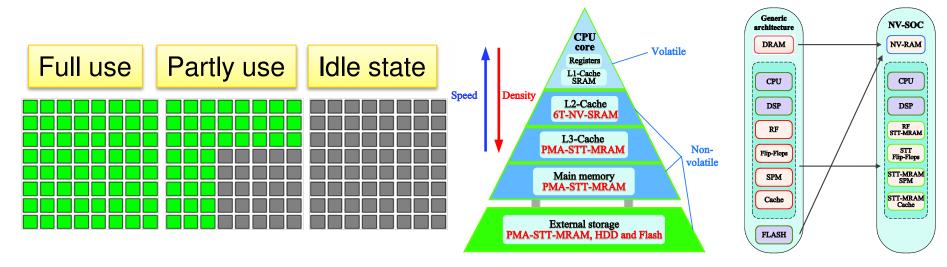

## Normally-Off Computing Systems

- Non-volatile storage: no static power

- "Instant on/off" capability

- Normally-Off when the CPU is in standby state

- Normally-On after power is reset

- Ultra-low power computing system

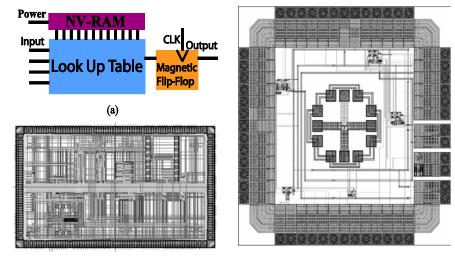

## Dynamic Reconfigurable Systems

• FPGA with SRAM to store the configuration

- Low power efficiency and logic density

- Challenge for dynamically reconfigurable or in run-time

- Spin-based memory as configuration

- STT-MRAM, TA-MRAM and racetrack memory etc

W.S. Zhao, et al., IEEE Trans. on Magnetics, vol.47, pp.2966-2969, 2011 W.S. Zhao, et al., ACM Trans. Reconfigurable Technology and Systems, vol.2, 2009.

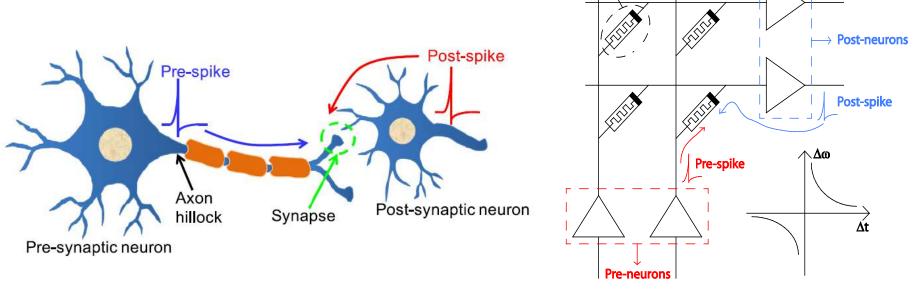

## Neuromorphic Systems

- Circuits and systems that work analogously to the brain

- Spintronics devices and memristor are the most promising candidates as synapse in neuromorphic systems currently

- Ultra-low power consumption

- Artificial intelligence

M. Sharad et al., IEEE Trans. Nano., Vol. 11, pp. 843-853, 2012.

K. Roy et al., IEEE ISLPED, pp.139-142, 2013.

Spintronic memristor as synapse

## **Conclusion and perspectives**

- Overview of spin-based devices and circuits, their challenges and merits in current applications

- Emerging novel computing paradigms and architectures beyongd Von-Neumann architecture

- In the short term (i.e., 5-10 years), STT-MTJ/CMOS hybrid memory and logic could be the major candidates to achieve the commercial steps.

- In the long term (i.e., 10-20 years), there isn't any evidence for any other devices or structures (e.g., Graphene based devices) to become the mainstream solution.

# Thanks for your attention! Questions??