# Analog dithering techniques for highly linear and efficient transmitters

Citation for published version (APA):

Arfaei Malekzadeh, F. (2012). *Analog dithering techniques for highly linear and efficient transmitters.* [Phd Thesis 1 (Research TU/e / Graduation TU/e), Electrical Engineering]. Technische Universiteit Eindhoven. https://doi.org/10.6100/IR728779

DOI:

10.6100/IR728779

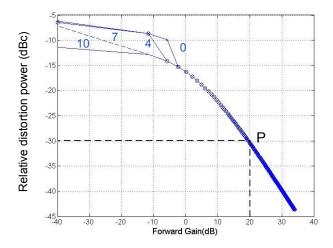

Document status and date:

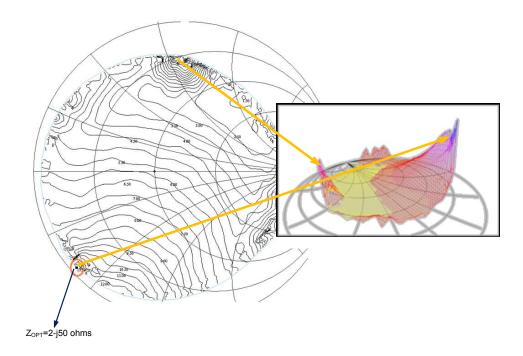

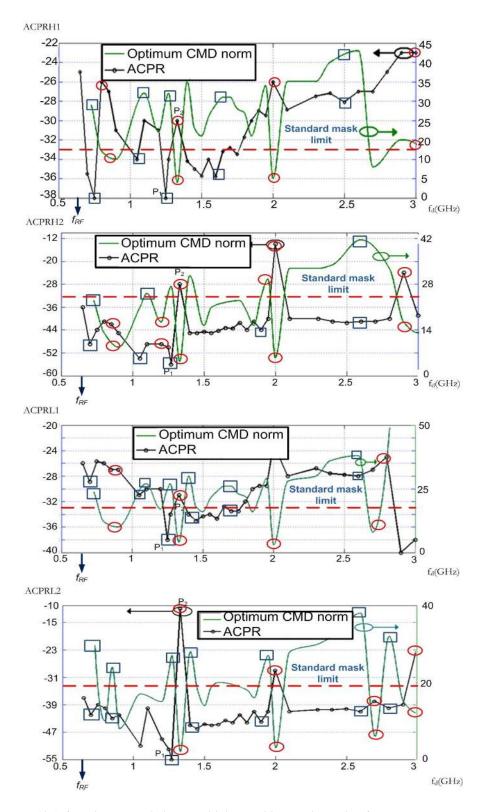

Published: 01/01/2012

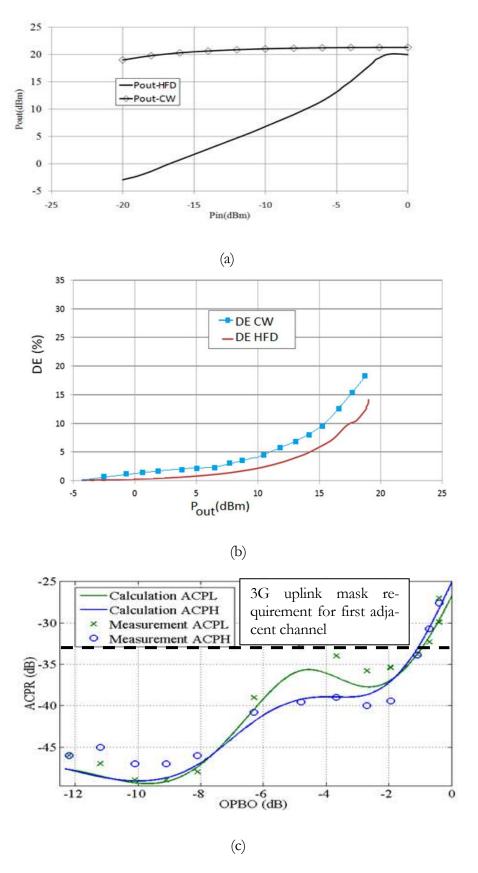

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 22. Aug. 2022

# Analog Dithering Techniques for Highly Linear and Efficient Transmitters

Foad Arfaei Malekzadeh

#### Front Cover:

Graphical description of dither averaging, Introduced in chapter 2

#### Back cover:

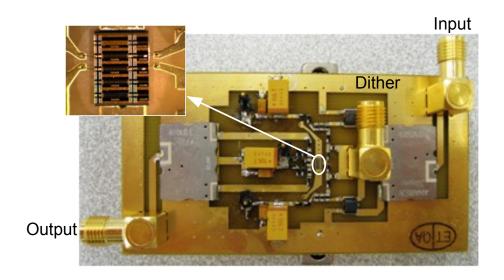

PCB photo of the current mode Class D amplifier, with common mode LFD, presented in chapter 8 and short CV of Foad Arfaei Malekzadeh

# Analog Dithering Techniques for Highly Linear and Efficient Transmitters

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de

Technische Universiteit Eindhoven, op gezag van de

rector magnificus, prof.dr.ir. C.J. van Duijn, voor een

commissie aangewezen door het College voor

Promoties in het openbaar te verdedigen

op woensdag 7 maart 2012 om 16.00 uur

door

Foad Arfaei Malekzadeh

geboren te Teheran, Iran

Dit proefschrift is goedgekeurd door de promotor:

prof.dr.ir. A.H.M. van Roermund

Copromotor:

dr.ir. R. Mahmoudi

A Catalogue record is available from the Eindhoven University of Technology Library.

CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Foad Arfaei Malekzadeh

Analog Dithering Techniques for Highly Linear and Efficient Transmitters / by Foad Arfaei

Malekzadeh. – Eindhoven: Technische Universiteit Eindhoven, 2012.

Proefschrift. –ISBN: 978-90-386-3101-1

NUR 959

Key words: Transmitter / Dithering / Efficiency / Linear / Analog

Copyright © 2012 by Foad Arfaei Malekzadeh, Eindhoven

All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic, mechanical, including photocopy, recording, or any information storage and retrieval system without the prior written permission of the copyright owner.

To my wife, Sahar, and to my parents

#### Samenstelling van de promotiecommissie:

prof. dr. ir. A.C.P.M. Backx prof.dr.ir. A.H.M. van Roermund dr.ir. R. Mahmoudi prof.dr.ir. M. Steyaert dr. R. B. Staszewski prof.dr. S. Weiland dr. ir. Fred van Rijs dr. ir. Derk Reefman Technische Universiteit Eindhoven, voorzitter Technische Universiteit Eindhoven, promoter Technische Universiteit Eindhoven, co-promoter Katholieke Universiteit Leuven Technische Universiteit Delft Technische Universiteit Eindhoven NXP Semiconductors Nijmegen Philips Corporate Technologies, Research

# **Contents**

| Contents |                                                            | vii  |

|----------|------------------------------------------------------------|------|

| Glossary | y                                                          | xiii |

| 1.Introd | luction                                                    | 19   |

| 1.1      | Motivation                                                 | 20   |

| 1.2      | Dithering concept                                          | 20   |

| 1.3      | Problem statement                                          | 21   |

| 1.4      | Limitations of existing analysis methods                   | 22   |

| 1.5      | Aim of the project                                         | 23   |

| 1.6      | Proposed approach                                          | 24   |

| 1.7      | Thesis outline                                             | 24   |

| 2.Dither | ring                                                       | 25   |

| 2.1      | Dithering concept                                          | 26   |

| 2.2      | Equivalent nonlinearity                                    | 27   |

| 2.3      | High and low frequency dithering                           | 29   |

| 2.4      | Rotating vector representation                             | 31   |

| 2.5      | Fourier series approach                                    | 33   |

|          | 2.5.1 High frequency dithering                             | 33   |

|          | 2.5.2 Low frequency dithering                              | 34   |

| 2.6      | Statistical approach                                       | 36   |

|          | 2.6.1 Equivalent nonlinearity for high frequency dithering | 37   |

viii Contents

|         | 2.6.2 Equivalent nonlinearity for low frequency dithering | 38 |

|---------|-----------------------------------------------------------|----|

| 2.7     | Conclusion                                                | 39 |

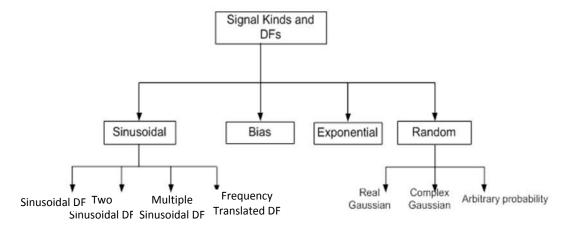

| 3.Desc  | ribing functions                                          | 41 |

| 3.1     | Sinusoidal DF                                             | 44 |

|         | 3.1.1 Single sinusoidal DF                                | 44 |

|         | 3.1.2 Two sinusoidal input DF                             | 46 |

|         | 3.1.3 Multiple sinusoidal input DF                        | 48 |

|         | 3.1.4 Frequency translated DF                             | 48 |

| 3.2     | Random input describing function                          | 49 |

|         | 3.2.1 Real Gaussian input DF                              | 49 |

|         | 3.2.2 Complex Gaussian DF                                 | 50 |

| 3.3     | Conclusions                                               | 51 |

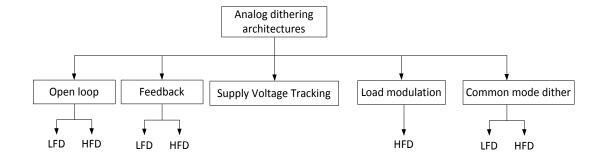

| 4.Arch  | itectures and topologies                                  | 53 |

| 4.1     | Architecture level considerations                         | 54 |

|         | 4.1.1 Open-loop                                           | 55 |

|         | 4.1.2 Closed-loop                                         | 55 |

|         | 4.1.3 Tracking                                            | 55 |

|         | 4.1.3.1 Tracking with open loop                           | 55 |

|         | 4.1.3.2 Tracking with closed loop                         | 56 |

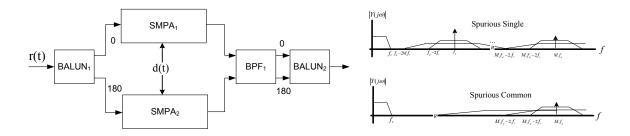

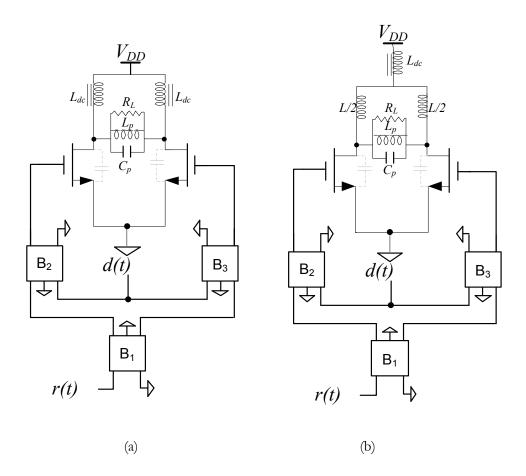

|         | 4.1.4 Common mode dither                                  | 56 |

|         | 4.1.5 Possible dithering locations                        | 56 |

|         | 4.1.6 Slope gain considerations                           | 57 |

| 4.2     | Circuit topologies                                        | 57 |

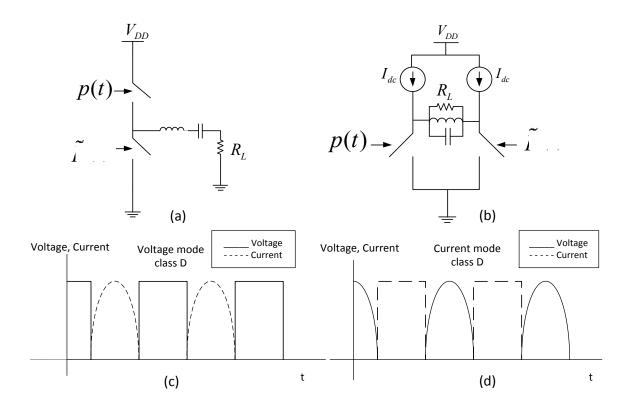

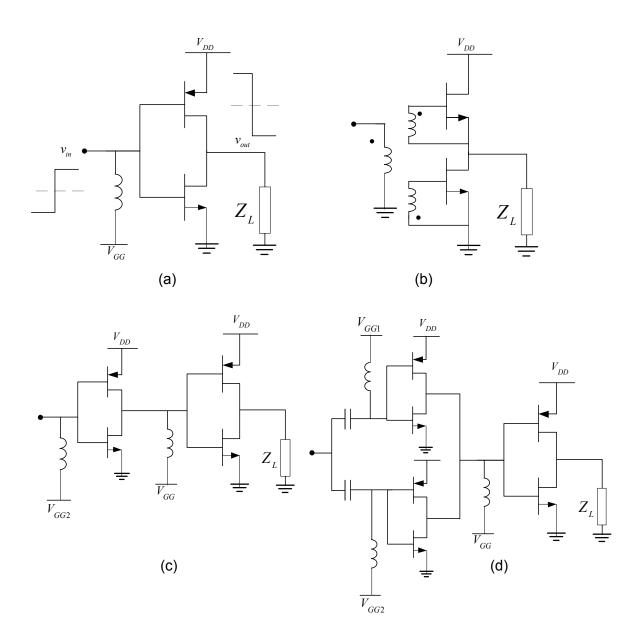

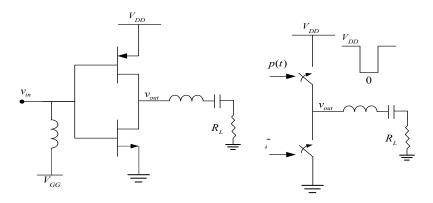

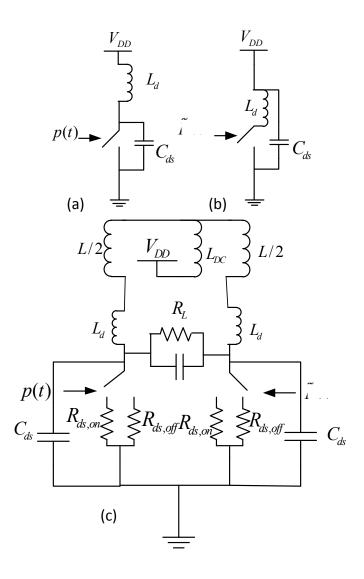

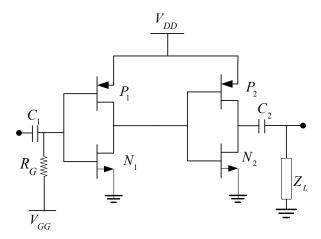

|         | 4.2.1 Voltage mode and current mode class-D               | 58 |

|         | 4.2.2 Design aspects of voltage mode class-D              | 59 |

|         | 4.2.3 Design aspects of the current mode class-D          | 68 |

| 4.3     | Dithering limitations                                     | 70 |

| 4.4     | Conclusion                                                | 71 |

| 5.Linea | arity analysis                                            | 73 |

Contents

| 5.1     | Existing methods and shortcomings 7            |     |

|---------|------------------------------------------------|-----|

| 5.2     | Signal specifications                          |     |

|         | 5.2.1 Probability distributions                | 75  |

|         | 5.2.2 Multisine representation of signals      | 76  |

|         | 5.2.3 DFT method to extract multisine          | 77  |

|         | 5.2.4 Statistical synthesis methods            | 78  |

| 5.3     | Proposed method                                | 78  |

| 5.4     | 5.4 Correlated analysis                        |     |

|         | 5.4.1 Open loop                                | 80  |

|         | 5.4.2 Closed loop                              | 80  |

| 5.5     | Nonlinear analysis                             | 83  |

|         | 5.5.1 Open loop real Gaussian                  | 84  |

|         | 5.5.2 Open loop complex Gaussian               | 86  |

|         | 5.5.3 Closed loop distortion                   | 87  |

|         | 5.5.4 Nonlinear metrics calculation            | 88  |

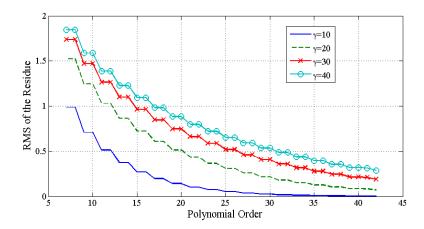

| 5.6     | Memory effects                                 | 89  |

|         | 5.6.1 Volterra series                          | 90  |

|         | 5.6.2 Wiener-Hammerstein models                | 91  |

| 5.7     | Conclusion                                     | 93  |

| 6.Spuri | ous analysis                                   | 95  |

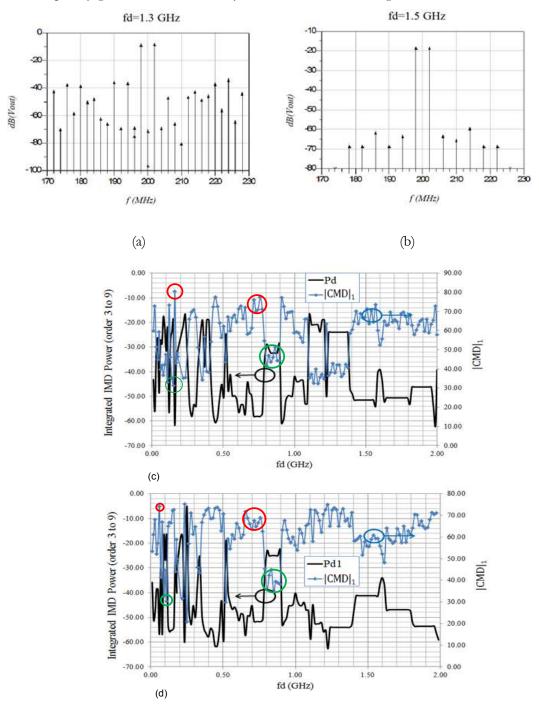

| 6.1     | Existing analysis methods and problems         | 96  |

| 6.2     | Proposed optimization approach                 | 98  |

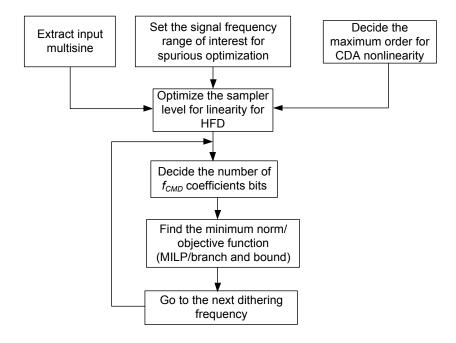

| 6.3     | Optimization technique for multi-sine          | 100 |

|         | 6.3.1 Discussion                               | 101 |

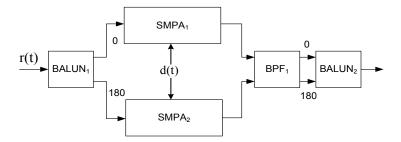

|         | 6.3.2 Common mode dithering topology           | 102 |

|         | 6.3.3 Harmonic multi-tone dither effects       | 102 |

| 6.4     | Case studies and validations                   | 103 |

| 6.5     | Applications in linearity-efficiency trade-off | 104 |

| 6.6     | Conclusion                                     | 105 |

| 7.High  | frequency dithering                            | 107 |

Contents

| 7.1             | Open loop VMCD                               | 108 |

|-----------------|----------------------------------------------|-----|

|                 | 7.1.1 Circuit design                         | 108 |

|                 | 7.1.2 Measurement and validation             | 111 |

| 7.2             | Self-oscillating class-D                     | 115 |

|                 | 7.2.1 Topology design                        | 116 |

|                 | 7.2.2 Circuit design                         | 118 |

|                 | 7.2.3 Measurement and validation             | 120 |

|                 | 7.2.4 Generic design procedure               | 122 |

| 7.3             | Conclusion                                   | 123 |

| 8.Low           | frequency dithering                          | 125 |

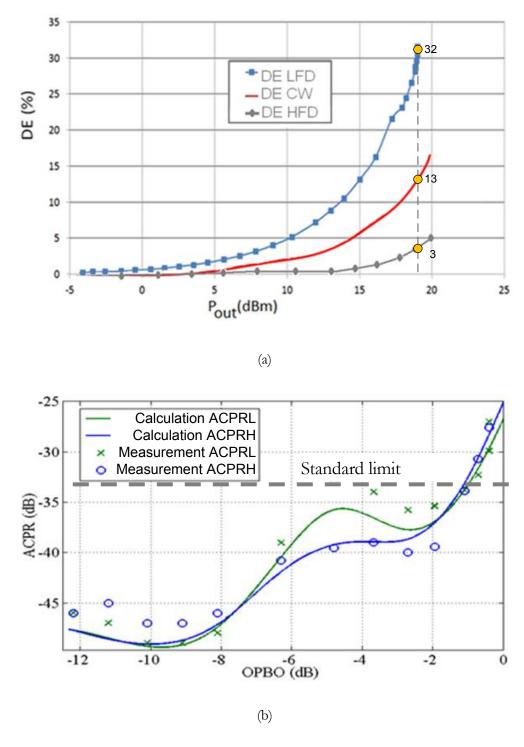

| 8.1             | Open loop VMCD                               | 126 |

|                 | 8.1.1 Fine tuning of the dithering frequency | 128 |

|                 | 8.1.2 Measurement and validation             | 128 |

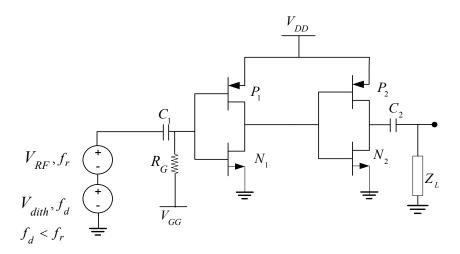

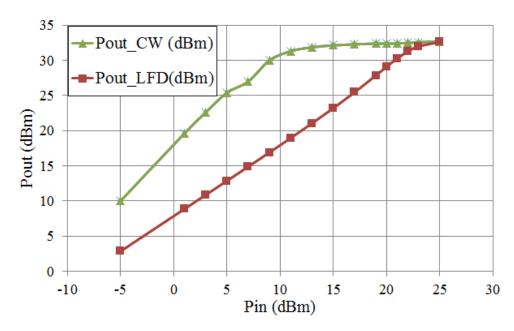

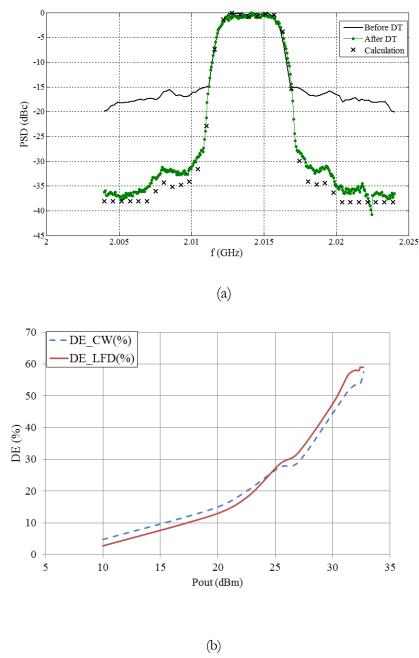

| 8.2             | Open loop CMCD                               | 130 |

|                 | 8.2.1 Circuit design                         | 130 |

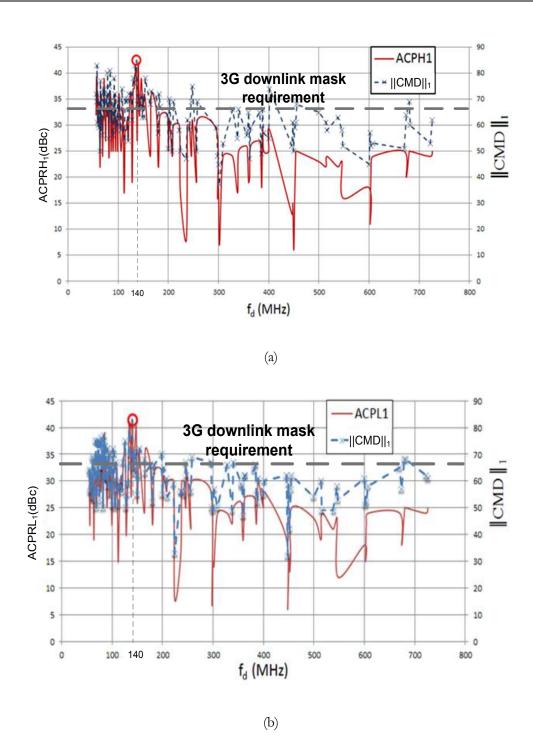

|                 | 8.2.2 Fine tuning                            | 134 |

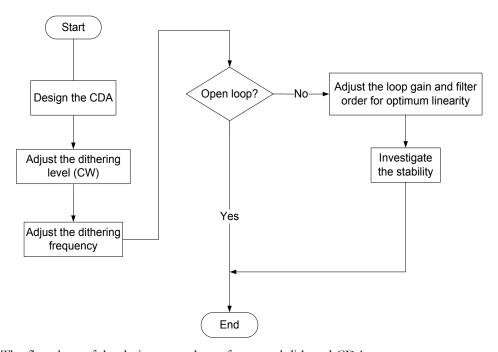

|                 | 8.2.3 Measurement and verification           | 135 |

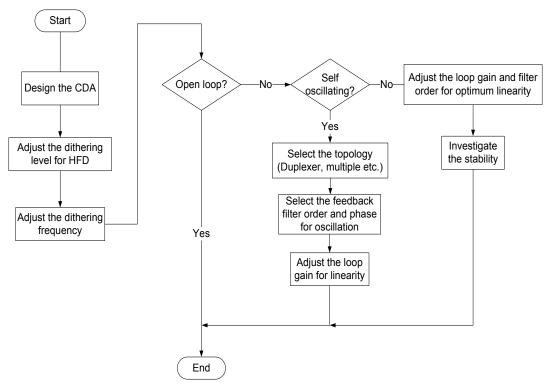

| 8.3             | Generic design procedure                     | 137 |

|                 | 8.3.1 Conclusion                             | 138 |

| 9.Nove          | l interpretations of dithering               | 139 |

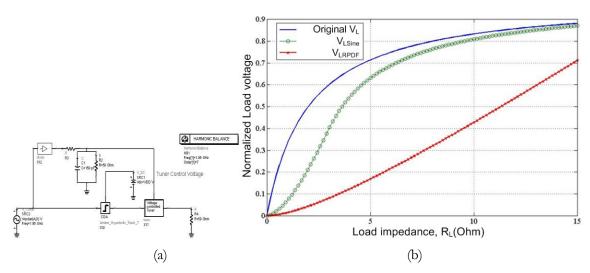

| 9.1             | Dynamic load modulation and dithering        | 140 |

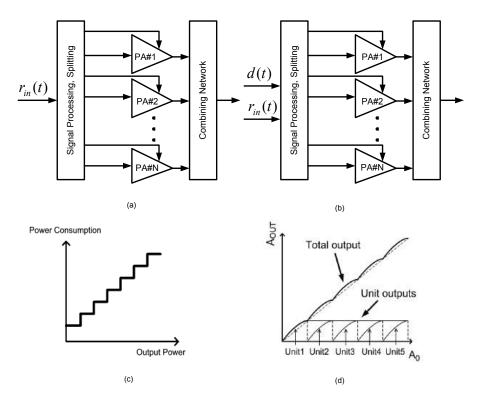

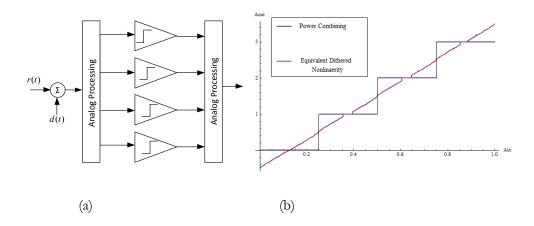

| 9.2             | Area modulation                              | 142 |

| 9.3             | RF-ADC with dithering                        | 144 |

| 9.4             | Mixer as dithering                           | 145 |

| 9.5             | Conclusion                                   | 150 |

| Conclu          | sions                                        | 151 |

| Recommendations |                                              | 153 |

| Contents |  | X |

|----------|--|---|

|----------|--|---|

| References       | 155 |

|------------------|-----|

| Publications     | 165 |

| Appendices       | 167 |

| Summary          | 177 |

| Samenvatting     | 179 |

| Acknowledgement  | 181 |

| Curriculum vitae | 183 |

Glossary

Glossary

# Glossary

| Symbol                    | Description                                                                            |

|---------------------------|----------------------------------------------------------------------------------------|

| $f_{NL}(.)$               | Nonlinear input-output operator                                                        |

| $f_{NL}^*(.)$             | Linearized (equivalent) nonlinear function after dithering and filtering               |

| f                         | Real frequency (Hz)                                                                    |

| $f_r$                     | Central frequency of the band-pass message signal (Hz)                                 |

| $\omega_r$                | Central frequency of the band-pass message signal (rad/sec)                            |

| $f_d$                     | Central frequency of the dithering signal (Hz)                                         |

| $\omega_d$                | Central frequency of the dithering signal (rad/sec)                                    |

| $\Delta f$                | Bandwidth of the input signal (Hz)                                                     |

| $\Delta\omega$            | Bandwidth of the input message signal (rad/sec)                                        |

| $\omega_{\Delta}$         | The difference between $\omega_r$ and $\omega_d$                                       |

| *                         | Convolution operator                                                                   |

| $p_d(r)$                  | Probability distribution of the message signal $r$                                     |

| $P_d(r)$                  | Cumulative probability distribution function of the signal $r$                         |

| $\mu(\alpha < r < \beta)$ | Amount of time of the time spent by the signal $r$ between values $\alpha$ and $\beta$ |

| ω                         | Radian frequency (rad/sec)                                                             |

| S                         | Complex radian frequency (rad/sec), in Laplace transformation                          |

| d(t)                      | Dithering signal                                                                       |

| $d_H(t)$                  | Dithering signal, high frequency                                                       |

| $d_L(t)$                  | Dithering signal, low frequency                                                        |

| $D_H(\omega)$             | Fourier transform of the high frequency dithering signal                               |

| $D_L(\omega)$             | Fourier transform of low frequency dithering signal                                    |

xiv

| $\boldsymbol{A}$        | Amplitude of the dithering sinusoid                                                       |

|-------------------------|-------------------------------------------------------------------------------------------|

| r(t)                    | Real Gaussian message signal                                                              |

| r[m]                    | Discrete time sampled signal of $r(t)$                                                    |

| $r_c(t)$                | Complex Gaussian message signal                                                           |

| $r_q(t)$                | A generic message signal                                                                  |

| $\tilde{r}(t)$          | Complex envelope of the complex Gaussian signal $r_c(t)$                                  |

| $r_1(t), r_2(t)$        | Real and imaginary parts of the input complex envelope                                    |

| $\sigma_r$              | Root mean square value of the signal $r$                                                  |

| $\sigma_d$              | Root mean square value of the signal $d$                                                  |

| x(t)                    | Combination of the dithering and message signals                                          |

| $\langle x(t)\rangle_k$ | k'th order average of signal $x(t)$                                                       |

| $\omega_s$              | Sampling frequency in multi-frequency averaging method                                    |

| y(t)                    | Direct output of the nonlinear block $f_{NL}$ before filtering                            |

| $N_{tones}$             | Number of tones in a multisine                                                            |

| $f_{res}$               | Tone spacing (frequency resolution) of a multisine (Hz)                                   |

| $\omega_{res}$          | Tone spacing (frequency resolution) of a multisine (rad/sec)                              |

| $y^*(t)$                | Output of the equivalent nonlinearity                                                     |

| $H(j\omega)$            | Output reconstruction filter, band pass or low pass                                       |

| h(t)                    | Impulse response function of the filter $H(j\omega)$                                      |

| h[m]                    | Discrete time impulse response of the filter                                              |

| $R_{\chi\chi}(\tau)$    | Autocorrelation function of signal $x(t)$                                                 |

| $S_{\chi\chi}(\omega)$  | Power spectral density (dBm/Hz or W/Hz).                                                  |

| $\Im(x(t))$             | Fourier transform operator on function $x(t)$                                             |

| $\mathcal{L}(x(t))$     | Laplace transformation operator on function $x(t)$                                        |

| DFT                     | Discrete Fourier transform                                                                |

| FFT                     | Fast Fourier transform                                                                    |

| IDFT                    | Inverse DFT operator                                                                      |

| P                       | Number of harmonics for a harmonic multisine dither                                       |

| $\theta_r(t)$           | The angle between the complex envelope phasor and real x axis                             |

| $\theta_1(t)$           | The angle between the superposition complex envelope phasor and                           |

| ·1(·)                   | real $x$ axis                                                                             |

| $\overline{r_1}(t)$     | Vector superposition of the sinusoidal dither complex envelope of                         |

| 1 ( )                   | the message signal The datagraphic the Fourier period representation of the output of the |

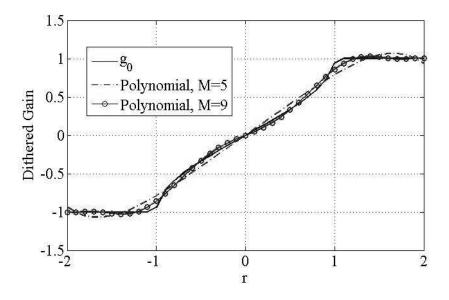

| $g_0(r)$                | The dc term in the Fourier series representation of the output of the                     |

|                         | nonlinearity, for low pass input $r$ .                                                    |

| $g_m(r)$                | Amplitude of the higher order dithering harmonics, in Fourier series.                     |

| $ar{y}$ B               | Time domain or statistical average of the time domain signal y                            |

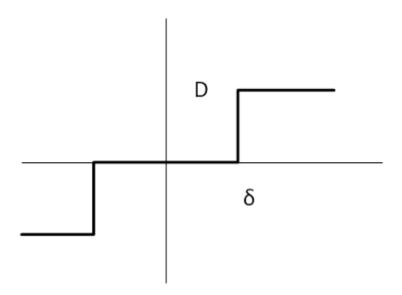

| D                       | Constant dc input to the nonlinear block                                                  |

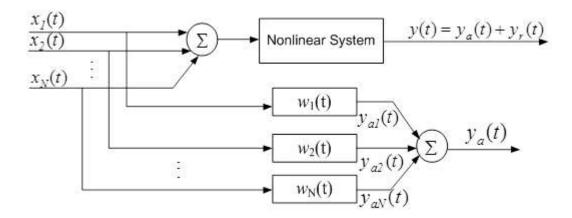

| $w_i(\tau)$             | Impulse response of the branch number $'i'$ , in the parallel filter bank approximation   |

| $v_{\cdot}(t)$          | Input signal to branch number $i'$ in equivalent parallel filter bank                     |

| $x_i(t)$                | approximation to the nonlinearity                                                         |

| $y_{ai}(t)$             | Output of the filter number $i'$ in the parallel filter bank                              |

| $y_a(t)$                | Output of the parallel filter bank                                                        |

| $y_r(t)$                | Difference of the linear approximation and original nonlinearity                          |

Glossary

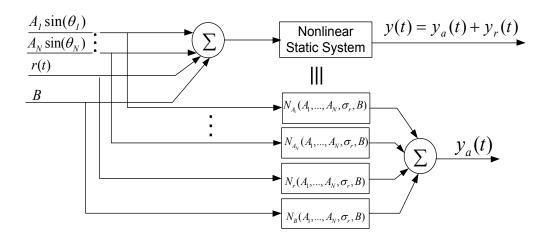

| $w_A(	au)$                      | Optimum filter impulse response for single sinusoid input to the nonlinear block            |

|---------------------------------|---------------------------------------------------------------------------------------------|

| $N_A(A,\omega)$                 | Single sinusoidal input describing function, frequency dependent                            |

| $N_{A_i}(A_1, A_2, \dots, A_N,$ | Describing function gain of combination of $N$ sinusoids, random                            |

| $\sigma_r, B$                   | signal and bias, corresponding to the sinusoidal number $'i'$ .                             |

| ,,                              | Frequency translated describing function for two in put sinusoids at                        |

| $M_{m,n,A}(A,B)$                | frequencies $\omega_A, \omega_B$ , and amplitudes $A, B$ respectively, for cross-           |

|                                 | modulation orders $m$ and $n$ .                                                             |

| $P_{m,n}(A,B), Q_{m,n}(A,B)$    | Real and imaginary parts of $M_{m,n}$ respectively                                          |

| $p_{lm}$                        | Coefficients of the surface fit for $i_D$ versus $v_{GS}$ and $v_{DS}$                      |

| $\alpha$ (t)                    | Instantaneous duty cycle of the output pulse train                                          |

| $\eta_P$                        | Coding efficiency of the output pulse train                                                 |

| $D = V_{DD}$                    | Upper level of the switched mode PA (Volts or Amperes) Supply voltage of the PA (Volts)     |

| $g_{0I}(r_1, r_2, A)$           | Describing function output for real part of the input envelope                              |

| $g_{0Q}(r_1, r_2, A)$           | Describing function output for imaginary part of the input envelope                         |

| · ·                             | Random part describing function for real Gaussian combined with a                           |

| $N_r(A,\sigma_r)$               | sinusoid with amplitude $A$                                                                 |

| N (A - )                        | Sinusoidal part describing function for real Gaussian combined with                         |

| $N_A(A,\sigma_r)$               | a sinusoid with amplitude A                                                                 |

| $Z_L(j\omega)$                  | Load impedance                                                                              |

| $C_{in}$                        | Input equivalent capacitance in the parasitic model                                         |

| $C_f$                           | Feedback equivalent capacitance in the parasitic model of VMCD                              |

| $C_{out}$                       | Output equivalent capacitance in the parasitic model                                        |

| $g_{c0}$                        | On state conductance of the switch                                                          |

| $R_{ds,on}$                     | On-state resistance of the switch                                                           |

| $R_{ds,off}$                    | Off-state resistance of the switch                                                          |

| $Z_s(j\omega)$                  | Source impedance                                                                            |

| $N_I(\sigma_r, A)$              | Describing function for real part of the input envelope                                     |

| $N_I(\sigma_r, A)$              | Describing function for imaginary part of the input envelope                                |

| $P_{dc}$                        | DC power consumption of the switched mode PA                                                |

| $P_{out}$                       | The power delivered to the load of the switched mode PA                                     |

| $\mathcal{Y}_{c}$               | Fully correlated output part of the switched mode PA                                        |

| $y_u$                           | Uncorrelated output part of the switched mode PA                                            |

| $y_{uf}$                        | Uncorrelated output part of the switched mode PA, including the                             |

| -                               | negative feedback effect in the closed loop                                                 |

| $\delta(t)$                     | Dirac delta function                                                                        |

| $\delta'(t)$                    | Doublet function                                                                            |

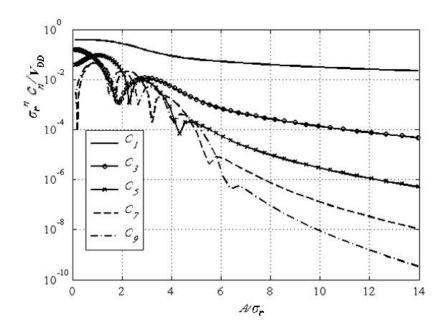

| $c_k(A,\sigma_r)$               | Correlation coefficient order k                                                             |

| i, q<br>Q                       | Real in-phase and quadrature input signals respectively Memory span in the W/H memory model |

| Y                               | memory span in the w/11 memory model                                                        |

Xvi

| $H_k(r)$                                        | Hermite polynomial of order $k$                                                                                        |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| $J_k(r)$                                        | Bessel function, first kind, order $k$                                                                                 |

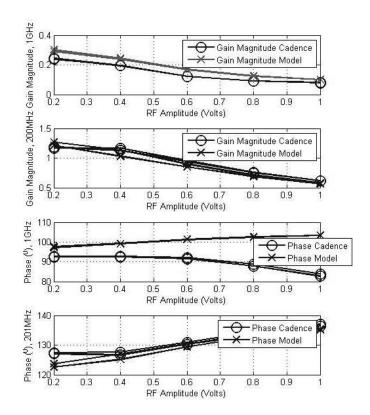

| $G_A(A, B, \omega),$<br>$G_B(A, B, \omega)$     | Calculated voltage gain of the equivalent parasitic model at frequencies $\omega_A, \omega_B$ , with amplitudes $A, B$ |

| $G_{m,A}(A,B,\omega),$<br>$G_{m,B}(A,B,\omega)$ | Measured voltage gain of the equivalent parasitic model                                                                |

| $\omega_{LC}$                                   | Limit cycle oscillation frequency                                                                                      |

| $G_F$                                           | Forward path gain in the feedback loop                                                                                 |

| $G_{S}$                                         | Subtraction gain in the negative feedback loop                                                                         |

| $\eta$                                          | Power added efficiency                                                                                                 |

| $G_f(\omega)$                                   | Forward path gain in a feedback loop                                                                                   |

| $G_{s}(\omega)$                                 | Subtraction gain in the feedback loop                                                                                  |

| $\sigma_{in}$                                   | rms value of the message signal at the CDA input                                                                       |

| $p(t), \widetilde{p(t)}$                        | Complementary input command signals of the CMCD                                                                        |

| $\ CMD\ _1$                                     | $L_1$ norm of the cross modulation                                                                                     |

| $f_{CMD}$                                       | Cross modulation frequency                                                                                             |

| $Z_L(j\omega)$                                  | Load impedance versus frequency                                                                                        |

| $G_L(\omega_{LC})$                              | The gain of the loop except CDA at the limit cycle frequency                                                           |

| $f_D$                                           | Nonlinear FIR operator                                                                                                 |

| $g(x,\dot{x})$                                  | First order functional form of the differential equation of nonlinear system                                           |

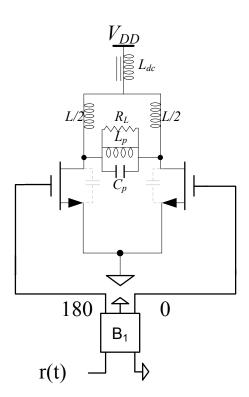

| $R_p$ , $L_p$ , $C_p$                           | Parallel tank resistance, inductance and capacitance                                                                   |

| $L_s$ , $C_s$                                   | Series resonator inductance and capacitance                                                                            |

| $R_L$ , $C_L$                                   | Equivalent parallel resistance and capacitance of the current buffer in the Gilbert cell mixer                         |

### Abbreviation Description

| F777.6 | T. 1                                 |

|--------|--------------------------------------|

| EVM    | Error vector magnitude               |

| ACPR   | Adjacent channel power ratio         |

| NPR    | Noise power ratio                    |

| MTPR   | Multi tone power ratio               |

| NBGN   | Narrow band Gaussian noise           |

| DF     | Describing function                  |

| PDF    | Probability distribution function    |

| RPDF   | Rectangular PDF (uniform)            |

| EF     | Absolute voltage gain error function |

| DE     | Drain efficiency                     |

| VMCD   | Voltage mode Class-D                 |

| CMCD   | Current mode Class-D                 |

| CMD    | Cross modulation                     |

| CDA    | Class-D amplifier                    |

| SMPA   | Switched mode PA                     |

| SOPA   | Self-oscillating Class-D             |

Glossary

LCA Limit cycle amplifier SDM Sigma delta modulator

ASDM Asynchronous sigma delta modulator

LP Load pull

LSB Least significant bit

MILP Mixed integer linear programming

PAE Power added efficiency

LFD Low frequency dithering

HFD High frequency dithering

MFA Multi frequency averaging

HB Harmonic balance

CE Circuit envelope method

*MSine* Multisine

TD Time domain approach

VIOP Volterra input output polynomial mappingEER Envelope elimination and restoration

Envelope tracking

PISPO Periodic in same periodic out

DF Describing function

SIDF Sinusoidal input describing function

TSIDF Two sinusoidal input describing function

RIDF Random input describing function

RSIDF Random plus sinusoidal describing function

PA Power amplifier

ADC Analog to digital convertor DSP Digital signal processing

EER Envelope elimination and restoration

Envelop tracking

WH Wiener Hammerstein model

PLM Power load modulation

CMD Cross modulation

PWM Pulse width modulation

CW Continuous wave

OFDM Orthogonal frequency division multiplexingWCMDA Wideband code division multiple access

QPSK Quadrature phase shift keying SNDR Signal to noise and distortion ratio

*RCE* Relative constellation error

3*G* Third generation project partnership

18 Glossary

# Chapter 1

# Introduction

Power amplifiers are the most power hungry and perhaps the most expensive part of the wireless transmitters in the RF chain. The key differentiators among different PAs are cost, yield, weight, efficiency, ease of design, reliability, ruggedness and high temperature operation. Generally, the most important of these requirements are linearity and efficiency. Modern communication systems employ high crest factor signals as a result of the urgent need of higher bandwidth efficiency. Achieving mandatory linearity constraints along with competitive efficiency requirements becomes more difficult with increased signal crest factor [37].

In the field of PA design, for linear and efficient operation, two distinct trends exist, which are either using an inherently linear PA (with poor efficiency) with supply or load modulation techniques (e.g. envelope tracking) to enhance their efficiency, while retaining the linearity (with pre-distortion or Cartesian feedback), or using inherently nonlinear (but power efficient) PAs and try to linearize them.

A sub-class of the efficient power amplifiers is known as the class of switched mode PAs (SMPA). These PAs have different classes of operation, while all of them have one thing in common: they move fast between the saturation and off-state of the devices, which makes either the voltage or the current of the device terminals of these amplifiers negligible, hence decreasing the power loss, and thus increasing the efficiency. Among them, operation classes D, E, F, F<sup>-1</sup> etc. can be named. Another similarity among them is that they all suffer from very poor linearity, i.e. because they switch between cut-off and saturation levels, they cannot reflect the real envelope variations of the input signal on the output signal, which is usually

switching between two constant levels. There are a couple of techniques, for linearization of SMPAs; among them are EER and out-phasing.

#### 1.1 Motivation

In order to obtain the required linearity-efficiency compromise with switched mode power amplifiers, various techniques are being employed in current wireless systems. Among them are polar modulation [94] and out-phasing techniques [95]. These have been discussed in detail. They use the real envelope signal to modulate a switched-mode amplifier output, or convert the modulated signal to a summation of two constant-envelope signals to be processed by switched mode PAs. The major drawback of all those techniques is the complicated signal processing that is needed for wave shaping and the poor efficiency of the tracking amplifier, which affects the overall linearization efficiency.

Besides these techniques, there are also time-domain encoding techniques, like sigma-delta modulators (SDM) or pulse-width modulators (PWM). They show good linearity-efficiency performance. In those techniques, the amplitude and phase information of a digitally modulated message signal is encoded in limited number of quantized levels of an output pulse train (e.g. zero and one for binary encoding) and their zero crossings. This makes it possible to use an efficient switched mode power amplifier like class D. The major drawback is a relatively high clocking (or sampling) frequency, which in turn will degrade the power efficiency due to more reactive power loss.

There is also a class of signal processing techniques which use an external signal to change the linearity behavior of hard nonlinearities, pruned as dithering techniques. The generic name of 'dithering' is used for this phenomenon, which is explained in the following section.

## 1.2 Dithering concept

The term 'dither' was published in books on analog computation and hydraulic controlled guns shortly after the war [96], [97]. In [108], it is stated that one of the earliest applications of dither came in World War II. Airplane bombers used mechanical computers to perform navigation and bomb trajectory calculations. These mechanical computers performed more accurately when flying on board the aircraft, and less well on ground. Engineers realized that the vibration from the aircraft reduced the error from sticky moving parts. Instead of moving in short steps, they moved more continuously. Small vibrating motors were built into the mechanical computers, and their vibration was called dither from the Middle English verb "didderen" meaning "to tremble" [108]. Dither successfully makes a digitization system a little more analog in the good sense of the word.

The concept of dithering to reduce quantization patterns was first applied by Lawrence G. Roberts [4] in his 1961 MIT master's thesis [98] and 1962 article [6] though he did not use the term dither. By 1964 dither was being used in the modern sense, described in [99].

The concept of dithering as a linearization technique is exploited in many applications. As an example, dithering has applications for linearization and for quantization noise reduction. Many analog-to-digital converter applications require low distortion for a very wide dynamic range of signals. Unfortunately, the distortion caused by digitizing an analog signal increases as the signal amplitude decreases, and is especially severe when the signal amplitude is of the same order as the quantizing step. In digital audio applications, for example, low-level signals occur often, sometimes alone and sometimes in the presence of larger signals. If these low-level signals are severely distorted by the quantization process, the usefulness of the system is greatly diminished. It is, in fact, possible to reduce the distortion, and also to improve the resolution below one LSB (least significant bit), by adding noise (or dither) to the signal of interest. For ideal converters, the optimum dither is white noise at a voltage level of about 1/3 LSB rms. The addition of dither effectively smoothes the ADC transfer function, which normally has a staircase-like appearance, but it comes with a slight reduction of the signal-to-noise ratio [100], [101].

#### 1.3 Problem statement

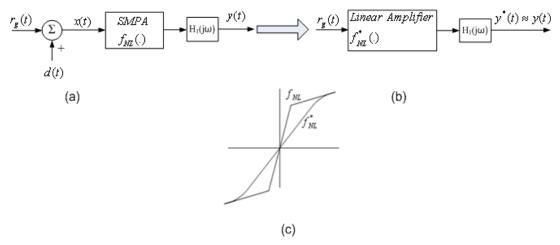

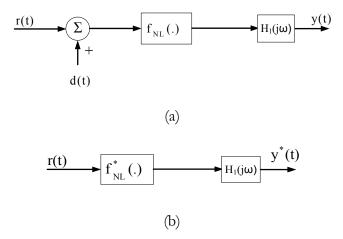

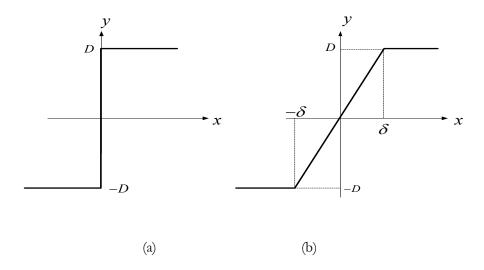

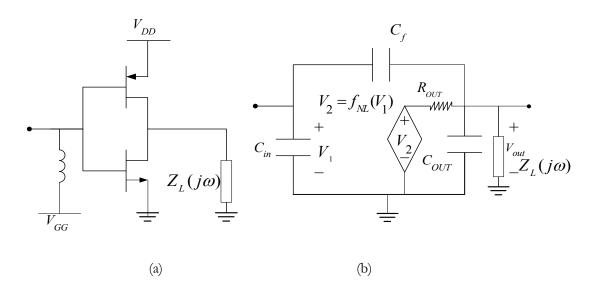

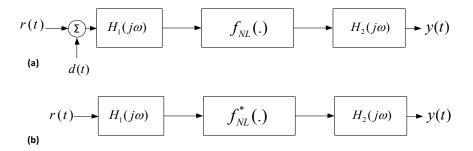

The topic of the current thesis lies in the realm of linearized SMPA design. Assuming that we have a static nonlinear input output transfer function, the problem is illustrated in Fig. 1-1. We have a signal that is called  $r_g(t)$  which is a band-limited (either a low pass or band-pass signal), and we have a static nonlinear input-output characteristic  $y = f_{NL}(x)$ , which is a single input

single output mapping function to describe the nonlinear block. The block resembles many types of common switched mode power amplifiers in which the switching device in the block is changing its state between off and saturation states, if we ignore the memory effects. The

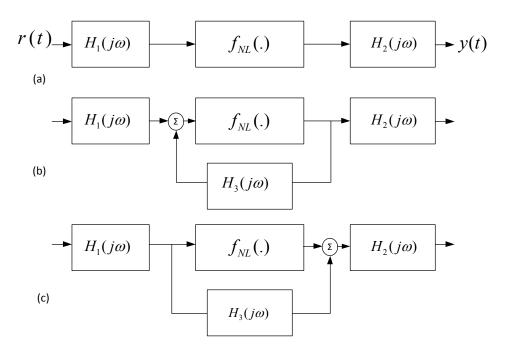

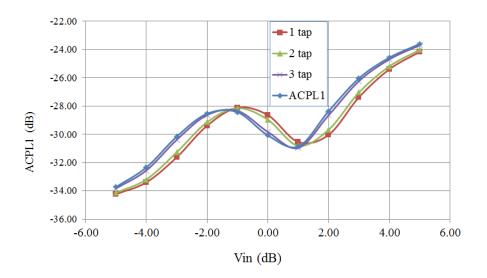

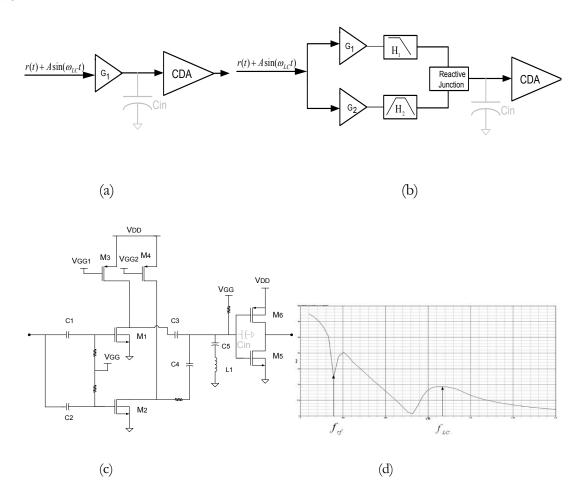

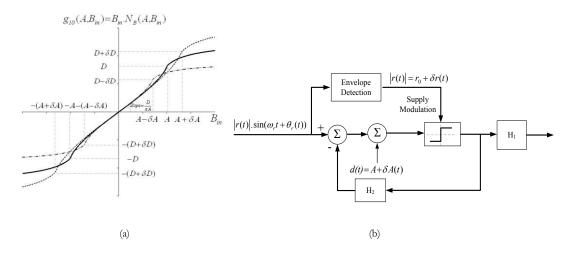

Fig. 1-1: (a): The problem of dithering, as the dither signal d(t), combined with a generic input signal  $r_g(t)$  is applied to an single input single output transfer characteristic  $y = f_{NL}(x)$ ; (b): the equivalent problem formulation, and(c): the relationship between the smoothed equivalent function and original function

goal is to find the effect of the dithering on the input-output characteristics and to find the conditions that must be fulfilled to satisfy this transformation. Therefore, the main problem can be stated as follows:

Is the dithering technique a feasible solution for simultaneous improvement of linearity and efficiency?

In view of the mentioned problem, the following questions can arise:

- 1. How can a generic theoretical framework be developed to formulate the linearity and efficiency parameters of the dithered system?

- 2. What are the effects of the system parameters on the dithered performance?, i.e.:

- a. What is the effect of the amplifier slope gain on overall performance?

- b. What is the effect of the process technology related reactive loss on the overall performance?

- c. Which circuit topologies show promising performance under dithering?

- 3. Which kinds of signals (e.g. sinusoids, random, ramp, etc.) can be used as dithering for linearity-efficiency improvement?

- a. What is the effect of the dither probability distribution on linearity and efficiency?

- b. What is the effect of frequency content of the dither on linearity and efficiency?

- c. What is the effect of dither frequency on linearity?

- d. What is the effect of the dither level on the linearity-efficiency performance?

- e. Are there any optimum frequency allocations for dither, for best linearity-efficiency compromise? If so, how can those optimum points be obtained?

- 4. Is there any general design procedure for a dithered amplifier?

- 5. Can the insight achieved from dithering analysis lead to new analog dithering applications?

# 1.4 Limitations of existing analysis methods

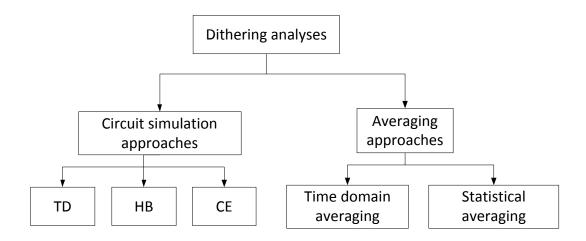

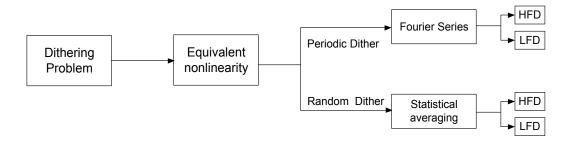

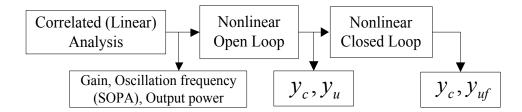

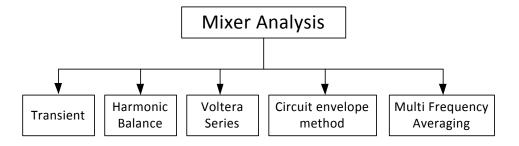

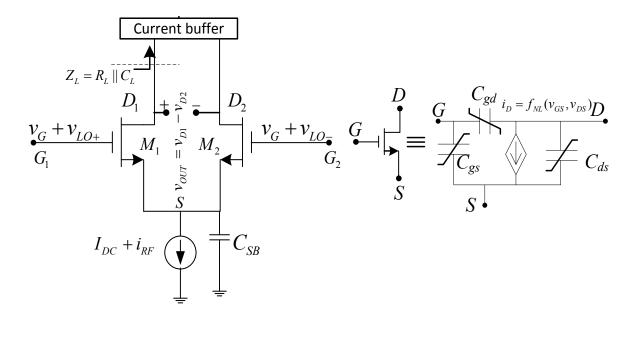

The status of current simulation techniques covers a wide range of studies for specific applications. In the field of power amplifiers, generally two different analysis approaches are taken, which are circuit simulation approaches and behavioral-modeling approaches, also called averaging approaches; both classes are illustrated in Fig. 1-2.

Fig. 1-2: Different approaches taken in the analyses of dithered SMPA

The circuit simulation approaches, like time domain (TD), harmonic balance (HB) or circuit envelope (CE), are numerical state of the art techniques which are suitable for any circuit topology with any kind of process technology. There are, however, many difficulties and problems in using these methods. Among them are the convergence problems, and the simulation time. In HB or CE, the number of harmonics and mixing orders should be high enough, to get accurate enough results [102], [103]. Moreover the circuit simulation techniques are not insightful regarding the intuitive effect of the dither properties on the nonlinearity.

As an alternative approach, averaging techniques are fully developed for dither problems in which the dither frequency approaches infinity; the limits imposed on the dither frequency are abstract and somehow unrealistic, but in this thesis we will show that they can be extended to be applied to real scenarios, for linearization of switched mode power amplifiers.

### 1.5 Aim of the project

The main objective of this thesis is to investigate new dithering based techniques and topologies, in order to linearize switched mode amplifiers and at the same time improve their linearity-efficiency trade-off.

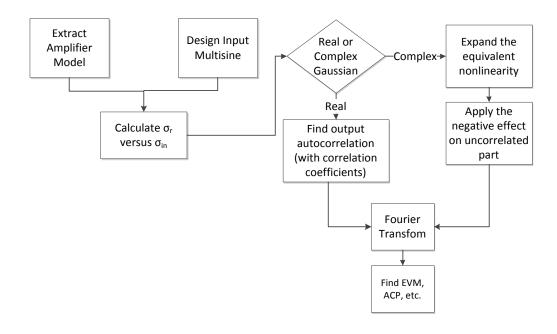

The effect of the dither frequency content and its statistical properties on linearity and efficiency of the dithered amplifier will be investigated. Behavioral modeling of the linearity metrics versus the dither level will be performed for general applications, including random input signals. Also an effort will be made in order to find the generic nonlinear metrics of a dithered system for wireless applications, like adjacent channel power ratio and error vector magnitude. Moreover design procedures are investigated for proper topologies, and for real applications.

# 1.6 Proposed approach

The approach taken in this thesis is the averaging-based technique to describe the transformation and the second order effects of the dither on nonlinear systems. The averaging techniques are based on the method developed by Bussgang and Zames et.al. in [34], [93] and later on used by Gelb et.al [4] to develop the describing function theory.

The idea of equivalent nonlinearity in nonlinear control theory will be applied to dither frequencies which are either close to or even below the input message signal. Therefore, techniques will be developed to extract the smoothing effect of the dither in terms of realistic linearity metrics that are used for real power amplifiers in wireless applications.

#### 1.7 Thesis outline

This thesis is structured as follows: chapter 2 introduces the idea of dither, categorizes the dither based on its frequency content compared to the message signal, and develops the idea of equivalent nonlinearity. Fourier series and statistical averaging methods are introduced to extract the equivalent function.

Chapter 3 introduces the idea of describing function as a tool for correlated analysis of the nonlinear blocks. Chapter 4 presents the circuit topologies and architectures that are suitable for application of dithering to obtain a linear and efficient PA in a real scenario. Chapter 5 deals with the linearity analysis, of the dithered PA, based on describing function and orthogonalization of the output components, through which all of the important PA metrics are achieved. Chapter 6 deals with the second order spurious effect and its relationship with the frequency content of the dither, and methods to optimize the dither signal, or to minimize the resulting spurious components.

Finally, all the theoretical findings are put into test, through the systems that were realized and evaluated in chapters 7 and 8. In those chapters, two open-loop switched-mode amplifiers and one self-oscillating architecture are realized and tested, and the expectations are approved by measurement results.

Chapter 9 discusses the possible applications of dithering in future systems, and the potential of the averaging techniques for mixer analysis.

# Chapter 2

# Dithering

Analog dithering is an elegant way to modify hard nonlinearities. In servomechanism study in control theory, dither has been defined as a high frequency signal, compared to system dynamics, that will reduce the sector size of the nonlinear characteristic [34, 64]. This is in turn related to system characteristics such as stability and linearity. However this definition does not cover all of the possible applications of the concept for any kind of dynamics and input frequency content to the system.

In this chapter, first a general and broader definition of the dithering concept is introduced. Then the concept of 'equivalent nonlinearity' is defined. This functional equivalence explains the linearization process in terms of dithering and simplifies the analysis of the dithered system. The insight obtained from equivalent nonlinearity can be utilized to find the distortion of amplifiers.

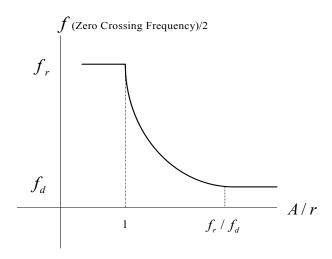

Based on the dithering frequency, the dithering process can be divided to high and low frequency. If the dither frequency is much higher than the maximum input frequency, it is called high frequency dithering; reversely, if it is lower than the zero crossing rate of the input bandpass signal, it is called low frequency dithering.

Two approaches can be followed in parallel, to obtain the equivalent nonlinearity function, which are called Fourier series method and the statistical method. The first approach is based on Fourier expansion, the second one relies on the statistical averaging concept. The advantages and disadvantages of each method are discussed in detail.

The frequency content of the high and low frequency dithering are studied based on the generic output spectral form. A different bandwidth constraint formula is derived for each. Afterwards the statistical conceptual model is applied to high and low frequency to derive the equivalent nonlinearity.

# 2.1 Dithering concept

Dithering is injection of an external signal to a linear or nonlinear system to obtain several possible objectives. Among them are augmenting the linearity of the open or closed loop system, robustness, and asymptotic stability, for a general class of nonlinear apparatus, reduction of quantization noise in data convertors; and adaptive enhancement of the closed loop linearity. The dithering can also be utilized to affect the dynamic behavior of the system and stop undesired chaotic behavior or undesired limit cycle oscillations in the system, or alleviate the resonance jump phenomenon in sliding mode control applications [4].

The dithering signal may be analog or digital, and can have any statistical and spectral characteristics. It can be a random or a deterministic signal and it can be correlated or uncorrelated to the input signal. Being a random signal, its value at each moment can be dependent or independent of its previous values in time, or in the other words it can be with memory or memory

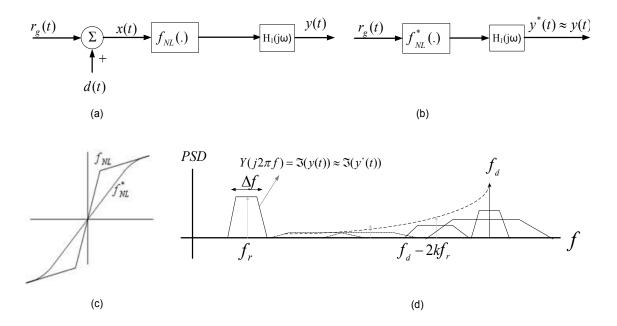

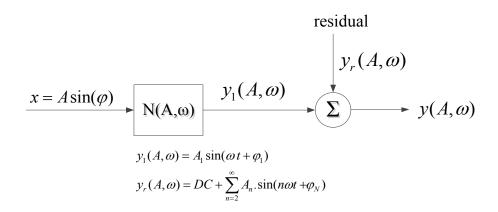

Fig. 2-1:(a) Continuous time dithering applied to a nonlinear apparatus; (b): equivalent nonlinearity concept model; (c): the shape of a hard nonlinearity  $f_{NL}$  is effectively transformed to softer one  $f^*_{NL}$ ; (d): the output frequency domain content of the linear operator  $f_{NL}$ .  $f^*_{NL}$  will generate the same baseband part as  $f_{NL}$  at the output of the filter.

less.

In case of having a nonlinear system, described with a general input output nonlinear tor  $y = f_{NL}(x)$ , the concept of the dithering is illustrated in Fig. 2-1-a, wherein signal d(t) is the continuous time dithering, x(t) is the input signal, and y(t) is the output signal of the nonlinear system. The output of the system is related to the total input as:

$$y = h_1(t) * f_{NL}(x(t)) = h_1(t) * f_{NL}(r_g(t) + d(t))$$

(2-1)

where  $h_1(t)$  is the impulse response of the filter  $H_1(j\omega)$ . Having a mathematical description of the single-input single-output  $f_{NL}(.)$  we can find the output response to any desired input. The only assumption is that the  $f_{NL}$  function is assumed to be memory-less, i.e. its output at each moment depends only on its input at the same instant.

# 2.2 Equivalent nonlinearity

The most important effect of dithering is *linearization* of hard nonlinear characteristics, i.e. the original nonlinearity is transformed to another one which has a smaller 'sector size', as depicted in Fig. 2-1-c. This is due to the fact that the *dither effectively acts as a moving average filter, and applying this kind of process to a hard nonlinearity, will always make it softer*, provided that the proceeding filter  $H_1$  is able to omit the undesirable spurious components at the output. This property is illustrated in Fig. 0-1-c, where the  $f^*_{NL}$  is the equivalent (linearized) nonlinearity, after applying dither signal d(t) to  $f_{NL}$  and proceeding filtering of its output. From now on, this new (transformed) mathematical operator is called equivalent nonlinearity.

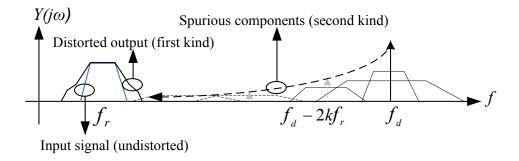

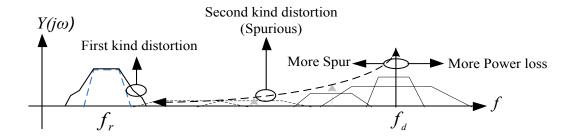

In other terms, equivalent nonlinearity is a new function, which includes the linearization effect of the dithering signal. If the input  $r_g(t)$  is a base-band signal (extending from dc to maximum frequency of  $f_r$ ), and the dithering frequency is a higher frequency, the output of the original nonlinearity will include a replication of the signal (with in-band distortion) and sidebands around the dithering signal frequency component and its higher order harmonics, as shown in Fig. 2-1-d.

The mathematical mechanism behind this phenomenon will be discussed more in the upcoming sections, and in chapter 3. So the definition of the equivalent nonlinearity implies that the output filter  $H_1(j\omega)$  has enough out of band rejection to omit the sidebands around the dithering frequency (and its harmonics) resulting in an output signal processed by the  $f^*(.)$  equivalent operator. The main advantages of the equivalent nonlinearity are:

<sup>1</sup> The sector size is defined as the maximum angle between the line crossing origin, and the horizontal axis. Generally a system with less sector size is assumed to be smoother.

1. It is a single input single output system: the effect of the dithering signal is embedded within the new function; therefore we won't need to analyze the system for combination of two input signals.

- 2. The equivalent function is a softer nonlinearity. Hence, it is much simpler to analyze. The extreme case is having an ideal limiter, which is very memory-intensive to analyze with numerical methods (due to discontinuity of the output). The 'softened' or linearized version of it is of a lower polynomial order and is easier to analyze with commercial simulators.

- 3. The formulation of the equivalent nonlinearity is insightful to understand the dithering effect intuitively.

The downside of the equivalent nonlinearity model is that it does not take into account the spurious side-bands of the dither frequency that penetrate into the signal band-width. When the frequency of the dither is chosen close to the bandwidth edge, it is impossible to filter out the spurs and they affect and degrade the linearity of the system as well. This issue is illustrated in Fig. 2-1-d, where the modulated side-bands penetrate into the input signal band when we reduce the  $f_d$ .

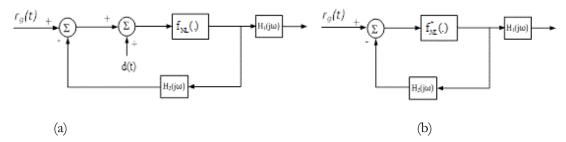

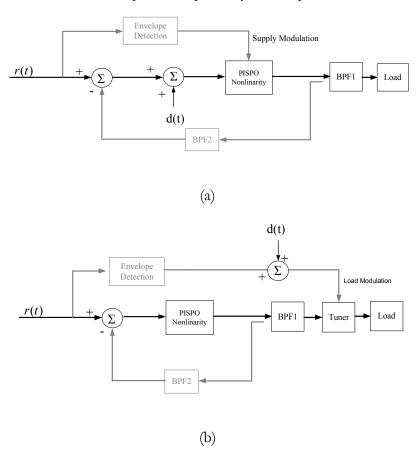

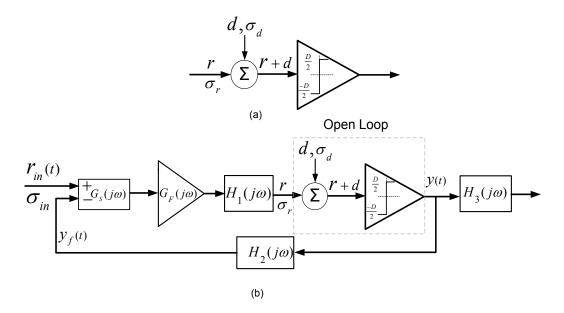

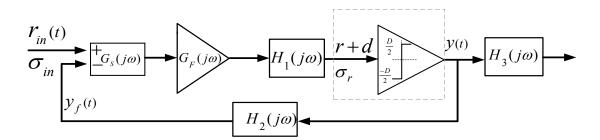

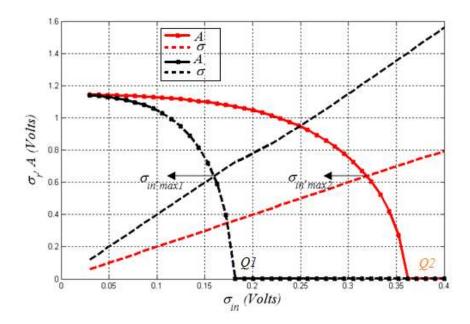

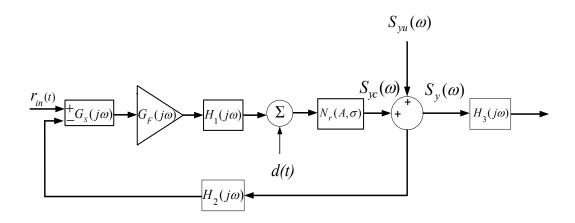

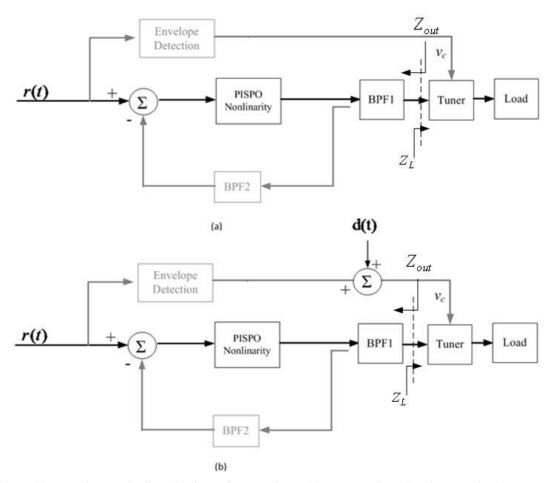

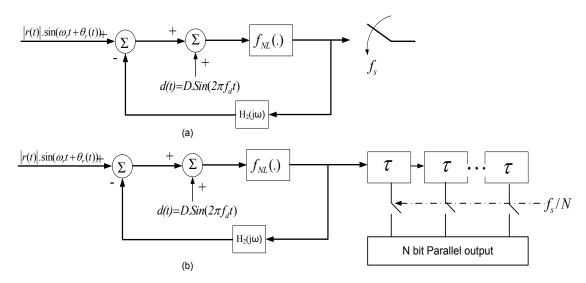

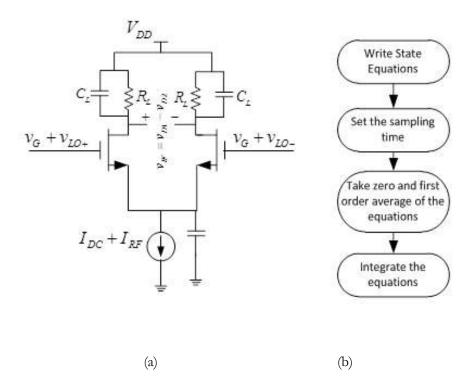

The system in which the dithering is applied to may be placed in an environment that provides sort of feedback from output to the input, or is intentionally designed to have a feedback, as illustrated in block diagram of Fig.2-2. The same concept of equivalent nonlinearity can also be used for the analysis of dithering in a negative feedback loop, provided that the feedback filter ( $H_2$  in Fig. 2-2) is sharp enough to effectively omit the dither component and its modulated side band spurious.

The complete analysis of the systems in Figures 2-1 and 2-2 means determination of signals in time and frequency domain in different points of the block diagram. For a linear systems analysis, everything is determined by the impulse response of the system. The output of the system is related to the input through the convolution integral.

$$y(t) = x(t) * h(t) = \int_{-\infty}^{\infty} x(\tau) . h(t, \tau) d\tau$$

(2-2)

or equivalently in frequency domain,  $Y(j\omega) = X(j\omega)$ . There are also several properties attributed to the linear systems and they are considered equivalent to each other: existence

Fig. 2-2 (a): Continuous time dithering applied to a nonlinear apparatus with negative feedback; (b): equivalent system, using the concept of equivalent nonlinearity.

and uniqueness of the solution for a given known input, continuous dependence of the output on the input and boundedness of the output in case of boundedness of the input.

These properties are not fulfilled even in the simplest cases of a memory-less nonlinear system. Some examples and reviews are given in [64]. Any system for which the superposition principle does not hold is defined to be nonlinear. In this case there is no possibility of generalizing from the responses for any class of inputs to the response for any other input. This constitutes a fundamental and important difficulty which necessarily requires any study of nonlinear systems to be quite specific. One can attempt to calculate the response for a specific case of initial conditions and input, but make very little inference based on this result regarding response characteristics in other cases.

In order to understand and be able to mathematically describe the behavior, the nonlinear system has to be described. There are several approaches to define and describe the nonlinear block performance. The analysis will be focused on the system block diagram of Fig. 2-1. The methods and necessary tools will be developed to find the response of the open loop system to some classes of input signal and the results obtained will be used for the nonlinear feedback system of Fig. 2-2. From now on, for the sake of simplicity, we limit the scope of discussion to memory-less nonlinearity, i.e. the output of the nonlinear system can only depend on its input at the same time and  $f_{NL}$  is a static single valued function. The memory effect model and analysis will be presented in section 5.3.

# 2.3 High and low frequency dithering

The dithering signal frequency can be classified to two different modes: dithering frequencies which are higher than the input signal frequencies, which we call high frequency dithering (HFD) and those which are below the input signal frequencies and are called low frequency dithering (LFD).

The low frequency dithering can be used for linearization of a nonlinear system, that process band-pass input signals. The band pass signals are defined as those signals which have no spectral components below a certain frequency. High frequency can be used for any kind of input

Fig. 2-3: Different approaches for random, high and low frequency dithers

signal including DC, below the dithering frequency. The main difference in formulation of equivalent nonlinearity for high and low frequency dithering is that for high frequency, the rate of variations of the dither is usually much higher than the input signal, therefore the equivalent nonlinearity is obviously time-invariant, and high frequency fluctuations are averaged out simply by a low pass filter placed at the output. On the other hand, for low frequency dithering, the dither signal dynamics is slower with regards to the signal value, but should be much higher than the envelope bandwidth. In case of low frequency dithering, the averaging process is performed on the complex envelope of the band-pass input signal. Hence in terms of instantaneous value, the system is time variant and therefore the equivalent nonlinearity versus value is meaningless. Due to this basic difference, the equivalent nonlinearity is defined versus value in high frequency and versus envelope value in low frequency dithering, as will be explained and formulated mathematically in 2.5. The spectral distribution for the high and low frequency cases imposes two different estimations of the 'linear bandwidth'<sup>2</sup>, and those estimations are given in section 2.4.

There are two basic methods to calculate the equivalent nonlinearity, which are namely Fourier series expansion approach (assuming a periodic high or low frequency dither) or time domain averaging and statistical averaging approach.

The first approach is based on multi-dimensional Fourier expansion of the output versus input, for periodic input, while the second one is applicable to any kind of dither signal, under certain mathematical assumptions. The assumption made about the dither in the latter is weaker than the periodicity and the dither should only be 'repetitive', i.e. its value probability distribution function should repeat itself versus time. A good example of repetitive signal is a two tone signal, when the two tones are not harmonically related. By this definition all of the periodic signals are repetitive but *not* vice versa. The advantage of statistical view is that it is generic in terms of input signal, and it is applicable to a broad family of signals, including periodic signals.

The drawback of the statistical view compared to the Fourier series expansion is that it overlooks the spurious sidebands around the dithering frequency and its harmonics. These components can be harmful to the signal integrity, but sometimes are unavoidable, especially when the dither frequency is close to the signal, as illustrated in Fig. 2-1-d. When the modulated spurious sidebands penetrate into the signal band, the linearity is always compromised. On the other hand, calculation of the Fourier coefficients for a general input signal and a general periodic dither can be very time consuming, tedious and memory-intensive, especially when the number of the frequency components grows large. An alternative approach to find the equivalent nonlinearity is developed in chapter 6.

In the following parts, first an intuitive understanding of the smoothing mechanism, based on rotating vector representation, for sinusoidal dither, is introduced. Then the Fourier series based approach for memory-less nonlinearities is explained, for high and low frequency. Afterwards the statistical point of view is developed for these two modes and different formulas

<sup>&</sup>lt;sup>2</sup> Linear bandwidth is the frequency range in which the spurious are low enough and the overall linearity is good.

for equivalent nonlinearity are derived, based on the value for high and envelope for low frequency dithering. Fig. 2-3 sums up the order and distinction of the two approaches to dithering problem. The memory effect can be super-imposed to the analysis on both of the approaches, and is discussed detail in chapter 5.

# 2.4 Rotating vector representation

An intuitive understanding of the dithering effect for sinusoidal dither can be obtained through the following expansion of the entire complex envelope around carrier frequency  $\omega_r$ :

$$x(t) = |r_g(t)| \sin(\omega_r t + \theta_r(t)) + A\sin(\omega_d t)$$

$$= r_1(t) \sin(\omega_r t + \theta_1(t))$$

(2-3-a)

while  $r_1(t)$  is the vector superposition of the phasors of the input complex envelope r(t) and the dithering phasor  $Aexp(j\omega_{\Delta}t)$ , as follows:

$$r_1(t) \triangleq \left| \left| r_g(t) \right| exp(j\theta_r(t)) + Aexp(j\omega_{\Delta}t) \right|$$

(2-3-b)

and  $\omega_{\Delta} = \omega_r - \omega_d$ .

Provided that the rotation speed of the dithering is much higher than that of the input signal

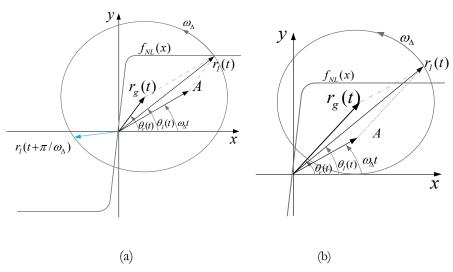

Fig. 2-4: Illustration of sinusoidal low frequency dithering effect on envelope r. The effective complex envelope vector rotates around a circle with a frequency much higher than the signal bandwidth (a): Linear averaging as the superposition vector sees the negative and positive values with proportion to the signal; (b): saturated averaging, in which the time duration experienced by summation is limited to either positive or negative y axis.

complex envelope bandwidth (i.e.  $\omega_d \gg \Delta \omega$ ), we can assume that the vector  $\overline{r_g}(t)$  is not moving in time and the dither vector is rotating around it with an angular speed of  $\omega_{\Delta}$ . Then after the averaging process (through a band-pass filter around  $\omega_r$  or a low pass filter from zero to frequency  $\omega_r$ ) the system would be effectively time invariant with respect to the input envelope  $r_g(t)$ .

The averaging process is depicted in the diagram of Figs. 2-4-(a, b) in the x-y plane, in which x and y represent the input and output signals of the nonlinear block respectively  $(y = f_{NL}(x))$ , and the imaginary part of the output complex envelope. The tip of the superposition vector  $r_1(t)$  (sum of rotating A, and  $r_g(t)$ ) moves along a circle. This circle is centered at point  $r_g(t)$  and its radius is the dither amplitude A.

Depending on the relative amplitudes of the dither and signal vectors, two different situations can be distinguished as follows:

- 1. Linear operation: For  $|r_g(t)| < A$ , as illustrated in Fig. 2-4-a, the dither component acts like a moving average filter and the average of the rotating vector will be proportional to the input vector  $r_g(t)$ , as long as the mapping of  $r_1(t)$  on the y axis passes through both positive and negative y. Intuitively, the average of the projection on the y axis will be proportional to the amplitude of the input signal  $r_g(t)$  and thus the dithering makes the hard saturation function linear.

- 2. Saturation: When the value of r(t) becomes larger than A ( $|r_g(t)| \ge A$ ), the superposition vector  $r_1(t)$  will be entirely projected on the positive (or entirely negative depending on the input sign) side of y, as shown in Fig. 2-4-b, which drives the nonlinear system into positive or negative saturation.

Hence the saturation threshold is a function of  $r_g/A$  ratio. The linearization effect will also depend on the average time spent in positive and negative sides of the x axis, which is not uniform for sinusoidal dither.

It should be noted that the same interpretation is true for the real part of the output envelope, either if the superposition signal is projected on the x axis and x is a saturation function of y instead, or using the same chart as Fig. 2-4, for another vector orthogonal to the original one. This intuitive demonstration is valid for both HFD and LFD sinusoidal ditherings.

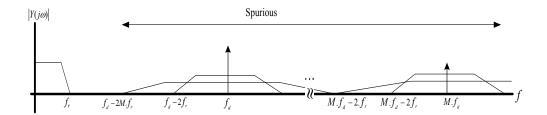

Fig. 2-5 Frequency content, the output of the nonlinear component after a high frequency dithering, with a single frequency  $f_d$ .

# 2.5 Fourier series approach

As long as the dithering signal is periodic, two-dimensional Fourier series expansion in combination with time domain averaging is a viable approach to extract the equivalent nonlinearity. We need to assume that the dither and signals frequency are non-commensurable, to have two degrees of freedom in Fourier series. Another way to express that condition in practical situations is to assume that the greatest common divisor of the two frequencies is much smaller than both of them:  $\gcd(f_d, f_r) \ll f_d, f_r$  provided that both of the frequencies are integers. This should be true for both HFD and LFD.

#### 2.5.1 High frequency dithering

In high frequency case, the dither signal, denoted as  $d_H(t)$  is assumed to have a frequency much higher than the maximum frequency component of the input signal  $r_g(t)$ . Usually the fundamental frequency of  $d_H(t)$ , or the minimum frequency component of its Fourier transform  $D_H(\omega)$  is much higher than the input signal frequency.

The dithering signal  $d_H(t)$  can be expressed as:

$$d_H(t) = \sum_{m=1}^p D_m \cdot \sin(m\omega_d t + \varphi_m), \text{ while } \omega_d \gg \omega_r$$

(2-4)

in which subscript H denotes high frequency as expressed by the condition. The output of the nonlinear operator is a function of the signal x(t), which has a combination of the input signal frequency and dithering frequency.  $f_{NL}$  can be expanded in a two dimensional Fourier series as:

$$y(t) = f_{NL}\left(r_g(t) + d_H(t)\right) = \sum_{m=0}^{\infty} g_m(r_g) \cdot \sin(m\omega_d t + \varphi_m) =$$

$$g_0(r_g, D_1, D_2, ..., D_P) + \sum_{m=1}^{\infty} g_m(r_g, D_1, D_2, ..., D_P) \cdot \sin(m\omega_d t + \varphi_m)$$

(2-5)

where  $g_0(r)$  is the transformed nonlinearity characteristic, shaped (linearized) by the high frequency dither  $d_H$  or the equivalent nonlinearity defined in section 2-2. There are averaging methods to achieve this term of the Fourier series which will be explained in the coming sections.

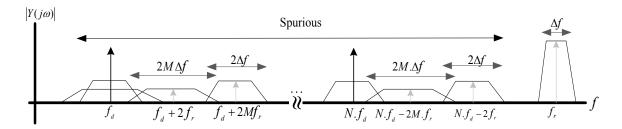

Fig. 2-6 Low frequency dithered frequency content, the output of the nonlinear component, with a single frequency  $f_d$ .

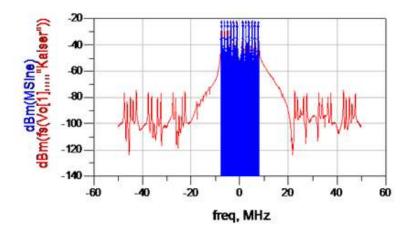

Under assumption of odd nonlinear characteristics for  $f_{NL}$ , Fig. 2-5 shows the output spectral content for a general nonlinear function  $f_{NL}$  in which the right hand term of (2-5) is truncated to 2M+1. As we see from the figure, the closest modulated sideband of the output of the nonlinearity had a widened and up converted version of the input, with intermodulation order of 2M.

#### 2.5.2 Low frequency dithering

The injection of a dither component with the main frequency lower than the input band pass signal  $(f_r)$  can again modify and linearize the nonlinear characteristics. The dither is called  $d_L$  as:

$$d_L(t) = \sum_{m=1}^{p} D_m \cdot \sin(m\omega_d t + \varphi_m), \text{ while } \omega_d < \omega_r$$

and the input is a band pass modulated signal around a central frequency  $f_r$ :

$$r_g(t) = Re\{\widetilde{r}_g(t).\exp(j\omega_r t + \varphi_r(t))\} = |\widetilde{r}_g(t)|.\cos(\omega_r t + \varphi_r(t))$$

(2-6)

As  $\omega_r = 2\pi f_r$  and  $\tilde{r}_g(t)$  is the complex envelope of the signal. The output Fourier series expansion can be written as:

$$y(t) = f_{NL} \left( r_g(t) + d_L(t) \right) =$$

$$\sum_{m,n=0}^{\infty}g_{mn}\big(\widetilde{r_g}(t),D_1,D_2,\dots,D_P\big).\sin\big(m\omega_rt+\varphi_r(t)+n\omega_d\,t\big)=$$

$$g_{10}(\tilde{r}_{g}(t), D_{1}, D_{2}, ..., D_{P}) + \sum_{m,n=1}^{\infty} g_{mn}(\tilde{r}_{g}(t), D_{1}, D_{2}, ..., D_{P}). \sin(m\omega_{r}t + \varphi_{r}(t) + n\omega dt)$$

(2-7)

while again  $g_{10}(r, D_1, D_2, ..., D_p)$  is the equivalent nonlinearity  $f_{NL}^*$  defined in section 2-2 and will be derived again in part 2-6. The generic spectral domain is according to equation (2-7) is depicted in Fig. 2-6, where again like high frequency case, the odd nonlinearity order is truncated to 2M+1 instead of  $\infty$ .

If the input signal is selected 'properly', so that the spurs don't interfere with the desired signal band,  $g_{10}$  is capable of linear amplification-processing of the input signal. This will be explained in detail in chapter 5.

When the dither frequency is selected to be much higher than the input signal, according to Fig. 2-5, the spurious sidebands won't affect the original linearized signal. This provides a way to estimate the bandwidth  $f_{rH}$ , as to avoid overlap between the M'th order sideband and original signal at the output:

$$f_d - 2Mf_{rH} > f_{rH} \tag{2-8}$$

which yields to the following equation:

$$f_{rH} < \frac{f_d}{2M+1} \tag{2-9}$$

where again the subscript H denotes high frequency dithering. By setting the M, the upper bound is derived for the bandwidth  $f_{rH}$ . The order M will depend on the order of the hard nonlinearity. Setting M=1, results in  $\frac{f_d}{3}$  as the fundamental limit, which agrees with the time domain analysis in [1].

For low frequency dithering, the fundamental dithering frequency  $f_d$  has to be at least half the band-width of the input signal and the input and dithering frequencies should be incommensurable. This can be explained based on the condition of not overlapping modulated dither around input carrier at  $f_r - f_d$  with the signal itself, as:

$$f_r - f_d < f_r - \frac{\Delta f_{max}}{2} \qquad \qquad \therefore \qquad \qquad f_d > \frac{\Delta f_{max}}{2} \tag{2-10}$$

The linearization process is illustrated in Fig. 2-5. The dither and its higher order harmonics will absorb the spurious cross modulations and the input signal is processed without distortion.

Based on the notation used in Fig. 2-5, a limit can be derived for the maximum bandwidth of the input band pass signal

$$\frac{m\Delta f_0}{2} < mf_d + \Delta f_{max} < f_r - \frac{\Delta f_{max}}{2} \tag{2-11}$$

while m is the integer floor function of the ratio of the two frequencies  $f_r$  and  $f_d$ , and  $\Delta f_{max}$  and  $\Delta f_0$  are the bandwidths of the system and the output band pass filter respectively. Based on (2-10), we can write:

$$\Delta f_L = 2f_r - m\Delta f_0 \tag{2-12}$$

where L denotes the low frequency and  $\Delta f_L$  indicates the maximum frequency span of the input band-pass signal. Equations (2-9) and (2-12) say nothing about the optimum points for the dithering frequency. This will be dealt with in chapter 6.

## 2.6 Statistical approach

As explained in the previous sections, the nonlinear system characteristic effectively changes in presence of the dithering signal. The method to study and describe this phenomenon will depend on the type of the input and dithering signal and of course the nonlinear apparatus itself.

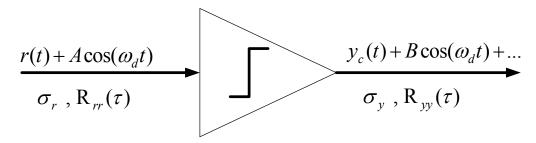

The concept of 'equivalent nonlinearity' was chosen to explain and achieve insight to the dithering effect. The terms left out of the summation, i.e.  $g_0$  in (2-5) and  $g_{10}$  in (2-7), define the equivalent nonlinearity respectively for high and low frequency dithering. The describing function concept defines a quasi-linear gain for different cases of static (time invariant and memory-less) nonlinear blocks, but this representation will depend on the stochastic behavior of the input signal. On the other hand there are approaches that do not depend on the deterministic mathematical description of the signal that drives the equivalent nonlinearity; these approaches are based on a so called probabilistic view.

Probabilistic view aims to find the equivalent nonlinearity based on the statistical description of the dithering signal, without imposing any limitation on the mathematical expression of the input signal. The set of conditions imposed on the dithering signal and the message signal does not include anymore the periodicity of the dither signal. This periodicity is replaced with a more relaxed condition of repetitive function [34]. The concept of equivalent nonlinearity is

Fig. 2-7(a) Open loop dither applied to static nonlinearity; (b) equivalent nonlinearity

illustrated in Fig.2-7-(a, b).

The two systems generate the same outputs as certain conditions on frequency of the dither and filter dynamics are met, and the modified  $f^*$  function is convolution of the probability distribution of the dithering signal with the original nonlinear function as follows:

$$f_{NL}^{*}(r_{g}) = \int_{-\infty}^{\infty} f_{NL}(r_{g} + \xi) P_{d}(\xi) d\xi$$

(2-13)

in which  $P_d$  represents the value distribution function of the dither signal and  $\xi$  is the instantaneous value of the dither signal. It can be achieved by taking the derivative of the cumulative distribution function of the dither signal, noted with capital letter P, defined as follows:

$$P_d(\xi) = \frac{\mu(t \in \{t_1, t_2\}, d(t) < \xi)}{t_2 - t_1}$$

(2-14)

in which  $\mu$  is the measure function [67], or the duration in which the function is less than a certain value  $\xi$ , in the observation interval  $t_1$ ,  $t_2$ .  $P_d$  is a monotonic increasing function of its argument. It is equal to 1 for infinite argument and 0 for minus infinite argument. The value probability distribution is:

$$p_d(\xi) = \frac{d(P_d(\xi))}{d\xi} \tag{2-15}$$

The condition in which the two functions ( $f^*$  and f) generate the same output depends on the frequency content of the input and the dithering signals, and the transfer function of the successive filter ( $H_1(j\omega)$ ). Two different cases have to be distinguished for high and low frequency dithering.

From now on the dither signal should be repetitive. Assuming  $\Delta T_d$  is the period of the dither signal, or the supermum<sup>3</sup> of the repetition time of the  $p_d(t)$ , the two cases are established below.

## 2.6.1 Equivalent nonlinearity for high frequency dithering

If the high frequency attenuation criterion:

$$\lim_{\omega \to \infty} \left( \omega H_1(j\omega) \right) = 0$$

<sup>&</sup>lt;sup>3</sup> In mathematics, given a subset S of a totally or partially ordered set T, the supremum (sup) of S, if it exists, is the least element of T that is greater than or equal to every element of S. Consequently, the supremum is also referred to as the least upper bound (lub or LUB). If the supremum exists, it is unique.

is met, the outputs of the two systems in Fig. 2-6 are identical, if the dither period tends to zero [34, 65]:

$$\lim_{\Delta T_d \to 0} (y^*(.) - y(.)) = 0$$

while modified f\* function is the convolution of the probability distribution of the dithering signal with the original nonlinear function as follows:

$$y^*(.) = f_{NL}^*(r_g) = \int_{-\infty}^{\infty} f_{NL}(r_g + \xi) P_d(\xi) d\xi$$

(2-16)

A detailed mathematical proof of this theorem is given in [34].

## 2.6.2 Equivalent nonlinearity for low frequency dithering

Assuming  $\omega_r$  is the central (carrier) frequency of the band pass signal, and  $\omega_r/2 < \omega_a < \omega_r - \Delta\omega$ , where  $\Delta\omega$  is the bandwidth of the band pass input signal, if the low frequency attenuation criteria are met, as stated below:

$$\lim_{|\omega - \omega_d| \to 0} ((\omega - \omega_r).H_1(j\omega)) = 0$$

Then the outputs of the two systems are identical, if the ratio of the dither period to the signal period tends to zero:

$$\lim_{\Delta T_d/\Delta T_0 \to 0} (y^*(.) - y(.)) = 0$$

where  $\Delta T_0 = 2\pi/\Delta\omega$ . The equivalent nonlinearity as a function of the real envelope of the modulated signal can be formulated as:

$$f_{NL}^{*}(r_g) \triangleq \int_0^{2\pi} \int_{-\infty}^{\infty} (\frac{1}{\pi}) p_d(\xi_2) . f_{NL}(r_g \cos \xi_1 + \xi_2) \cos \xi_1 . d\xi_2 . d\xi_1$$

(2-17)

while  $p_d(.)$  is the probability distribution function of the value of the dithering signal d(t),  $\xi_1$  represents the phase of the input sinusoid and  $\xi_2$  represents the dither.

This theorem is similar to the correlation equation presented in [34] for low pass signals, but it formulates the envelope transfer function for low frequency dithering. It shows the smoothed shape of the nonlinearity for any kind of periodic dithering signal, under the following conditions:

- 1. The frequency of the dithering signal is high enough compared to the complex envelope bandwidth.

- 2. It is high enough compared to the filter bandwidth.

- 3. It is low enough compared to the carrier frequency.

- 4. Spurious cross modulation components of dithering and signal are negligible.

Then the two systems of Fig. 2-7-a,b become equivalent.

It is easy to apply equations 2-16 and 2-17, to various nonlinear functions and see the result of application of different dithering signals on equivalent nonlinearity.

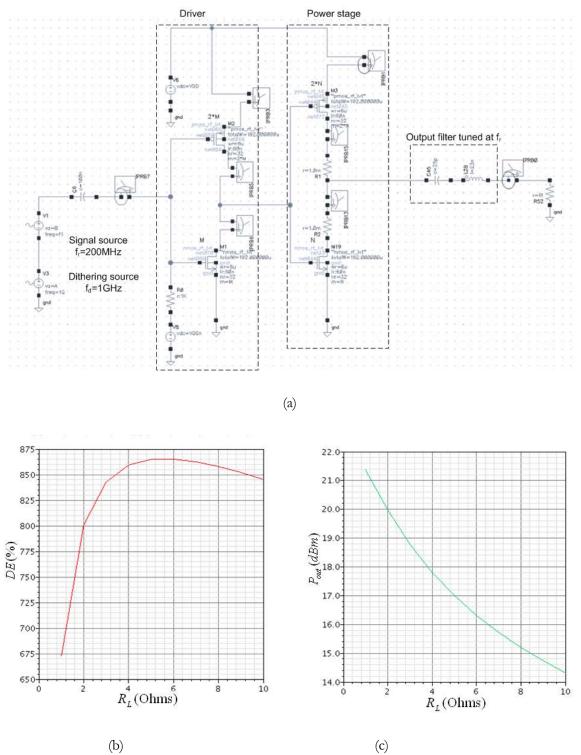

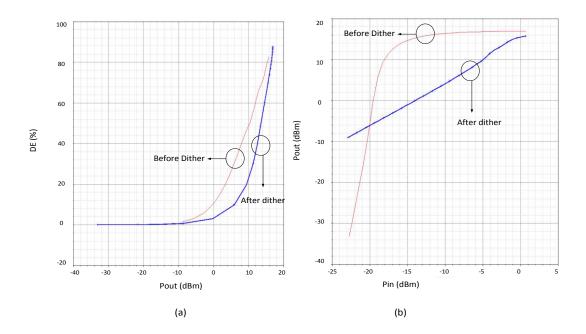

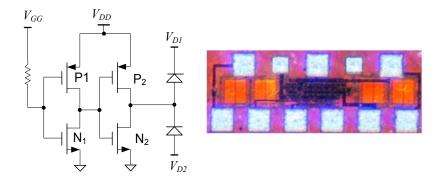

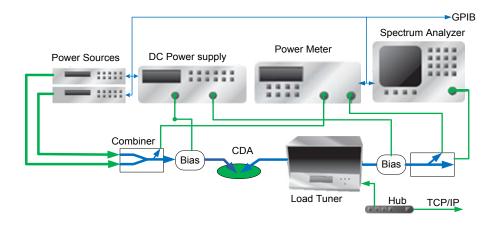

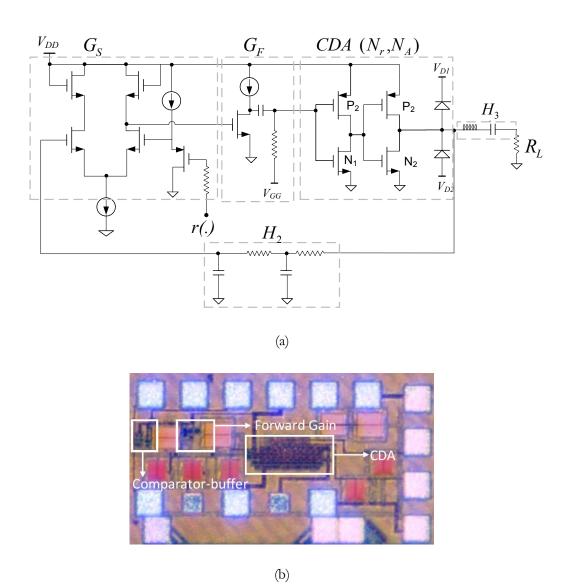

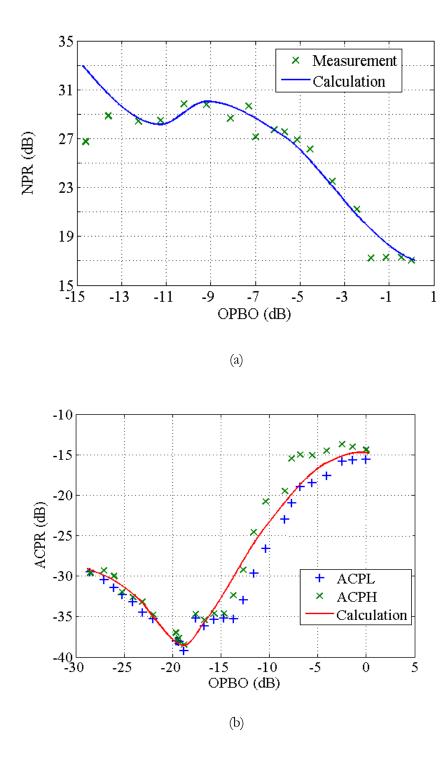

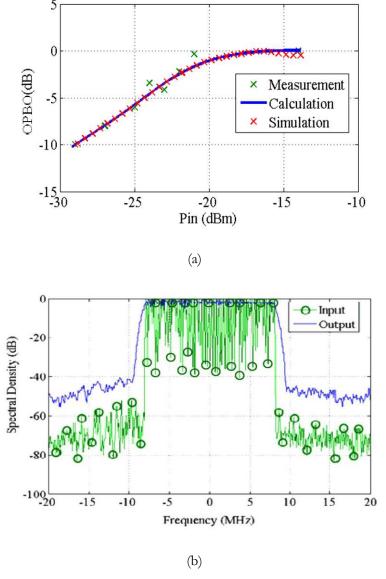

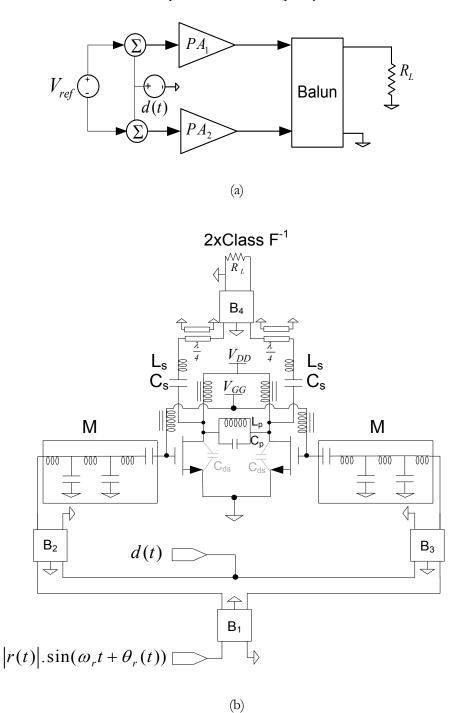

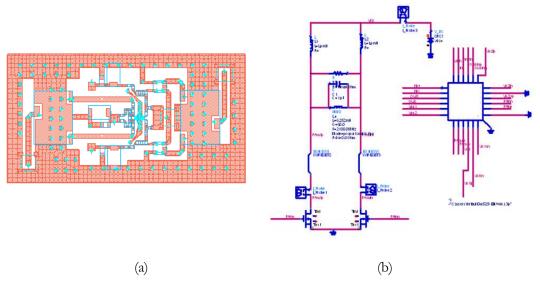

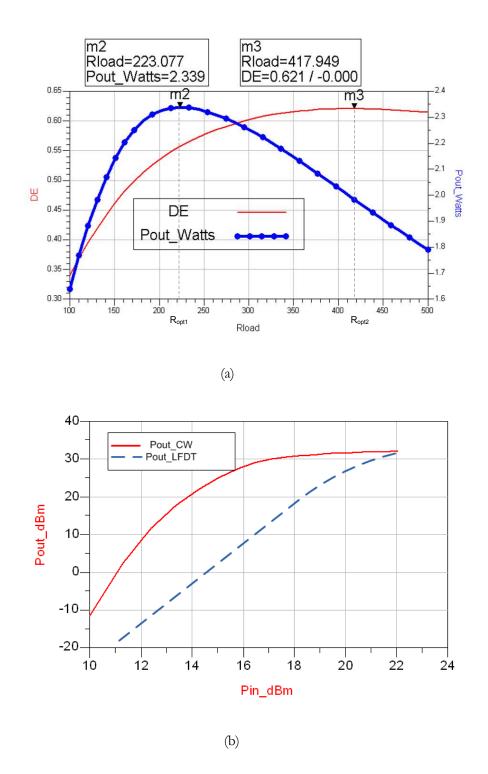

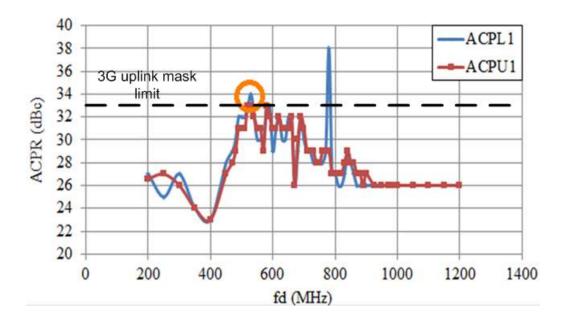

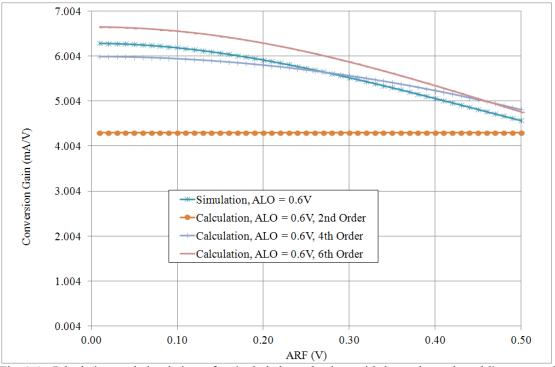

## 2.7 Conclusion