# Research Article Analogue Behavioral Modeling of GTO

## Y. Azzouz,<sup>1</sup> H. Schneider,<sup>2</sup> L.-A. Coyitangiye,<sup>1</sup> and B. Ravelo<sup>1</sup>

<sup>1</sup> IRSEEM, EA 4353, ESIGELEC, Avenue Galilée, BP 10024, 76801 Saint-Etienne du Rouvray Cedex, France

<sup>2</sup> Laboratoire Plasma et Conversion d'Energie (LAPLACE), INPT, Université de Toulouse—UPS, 118 Route de Narbonne, 31062 Toulouse Cedex 9, France

Correspondence should be addressed to B. Ravelo, blaise.ravelo@esigelec.fr

Received 14 January 2011; Revised 16 May 2011; Accepted 16 May 2011

Academic Editor: Henry S. H. Chung

Copyright © 2011 Y. Azzouz et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

An analog behavioral model of high power gate turn-off thyristor (GTO) is developed in this paper. The fundamental methodology for the modeling of this power electronic circuit is based on the use of the realistic diode consideration of non-linear junctions. This modeling technique enables to perform different simulations taking into account the turn-on and turn-off transient behaviors in real-time. The equivalent circuits were simulated with analog software developed in our laboratory. It was shown that the tested simple and compact model allows the generation of accurate physical characteristics of power thyristors under dynamic conditions. The model understudy was validated with analog simulations based on operational amplifier devices.

## 1. Introduction

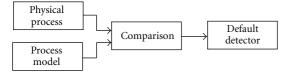

The commands of variable-speed high-power drives are currently main problems for electronic power equipment designers faced with the increase of system complexity [1–4]. Usually, the first step for implementing the basic model employed for system diagnosis [5–7] is to measure the difference between the signals from the physical process provided by the captors or actuators and the theoretical value calculated with the models. This technique is based on the theory of analytical redundancy illustrated in Figure 1 which is generally used in automatic area.

Therefore, this redundancy is expressed by analytical models described by mathematical equations (or other models) deduced from the fundamental physic laws, representing causal relationships between the signals in the system. The measurements obtained from different captors integrated in the system can then be connected by these models. The diagnosis is so explored by verifying a consistency control between the data collected by the observation system and those predicted by the model [6, 7].

The difficulties encountered with the use of numerical mathematical models [8–13] to achieve real-time simulation of complex and fast systems (e.g., converter-machine gathered) lead us currently to develop the typical analog

simulation. Moreover, the development of microelectronics notably the expansion of operating frequency band and accuracy of analogue operators enables to overcome the major handicaps of the analog simulation. The use of analog simulator, as real-time model (knowing the properties of the simulator as well as the performances), allows to consider new solutions for the parameter estimation and diagnosis problems: such as, the improvement of performances in terms of calculation of speed and real-time comparison between the physical process and its model. These two properties permit us to represent the state of an electrical or electronic system at any instant time, which brings new solutions to the diagnosis and estimation problems of variable-speed drives [5].

It is interesting to note that before the emergence of numerical simulations, the electronic and electrical engineering researchers suffer due to the lack of the adequate computation tools suitable for the achievement of relevant analog simulations. Since the numerical simulation widened its sphere of activity, it becomes the tool mostly used than analog simulation [14, 15]. However, in general, the analog simulation is more suitable than the numerical simulation for the modeling of complex circuit notably for the power electronic application and fast systems as the converters and electrical machines. For example, real-time simulations

FIGURE 1: Principle of diagnosis based on the comparison between the real process and its equivalent model [5–7].

can be achieved by using analog operators which offer the possibility of parallel calculations. These main advantages of analog approach enable us to represent, in real time, the state of electric and/or electronic power systems. Thus, new solutions for diagnosis which facilitate the maintenance of the electrotechnical equipments can be considered [16–20]. In this area, few studies are available in the literature especially for the modeling of command circuits [1–3]. In fact, the existing simulation tools as proposed in [8–15] are not sufficient for taking into account certain realistic effects as the current and voltage commutations and the physical phenomenon as the diffusion current appearing, for example, in the power diode.

For this reason, we develop in this paper the principle of analog modeling dedicated to the most useful electronic components such as the capacitor, the inductor. These elements are simulated conventionally with an analog calculator from their characteristic equations based on the analysis of voltage variables. More importantly, for the usual case of reactive elements as the inductors and capacitors, one finds that that certain mathematical or analytical representations (as the differentiation and integration operations) are hardly to implement in numerical tools because they are too sensitive to the unrealistic variations of electrical signals. Facing to this finding, the cohabitation of analog and numerical simulations can become complementary.

Then, we give more attention to the simulation of the diode because it plays the role of basic element constituting the GTO modeling. Meanwhile, the verification result regarding the diode model is a prerequisite condition before the approach to the GTO modeling. Finally, we treat the model of this latter prior to four phenomena: the switching power, the tail phenomenon responsible for the switching losses, the delay in the starting time, and the derivative operation effect.

The aim of this paper is to develop an analog model of high-voltage GTO suitable to predict accurately the dynamic characteristics of command circuits. The GTO is widely used in high power, high voltage of about 8 kV, and high current of about 4 kA for switching applications such as traction system of electric vehicles. The model presented in this paper is based on the diode switching behavior and described by the equivalent circuit of passive components such as capacitor and inductance. These elements, characterized by the input and output voltages, are simulated by using a traditional analog solver. The model includes the high switching capacity, tail current, the delayed-time response, and dV/dt triggering. It also incorporates the reverse recovery effect in transient response.

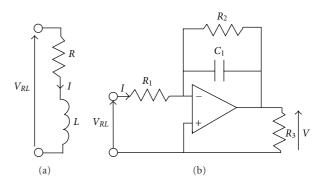

FIGURE 2: Equivalent circuit of a realistic inductance.

## 2. Analog Simulation

As reported in [21, 22], the analog behavioral modeling requires a high-speed calculation and an easy implementation of electrical circuit network equations for describing the elements as the inductor and capacitor components, machine, switch, and so forth. In this section, we first consider an analog modeling of passive components such as inductances and capacitors.

2.1. Circuit Equivalent of an Inductance. By considering the schematic shown in Figure 2(a), the voltage and current flowing through the inductance are linked by the following integral-differential equation:

$$I = \frac{1}{L} \int (V_{RL} - R \cdot I) dt.$$

(1)

Meanwhile, the current I can be obtained through an integrator circuit. Figure 2(b) represents the equivalent analog model of the inductance depicted in Figure 2(a). As noted through the Laplace transform (which corresponds here with the variable s), it is well known that this expression can be rewritten as:

$$V_{RL}(s) = (R + L \cdot s) \cdot I(s).$$

<sup>(2)</sup>

Via Kirchhoff's and Ohm's laws applied to the circuit presented in Figure 2(b), one can express

$$\frac{V(s)}{V_{RL}(s)} = \frac{R_2}{R_1(1+R_2 \cdot C_1 \cdot s)} \\

V(s) = R_3 \cdot I(s)$$

$$V_{RL}(s) = \frac{R_1 \cdot R_3}{R_2}(1+R_2 \cdot C_1 \cdot s) \cdot I(s).$$

(3)

So, the equivalence between the linear networks depicted in Figures 2(a) and 2(b) can be obtained by the identification of (2) and (3):

$$\left\{\frac{R_1 \cdot R_3}{R_2} = R, \ R_1 \cdot R_3 \cdot C_1 = L\right\}.$$

(4)

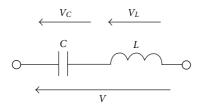

FIGURE 3: Equivalent circuit of a realistic capacitor.

FIGURE 4: Equivalent circuit of a capacitor.

*2.2. Capacitor Equivalent Circuit.* It is well known that the current flowing through a capacitor *C* is ideally defined by

$$I_C = C \frac{dV_C}{dt}.$$

(5)

However, it is noteworthy that the use of this ideal model of capacitor is extremely sensitive to the input voltage variation due to the derivative operator with respect to the time variable d/dt. In fact, certain unrealistic signal noises like numerical imperfections are considerably amplified. To reduce this unrealistic effect, we propose to insert an optimized inductive element having low value in order to avoid the change of the capacitor behaviour. This allows us to realize a more practical analog model of the capacitor based on the integral operator. Therefore, the current flowing through the ideal capacitor can be written as follows:

$$L\frac{di}{dt} = V - V_C \Longrightarrow I = \frac{1}{L} \int (V - V_C) dt,$$

$$I = C\frac{dV_C}{dt} \Longrightarrow V_C = \frac{1}{C} \int I dt.$$

(6)

One can see that in practice a capacitor element should include two integrators which behave as inductive and capacitive integrators in cascade as shown in Figure 3.

The Laplace transform of (6) gives

$$\{L \cdot s \cdot I(s) = V(s) - V_C(s), I(s) = C \cdot s \cdot V_C(s)\}.$$

(7)

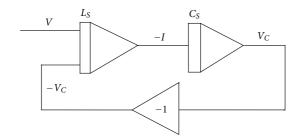

So, the equivalent functional model representing this last equation which governs the linear network introduced in Figure 3 is established in Figure 4.

2.3. Scale Factor of Reactive Elements. Since certain power system parameters (supply voltage, load current, etc.) with high values cannot be implemented to the analog operators considered (e.g., maximum voltage of about 15 V), to pass

this constraint, we propose in this article to use a scale factor constant. By denoting  $X_{\text{real}}$  the real parameter (which can be expressed in V, A, Hz, etc.) associated to the simulated parameter  $[X]_{\text{sim}}$  which corresponds, for example, to a voltage quantity, the real maximum value  $X_m$  of scaling Xparameter must correspond to the maximum voltage that can be supported by analogue operators. This supposition can be written by using the following transformations,  $X_{\text{real max}} \rightarrow [X]_{\text{sim max}}$  and  $X_{\text{real}} \rightarrow [X]_{\text{sim}}$ . In other word, we realise the real value  $X_{\text{real}} = (X_{\text{real max}}/[X]_{\text{sim max}})[X]_{\text{sim}}$ . For example, if the analogue operators support a maximum voltage of 10 V, the real value should be equal to  $X_{\text{real}} = (X_{\text{real max}}/10)[X]_{\text{sim}}$ . The ratio between maximum real value and maximum simulated value is called "scale factor". It is denoted as  $K_V$  for the case of voltage parameter:

$$K_V = \frac{V_{\text{real max}}}{[V]_{\text{sim max}}}.$$

(8)

Similarly, for the other electrical parameters as current and frequency, it is, respectively, written as follows:

$$K_I = \frac{I_{\text{real max}}}{[I]_{\text{sim max}}},\tag{9}$$

$$K_f = \frac{f_{\text{real max}}}{[f]_{\text{sim max}}}.$$

(10)

Therefore, the inductance and capacitor can be respectively described by

$$[L]_{\rm sim} = \frac{K_i}{K_V} L_{\rm real},\tag{11}$$

$$[C]_{\rm sim} = \frac{K_V}{K_I} C_{\rm real}.$$

(12)

## 3. Modeling of Power Diodes

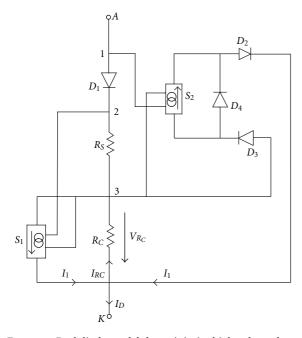

For the sake of simplification, an ideal diode can be modeled by a classical switch. In order to simulate this type of switch element, an adequate function is needed. In addition, in order to respect the scale factors between the real and simulated quantities, it is necessary to have a negligible voltage drop when the diode is switched on. Hence, the diode model was chosen because it is characterized by spontaneous switching at low voltage drop usually around 0.7 V. However, when this simulated voltage drop is applied on the highpower circuit, it must be multiplied by a factor, for example,  $K_{\nu} = 100$ . Thus, the real drop voltage can reach a high value of about 70 V. In order to remove this high voltage drop, one proposes a circuit displayed in Figure 5 which is based on diodes and current sources.

3.1. Simulation of an Ideal Diode. Diode  $D_1$  is the effective diode that describes a considered switch element. The other diodes  $D_2$ ,  $D_3$ , and  $D_4$  are used to activate the voltage compensation only when diode  $D_1$  is on.  $S_1$  and  $S_2$  are voltage-controlled current sources and will remove the high

FIGURE 5: Real diode model that minimize high voltage drop.

voltage drop due to  $D_1$ .  $S_1$  is controlled by voltages at nodes 2 and 3. The corresponding current gain is equivalent to  $G_{S_1} = 1/R_S$ , and thus, the current in  $S_1$  is given by  $I_1 = V_{23}/R_S$ .  $S_2$  is controlled by the voltages at nodes 1 and 3. The gain and the current through  $S_2$  are, respectively, equivalent to  $G_{S_2} = 1/R_C$ and  $I_2 = V_{13}/R_C$ . The voltage across the  $R_C$  resistor is given by

$$V_{R_C} = R_C \cdot I_{RC} = R_C \cdot (I_2 + I_1 - I_D) = R_C \left(\frac{V_{13}}{R_S} + \frac{V_{23}}{R_C} - I_D\right).$$

(13)

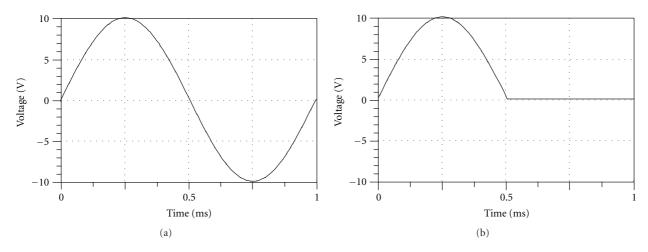

After simplification, one obtains  $V_{13} = V_{R_c}$ . These controlled current sources will create a voltage drop equal and opposite to the voltage drop generated by the diode  $D_1$ . Then, they should compensate the total drop voltage in the circuit. The diode model represented in Figure 5 has been simulated in half wave rectifier circuit, and time domain results are shown in Figure 6. We can see that during the period of the diode conduction, the voltage across the diode load is equal to the input voltage (no diode voltage drop).

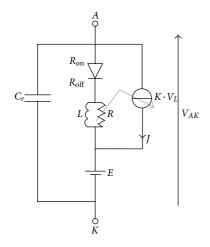

3.2. Simulation of a Realistic Diode. The analog model is based on the model used in the Success software developed in our laboratory. In this software, the power diode dynamic behavior is compared to the capacitive phenomenon due to the stored charges during the conduction caused by the high-diffusion capacitor and the space charge region which appears when the diode is turned off (low-depletion capacitance). As can be seen in Figure 7, the Success diode model is represented by a resistor with two states  $R_{on}/R_{off}$ that can accurately switch from the low voltage (on state) to the high voltage (off state). When the diode is forwardbiased, the diode resistance value is  $R_{on}$ . The static model is characterized by  $R_{on}$  and voltage source *E*. Whereas for the dynamic behavior, the diffusion capacitor, represented by voltage-controlled current source, denoted that  $V_L$  is added to the model. When the diode is reverse-biased, the diode resistance value becomes  $R_{off}$ . It is interesting to point out that the inductance L can detect the value of di/dt, and the resistance R, connected in parallel with L, controls the current source at the value of  $K \cdot V_L$ . This model can be extended to power diode models. It is worth underlining that for this purpose the following statements must be taken into account.

- (i) The diode reverse recovery: it depends on diode physics (size) and components including the commutation circuit (resistor or inductance load).

- (ii) The diode voltage rises: when the diode switches from conducting to nonconducting state; the space charge region increases and power loss are dissipated by commutation.

- (iii) The overshoot voltage at switching on, this parameter is not taken into account in our model because the switching-off state is more important in power diode.

A complete power diode model is obtained by adding a diffusion capacitor model to the real diode model.

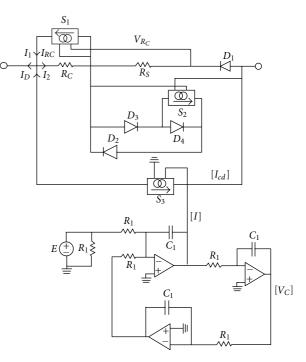

As highlighted in Figure 8, the simulated model is based on the load current which combines the diode and capacitance currents through  $S_3$ . It is worth noting that when the diode  $D_1$  is off, the output current is equivalent to the diffusion capacitor current  $S_3$ .

3.3. Diffusion Capacitor Scale Factor. By using the models proposed previously, the real value of the diffusion capacitor  $C_d$  can be calculated. We assume that  $I_{cd}$  is the real current in the diffusion capacitor.  $I_{cd}$  corresponds to the simulated current, and  $C_{d real}$  is the real value of  $C_d$ .

$$I_{cd} = C_{d \operatorname{real}} \frac{dV_C}{dt} \Longrightarrow V_C = \frac{1}{C_{d \operatorname{real}}} \int I_{cd} dt.$$

(14)

As represented in Figure 8, the diffusion current is described by

$$[I_{cd}] = G_{S_3}[I], (15)$$

whereas the voltage diffusion should be

$$[V_C] = \frac{1}{R_1 C_1} \int [I] dt.$$

(16)

Substituting (15) into the previous expression, we have

$$[V_C] = \frac{1}{R_1 C_1 G_{S_3}} \int [I_{cd}] dt.$$

(17)

With the considered analog diode model, the following mesh relations are obtained:

$$[V_{AK}] = [V_{D1}] - [V_{R_C}],$$

(18)

$$[V_{R_C}] = R_C \cdot [V_{D1}] \cdot G_{S_2}, \tag{19}$$

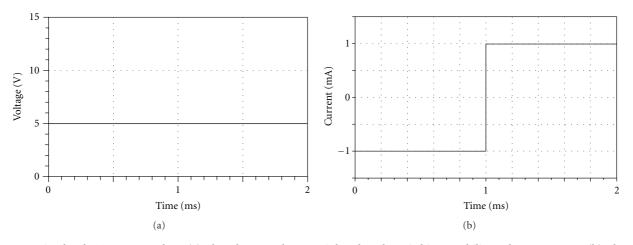

FIGURE 6: Simulated diode input—(a) and output—(b) voltages.

FIGURE 7: Success diode circuit model.

where  $R_C$  is the resistance of compensation. By combining the two previous relations, the following expression is deduced:

$$[V_{AK}] = \frac{[V_{R_C}]}{R_C G_{S_2}} - [V_{R_C}] \Longrightarrow [V_{AK}] = [V_{R_C}] \left(\frac{1 - R_C G_{S_2}}{R_C G_{S_2}}\right).$$

(20)

Under condition  $R_C G_{S_2} \leq 1$ , one proposes the following factor:

$$\alpha = \frac{1 - R_C G_{S_2}}{R_C G_{S_2}}.$$

(21)

Knowing that the difference between the two voltages is relatively low, it is obvious that  $[V_C] \approx [V_{R_C}]$ . Then, the combination of formulae (17), (19), and (20) entails the following reduced equation:

$$[V_{AK}] = \frac{\alpha}{R_1 C_1 G_{S_3}} \int [I_{cd}] dt.$$

<sup>(22)</sup>

FIGURE 8: Complete power diode model.

Knowing that the real value of  $V_{AK}$  and that one of the current are, respectively, defined as  $[V_{AK}] = V_{AK}/K_V$  and  $[I_{CD}] = I_{CD}/K_I$ , it yields that

$$[V_{AK}] = \alpha \frac{K_V}{K_I} \frac{1}{R_1 C_1 G_{S_3}} \int [I_{cd}] dt = V_C.$$

(23)

From (14) and (20), we demonstrate that  $C_{d real}$  depends on  $R_1$  and  $C_1$ :

$$C_{d \text{ real}} = \frac{K_1}{K_V} \cdot \frac{R_1 C_1 G_{S_3}}{\alpha}.$$

(24)

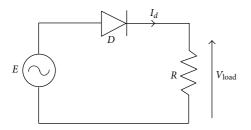

FIGURE 9: Half wave rectifier circuit simulation.

The value of  $R_1$  and  $C_1$  can be extracted from relation (23). By assuming that  $R_C \cdot G_{S_2} = 0.999$  or  $\alpha = 10^{-3}$  and  $G_{S_3} = 10^{-4}$ , therefore, one gets

$$R_1 \cdot C_1 = C_{d \text{ real}} \cdot \frac{\alpha}{G_{S_3}} \cdot \frac{K_V}{K_I} \Longrightarrow R_1 \cdot C_1 = 10 \frac{K_V}{K_I} \cdot C_{d \text{ real}}.$$

(25)

In order to confirm the relevance of the above theoretical approach, modeling of an half wave rectifier and a voltage chopper circuit is examined in the next section.

#### 4. Validation of the Analog Diode Model

In this section, the validity of the analog model presented previously in Figure 8 is investigated. For that two structures, we considered first a half wave rectifier circuit and second a voltage chopper circuit.

4.1. Half Wave Rectifier Circuit. The circuit introduced in Figure 8 is used here to check the compensation of the voltage drop and the ability of the model to generate a reverse current. In this section, we are interested to the qualitative aspect of the electrical quantities. So, the model must simulate accurately physical phenomena during the blocking state. In this section, the diode model depicted in Figure 8 was implemented in circuit simulation shown in Figure 9.

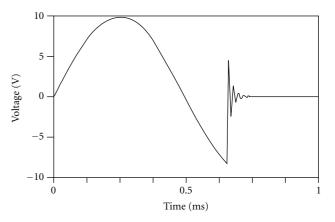

The simulation results shown in Figure 10 allow to validate the analog model. One finds that perfect voltage compensation is respected, because the input voltage *E* equals the output  $V_{\text{load}}$  during the conduction of the diode. Furthermore, a turnoff of the diode occurs only after the reverse recovery conduction. This important phenomenon confirms the efficiency of the analog model proposed in Figure 8.

One underlines here that a diode element is ideally blocked when the current becomes zero. But, in reality, the typical power diode continues to conduct the current inversely due to the diffusion capacitor. This effect is known as the reverse recovery phenomenon. This corresponds to the negative alternation of the wave represented by Figure 10. So, the model proposed enables to characterize this singular effect qualitatively.

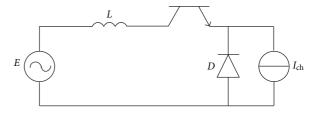

4.2. Buck Converter. The buck circuit described in Figure 11 was simulated with the diode element STF-75545 available

FIGURE 10: Transient simulation of  $V_{\text{load}}$  voltage.

FIGURE 11: Buck converter circuit.

in the software Success simulator which was developed in our laboratory. The diode parameters are defined as  $R_{on} = 1 \text{ m}\Omega$ ,  $R_{off} = 1 \text{ m}\Omega$ , E = 0.75 V,  $C_r = 0.53 \text{ nF}$ ,  $R_1 = 9.52 \mu\Omega$ , and K = 164461. The real diffusion capacitor can be calculated using these parameters, so that  $C_{dreal} = K \cdot L/R_{on} = 5.76 \text{ mF}$  is obtained. This diode model was tested in the buck converter circuit shown in Figure 11 where E = 1 kV and  $I_{ch} = 1 \text{ kA}$ .

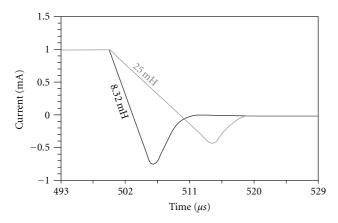

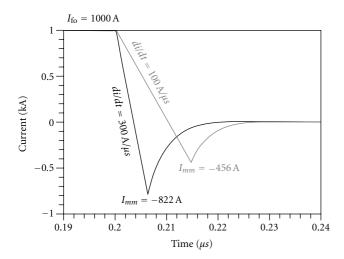

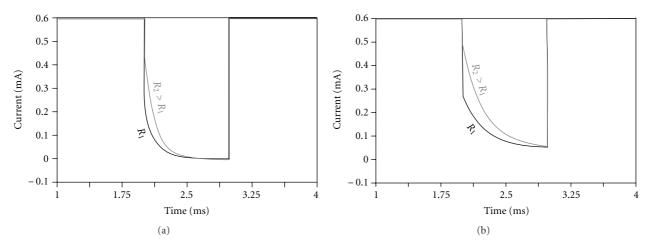

This circuit allows the calculation of the scale factor for the current and voltage, respectively, given by  $K_I$  =  $I_{\rm max}/I_{\rm sim} = 10^6$  and  $K_V = V_{\rm max}/V_{\rm sim} = 400$ . The simulated parameters are equal to  $[I_{ch}]_{analog} = 1 \text{ mA}$  and  $[E]_{analog} = 2.5 V.$  The di/dt rating is adjusted by using two values of inductances  $L_1 = 10 \,\mu\text{H}$  and  $L_2 = 3.33 \,\mu\text{H}$ . The corresponding analog values are defined as  $[L_1] =$  $L_{\text{real}} \cdot (K_I/K_V) = 8.32 \text{ mH} \text{ and } [L_2] = L_{\text{real}} \cdot (K_I/K_V) =$ 25 mH. The main diode model parameters are given by  $R_C \cdot G_{S_2} = 0.999$ . So, for  $R_C = 1 \text{ k}\Omega$ , we have obtained  $G_{S_2} = 999.10^{-6}$ . The other parameters are equal to  $G_{S_1} = 10^{-3}$ ,  $G_{S_3} = 10^{-4}$ , and  $R_S = 1 \text{ k}\Omega$ . By substitution of these values in relation (12),  $R_1 \cdot C_1 = 23.10^{-6}$  s is calculated, and assuming that  $R_1 = 10 \text{ k}\Omega$ , as result, we can write that  $C_1 = 2.3 \,\mathrm{nF}$ . Simulations have been performed using the circuit presented in Figure 11. Thus, we obtain the results displayed in Figure 12. It can be shown that the model allows the simulation of the reverse recovery phase; the maximum reverse current becomes dependent of the inductive load.

In order to validate the power diode analog model, the obtained model results are compared with the numerical model ones which are depicted in Figure 13. In both cases, the maximum reverse current and the reverse recovery time seem to be in good agreement.

FIGURE 12: Transient evolution of inductive load turnoff with two different inductance values obtained by using analog diode model.

FIGURE 13: Transient evolution of inductive load turnoff with two different inductance values obtained by using numerical diode model.

FIGURE 14: Equivalent circuit of GTO [17].

FIGURE 15: Complete numerical model of GTO [17].

4.3. Model Limitations. As illustrated in Figures 12 and 13, the snap-off period which occurs while the current is rising rapidly along the reverse peak is not the same for the numerical and analog models. For the analog model, this period cannot be adjusted because the reverse recovery state is represented by two dependent circuits, while the numerical model is flexible.

## 5. Simulation of GTO

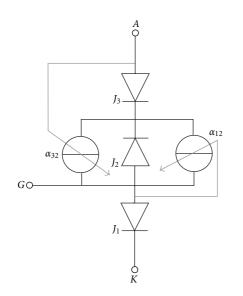

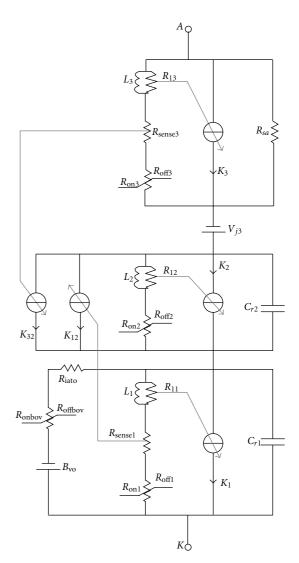

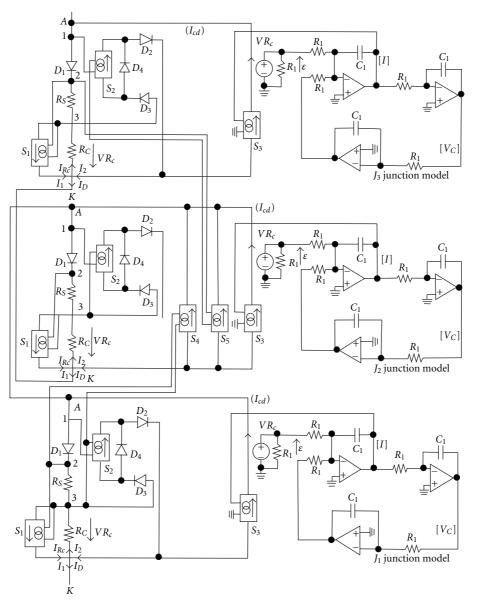

5.1. Modeling of an Ideal GTO. Many research efforts are dedicated to the new models for GTO devices, particularly those intended for circuit simulation [23–25]. The proposed circuit model for the numerical simulator is schematized in Figure 14. For this model, three junctions  $J_1$ ,  $J_2$ , and  $J_3$  are represented by three diodes and two current sources as indicated in Figure 14. The simulation approach of GTO is based on the replacing of each diode by the corresponding analog model shown in Figure 5.

FIGURE 16: Complete schematic of the under-study analog model of GTO.

5.2. GTO Model Simulation. An analog simulation of GTO is proposed in order to evaluate, in real time, the behavior of this component in its environment. First of all, we studied the principal static characteristics and the dynamic behavior of the GTO. Then, we carried out an identification of the model parameters and modeling of principle features for the dynamic behavior of GTO: dynamic capability of blocking, reverse tail current, delayed turn-off time, and dV/dt rating. The complete GTO analog model introduced in Figure 15 is obtained from the model depicted in Figure 14 where each diode junction is replaced by the model described in Figure 8. The avalanche breakdown of the junction GK is modeled by a diode in series with voltage source  $B_{V0}$ . Then, the resistances  $B_{V0}$  and  $R_{iato}$  represent the maximum of current supported by the junction GK. Resistance  $R_{sa}$  is used to describe the asymmetrical behavior of GTO.

Therefore, for the simplicity of simulation, the methodology uses an ideal model which does not include the effect of diffusion capacitor and avalanche breakdown.

## 6. Analog Model Validation

We recall that the main features of turnoff of GTO are: the dynamic turn-off performances, the reverse tail current, the delayed turn-off, time and the time derivative voltage dV/dt. In this section, the significance of each mechanism incorporated in GTO behavior is evaluated in order to highlight their importance. Comparisons are made between the analog response and the physical behavior by considering the circuit shown in Figure 16. One points out that this analog model seems relatively complex because it transposes the classical simple circuit model of Figure 15 by its analog

FIGURE 17: Simulated GTO output voltage (a) when the control current is less than the switching capability and output current (b) when the control current is higher than the switching capability.

equivalent model. We replace here the junctions by the analog model proposed prior to the real-time simulation model. We underline that despite the accuracy of the physical models [12, 13] thanks to its intrinsic characteristics, the analog model investigated here consumes less computation time and is less complex to implement, and it does not necessitate the knowledge of the internal GTO structure parameters. By cons, the numerical models introduced in [8–11] are much simpler than these physical models, but they are only valid for numerical computations. Also, compared with these numerical models, the analog one developed here presents advantages notably necessary for the achievement of more performing electrical system diagnosis as the real-time analysis.

*6.1. Controlled Switch.* It is interesting to recall the following basic electronic functions during the switch control:

- (i) *Triggering*. The GTO is switched on by a positive gate current and then turned on the NPN bipolar transistor.

- (ii) *Turned On*. The thyristor remains in the on state with a holding current to allow the GTO conduction.

- (iii) Turned Off. The turn-off thyristor occurs when the accumulated charges during the conduction have been removed by the gate terminal. For that, the current flowing through anode falls below threshold current, and the gate current must be high enough (blocking capability):

$$I_G \ge \frac{\alpha_{12} + \alpha_{23} - 1}{\alpha_{12}} \cdot I_A,$$

(26)

where  $\alpha_{12}$  and  $\alpha_{23}$  represent the current gain. Note that for  $\alpha_{12} = 1$ , the switch performance depends only on the value of  $\alpha_{23}$ . As this gain is usually a small value, the switching gain will increase. To decrease this value, it is necessary to reduce the carrier lifetime which is suitable for switching of the period.

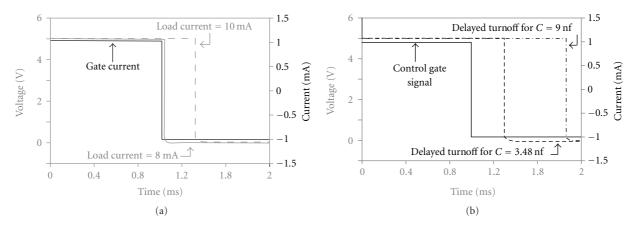

It is obvious that when the controlled switch is not strong enough, the total blocking of the junction P will not be achieved, and the GTO will fail. In that case, a pulse current on the gate terminal is more appropriate to enhance the switching performance. Simulations have been performed for the analog model. So, as depicted in Figure 17, the evidence of switching capability is observed. Moreover, Figure 17(a) indicates the absence of turn off. Indeed, if the gate current is less than the switching capability, the output voltage equals to the input voltage (GTO was not blocked). However, if the gate current is higher enough, the GTO is turned off as explained in Figure 17(b), and the above condition (26) is verified.

6.2. Simulation of Tail Current. During its operation, the GTO is subjected to severe failures due to tail phenomenon. The presence of tail current causes losses in the GTO structure. The tail current is simulated by including in the model the diffusion capacitor of junction  $J_1$ . Simulation results displayed in Figures 18(a) and 18(b) illustrates the effect of diffusion capacitor of  $J_1$  when tail current occurs. It is shown also that the tail current deals with the gain of the source that is biasing the diffusion capacitor. As the gain rises, the tail current increases due to more stored charges that must be removed in a longer time.

6.3. The Delayed Turn-Off Time. The analog model of diffusion capacitor junction  $J_2$  is added to the complete model. Simulation results shown in Figure 19 represent the effect of diffusion capacitor on the delay time to turn off. One can see that the anode current influences considerably the time delay.

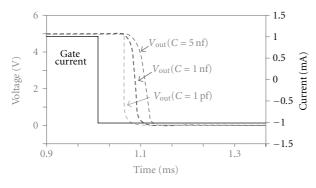

6.4. dV/dt Simulation. During the turn-off state, the GTO does not exceed a maximum value of dV/dt, this value is a function of the current conduction before the cut-off state. The simulation of dV/dt is achieved with capacitances added in parallel to the junction  $J_2$ . As plotted in Figure 20, dV/dt increases with the capacitance.

FIGURE 18: Simulation of tail current for two loads and for diffusion capacitor with gain (a)  $G_a = 1$  and (b)  $G_b = 2$ .

FIGURE 19: Effects of load current (a) and diffusion capacitor (b) on the delayed turn-off time.

FIGURE 20: dV/dt simulation results.

## 7. Conclusion

The behavioral modeling method developed in this paper is based on the analog modeling of diode and GTO with three junctions. Theoretical approach illustrating the methodology of this electronic power component modeling was presented. It was evidenced toward simulations that the model proposed provides interesting performances in the term of characterization of transient phenomena eventually appearing due to the switching modes. It is noteworthy that the analog behavior enables also to predict certain behaviors which cannot be expressed with classical numerical models [8–11] in real time. Most importantly, compared to these numerical models, it enables to explain also that the analog simulation which allows to understand more deeply the different aspects of switching mechanisms of GTO. Finally, the simulation of these mechanisms in real time permits to extract the state of the components in use.

## References

- [1] M. H. Rashid, *Power Electronics Handbook: Devices, Circuits, and Applications*, Academic Press, New York, NY, USA, 2nd edition, 2010.

- [2] M. Z. Sujod, "6 Pulse GTO thyristor converter simulation," in Proceeding of the 5th Student Conference (SCOReD '07), pp. 1– 5, Selangor, Malaysia, December 2007.

- [3] M. S. El-Moursi and A. M. Sharaf, "Novel controllers for the 48-pulse VSC STATCOM and SSSC for voltage regulation and reactive power compensation," *IEEE Transactions on Power Systems*, vol. 20, no. 4, pp. 1985–1997, 2005.

- [4] M. Chinthavali, L. M. Tolbert, and B. Ozpineci, "SiC GTO thyristor model for HVDC interface," in *IEEE Power Engineering Society General Meeting*, vol. 1, pp. 680–685, June 2004.

- [5] M. Lebbal, G. Hoblos, H. Chafouk, and D. Lefebvre, "On modeling and diagnosis of hybrid dynamical systems," *International Journal of Intelligent Systems Technologies and Applications*, vol. 7, no. 2, pp. 137–156, 2009.

- [6] H. Chafouk, G. Hoblos, N. Langlois, S. Le Gonidec, and J. Ragot, "Soft computing algorithm to data validation in aerospace systems using parity space approach," *Journal of Aerospace Engineering*, vol. 20, no. 3, pp. 165–171, 2007.

- [7] H. Chafouk, G. Hoblos, N. Langlois, S. Le Gonidec, and J. Ragot, "Soft computing approach for data validation," *Journal* of Aerospace Computing, Information and Communication, vol. 4, no. 1, pp. 628–635, 2007.

- [8] S. M. Zahim, M. Norainon, J. M. Shawal, and R. I. R. M. Taufika, "Iterative numerical method of gate turn-off thyristor: comparative study between Si and SiC," *American Journal of Engineering and Applied Sciences*, vol. 2, no. 2, pp. 446–450, 2009.

- [9] S. M. Zahim, "Modelling and simulation of GTO thyristor and its application in a 6 pulse converter," in *Proceedings of the 19th IASTED International Conference on Modelling and Simulation* (*MS '08*), pp. 409–413, Quebec City, Canada, May 2008.

- [10] http://www.mathworks.com/help/toolbox/physmod/powersys /ref/gto.html.

- [11] http://www.itu.dk/stud/speciale/segmentering/Matlab6p5/ help/toolbox/powersys/gto.html.

- [12] F. Lannuzzoa and G. Busattob, "A lumped-charge model for gate turn-off thyristors suitable for circuit simulation," *Microelectronics Journal*, vol. 30, no. 6, pp. 543–550, 1999.

- [13] http://electricalandelectronics.org/2009/04/14/two-transistormodel-of-a-thyristor/.

- [14] M. Zécri, H. Schneider, and M. Metz, "Real time analog simulation of transformers taking into account the saturation phenomena," in *Proceedings of the 6th International Conference* on Modeling and Simulation of Electric Machines Converters and Systems (ELECTRIMACS '99), Lisboa, Portugal, 1999.

- [15] M. Zécri, H. Schneider, A. Braham, and L. Etcheverry, "Analog real time emulator for power converters," in *Proceedings of* the 3rd International Power Electronic and Motion Control Conference (IPEMC '00), Beijing, China, 2000.

- [16] H. Schneider, M. Metz, H. Piquet, H. Foch, J. Courault, and O. Lapierre, "Utilization of real-time models for the survey and maintenance of high power electrotechnical systems," *Mathematics and Computers in Simulation*, vol. 38, no. 4–6, pp. 303–310, 1995.

- [17] A. Kaabouch, H. Schneider, J. Boucher et al., "Design and realization of analog simulator for real time estimation of an electrotechnical system state," in *The European Design and Test Conference*, pp. 27–31, Paris, France, 1996.

- [18] R. Abtahi, G. Jasmin, G. Lachiver, A. Leroux, and D. Mukhedkar, "Real time electronic analog simulation of a three-phase transmission line," *IEEE Transactions on Power Delivery*, vol. 3, no. 3, pp. 1257–1266, 1988.

- [19] E. Dallago and G. Sassone, "Analogue simulation of a DC brushless drive," *IEE Proceedings B*, vol. 139, no. 3, pp. 245– 251, 1992.

- [20] J. Arai and Y. Noro, "Induction machine model for an analog power system simulator," *IEEE Transactions on Power Systems*, vol. 8, no. 4, pp. 1478–1482, 1993.

- [21] C. Toumazou, F. J. Lidgey, and P. Y. K. Cheung, "Currentmode analogue signal processing circuits—a review of recent developments," in *Proceedings of the 22nd IEEE International Symposium on Circuits and Systems (ISCAS '89)*, pp. 1572– 1575, May 1989.

- [22] C. Toumazou, F. J. Lidgey, and D. G. Haigh, Analogue IC Design: The Current Mode Approach, Peter Peregrines, London, UK, 1990.

- [23] K. J. Tseng and P. R. Palmer, "Mathematical model of gate-turn-off thyristor for use in circuit simulations," *IEE Proceedings: Electric Power Applications*, vol. 141, no. 6, pp. 284–292, 1994.

- [24] X. He, B. W. Williams, and T. C. Green, "A composite gate turn-off thyristor model and its application," in *Proceedings* of the 28th Annual Meeting of the IEEE Industry Applications Conference, vol. 2, pp. 1202–1207, October 1993.

- [25] K. Y. Wong, P. O. Lauritzen, S. S. Venkata, A. Sundaram, and R. Adapa, "An SCR-GTO model designed for a basic level of model performance," in *Proceedings of the 31th IAS Conference Record of the IEEE Industry Applications Annual Meeting (IAS* '96), pp. 1517–1523, San Diego, Calif, USA, October 1996.

Advances in Civil Engineering

Rotating Machinery

Journal of Sensors

International Journal of Distributed Sensor Networks

Journal of Robotics

International Journal of Chemical Engineering

International Journal of Antennas and Propagation

Active and Passive Electronic Components

in Engineering

Shock and Vibration

Aerospace

Engineering

Acoustics and Vibration