# Analogue frontend amplifiers for bio-potential measurements manufactured with a-IGZO TFTs on flexible substrate

Citation for published version (APA):

Garripoli, C., van der Steen, J. L., Torricelli, F., Ghittorelli, M., Gelinck, G. H., van Roermund, A. H. M., & Cantatore, E. (2017). Analogue frontend amplifiers for bio-potential measurements manufactured with a-IGZO TFTs on flexible substrate. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 7(1), 60-70. [7733099]. https://doi.org/10.1109/JETCAS.2016.2616723

DOI:

10.1109/JETCAS.2016.2616723

Document status and date:

Published: 15/03/2017

#### Document Version:

Accepted manuscript including changes made at the peer-review stage

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 26. Aug. 2022

# Analogue frontend amplifiers for bio-potential measurements manufactured with a-IGZO TFTs on flexible substrate

Carmine Garripoli, Jan-Laurens J.P. van der Steen, Fabrizio Torricelli, Matteo Ghittorelli, Gerwin H. Gelinck, Arthur H.M. van Roermund, *Senior Member, IEEE*, and Eugenio Cantatore, *Fellow, IEEE*

Abstract— Three novel differential amplifier topologies using double gate a-IGZO TFTs on flexible substrate are presented in this paper. The designs exploit positive feedback and a load with self-biased top gate to achieve the highest static gain in single stage a-IGZO amplifiers reported to date. After fabrication, the three amplifiers exhibit respectively a static gain of 14 dB, 21.5 dB and 30 dB, with a bandwidth of 2 kHz, 400 Hz and 150 Hz. Also, for each circuit the input referred noise has been measured to be 420  $\mu V_{rms}$ , 195  $\mu V_{rms}$  and 146  $\mu V_{rms}$ , respectively. Based on these results, the a-IGZO amplifier providing the highest gain is suitable as front-end for heart rate measurements and, with some further optimization verified in simulation, can also be used for other bio-potential applications, like electro hysterogram and electro cardiogram.

Index Terms— a-IGZO, amplifier, bio-potential, ECG, EMG, EHG, flexible, flicker noise, front-end, thin film transistor.

#### I. INTRODUCTION

**T**EART, muscles in activity and neural tissues generate Thio-potentials, which are by nature signals distributed over the body surface. However, ambulatory bio-potential measurements are often impaired by patient movements, which induce strong variations in the impedance of the measurement electrodes. This causes large unwanted signals, called "motion artefacts", which are typically in the same frequency range as the bio-potentials, and thus difficult to distinguish from the target signals. Compared to traditional methods of bio-potential monitoring using bulky wet and dry passive electrodes, ultra-light electrodes in adhesion to the skin and integrating analogue front-ends can potentially reduce motion artefacts, while increasing the robustness to common-mode electric disturbances like e.g. interference from the mains. This is because a very light electrode is likely to experience small mechanical forces and thus small alterations

C. Garripoli, A.H.M. van Roermund and E. Cantatore are with the Mixed-Signal Microelectronics Group, Eindhoven University of Technology, P.O. Box 513, 5600MB Eindhoven, The Netherlands (e-mail: C.Garripoli@tue.nl).

of the mutual position between electrode and skin during the movements. A technology platform able to manufacture ultra light-weight circuits on large area flexible substrates would thus be ideally suited to measure bio-potentials distributed on the body surface, while improving resilience to motion artefacts and interferers. Large-area electronics manufactured at near to ambient temperature on flexible plastic substrates seems thus an excellent fit to medical applications based on bio-potential measurements.

A first well-known application example is multi-led electro cardiogram (ECG) acquisition. Another interesting application is presented in [1], where the electro hysterogram (electrical activity due to the uterus contractions - EHG) is monitored by a matrix of electrodes placed on top of the abdomen of pregnant women. From the analysis of the EHG signals over a certain area the contraction conduction velocity can be extracted, which can be used to estimate preterm delivery with high accuracy. Further examples include EMG [2] and EEG measurements [3], muscular stimulation [4], etc.

Crucial to the development of electronics on flexible foils are semiconductor materials which can be processed at low temperature. The most popular are probably pentacene [5], amorphous Silicon (a-Si) [6], and amorphous Indium-Gallium-Zinc Oxide (a-IGZO) [7]. This last material is gaining increasing interest due to its higher mobility [8], which in circuits leads to higher transconductance, higher gain and lower thermal noise. Also the large area uniformity of a-IGZO [9] is very relevant to circuits, as it results in better matching, higher resilience to common mode disturbances, and lower offsets.

Many applications of a-IGZO Thin Film Transistors (TFTs) have been demonstrated already, such as large AMOLED display backplanes [10], USB powered NFC tags [11], and flexible x-ray imagers [12].

In order to enable all these applications, high-performance analogue, digital and mixed-signal circuit blocks manufactured with a-IGZO TFTs on flexible substrates need to be developed. Analogue building blocks such as amplifiers have been already shown [13] – [18], and also DACs [19], and logic circuits [11]. On the other hand, some other basic blocks are still not available. For instance, the implementation of stable reference circuits, such as bandgap references, is not trivial with a-IGZO, due to the lack of bipolar transistors and

J.-L. P. J. van der Steen, is with the Holst Centre/TNO, Eindhoven 5656AE, The Netherlands.

F. Torricelli is with Department of Information Engineering, University of Brescia, Brescia 25123, Italy

G. H. Gelinck is with the Holst Centre/TNO, Eindhoven 5656AE, The Netherlands, and also with the Department of Applied Physics, Technical University of Eindhoven, Eindhoven 5612AZ, The Netherlands.

diodes. For this reason, it is difficult to build stable biasing circuits and supply regulators in this technology.

The focus of this paper is on analogue front-end amplifiers for bio-potential measurement manufactured with a-IGZO TFT on flexible substrate. More in detail, novel a-IGZO single stage amplifiers with high gain, which can be used as first stage in a bio-potential front-end chain, are proposed, designed and characterised. Increasing the gain of the first stage in a front-end relaxes the noise requirements of the following gain stages, thus improving overall power consumption and area occupation. Special attention is devoted to the experimental analysis of the amplifier noise performance, which is typically missing in prior literature, and to understand if these blocks can successfully support different kind of applications based on bio-potential measurements.

The paper is further organised as follows: In Section II the process technology is introduced, together with a model of the a-IGZO TFT channel current and noise. In Section III three novel a-IGZO high-gain amplifier topologies are introduced and analysed. Measurements of these amplifiers are presented in Section IV. In Section V the measurements results are discussed, followed by some conclusions in Section VI.

#### II. PROCESS TECHNOLOGY AND TFT MODELLING

In this section, an overview of the a-IGZO TFT fabrication process is given, followed by an introduction to the modelling of channel current and noise.

#### A. a-IGZO TFT devices

The devices manufactured in our technology are TFTs with a-IGZO as semiconductor. Since only a-IGZO is used, only n-type transistors are available.

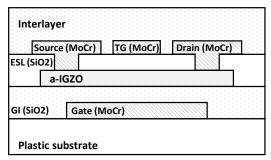

Fig. 1 shows the cross section of a typical device, which has a staggered bottom-gate top-contact structure. All the layers are processed at a maximum temperature of 200 °C on top of a flexible PEN plastic substrate, which is hold on glass during manufacturing and released afterwards. The circuits realized can thus be bent without modifying in significant way their electrical characteristics, as it has been shown in [20].

First, a 100 nm chromium-molybdenum metal film, which provides the gate layer, is sputtered on top of the flexible plastic substrate, and patterned using photolithography. On top, a 200 nm SiO<sub>2</sub> gate insulator is formed by a PECVD process, which is followed by the DC sputtering of the IGZO layer with a thickness of 12 nm. After the IGZO deposition a photoresist layer is spin coated on top, and is exposed using maskless lithography tools. The IGZO layer is thus wet-etched in an oxalic acid solution, followed by the stripping of the photoresist layer. Above the semiconductor there is an Etch-Stop Layer (ESL), which prevents damage of the IGZO when processing the other layers. In order to create the contact openings, the ESL layer is etched and a second metal layer is sputtered to form the source and drain. Finally, a passivation layer (interlayer) is sputtered on top of the second metal layer in order to avoid interaction with the environment, and protect the layers underneath from further processing steps. The overall process is made on a 32 cm by 32 cm substrate.

**Fig. 1:** Cross section of an a-IGZO TFT. The layer stack is formed as follows (from the bottom): Plastic substrate, gate metal, gate insulator (GI), a-IGZO, ESL, source/drain metal, and final insulator (interlayer).

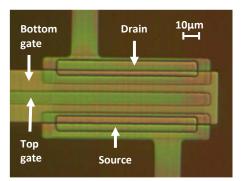

Fig. 2: Picture of a fabricated double gate TFT.

Due to the presence of the ESL on top of the semiconductor, it is possible to have an area overlapping the channel on the second metal layer, which can be used as a second (or top) gate (TG in Fig. 1). Because of the extension of the connection from the contact opening, the top gate will only have a partial overlap with the channel, as shown in Fig. 1. Fig. 2 shows a microscope picture of a double gate TFT, in which the metallization of gate, drain, and source are recognizable.

The minimum feature size of this technology is 5  $\mu$ m, which results in a minimum channel length of 15 $\mu$ m for single gate devices, and 30  $\mu$ m for double gate devices.

#### B. Channel current modelling

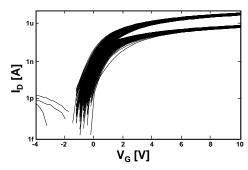

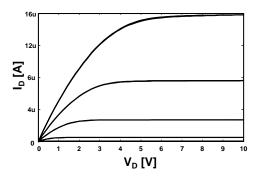

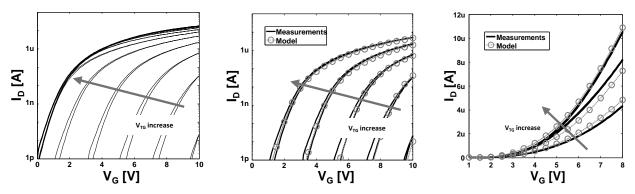

Fig. 3 shows the measured transfer curves of 100 single gate TFTs with the same aspect ratio, measured on the same foil, while Fig. 4 shows a sample output characteristic from this population of devices. In order to describe these characteristics, the analytical physical-based model described by Ghittorelli et al. in [21] has been implemented in a Verilog-A script, and run on an electrical simulator.

To extract the model parameters, first, the transfer and output curves have been measured on groups of devices with length scaling from 200  $\mu$ m down to 15  $\mu$ m and width scaling from 200  $\mu$ m down to 15  $\mu$ m. Then, the parameters for the channel model are extracted according to the procedure described in [22]. It has been observed that the model in [21] tends to overestimate the drain current due to contact effects. For this reason, the contact model described in [23] has been added to the simulation model, and its parameters have been

Fig. 3: Transfer characteristics measured on 100 single gate TFTs manufactured on the same foil, with  $W/L = 100 \mu m/30 \mu m$  at drain voltage of 0.1 V and 1 V

Fig. 4: Output curves measured on a TFT with  $W/L=100\mu m/30\mu m$  at  $V_G=\{2; 4; 6; 8; 10\}$  V

suitably extracted from the measurements.

In order to model the electrical characteristics of double gate TFTs, an approach similar to [24] has been followed. It has been observed that the TG bias modifies the transfer curves in two ways: a threshold modulation for negative TG bias, and a modulation of the on-current for positive TG bias. As observed in [24], threshold modulation occurs for negative TG-source bias voltages, which causes depletion of the region underneath the TG. The threshold voltage of the whole channel will increase as the depletion layer under the top gate increases, and this can be justified by a capacitive division between the bottom gate and top gate potential.

On the other hand, when a positive voltage is applied to the TG, a modulation of the channel on-current is observed. Under

this bias condition, indeed, accumulation in the semiconductor layer under the TG occurs. If the main TFT channel above the bottom gate is formed, the total on-current is increased due to the presence of the second accumulation sheet. If the main TFT channel is absent, due to the bottom gate (VG) bias, the device remains off because the second accumulation sheet cannot reach the source and drain contacts.

Taking into account these phenomena, the influence of the TG bias on the transistor characteristics has been modelled for  $V_{TG} < 0 \text{ V}$  as follows:

$$V_{TH} = V_{TH,0} - \eta V_{TG} \tag{1}$$

And for  $V_{TG} > 0V$  as:

$$I_D = I_{D,0} (1 + \alpha V_{TG}) \tag{2}$$

(1) describes the threshold modulation as linear function of TG voltage by means of a top gate coupling coefficient η, as explained also in [24].V<sub>TH,0</sub> is the value of threshold voltage with zero applied TG bias. For this particular technology, the thickness of the gate insulator layer is double compared to the ESL, and, due to different processing, the dielectric constant of the gate dielectric is lower than that of the ESL. This leads to a  $\eta$  which is as large as 2.1. The on-current increase with positive  $V_{TG}$  is modelled in (2) with a linear dependence of the on-current on the TG voltage, through the coefficient a. The value of  $\alpha$  is extracted from measurement and is 0.25 V<sup>-1</sup>. I<sub>D,0</sub> represent the drain current with zero applied TG bias. Fig. 5a shows the typical transfer characteristics obtained measuring a double gate TFT. Confirming our analysis, it can be observed that the transfer curve moves as the TG voltage increase from negative towards zero. For positive TG the subthreshold region is basically independent on V<sub>TG</sub>, while the above threshold current increases as the TG voltage becomes more positive.

In Fig. 5b a comparison between the model and the measurements is shown for negative TG bias voltages in the range -5 V to -1 V. A very good agreement is reached. Fig. 5c shows the same comparison for positive TG bias voltages of 0 V, 2 V and 5 V. In this bias region, a larger disagreement between model and measurements can be observed. This is because the on-current modulation factor  $\alpha$  is actually not exactly constant for changing TG bias. For this reason, further studies on the modelling of TG bias influence on the TFT

Fig. 5a: Transfer characteristics measured with  $V_{TG}$  in the range {-5,5} and a step of 1 V, increasing in the direction of the arrow. 5b: Detail of negative  $V_{TG}$  measurements and simulations: a threshold modulation is observed. 5c: Measurements and simulations for positive  $V_{TG} = 0$ ; 2; 5 V: an on-current modulation is observed.

**Fig. 6:** Schematic of the amplifier with positive feedback and diode connected load.

characteristics are needed.

#### C. Device noise modelling

Current noise in field effect transistors is typically modelled by two main contributions: thermal noise and flicker noise. The former has been described using the Johnson formulation [25]:

$$S_{ID}(f) = 4k_B T (2/3 g_m) \tag{3}$$

Where  $k_B$  is the Boltzmann constant, T is the temperature, and  $g_m$  is the transconductance of the device.

For low frequency noise, the Hooge model described in [26] is used. Because of the dependence of the thermal noise on the transcoductance, numeric differentiation is typically needed to simulate thermal noise. This approach is prone to numeric errors. To avoid this, and also to have a tool which enables hand calculations, an analytic expression of the channel current has been used here [27]:

$$I_D = \frac{W}{L} \beta [V_{OV,S}^{\ \gamma} - V_{OV,D}^{\ \gamma}] \tag{4}$$

where the overdrive voltage  $V_{ov,X}$  is defined as:

$$V_{OV,X} = V_{SS} \ln[1 + \exp(\frac{V_G - V_X - V_{TH}}{V_{SS}})]$$

(5)

and X refers to source or drain nodes, while  $V_{SS}$  is the subthreshold slope. The parameters of this analytic model are extracted from measurements according to [28]. The transconductance is then calculated analytically as  $\partial I_D/\partial V_G$ , with  $I_D$  defined in (4), and it is used to calculate the thermal contribution to the total TFT noise Power Spectral Density (PSD) in simulation.

Flicker noise in a-IGZO devices is well described by mobility fluctuation theory, as shown in [29], and its PSD can be described as follows:

$$S_{ID}(f) = \frac{\alpha_H q I_D^2}{fWLC_i(V_{GS} - V_{TH})}$$

(6)

In (6) the PSD is function of geometrical TFT parameters, the bias point, and the Hooge coefficient  $\alpha_H$ . The latter has been extracted from noise measurements on different circuit topologies, and is equal to 0.025. This value determined for  $\alpha_H$  is well in line with values previously reported in literature

**Fig. 7:** Schematic of the amplifier positive feedback and a new topology for the load circuit.

**Fig. 8:** Amplifier with positive feedback and a load circuit (M<sub>3</sub>, M<sub>5</sub>, and M<sub>7</sub>) which drastically improves DC gain.

[29], [30] for a-IGZO TFTs.

#### III. DESIGN OF NOVEL IGZO AMPLIFIER CIRCUITS

In this section, three novel amplifier topologies built using unipolar a-IGZO TFTs are presented. The main goal of these circuits is to improve the DC gain provided by a single stage amplifier. This is important and challenging, because unipolar TFT circuits, like the ones explored here, typically suffer from reduced gain. The best a-IGZO single stage amplifier reported in prior literature is described in [31], and its gain is 9.86 V/V.

Our first amplifier consists of a simple differential pair with positive feedback applied to the top gates of the input devices, which is used as a starting point for further optimization. The other two architectures contain non-conventional load circuits which exploit the top gate available in our technology.

Also, a first attempt to realize a reliable bias scheme for a-IGZO circuits is shown.

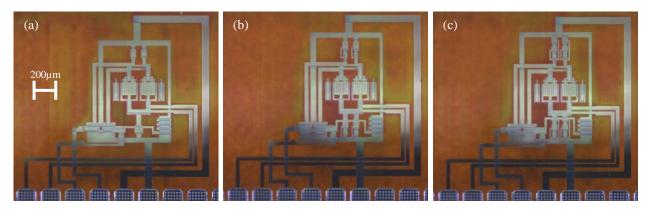

Fig. 9: Microphotograph of the amplifiers presented in Sections III.A (a), III.B (b), and III.C (c).

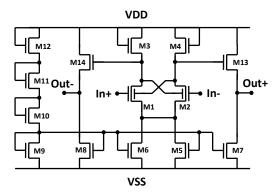

#### A. a-IGZO differential amplifier with positive feedback

Fig. 6 shows the schematic of the first topology studied. M1 and M2 are double gate devices, connected as a source coupled differential pair. Transistors M3 and M4 are n-type TFTs in a diode connected configuration, and act as load of the differential amplifier. The top gate of the drivers in each branch is connected to the output of the opposite branch, in a cross coupled fashion, creating a positive feedback which increases the gain. Analytically, the small-signal gain can be calculated to be:

$$G = \frac{g_{m1,2}/g_{m3,4}}{1 - \alpha g_{m1,2}/g_{m3,4}}$$

(7)

in this equation the open loop gain is given by the ratio of driver to load transconductances, multiplied by the top gate coupling factor. Since the top gate-source DC bias point ( $V_{TG}$ ) is positive, the coupling coefficient is reduced to on-current modulation coefficient  $\alpha$ , which is 0.25. The loop gain is less than one, and the closed loop gain is increased by the positive feedback.

At the output stage, a buffer, which consists of a source follower stage M13-M14, is used to interface the amplifier with the measurement setup. It also has the function of level shifter, and brings the output DC voltage to a bias level similar to the input nodes. This enables the straightforward use of a resistive feedback network around the amplifier, if needed.

Transistors M5 to M12 compose the bias circuit of this amplifier. The supply voltage is divided by four through a voltage divider composed by M9 to M12. This voltage is then used to bias the gate of M5 to M8, which are used as tail current source for the amplifier stage and the buffers. Above threshold and in saturation region (4) becomes:

$$I_D = \frac{W}{L} \beta (V_{GS} - V_{TH})^{\gamma} \tag{8}$$

From eq. 8 the output bias point as function of the supply voltage can be easily calculated as:

$$V_{O} = V_{CC} - \left[ \sqrt[7]{\frac{S_{6}}{S_{3}}} (V_{CC} / 4 - V_{TH}) + V_{TH} \right] - \left[ \sqrt[7]{\frac{S_{14}}{S_{8}}} (V_{CC} / 4 - V_{TH}) + V_{TH} \right]$$

(9)

Here  $S_{\rm i}$  represents the W/L ratio of the TFT  $M_{\rm i}$  and  $V_{CC}$ =V<sub>DD</sub>-V<sub>SS</sub> is the supply rail. From (9), it is easy to observe that, if  $S_6=S_3$ , and  $S_{14}=S_8$ , the output bias point will be equal to half of the supply rail, independently on the value of threshold voltage. Realising an output voltage bias point which is insensitive to threshold variations can be very useful in case of cascading different gain stages. Also, it allows alignment of the input and output common mode levels, enabling the use of resistive feedback networks. The proposed threshold-insensitive biasing of the output node works well as long as the devices are in saturation regime, and if the devices are matched. This biasing approach provides an efficient way to fix the voltage bias points independently of TFT threshold variations, which can be as large as a few volts between different technology batches. The drawback is that the bias current is not set directly by the biasing circuitry, but it is defined by the tail current source topology and the supply voltage. For this reason, the three amplifier topologies presented in this section will have different bias currents at the same supply voltage.

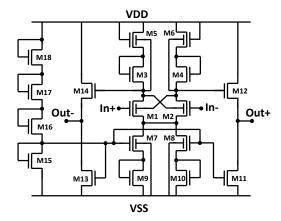

B. a-IGZO differential amplifier with positive feedback and source degenerated load with self-biased top gate

The amplifier presented in this section uses a new topology which increases the output resistance, and thus the DC gain. As shown in Fig. 7, M5 and M3 are diode connected TFTs in series, and the top gate of M5 is connected to the source of M3. When the current in this branch increases, the voltage across  $M_3$  increases, and the  $V_{TG}$  of  $M_5$  becomes more negative. When this happens,  $M_5$  is depleted of charges and becomes more resistive. Therefore, the total small signal output resistance is larger than the series of two diode connected load, due to the effect of the second gate over  $M_5$ . The total output resistance can be expressed as:

$$R_{OUT} = \frac{1}{g_{m5}} \left[ 1 + \frac{g_{m5}}{g_{m3}} (1 + \eta) \right]$$

(10)

Since the  $V_{TG}$  is negative,  $\eta$  corresponds to the threshold modulation coefficient, which is typically bigger than 2 for this technology. As transistors M3 and M5 are equal, (10) clearly shows that this topology increases the small signal resistance of M3 by a factor of  $1+\eta$ .

The technique implemented for biasing this circuit is similar to the one described in section III.A. However, here the complete

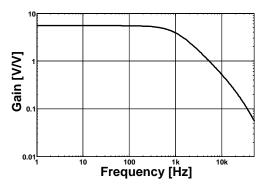

Fig. 10: Frequency response of the circuit in Fig. 6

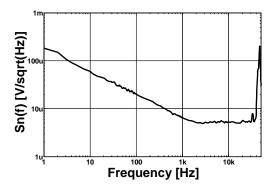

**Fig. 11:** Input noise spectral density of the circuit in Fig. 6

load circuit is replicated as a tail current source, namely  $M_7$ ,  $M_9$ ,  $M_8$ , and  $M_{10}$ . Also in this circuit  $S_{13} = S_{14}$ , and  $S_{11} = S_{12}$ , as in section III.A. Therefore, setting the  $V_{GS}$  of  $M_{13}$  (and thus of M14) and  $V_{G7}$  -  $V_{S9}$  (and thus  $V_{G5}$  -  $V_{S3}$ ) equal to  $V_{CC}/4$  will bring the output bias voltage to half of the supply rail.

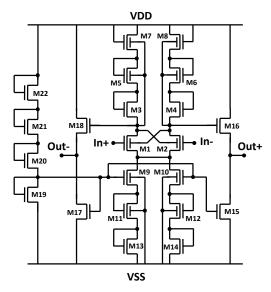

C. a-IGZO differential amplifier with positive feedback and enhanced source degenerated load with self-biased top gate

The amplifier presented in this section represents a further improvement in terms of DC gain compared to the topologies discussed previously. The schematic is shown in Fig. 8.

This topology uses the same technique to increase the output resistance as described in section III.B, but adds another double gate diode load, M7, on top the stack, with its second gate connected to the source of M3.

The total output resistance can be expressed in this case as:

$$R_{OUT} = \frac{1}{g_{m7}} + \frac{1}{g_{m5}} (1 + \eta) + \frac{1}{g_{m3}} (1 + \eta)^2$$

(11)

(11) shows that the output resistance of M5 is increased by a factor of  $1+\eta$ , and the output resistance of M3 is increased by  $(1+\eta)^2$ , which leads to a remarkable increase in DC gain, compared to the stage presented in III.A.

For this amplifier, the input pair and the bias techniques are the same explained in section III.A and III.B.

#### IV. MEASUREMENT RESULTS

The circuits presented in Section III have been designed and fabricated on foil as described in Section II. The plate contains devices for the characterization of the technology and several

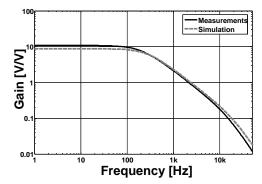

Fig. 12: Frequency response of the circuit in Fig. 7

**Fig. 13:** Input noise spectral density of the circuit in Fig. 7

test circuits. The transfer and output characteristics of 12 TFTs with widths ranging from 15  $\mu m$  to 200  $\mu m$  and lengths ranging from 15  $\mu m$  to 200  $\mu m$  have been measured using the Keysight B1500A Semiconductor Parameter Analyser. The results have been used to extract the parameters of the model implemented in the simulator.

The measurement setup for the amplifiers consists of a voltage buffer, connected with probe needles and short coax cables the output of the amplifiers, and an instrumentation amplifier. The output of the instrumentation amplifier is fed into the HP35670A Dynamic Signal Analyser in order to measure the frequency response and output noise. The parasitic capacitance introduced by this setup is about 20 pF, and all measurements use a supply voltage for the amplifiers of  $\pm 10~\rm V$ .

In the following subsections, the measurement results of the different amplifier topologies are reported. In the last subsection the agreement between measurements and circuit simulations is discussed.

#### A. Differential amplifier with positive feedback

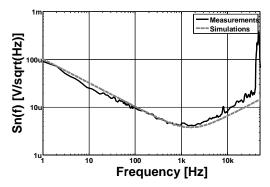

The frequency response and noise spectral density referred to input for the amplifier in Fig. 6 (Section III.A) have been measured, and the results are shown in Fig. 10 and 11. The DC gain is measured to be 5.4 V/V, or 14 dB. The cutoff frequency reaches 2 kHz, due to the internal pole of the amplifier. The output pole is at about 20 kHz.

The noise spectral density clearly shows a flicker behaviour up to the corner frequency of 2 kHz, reaching about 200  $\mu V/Hz^{1/2}$  at 1 Hz, down to 5  $\mu V/Hz^{1/2}$  in the thermal noise region. The integrated equivalent noise at the input is 420  $\mu V_{rms}$ . The measured current consumption of the gain stage is 2.5  $\mu A$ .

### B. Differential amplifier with positive feedback and source degenerated load with self-biased top gate

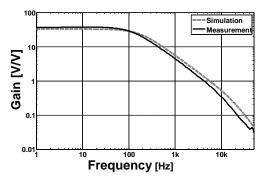

The measurements of the amplifier in Fig. 7 (Section III.B), shown in Fig. 12, demonstrate a DC gain of 12 V/V, or 21.5 dB, which is more than a factor two improvement on the previous topology. At the same time, because of the increase in output resistance, the bandwidth decreases to 400 Hz. The output pole, due to the load capacitance, stays at 20 kHz.

The measured noise spectrum is presented in Fig. 13. The noise spectral density at 1 Hz is 100  $\mu V/Hz^{1/2}$ , and the total equivalent integrated noise at the input is 195  $\mu V_{rms}$ .

It is interesting to notice that the graph shows a 1/f behaviour up to 1 kHz, followed by a positive slope in the noise spectral density at higher frequencies. This phenomenon is observed because the main contribution to the noise in the circuit comes from TFTs which are not the input pair. When this happens, the noise transfer function is different from the signal transfer function. For this reason, the spectrum of the input equivalent noise shows a behaviour which is different from the typical 1/f trend at low frequency and white noise at high frequency. In this particular case, as it is demonstrated analyzing the contribution of the different TFTs in an AC noise simulation, the largest contribution to the noise comes from the source degeneration TFTs M3 and M4 (Fig. 7), followed by the input pair.

The current consumption measured for the gain stage is 100nA.

## C. Differential amplifier with positive feedback and enhanced source degenerated load with self-biased top gate

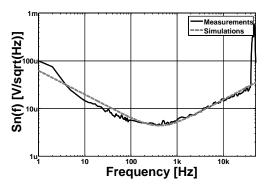

In Fig. 14 and 15 are shown the measurements of both the frequency response and input noise spectrum of the circuit in Fig. 8 (Section III.C). The frequency response shows that this circuit has a DC gain which reaches 35 V/V, or 30 dB, and a cutoff frequency of 150 Hz (Fig. 14). The topology adopted for the load gives thus a 16 dB improvement compared to the circuit with diode connected load.

The input noise spectral density is shown in Fig. 15, and the integrated input noise is 146  $\mu V_{rms}$ . The same behaviour observed in the noise spectral density of Fig. 13 is present in the graph of Fig. 14, because the main contribution to the noise comes from the TFTs  $M_3$  and  $M_4$  in Fig. 8.

The low-frequency noise measurements require seven hours of measurements time, and we could not observe relevant changes of the amplifier performance during this operational time.

Repeating the noise measurements of this amplifier topology after 10 months of shelf life, the gain was found constant at 30dB, but the 3dB bandwidth decreased to 8Hz and the input referred noise increased to 290  $\mu$ Vrms. TFT stack optimization and suitable encapsulation layers are presently actively researched to improve shelf life stability.

Fig. 14: Frequency response of the circuit in Fig. 8

**Fig. 15:** Noise referred to input of the circuit in Fig. 8

The measured power consumption for the gain stage is 20 nA. It is important to notice that the chosen biasing strategy does not fix the tail currents, and thus circuits with different topologies do have different biasing currents. However, the DC gain of all circuits proposed in Section III is at the first order independent from the bias current, as it is actually determined by the ratio of transcoductances. For this reason we can be sure that the improvements in DC gain are actually achieved thanks to the novel circuit topologies proposed, and are not due to changes in the tail currents.

#### D. Circuit simulations

The measurements of the circuits described in sections III.A to III.C show very good agreement with the simulation results, which are obtained using the analytical physical-based model described in Section II and the parameter set extracted from the characterization TFTs. In particular, the graphs in Fig. 12 and 13 show that the model describes well the AC behaviour of the circuits.

Fig. 13 and 15 also show a good agreement between input noise spectral density measurements and the AC noise simulations based on the model presented in Section II. A comparison between the topologies presented in this work is given in Table I, while a comparison with previous literature has been given in Table III.

TABLE I

COMPARISON BETWEEN THE TOPOLOGIES PRESENTED IN THIS WORK

|       | Gain<br>[dB] | BW<br>[Hz] | Unity<br>gain<br>freq.<br>[kHz] | Current cons. [nA] | Input referred noise [V <sub>rms</sub> ] | Noise<br>efficiency<br>factor |

|-------|--------------|------------|---------------------------------|--------------------|------------------------------------------|-------------------------------|

| III.A | 14           | 2000       | 4                               | 2500               | 420 μ                                    | 582                           |

| III.B | 21.5         | 400        | 2.5                             | 100                | 195 μ                                    | 120                           |

| III.C | 30           | 150        | 5.5                             | 20                 | 146 μ                                    | 66                            |

#### V. DISCUSSION

#### A. Circuit results

A major drawback of designing circuits in a-IGZO technology is the lack of a complementary n and p-type devices, which strongly limits the options for circuit topologies, and especially has a detrimental impact on gain. For this reason, the second gate in the source/drain metal layer has been exploited here in order to design nonconventional topologies targeting high DC gain in single stage amplifiers. As the measurements show, the circuits in III.B and III.C reach a gain above 20dB, which allows relaxing the noise requirements of the following stages. It is worth mentioning that high gain unipolar topologies based on loads in zero-V<sub>GS</sub> configuration are not suitable to our technology, since the value of the threshold voltage is always above zero, and thus bias currents would become too low to guarantee any useful bandwidth.

The poor speed performance obtained compared to silicon devices is due to the low mobility offered by a-IGZO, which is at least two orders of magnitude lower than crystalline silicon, and to the high value of parasitic capacitances in the non self-aligned TFT devices offered by our technology.

As discussed in Sections IV.B and IV.C, the noise performance in the proposed amplifiers is mainly influenced by TFTs in the load circuits. This means that there is still margin to improve the noise performance of these gain stages.

It is interesting to notice that in current literature on low frequency noise in a-IGZO TFTs, a dependence of the input-referred flicker noise on the bias current has been noticed [30]. However, a difference of just a factor 4 can be observed between the low-frequency noise densities in Fig. 11 and 15, while the bias current in these two circuits differs by almost two orders of magnitude. Deriving the input referred flicker noise from (6) and using the simplified current model in (4) the input flicker noise for a single TFT can be written as:

$$S_{n,in}(f) = \frac{2\alpha_H q}{C_i \gamma^2 W^{\frac{\gamma+1}{\gamma}} L^{\frac{\gamma-1}{\gamma}} f} \sqrt[\gamma]{\frac{I_D}{\beta}}$$

(12)

The  $\gamma$  parameter obtained from parameter extraction is 3.3, thus scaling the current by 2 orders of magnitude should result in a decrease in PSD only by a factor of 7. Therefore, even if a dependency of the 1/f noise from the bias point exists, reducing the current to decrease low frequency noise is not a very effective strategy. Standard approaches such as increasing the area of the devices will be much more effective and can be used to further improve the noise level in the

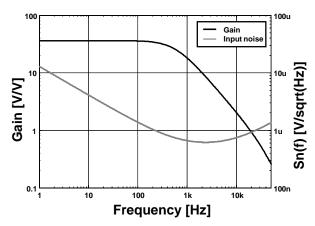

**Fig. 16:** Simulation results of gain and input noise spectral density for the amplifier described in III.C, optimized for improved noise performances.

TABLE II

WIDTH AND LENGTH OF THE TFTS IN TOPOLOGY III.C, BEFORE AND AFTER

OPTIMIZATION.

| TFT                 | W/L [µm/µm] before optimization | W/L [µm/µm] after optimization |

|---------------------|---------------------------------|--------------------------------|

| M1, 2               | 400/30                          | 2000/30                        |

| M3, 4, 13, 14       | 15/15                           | 100/100                        |

| M5,6,7,8,9,10,11,12 | 30/30                           | 120/100                        |

amplifiers proposed in this work.

#### B. Application perspective

The characteristics of flexibility and large area coverage, make our technology suitable for medical applications in which the acquisition of bio-potential on a surface is helpful or necessary. One example is described by Rabotti et al. in [1], where a matrix of passive electrodes is used to acquire electro EHG signals. These signals are used to monitor the uterine action potential conduction velocity, in order to predict preterm labour of pregnant women. The system uses at a moment a matrix of passive electrodes and a large number of discrete bio-potential amplifiers, resulting in an obtrusive and unpractical solution. A matrix of electrodes on foils with embedded a-IGZO TFT bio-potential amplifiers would be an excellent approach to ensure wearability and comfort of use in this application. In [1] it has been shown that it is possible to extract conduction velocity with very good accuracy from signals having an SNR of 5.88 dB. Here the SNR is expressed

$$SNR = \frac{V_{sign,pp}}{2\sqrt{2}V_{n,rms}} \tag{13}$$

The amplitude of the EHG signal is typically more than 500  $\mu Vpp$  in a 10 Hz bandwidth: the requirement for a front end to meet the target SNR is thus an input noise of 90  $\mu V_{rms}$ . The best of the presented amplifiers reaches 125  $\mu V_{rms}$ , input noise in 10Hz band, therefore the target SNR demanded by EHG seems at reach. Indeed, Fig. 16 shows the simulation of gain and input noise for the amplifier topology presented in III.C, after some further optimization in the transistor dimensions to

TABLE III

PERFORMANCE COMPARISON

|              | Gain<br>[dB] | BW<br>[kHz] | Unity<br>gain<br>freq.<br>[kHz] | Power cons.<br>[μW] |         | Nr. of stages |

|--------------|--------------|-------------|---------------------------------|---------------------|---------|---------------|

| [10]         | 22.5         | 5.6         | 31                              | 160                 |         | 3             |

| [11]         | 19           | 25          | 330                             | 6760                |         | 2             |

| [12]         | 25           | 220         | 3900                            | 2320                |         | 2             |

| [13]         | 34           | 5           | N.A.                            | 570                 |         | 1             |

| [14]         | 18.7         | 108         | 427                             | 0.9                 |         | 3             |

| [15]         | 24.5         | 6           | 32                              | N.A.                |         | 3             |

| [28]         | 19.9         | 0.25        | 2.5                             | N.A.                |         | 1             |

| This<br>work | 30           | 0.15        | 5.5                             | $0.4^{*}$           | 188.4** | 1             |

Power consumption for a 20V supply voltage: \*including only the gain stage; \*\* including the gain stage and the output buffer, which was designed to drive an off-chip load of 20pF.

decrease the input noise. This amplifier shows an input noise of 20  $\mu V_{rms}$  in the EHG band, with a current consumption in the gain stage of 32 nA, and thus is sufficiently low-noise for EHG measurements. Besides, if chopping is used to decrease the influence of 1/f noise on the amplification chain, applying a chopping frequency of only 30 Hz to the amplifier presented in Section III.C will already be sufficient to meet the SNR required for EHG measurements.

Another case study which is worth mentioning is Heart Rate (HR) monitoring during physical activities, described in [32]. In this kind of wearable application, the use of a flexible electronic frontend could be a very interesting option, for its potential of decreasing motion artefacts. The authors of [32] use a Doubechies orthonormal wavelet to improve the detection rate of R-spikes present in the ECG signal. The algorithm is evaluated by analysing real signals with different SNR, from 36 dB to 6 dB, and the results show a correct detection rate of 94.8% on signals with 6 dB of SNR.

Considering the amplitude of R-waves, which is typically larger than 1 mV  $_{pp}$  in a 100 Hz bandwidth, the input noise in band can be as high as 177  $\mu V_{rms}.$  This is larger than the input noise measured for the amplifier presented in section III.C. Therefore, we can say that our best amplifiers are already suitable for HR detection in the presence of typical signal amplitudes.

Finally, the noise performance required for medical diagnosis on ECG [33] is less than 30  $\mu V_{rms}$  integrated noise in a 150 Hz band, which means that none of the amplifiers we measured meets this requirement. However, the noise-optimized amplifier simulated in Fig. 16 has an input equivalent noise in the ECG band of 29.5  $\mu V_{rms}$  and thus would be suitable, from the SNR perspective, to perform medical-grade ECG measurements, even without chopping

#### VI. CONCLUSION

In this paper different topologies of high-gain single stage a-IGZO amplifiers have been presented, together with their dynamic measurement and, for the first time in literature, their experimental noise characterization. As a first result, the novel amplifier topologies shown in this paper improve the DC gain compared to single-stage a-IGZO amplifiers previously presented in literature. Table II shows TFT dimentions before and after optimization. Secondly, the value of the Hooge parameter  $\alpha_H$  extracted by low frequency noise circuit measurements is in agreement with previous literature results available for a-IGZO TFTs. Finally a very good agreement has been achieved between circuit simulations of noise and AC dynamics of the amplifiers circuits and the corresponding measurements. The experimental characterization shows that the proposed amplifier which achieves the best integrated input noise can be used for HR detection in typical cases. Furthermore, simulations demonstrate that with an improved design, both EHG measurements and medical grade ECG acquisition can be performed using an a-IGZO front-end. The integration of ultra-lightweight electrodes and front-end amplifiers on a foil in adhesion with the skin appears thus as a promising innovative route to build systems for the measurement of bio-potentials distributed on the body surface with the ability to ensure high immunity from motion artefacts.

#### ACKNOWLEDGEMENT

This research is supported by the Dutch Technology Foundation STW, which is part of the Netherlands Organisation for Scientific Research (NWO), and which is partly funded by the Ministry of Economic Affairs.

#### REFERENCES

- C. Rabotti, M. Mischi, S. G. Oei, J. W. M. Bergmans, "Noninvasive Estimation of the Electrohysterographic Action-Potential Conduction Velocity," IEEE Trans. Biomed. Eng., VOL. 57, NO. 9, Sept. 2010.

- [2] Zwarts M. J., Stegeman D. F., "Multichannel surface EMG: basic aspects and clinical utility," Muscle Nerve. 2003 Jul;28(1):1-17.

- [3] L.F. Márton, L. Bakó, S.T. Brassai, L. Losonczi, "Multichannel EEG Signal Recording Analysis based on Cross Frequency Coupling Method," INTER-ENG 2013, 10-11 October 2013, Petru Maior University of Tirgu Mures, Romania.

- [4] W. Happak; H. Gruber; J. Holle; W. Mayr; C. Schmutterer; U. Windberger; U. Losert; H. Thoma, "Multi-channel indirect stimulation reduces muscle fatigue," Proceedings of the Annual International Conference of the IEEE Engineering in Medicine and Biology Society, 1989

- [5] H. Klauk, M. Halik, U. Zschieschang, G. Schmid, W. Radlik, "Polymer Gate Dielectric Pentacene TFTs and Circuits on Flexible Substrates" IEEE IEDM 2002.

- [6] K. Long, A. Z. Kattamis, I.-C. Cheng, H. Gleskova, S. Wagner, and J. C. Sturm, "Stability of Amorphous-Silicon TFTs Deposited on Clear Plastic Substrates at 250 C to 280 C," IEEE Electron Device Letters, VOL. 27, NO. 2, Feb. 2006.

- [7] M. Mativenga, M. H. Choi, J. W. Choi, J. Jang, "Transparent Flexible Circuits Based on Amorphous-Indium-Gallium-Zinc-Oxide Thin-Film Transistors," IEEE Electron Device Letters, VOL. 32, NO. 2, Feb. 2011.

- [8] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," Nature, VOL. 432, 25, Nov. 2004.

- [9] J. K. Jeong, J. H. Jeong, J. H. Choi, J. S. Im, S. H. Kim, H. W. Yang, K. N. Kang, K. S. Kim, T. K. Ahn, H. J. Chung, M. Kim, B. S. Gu, J. S. Park, Y. G. Mo, H. D. Kim, H. K. Chung, "12.1-Inch WXGA AMOLED Display Driven by Indium-Gallium-Zinc Oxide TFTs Array," SID 2008 Digest.

- [10] J. Lee, D. Kim, D. Yang, S. Hong, K. Yoon, P. Hong, C. Jeong, H. Park,

- S. Y. Kim, S. K. Lim, S. S. Kim, "World's Largest (15-inch) XGA AMLCD Panel Using IGZO Oxide TFT," SID 2008 Digest.

- [11] K. Myny, B. Cobb, J. L. van der Steen, A. K. Tripathi, J. Genoe, G. Gelinck, P. Heremans, "Flexible Thin-Film NFC Tags Powered by Commercial USB Reader Device at 13.56MHz," IEEE International Solid-State Circuits Conference 2015.

- [12] G. H. Gelinck, A. Kumar, D. Moet, J. P. J. van der Steen, A. J. J. M. van Breemen, S. Shanmugam, A. Langen, J. Gilot, P. Groen, R. Andriessen, M. Simon, W. Ruetten, A. U. Douglas, R. Raaijmakers, P. E. Malinowski, K. Myny, "X-Ray Detector-on-Plastic With High Sensitivity Using Low Cost, Solution-Processed Organic Photodiodes," IEEE Trans. El. Dev., VOL. 63, NO. 1, Jan. 2016.

- [13] K. Ishida, R. Shabanpour, B. K. Boroujeni, T. Meister, C. Carta, F. Ellinger, L. Petti, N. S. Münzenrieder, G. A. Salvatore, G. Tröster, "22.5 dB Open-Loop Gain, 31 kHz GBW Pseudo-CMOS Based Operational Amplifier with a-IGZO TFTs on a Flexible Film," IEEE Asian Solid-State Circuits Conference Nov. 2014.

- [14] R. Shabanpour, K. Ishida, T. Meister, N. Münzenrieder, L. Petti, G. Salvatore, B. Kheradmand-Boroujeni, C. Carta, G. Tröster, F. Ellinger, "A 70°Phase Margin OPAMP with Positive Feedback in Flexible a-IGZO TFT Technology," IEEE MWSCAS 2015.

- [15] Shabanpour, R., et al. "High gain amplifiers in flexible self-aligned a-IGZO thin-film-transistor technology." Electronics, Circuits and Systems (ICECS), 21st IEEE International Conference on. 2014.

- [16] Bahubalindruni, Pydi Ganga, et al. "Analog circuits with high-gain topologies using a-GIZO TFTs on glass." Journal of Display Technology 11.6 (2015): 547-553.

- [17] Zysset, Christoph, et al. "IGZO TFT-based all-enhancement operational amplifier bent to a radius of 5 mm." IEEE Electron Device Letters 34.11 (2013): 1394-1396.

- [18] Kim, Kichan, Keun-Yeong Choi, and Hojin Lee. "a-InGaZnO thin-film transistor-based operational amplifier for an adaptive DC–DC converter in display driving systems." IEEE Transactions on Electron Devices 62.4 (2015): 1189-1194.

- [19] D. Raiteri, F. Torricelli, K. Myny, M. Nag, B. Van der Putten, E. Smits, S. Steudel, K, Tempelaars, A. Tripathi, G. Gelinck, A. Van Roermund, E. Cantatore, "A 6b 10MS/s current-steering DAC manufactured with amorphous Gallium-Indium-Zinc-Oxide TFTs achieving SFDR > 30dB up to 300kHz," IEEE International Solid-State Circuits Conference 2012.

- [20] A. K. Tripathi, K. Myny, B. Hou, K. Wezenberg, G. H. Gelinck, "Electrical Characterization of Flexible InGaZnO Transistors and 8-b Transponder Chip Down to a Bending Radius of 2 mm," IEEE Trans. El. Dev., VOL. 62, NO. 12, Dec. 2015.

- [21] M. Ghittorelli, F. Torricelli, L. Colalongo, Z. M. Kovács-Vajna, "Accurate Analytical Physical Modeling of Amorphous InGaZnO Thin-Film Transistors Accounting for Trapped and Free Charges," IEEE Trans. El. Dev., VOL. 61, NO. 12, Dec. 2014.

- [22] F. Torricelli, K. O'Neill, G. H. Gelinck, K. Myny, J. Genoe, E. Cantatore, "Charge Transport in Organic Transistors Accounting for a Wide Distribution of Carrier Energies—Part II: TFT Modeling," IEEE TRANS. EL. DEVI., VOL. 59, NO. 5, MAY 2012.

- [23] A. Valletta, A. Daami, M. Benwadih, R. Coppard, G. Fortunato, M. Rapisarda, F. Torricelli, L. Mariucci, "Contact effects in high performance fully printed p-channel organic thin film transistors," Applied Physics Letters 99, 233309 (2011).

- [24] K. Myny, M. J. Beenhakkers, N. A. J. M. van Aerle, G. H. Gelinck, J. Genoe, W. Dehaene, P. Heremans, "Unipolar Organic Transistor Circuits MadeRobust by Dual-Gate Technology," IEEE JSSC, VOL. 46, NO. 5, May 2011.

- [25] Razavi, Behzad. Design of Analog CMOS Integrated Circuits. Boston, MA: McGraw-Hill, 2001.

- [26] L. K. J. Vandamme, Xiaosong Li, D. Rigaud, "I/f Noise in MOS Devices, Mobility or Number Fluctuations?," IEEE Trans. Electron Devices, VOL. 41, NO. 11, Nov. 1994.

- [27] O. Marinov, M. J. Deen, U. Zschieschang, H. Klauk, "Organic Thin-Film Transistors: Part I—Compact DC Modeling," IEEE TRANS. Electron Devices, VOL. 56, NO. 12, Dec. 2009.

- [28] M. Jamal Deen, O. Marinov, U. Zschieschang, H. Klauk, "Organic Thin-Film Transistors: Part II—Parameter Extraction," IEEE Trans. Electron Devices, VOL. 56, NO. 12, Dec. 2009.

- [29] W. Cheong, C. Hwang, I. Cho, H. Kwon, J. Lee, "Low-Frequency Noise in Amorphous Indium-Gallium-Zinc-Oxide Thin-Film Transistors" IEEE Electron Device Letters, VOL. 30, NO. 5, MAY 2009.

- [30] T. Fung, G. Baek, J. Kanickib, "Low frequency noise in long channel amorphous In–Ga–Zn–O thin film transistors," J. Appl. Phys. 108, 074518 2010.

- [31] Y.-H. Tai, H.-L. Chiu, L.-S. Chou, and C.-H. Chang, "Boosted Gain of the Differential Amplifier Using the Second Gate of the Dual-Gate a-IGZO TFTs," IEEE Electron Device Letters, VOL. 33, NO. 12, Dec. 2012.

- [32] U. J. Yoon, Y. S. Noh, Y. M. Han, M. Y. Kim, J. H. Jung, I. S. Hwang, H. R. Yoon, I. C. Jeong, "Electrocardiogram signal processing method for exact Heart Rate detection in physical activity monitoring system: Wavelet Approach," IECBES 2010.

- [33] Anonymous, "Diagnostic electrocardiographic devices" ANSI/AAMI EC11-1991. Arlington, VA: Association for the Advancement of Medical Instrumentation, 1991.

Carmine Garripoli was born in Locri, Italy, in 1989. He received the Bachelor and Master degrees in electronic engineering from the Università della Calabria, Arcavacata di Rende, Italy, in 2011 and 2014, respectively. He is currently working toward the Ph.D. degree at the Mixed-signal Microelectronics

Group, Department of Electrical Engineering, TU Eindhoven, Eindhoven, The Netherlands. His research interests include analog and mixed signal circuit for front ends, metal-oxide TFT technology, and large area electronics on flexible substrate.

Jan-Laurens J.P. van der Steen received the M.Sc. and Ph.D. degree in electrical engineering from the University of Twente, The Netherlands, in 2006 and 2011, respectively. Part of his Ph.D. research was carried out at the University of Udine, Italy. He has been with the Holst Centre, Eindhoven, The Netherlands, since

2011.

**Fabrizio Torricelli** received the Ph.D. degree from the University of Brescia, Brescia, Italy, in 2010. He was a Post-Doctoral Fellow with the Eindhoven University of Technology, Eindhoven, The Netherlands, from 2010 to 2012. He is currently an Assistant Professor with the University of Brescia. His current research

interests include the theoretical and experimental analysis of organic and amorphousoxide materials, the design of optoelectronic devices, and nonvolatile memories.

Matteo Ghittorelli (S'15) received the Ph. D. degree from the University of Brescia, Brescia, Italy, in 2016, where he is currently a Post-Doctoral Fellow. His current research interests include the physical modelling and simulation of organic and amorphous-oxide thin film transistors, and the design of high-

functionality circuits in emerging large-area technologies.

Gerwin H. Gelinck received the Ph.D. degree from the Technical University in Delft, The Netherlands, in 1998. He joined Philips Research as a Senior Scientist in 1998. From 2002 to 2006, he was the Chief Scientist of Polymer Vision. Since 2007, he has been a Program Manager at Holst Centre. Since 2014, he has been a

Professor at the Technical University of Eindhoven.

Arthur H.M. van Roermund (SM'95) was born in Delft, The Netherlands, in 1951. He received the M.Sc. degree in EE in 1975 from Delft University of Technology and the Ph.D. degree in Applied Sciences from K.U.Leuven, Belgium, in 1987. From 1975 to 1992 he was with Philips Research Laboratories in

Eindhoven. From 1992 to 1999 he has been a full professor at the EE department of Delft University of

Technology, where he was chairman of the Electronics Research Group and member of the management team of DIMES. From 1992 to 1999 he has been chairman of a twoyears post-graduate school for chartered designer. From 1992 to 1997 he has been consultant for Philips. October 1999 he joined Eindhoven University of Technology as a full professor, chairing the Mixed-signal Microelectronics Group. From Sept. 2002 to Sept. 2012 he is has been director of research of the Department of Electrical Engineering. From 2009 to 2012 he has been a member of the supervisory board of the NRC Photonics research centre. He is chairman of the board of ProRISC, the microelectronics platform in the Netherlands, and vice chair of the ICT-research platform for the Netherlands (IPN). Since 2001, he is standing co-organiser of the yearly workshop on Advanced Analog Circuit Design (AACD). In 2004 he achieved the Simon Stevin Meester award, coupled to a price of 500.000 € for his scientific and technological achievements. In 2007 he was member of an international assessment panel for the Department of Electronics and Information of Politecnico di Milano, Italy; in 2009 for Electronics and Electrical Engineering for the merged Aalto University Finland; and in 2012 for KTH, Stockholm, Sweden. He authored/co-authored about 500 articles and 30 books.

Eugenio Cantatore (F'16) received his Master and Ph.D. Degree in Electrical Engineering from Politecnico di Bari, Bari, Italy in 1993 and 1997 respectively. From 1997 to 1999 he was fellow at the European Laboratory for Particle Physics (CERN) Geneva, Switzerland. In 1999 he

moved to Philips Research, Eindhoven, The Netherlands as senior scientist and in 2007 joined the Eindhoven University of Technology, where he is full professor since 2016. His research interests include the design and characterization of electronic circuits exploiting emerging technologies as well as the design of ultra-low power micro-systems for medical applications. He authored or co-authored more than 140 papers in journals and conference proceedings, and 13 patents or patent applications. He is active in the Technical Program Committees of ESSDERC, ESSCIRC and ISSCC and has been member of the Executive Committee of ISSCC. Since 2013 he is chair of the Technology Directions subcommittee of ISSCC. In 2006 he received from ISSCC the Beatrice Winner Award for Editorial Excellence and was nominated in the Scientific American top 50 list. He received the Philips Research Invention Award in 2007, the Best Paper Award from ESSDERC 2012 and the Distinguished Technical Paper Award from ISSCC 2015.