# Analysis and Assessment of Modular Multilevel Converter Internal Control Schemes

Shuren Wang, Student Member, IEEE, Grain P. Adam, Member, IEEE, Ahmed M. Massoud, Senior Member, IEEE, Derrick Holliday, and Barry W. Williams

Abstract—Adoption of distributed submodule (SM) capacitors in a modular multilevel converter (MMC) necessitates complex controllers to ensure the stability of its internal dynamics. This paper presents comprehensive analysis and assessment of different proportional resonant (PR)-based control schemes proposed to stabilize the internal dynamics and ensure ac and dc sides power quality of the MMC within a dc transmission system. With the consideration of passive component tolerances, different energy and voltage based control schemes under various conditions are analyzed. It has been established that without vertical voltage balance control, unequal passive component values in the upper and lower arms of the same phase-leg may cause: unbalanced fundamental currents in the arms, unequal dc voltage across the arms, and fundamental oscillations in the common-mode currents that lead to fundamental frequency ripple in the dc link current. The theoretical analysis that explains this mechanism is presented, and is used to show that vertical voltage balancing is necessary for the nullification of arm voltage difference and suppression of odd oscillations caused by capacitive/inductive asymmetry between arms of the same phase-leg. Simulations support the theoretical analysis and the effectiveness of voltage balancing in ensuring correct operation, independent of tolerances of the MMC passive elements and operating conditions. A new direct method for elimination of fundamental oscillations in the common-mode and dc link current is proposed. Experimental results from a singlephase MMC prototype validate the presented theoretical discussions and simulations.

Index Terms—dc link oscillations, internal control, internal dynamics, modular multilevel converter.

### I. INTRODUCTION

WITHIN point-to-point and multi-terminal high-voltage direct current (HVDC) transmission systems, the voltage source converter (VSC) is the preferred technology as it offers dc power reversal with change of current polarity rather than change of voltage polarity (as with line commutated converters), independent control of active and reactive power with the ability to generate leading and lagging reactive power, no minimum dc power flow; and resilience to ac network disturbances and faults. Among many VSC topologies, the MMC is the preferable choice because of its modularity, low switching frequency and high quality ac/dc waveforms [1]–[3].

ang@strath.ac.uk; grain.adam@strath.ac.uk; derrick.holliday@strath.ac.uk; barry.williams@strath.ac.uk).

Ahmed M. Massoud is with Qatar University, Doha, Qatar. (e-mail: ahmed. massoud@qu.edu.qa).

Manuscript received July 27, 2018; revised November 19, 2018; accepted February 03, 2019. (Corresponding author: Shuren Wang.)

Shuren Wang, Grain P. Adam, Derrick Holliday and Barry W. Williams are with the University of Strathclyde, Glasgow, G1 1RD, U.K. (e-mail: shuren.w

The MMC requires a number of high and low-level controllers to regulate its output ac and dc voltages, as well as the active and reactive power exchanged with the ac grid. With the high modularity of the MMC circuit topology, however, there are many distributed passive voltage sources or energy tanks facilitating the use of low-voltage rated switching devices, for suppression of electromagnetic interference (EMI) and for providing fault-tolerant operation. The use of distributed floating capacitors in the MMC results in a converter with complex internal dynamics (dynamics between SMs of the same arm, upper and lower arms of the same leg, and different legs), so the converter is difficult to stabilize over the full operating range. Also, MMC capacitor voltages affect the synthesis of common and differential mode arm voltages that create common and differential mode currents respectively. Normally, the common-mode current within the MMC leg consists of dc and even harmonic currents, and its dc component helps transfer power between the dc side and the MMC arms, while the ac component (usually referred to as circulating current) increases capacitor voltage ripple and semiconductor losses [4]-[7]. Many control strategies have been developed to suppress the circulating current and capacitor voltage ripple, and these strategies broadly exploit injection of appropriate harmonics into the common-mode voltage or arm currents [8]– [12]. The comparatively decoupled nature of the inner and outer MMC circuits facilitates the control of the inner variables without influencing the output performance, neither dc side nor ac side. Once the MMC internal dynamics are controlled, its overall performance under normal and abnormal ac grid conditions, particularly its dynamic response due to the decoupling of SM capacitor voltage from the dc link voltage, are improved [13]–[19].

1

Still, fundamental plus higher-order harmonics which appear as capacitor voltage ripple are unavoidable due to the unique operation of the MMC where both inner and outer circuits contribute to arm currents which flow through the SM capacitors with finite combined inertia, causing voltage ripple which is out of phase in the upper and lower arms of each leg. The main variables that influence the internal dynamics are SM, arm and leg voltages, which represent three coupled control hierarchies within the MMC that could be exploited to enhance

its performance independent of operating conditions. Voltage control of each SM capacitor is essential for ensuring switching device safety and good performance of higher hierarchies. Different methods for managing voltage differences amongst SMs of the same arm caused by different charging/discharging times and non-ideal parameters are widely discussed in the literature, including SM voltage control algorithms based on either centralized or individual schemes [20]-[25]. Many have focused on control of higher hierarchies such as arm and leg capacitor voltages, and arm and leg energy (power integral), considering both normal and abnormal cases [26]-[49]. The importance of controlling MMC arm voltage was first recognized in [26] where internal voltage regulation was implemented based on an individual SM voltage balancing method with Phase-Shifted Carrier Pulse Width Modulation (PSC-PWM). The individual SM balancing method was improved in [27]-[34] by direct control of the MMC arm voltages, which is realized through manipulation of the active powers of the upper and lower arms of each phase-leg in order to estimate the appropriate fundamental current to be injected into the common-mode current of each leg. Early studies identified the importance of controlling the MMC internal stored capacitive energy for safe and proper operation [35], [36]. Subsequently, a comprehensive study of MMC capacitive energy variation during asymmetric ac faults was presented, considering three control objectives (suppression of negative currents to zero, balanced active power or balanced reactive power) [37]. The study concluded that the control objective which eliminates reactive power oscillations offers clear advantage over maintaining balanced output phase current or oscillation free active power, particularly, in terms of capacitor energy and voltage ripple for reactive power loadings, ranging from unity to zero power factor [37]. In [38]-[44], methods of balancing the arm voltage (or energy) using the concept of equivalent arm capacitance was proposed, and was assessed considering a single-phase to ground fault with a number of control objectives. However, some of the claims in [38] may be misinterpretation of the findings, particularly with regard to the relationship between the ability to suppress circulating currents and injection of negative sequence current into the ac grid. But generally, the methods discussed in [38]–[44] show satisfactory MMC operation during normal and abnormal conditions.

In general, most research neglects passive element tolerances such as for SM capacitance and arm inductance [50]–[52]. A steady-state comparison of voltage and energy MMC balancing approaches that employ three-level flying capacitor SMs, is presented in [53], and its main finding indicates that unequal capacitances affect the quality of the ac side waveforms when an energy-based control approach is employed. The impact of unequal arm inductances on MMC performance is investigated in [54], and this study recommends the use of additional controllers (proportional resonant, PR-based) to prevent the development of a dc component in the ac side waveforms and to suppress fundamental oscillation in the dc link. A general modeling framework and design methodology that considers parameter uncertainty in order to decide the required design margins and predict the operation range has been introduced in

[55], but does not reveal any potential implications of SM capacitance or arm inductance tolerances on wider MMC performance. Although the negative effects of SM capacitor voltage difference can be eliminated by voltage balancing algorithms at the SM level, the differences in SM capacitances due to tolerances could not be handled adequately by the innerarm balancing within each arm. That is, as the ac output controller selects different SMs during operation with a fixed number of inserted and bypassed SMs, capacitance asymmetry may appear as variable capacitance in each phase-leg (upper plus lower arms), rather than fixed capacitance  $C_{SM}/N$ .

Considering MMC passive component tolerances, this paper presents comprehensive analytical assessments of different control methods proposed in the literature to control MMC internal dynamics, namely, the voltage and energy based controllers and their variants. This assessment considers two SM-level voltage balancing approaches. The presented mathematical analysis and simulations show that unequal SM capacitance in the upper and lower arms of the same phase-leg (vertical asymmetry) introduces negative sequence currents into the MMC arms and appears as fundamental current in the common-mode currents; thus, causing excessive voltage ripple in the common-mode voltage, with negative sequence fundamental current tending to leak into the dc link current. Ditto for arm inductance tolerance. Detailed investigation reveals that the vertical voltage-based balancing controller helps suppress fundamental oscillation in the common-mode currents and dc link current in the case of vertical asymmetry of SM capacitances and arm inductances. A direct method for eliminating the fundamental circulating current is proposed. The proposed method is effective in ensuring MMC dc link current quality with worst-case passive component asymmetry at the expense of a marginal reduction in the modulation index control range.

The remainder of this paper is organized as follows: Section II presents a brief review of the fundamentals of the modular multilevel converter, including basic definitions which will be used in subsequent sections. Section III describes a number of control architectures that can be used to manipulate the common-mode current in order to regulate MMC internal dynamics. The mechanism that generates dc side oscillation as a result of different capacitance tolerances between the upper and lower arms of the same phase-leg, is presented in Section IV. Section V presents simulation evaluation of the different control schemes being studied and Section VI gives experimental results. Finally, Section VII concludes this paper.

# II. SYSTEM STRUCTURE AND PARAMETERS

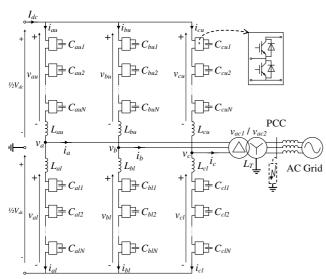

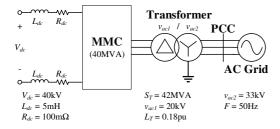

Fig. 1 shows a three-phase half-bridge MMC connected to an ac grid  $(v_{ac2})$  via a  $\Delta$ -Y interfacing transformer. The output phase voltage measured relative to ground at the ac pole of each phase is  $v_{io}$ , and  $V_{dc}$  and  $I_{dc}$  are the dc link voltage and current respectively. Each MMC arm incorporates an arm inductor L and N series-connected SMs.

With the positive direction arm currents  $i_{ij}$  (where, i: a, b, c, are for three phase-legs and j: u, l, indicate the upper and lower arms respectively) and ac output current  $i_i$  as indicated in Fig.

Fig. 1. MMC circuit configuration.

1, the common and differential mode currents  $i_{icm}$  and  $i_{idiff}$  of an arbitrary phase-leg i are defined as  $i_{icm} = \frac{1}{2}(i_{iu}+i_{il})$  and  $i_{idiff} = i_{io}$ =  $i_{iu}$ - $i_{il}$  respectively. This means that the common-mode current refers to the arm current component which is shared between the upper and lower arms of the leg, and consists of a dc component due to dc power transfer and an ac component which is predominantly  $2^{nd}$  order harmonics. For the  $i^{th}$  leg,  $V_{cijk}$ represents the capacitor voltage of the  $k^{th}$  SM in the  $j^{th}$  arm and  $V_{cij}$  is the sum of the SM capacitor voltages of the  $j^{th}$  arm of the  $i^{th}$  phase-leg, where k = 1-N. The voltage developed across an MMC arm  $v_{ij}$  can therefore be approximated by the product of modulation or insertion function  $m_{ij}$  (normally  $0 \le m_{ij} \le 1$ ) and its respective SM capacitor voltage sum  $V_{cij}$ :  $v_{ij}(t) = m_{ij}(t) \times V_{cij}(t)$ [52]. With these assumptions, the differential-mode voltage and current of each phase resemble the output phase voltage  $v_i$  and current, that is,  $v_{io}(t) = v_{idiff}(t) = v_{iu}(t) - v_{il}(t)$ . Also, the common and differential modes of the upper and lower arm capacitor voltage sums are defined as:

$$\Sigma V_{ci} = V_{ciu} + V_{cil}$$

$$\Delta V_{ci} = V_{ciu} - V_{cil}$$

(1)

$$\Delta V_{ci} = V_{ciu} - V_{cil} \tag{2}$$

Then, the common-mode capacitor voltage sum  $(\sum V_{ci})$  is mostly comprised of a dc component and a small ac component that drives the circulating current in each arm, when counter harmonics are not injected into the common-mode voltage of each leg. The differential-mode capacitor voltage sum ( $\Delta V_{ci}$ ) of each leg is mainly comprised of the fundamental ac voltage, provided the upper and lower arm capacitor voltage sums have the same dc components.

Practically, it is essential to account for the passive component tolerances [53], [54], [56] for the following reasons:

- 1) Each MMC SM must be regulated correctly to ensure that the voltage stresses on each SM capacitor and switching device do not exceed their rated voltage;

- Although the majority of publications assume identical SM capacitance, the inherent SM capacitance tolerances have noticeable adverse impact in terms of stored energy variation;

- Provided the SM capacitors and arm inductors play fundamental roles in the synthesis of the ac and dc output voltages and power transfer between ac and dc sides, substantial differences in their magnitudes lead to unbalanced fundamental arm currents, which could affect the common-mode and dc link currents; and

- The assumption of identical SM capacitance leads to performance deterioration of some control methods in hardware implementation, which appears as voltage imbalance between the arms of the same or different legs,

Accurate theoretical quantification of the impact of SM capacitance tolerance on MMC performance is difficult as it involves a large number of components with highly complex dynamics that operate as part of a variable structure system, with variability of the structure influenced by several controllers. The study of the potential impact of SM capacitance tolerance is divided into three parts:

- Capacitance tolerance impacts on the pattern and rate of the capacitor voltage variation at the SM level within each arm (this effect is expected to be mitigated by SM level capacitor voltage balancing);

- Vertical asymmetry (the upper and lower arms of the same phase-legs present different total capacitances) may lead to unequal voltage or energy distribution between the upper and lower arms; and

- Horizontal asymmetry (the phase-legs reflect different equivalent capacitances) may cause unequal energy distribution and excessive circulating currents between

Generally, there are two SM capacitor voltage balancing approaches, depending on the employed modulation method. The first approach calculates the number of SMs to be inserted into the conduction path and bypassed from each arm using nearest voltage level modulation [57]-[59] or pulse width modulation with various carrier arrangements such as Phase-Shifted Carrier PWM (PSC-PWM) [60], [61] or phase disposition PWM (PD-PWM) [62], [63]. The SM number to be inserted and bypassed, and the sorted order of SM capacitor voltages for each arm, are fed to the SM selection algorithm. The second approach assigns the PSC-PWM and a dedicated modulating signal to each SM, with SM capacitor voltage being controlled individually by additional components injected into the main modulation signal of the arms [64]-[68]. As both balancing algorithms usually operate at high frequency [25], [69], the analysis in this paper assumes that the impact of SM capacitance differences at the SM-level is mitigated by the capacitor voltage balancing method.

#### III. ASSESSMENT OF INTERNAL CONTROL SCHEMES

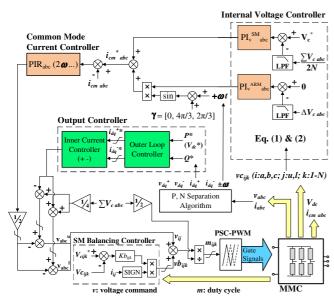

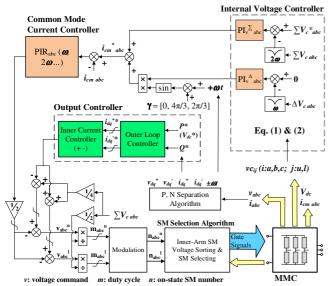

In this section, different control schemes for ensuring MMC internal stability are analyzed. From the modulation and SM voltage balancing point of view, these methods are divided into two broad categories. Methods that use dedicated SM controllers to regulate individual SM capacitor voltage without employing capacitor voltage sorting, are classified as Method-I

Fig. 2. Schematic diagram of Method-I.

Fig. 3. Schematic diagram of Method-II.

Fig. 4. Arm controller schematic diagrams of Methods III and IV.

(with such methods, capacitor voltage balancing and modulation represent two successive stages or layers). Whereas methods that insert or bypass SMs based on the combined outcomes of modulation and a capacitor voltage sorting algorithm, are classified as Methods II to IV (in these cases, capacitor voltage balancing and the modulation process are inseparable).

Fig. 2 and Fig. 3 depict generic control structures for the Methods I and II respectively, with both employing the same controller for regulating the output ac currents and active and reactive power. Both methods employ a positive and negative separation stage that decomposes the three-phase voltages and currents into positive and negative sequence components to be used by the inner current controller to compute the modulating signals [13]–[19].

Because the common-mode arm voltage or common-mode capacitor voltage sum only influences the common-mode current in each leg, its exploitation to regulate arm or leg voltage or energy will not affect the differential ac output current or voltage of the MMC, provided any modification is applied to both the upper and lower arm voltage commands and the modulation functions remain within the linear range (no saturation). All the methods investigated include a dedicated controller for MMC internal dynamics regulation, and a proportional-resonant controller tuned at  $2\omega$  for circulating current suppression in each leg [9], [37], [70]. To minimize the adverse impact of cross-modulation due to undesirable SM capacitor voltage dynamics on the output voltage and current waveforms, a dedicated PI controller is used in each leg to regulate the common-mode capacitor voltage sum independent of the dc link voltage. Thus SM capacitor voltage dynamics and regulation are decoupled from the dc link voltage. From observation of the active power of the upper and lower arms and literature review, injection of a small fundamental current into the common-mode current of each leg improves the vertical balance, specifically, equalizing SM capacitor voltages or energy sum of the upper and lower arms of the same leg [33], [38], [42]–[44].

# A. Method-I: Internal Voltage Control Scheme Based on Individual SM Voltage Balancing

This method does not employ a sorting-based SM capacitor voltage balancing algorithm in the inner layer as originally envisioned by Marquardt. Rather it uses a simple proportional controller at each SM level to regulate the capacitor voltage in an isolated manner. The SM capacitor voltage controller estimates the adjustment to be introduced to the main modulation signal of each arm in order to synthesize the modulating signal to be compared with the dedicated PSC of each SM [26], [71]. A depiction of Method-I in Fig. 2 shows that the main modulation signal of the arm or leg is modified by an amount that represents the output of the capacitor voltage controller multiplied by the polarity of the arm current  $(Kb_{ijk}\times(V_{cijk}*-V_{cijk})\times sign(i_{ij}),$  where  $Kb_{ijk}$  represents the proportional gain of the SM capacitor voltage controller). The main attribute of this method over a sorting-based method is that the average switching frequency of the switches is constant

in all SMs and equal to the assigned carrier frequency, independent of modulation depth. Therefore, this method ensures even thermal distribution and simpler design of the heat management system [72].

Two ways to implement Method-I have emerged, viz. [73]-[76] and [20], [27]–[31]. The main difference is the choice of the reference  $V_{cijk}$ \* used by each SM capacitor voltage controller that ensures capacitor voltage balancing. The first implementation sets the reference voltage for each SM capacitor constant (dc) or equal to the average of the commonmode capacitor voltage sum per leg, excluding the ripple  $(V_{cijk}^*)$ =  $\frac{1}{2}\sum V_{ci}/N$ ). The initial premise of this implementation is that, if the common-mode capacitor voltage sum is tightly controlled and the individual SM capacitor voltages in the entire leg are also controlled to balance, the upper and lower arm capacitor voltage sums of the same leg will be the same, which means vertical balancing is eventually achieved. Low pass filters are needed to prevent introducing SM voltage ripple into the control loops. A common implementation uses the SM arithmetical average voltage of each arm as a reference, balancing SM voltage within one arm. This shows good dynamic response and has low parameter sensitivity [20].

For management of internal arm-level dynamics, Method-I in Fig. 2 uses both average SM capacitor voltage control and arm voltage balancing control [30], [77]. The average SM voltage controller ensures the SM average capacitor voltage of each leg is controlled and independent of the dc link voltage. This is achieved through manipulation of the common-mode current of each leg, whilst the arm voltage balancing controller aims to eliminate any error between the dc components of the capacitor voltage sum of the upper and lower arms of the same leg. This is facilitated by manipulation of the active-power difference between the upper and lower arms of the same leg, through injection of a small fundamental current into the common-mode current which is predominantly dc with a remnant of the circulating current [27]–[34], [76], [78]. As shown in Fig. 2, SM voltage and arm balancing controllers PI<sub>v</sub>SM and PI<sub>v</sub>ARM control the common and differential mode capacitor voltage sums respectively, with the ac components of the measured capacitor voltages low-pass filtered (LPFs in Fig. 2). In previous studies [34], [77], both common and differential mode controllers use only proportional terms, benefiting from the natural ability of the MMC to balance its arm capacitor voltages. Hence the integral terms only accelerate convergence toward the desired settling points with zero steady-state error.

Accordingly, common and differential mode mean capacitor voltage sum control are achieved, therefore, horizontal and vertical balance are ensured with decoupled capacitor voltages. As a well-designed SM balancing scheme can isolate SM-level manipulation and higher-level control, the direct higher level voltage control scheme can naturally be applied to the sorting algorithm, as to be discussed [37].

# B. Method-II: Internal Voltage Control Scheme Based on Sorting Algorithm

The conventional MMC control system has a similar structure to that of the two-level converter with minor controller modifications to account for circulating currents. This approach is known for its simplicity and stability, but its main drawback is that the SM capacitor voltages are directly coupled to (or track) the MMC dc link voltage. This means any change in active power set-point necessitates dc link voltage change of the power controlling converter. The SM capacitor voltages and their corresponding energy levels are also changed. As a result, such a controlled MMC tends to suffer from slow dynamic response and is subject to strict and slow power ramp rates. Therefore, Method-II with an additional control stage to manage the MMC internal dynamics and decouple the common-mode SM capacitor voltage sum from the dc link voltage in order to improve dynamic response, was proposed. In this paper, Method-II adopts similar common and differential mode capacitor voltage sum controllers,  $PI_v^{\Sigma}$  and  $PI_v^{\Delta}$ , respectively, as proposed by Akagi et al. [26], [77], implemented with Method-I to regulate MMC internal dynamics.

The MMC leg common and differential mode capacitor voltage sums contain ac components, predominantly 2<sup>nd</sup> and 1<sup>st</sup> harmonics respectively [51], [79]; therefore, a number of notch filters tuned at  $2\omega$  and  $\omega$  suppress these ac components in Fig.

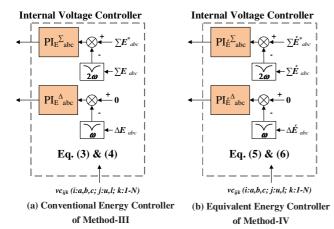

### C. Method-III: Conventional Energy Control Scheme

MMC internal dynamics regulation using energy-based controllers, as shown in Fig. 4(a), is referred to as Method-III in this paper. The control structure is similar to Method-II, but it regulates the dc components of the common and differential mode energy of the upper and lower arms of each leg to be constant and zero respectively [38], [42], [44]. The common and differential mode capacitor energy sums of each leg are:

$$\Sigma E_{i} = \frac{1}{2} \left( \sum_{k=1}^{N} C_{iuk} \times V_{ciuk}^{2} + \sum_{k=1}^{N} C_{ilk} \times V_{cilk}^{2} \right)$$

$$\Delta E_{i} = \frac{1}{2} \left( \sum_{k=1}^{N} C_{iuk} \times V_{ciuk}^{2} - \sum_{k=1}^{N} C_{ilk} \times V_{cilk}^{2} \right)$$

(4)

$$\Delta E_{i} = \frac{1}{2} \left( \sum_{iuk}^{N} C_{iuk} \times V_{ciuk}^{2} - \sum_{ilk}^{N} C_{ilk} \times V_{cilk}^{2} \right)$$

(4)

where the capacitance and voltage of each SM are incorporated into the calculation. Studies have shown that the common and differential mode capacitor energy sums of each leg oscillate or contain the same dominant frequencies as in the common and differential mode capacitor voltage sums respectively, i.e.  $2\omega$ and  $\omega$ , where  $\omega$  represents fundamental angular frequency [42], [44]. Therefore, notch filters tuned at  $2\omega$  and  $\omega$  are adopted respectively to obtain the corresponding dc components. Most (if not all) previous research that has studied the conventional energy-based controller ignores SM capacitance tolerance. Assuming that all SM capacitances are equal results in the dc components of the common and differential mode energy sums being constant and zero respectively, representing sufficient and necessary conditions for balanced arm capacitor voltage sums. Mathematically, forcing the dc component of the total energy of the upper and lower arms to be equal does not ensure that the upper and lower arms have the same dc components of voltage. The adverse implication of such a fallacy remains unobserved in previous studies as the MMC operates away from its maximum modulation index range, whence all SM capacitors of each arm are inserted or bypassed in order to

synthesize the output ac voltage, as will be shown. With unequal capacitance in the upper and lower arms, uncontrolled and unequal fundamental currents are induced into the leg common-mode currents, which can potentially result in a dc output voltage bias.

## D. Method-IV: Equivalent Energy Control Scheme

The energy calculation in Method-IV neglects the SM capacitance tolerances and assumes each arm has an equivalent capacitance [38], [42], and is thus termed "Equivalent Energy Control". The method can be viewed as an alternative implementation of the conventional energy-based controller, but the equal SM capacitance assumption means it can be viewed as another implementation of Method-II using the difference and sum of two arm voltages squared instead of direct control of common and differential mode capacitor voltage sums. Assuming the ideal case of equal SM capacitance, the common and differential mode capacitor voltage sums of the legs are:

$$\sum_{E_{i}}^{e} = \frac{1}{2} C_{arm} \times (V_{ciu}^{2} + V_{cil}^{2})$$

(5)

$$\Delta E_{i} = \frac{1}{2} C_{arm} \times (V_{ciu}^{2} - V_{cil}^{2})$$

(6)

where  $C_{arm}$  represents the equivalent capacitance of the arm and superscript "e" refers to the equivalent energy (or energy calculated based on the equal equivalent capacitance). The reference of common-mode capacitor energy sum for a generic leg is:

$$\sum_{i=1}^{e} \sum_{i=1}^{e} 2 \times \frac{1}{2} C_{arm} (N \times V_{c}^{*})^{2} = 2N \times \frac{1}{2} C_{SM} (V_{c}^{*})^{2}$$

(7)

where  $C_{SM}$  represents the capacitance of each SM and  $V_c$ \* refers to the SM voltage reference as in Fig. 2. Similarly, the controllers are shown in Fig. 4(b) and the control objectives of the internal arm controller using Method-IV are to achieve energy balance both among legs and between upper and lower arms within each leg. When these objectives are satisfied, the following equations hold:

$$\frac{1}{2}C_{arm} \times (V_{ciu}^{2} + V_{cil}^{2}) = \frac{1}{2}C_{arm} \times 2(N \times V_{c}^{*})^{2}$$

$$\frac{1}{2}C_{arm} \times (V_{ciu}^{2} - V_{cil}^{2}) = 0$$

(8)

Solving (8) and (9), yields

$$\frac{1}{2}C_{arm} \times (V_{cii}^{2} - V_{cil}^{2}) = 0 \tag{9}$$

$$V_{ciu}^2 = V_{cil}^2 = (N \times V_c^*)^2 \Rightarrow V_{ciu} = V_{cil} = N \times V_c^*$$

(10)

Practically, in the equivalent energy method, the controllers manipulate the sum and difference of squares of the arm voltage sum, where the term  $\frac{1}{2}C_{arm}$  can be treated as a coefficient lumped into the PI controller gains.

### IV. COMPREHENSIVE ANALYSIS OF INTERNAL ARM-LEVEL **CHARACTERISTICS**

As described, and mentioned in [42], [64], management of the MMC inner dynamics requires horizontal balancing (leg a, b and c) and vertical balancing (upper and lower arms of the same leg, iu and il). Some publications have adopted the use of a dedicated controller to ensure horizontal balancing by forcing the dc link current to be equally split among the three legs of the three-phase MMC. Such enforced equalization of the common-mode dc current of the three legs can lead to unnecessary curtailment of the dc or active power exchanged between the dc and ac sides during unbalanced and asymmetric ac faults [4], [32], [38]. Although this approach performs well during normal operation, it exhibits unsatisfactory performance during operation with unbalanced ac voltages and asymmetric ac faults (as equalization of dc current per leg could be an unachievable control objective in some situations). Therefore, a relaxed MMC horizontal balancing approach is preferred, in which the common-mode capacitor voltage sum of the three legs is controlled to be the same and constant. Such control of the common-mode capacitor voltage sum ensures satisfactory operation over the full range and with fast dynamic response at both the ac and dc sides. This is because of the reduced coupling between the principal ac and dc variables involved in the power transfer and synthesis of the output voltages and currents.

Concerning vertical balancing, unbalanced voltage between the upper and lower arms of the same leg appears not to cause dc offset or even harmonics in the ac output voltage [2], [80], [81]. But this observation is true only when the MMC operates at relatively low modulation indices (where it does not need to insert or bypass all the SMs in its arms to satisfy output voltage requirements). Failure to nullify the errors between the mean value of upper and lower arm capacitor voltage sums (basically differential capacitor voltage sum) may introduce dc offsets into ac output voltages and currents when MMC operation requires all SMs. However, the potential problems of dc offsets and even harmonics in the output waveforms can be avoided by using redundant SMs in each MMC arm or by regulating the capacitor voltage sum of each arm to be higher than the actual dc link voltage (thus, appearing to have redundant SMs). As stated, when the upper and lower arms of the same phase-leg have different capacitances, uncontrolled fundamental current appears in the common-mode current of each phase-leg, and also in the dc link current. This problem could be typically avoided, however, if the dc components of the differentialmode capacitor voltage sums of the upper and lower arms of all three phase-legs are nullified (or forced to zero).

To substantiate this discussion mathematically, approximate analysis is used to explain the influence of asymmetric arm capacitance, assuming [51], [82]:

- Modulation signals are continuous and harmonic free; 1)

- Switching frequency is sufficiently high, so the output and arm currents and voltages can be assumed constant within each switching period;

- The capacitance tolerances between the SMs of each arm are taken into account, but for simplicity these tolerances are reflected to the mean or equivalent capacitance of each arm:

- The SM capacitor voltages within one arm are balanced; 4) and

- Common-mode capacitor voltage sum (SM average) 5) controllers are effective among three legs.

For simplicity, the MMC inherent second and higher even order harmonic circulating currents are suppressed. Thus, taking phase-leg i as an example, the upper and lower arm currents are:

$$i_{iu}(t) = \frac{1}{2}i_i(t) + i_{icm}(t) = \frac{\sqrt{2}}{2}I_i\sin(\omega t + \varphi_i) + I_{icm}$$

(11)

$$i_{il}(t) = -\frac{1}{2}i_{i}(t) + i_{icm}(t) = -\frac{\sqrt{2}}{2}I_{i}\sin(\omega t + \varphi_{i}) + I_{icm}$$

(12)

where  $I_i$  and  $\varphi_i$  are the rms and phase angle of fundamental output current respectively, and  $i_{icm}$  only consists of dc component  $I_{icm}$ .

Independent of the modulation method, the switching functions that describe or define the number of SMs to be inserted from the arms of each leg can be approximated by the followings average and normalized insertion functions:

$$S_{iu}(t) = \frac{1}{2} - \frac{1}{2}M_i \sin(\omega t + \varphi_s) + M_{icm}$$

(13)

$$S_{il}(t) = \frac{1}{2} + \frac{1}{2}M_i \sin(\omega t + \varphi_s) + M_{icm}$$

(14)

where  $M_i$  and  $\varphi_s$  are the amplitude and phase angle of the modulation index respectively,  $M_{icm}$  is the output of commonmode controller,  $0 \le M_i \le 1$  and  $0 \le M_{icm} \le 1$ .

The upper and lower SM average capacitor currents can be approximated as [51], [79]:

$$i_{cu}(t) = I_{icm}(\frac{1}{2} + M_{icm}) - \frac{\sqrt{2}}{8} I_i M_i \cos(\varphi_s - \varphi_i)$$

$$- \frac{1}{2} I_{icm} M_i \sin(\omega t + \varphi_s) + \frac{\sqrt{2}}{2} I_i (\frac{1}{2} + M_{icm}) \sin(\omega t + \varphi_i)$$

$$+ \frac{\sqrt{2}}{8} I_i M_i \cos(2\omega t + \varphi_s + \varphi_i)$$

(15)

$$i_{cl}(t) = I_{icm}(\frac{1}{2} + M_{icm}) - \frac{\sqrt{2}}{8} I_i M_i \cos(\varphi_s - \varphi_i) + \frac{1}{2} I_{icm} M_i \sin(\omega t + \varphi_s) - \frac{\sqrt{2}}{2} I_i (\frac{1}{2} + M_{icm}) \sin(\omega t + \varphi_i) + \frac{\sqrt{2}}{9} I_i M_i \cos(2\omega t + \varphi_s + \varphi_i)$$

(16)

where dc components control the mean SM voltages and fundamental and second-order harmonics constitute SM voltage ripple. By integrating the average capacitor currents in (15) and (16), the upper and lower arm capacitor voltage sums

$$v_{cu}(t) = v_{cu}^{0} + \frac{1}{C_{u}} \int i_{cu}^{\omega, 2\omega} dt$$

$$= V_{cu} + A_{u} \cos(\omega t + \varphi_{s}) - B_{u} \cos(\omega t + \varphi_{t}) + D_{u} \sin(2\omega t + \varphi_{s} + \varphi_{t})$$

(17)

$$v_{cl}(t) = v_{cl}^{\ 0} + \frac{1}{C_l} \int i_{cl}^{\ \omega, 2\omega} dt$$

$$\tag{18}$$

$$= V_{cl} - A_l \cos(\alpha t + \varphi_s) + B_l \cos(\alpha t + \varphi_t) + D_l \sin(2\alpha t + \varphi_s + \varphi_t)$$

$$= V_{cl} - A_l \cos(\omega t + \psi_s) + B_l \cos(\omega t + \psi_i) + D_l \sin(2\omega t + \psi_s + \psi_i)$$

$$I. M. \sqrt{2}I \qquad \sqrt{2}IM \qquad I$$

where

$$A_u = \frac{I_{icm} M_i}{2\omega C_u}$$

,  $B_u = \frac{\sqrt{2}I_i}{2\omega C_u} (\frac{1}{2} + M_{icm})$ ,  $D_u = \frac{\sqrt{2}I_i M_i}{16\omega C_u}$ ,  $A_l = \frac{I_{icm} M_i}{2\omega C_l}$

,

$$B_l = \frac{\sqrt{2}I_i}{2\omega C_l}(\frac{1}{2} + M_{icm})$$

,  $D_l = \frac{\sqrt{2}I_iM_i}{16\omega C_l}$  , and  $C_u$  and  $C_l$  represent the

equivalent capacitances of the upper and lower arms respectively. DC components of capacitor voltages  $v_{cu}^0$  and  $v_{cl}^0$ represent the settling points for the upper and lower arm capacitor voltage sums [50], [51]. Switching action then reflects SM voltage back to the ac terminals and the common-mode voltage of each phase-leg is described by:

$v_{icm}(t) = v_{iu}(t) + v_{il}(t) = NS_{iu}(t)v_{cu}(t) + NS_{il}(t)v_{cl}(t)$  (19) where  $S_{iu}$  and  $S_{il}$  remain unchanged as (13) and (14) because no new component is added into the switching functions. Similarly, as the dc component of the mean common-mode capacitor voltage sum is controlled to  $2N \times V_c^*$ , only ac components are considered.

Based on (13), (14), (17), (18) and (19), the ac components (frequency at  $\omega$ ,  $2\omega$  and  $3\omega$ ) of the leg common-mode voltages are:

$$v_{icm}(t)^{(\omega)} = v_{iu}(t)^{(\omega)} + v_{il}(t)^{(\omega)} = N(\frac{1}{2} + M_{icm})(A_u - A_l)\cos(\omega t + \varphi_s)$$

$$-N[(\frac{1}{2} + M_{icm})(B_u - B_l) + \frac{1}{4}M_i(D_u - D_l)]\cos(\omega t + \varphi_i)$$

$$-\frac{1}{2}M_i(V_{cu} - V_{cl})\sin(\omega t + \varphi_s)$$

(20)

$$v_{icm}(t)^{(2\omega)} = v_{iu}(t)^{(2\omega)} + v_{il}(t)^{(2\omega)} = -N\frac{1}{4}M_i(A_u + A_l)\sin(2\omega t + 2\varphi_s) + N\left[\frac{1}{4}M_i(B_u + B_l) + (\frac{1}{2} + M_{icm})(D_u + D_l)\right]\sin(2\omega t + \varphi_s + \varphi_l)$$

(21)

$$v_{icm}(t)^{(3\omega)} = v_{iu}(t)^{(3\omega)} + v_{il}(t)^{(3\omega)} = \frac{1}{4} NM_i(D_u - D_l)\cos(3\omega t + 2\varphi_s + \varphi_i)$$

(22)

where the voltage ripple at  $\omega$ ,  $2\omega$ , and  $3\omega$  generates corresponding common-mode ac currents. Equation (20) indicates that unequal capacitances of the upper and lower arms of the same leg can lead to the appearance of fundamental voltage in the common-mode capacitor voltage sum which would drive fundamental current in the common-mode loop of each phase-leg. Equation (21) represents the component of the common-mode voltage that would drive 2nd order harmonic current in each phase-leg, which will be eliminated. Any resistance in the common-mode circuit loop is neglected for simplicity, thus only total inductance of the common-mode loop is considered [51]. The amplitude of the  $3\omega$  components is small compared to that at  $\omega$ , so the common-mode current (due to the fundamental voltage ripple) is:

$$\begin{split} i_{icm}(t)^{(\omega)} &= \frac{1}{L_u + L_l} \int v_{icm}(t)^{(\omega)} dt \\ &= K_1 \sin(\omega t + \varphi_s) - K_2 \sin(\omega t + \varphi_i) + K_3 \cos(\omega t + \varphi_s) \\ &= \sqrt{K_1^2 + K_2^2 + K_3^2 - 2K_2 \sqrt{K_1^2 + K_3^2}} \cos(2\varphi_s - \varphi_k) \\ &\times \sin \left[ \omega t + \arctan(\frac{\sqrt{K_1^2 + K_3^2} \sin(\varphi_s + \varphi_k) - K_2 \sin(\varphi_s)}{\sqrt{K_1^2 + K_3^2} \cos(\varphi_s + \varphi_k) - K_2 \cos(\varphi_s)} \right) \end{split}$$

(23)

where  $L_u$  and  $L_l$  are the upper and lower arm inductances respectively,  $\varphi_k = \arctan(\frac{K_3}{K_1}), \qquad K_1 = N \frac{(\frac{1}{2} + M_{icm})(A_u - A_l)}{\omega(L_u + L_l)},$   $K_2 = N \frac{(\frac{1}{2} + M_{icm})(B_u - B_l) + \frac{1}{4}M_i(D_u - D_l)}{\omega(L_u + L_l)}, \text{ and } K_3 = \frac{M_i(V_{cu} - V_{cl})}{2\omega(L_u + L_l)}.$

The amplitude range of the fundamental common-mode current is

$$\sqrt{K_1^2 + K_2^2 + K_3^2 - 2K_2\sqrt{K_1^2 + K_3^2}}$$

$$\leq \sqrt{K_1^2 + K_2^2 + K_3^2 - 2K_2\sqrt{K_1^2 + K_3^2}\cos(2\varphi_s - \varphi_k)} \leq$$

$$\sqrt{K_1^2 + K_2^2 + K_3^2 + 2K_2\sqrt{K_1^2 + K_3^2}}$$

(24)

Considering the range of  $M_i$  and  $M_{icm}$ , and the definitions of  $K_1$ ,  $K_2$  and  $K_3$ , it can be concluded that when  $C_u \neq C_l$  the fundamental frequency current in (23) must exist in the common-mode current.

Accordingly, for one MMC leg, capacitance asymmetry leads to odd harmonics in the common-mode current (mainly a fundamental frequency component), and its amplitude, depending on various variables, increases proportionally with capacitance difference. Generally, asymmetric capacitance in one leg results in two major effects:

As asymmetry is random among the legs, the amplitude and phase angle of the fundamental common-mode currents of the three legs will be unbalanced, causing unbalanced fundamental current to feed into the dc link current; and

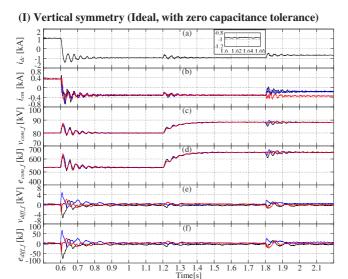

#### (I) Vertical symmetry (Ideal, with zero capacitance tolerance)

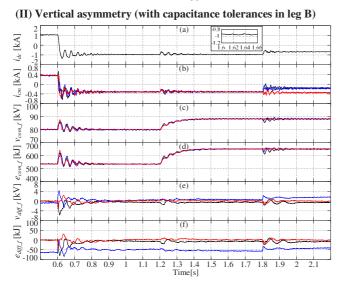

#### (II) Vertical asymmetry (with capacitance tolerances in leg B)

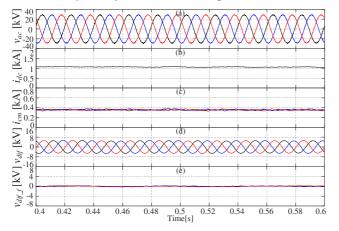

Fig. 5. Waveforms of 40kV-MMC in vertically symmetric and asymmetric cases: (a) ac output voltage  $v_{ac}$ , (b) dc link current  $i_{dc}$ , (c) common-mode current  $i_{cm}$ , (d) differential-mode capacitor voltage sum  $v_{diff}$ , (e) 50Hz-notch filtered differential-mode capacitor voltage sum  $v_{diff}$ .

Fig. 6. Normalized arm terminal voltages and common-mode capacitor voltages of methods in asymmetric case.

Fig. 7. Illustrative 40MW MMC for HVDC transmission system.

2) Such additional fundamental arm currents interact with switching functions, resulting in dc and  $2\omega$  voltage deviation of the upper and lower arms.

The following mathematical derivation establishes the generation of such dc and  $2\omega$  deviation. For simplicity, additional fundamental current is added into the ideal arm currents in (11) and (12):

$$i_{iu}'(t) = \frac{1}{2}i_i(t) + i_{icm}(t)$$

$$= \frac{\sqrt{2}}{2}I_i\sin(\omega t + \varphi_i) + I_{icm} + \sqrt{2}I_{icm\omega}\sin(\omega t + \varphi_{icm\omega})$$

(25)

$$i_{il}'(t) = -\frac{1}{2}i_{i}(t) + i_{icm}(t)$$

$$= -\frac{\sqrt{2}}{2}I_{i}\sin(\omega t + \varphi_{i}) + I_{icm} + \sqrt{2}I_{icm\omega}\sin(\omega t + \varphi_{icm\omega})$$

(26)

where  $I_{icm\omega}$  and  $\varphi_{icm\omega}$  are the rms and phase angle of the fundamental common-mode current respectively. If no active controller is designed for the fundamental oscillation, the switching functions remain as (13) and (14). The SM mean capacitor currents are:

$$i_{cu}'(t) = I_{icm}(\frac{1}{2} + M_{icm}) - \frac{\sqrt{2}}{8}I_iM_i\cos(\varphi_s - \varphi_i) - \frac{\sqrt{2}}{4}I_{icm\omega}M_i\cos(\varphi_s - \varphi_{icm\omega})$$

$$-\frac{1}{2}I_{icm}M_i\sin(\alpha t + \varphi_s) + \frac{\sqrt{2}}{2}I_i(\frac{1}{2} + M_{icm})\sin(\omega t + \varphi_i)$$

$$+ \sqrt{2}I_{icm\omega}(\frac{1}{2} + M_{icm})\sin(\omega t + \varphi_{icm\omega})$$

$$+ \frac{\sqrt{2}}{8}I_iM_i\cos(2\omega t + \varphi_s + \varphi_i) + \frac{\sqrt{2}}{4}I_{icm\omega}M_i\cos(2\omega t + \varphi_s + \varphi_{icm\omega})$$

$$(27)$$

$$i_{cl}'(t) = I_{icm}(\frac{1}{2} + M_{icm}) - \frac{\sqrt{2}}{8}I_iM_i\cos(\varphi_s - \varphi_i) + \frac{\sqrt{2}}{4}I_{icm\omega}M_i\cos(\varphi_s - \varphi_{icm\omega})$$

$$+ \frac{1}{2}I_{icm}M_i\sin(\omega t + \varphi_s) - \frac{\sqrt{2}}{2}I_i(\frac{1}{2} + M_{icm})\sin(\omega t + \varphi_i)$$

$$+ \sqrt{2}I_{icm\omega}(\frac{1}{2} + M_{icm})\sin(\omega t + \varphi_{icm\omega})$$

$$+ \frac{\sqrt{2}}{8}I_iM_i\cos(2\omega t + \varphi_s + \varphi_i) - \frac{\sqrt{2}}{4}I_{icm\omega}M_i\cos(2\omega t + \varphi_s + \varphi_{icm\omega})$$

$$(28)$$

where the dc and  $2\omega$  ac components in (27) each contain a term related to the amplitude of fundamental frequency commonmode current  $\sqrt{2} I_{icm\omega}$  which has the opposite sign to the corresponding term in (28). Charging and discharging SMs with the currents in (27) and (28) causes dc,  $\omega$  and  $2\omega$  differences between the upper and lower arms. Also, both dc and  $2\omega$ frequency voltage differences are introduced by the non-zero fundamental frequency common-mode current. Furthermore, the voltage differences contribute to the common-mode loop current ripple through the coefficient  $K_3$  in (24), leading to MMC inner-leg interactions. Also, this analysis initially assumed the output of the common-mode capacitor voltage sum controller to be a pure dc component to maintain the constant SM average dc voltage. However, the fundamental fluctuations will induce small corresponding components into the PI controllers, depending on bandwidth and phase-shift characteristics. Therefore, both dc and  $\omega$  frequency voltage deviation continues until reaching equilibrium in terms of phase angle and magnitude change. Moreover, the mathematically analysis assumed an ideal MMC dc power supply. However, long distance cables introduce parasitic parameters and as a result, the fundamental oscillation in one leg influences other legs through the weak dc terminal voltage, actuating fundamental oscillations and arm voltage differences as well. This phenomenon could be considered as power circulating among three legs to compensate for the stored energy of

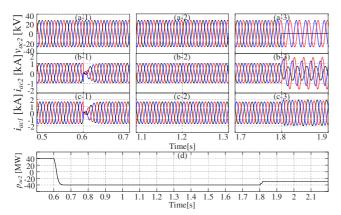

Fig. 8. AC output performance: (a) grid phase voltage  $v_{ac2}$ , (b) grid current  $i_{ac2}$ , (c) MMC side current  $i_{ac1}$ , (d) mean active power  $p_{ac2}$ .

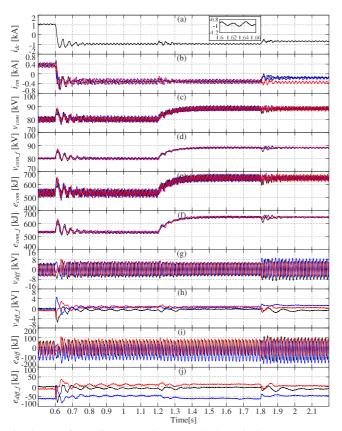

Fig. 9. Waveforms of only average voltage controller in symmetric case: (a) dc link current  $i_{dc}$ , (b) common-mode current  $i_{cm}$ , (c) common-mode capacitor voltage sum  $v_{com}$ , (d) filtered common-mode capacitor voltage sum  $v_{com,f}$ , (e) common-mode capacitor energy sum  $e_{com,f}$ , (g) differential-mode capacitor voltage sum  $v_{diff}$ , (h) filtered differential-mode capacitor voltage sum  $v_{diff}$ , (i) differential-mode capacitor energy sum  $e_{diff}$ , (j) filtered differential-mode capacit

different arms, which is an inter-leg interaction. Based on the previous discussions on such a complicated system, an accurate calculation of the amplitude of the fundamental frequency dc link current ripple caused by passive component tolerances is extremely tedious, with much uncertainty that cannot be accounted for readily, such as collective action of various internal controllers. Therefore, the presented analysis is an attempt to explain the mechanism of the inducement of

fundamental current ripple and its potential causes, rather than a precise quantification of its magnitude. Fortunately, there are various internal control schemes that are able to (or intend to) suppress such ripple, facilitating MMC internal and external decoupling.

For unbalanced grid analysis, most approaches in the literature focus on eliminating the  $2\omega$  power component, which causes the dc voltage and/or dc current oscillation [14]. However, unlike the  $2\omega$  components only occurring during output unbalanced conditions, oscillation at  $\omega$  always exists due to MMC charging and discharging with unequal arm capacitances in the same leg. Similarly, the tolerances of arm inductance within one leg can cause the same current oscillation as the energy stored in the arm inductors and the ac voltage drops they present are no longer balanced. Therefore, additional controllers are needed to regulate the inherent fundamental current difference between arms and energy differences caused by passive component tolerances. This discussion shows that a vertical balancing controller that minimizes the differentialmode capacitor voltage sum is effective for correct MMC operation when passive components tolerances are significant. Also, in the asymmetry case, the incorporation of a dedicated controller to directly eliminate the fundamental current from the common-mode current of each leg, may aid suppression of fundamental frequency oscillation of the dc link current, but cannot eliminate the differential-mode capacitor voltage sum.

#### V. SIMULATION EVALUATION

The MATLAB/SIMULINK MMC model described in section II is used to clarify some of the issues due to the potential mismatch of MMC capacitance and arm inductance.

$\label{eq:table_interpolation} TABLE\ I$  Simulation Parameters of The  $40MVA\ MMC$

| Rated power                    | 40MVA           |  |  |

|--------------------------------|-----------------|--|--|

| DC voltage                     | 40kV            |  |  |

| AC grid line voltage           | 33kV            |  |  |

| AC grid frequency              | 50Hz            |  |  |

| Transformer leakage inductance | 0.18pu          |  |  |

| Transformer ratio              | 20/33kV         |  |  |

| Arm inductance                 | 6.1mH(0.2pu)    |  |  |

| Numbers of SMs per arm         | 20              |  |  |

| SM capacitance                 | 6.7mF(40kJ/MVA) |  |  |

| Modulation carrier frequency   | 1.0kHz          |  |  |

The differences between individual SM capacitance of arms are simulated by making the values of arm equivalent capacitances different, and it is assumed that the asymmetry only exists in leg B for ease of illustration. For horizontal capacitance asymmetry, it is assumed that the equivalent capacitance of leg B SMs is  $0.9C_{SM}$ . Whilst for vertical capacitance asymmetry, the equivalent capacitances of the SMs of the upper and lower arms of leg B are  $0.9C_{SM}$  and  $1.1C_{SM}$  respectively. It is assumed that the SMs of legs A and C have nominal capacitance  $C_{SM}$ . Similar considerations are applied for the arm inductance asymmetry study.

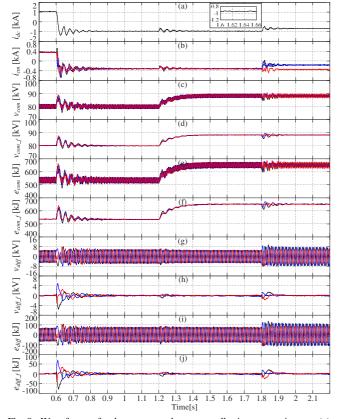

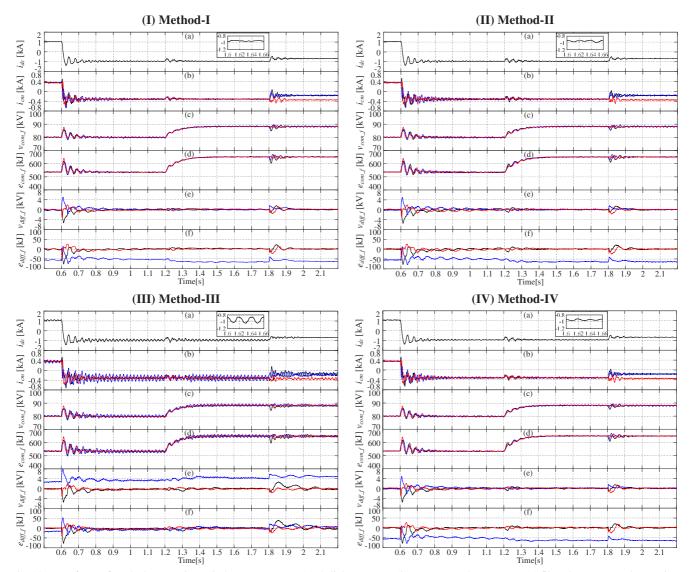

Fig. 10. Waveforms of Methods I to IV in the symmetrical case: (a) dc link current  $i_{dc}$ , (b) common-mode current  $i_{cm}$ , (c) filtered common-mode capacitor voltage sum  $v_{com\_f}$ , (d) filtered common-mode capacitor energy sum  $e_{com\_f}$ , (e) filtered differential-mode capacitor voltage sum  $v_{diff\_f}$ , (f) filtered differential-mode capacitor energy sum  $e_{diff\_f}$ .

# A. Vertical Balance Study of MMC in an Open-Loop Condition

This subsection illustrates basic MMC behavior with and without SM capacitance tolerances in leg B, assuming inverter mode operation, with parameters in Table I but feeding a passive load. Fig. 5 show simulation waveforms of the output ac voltages, dc link current, common-mode currents, and differential-mode capacitor voltage sums, where 0 and  $\pm 10\%$  tolerances are applied to SM capacitances of the arms in leg B, and without active vertical balance control. The plots in Fig. 5-I show that the mean differential-mode capacitor voltage sums of the three legs are near zero with zero SM capacitance tolerance. The dc link current and common-mode currents do not exhibit any low frequency oscillation. However, when  $\pm 10\%$  SM capacitance tolerance is incorporated, Fig. 5-II shows the common-mode currents contain noticeable unbalanced ac components, with significant 50Hz components

in both the common-mode and dc link currents [see Fig. 5-II(b) and (c)]. Also, the pre-filtered and post-filtered differential-mode capacitor voltage sums become unbalanced and deviate from zero, respectively [see Fig. 5-II(d) and (e)].

To further substantiate the discussion in section III, particularly, the effectiveness of different implementations of the vertical balancing controllers previously described, are assessed when SM capacitance tolerance is considered. Three sets of simulation cases are presented, namely, without vertical balancing, and with voltage and energy based vertical balancing methods, where the dc link voltage remains 40kV, modulation index is fixed at 95%, and two set points common-mode capacitor voltage sums, namely, 80kV ( $V_c$ =1pu) and 88kV ( $V_c$ =1.1pu).

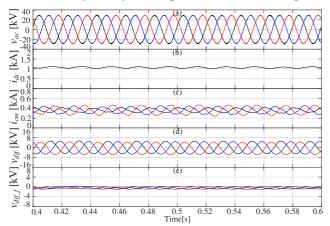

Fig. 6 summarizes the normalized arm voltages of leg B and their corresponding upper and lower arm capacitor voltage sums, with vertical SM capacitance asymmetry of  $\pm 10\%$ . Fig.

Fig. 11. Waveforms of average voltage controller in horizontal asymmetry case: (a) dc link current  $i_{cls}$ , (b) common-mode current  $i_{cm}$ , (c) common-mode capacitor voltage sum  $v_{coms}$ , (d) filtered common-mode capacitor voltage sum  $v_{com}$ , (e) common-mode capacitor energy sum  $e_{com}$ , (f) filtered common-mode capacitor energy sum  $e_{com}$ , (g) differential-mode capacitor voltage sum  $v_{diff}$ , (h) filtered differential-mode capacitor voltage sum  $v_{diff}$ , (i) differential-mode capacitor energy sum  $e_{diff}$ , (j) filtered differential-mode capacitor energy sum  $e_{diff}$ ,

6(a) and (d), and (b) and (e) show that without vertical balancing and with voltage-based vertical balancing the drift of the differential-mode capacitor voltage sums from zero remain small for both set points of the common-mode capacitor voltage sums of 1pu and 1.1pu; thus both arms are able to synthesize the correct arm voltages. In contrast, Fig. 6(c) and (f) show that with the energy-based vertical balancing the drift of the differential-mode capacitor voltage sums from zero becomes large as the set point of the common-mode capacitor voltage sums increases from 1pu to 1.1pu; thus making the arm with lower voltage unable to synthesize the correct arm voltages. This problem would be exacerbated if the MMC operates at higher modulation indices that approach unity for SPWM and 1.155 with SPWM plus 3rd harmonics. Fig. 6(f) shows even though the modulation index or upper and lower voltages do not hit the limits, the dc components of capacitor voltage sums of the upper and lower arms become unequal, and this may cause dc-offset in the output ac voltages if not mitigated.

# B. Waveform Study of Internal Control Schemes

This section assesses the performance of different internal control methods described above when the MMC is connected to an ac grid as shown in Fig. 7, with its simulation parameters in Table I, and with and without considering SM capacitance tolerances.

Initially, the MMC is controlled to inject 40MW into an ac grid and regulates its average SM capacitor voltage at 2kV (common-mode capacitor voltage sum is 80kV). At 0.6 s, a step change is applied to the active power output references to reverse the power flow from 40MW to -40MW. At 1.2s, a step change is applied to the common-mode capacitor voltage sums to increase the average common-mode capacitor voltage sums (SM average capacitor voltage) by 0.1pu. At 1.8s, a single-line-to-ground (SLG) fault is applied at the point of common coupling of phase A. The reactive power output is controlled to be zero. During the SLG fault, the positive-sequence overcurrent limit is set to 1.1pu and the negative-sequence current is suppressed to zero.

Since the steady-state and dynamics of the output quantities with different inner control schemes are the same, only threephase phase voltages and currents at the PCC, MMC ac current at the low-voltage side of the interfacing transformer, and average active power are given in Fig. 8. Fig. 8(a-1), (b-1) and (c-1), and (a-2), (b-2) and (c-2), and (a-3), (b-3) and (c-3) show the voltages and currents at the PCC and currents at the converter side, zoomed around t=0.6s (instant of active power reversal), t=1.2s (application of step change to reference of common-mode capacitor voltage sums) and t=1.8s (initiation of single-phase ac fault) respectively. These simulation waveforms show the MMC exhibits quick dynamic response during power reversal, presents high quality ac side waveforms to the ac grid, and the magnitude increases of the commonmode capacitor voltage sums do not lead to any noticeable changes in ac current waveforms (which indicates good decoupling of the external dynamics). Also, during the solid single-phase ac fault, the converter ac side currents remain balanced as expected (because of negative sequence current suppression). Fig. 8(d) shows active power the MMC injects into PCC over the entire simulation period. The plots shown in Fig. 8 confirm the simulated MMC operates correctly, and are similar for all methods being compared in this paper.

#### 1) Performance of Control Schemes in the Symmetrical Case

Fig. 9 shows waveforms when only the common-mode capacitor voltage sum (SM average voltage) controller is used with symmetric capacitance. The power reversal at 0.6s triggers a brief damped oscillation period in the arm currents, voltages and energies. When the step change is applied to the reference common-mode capacitor voltage sum (to vary its mean from 80kV to 88kV) at 1.2s, the differential-mode capacitor voltage and energy sums exhibit clear fluctuations. Fig. 9(c) and (d) show that the common-mode capacitor voltage sums follow the reference commands, hence horizontal capacitor voltage balance is maintained. As expected, the common-mode capacitor energy sum increases with the common-mode capacitor voltage sum [see Fig. 9(e) and (f)]. In the pre-fault condition, the dc link current is equally distributed between the three legs, which results in balanced common-mode currents, but during the SLG fault, the dc component of the commonmode currents are not equal as expected [see Fig. 9(b)].

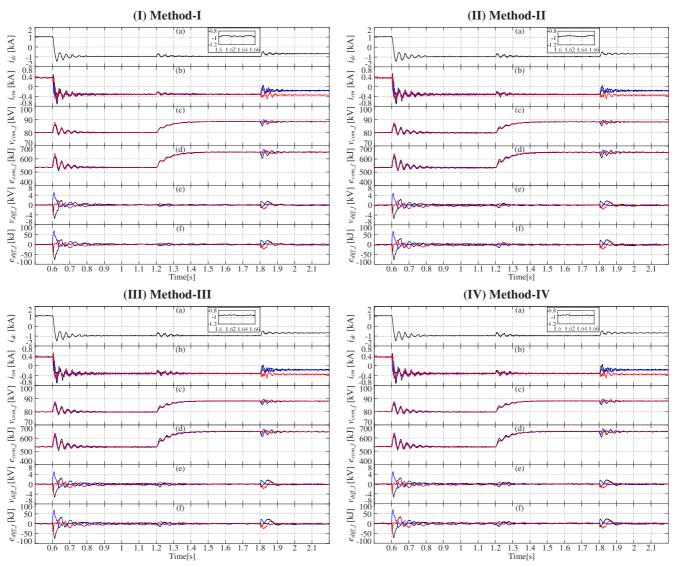

Fig. 12. Waveforms of Method-I to IV in horizontal asymmetry case: (a) dc link current  $i_{dc}$ , (b) common-mode current  $i_{cm}$ , (c) filtered common-mode capacitor voltage sum  $v_{com_sf}$ , (d) filtered common-mode capacitor energy sum  $e_{com_sf}$ , (e) filtered differential-mode capacitor voltage sum  $v_{diff_sf}$ , (f) filtered differential-mode capacitor energy sum  $e_{diff_sf}$ .

The performance of Methods I to IV with zero capacitance tolerance is examined (only the filtered waveforms of the capacitor voltage and energy sums are presented) and system operating conditions remain the same as previously outlined. Parts (a) and (b) in Fig. 10-I to IV show that all the control methods maintain the same quality dc link current and common-mode currents in the symmetrical case. Horizontal leg energy and voltage balance are achieved, with dc link current equally distributed among the three legs. During the SLG fault, the common-mode mean currents become unequal, with the average SM voltage unchanged, thus, the three common-mode capacitor energy sums (leg power integral) are unchanged [see (c)-(f) in Fig. 10-I to IV]. For vertical balance of the symmetric legs, the mean voltage (energy) difference of the arms remains zero [see (e) and (f) in Fig. 10-I to IV]. It is concluded that the analyzed control methods basically show the same performance, with both horizontal and vertical voltage/energy balance with symmetrical capacitance.

# 2) Performance of Control Schemes With Horizontal Capacitance Asymmetry

Each leg B SM capacitance is assumed to be  $0.9C_{SM}$ , while that of legs A and C are  $C_{SM}$ . Fig. 11 shows the waveforms when only a common-mode capacitor voltage sum controller is used. Because the common-mode capacitor voltage sums are horizontally balanced, the average common-mode capacitor energy sum of leg B is lower than those in legs A and C [see Fig. 11(c)-(f)]. In the horizontal asymmetry case, without vertical balancing (differential-mode capacitor voltage/energy sum) control, the dc link current and common-mode currents show no difference from those of the symmetric case [see (a) and (b) in Fig. 9 and Fig. 11].

The effectiveness of control Methods I to IV with horizontal asymmetry can be assessed from the simulation waveforms in

Fig. 13. Waveforms of average voltage controller in vertical asymmetry case: (a) dc link current  $i_{dc}$ , (b) common-mode current  $i_{cm}$ , (c) common-mode capacitor voltage sum  $v_{com,s}$  (d) filtered common-mode capacitor voltage sum  $v_{com,f}$ , (e) common-mode capacitor energy sum  $e_{com}$ , (f) filtered common-mode capacitor energy sum  $e_{com,f}$ , (g) differential-mode capacitor voltage sum  $v_{diff,f}$ , (h) filtered differential-mode capacitor voltage sum  $v_{diff,f}$ , (i) differential-mode capacitor energy sum  $e_{diff,f}$ , (j) filtered differential-mode capacitor energy sum  $e_{diff,f}$ .

Fig. 12 (only the filtered waveforms of the capacitor voltage and energy sums are presented). The system operating conditions remain unchanged. When horizontal voltage balance is accomplished by Methods I and II, the common-mode capacitor energy sum stored in leg B is lower than symmetrical legs A and C because of lower capacitance during steady-state and remain unchanged during dynamic conditions. This indicates the three legs exchange zero energy (active power integral) with the ac grid [see (c) and (d) in Fig. 12-I and II]. Without vertical capacitance asymmetry, dc link current, common-mode current and differential-mode characteristics show no obvious difference from those of the symmetric case [see (a), (b), (e) and (f) in Fig. 12-I and II]. The same performance is seen in Fig. 12-IV for Method-IV that purports to control energy through equal equivalent capacitance and square of voltage sum, as discussed in section III. Fig. 12-III(c) and (d) show that with balanced common and differential mode capacitor energy sums, the capacitor voltage sum of leg B is higher than the other legs with horizontal asymmetrical capacitance (when capacitances of both arms of leg B are deliberately set different from those of legs A and C). There is no noticeable difference in the dc link current, common-mode currents and differential-mode characteristics from those of the symmetry case [see Fig. 12-III(a), (b), (e) and (f)].

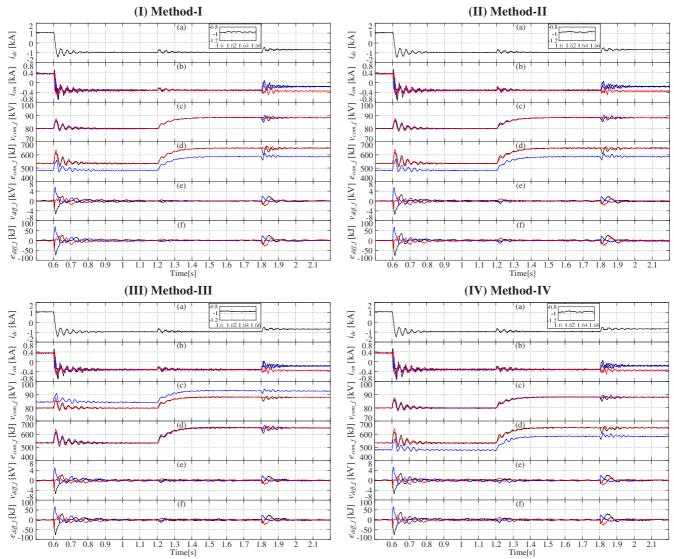

# 3) Performance of Control Schemes With Vertical Capacitance Asymmetry

For the vertical asymmetry case of leg B, each SM capacitance of the upper arm is assumed to be  $0.9C_{SM}$ , while those of the lower arm are  $1.1C_{SM}$ . Fig. 13 shows the waveforms when only common-mode capacitor voltage sum control is used. The mean values of common-mode capacitor voltage and energy sums of the three legs are basically the same [see Fig. 13(c)-(f)]. However, without vertical symmetry, the deviations observed in the differential-mode capacitor voltage and energy sums indicate that neither vertical voltage balance nor vertical energy balance is achieved, especially in leg B [see Fig. 13(g)-(j)]. Also, the dc link and common-mode currents exhibit 50Hz oscillation [see Fig. 13(a) and (b)]. This 50Hz oscillation in the common-mode currents of the legs with symmetrical capacitances (legs A and C) is caused by coupling interaction through the shared dc bus terminal. Fundamental components of the common-mode currents further actuate small dc voltage deviations in the differential-mode capacitor voltage sum of legs A and C. Provided the dc voltage deviation between the upper and lower arms remains small, and the output ac voltages being synthesized do not require the modulation index to reach its maximum limit [see Fig. 13(g) and (h)], the MMC output ac voltage is not affected.

MMC internal dynamic regulation performance results for Methods I to IV during vertical asymmetry are given in Fig. 14. For the voltage-based control schemes in Fig. 14-I and II (c) and (d), horizontal voltage balance is maintained, with the mean values of the common-mode capacitor energy sums controlled to be equal and constant. Also, the vertical voltage balance controllers have reduced the deviation of the mean differentialmode capacitor voltage sum to zero, achieving equalization of the total dc capacitor voltage sum across both arms of each leg under normal and fault conditions [see (e) in Fig. 14-I and II]. However, the capacitor energy sums of each arm remain unequal as predicted [see (f) in Fig. 14-I and II]. With these voltage-based methods that include both horizontal and vertical controllers, the positive and negative sequence fundamental currents which appear as unbalanced ac components in the common-mode currents, are significantly reduced, with the 50Hz negative sequence current that appears as oscillation in the dc link current being suppressed [see (a) and (b) in Fig. 14-I and II]. Also, the results of Method-IV (capacitor voltage sum squared as the control variable instead of the actual energy), indicate that its performance under normal and abnormal conditions is similar to that of the Methods I and II [see Fig. 14-IV]. In contrast, the results of Method-III that exploits the actual energy as control variables, show that the horizontal balancing indicators such as the common-mode capacitor energy and voltage sums remain balanced during vertical asymmetry [see Fig. 14-III(c) and (d)]. The differential-mode capacitor energy sums of all three legs are, however, nullified after an extended oscillation period (which indicates vertical arm energy balance is ensured), under both normal and fault conditions [see Fig. 14-III(f)]. However, ensuring vertical energy balance in Method-

Fig. 14. Waveforms of Methods I to IV in vertical asymmetry case: (a) dc link current  $i_{dc}$ , (b) common-mode current  $i_{cm}$ , (c) filtered common-mode capacitor voltage sum  $v_{com\_f}$ , (d) filtered common-mode capacitor energy sum  $e_{com\_f}$ , (e) filtered differential-mode capacitor voltage sum  $v_{diff\_f}$ , (f) filtered differential-mode capacitor energy sum  $e_{diff\_f}$ .

III increases the deviation of the mean differential-mode capacitor voltage sums from zero, which leads to failure of arm vertical voltage balance in the case of vertical asymmetry [see Fig. 14-III(e)]. This phenomenon increases the magnitudes of unbalanced 50Hz components in the common-mode currents and common-mode capacitor voltage, which reflect into the dc link current [see Fig. 14-III(a)-(d)]. As Method-III fails to ensure arm voltage balance, the mean capacitor voltage sum of leg B lower arm is approximately 38kV and 42kV, respectively, before and after the application of the step change to the common-mode capacitor voltage sum at 1.2s. This indicates that the dc voltage across the lower arm remains below 40kV and 44kV, respectively, before and after 1.2s, but high enough and sufficient to synthesize the required MMC output ac voltage amplitude. Thus, no distortion is observed in the output ac voltage [see Fig. 8(c) and Fig. 14-III(e)].

# 4) Performance of Direct Fundamental Current Ripple Suppression

This paper proposes an alternative method to directly eliminate the fundamental components from the MMC common-mode currents, where significant vertical capacitance asymmetry is expected. Instead of dedicated voltage or energy-based differential-mode controllers, a PR controller tuned at 50Hz is used to suppress the  $\omega$ component in the common-mode currents. This means, a zero-magnitude fundamental component is adopted as the reference for the 50Hz band, rather than the differential-mode capacitor voltage sum controllers  $PI_v^{\Delta}$  in Fig. 3. Its effectiveness has been assessed in this subsection and experimental results in the section VI. Simulation waveforms with zero and  $\pm 10\%$  vertical capacitance tolerances are presented in Fig. 15-I and II respectively. These results show that with the common-mode capacitor voltage sum being controlled, horizontal capacitor voltage balance is

Fig. 15. Waveforms of the direct fundamental oscillation elimination method in symmetry and vertical asymmetry cases: (a) dc link current  $i_{dc}$ , (b) common-mode current  $i_{cm}$ , (c) filtered common-mode capacitor voltage sum  $v_{com\_f}$ , (d) filtered common-mode capacitor energy sum  $e_{com\_f}$ , (e) filtered differential-mode capacitor voltage sum  $v_{diff\_f}$ , (f) filtered differential-mode capacitor energy sum  $e_{diff\_f}$ .

achieved [see (c) in Fig. 15-I and II]. When vertical capacitance tolerance asymmetry is considered, the 50Hz oscillation in the common-mode currents of the three legs and dc link current are suppressed [see Fig. 15-II(a) and (b)]. The 50Hz fundamental oscillation of the common-mode capacitor voltage is cancelled by injecting the appropriate fundamental frequency voltage into the modulating signals in order to produce the needed fundamental current to neutralize the 50Hz component [see Fig. 15-II(c)]. However, the proposed fundamental current elimination is unable to nullify the mean differential capacitor voltage sums with vertical capacitance asymmetry (both arm capacitor voltages remain unbalanced) [see Fig. 15-II(d) and (e)]. This may limit the maximum attainable modulation index as the arms with the lower dc voltages would be unable to synthesize the needed arm voltages at high modulation indices.

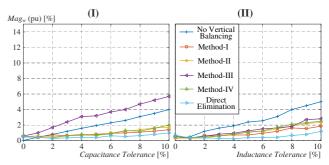

Fig. 16. The relationship between normalized dc link current ripple magnitude and passive component tolerances, with different control methods (Table I).

Fig. 17. The relationship between normalized dc link current ripple magnitude and passive component tolerances, with different control methods (Table II).

(b) Photograph of experimental setup

Fig. 18. Schematic diagram and photograph of the prototype scale-down single-phase MMC with three SMs per arm.

# C. Overall Comparison, in Terms of Fundamental Current Ripple

Iterative simulations of methods for a range of SM capacitance and arm inductance tolerances show the overall relationship between the passive component tolerances and normalized fundamental frequency dc link current ripple

magnitude with different voltage levels, in Fig. 16 and Fig. 17 respectively. The base of ripple magnitude normalization is the mean dc link current.

Based on the parameters in Table I, the overall relationship between vertical capacitance and inductance asymmetry (different capacitance and inductance tolerances between upper and lower arms of the same leg) and normalized magnitude of fundamental frequency dc link current ripple are shown in Fig. 16-I and Fig. 16-II respectively, based on the different control methods being examined in this paper. Under these simulated conditions, the fundamental ripple magnitude is generally below 5% with all control methods, for SM capacitance and arm inductance tolerances ranging from 0 to 10%. With no vertical balancing controller, no fundamental current appears in the dc link when SM capacitance and arm inductance tolerances are zero (ideal or vertical symmetry), but the 50Hz oscillation magnitude in the dc link current increases linearly with MMC passive component tolerance. This study also shows that as capacitance asymmetry increases, control methods I, II, IV and the direct fundamental frequency current elimination method remain capable of suppressing the dc link fundamental current ripple. Method-III, however, leads to the fundamental frequency current ripple magnitudes increasing with the increasing SM capacitance tolerance. The conclusions drawn from the above discussion of Fig. 16 are in accordance with the approximate theoretical analysis articulated mathematically in

To further illustrate the impact of the switching voltage step (voltage per SM) on dc power quality, the same MMC system and control methods with different parameters, as listed in Table II, is investigated.

The plots in Fig. 17 for the 100kV dc link voltage MMC with each SM voltage of 5kV show the same trend as counterparts in Fig. 16 when the dc link voltage is 40kV and SM voltage is 2kV. In addition to the increased fundamental current ripples due to capacitance and inductance tolerances, Fig. 16 and Fig. 17 show further increase of the current ripple with the dc link voltage, meaning that the ripple amplitude is exacerbated by the increased average SM capacitor voltage (or switching voltage), confirming the theoretical discussion in section IV. The traces of two MMCs (40MVA and 100MVA) in Fig. 16 and Fig. 17 are for the same dc current (1kA), arm inductance and converter inertia in per unit.

TABLE II SIMULATION PARAMETERS OF THE 100MVA MMO

| SIMULATION FARAMETERS OF THE TOOM VAIVING |                 |  |  |  |

|-------------------------------------------|-----------------|--|--|--|

| Rated power                               | 100MVA          |  |  |  |

| DC voltage                                | 100kV           |  |  |  |

| AC grid line voltage                      | ltage 66kV      |  |  |  |

| AC grid frequency                         | 50Hz            |  |  |  |

| Transformer leakage inductance            | 0.18pu          |  |  |  |

| Transformer ratio                         | 50/66kV         |  |  |  |

| Arm inductance                            | 15.3mH(0.2pu)   |  |  |  |

| Numbers of SMs per arm                    | 20              |  |  |  |

| SM capacitance                            | 2.7mF(40kJ/MVA) |  |  |  |

| Modulation carrier frequency              | 1.0kHz          |  |  |  |

In summary, the vertical passive component tolerances tend to cause drift of the differential-mode capacitor voltage sum from zero and fundamental frequency dc link current ripple for an MMC system, as pointed out in the mathematical expressions (23), (27) and (28). The arm-level SM capacitor voltage sum imbalance and fundamental frequency dc current ripple due to vertical parameter asymmetry displayed in the simulations waveforms confirm the main hypothesis and discussion in section IV. Voltage-based vertical balancing controllers (Methods I, II and IV), based on expressions (17) and (18), can eliminate the differential-mode capacitor voltage sum, and suppress the fundamental frequency oscillation in the common-mode loop to some extent. The proposed control method that directly suppresses fundamental components of the common-mode current in (27) and (28) regardless of arm voltage balance, shows superior performance in terms of dc link fundamental current ripple suppression.

### VI. EXPERIMENTAL RESULTS

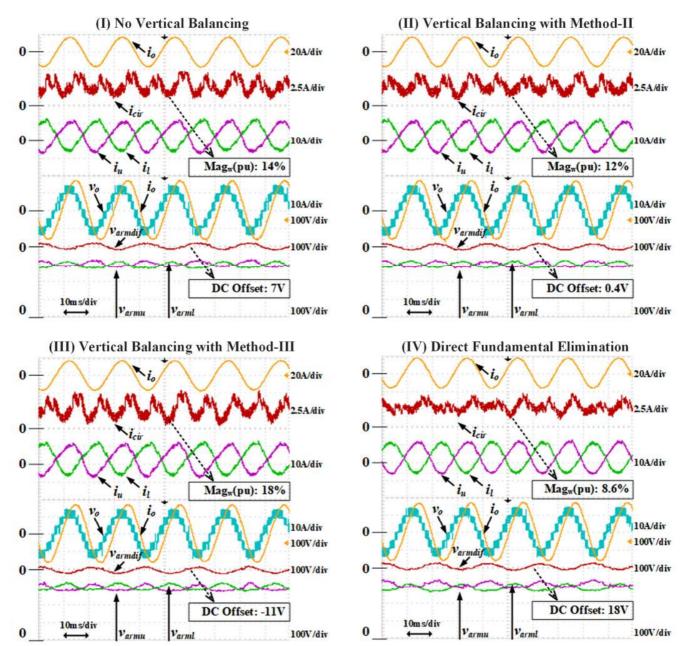

This section uses a prototype single-phase MMC shown in Fig. 18, with parameters in Table III and IV, to validate the previously presented analysis and simulations, particularly, with regard to the relationship between passive parameter mismatch, differential-mode capacitor voltage sum, and induced fundamental circulating current. As part of validation process, a number of experimental scenarios are presented, namely, no vertical balancing, and scenarios with Method-II (voltage-based vertical balancing), Method-III (energy-based vertical balancing) and the proposed direct fundamental circulating current elimination method. Table IV shows SM capacitances and inductances of the experimental test rig, with vertical symmetrical and asymmetrical capacitances. Besides capacitor voltage balancing, the horizontal voltage balancing controller that regulates the mean common-mode capacitor voltage sum of the phase-leg at rated dc link voltage (300V), is implemented in all scenarios. The sorting-based inner arm SM voltage balancing method with PD-PWM modulation is adopted.

TABLE III

PARAMETERS OF THE SINGLE-PHASE MMC PROTOTYPE

| I ARAMETERS OF THE SINGLE-I HASE MINIC I ROTOTTE |           |  |  |

|--------------------------------------------------|-----------|--|--|

| Rated power                                      | 1kW       |  |  |

| DC voltage $V_{dc}$                              | 300V      |  |  |

| Load resistance $R_{load}$                       | $5\Omega$ |  |  |

| Load inductance $L_{load}$                       | 12.5mH    |  |  |

| Nominal arm inductance $L_{arm}$                 | 5mH       |  |  |

| Numbers of SMs per arm                           | 3         |  |  |

| Nominal SM capacitance $C_{SM}$                  | 1.8mF     |  |  |

| Modulation index                                 | 0.8       |  |  |

| Modulation carrier frequency                     | 2.0kHz    |  |  |

TABLE IV

VALUES OF THE PASSIVE COMPONENTS

(FOR BOTH SYMMETRY AND ASYMMETRY CASES)

|          | Symmetry | Asymmetry |  |  |

|----------|----------|-----------|--|--|

| $C_{ul}$ | 1.84mF   |           |  |  |

| $C_{u2}$ | 1.80mF   |           |  |  |

| $C_{u3}$ | 1.78mF   |           |  |  |

| $C_{ll}$ | 1.82mF   |           |  |  |

| $C_{l2}$ | 1.74mF   | 1.62mF    |  |  |

| $C_{l3}$ | 1.79mF   | 1.66mF    |  |  |

| $L_u$    | 5.5mH    |           |  |  |

| $L_l$    | 5.7mH    |           |  |  |

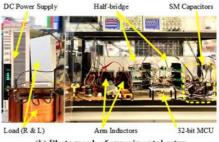

Fig. 19. Waveforms of no vertical balancing, Method-II, Method-III and the direct elimination method in vertical symmetry case.

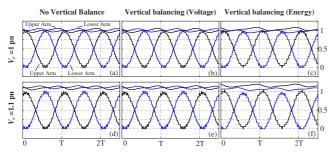

Fig. 19 shows experimental waveforms with no vertical balancing, voltage-based vertical balancing, energy-based vertical balancing, and the proposed direct fundamental circulating elimination method, when the SM capacitors are near match in order to reflect the ideal case of vertical symmetry. The fundamental circulating current magnitude of the method without vertical balancing is smallest in symmetrical case because no active injected current is present, as shown Fig. 16 and Fig. 17. The magnitude of fundamental circulating currents that exist in the common-mode current are practically the same for the cases with voltage-based vertical balancing and energy-based vertical balancing, see Fig. 19-II and III. While the proposed direct elimination of fundamental

current exhibits a reduction compared with that of the voltage/energy balancing methods, which can be seen in Fig. 19-IV, but with the penalty of creating substantial arm voltage imbalance, with the error in the dc offset of the differential mode capacitor voltage sum  $V_{armdij}$  amount to 9V (equivalent to SM capacitor voltage deviations of  $\pm 1.5\%$  from their respective nominal values). With small SM capacitance value errors plus randomness of the unquantified errors introduced by semiconductor voltage drops, switching characteristics and other nonlinearities, the cases with no vertical balancing and energy-based vertical control show modest drifts or errors between the capacitor voltage sums across the upper and lower arms (see Fig. 19-I and III), while the voltage-based vertical balancing in Fig. 19-II shows the smallest dc voltage error

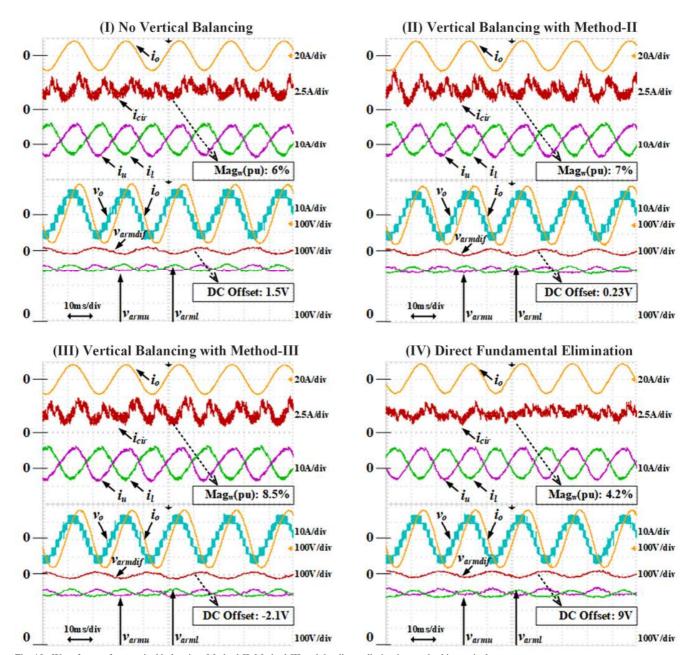

Fig. 20. Waveforms of no vertical balancing, Method-II, Method-III and the direct elimination method in vertical asymmetry case.