# Analysis and Design of a 195.6 dBc/Hz Peak FoM P-N Class-B Oscillator With Transformer-Based Tail Filtering

Marco Garampazzi, *Student Member, IEEE*, Paulo M. Mendes, *Senior Member, IEEE*, Nicola Codega, *Member, IEEE*, Danilo Manstretta, *Member, IEEE*, and Rinaldo Castello, *Fellow, IEEE*

Abstract—A complementary p-n class-B oscillator with two magnetically coupled second harmonic tail resonators is presented and compared to an N-only reference one. An in depth analysis of phase noise, based on direct derivation of the Impulse Sensitivity Function (ISF), provides design insights on the optimization of the tail resonators. In principle the complementary p-n oscillator has the same optimum Figure of Merit (FoM) of the N-only at half the voltage swing. At a supply voltage of 1.5 V, the maximum allowed oscillation amplitude of the N-only is constrained, by reliability considerations, to be smaller than the value that corresponds to the optimum FoM even when 1.8 V thick oxide transistors are used. For an oscillation amplitude that ensures reliable operation and the same tank, the p-n oscillator achieves a FoM 2 to 3 dB better than the N, only depending on the safety margin taken in the design. After frequency division by 2, the p-n oscillator has a measured phase noise that ranges from -150.8 to -151.5 dBc/Hz at 10 MHz offset from the carrier when the frequency of oscillation is varied from 7.35 to 8.4 GHz. With a power consumption of 6.3 mW, a peak FoM of 195.6 dBc/Hz is achieved.

Index Terms—Class-B, class-C, class-F, distributed oscillator, figure of merit (FoM), oscillator, phase noise, voltage-controlled oscillator (VCO).

# I. INTRODUCTION

N LC oscillators reducing the power consumption while preserving low phase noise is a key goal especially for mobile applications. This can be achieved acting on the oscillator topology and/or on the tank quality factor (Q). Oscillator topology affects the power vs phase noise trade-off in two equally important ways. First, acting on the conversion of circuit noise into phase noise through the impulse sensitivity function (ISF) [1]; second, changing the maximum achievable power conversion efficiency  $(\eta_P)$ , i.e., the conversion of DC power  $(P_{DC})$  into resonator RF power  $(P_{RF})$ , which directly affects phase noise [2]. The use of voltage-biased topologies

Manuscript received November 21, 2014; revised February 08, 2015; accepted March 05, 2015. Date of publication April 06, 2015; date of current version June 23, 2015. This paper was approved by Guest Editor Kenichi Okada. This work was supported by the European Marie Curie IAPP Grant Agreement N 251399.

- M. Garampazzi and N. Codega are with Marvell Italy s.r.l., 27100 Pavia, Italy.

- P. M. Mendes is with the DEI–Campus de Azurém, Universidade do Minho, 4800-058 Guimarães, Portugal.

- D. Manstretta and R. Castello are with the Università degli Studi di Pavia, 27100 Pavia, Italy.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2015.2413851

[3]–[5] eliminates a source of phase noise (i.e., the current generator) and improves power efficiency, but increases the sensitivity to supply voltage variations. Large voltage swings (relative to the supply voltage) are desirable to achieve high voltage efficiency, thus high power efficiency, and to reduce phase sensitivity to device noise, but they can drive the active devices into the triode region, thereby loading the tank, potentially degrading phase noise. Class-C oscillators [6], [7] use sharp current pulses to improve current efficiency, but voltage efficiency is limited to avoid loading the tank. Adopting a low supply voltage (e.g., 0.475 V in [3]), the active devices do not enter into triode even as the signal swing approaches (or exceeds) the supply rails, but performances become very sensitive to supply voltage variations [8] and, to preserve power efficiency, a dedicated switch-mode voltage regulator may be needed, thus increasing cost. In class-F oscillators [9] a non-sinusoidal waveform is created using higher order resonators, increasing the signal slope and reducing the ISF. However, as shown in [2] this requires multiple high-Q inductors. Alternatively, the multiple resonances of a transformer can be exploited, reducing area occupation. If a step-up transformer is used to magnetically couple gate and drain, the gate voltage swing can be enhanced [9], further reducing the ISF. The clip-and-restore [5] oscillator deliberately pushes the active devices into deep triode in order to create a non-sinusoidal waveform at the drain that alters the ISF. When the active devices are ON their drain voltage is nearly flat, desensitizing the oscillation phase to circuit noise. Tank loading is countered using two step-up transformers in series to boost the gate voltage swing and reduce the ISF. Class-D oscillators operate the LC tank in a peculiar time-variant regime, resulting in high  $\eta_P$  and low phase noise. However, the peak voltage swings of about three times the supply voltage forces the choice of a low supply voltage (0.4 V in [4], [10]) and results in frequency pushing. Among the proposed solutions [3], [4], [7], [9]–[27], the one that has achieved the best efficiency, as measured by the Excess Noise Factor (ENF) [2], is the Class-B oscillator with an additional LC tank (resonating at  $2\omega_0$ ) inserted at the source of the active devices [26]. The switching transistors can enter the triode region without loading the tank since, intuitively they see a high impedance in series with them, effectively altering the active devices ISF in a way similar to the class- $F_2$  oscillator in [28], achieving high  $\eta_P$  and low phase noise. Ideally 100%  $\eta_P$  can be achieved, but with voltage swings approaching  $\pi$  times the supply voltage. Adopting a

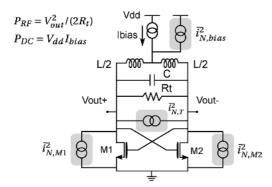

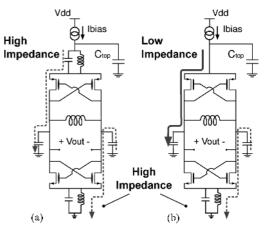

Fig. 1. Class-B oscillators with main noise sources: LC-tank losses, switching transistors and bias circuitry.

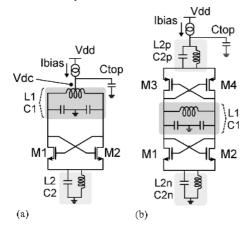

Fig. 2. Class B with tail filter: (a) N-only; (b) p-n. Numerical examples assume  $L_1=600$  pH,  $Q_1=20$  and  $L_2=400$  pH,  $Q_2=20$  at 2 GHz.

complementary (push-pull) topology, the peak efficiency is reached at lower (theoretically half) voltage swing compared with an N-type-only one, avoiding reliability concerns. For this reason we present a high efficiency complementary Class-B oscillator with dual LC tail filter, which can use efficiently the supply current and achieve a low phase noise. In Section II we briefly recall the definition of ENF and its expression for an important class of LC-oscillators. Section III analyzes the phase noise in class-B oscillators (both N-only and p-n) with tail filter and derives an accurate closed-form expression for phase noise and ENF, providing useful design insights. Section IV gives more details on the practical design aspects of the proposed p-n oscillator with transformer-based tail filtering and reports on the experimental results. Section V draws the conclusions.

# II. EXCESS NOISE FACTOR IN LC-TANK OSCILLATORS

To benchmark the performance of an oscillator we rely on the widely used Figure of Merit [29] (FoM) that normalizes phase noise to frequency of oscillation ( $\omega_0$ ), offset frequency from the carrier ( $\Delta\omega$ ) and power consumption ( $P_{DC}$ ). The phase noise of a classic LC-tank oscillator (Fig. 1) can be estimated, using the theory of Hajimiri and Lee [1], computing the ISF for the main noise sources. Considering only the noise coming from the tank losses, assuming a sinusoidal waveform and that the energy restoring element does not load the tank (such that the ISF of the tank has a mean square value of 1/2), when the power conversion efficiency  $\eta_P$  (=  $P_{RF}/P_{DC}$ ) is 100% the oscillator

FoM reaches a thermodynamic limit ( $FoM_{max}$ ) that depends only on the Q of the tank:

$$FoM_{MAX} = -10 \log \left( \frac{k_B T}{2 \cdot 10^{-3} Q^2} \right)$$

$$= 173.8 \frac{dBc}{Hz} + 10 \log(2Q^2). \tag{1}$$

The ENF, defined [2] as the difference between  $FoM_{MAX}$  and the actual FoM, provides a figure of merit of the topology, independent from the tank Q. For a VCO where the negative resistance transistors have a gate-to-source voltage equal to the tank single-ended voltage, Mazzanti and Andreani [6], [30], [31] have shown that, if the active devices do not load the tank, the transistors contribution to phase noise is  $\gamma_{MOS}$  times the tank noise. Using this result ENF is given by:

$$ENF = 10\log\left(\frac{1 + \gamma_{MOS}}{\eta_P}\right). \tag{2}$$

This shows that in a classic LC-tank oscillator which drives the tank with high impedance phase noise is minimized by maximizing power efficiency. The use of an additional LC tank at the source of the active devices of a class-B oscillator (Fig. 2(a)) was originally proposed to reduce the current source noise [26] thanks to the filtering action of the large capacitance  $(C_{top})$  in parallel with it. This topology has, however, two other important advantages. First, the common source node can swing below ground, increasing the maximum achievable voltage swing. Since current efficiency remains nearly constant,  $\eta_P$  is also increased, ultimately reaching a value close to 90%. Second, the switching transistors can enter the triode region without loading the tank since they see a high impedance in series with them. Hence, as suggested by (2) the peak efficiency corresponds also to the peak FoM because, thanks to the tail resonator, noise remains constant even when the switching transistors are pushed deeply into linear region. Table I compares the measured performance of various VCOs with different topologies, including their ENF1 (computed using the data available in the referenced papers). The comparison shows that the class-B oscillator with tail filter in [26] is superior by more than 1 dB compared to any reported VCO (assuming accurate Q estimation). The main problem of this topology is the fact that for the optimum FoM the peak voltage across the transistors is more than twice the supply voltage. For the oscillator in [26], implemented in a 0.35  $\mu$ m CMOS technology and biased from 2.5 V, the peak FoM of 195.4 dBc/Hz is reached with a  $\eta_P$  of 81% for a peak swing of 6.4 V (computed from the values of tank Q, inductor and current provided in the paper). Large voltages can seriously damage the transistors and reduce significantly their lifetime [32], [33]. This issue can be solved if a low supply voltage is chosen (e.g., 0.4 V in [4]). However, when the oscillator is embedded in a complex system its supply voltage must be derived from an available switched-mode power supply (SMPS), possibly shared by other analog rather than digital blocks to avoid unacceptable spur levels and keep costs low. The difference between the SMPS

<sup>1</sup>Even though for class-D and class-F the hypotheses used to derive (2) are often violated, (1) still provides a useful practical reference to compare different topologies.

| Ref          | Topology                                 | Tech           | Area [mm²] | V <sub>dd</sub> | $V_{out} \ [V]$  | f <sub>osc</sub><br>[GHz] | Tuning<br>Range<br>% | Phase<br>Noise<br>[dBc/Hz]           | FoM [dB]    | $FoM_T \ [	ext{dB}]$ | Q  | ENF<br>[dB] |

|--------------|------------------------------------------|----------------|------------|-----------------|------------------|---------------------------|----------------------|--------------------------------------|-------------|----------------------|----|-------------|

| [7]          | Class-C<br>p-n                           | 0.18um<br>CMOS | 0.075      | 1.8             | 0.9              | 6.1/7.5                   | 18%                  | -120/-123<br>@2 <i>MHz</i>           | 189-191     | 196                  | 10 | 5.8         |

| [6]          | Class-C<br>N-only                        | 0.13um<br>CMOS | -          | 1               | 1.24             | 4.5/5                     | 10.5%                | -132.8<br>@3 <i>MHz</i>              | 193.5-196   | 196.4                | 17 | 5.4         |

| [26]         | Class-B<br>N-only                        | 0.35um<br>CMOS | -          | 2.5             | 6.4 1            | 1.2                       | -                    | -153<br>@3 <i>MHz</i>                | 195.4       | -                    | 14 | 4.3         |

| [4]          | Class-D                                  | 65nm<br>CMOS   | 0.12       | 0.4             | 1.28             | 2.5/3.3                   | 46%                  | -144<br>@5 <i>MHz</i>                | 189-190     | 199                  | 10 | 6.8         |

| [3]          | Colpitts                                 | 0.13um<br>CMOS | 0.28       | 0.48            | 1.5              | 4.9                       | 2.4%                 | -136.3<br>@3 <i>MHz</i>              | 196.2       | 184.2                | 18 | 5.8         |

| [53]         | Clip and restore                         | 65nm<br>CMOS   | 0.19       | 1.5             | 3.5              | 3.64/4                    | 10.2%                | -135<br>@1 <i>MHz</i>                | 190.1       | 190.3                | 11 | 7.6         |

| [9]          | Class-F                                  | 65nm<br>CMOS   | 0.12       | 1.2             | 2                | 5.9/7.6                   | 25%                  | -142.2<br>@3 <i>MHz</i>              | 192.2       | 200.2                | 16 | 8.7         |

| [28]         | Class-<br>F <sub>2</sub>                 | 65nm<br>CMOS   | 0.2        | 1.3             | 4.5              | 7.2/8.8                   | 19%                  | -144.8 <sup>2</sup><br>@3 <i>MHz</i> | 191.8       | 197.4                | 14 | 7.92        |

| This<br>Work | Class-B<br>N-only                        | 55nm<br>CMOS   | 0.17       | 1.5             | 2.1 1            | 7.4/8.4                   | 13%                  | $^{-152.8^2}_{@10MHz}$               | 190.5-192.3 | 194.5                | 15 | 8           |

| This<br>Work | Class-B<br>p-n                           | 55nm<br>CMOS   | 0.19       | 1.5             | 1.6 <sup>1</sup> | 7.4/8.4                   | 13%                  | -151.5 <sup>2</sup><br>@10MHz        | 194.3-195.6 | 197.8                | 15 | 4.7         |

| 1 Estin      | <sup>1</sup> Estimated from calculations |                |            |                 |                  |                           |                      |                                      |             |                      |    |             |

TABLE I COMPARISON TABLE.

<sup>&</sup>lt;sup>2</sup> After division by 2

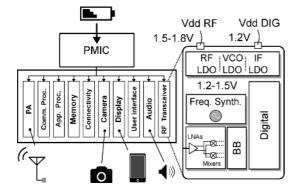

Fig. 3. Conceptual block diagram of a complete mobile system.

level and the oscillator supply voltage will be absorbed by a low-voltage drop supply (LVDS) regulator. For a fixed SMPS voltage level, a low oscillator supply voltage leads inevitably to a low LVDS efficiency and therefore to a degradation of the overall power efficiency. In today's platforms these voltages are often larger than 1.2 V, with typical values in the range of 1.5 V to 1.8 V (Fig. 3) [34]–[42]. This makes attractive the use of a complementary p-n topology, shown in Fig. 2(b), which has twice the current efficiency of the N-only one and achieves the same peak power efficiency (or equivalently reaches the same peak FoM), but with half the voltage swing. In [17] a p-n version of the oscillator of [26] was presented which achieved a FoM of 183.8 dBc/Hz and a ENF of 11 dB. However, the focus of that work was to reduce the tail current 1/f noise, not to reduce ENF. This solution will be studied in depth and compared with the N-only topology in the next section.

# III. ANALYSIS OF CLASS-B OSCILLATORS WITH TAIL FILTER

The Class-B oscillator with tail filter can achieve low ENF thanks to the possibility to obtain very good efficiency without increasing the noise. In fact a big capacitor filters out the noise of the current generator (that allows to minimize the voltage headroom dedicated to it), while the tail LC filter provides a high source impedance, allowing to push the oscillator towards a high power efficiency without incurring into phase noise degradation. In the following analysis the goal is to demonstrate this intuitive argument and, obtaining a closed form expression for the phase noise, to give some insights on the design of this type of oscillators. The details of the derivation will be reported in Appendix A. At first the N-only topology will be studied and then the analysis will be extended to the p-n topology.

# A. N-Only Class-B Oscillator With Tail Filter

The analysis will refer to the top-biased oscillator in Fig. 2(a), but the same considerations can be done for a bottom biased oscillator. The main LC tank resonates at the fundamental frequency  $(f_0)$  and the tail tank resonates at  $2f_0$ . The ISFs are calculated starting from the state vector  $\vec{X}$  [1], [43], [44]:

$$\vec{X} = \begin{bmatrix} V_{C_1} & \sqrt{\frac{L_1}{C_1}} I_{L_1} & \sqrt{\frac{C_2}{C_1}} V_{C_2} & \sqrt{\frac{L_2}{C_1}} I_{L_2} \end{bmatrix}$$

(3)

where the four state variables correspond to voltages on the capacitors and the currents flowing through the inductors, scaled in such a way that the squared sum of the state variables is proportional to the stored energy, as done in [2], [45], where this approach was found to be accurate. In steady state  $V_{C1} = A_1 \sin(\omega_0 t)$  and  $V_{C2} = A_2 \cos(2\omega_0 t)$ , where  $C_1$  and  $C_2$  are the total capacitance at the main LC tank and tail tank respectively.

Estimated from calculations

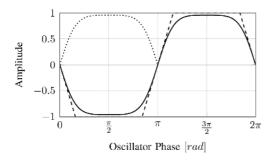

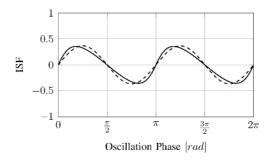

Fig. 4. Soft switching behavior (oscillator of Fig. 2(a)): idealized (dashed), smoothing function  $f(\varphi)$  (continuous), and its modulus  $g(\varphi)$  (dotted).

1) Main Tank Losses: If a noise charge is injected across the main tank it will appear across capacitor  $C_1$ , creating a perturbation in the first state variable  $\Delta X_1 = \Delta q/C_1$ . As a result the ISF associated with the main tank losses can be directly calculated as shown in Appendix A as:

$$\Gamma_1 = \frac{\cos(\omega_0 t)}{\left(1 + 4\frac{C_2}{C_1} \frac{A_2^2}{A_1^2}\right)} \tag{4}$$

where the constant  $q_{\text{max}}$  is set equal to  $A_1C_1$ .

2) Tail Tank Losses: If a noise charge  $\Delta q$  is injected across the tail tank, it will affect the oscillator nodes in a time-dependent manner, due to the transistors switching action. During the oscillation period it is possible to distinguish two cases: first, the plateau, when one transistor is ON and the other one is OFF; second, during transitions, when both transistors are ON. When one transistor is ON the charge injected at the source will be instantaneously divided between capacitors  $2C_1$  and  $C_2$ <sup>2</sup>, affecting both tank voltages ( $\Delta V_1 = \pm \Delta V_2$ , where  $V_1$  and  $V_2$ are the voltages across the main tank and tail tank respectively, depending on whether  $M_1$  or  $M_2$  is ON). During transitions instead the capacitance sees only  $C_2$  and there is no effect on  $V_1$ . To account for this "soft switching" behavior, idealized by the dashed line in Fig. 4, a smoothing function  $f(\omega_0 t)$  (thick line in Fig. 4) and its modulus  $g(\omega_0 t) = |f(\omega_0 t)|$  (dotted line in Fig. 4) are introduced.  $f(\varphi)$  is defined as the difference between the active devices  $\mathcal{V}_{ds}$  normalized to their sum and it can be expressed as a function of the steady-state oscillation state as:

$$f(\varphi) = \frac{A_1 \sin(\varphi)}{2(A_2 \cos(2\varphi) - V_{dc})}$$

(5)

where  $V_{dc}$  is the effective supply voltage, as shown in Fig. 2(a). Using the above definition, the effect of  $\Delta q$  on the tank voltages  $V_1$  and  $V_2$  can be approximated as follows:

$$\Delta V_1 = -\frac{f(\varphi)\Delta q}{2C_1 + C_2} \quad \Delta V_2 = -\frac{g(\varphi)\Delta q}{2C_1 + C_2} - \frac{\Delta q}{C_2} (1 - g(\varphi)). \tag{6}$$

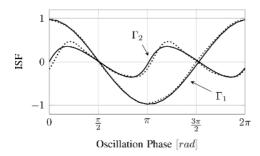

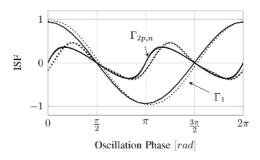

Following the same steps as for the ISF of the main tank, reported in Appendix A, the ISF of the tail tank ( $\Gamma_2$ ) can be calculated. The plot of the corresponding waveform is reported in

<sup>2</sup>Here we assume that during the plateau the ON transistor operates close to an ideal switch. This assumption proves more accurate at higher amplitudes of operation, which is the optimum operation region of the oscillator.

Fig. 5. Impulse Sensitivity Function of the second harmonic tank (oscillator of Fig. 2(a)): considering the more complete analysis (continuous) and approximated with just second harmonic (dashed).

Fig. 5 (thick line). Approximating  $\Gamma_2$  with its dominant harmonic component at  $2f_0$ , a sufficiently accurate closed form expression is found  $(\Gamma_{2,2f_0})$ , shown as dashed line in Fig. 5.

$$\Gamma_{2,2f_0} \cong \frac{1}{\left(1 + 4\frac{C_2}{C_1}\frac{A_2^2}{A_1^2}\right)} \left(2\sqrt{2}\frac{A_2}{A_1}\sin(2\varphi)\right).$$

(7)

3) Active Devices: To derive the ISF of the active devices we study the effect of a noise charge  $\Delta q$  injected between the tail node and one output node. A charge injected at one output node is equivalent to the superposition of one differential plus one common mode charge injection both of  $\Delta q/2$ . Differential and tail charge injection have already been discussed. A common mode charge injected at the main tank, through the switching action of the transistors, appears periodically also across the tail capacitor and its effect can be approximated as:

$$\Delta V_1 = -\frac{\Delta q}{2C_1} + f(\varphi) \left( \frac{\Delta q}{2(2C_1 + C_2)} + \frac{\Delta q}{4C_1} \right)$$

$$\Delta V_2 = \frac{\Delta q \cdot g(\varphi)}{2(2C_1 + C_2)} + (1 - g(\varphi)) \frac{\Delta q}{C_2}.$$

(8)

Adding up all the contributions the transistors ISF  $\Gamma_M$  is found as:

$$\Gamma_{M} = \frac{1}{A_{1} \left( 1 + 4 \frac{C_{2}}{C_{1}} \frac{A_{2}^{2}}{A_{1}^{2}} \right)} \left( -\frac{A_{1}}{2} \cos(\varphi) - 2A_{2} \sin(2\varphi) + \frac{(4C_{1} + C_{2}) \cos(\varphi) (A_{1} f(\varphi) + 8A_{2} g(\varphi) \sin(\varphi))}{4(2C_{1} + C_{2})} \right). \tag{9}$$

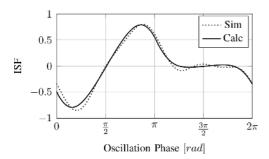

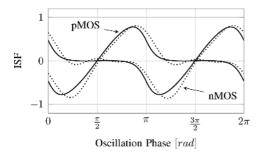

The above expressions were validated against numerical simulations for different values of device parameter using the method suggested by Pepe *et al.* [46], based on periodic transfer function simulations. The results for a representative case are plotted in Figs. 6–7.

4) Total Phase Noise: Starting from the ISFs expression in (4), (7) and (9) the corresponding phase noise contributions have been calculated, as shown in Appendix A. The results are compared with simulation results in Fig. 8. It can be seen that our analysis accurately models not only the overall phase noise, with less than 0.5 dB error, but also its main individual contributions, with an error always less than 1 dB. Using further simplified ISF expressions, i.e., considering only the harmonic components at

Fig. 6. Main tank and tail tank ISFs simulated (dotted) and evaluated (continuous) of Fig. 2(a).

Fig. 7. Active devices ISF simulated (dotted) and evaluated (continuous) of Fig. 2(a).

Fig. 8. Output noise not normalized to the carrier of the different sources: simulated (markers) and calculated (lines) of oscillator of Fig. 2(a).

$f_0$  and  $2f_0$ , the following closed form expression for the oscillator phase noise is found:

$$L_{tot}(\Delta\omega) = 10 \log \left( \frac{k_B T}{2P_{sig}} \left( \frac{\omega_0}{\Delta\omega Q_1} \right)^2 \frac{(1+\gamma) \left( 1 + 16 \frac{A_2^2}{A_1^2} \frac{C_2}{C_1} \frac{Q_1}{Q_2} \right)}{\left( 1 + 4 \frac{C_2}{C_1} \frac{A_2^2}{A_1^2} \right)^2} \right)$$

(10)

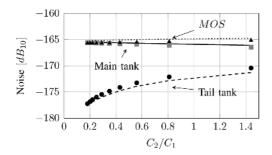

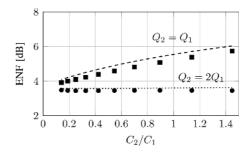

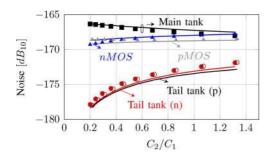

Based on (10) the ENF has been calculated for different values of the tank capacitors and quality factors and compared with simulations in Fig. 9. A few considerations can be made. As (10) suggests, as a general rule the quality factor of the second harmonic tank should be maximized. In this way three effects are achieved. First, the absolute noise is reduced. Second, the impedance seen by the main tank during the switching transitions is increased, reducing loading effects. This translates into a reduction of the factor that multiplies  $1+\gamma$  in (10). Third, power efficiency is increased. Another design choice is the size of the

Fig. 9. ENF for different values of tank capacitors and quality factors simulated (markers) and calculated (lines).

Fig. 10. Complementary p-n class-B oscillator with (a) dual and (b) single  $2\omega_0$  LC tanks at the tails.

tail capacitance  $C_2$ . Notice that  $C_2$  appears squared at the denominator and instead it is linear at the numerator in (10). However,  $C_2$  is always multiplied by the square of  $A_2$  and, if  $C_2$  is increased,  $A_2$  decreases, leading to a higher phase noise. The ENF shows an optimum for a relatively small values of  $C_2$  which depends on the quality factors ratio  $Q_2/Q_1$ . If  $Q_2$  is larger than  $Q_1$  then the value of  $C_2$  has a reduced effect. Assuming a very high  $Q_2$ , the numerator in (10) approaches  $1+\gamma$  and eventually surpassing the behavior of a "close to ideal" oscillator as given by (2). It is worth mentioning that a good approximation of the switching behavior is mandatory to obtain an accurate result (a key difference compared to the class-F analysis in [2]).

# B. P-N Class-B Oscillator With Tail Filter

Let us now consider the p-n Class B oscillator shown in Fig. 2(b), where two second harmonic tail resonators are used, one at the NMOS source and the other at the PMOS source. Notice that, a simpler solution would be the one shown in Fig. 10(b), where the source of the PMOS transistors is connected directly to the current source and to the large capacitor  $C_{top}$ . It was shown by Andreani [47] that assuming a perfectly differential tank capacitance and a high impedance on one side, a complementary class-B oscillator has the same phase noise behavior of an N-only oscillator. However, since the tank cannot be made perfectly-differential, the PMOS transistors noise would see a low impedance path to ground, thereby loading the tank and increasing phase noise at large amplitudes [48]. The impulse sensitivity function theory can be applied

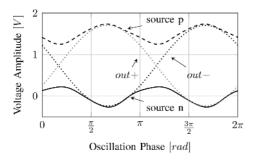

Fig. 11. Simulated voltage waveforms of the oscillator in Fig. 10(a).

to resonators which consist of more energy storing elements (e.g., a transformer). According to the ISF theory when a noise impulse charge is applied, only the voltage across the capacitor changes and no effect is present on the current flowing through the inductor [1]. This will be confirmed by simulation results at the end of this section. To compute the ISF for each noise source the starting point is the definition of the state vector, that in this case is of sixth order since three tanks are present. See equation (11) at the bottom of the page. Now referring to Fig. 11 the steady state is approximated  $V_{C1} = A_1 \sin(\omega_0 t)$ ,  $V_{C_{2n}} = A_{2n} \cos(2\omega_0 t)$  and  $V_{C_{2p}} = -A_{2p} \cos(2\omega_0 t)$ .

1) Noise Sources and ISF: Following the same steps outlined above for the N-only oscillator, the ISF for the main tank can be calculated as

$$\Gamma_1 = \frac{\cos(\omega_0 t)}{\left(1 + 4\frac{C_{2n}}{C_1}\frac{A_{2n}^2}{A_2^2} + 4\frac{C_{2p}}{C_1}\frac{A_{2p}^2}{A_2^2}\right)}.$$

(12)

It is clear that (12) is equal to (4) if  $A_{2n}=A_{2p}=A_2$  and  $C_{2n}=C_{2p}=C_2/2$  and everything else is the same. To model the effect of cross-coupled pairs switching on the tail tanks, the functions  $f_n(\varphi)$  and  $f_p(\varphi)$  are defined, similarly to the  $f(\varphi)$  function for the N-only oscillator:

$$f_{n,p}(\varphi) = \frac{A_1 \sin(\varphi)}{2(A_{2n,p}\cos(2\varphi) - V_{dc})}$$

(13)

where  $V_{dc}$  is the common mode output voltage. Using the above definitions, the effect of  $\Delta q$  on the tank voltages  $V_1$  and  $V_{2n}/V_{2p}$  can be written similarly to (5) with  $f(\varphi)$  replaced by  $f_n(\varphi)/f_p(\varphi)$ . The underlying assumption is that a charge injected at the NMOS tail has no effect on the PMOS tail capacitance and vice versa. Following the same steps as for the N-only oscillator, the ISF of the tail tanks  $\Gamma_{2n}$  and  $\Gamma_{2p}$  can be calculated. A simple analytical expression can be found extracting only the dominant harmonic component at  $2f_0$ :

$$\Gamma_{2,n/p} \approx \frac{1}{\left(1 + 4\frac{C_{2n}}{C_1} \frac{A_{2n}^2}{A_1^2} + 4\frac{C_{2p}}{C_1} \frac{A_{2p}^2}{A_1^2}\right)} \left(2\sqrt{2} \frac{A_{2,n/p}}{A_1} \sin(2\varphi)\right). \tag{14}$$

Fig. 12. Main tank ( $\Gamma_1$ ) and tail tanks ( $\Gamma_2$ ) ISFs simulated (dotted) and evaluated (continuous) of oscillator of Fig. 2(b).

As for the main tank ISF, (14) is equal to (7) if  $A_{2n} = A_{2p} = A_2$  and  $C_{2n} = C_{2p} = C_2/2$  and everything else is the same. To evaluate the ISF of the transistors, we start considering the effect of a charge injected between the drain and source of the NMOS transistor M2 in Fig. 2(b). The injected charge  $\Delta q$  can be decomposed into a charge injected at the source plus an opposite charge injected at the drain that can be split into equal commonmode and differential components. The effect of the differential charge injected at the drain is only on the main tank capacitors:  $\Delta V_1 = \Delta q/2C_1$ . The combined effect of injecting  $\Delta q$  at the source and  $\Delta q/2$  at the two drains is highly time-varying. When M2 and M3 are ON, we have:

$$\Delta V_1 = -\frac{\Delta q}{2C_1 + C_{2p}} - \frac{\Delta q}{2C_1 + C_{2n}} \quad \Delta V_{2,n} = \frac{\Delta q}{2C_1 + C_{2n}}$$

$$\Delta V_{2,p} = -\frac{\Delta q}{2C_1 + C_{2p}}.$$

(15)

When M2 and M3 are OFF, the sign of  $\Delta V_1$  is reversed, while  $\Delta V_{2n}$  and  $\Delta V_{2p}$  stay the same. During switching transitions  $\Delta V_1 = \Delta V_{2p} = 0$  and  $\Delta V_{2n} = \Delta q/C_{2n}$ . As a result the ISF is well approximated as:

$$\Gamma_{M,n} = \frac{1}{A_1 \left( 1 + 4 \frac{C_{2n}}{C_1} \frac{A_{2n}^2}{A_1^2} + 4 \frac{C_{2p}}{C_1} \frac{A_{2p}^2}{A_1^2} \right)} \times \left( \frac{A_1}{2} \cos(\varphi) + 2A_{2,n} \sin(2\varphi) \right). \quad (16)$$

Similarly, the ISF of the PMOS transistors can be derived as:

$$\Gamma_{M,p} = \frac{1}{A_1 \left( 1 + 4 \frac{C_{2n}}{C_1} \frac{A_{2n}^2}{A_1^2} + 4 \frac{C_{2p}}{C_1} \frac{A_{2p}^2}{A_1^2} \right)} \times \left( -\frac{A_1}{2} \cos(\varphi) - 2A_{2,p} \sin(2\varphi) \right). \quad (17)$$

Figs. 12–13 report the simulated and calculated waveforms for the main tank, the tail tanks and the NMOS and PMOS transistors ISFs, showing in all cases quite good accuracy.

$$\vec{X} = \begin{bmatrix} V_{C_1} & \sqrt{\frac{L_1}{C_1}} I_{L_1} & \sqrt{\frac{C_{2n}}{C_1}} V_{C_{2n}} & \sqrt{\frac{L_{2n}}{C_1}} I_{L_{2n}} & \sqrt{\frac{C_{p2}}{C_1}} V_{C_{2p}} & \sqrt{\frac{L_{2p}}{C_1}} I_{L_{2p}} \end{bmatrix}$$

(11)

Fig. 13. Active devices (nMOS, pMOS) ISF simulated (dotted) and evaluated (continuous) of oscillator of Fig. 2(b).

Fig. 14. Simulated ISFs with and without transformer coupling of Fig. 18.

Fig. 15. Output noise not normalized to the carrier of the different sources: simulated (markers) and calculated (lines) of oscillator of Fig. 2(b).

Fig. 16. Simulated Excess Noise Factor of N only (markers) and p-n (lines) (oscillators of Fig. 2).

2) Overall Phase Noise and ENF: Starting from the ISFs expressions in (12), (14) and (16)–(17) the corresponding phase noise contributions have been calculated, as shown in Appendix A. The results are compared with simulation results in Fig. 15 showing very good accuracy as for the N-only oscillator. To compare p-n and N-only oscillators the ENF has been calculated and simulated for both and the results are plotted in Fig. 16 for different values of tail tanks capacitance and quality factors. In the designs the p-n oscillator is operated

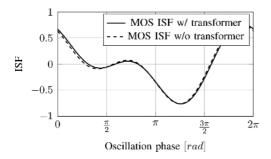

at twice the supply voltage of the N-only and the tail capacitors  $C_{2n}$ ,  $C_{2p}$  are both set to 1/2 the value of  $C_2$  in the N-only. As expected the ENF of the two oscillators is essentially the same, showing once again that in principle, when no design constraints are imposed, N-only and p-n structures achieve the same efficiency. One main drawback in using the p-n oscillator with tail filter is related to the need of two tail filters, which means more than doubling the filter's area occupation [49]. The use of a transformer at the tail represents a suitable solution to this problem without changing the ISF and thus the characteristic of this topology (Fig. 14 shows the simulated transistor's ISF with and without the magnetic coupling). The use of a transformer, however, leads to practical limitations, since for example in general is easier to achieve a better quality factor by using two separate inductors instead of a transformer, but the analysis presented is a suitable tool to determine the impact on the overall performance.

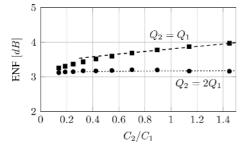

# C. Effect of Supply Voltage Limitations on P-N and N-Only Oscillators

The above analysis has disregarded any consideration related to technology reliability limitations. When these limitations are considered, depending on the type of transistors, the topology and on the available voltage supply the minimum achievable ENF can be affected. The large electric field experienced by the gate oxide in high swing oscillators can potentially reduce their long term reliability mainly due to time-dependent dielectric breakdown (TDDB) [50]. In our design a 55 nm CMOS technology was adopted, which provides standard transistors with a nominal supply of 1.2 V and high voltage thick (3.4 nm) oxide transistors having a nominal supply voltage of 1.8 V. The data extrapolated from the manufacturer TDDB reliability guidelines suggest a maximum DC oxide voltage of 2.4 V for thick oxide devices for 10-years 0.1% chip failure rate at 125°C. Recent publications [28], [50] analyze more in detail reliability issues in oscillators suggesting that such limits may be overly pessimistic. Publicly available data [50] on 3.5 nm thick oxide devices indicate a characteristic time to breakdown  $(\eta)$  of 8. 10<sup>5</sup> s (for 63.3% probability) at 4 V oxide voltage and 140°C for an area of  $10^3 \ \mu \text{m}^2$ . Applying the Weibull distribution [50] with a slope factor  $\beta = 2$ , a voltage acceleration factor n = 40and a device size of 50  $\mu$ m<sup>2</sup> the estimated maximum voltage is about 3.2 V<sup>3</sup> for a time to breakdown  $(T_{BD})$  of 10 years with a circuit failure rate of 0.002% (roughly corresponding to a 10 mm<sup>2</sup> chip failure rate of 0.1% for a 0.2 mm<sup>2</sup> circuit area). An accurate technology reliability characterization is necessary to correctly estimate the maximum voltage for the desired  $T_{BD}$ . In our design a conservative 2.1 V maximum VCO swing (peak differential) was taken as a design target that corresponds to about 2.15 V maximum gate-source voltage swing. This was obtained from the maximum oxide voltage specified by the manufacturer reduced by about 10% to take into account the uncertainty in the control of the maximum VCO swing in the presence of technology temperature and supply variations. Keeping

$^{3}$ Notice that, given the exponential dependence between  $T_{BD}$  and oxide voltage, the fact that the oxide reaches the peak voltage only for a small fraction of the oscillation period does significantly change the maximum allowed voltage in AC regime with respect to DC [28].

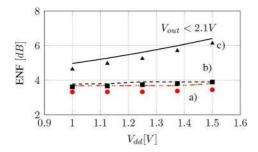

Fig. 17. Excess noise factor of (a) p-n (red) and b,c) N only (black) oscillators (Fig. 2) as a function of supply voltage: simulated (markers) and calculated (lines).

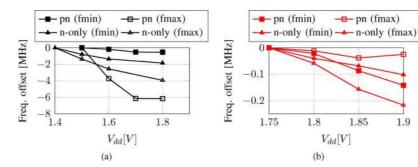

the (fairly aggressive) safety margin of 10% but starting from the less conservative maximum oxide voltage of 3.2 V the maximum VCO swing becomes about 2.8 V. An N-only topology achieves the same minimum ENF of a corresponding complementary pn-structure at twice the voltage swing and is therefore more affected by reliability constraints. In Fig. 17 we report the minimum achievable ENF for a p-n (curve a) and an N-only (curve b) class-B oscillators with resonant tail filters as a function of the supply voltage. The simulations were carried out using high voltage transistors. In curve b the N-only oscillator is pushed to its maximum voltage swings and it achieves approximately the same ENF of the p-n oscillator. However, for a supply voltage of 1.5 V the maximum swing is close to 3.8 V, which exceeds even more the relaxed oxide reliability limits. If the maximum voltage swing is limited to 2.1 V, curve c is obtained. At 1.5 V the minimum achievable ENF increases by as much as 3 dB. The penalty gradually reduces as the supply voltage is reduced and is below 1 dB for 1 V supply voltage.

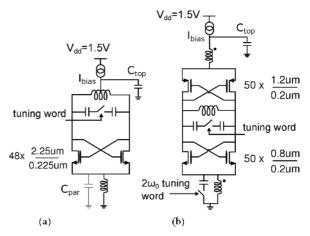

# IV. OSCILLATOR DESIGN AND EXPERIMENTAL RESULTS

The difficulty to extract the tank Q, together with the high sensitivity of phase noise to Q, limits the ability to accurately assess the potential of a new topology. Because of this we have built a test chip that allows to compare the proposed topology with a reference oscillator, both working in the same operating conditions. The implemented chip prototype includes the class-B complementary p-n oscillator (with magnetically coupled tail filters), together with a class-B N-only oscillator with a single tail filter (used as reference) and was fabricated in a 55 nm standard CMOS technology with only one thick metal layer. Circuit schematics are reported in Fig. 18. The oscillators use thick oxide devices and are biased from a 1.5 V internal supply derived from the external 1.8 V supply through an on-chip band-gap referenced programmable low-voltage-drop regulator. Both use identical tanks and can be tuned from about 7.4 GHz to 8.4 GHz (before frequency division by 2, using a classical CML divider) with a 5 bits MOM capacitor bank. Small sized varactors (used for fine tuning) were not included. For the tail tank the main design goal is to maximize its impedance at  $2\omega_0$ . This can be achieved using a high Q tank and/or a large inductor. A small inductor with high Q is preferable because it allows to use very large switching devices (with very low  $r_{ON}$  but large parasitic capacitance). This allows to improve power efficiency and gives about 1 dB phase

Fig. 18. Class-B oscillators with  $2\omega_0$  LC tail filters: (a) N-only and (b) p-n.

Fig. 19. Chip photo.

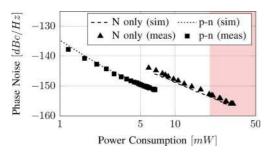

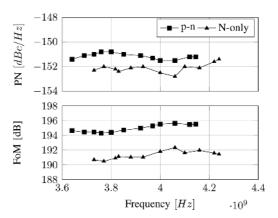

noise improvement (from simulations), although at the cost of an extra capacitor array for the tuning of the  $2\omega_0$  tank. Using coupled inductors allows to save area and to use single tunable capacitor array. The coupled tanks (with inductor values of 180 pH and 130 pH and a coupling factor of 0.7) have a quality factor of about 10. A single 3-bit capacitor bank at the NMOS switching transistors source (controlled independently from the main tank) is used for tuning them. For the N-only oscillator the single tail tank has a quality factor of about 6 and uses an inductor of 300 pH. A die photograph of the oscillators is shown in Fig. 19: the N-only and p-n oscillators have an active area of  $0.17 \text{ mm}^2$  and  $0.19 \text{ mm}^2$  respectively. Fig. 20 shows the measured phase noise at the minimum and maximum frequencies for both oscillators. The  $1/f^3$  noise corner is between 200 kHz and 400 kHz for the p-n oscillator and between 400 kHz and 600 kHz for the N only while the  $1/f^2$ noise exceeds the 2G TX specification at 20 MHz frequency offset by more than 7 dB for the p-n oscillator and by 8 dB for the N-only, giving sufficient margin for other non-idealities. N-only oscillator (Fig. 20) has higher flicker noise sensitivity compared to the p-n, probably due to a slightly mistuning of the tail filter [51]. Fig. 21 shows the phase noise of both oscillators at the maximum frequency as a function of power consumption. The p-n oscillator reaches a minimum phase

Fig. 20. Phase noise measurements (after freq divider by 2) at the minimum and maximum frequency of oscillation.

Fig. 21. Measured (dots) phase noise at 10 MHz offset after freq. divider by 2 and simulated (lines) phase noise with 6 dB reduction as a function of power dissipation of p-n and N only oscillators. Shaded area corresponds to voltage swings in excess of 2.1 V.

noise of  $-151.5 \, \mathrm{dBc/Hz}$  for an estimated oscillation amplitude of 1.6 V. The p-n oscillator has 0-1 dB lower phase noise of the N-only one with half the power consumption (i.e., the same output voltage for the same tank) thanks to the higher Q of the tail resonator. The N-only oscillator reaches its minimum phase noise of  $-156 \, \mathrm{dBc/Hz}$  at  $\sim 4 \, \mathrm{times}$  the power consumption of its p-n counterpart (i.e., for an amplitude of  $\sim 3.2~\mathrm{V}$ ). The tail tank of the N-only is not tunable, which leads to some residual loading effects, responsible for an estimated 0.5-1 dB phase noise degradation. The best achievable FoM is 195.6 dBc/Hz for the p-n oscillator and 192.3 dBc/Hz for the N-only, if conservatively limited to AC output voltage of 2.1 V, and it varies about 1.3 dB and 1.8 dB respectively across the tuning range (Fig. 22). Pushing the N-only to its limit oscillation amplitude further improves its FoM to 193.5 dBc/Hz, but poses reliability concerns. Table I compares the two prototype oscillators [54] with the state of the art. With the exception of [3], the average FoM over the tuning range of the p-n oscillator is the highest reported. However the oscillator in [3] has an

Fig. 22. Measured phase noise and FoM at 10 MHz offset over tuning range.

unpractical low supply and its FoM drops by 1 dB for a 25 mV supply voltage variation. For a further comparison the ENF was computed. The Q of the two prototype oscillators was estimated measuring both the minimum supply current needed to start-up oscillations and the maximum absorbed current for a given supply voltage. Fitting the measured number with simulation gives in both cases an estimated Q between 14 and 15. Together with the same oscillator topology of the N-only oscillator in [26] (that does not take into account any possible stress effect), the presented pn-oscillator has the lowest reported ENF. The p-n oscillator also has a high  $FoM_T$  of 197.1 dBc/Hz, which is among the best of the high FoM and low ENF oscillators reported in the literature. Frequency pushing was measured at maximum and minimum frequencies by changing the regulator output voltage and varying the regulator supply voltage and the results are reported in Fig. 23.

# V. CONCLUSION

The phase noise of N-only and p-n class-B oscillators with second harmonic tail resonant tanks has been analyzed. An accurate analytical formula is found that provides useful design insights. The analysis shows that the p-n oscillator outperforms the N-only for supply voltages of 1 V or higher. We have proposed a complementary class-B oscillator with transformer based tail filtering that exhibits a high efficiency and has 3–4 dB better FoM than a reference N-only oscillator, when the maximum AC output voltage is conservatively limited to less than 2.1 V, at a supply voltage of 1.5 V. The transformer based tail filter permits to save area compared to classical implementations and allows to achieve a more constant FoM across the tuning range thanks to the tuning. The fabricated 55 nm CMOS oscillator displays one of the best reported ENF avoiding reliability concerns.

# **APPENDIX**

The system can be represented as the steady-state vector  $\vec{X}_0$  [1], [43], [44] in (A.1) to which a random perturbation vector  $\Delta X$  will be added. See equation (A.1) at the bottom of the page.

$$\vec{X}_0 = \begin{bmatrix} A_1 \sin(\omega_0 t) & A_1 \cos(\omega_0 t) & A_2 \sqrt{\frac{C_2}{C_1}} \cos(2\omega_0 t) & A_2 \sqrt{\frac{C_2}{C_1}} \sin(2\omega_0 t) \end{bmatrix}$$

(A.1)

1.9

pn (fmax)

1.85

$V_{dd}[V]$

Fig. 23. Frequency pushing measurements (after frequency divider): measured frequency offset from nominal as function of the supply voltage (a) and as a function of the regulator supply voltage (b).

When a charge pulse  $\Delta q$  is applied across one of the capacitors a steady state phase error is produced in the oscillator. The phase error  $\Delta \phi_i = \Gamma(\omega_0 t) \Delta q / q_{\rm max}$  is a function of the time instant (within the oscillation period) when the charge pulse is injected and is proportional to the Impulse Sensitivity Function  $\Gamma$ . Neglecting the component of  $\Delta X$  orthogonal to the trajectory, the phase perturbation  $\Delta \phi$  can be derived from the state variables derivatives dX/dt [1], [44] where the ISF in terms of state-space vectors is given in (A.2) [1], [44].

$$\Gamma_i = \omega_0 \frac{q_{\text{max}}}{\Delta q} \frac{\Delta \vec{X}_i \cdot \dot{\vec{X}}}{|\dot{\vec{X}}|^2}.$$

(A.2)

In (A.2)  $q_{\text{max}}$  is just a normalizing factor, being the maximum charge across the capacitor placed between the nodes of interest.

Once the phase responses of the noise sources have been evaluated, the phase noise  $L(\Delta\omega)$  caused by a white current noise source  $i_{n,i}^2$  can be obtained using (A.3).

$$L(\Delta\omega) = 10 \log \left[ \frac{\Gamma_{i_n,rms}^2 i_{n,i}^2}{\frac{\Delta f}{2q_{\max}^2 \Delta \omega^2}} \right]. \tag{A.3}$$

This assumes that the noise perpendicular to the steady statespace trajectory of the oscillation does not generate any contribution to phase noise. Andreani and Wang [44], based on the more accurate phase noise evaluation proposed by Demir et al. [52] and Kaertner [43], have demonstrated that the error made without considering this component, using appropriate normalization factor of the state variables, is in fact negligible.

The active devices are clearly non-stationary sources:  $i_{n,MOS}^2 = 4k_BT(\gamma g_m(\omega_0 t) + g_{ds}(\omega_0 t))$ . Their phase noise contribution can be calculated using the general expression:

$$L_M(\Delta\omega) = 10 \log \left( \frac{1}{T} \int_0^T \frac{i_{n,MOS}^2(\omega_0 t) \Gamma_M^2(\omega_0 t)}{2q_{\max}^2 \Delta\omega^2} \right). \tag{A.4}$$

It is easy to show that since  $g_{ds}$  is large only when  $\Gamma_M$  is close to zero, its contribution can be neglected, hence  $g_m(\omega_0 t)$  can be

expressed as  $(\partial I_D/\partial t)/(\partial V_{qs}/\partial t)$ . Furthermore, since  $\partial V_s/\partial t$ is close to zero during the switching transients, as shown in Fig. 11, i.e., when both  $g_m(\omega_0 t)$  and  $\Gamma_M(\omega_0 t)$  are non-zero,  $\partial V_{qs}/\partial t$  in (A.4) can be approximated as  $-\partial V_{ds}/\partial t$  yielding the simplified expression in (A.5) at the bottom of the page. where  $\Gamma_M(\omega_0 t)$  was approximated considering only the first and second harmonic. In (A.5) only the first and second harmonic of the drain current, equal respectively to the main and tail tank currents, give a non-zero integral. The resulting overall phase noise expression is reported in (10), confirming the general result that the active devices contribute  $\gamma$  times the phase noise contribution due to the tanks losses. Notice that the general result found in [6], [30] in principle cannot be applied since the active devices work in deep triode and they do not act as a memory-less transconductor due to the tail tank.

### ACKNOWLEDGMENT

The authors wish to acknowledge Marvell Tech. Group for providing silicon access.

# REFERENCES

- [1] A. Hajimiri and T. Lee, "A general theory of phase noise in electrical oscillators," IEEE J. Solid-State Circuits, vol. 33, no. 2, pp. 179-194,

- [2] M. Garampazzi, S. Dal Toso, A. Liscidini, D. Manstretta, P. Mendez, L. Romanò, and R. Castello, "An intuitive analysis of phase noise fundamental limits suitable for benchmarking LC oscillators," IEEE J. Solid-State Circuits, vol. 49, no. 3, pp. 635-645, 2014.

- [3] T. Brown, F. Farhabakhshian, A. Guha Roy, T. Fiez, and K. Mayaram, "A 475 mV, 4.9 GHz enhanced swing differential colpitts VCO with phase noise of -136 dBc/Hz at a 3 MHz offset frequency," *IEEE J*. Solid-State Circuits, vol. 46, no. 8, pp. 1782-1795, Aug. 2011.

- [4] L. Fanori and P. Andreani, "A 2.5-to-3.3 GHz CMOS class-D VCO," in IEEE ISSCC Dig. Tech. Papers, 2013, pp. 346-347.

- M. Babaie, A. Visweswaran, Z. He, and R. Staszewski, "Ultra-low phase noise 7.2-8.7 GHz clip-and-restore oscillator with 191 dBc/Hz FoM," in 2013 IEEE Radio Frequency Integrated Circuits Symp. (RFIC), Jun. 2013, pp. 43-46.

- [6] A. Mazzanti and P. Andreani, "Class-C harmonic CMOS VCOs, with a general result on phase noise," IEEE J. Solid-State Circuits, vol. 43, no. 12, pp. 2716-2729, 2008.

$$L_M(\Delta\omega) = 10\log\left(\frac{2}{T}\int_0^T \frac{4k_BT\gamma\sum_{k=0}^\infty kI_{k,out}\cos(k\omega_0t + \phi_k)}{2q_{\max}^2\Delta\omega^2} \left(\frac{A_1}{2}\cos(\omega_0t) + 2A_2\sin(2\omega_0t)\right)dt\right)$$

(A.5)

- [7] A. Mazzanti and P. Andreani, "A push-pull class-C CMOS VCO," IEEE J. Solid-State Circuits, vol. 48, no. 3, pp. 724–732, 2013.

- [8] S. Levantino, C. Samori, A. Bonfanti, S. Gierkink, A. Lacaita, and V. Boccuzzi, "Frequency dependence on bias current in 5 GHz CMOS VCOs: Impact on tuning range and flicker noise upconversion," *IEEE J. Solid-State Circuits*, vol. 37, no. 8, pp. 1003–1011, Aug. 2002.

- [9] M. Babaie and R. Staszewski, "A class-F CMOS oscillator," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3120–3133, Dec. 2013.

- [10] L. Fanori and P. Andreani, "Class-D CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3105–3119, Dec. 2013.

- [11] H. Wang, "A 9.8 GHz back-gate tuned VCO in 0.35  $\mu$ m CMOS," in *IEEE ISSCC Dig. Tech. Papers*, 1999, pp. 406–407.

- [12] A. Hajimiri and T. Lee, "Design issues in CMOS differential LC oscillators," *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 717–724, 1999.

- [13] B. D. Muer, M. Borremans, M. Steyaert, and G. Li Puma, "A 2-GHz low-phase-noise integrated LC-VCO set with flicker-noise upconversion minimization," *IEEE J. Solid-State Circuits*, vol. 35, no. 7, pp. 1034–1038, 2000.

- [14] C. Samori, A. Lacaita, A. Zanchi, S. Levantino, and G. Cali, "Phase noise degradation at high oscillation amplitudes in LC-tuned VCOs," *IEEE J. Solid-State Circuits*, vol. 35, no. 1, pp. 96–99, 2000.

- [15] F. Svelto, S. Deantoni, and R. Castello, "A I mA, -120.5 dBc/Hz at 600 kHz from 1.9 GHz fully tuneable LC CMOS VCO," in *Proc. IEEE Custom Integrated Circuits Conf.*, 2000, pp. 577–580.

- [16] D. Ham and A. Hajimiri, "Concepts and methods in optimization of integrated LC VCOs," *IEEE J. Solid-State Circuits*, vol. 36, no. 6, pp. 896–909, 2001.

- [17] P. Andreani and H. Sjoland, "Tail current noise suppression in RF CMOS VCOs," *IEEE J. Solid-State Circuits*, vol. 37, no. 3, pp. 342–348, 2002.

- [18] N. H. W. Fong, J. O. Plouchart, N. Zamdmer, D. Liu, L. Wagner, C. Plett, and N. Tarr, "Design of wide-band CMOS VCO for multiband wireless LAN applications," *IEEE J. Solid-State Circuits*, vol. 38, no. 8, pp. 1333–1342, 2003.

- [19] G. De Astis, D. Cordeau, J.-M. Paillot, and L. Dascalescu, "A 5 GHz fully integrated full PMOS low phase noise LC VCO," in *Proc. IEEE Compound Semiconductor Integrated Circuits Symp.*, 2004, pp. 151–154.

- [20] H. Kim, S. Ryu, Y. Chung, J. Choi, and B. Kim, "A low phase-noise CMOS VCO with harmonic tuned LC tank," *IEEE Trans. Microw. Theory Techn.*, vol. 54, no. 7, pp. 2917–2924, 2006.

- [21] H.-H. Hsieh and L.-H. Lu, "A high-performance CMOS voltage-controlled oscillator for ultra-low-voltage operations," *IEEE Trans. Microw. Theory Techn.*, vol. 55, no. 3, pp. 467–473, 2007.

- [22] S. Toso, A. Bevilacqua, M. Tiebout, N. D. Dalt, A. Gerosa, and A. Neviani, "A 0.06 mm<sup>2</sup> 11 mW local oscillator for the GSM standard in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 45, no. 7, pp. 1295–1304, 2010.

- [23] P. Andreani, K. Kozmin, P. Sandrup, M. Nilsson, and T. Mattsson, "A TX VCO for WCDMA/EDGE in 90 nm RF CMOS," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1618–1626, Jul. 2011.

- [24] A. Liscidini, L. Fanori, P. Andreani, and R. Castello, "A 36 mW/9 mW power-scalable DCO in 55 nm CMOS for GSM/WCDMA frequency synthesizers," in *IEEE ISSCC Dig. Tech. Papers*, 2012, pp. 348–350.

- [25] G. Li, L. Liu, Y. Tang, and E. Afshari, "A low-phase-noise wide-tuning-range oscillator based on resonant mode switching," *IEEE J. Solid-State Circuits*, vol. 47, no. 6, pp. 1295–1308, 2012.

- [26] E. Hegazi, H. Sjoland, and A. Abidi, "A filtering technique to lower LC oscillator phase noise," *IEEE J. Solid-State Circuits*, vol. 36, no. 12, pp. 1921–1930, Dec. 2001.

- [27] P. Andreani, X. Wang, L. Vandi, and A. Fard, "A study of phase noise in Colpitts and LC-tank CMOS oscillators," *IEEE J. Solid-State Circuits*, vol. 40, no. 5, pp. 1107–1118, May 2005.

- [28] M. Babaie and R. Staszewski, "An ultra-low phase noise class-f2 CMOS oscillator with 191 dBc/Hz FoM and long-term reliability," *IEEE J. Solid-State Circuits*, vol. 50, no. 3, pp. 679–692, Mar. 2015.

- [29] P. Kinget, Integrated GHz Voltage Controlled Oscillators. Boston, MA, USA: Kluwer Academic, 1999, pp. 353–381.

- [30] D. Murphy, J. Rael, and A. Abidi, "Phase noise in LC oscillators: A phasor-based analysis of a general result and of loaded," *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 57, no. 6, pp. 1187–1203, 2010.

- [31] J. Bank, "A harmonic-oscillator design methodology based on describing functions," Ph.D. dissertation, Chalmers University of Technology, Chalmers, Sweden, 2006.

- [32] E. Xiao, J.-S. Yuan, and H. Yang, "Hot-carrier and soft-breakdown effects on VCO performance," *IEEE Trans. Microw. Theory Techn.*, vol. 50, no. 11, pp. 2453–2458, Nov. 2002.

- [33] L. Larcher, D. Sanzogni, R. Brama, A. Mazzanti, and F. Svelto, "Oxide breakdown after RF stress: Experimental analysis and effects on power amplifier operation," in *Proc. 44th Annu. IEEE Int. Reliability Physics Symp.*, Mar. 2006, pp. 283–288.

- [34] L. Vercesi, L. Fanori, F. D. Bernardinis, A. Liscidini, and R. Castello, "A dither-less all digital PLL for cellular transmitters," *IEEE J. Solid-State Circuits*, vol. 47, no. 8, pp. 1908–1920, Aug. 2012.

- [35] T. Choke et al., "A multiband mobile analog TV tuner SoC with 78-dB harmonic rejection and GSM blocker detection in 65-nm CMOS," IEEE J. Solid-State Circuits, vol. 48, no. 5, pp. 1174–1187, May 2013.

- [36] M. Hammes, C. Kranz, D. Seippel, J. Kissing, and A. Leyk, "Evolution on SoC integration: GSM baseband-radio in 0.13 μm CMOS extended by fully integrated power management unit," *IEEE J. Solid-State Circuits*, vol. 43, no. 1, pp. 236–245, Jan. 2008.

- [37] Y. Huang *et al.*, "A high-linearity WCDMA/GSM reconfigurable transceiver in 0.13 μm CMOS," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 1, pp. 204–217, Jan. 2013.

- [38] M. Jeong et al., "A 65 nm CMOS low-power small-size multistandard, multiband mobile broadcasting receiver SoC," in *IEEE ISSCC Dig. Tech. Papers*, 2010, pp. 460–461.

- [39] S. Liao et al., "A 70-Mb/s 100.5-dBm sensitivity 65-nm LP MIMO chipset for WiMAX portable router," *IEEE J. Solid-State Circuits*, vol. 47, no. 1, pp. 61–74, Jan. 2012.

- [40] S. Plevridis et al., "A 65 nm 3G femtocell multiband transceiver," in Proc. IEEE Radio Frequency Integrated Circuits Symp., 2014, pp. 137–140.

- [41] J. Strange et al., "A HSPA-WCDMA/EDGE 40 nm modem SoC with embedded RF transceiver supporting RX diversity," in Proc. IEEE Radio Frequency Integrated Circuits Symp., 2014, pp. 133–136.

- [42] T. Tsukizawa et al., "A fully integrated 60 GHz CMOS transceiver chipset based on WiGig/IEEE802.11ad with built-in self calibration for mobile applications," in *IEEE ISSCC Dig. Tech. Papers*, 2013, pp. 230–231.

- [43] F. Kaertner, "Determination of the correlation spectrum of oscillators with low noise," *IEEE Trans. Microw. Theory Techn.*, vol. 37, no. 1, pp. 90–101, 1989.

- [44] P. Andreani and X. Wang, "On the phase-noise and phase-error performances of multiphase LC CMOS VCOs," *IEEE J. Solid-State Circuits*, vol. 39, no. 11, pp. 1883–1893, 2004.

- [45] A. Moroni, R. Genesi, and D. Manstretta, "Analysis and design of a 54 GHz distributed "hybrid" wave oscillator array with quadrature outputs," *IEEE J. Solid-State Circuits*, vol. 49, no. 5, pp. 1158–1172, May 2014.

- [46] F. Pepe, A. Bonfanti, S. Levantino, P. Maffezzoni, C. Samori, and A. Lacaita, "An efficient linear-time variant simulation technique of oscillator phase sensitivity function," in *Proc. Int. Conf. Synthesis, Modeling, Analys. and Simulation Methods and Applications to Circuit Design (SMACD)*, 2012, pp. 17–20.

- [47] P. Andreani and A. Fard, "More on the phase noise performance of CMOS differential-pair LC-tank oscillators," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2703–2712, 2006.

- [48] J. Rael and A. Abidi, "Physical processes of phase noise in differential LC oscillators," in *Proc. IEEE Custom Integrated Circuits Conf.*, CICC, 2000, pp. 569–572.

- [49] Z. Tang, X. Wan, M. Wang, and J. Liu, "A 50-to-930 MHz quadrature-output fractional-n frequency synthesizer with 770-to-1860 MHz single-inductor LC-VCO and without noise folding effect for multistandard DTV tuners," in *IEEE ISSCC Dig. Tech. Papers*, 2013, pp. 358–359.

- [50] M. Babaie and R. Staszewski, "A study of RF oscillator reliability in nanoscale CMOS," in *Proc. Eur. Conf. Circuit Theory and Design* (ECCTD), 2013, pp. 1–4.

- [51] F. Pepe, A. Bonfanti, S. Levantino, and A. Lacaita, "Impact of non-quasi-static effects on 1/f<sup>3</sup> phase noise in a 1.9-to-2.6 GHz oscillator," in *Proc. IEEE Radio Frequency Integrated Circuits Symp.*, 2014, pp. 425–428.

- [52] A. Demir, A. Mehrotra, and J. Roychowdhury, "Phase noise in oscillators: A unifying theory and numerical methods for characterization," *IEEE Trans. Circuits Syst. I: Fund. Theory Applicat.*, vol. 47, no. 5, pp. 655–674, 2000.

- [53] A. Visweswaran, R. Staszewski, and J. Long, "A low phase noise oscillator principled on transformer-coupled hard limiting," *IEEE J. Solid-State Circuits*, vol. 49, no. 2, pp. 373–383, Feb. 2014.

- [54] M. Garampazzi, P. Mendes, N. Codega, D. Manstretta, and R. Castello, "A 195.6 dBc/Hz peak FoM P-N class-B oscillator with transformer-based tail filtering," in *Proc. 40th European Solid-State Circuits Conf.*, ESSCIRC 2014, 2014, pp. 311–334.

Marco Garampazzi (S'13) was born in Milan, Italy, in 1986. He received the M.Sc. (*summa cum laude*) degree and the Ph.D. degree in electronic engineering from University of Pavia, Italy, in 2011 and 2014, respectively. He was a Ph.D. intern with Marvell Semiconductor, Aliso Viejo, CA, USA.

In 2014 he joined Marvell Technology Group, Italy, as Analog Design Engineer and he is currently working on RF front-ends for multistandard transceiver.

**Paulo M. Mendes** (SM'11) received the B.Sc. and the M.Sc. degrees in electrical engineering from the University of Coimbra, Coimbra, Portugal, in 1995 and 1999, respectively, and the Ph.D. degree in industrial electronics from the University of Minho, Guimarães, Portugal, in 2005.

He is an Associate Professor at the University of Minho, and a researcher at the MEMS Center, University of Minho. He has been involved in several projects related to project, fabrication, and characterization of wireless microsystems, as well of biomed-

ical microdevices.

Dr. Mendes is a member of the European Microwave Association, the IEEE Antennas and Propagation Society, the IEEE Engineering in Medicine and Biology Society, and the IEEE Industrial Electronics Society.

Nicola Codega (S'08–M'10) was born in Sondrio, Italy, in 1986. He received the M. Sc. degree (summa cum laude) and the Ph.D. degree in electronic engineering from University of Pavia, Italy, in 2010 and 2013, respectively. He was a Ph.D. intern in Marvell, Italy, from 2010 to 2013 and Marvell, Aliso Viejo (CA) USA, in 2012, working on multi-standard reconfigurable transceivers for mobile communications

In 2013 he joined Marvell Technology Group, Italy, as Analog Design Engineer and he is currently

working on transceivers for high-speed serial communications

**Danilo Manstretta** (M'03) received the Laurea degree (*summa cum laude*) and the Ph.D. degree in electrical engineering and computer science from the University of Pavia in 1998 and 2002, respectively. During his studies, he worked on CMOS RF front-end circuits for direct-conversion wireless applications.

From 2001 to 2003 he was with Agere Systems as a Member of Technical Staff, working on WLAN transceivers and linear power amplifiers for base stations. From 2003 to 2005 he was with Broadcom Cor-

poration, Irvine, CA, working on RF tuners for TV applications. In 2005 he joined the University of Pavia as an Assistant Professor and was granted tenure in 2008. His research interests are in the field of analog, RF and millimeter-wave integrated circuit design.

Dr. Manstretta is a member of the Technical Program Committee of the IEEE Radio Frequency Integrated Circuits (RFIC) Conference since 2006. He was co-recipient of the 2003 IEEE JOURNAL OF SOLID-STATE CIRCUITS Best Paper Award.

**Rinaldo Castello** (S'78–M'78–SM'92–F'99) graduated from the University of Genova (*summa cum laude*) in 1977 and received the M.S. and the Ph. D. from the University of California, Berkeley, in '81 and '84.

From '83 to '85 he was Visiting Assistant Professor at the University of California, Berkeley. In 1987 he joined the University of Pavia where he is now a Full Professor. He consulted for ST-Microelectronics, Milan, Italy up to 2005 in '98 he started a joint research centre between the University of Pavia and

ST and was its Scientific Director up to '05. He promoted the establishing of several design centre from multinational IC companies in the Pavia area among them Marvell for which he has been consulting from 2005.

Dr. Castello has been a member of the TPC of the European Solid State Circuit Conference (ESSCIRC) since 1987 and of the International Solid State Circuit Conference (ISSCC) from '92 to '04. He was Technical Chairman of ESSCIRC '91 and General Chairman of ESSCIRC '02, Associate Editor for Europe of the IEEE JOURNAL OF SOLID-STATE CIRCUITS from '94 to '96 and Guest Editor of the July '92 special issue. From 2000 to 2007 he has been Distinguished Lecturer of the IEEE Solid State Circuit Society. He was named one of the outstanding contributors for the first 50 and 60 years of ISSCC and a co-recipient of the Best Student Paper Award at the 2005 Symposium on VLSI of the Best Invited Paper Award at the 2011 CICC and of the Best Evening Panel Award at ISSCC 2012. He was one of the two European representatives at the Plenary Distinguished Panel of ISSCC 2013 and the Summer 2014 issue of the IEEE Solid-State Circuit Magazine was devoted to him.