### FLORE Repository istituzionale dell'Università degli Studi di Firenze

# Analysis and Design of Choke Inductors for Switched-Mode Power Inverters

Questa è la Versione finale referata (Post print/Accepted manuscript) della seguente pubblicazione:

#### Original Citation:

Analysis and Design of Choke Inductors for Switched-Mode Power Inverters / Saini, Dalvir K.; Ayachit, Agasthya; Reatti, Alberto; Kazimierczuk, Marian K.. - In: IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS. - ISSN 0278-0046. - ELETTRONICO. - 65:(2018), pp. 2234-2244. [10.1109/TIE.2017.2740847]

#### Availability:

This version is available at: 2158/1095859 since: 2021-02-26T17:17:05Z

#### Published version:

DOI: 10.1109/TIE.2017.2740847

#### Terms of use:

Open Access

La pubblicazione è resa disponibile sotto le norme e i termini della licenza di deposito, secondo quanto stabilito dalla Policy per l'accesso aperto dell'Università degli Studi di Firenze (https://www.sba.unifi.it/upload/policy-oa-2016-1.pdf)

#### Publisher copyright claim:

Conformità alle politiche dell'editore / Compliance to publisher's policies

Questa versione della pubblicazione è conforme a quanto richiesto dalle politiche dell'editore in materia di copyright.

This version of the publication conforms to the publisher's copyright policies.

(Article begins on next page)

## Analysis and Design of Choke Inductors for Switched-Mode Power Inverters

Dalvir K. Saini , Agasthya Ayachit , Alberto Reatti, *Member, IEEE*, and Marian K. Kazimierczuk , *Fellow, IEEE*

Abstract—This paper presents the design, analytical estimation of power losses, and experimental measurement of choke inductors for switched-mode power inverters. The described approach is applicable to a wide variety of circuits such as Class-E inverters and converters. The expressions required to design the magnetic core in the choke inductor using the area-product  $(A_p)$  method are given. The equations for the dc resistance, ac resistance at high frequencies, and dc and ac power losses are provided for the solid round winding wire. To validate the presented approach, an example class-E zero-voltage switching power inverter with practical specifications is considered. A core with air gap is selected to avoid core saturation in the choke inductor, which conducts dc current and a small ac current. The gapped core power loss density and power loss are estimated using Steinmetz empirical equation. It is shown that the winding power loss due to the dc current is dominant for the given design. A comparison between the area-product  $A_p$  method and the preexisting core geometry coefficient  $K_g$  method is presented. The measured magnitude of the inductor impedance has shown that the designed choke is useful up to ten times the switching frequency.

Index Terms—Area—product method, choke inductance, class-E zero-voltage switching (ZVS) power inverter, core power loss, gapped core, impedance, magnetic core, power amplifiers, power inverters, winding power loss.

#### NOMENCLATURE

| $I_{Lf}, I_I$           | DC component of choke current, input current.     |

|-------------------------|---------------------------------------------------|

| $\Delta i_{Lf},I_{Lfm}$ | Peak-to-peak value, peak value of ac component    |

|                         | of choke current.                                 |

| $P_I, V_I$              | DC supply power, DC supply voltage.               |

| $P_O$                   | DC output power.                                  |

| $V_{Rm}$                | Amplitude of output voltage of class-E amplifier. |

| $L_f$                   | Choke inductance.                                 |

| $Q_L$                   | Quality factor of the resonant circuit.           |

| R                       | Load resistance of class-E amplifier.             |

| D, T                    | Duty cycle, total time period of each switching   |

|                         | cycle.                                            |

Manuscript received January 26, 2017; revised April 30, 2017 and July 9, 2017; accepted July 17, 2017. Date of publication August 21, 2017; date of current version December 15, 2017. (Corresponding author: Agasthya Ayachit.)

D. K. Saini, A. Ayachit, and M. K. Kazimierczuk are with the Department of Electrical Engineering, Wright State University, Dayton, OH 45435 USA (e-mail: saini.11@wright.edu; ayachit.2@wright.edu; marian.kazimierczuk@wright.edu).

A. Reatti is with the Department of Information Engineering, University of Florence, Florence 50139, Italy (e-mail: alberto.reatti@unifi.it).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TIE.2017.2740847

| $f_s, \omega_s$ | Switching | frequency, | angular | switching | fre- |

|-----------------|-----------|------------|---------|-----------|------|

|                 | quency.   |            |         |           |      |

$v_{Lf}$  Instantaneous voltage across choke inductor.  $I_{Lf(max)}$  Peak value of choke current including both dc and ac components.

$\delta_r$  Ratio of peak value to dc value of choke

$I_{m1}$ ,  $I_{m3}$  Fundamental, third harmonic choke current magnitudes.

$W_{Lf}$  Maximum energy stored in the choke inductor.

$A_p$  Area-product factor.  $W_a$  Core window area.  $A_c$  Core cross-sectional area.

$V_c$  Volume of core.

$J_{\rm rms}$  RMS choke winding current density.

$K_u$  Window utilization factor.

$l_{g(\min)}, l_g$  Minimum air-gap length, chosen standard air-gap

length.

$l_c$  Mean magnetic path length.  $l_T$  Average length per turn of winding.

$l_w$  Total length of winding.

$\mu_{rc}$  Manufacturer-specified core relative permeabil-

ity.

N Number of winding turns in choke inductor.  $B_s$  Saturation flux density at operation temperature.

$B_{pk}$  Peak value of magnetic flux density including its

dc and ac components.

$B_{cm}$  Magnitude of fundamental component of magnetic

flux density.

k, a, b Steinmetz empirical coefficients.

$\delta_w$  Winding skin depth.

$A_{w(\min)}$  Calculated minimum cross-sectional area of the

winding.

$A_w$  Chosen cross-sectional area of the winding.

$A_e$  Effective cross-sectional conductor area due to

skin effect.

$d_{i(\min)}, d_i$  Calculated minimum inner wire diameter, chosen

inner wire diameter.

$d_o$  Standard winding outer wire diameter.  $R_{wdc}$  DC winding resistance at room temperature.

$R_{w}$  dc winding resistance at room temperature.  $R_{w}$  AC winding resistance at room temperature.  $P_{Rw}$  Conduction power loss caused by dc choke cur-

rent.

| $P_{Rwac}$               | Conduction power loss caused by fundamental         |

|--------------------------|-----------------------------------------------------|

|                          | component of choke current.                         |

| $P_{vg}$                 | Gapped-core power loss density.                     |

| $P_{Cg}$                 | Gapped-core power loss.                             |

| $P_{Lf}$                 | Total power loss in choke inductor.                 |

| $C_{tt}$                 | Turn-to-turn capacitance of single-layer choke in-  |

|                          | ductor.                                             |

| $C_s$                    | Total self-capacitance of single-layer choke induc- |

| ~                        | tor.                                                |

| p                        | Winding pitch.                                      |

| $k_c$                    | Capacitance factor dependent on number of con-      |

|                          | ductor turns.                                       |

| $Z_s$                    | Impedance of the choke inductor.                    |

| $f_0, \omega_0$          | Self-resonant frequency, angular self-resonant fre- |

|                          | quency.                                             |

| $f_{zi}$ , $\omega_{zi}$ | Frequency of zero, angular frequency of zero.       |

| $Q_0$                    | Unloaded quality factor of choke inductor.          |

| $Q_0 \ \xi$              | Damping factor of choke inductor.                   |

| $F_f$                    | McLyman's fringing factor.                          |

| $V_{ m DSM},I_{ m DM}$   | Maximum manufacturer-specified switch voltage       |

|                          | and current stresses.                               |

| $\eta$                   | Efficiency of class-E amplifier.                    |

| $\eta_{\it p}$           | Porosity factor.                                    |

#### **CONSTANTS**

Resistivity of conductor at any temperature T.

Absolute free-space permittivity (8.854  $\times$  10<sup>-12</sup> F/m).  $\epsilon_0$ Copper resistivity (1.724  $\times$  10<sup>-8</sup>  $\Omega \cdot$  m at T = 20 °C.)  $\rho_w$ Permeability of free-space  $(4\pi \times 10^{-7} \text{ H/m})$ .  $\mu_0$

Relative permeability.  $\mu_r$

$\rho_w(T)$

Copper temperature coefficient of resistance (0.00393  $\alpha_{Cu}$  $C^{-1}$ ).

#### I. INTRODUCTION

AGNETIC components are integral parts of many electronic circuits. A good dc choke must ideally conduct only the dc component of its current. However, in practical situations, chokes also allow a fraction of ac current in addition to its dc component. Moreover, the waveform of the ac component at high frequencies is not sinusoidal resulting in losses due to high-order harmonics. A detailed design methodology for a magnetic component must address the following.

- 1) Select an appropriate core, which satisfies both electromagnetic conditions and core window area restrictions [1]–[7], [29].

- 2) Choose a sufficient air-gap length to avoid core saturation and minimize core power loss [8]–[12]

- 3) Provide an optimized winding geometry and winding arrangement [13]–[15].

- 4) Predict the winding and core power losses; hence, the total power loss [16]–[19].

- 5) Identify an appropriate model that best represents the inductor behavior over a range of operating frequencies and to be able to predict the ac characteristics [20]–[25].

This paper presents a comprehensive procedure to design the choke inductors such as those used in class-E power inverters. These inverters belong to a class of highly efficient electronic circuits. Therefore, the component design must be optimized to yield a maximum efficiency. Primarily, two main methods exist for designing the dc choke inductor [1]-[5]: area-product  $A_p$  method and core-geometry coefficient  $K_g$  method. The  $K_g$ method does not take the wire current density into account. If the core-geometry coefficient is overestimated, then the wire current density exceeds its maximum value. Therefore, the iteration must be repeated until the current density condition is satisfied. In addition, the  $K_g$  method assumes that the ac losses in the winding and the core are much smaller than the dc winding loss. This requires a high inductance and a larger core volume. On the upside, this method directly predicts the winding power loss in the choke inductor. The design of choke inductor for power inverters using the  $K_g$  method was developed in [4]. In this paper, the choke inductor is designed using the area-product  $A_n$  method. This is a widely adopted method to design magnetic components, especially in pulse width modulation (PWM) dc-dc converters as well as in ac resonant circuits [2], [5]. Since a majority of the current is dc, an air gap is essential to avoid core saturation and operate within permissible temperature limits [8]–[10]. An expression to estimate the minimum air gap length required to avoid the two restrictions is provided in Sections III-B and -C. The core losses in ac choke inductors are significantly higher than that in dc choke inductors. An attractive method for core loss measurement was proposed in [29]. As air gap is introduced, the ac flux density in the core decreases by a large factor, thereby reducing the core power loss [9], [10]. A loss estimation method for the choke inductor with a gapped core for dc chokes is presented in this paper. The analysis presented in this paper includes the effect of fringing [1]. Typically, in switching circuits, the current through the choke inductors are nonsinusoidal [11], [16], [25], [27], [28], [30]. The losses in the winding as well as in the magnetic core are caused by the dc, fundamental and higher order harmonics. Therefore, Fourier analysis is performed and the magnitude of the harmonic components are evaluated.

The objectives of this paper are as follows.

- 1) To develop a theoretical framework required to design choke inductors for switched-mode power inverters.

- 2) To derive the relevant expressions required to design the magnetic gapped core using the area-product method.

- 3) To determine impedance characteristics and compute the useful bandwidth of the choke inductor.

- 4) To present the design equations necessary to calculate dc and ac resistances and the corresponding dc and ac power

- 5) To validate the design of a class-E power inverter through experimental results.

#### II. DESIGN EXPRESSIONS

The main intent of this section is to present a step-by-step solution through analytical expressions required to design the choke inductor. The Fourier analysis of the choke inductor current has been introduced here. The area-product  $(A_p)$  method has been widely discussed in the literature for PWM dc-dc converters. However, a systematic theoretical framework to use

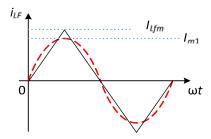

Fig. 1. Waveforms of the ac component of the choke inductor current and its fundamental harmonic component in class-E inverter.

the  $A_p$  method for the design of magnetic cores in choke inductors has not been previously reported. The relevant expressions for the core and winding power losses are discussed. The technique to determine the frequency response and hence the bandwidth of the choke inductors is also presented here.

#### A. Fourier Analysis of Choke Inductor Current

A switched-mode power inverter consists of dc supply voltage  $V_I$ , a switch S operating at a switching frequency  $f_s$ , a choke inductor  $L_f$ , a passive resonant network, and load resistance  $R_L$ . The output power of the inverter is denoted as  $P_O$ . Detailed circuit operation of inverters, for example in class-E mode has been discussed in [26]. The choke inductance  $L_f$  conducts the input current  $I_I = I_{Lf}$  and comprises an ac component  $\Delta i_{Lf}$  superimposed on a load-dependent dc component given by

$$i_{Lf} = I_{Lf} + \Delta i_{Lf}. \tag{1}$$

The supply dc current is

$$I_{Lf} = I_I = \frac{P_I}{V_I} = \frac{P_O}{nV_I}$$

(2)

where  $\eta$  is the overall efficiency of the inverter and  $P_I$  is the supply power. The maximum choke inductor current ripple occurs at a duty ratio D=0.5 [26]. During the charging instant, the voltage across the choke inductor is  $v_{Lf}=V_I$ . Therefore, the peak-to-peak inductor current ripple is

$$\Delta i_{Lf} = \frac{1}{L_f} \int_0^{DT} v_{Lf} dt = \frac{V_I DT}{2L_f} = \frac{V_I}{2f_s L_f}.$$

(3)

The amplitude of the ac current component is

$$I_{Lfm} = \frac{\Delta i_{Lf}}{2} = \frac{V_I}{4f_s L_f}.$$

(4)

The choke inductor must be able to reduce the ac component  $\Delta i_{Lf}$  ideally to zero and conduct only the dc current  $I_{Lf}$ . In practical cases, the choke can be designed to reduce the inductor current ripple by a factor  $\delta_r = I_{Lfm}/I_{Lf}$ . A very low ripple factor  $\delta_r$  is preferred. The peak current  $I_{Lf(\max)}$  through the choke is

$$I_{Lf(\text{max})} = I_{Lf} + I_{Lfm} = \frac{P_O}{\eta V_I} + \frac{V_I}{4f_s L_f}.$$

(5)

The ac component of the current through the choke is approximated by a symmetrical triangular wave of magnitude  $I_{Lfm}$  as shown in Fig. 1. The Fourier series expansion of the triangular

wave is

$$i_{Lfn} = \frac{8I_{Lfm}}{\pi^2} \sum_{n=1,3,5,\dots}^{\infty} \frac{(-1)^{(n-1)/2}}{n^2} \sin(n\omega_s t)$$

$$= \frac{8I_{Lfm}}{\pi^2} \left( \sin \omega_s t - \frac{1}{9} \sin 3\omega_s t + \frac{1}{25} \sin 3\omega_s t \cdots \right)$$

(6)

where  $\omega_s$  is the angular switching frequency. The fundamental component of the triangular waveform is

$$i_{Lf1} = I_{m1} \sin \omega_s t = \frac{8I_{Lfm}}{\pi^2} \sin \omega_s t. \tag{7}$$

The third harmonic component is

$$i_{Lf3} = -I_{m3}\sin 3\omega_s t = -\frac{8I_{Lfm}}{9\pi^2}\sin 3\omega_s t = -\frac{I_{m1}}{9}\sin 3\omega_s t.$$

(8)

The even harmonics (n=2,4,6,...) are zero since the triangular waveform is assumed to be symmetric about its dc value. By expanding the series, it can be noted that the amplitudes of the harmonics for  $n \geq 3$ , i.e.,  $I_{m3}$ ,  $I_{m5}$ , ... are much lower than the amplitude of the fundamental  $I_{m1}$ . Therefore, the effect of the higher order harmonics of the choke inductor current on the winding and core power can be neglected. One must note that the nature of the inverter operation causes the choke inductor waveform to increase and decrease in an exponential fashion rather than as a pure triangular wave. Such a waveform results in even harmonic components, however, have negligible current magnitudes compared to the fundamental component.

#### B. Design of Magnetic Core Using Area-Product Method

To design the choke, the magnetic material, core shape and size, winding wire diameter, and number of turns must be estimated. The area-product method relates the geometrical core parameters described by the core manufacturers with the inductor magnetic and electric parameters [2]. The maximum energy stored in the choke inductor due to both dc and ac currents is

$$W_{Lf} = \frac{1}{2} L_f I_{Lf(\text{max})}^2. (9)$$

The window utilization factor  $K_u$  and the saturation flux density  $B_s$  are assumed *a priori* for the maximum inductor current and the maximum operating temperature. The current density of the conductor is selected based on the rms current requirement and is discussed in the following section. The core area–product is given by [2]

$$A_p = W_a A_c = \frac{2W_{Lf}}{K_u J_{\text{rms}} B_s} \tag{10}$$

where  $W_a$  is the core window area and  $A_c$  is the core cross-sectional area, both of which are mentioned in the core manufacturer datasheet. The quantity  $J_{\rm rms}$  is the rms wire current density, where  $J_{\rm rms} = 5 \, {\rm A/mm^2}$  is used in this paper. Furthermore, the window area is estimated from (10) as

$$W_a = \frac{A_p}{A_c}. (11)$$

The minimum gap length to avoid core saturation is [9]

$$l_{g(\min)} = \frac{2\mu_0 W_{Lf}}{A_c B_s^2} - \frac{l_c}{\mu_{\rm rc}}$$

(12)

where  $\mu_0$  is the permeability of free-space,  $\mu_{\rm rc}$  is the relative permeability of the core material,  $l_c$  is the mean magnetic path length. A standard gap length  $l_g > l_{\rm g(min)}$  is chosen, which satisfies  $B_{pk} << B_s$ , where  $B_{pk}$  is the peak flux density. For the selected gap length, the number of turns required to meet the desired inductance is

$$N = \sqrt{\frac{L_f}{\mu_0 A_c}} \left( l_g + \frac{l_c}{\mu_{\rm rc}} \right). \tag{13}$$

Alternatively, low iron powder cores with a low relative permeability  $\mu_{\rm rc}$  can be utilized. This affects the winding design. The dc current as well as the ac current through the choke are functions of the load resistance of the inverter. In several applications, for example, class-E zero-voltage switching (ZVS) inverter in wireless power charging systems, the load resistance is a function of the distance between the transmission coil and the receiver coil. In such operating conditions, the dc and ac currents may exceed a critical value causing the core to saturate. This requires an air gap in the core. For the gapped core, the peak value of the magnetic flux density in the core of the choke inductor is given as

$$B_{pk} = \frac{\mu_{\text{rc}} \mu_0 N I_{Lf(\text{max})}}{l_c \left(1 + \frac{\mu_{\text{rc}} l_g}{l_c}\right)}.$$

(14)

However, the amplitude of magnetic flux density due to the fundamental of the ac component of the choke inductor current is

$$B_{cm} = \frac{\mu_{rc}\mu_0 N I_{m1}}{l_c \left(1 + \frac{\mu_{rc}l_g}{l_c}\right)} = \frac{8\mu_{rc}\mu_0 N I_{Lfm}}{\pi^2 l_c \left(1 + \frac{\mu_{rc}l_g}{l_c}\right)}.$$

(15)

For the gapped core, the Steinmetz empirical equation for the power loss density at frequency  $f_s$  is [8], [9]

$$P_{vg} = kf^{a}B_{cm}^{b} = kf_{s}^{a} \left[ \frac{8\mu_{rc}\mu_{0}NI_{Lfm}}{\pi^{2}l_{c}\left(1 + \frac{\mu_{rc}l_{g}}{l_{c}}\right)} \right]^{b}$$

(16)

where k, a, and b are the Steinmetz empirical coefficients [8]. Consequently, the total power loss in the gapped core is

$$P_{Cg} = P_{vg} V_c = k f_s^a \left[ \frac{8\mu_{rc} \mu_0 N I_{Lfm}}{\pi^2 l_c \left( 1 + \frac{\mu_{rc} l_g}{l_c} \right)} \right]^b A_c l_c$$

(17)

where  $V_c = A_c l_c$  is the volume of the core.

#### C. Winding Design

This section provides a methodology to design the inductor with a solid round winding. The solid round winding is designed to withstand the maximum current stress at a uniform dc current density. Assuming a copper conductor, the skin depth as a

function of frequency is [2]

$$\delta_w = \sqrt{\frac{\rho_w}{\pi f_s \mu_r \mu_0}} \tag{18}$$

where  $\rho_w = 1.724 \times 10^{-8} \ \Omega \cdot m$  at  $T = 25 \ ^{\circ}C$  is the resistivity of the conductor,  $f_s$  is the operating frequency,  $\mu_r$  is the relative permeability of the conductor ( $\mu_r = 1$  for metals), and  $\mu_0$  is the absolute permeability of free space. For a wire current density  $J_m$ , the miminum wire cross-sectional area  $A_{w(\min)}$  required to withstand the peak inductor current  $I_{Lf(\max)}$  is

$$A_{w(\min)} = \frac{I_{Lf(\max)}}{J_{\text{rms}}}.$$

(19)

Assuming that a solid round wire is used, the chosen wire must have an inner diameter  $d_i$  greater than  $d_{i(\min)}$  given by

$$d_i > d_{i(\min)} = \sqrt{\frac{4A_{w(\min)}}{\pi}} = \sqrt{\frac{4I_{Lf(\max)}}{\pi J_{rms}}}$$

(20)

which can be selected from a wire datasheet. In addition, the average length per turn  $l_T$  of the winding wound around the core is estimated. The total length of the winding is  $l_w = N l_T$ . The dc resistance of the solid-round winding is

$$R_{wdc} = \frac{\rho_w l_w}{A_w} = \frac{4\rho_w N l_T}{\pi d_i^2}.$$

(21)

The conduction power loss due to the dc component is

$$P_{Rwdc} = I_{Lf}^2 R_{wdc} = \frac{4\rho_w N l_T I_I^2}{\pi d_i^2}.$$

(22)

The solid-round winding wire ac resistance of single-layer inductor is determined by Dowell's equation [3]

$$R_w = R_{wdc} A \frac{\sinh(2A) + \sin(2A)}{\cosh(2A) - \cos(2A)}$$

(23)

where A is the relative winding inner diameter given by

$$A = \left(\frac{\pi}{4}\right)^{(3/4)} \frac{d_i}{\delta_m} \sqrt{\eta_p} \tag{24}$$

where  $\eta_p$  is the porosity factor. The winding power loss due to the ac component

$$P_{wac} = \frac{I_{m1}^2}{2} R_w = \frac{64 I_{Lfm}^2}{2\pi^4} R_w.$$

(25)

The selected core allows for a single layer winding to be wound, and therefore, the proximity effect is neglected in this paper.

For the designed inductor with solid-round winding, the total power loss is the sum of the core power loss given in (17), the power loss due to dc current given in (22), and the winding loss given in (25), and is expressed as

$$P_{Lf} = P_{Cg} + P_{Rwdc} + P_{wac}.$$

(26)

#### D. Choke Impedance

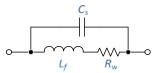

The parasitic components, such as the turn-to-turn capacitance and winding-to-core capacitance, create an upper limit for the useful bandwidth of the choke inductor [22]–[24]. The lumped-element model of a choke inductor is shown in Fig. 2.

Fig. 2. High-frequency lumped-element model of a choke inductor.

The resistance  $R_w$  is the ac series winding resistance,  $L_f$  is the inductance [14]–[19], and  $C_s$  is the self-capacitance.

The turn-to-turn capacitance of single-layer inductor with separation between adjacent turns  $s = p - d_o$  is [24]

$$C_{tt} = \frac{2\epsilon_0 l_T}{\sqrt{\left(\frac{1}{\epsilon_r} \ln \frac{d_o}{d_i} + \frac{p}{d_o}\right)^2 - 1}} \times \tan^{-1} \left(\sqrt{1 + \frac{2}{\frac{1}{\epsilon_r} \ln \frac{d_o}{d_i} + \frac{p}{d_o} - 1}}\right)$$

(27)

where  $l_T$  is the wire length-per-turn, p is the winding pitch,  $\epsilon_0 = 8.854 \times 10^{-12}$  F/m is the permittivity of free space,  $\epsilon_r$  is the relative permittivity, and  $d_i$  and  $d_o$  are the inner and outer diameters of the winding, respectively. For a multilayer inductor with N turns of winding and a magnetic core, the self-capacitance can be determined as [23]

$$C_s = k_c C_{tt} (28)$$

where  $k_c$  is the coefficient dependent on the number of turns required to estimate the total self-capacitance of the winding conductor for inductors with magnetic core. The value of  $k_c$  is  $k_c = 1.375$  for N = 5,  $k_c = 1.3684$  for N = 6,  $k_c = 1.3666$  for N = 7,  $k_c = 1.3662$  for N = 8,  $k_c = 1.3661$  for N = 9, and  $k_c = 1.366$  for  $N \ge 10$  and is explained in detail in [23]. At high frequencies, the displacement current bypasses the inductance and flows through the capacitance. The impedance of the choke model shown in Fig. 2 is

$$Z_s = (R_w + j\omega L_f)||\frac{1}{j\omega C_s} = R_w \frac{1 + \frac{j\omega}{\omega_{zi}}}{1 + \frac{j\omega}{Q_0\omega_0} - \left(\frac{\omega}{\omega_0}\right)^2}$$

(29)

where the frequency of the zero, self-resonant frequency, and the quality factor are, respectively

$$\omega_{zi} = \frac{R_w}{L_f}$$

$$f_0 = \frac{\omega_0}{2\pi} = \frac{1}{2\pi\sqrt{L_f C_s}}$$

and

$$Q_0 = \frac{1}{2\xi} = \frac{1}{R_W} \sqrt{\frac{L_f}{C_s}}.$$

(30)

#### III. DESIGN OF CHOKE FOR CLASS-E POWER INVERTER

#### A. Electrical Parameters

A choke inductor is designed for an example class-E power inverter with the following specifications: supply voltage  $V_I$  =

5 V, output power  $P_O = 10$  W, switching frequency  $f_s = 250$  kHz. The initial efficiency of the inverter is assumed as  $\eta = 0.95$  and the loaded quality factor of the resonant circuit is  $Q_L = 10$ . From [26], the load resistance is

$$R = \frac{8}{\pi^2 + 4} \frac{V_I^2}{P_O} = 0.5768 \times \frac{5^2}{10} = 1.44 \,\Omega \tag{31}$$

and the desired choke inductance is [26]

$$L_f = 2\left(\frac{\pi^2}{4} + 1\right)\frac{R}{f_s} = 6.93 \times \frac{1.44}{250 \times 10^3} = 40 \,\mu\text{H}.$$

(32)

The dc input current using (2) is  $I_I = I_{Lf} = 2.105$  A. The amplitude of the ac current through the choke inductance using (4) is  $I_{Lfm} = 125$  mA. Therefore, the peak value of the choke inductor current is  $I_{Lf(max)} = I_{Lf} + I_{Lfm} = 2.23$  A. The peak current is assumed as  $I_{Lf(max)} = 2.5$  A in order to provide a considerable safety margin.

#### B. Selection of Magnetic Core and Winding Wire

The maximum energy stored in the choke inductor using (9) is

$$W_{Lf} = \frac{1}{2} L_f I_{Lf(\text{max})}^2 = 0.125 \,\text{mJ}.$$

(33)

Assume the following parameters for the core: current density  $J_{\rm rms} = 5 \,{\rm A/mm^2}$ , window utilization factor  $K_u = 0.3$ , saturation magnetic field density  $B_s = 0.25 \,{\rm T}$  at  $T = 90 \,{}^{\circ}{\rm C}$  for P-type material. The core area product using (10) is

$$A_p = \frac{2W_{Lf}}{K_u J_{\text{rms}} B_s} = 0.0666 \,\text{cm}^4. \tag{34}$$

A Magnetics ferrite gapped pot P-type core 43019UG was selected, which has:

- 1) core area product  $A_p = 0.74 \,\mathrm{cm}^4$ ;

- 2) core cross-sectional area  $A_c = 137 \text{ mm}^2$ ;

- 3) mean magnetic path length  $l_c = 45.2 \text{ mm}$ ;

- 4) relative permeability of the core material  $\mu_{\rm rc} = 2500$ .

The P-type material has the following properties. The maximum usable frequency is 1.8 MHz, Curie temperature is  $T_c = 210$  °C, saturation flux density at T = 25 °C is 0.47 T, and resistivity is  $5 \Omega \cdot m$ . The fundamental frequency and its third harmonic are within the bandwidth of the core. The selected core has a standard gap length of  $l_g = 1.25$  mm. In order to ensure the gap length suffices that required to avoid core saturation, one may calculate the minimum gap length as

$$l_{g(\text{min})} = \frac{2\mu_0 W_{Lf}}{A_c B_s^2} - \frac{l_c}{\mu_{\text{rc}}} = 0.0216 \,\text{mm}$$

(35)

which is lower than the chosen  $l_g = 1.25$  mm. The number of turns needed to achieve the required inductance using the selected gapped core is

$$N = \sqrt{\frac{L_f}{\mu_0 A_c} \left( l_g + \frac{l_c}{\mu_{\rm rc}} \right)} = 17.144.$$

(36)

The number of turns N = 18 was selected. For the selected core, the effective height is  $2D - l_g = 13 - 1.25 = 11.75$  mm, where 2D is the height of the core window typically provided in

core manufacturer datasheets. The McLyman's fringing factor is [1]

$$F_f = 1 + \frac{l_g}{\sqrt{A_c}} \ln \frac{2D - l_g}{l_g} = 1.239.$$

(37)

The inductance including the fringing effect is

$$L_f = \frac{\mu_0 A_c N^2}{l_g / F_f + l_c / \mu_{\rm rc}} = 54.48 \,\mu\text{H}.$$

(38)

As desired, the actual choke inductance due to fringing effect is higher than the calculated value given in (32). The cross-sectional area required by the winding to sustain the current stresses using (19) is

$$A_w = \frac{I_{Lf(\text{max})}}{J_{\text{rms}}} = \frac{2.5}{5 \times 10^6} = 0.5 \,\text{mm}^2$$

(39)

to yield the minimum conductor diameter as  $d_i = 0.797$  mm. From the AWG datasheet, the selected winding is AWG20. The inner diameter of the selected wire is  $d_i = 0.812$  mm, the outer diameter is  $d_o = 0.879$  mm to yield the bare wire area as  $A_w = 0.5178$  mm<sup>2</sup>. The outer cross section area of the winding wire is

$$A_{wo} = \frac{\pi d_o^2}{4} = 0.606 \,\text{mm}^2. \tag{40}$$

Using (11), the window area is  $W_a = A_p/A_c = 54.01 \text{ mm}^2$ . However, the required core winding window area is

$$W_a = \frac{NA_{wo}}{K_v} = 36.36 \,\text{mm}^2 < 54.01 \,\text{mm}^2 \tag{41}$$

which ensures that the selected core can sufficiently accommodate the winding structure. Furthermore, the wire length-persingle turn wound around the center-post of the selected core of diameter F = 13.3 mm is

$$l_T = \pi(F + d_o) = 44.4 \,\text{mm}.$$

(42)

Therefore, total wire length is  $l_w = N l_T = 0.799\,$  m. Taking the leads and winding angle into account, let us assume  $l_w = 0.82\,$  m.

For the selected core material, the saturation flux density is  $B_s = 0.45$  T at 25 °C. However, in order to account for the rise in choke ambient temperature, a derated saturation flux density  $B_{s(\text{min})} = 0.25$  T at T = 90 °C is considered. Using the given core and electrical parameters, the peak value of the magnetic flux density for the gapped core as given in (14) is

$$B_{pk} = \frac{\mu_0 \mu_{\rm rc} N I_{Lf(\text{max})}}{l_c + \mu_{\rm rc} l_g} = 44.7 \,\text{mT} < B_{s(\text{min})}.$$

(43)

From the fundamental harmonic approximation discussed in Section II-A, the triangular waveform of the ac component of the choke inductor current is approximated by its fundamental sinusoidal component. The amplitude of the fundamental of ac component through the choke inductor is

$$I_{m1} = \frac{8}{\pi^2} I_{Lfm} = 0.1013 \,\text{A}.$$

(44)

The amplitude of the fundamental component of the flux density using (15) is

$$B_{cm} = \frac{\mu_0 \mu_{\rm rc} N I_{m1}}{l_c + \mu_{\rm rc} l_g} = 1.822 \,\text{mT}.$$

(45)

#### C. Power Losses in the Choke

For the selected core material and the specified operating frequency  $f_s = 250$  kHz, the Steinmetz parameters are k = 0.0573, a = 1.66, and b = 2.68. The total core power loss density at  $B_{cm} = 3.644$  mT using (16) is

$$P_{vg} = kf^a (B_{cm})^b = 0.011 \frac{\text{mW}}{\text{cm}^3}.$$

(46)

The volume of the core is given as

$$V_c = A_c l_c = 137 \times 45.2 = 6.192 \,\mathrm{cm}^3.$$

(47)

Therefore, the total power loss in the gapped core using (17) is

$$P_{Cg} = P_{vg}V_c = 0.011 \frac{\text{mW}}{\text{cm}^3} \times 6.192 \text{ cm}^3 = 0.073 \text{ mW}.$$

(48)

For the copper winding, the skin depth at the switching frequency using (18) is obtained as

$$\delta_w = \sqrt{\frac{\rho_w}{\pi f_s \mu_r \mu_0}} = 0.132 \,\text{mm}.$$

(49)

The dc resistance of the solid round winding is

$$R_{wdc} = \frac{4\rho_w N l_T}{\pi d_i^2} = 26.6 \,\text{m}\Omega \tag{50}$$

yielding the conduction winding loss due to the dc current as

$$P_{Rwdc} = I_{Lf}^2 R_{wdc} = 117.8 \,\text{mW}.$$

(51)

For a porosity factor  $\eta_p=0.9$ , the relative winding inner diameter is given by

$$A = \left(\frac{\pi}{4}\right)^{(3/4)} \frac{d_i}{\delta_w} \sqrt{\eta_p} = 4.869.$$

(52)

The ac resistance of the solid round winding using (23) at  $f_s = 250 \text{ kHz}$  is

$$R_w = R_{wdc} A \frac{\sinh(2A) + \sin(2A)}{\cosh(2A) - \cos(2A)} = 121.9 \,\text{m}\Omega.$$

(53)

Hence,  $F_R = R_w/R_{wdc} = 4.58$ . The power loss due to the ac component

$$P_{\text{wac}} = \frac{I_{m1}^2}{2} R_w = 0.625 \,\text{mW}. \tag{54}$$

The ratio of the winding dc power loss to the winding ac power loss is

$$\frac{P_{Rwdc}}{P_{wac}} = \frac{117.8}{0.625} = 188.5. \tag{55}$$

One can observe that the winding dc power loss due to the dc current component is a much significant contributor to the overall power loss in the choke inductor. Neglecting the losses in the core and the ac winding loss, the power loss in the choke inductor at  $T=25~^{\circ}\mathrm{C}$  is

$$P_{Lf} \approx P_{Rwdc} = 117.8 \,\text{mW}. \tag{56}$$

For the third harmonic  $3f_s = 750$  kHz, using (8), (18), and (23),  $I_{m3} = 0.0113$  A,  $\delta_{w3} = 0.0764$  mm, and  $R_{w3} = 0.2106 \Omega$ , respectively. The ac winding power loss is  $P_{w3} = 0.01345$  mW, which is negligible as compared to the winding dc power loss and the power loss due to fundamental component.

The conductor resistivity increases with temperature by the relation  $\rho_w(T) = \rho_w(25 \,^{\circ}\text{C})[1 + \alpha_{Cu}(T - 25)]$ , where  $\alpha_{Cu} = 0.00393 \,^{\circ}\text{C}^{-1}$ . Using (21) and (22), the dc winding resistance and the winding power loss also increase with temperature, respectively. The dc winding power loss is  $P_{Rwdc} = 121.3 \, \text{mW}$  at  $T = 50 \,^{\circ}\text{C}$  and  $P_{Rwdc} = 143 \, \text{mW}$  at  $T = 100 \,^{\circ}\text{C}$ .

#### D. Choke Impedance

The selected AWG20 winding conductor has the following specifications: inner diameter  $d_i = 0.812$  mm, outer diameter  $d_o = 0.879$  mm, and permittivity of the wire insulating material  $\epsilon_r = 3.3$ . The wire length per turn  $l_T = 41.78$  mm. Assuming a tightly wound inductor, then pitch  $p = d_o$ . Using (27), the turn-to-turn capacitance is  $C_{tt} = 4.905$  pF. The self-capacitance of the winding for N = 18 at  $k_c = 1.366$  using (28) is  $C_s = k_c C_{tt} = 1.366 \times 4.905 = 6.702$  pF. At  $R_w = 0.183$   $\Omega$  computed at the switching frequency, using (30), the frequency of the zero, the unloaded quality factor, and the self-resonant frequency are  $f_{zi} = 4.575$  kHz,  $Q_0 = 13.351 \times 10^3$ , and  $f_0 = 9.72$  MHz, respectively.

### IV. COMPARISON OF RESULTS WITH CORE-GEOMETRY COEFFICIENT $(K_g)$ METHOD

The core geometry coefficient  $(K_g)$  method is another viable design technique for magnetic core selection [1], [4]. This technique is based on an assumption that the ac winding loss and the ac core loss are much lower than the dc winding loss. This occurs when the ac component of the choke current is significantly lower than its dc component; therefore, a high-valued choke inductance is required to support this condition. For the purpose of comparing the outcomes of  $A_p$  and  $K_g$  methods, the following cases are considered.

### A. Case 1: Comparison Using Calculated Choke Inductance

The electrical specifications and the inductance are as given in Section III-A. The ripple-to-dc current ratio for the given design is

$$\delta_r = \frac{\Delta i_{Lf}}{I_L} = \frac{2I_{Lfm}}{I_L} = \frac{2 \times 0.125}{2.105} = 11.8\%.$$

(57)

The expression for the core geometry coefficient is

$$K_g = \frac{\rho_w L_f^2 I_I^2 (1 + \delta_r / 2)^2}{\alpha P_O B_s^2}$$

(58)

where  $\alpha = P_{Rwdc}/P_O$  is a constant, which is assumed during the initial stages and the remainder of the parameters are as defined

previously. Assuming  $\alpha = 0.005$  yields  $K_g = 0.00194 \, \mathrm{cm}^5$ . From [1], PC41811 ferrite pot core with  $K_g = 0.005287 \, \mathrm{cm}^5$  is the appropriate selection. The area–product  $A_p$  for the selected core from [32] is  $A_p = 0.11413 \, \mathrm{cm}^4$ , which satisfies the value calculated in (34). Therefore, if the inductance is estimated based on the circuit-oriented approach, then the two methods result in nearly identical magnetic cores.

### B. Case 2: Comparison Using Required Ripple-to-DC Current Ratio

In order to achieve a low ac core and winding power loss, the ripple-to-dc current ratio must be very small. Assume  $\delta_r=1\%$ . For  $I_I=2.105\,$  A, then using (57),  $\Delta i_{Lf}=0.01\times 2.105=21.05\,$  mA. Using (2) and (4) in (57) results in the choke inductance as

$$L_f = \frac{1}{2 f_s \delta_r} = \frac{1}{2 \times 250 \times 10^3 \times 0.01} = 0.2 \,\text{mH}.$$

(59)

Using (58), the core geometry coefficient is  $K_g = 0.04376 \,\mathrm{cm}^5$ . Using [1], PC3019 ferrite pot core with  $K_g = 0.0804 \,\mathrm{cm}^5$  can be chosen, whose  $A_c = 137 \,\mathrm{mm}^2$ ,  $l_c = 45.2 \,\mathrm{mm}$ , and volume  $V_c = A_c l_c = 6.192 \,\mathrm{cm}^3$ . The peak choke current is  $I_{Lf(\mathrm{max})} = I_I + \Delta i_{Lf}/2 = 2.11 \,\mathrm{A}$ . The energy stored using (9) is  $W_{Lf} = 0.4475 \,\mathrm{mJ}$ . Therefore, the area–product  $A_p$  using (10) is  $A_p = 0.238 \,\mathrm{cm}^4$ . Using [32], PC42213 is chosen, core volume  $V_c = 2.81 \,\mathrm{cm}^3$ , i.e., the core selected using  $A_p$  method is relatively smaller than that by  $K_g$  method.

#### V. EXPERIMENTAL RESULTS

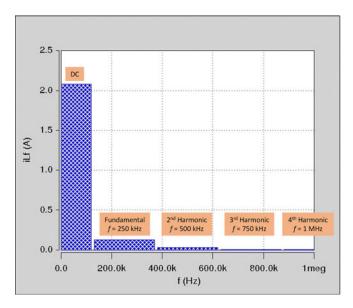

A class-E power inverter was designed, built, and tested to verify the theoretical predictions. For the specifications given in the previous section, the values of the inverter components were obtained as follows [26]: choke inductance  $L_f = 40 \,\mu\text{H}$ (as calculated earlier), shunt capacitor  $C_1 = 81.05$  nF, resonant capacitor C = 49.89 nF, resonant inductor  $L = 9.81 \,\mu\text{H}$ , and load resistor  $R = 1.44 \Omega$ . The circuit was simulated and the Fourier analysis of the choke inductor current was captured. Fig. 3 shows the simulated frequency spectrum of the choke inductor current showing the dc, fundamental, second, third, and fourth harmonics. Two main conclusions can be made: 1) the dc current component of the choke current is significantly larger than the amplitude of the fundamental component and 2) the amplitudes of the higher order harmonics are relatively smaller than the fundamental, decreases with frequency, and, therefore, can be neglected in estimating the inductor power loss. The even harmonics are present, however, they have negligible amplitudes, because the choke inductor current waveform has exponentially rising and falling edges.

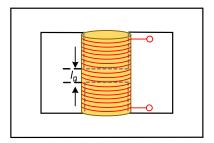

The choke inductor was built using the selected core and winding conductor discussed in Section III-B. A conceptual representation of the cross-sectional view of the choke inductor with gapped core is shown in Fig. 4. First, the ac characteristics were measured to ensure whether the operating frequency of the choke exists within the useful range of frequencies, where only the inductive properties are dominant. An HP4194A impedance/gain-phase analyzer was used to capture

Fig. 3. Simulated frequency spectrum obtained using Fourier analysis of the choke inductor current.

Fig. 4. Conceptual representation of the choke inductor with gapped core.

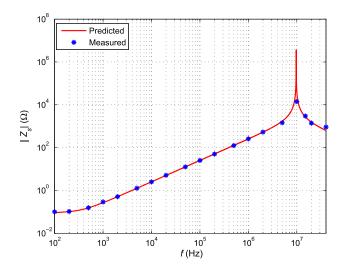

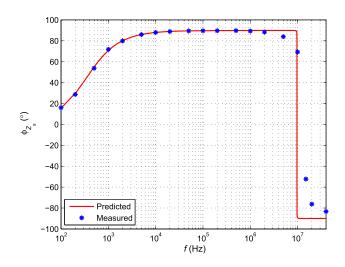

the measurement data. The instrument was capable of measuring the impedance up to 40 MHz. The measured low-frequency inductance was  $L_f \approx 48 \,\mu\text{H}$ . The measured dc winding resistance was  $R_{\rm wdc} = 33.33 \text{ m}\Omega$  at the choke operating temperature T = 38 °C. The calculated value of the dc winding resistance at the choke operating temperature was  $R_{wdc} = 28.48 \,\mathrm{m}\Omega$ . A difference of  $4.85 \,\mathrm{m}\Omega$  could be attributed to the lead and parasitic resistances of the winding and the measuring equipment, respectively. The subsequent results to validate the theory takes into account the measured dc winding resistance. The measured dc current through the choke inductor was  $I_{Lf} = 2.173$ A. Hence, the power loss in the choke due to dc current was  $P_{Rwdc} = I_{Lf}^2 R_{wdc} = 157.4$  mW. As shown in Section III-B and -C, the winding power loss due to the ac component of the inductor current  $P_{wac}$  and the core loss  $P_{Cg}$  were much lower than the winding dc power loss  $P_{Rwdc}$ . The choke power loss was less than 5.7% of the overall power loss of the class-E inverter. Fig. 5 compares the theoretical and experimental plots of magnitude of the impedance of the inductor. The measured resonant frequency was observed at  $f_0 = 10.2$  MHz and the theoretically estimated value is 9.72 MHz. At the operating frequency of the described circuit, the impedance is  $|Z_s| \approx 70 \,\Omega$ , which is nearly 50 times higher than the load resistance. Fig. 6

Fig. 5. Theoretically predicted and measured magnitudes of the inductor impedance as a function of frequency.

Fig. 6. Theoretically predicted and measured phases of the inductor impedance as a function of frequency.

shows a comparison of the theoretical and experimental plots of phase of the inductor impedance. At dc and very low frequencies, the impedance is dominated primarily by the dc winding resistance. With increase in frequency, the inductive characteristics are dominant. At frequencies beyond the resonant frequency, the self-capacitance dominates the inductance and the phase rolls off to -90°. If frequency-dependent winding resistance  $R_w$  and inductance  $L_f$  are used,  $Z_s$  and  $\phi_{Z_s}$  remain unchanged.

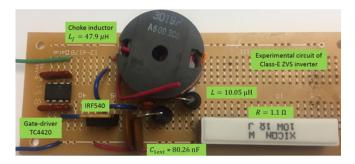

The components used in the experiments are summarized in Table I. The IRF540 silicon n-type power transistor with maximum drain-to-source voltage  $V_{\rm DSM}=100\,$  V, maximum drain current  $I_{\rm DM}=20\,$  A, and output capacitance  $C_o=C_{\rm oss}-C_{\rm rss}=560-120=440\,$  pF was considered. The transistor was driven by a low-side high-speed gate-driver TC4420 by Microchip Technology. Fig. 7 shows the photograph of the laboratory prototype of the class-E inverter including the choke inductor built and tested in the previous section. Fig. 8 shows

TABLE I

COMPONENTS USED IN EXPERIMENTS

| Component                     | Calculated           | Measured                                                |

|-------------------------------|----------------------|---------------------------------------------------------|

| $\overline{L_f}$              | 40 μΗ                | 48 μΗ                                                   |

| MOSFET                        | •                    | IRF540                                                  |

| $C_{1\text{ext}} = C_1 - C_o$ | 80.9 nF              | $80.26 \text{ nF, esr} = 26.2 \text{ m}\Omega$          |

| L                             | $9.81 \mu\mathrm{H}$ | $10.05 \mu\text{H},  \text{esr} = 29.98 \text{m}\Omega$ |

| C                             | 49.89 nF             | 50.09 nF, esr = $16.2$ mΩ                               |

| R                             | $1.44\Omega$         | $1.52\Omega$                                            |

Fig. 7. Photograph of the circuit used in experiments.

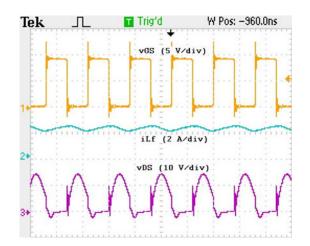

Fig. 8. Experimentally obtained waveforms of gate-to-source voltage  $v_{\rm GS}$  (upper trace), choke inductor current  $i_{Lf}$  (middle trace), and drain-to-source voltage  $v_{\rm DS}$  (lower trace).

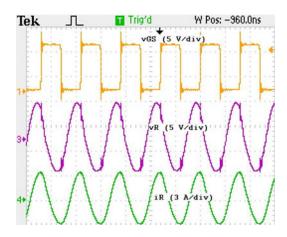

the experimentally obtained waveforms for the gate-to-source voltage  $v_{\rm GS}$ , choke inductor current  $i_{Lf}$ , and drain-to-source voltage  $v_{\rm DS}$ . The duty cycle was set at 50%. The average choke inductor current was measured as  $I_{Lf}=2.21$  A. The ac component was  $I_{Lfm}=0.35$  A. The maximum drain-to-source voltage was  $V_{\rm DSM}\approx 18$  V. The drain-to-source voltage reduces to zero before MOSFET turn-ON. Fig. 9 shows the waveforms of load voltage and load current. The amplitude of the output voltage was  $V_{Rm}=5.45$  V and the amplitude of the output current was 2.92 A. The load power is  $P_O=V_{Rm}^2/(2R)=5.45^2/(2\times 1.52)=9.77$  W. The input current was measured as  $I_I=I_{Lf}=2.105$  A. At an input voltage  $V_I=5$  V, the input power is  $P_I=V_II_{Lf}=5\times 2.105=10.525$  W. The measured efficiency was  $\eta=P_O/P_I\approx 93\%$ .

Fig. 9. Experimentally obtained waveforms of gate-to-source voltage  $v_{GS}$  (upper trace), load voltage  $v_R$  (middle trace), and load current  $i_R$  (lower trace).

#### VI. CONCLUSION

This paper has presented the design procedure for the choke used in class-E ZVS power inverters using the area-product method. The area-product method was compared with the  $K_g$ method. A gapped core has been selected to avoid core saturation. The core power loss has been evaluated through a modified Steinmetz equation for gapped cores. The ac component of the flux density was reduced significantly by the placing an air gap resulting in a low core power loss. The ac resistance of solid round winding has been determined using Dowell's equation. The dc and ac winding power losses due to the dc and ac fundamental choke current components have been determined. It has been shown that the ac winding loss is significantly lower than the dc winding loss and can be neglected for the design presented in this paper. The dc winding loss is also higher than the core power loss for the designed choke. Thus, the power loss due to the dc choke inductor current is the dominant loss component. The Fourier analysis result has revealed that the dc component of the current through the choke is dominant compared to the fundamental and the harmonics. Therefore, the power loss due to the harmonics in the choke inductor current can be neglected. The self-capacitance has been determined and can be included in the shunt capacitor of the class-E inverter. The contributions of this paper are as follows.

- A systematic procedure to design the choke inductor for switched-mode inverters, namely, class-E ZVS inverter has been introduced. The procedure involves the design of the choke using the area-product (A<sub>p</sub>) method, which combines both the electrical and the mechanical properties of the magnetic core and the winding.

- 2) Previous works on choke design were performed using the geometry coefficient method or the K<sub>g</sub> method by Sekiya et al. The results are very useful as they provide a good description of core power losses and mechanical specifications. However, there is a huge gap in the literature in the area of choke design using the area-product method, which is vital for core selection from many core distributors such as Magnetics, Inc. These distributors

- list  $A_p$  as the core selection criterion. Therefore, the rigorous procedure for choke design, which computes the required  $A_p$ , identify the appropriate core material, size, and shape, and evaluate the choke performance has been presented in this paper.

- 3) The outcome of the area product  $A_p$  method is a magnetic core identical or smaller in volume to that obtained through the core geometry coefficient method  $(K_g)$ .

- 4) The ac characteristics of the choke inductor have been evaluated and measured. This is very important for inverters such as class-E inverter, where the total transistor shunt capacitance plays a critical role in ensuring ZVS operation. By estimating the self-capacitance of the designed choke inductor, the total value of the external shunt capacitance can be determined, which has not been previously reported through analytical means for the class-E inverter. Also, the bandwidth of the inductors that shows a good performance over a range of frequencies has also been presented.

Future work can be to extend the presented methodology for the design of chokes in other switched-mode inverters and radiofrequency power amplifiers and study for design optimization.

#### **REFERENCES**

- C. W. T. McLyman, Transformer and Inductor Design Handbook, 3rd Ed. New York, NY, USA: Marcel Dekker, 2004.

- [2] M. K. Kazimierczuk, High-Frequency Magnetic Components, 2nd. Ed. Chichester, U.K.: Wiley, 2014.

- [3] P. L. Dowell, "Effect of Eddy currents in transformer windings," Proc. Inst. Elect. Eng., vol. 113, no. 8, pp. 1387–1394, 1966.

- [4] H. Sekiya and M. K. Kazimierczuk, "Design of RF-choke inductors using core geometry coefficient," in *Proc. Elect. Manuf. Coil Winding Conf.*, Nashville, TN, USA, Sep. 2009.

- [5] M. K. Kazimierczuk and H. Sekiya, "Design of ac resonant inductors using area product method," in *Proc. IEEE Energy Convers. Congr. Exhib.*, San Jose, CA, USA, Sep. 2009, pp. 994–1001.

- [6] Z. Zhang, K. D. T. Ngo, and J. L. Nilles, "Design of inductors with significant AC flux," *IEEE Trans. Power Electron.*, vol. 32, no. 1, pp. 529–539, Jan. 2017.

- [7] B. J. Lyons, J. G. Hayes, and M. G. Egan, "Magnetic material comparisons for high-current inductors in low-medium frequency DC-DC converters," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, Anaheim, CA, USA, 2007, pp. 71–77.

- [8] C. P. Steinmetz, "On the law of hysteresis," *Proc. IEEE*, vol. 72, no. 1, pp. 197–221, Feb. 1984.

- [9] A. Ayachit and M. K. Kazimierczuk, "Steinmetz equation for gapped magnetic cores," *IEEE Magn. Lett.*, vol. 7, May 2016.

- [10] A. Ayachit and M. K. Kazimierczuk, "Sensitivity of effective permeability for gapped magnetic cores with fringing effect," *IET Circuits, Devices* Syst., vol. 11, no. 3, pp. 209–215, May 2017.

- [11] J. Zhang, W. G. Hurley, and W. H. Wolfle, "Gapped transformer design methodology and implementation for LLC resonant converters," *IEEE Trans. Ind. Appl.*, vol. 52, no. 1, pp. 342–350, Jan. 2016.

- [12] L. Dalessandro, W. G. Odendaal, and J. W. Kolar, "HF characterization and non-linear modeling of a gapped toroidal magnetic structure," *IEEE Trans. Power Electron.*, vol. 21, no. 5, pp. 1167–1175, Sep. 2006.

- [13] W. Chen, J. He, H. Luo, Y. Hu, and C.-C. Wen, "Winding loss analysis and new air-gap arrangement for high-frequency inductors," in *Proc. IEEE Power Electron. Spec. Conf.*, Vancouver, BC, USA, 2001, vol. 4, pp. 2084–2089

- [14] R. P. Wojda and M. K. Kazimierczuk, "Analytical winding size optimization of solid-round-wire windings," *IEEE Trans. Ind. Electron.*, vol. 60, no. 3, pp. 1033–1041, Mar. 2013.

- [15] R. P. Wojda and M. K. Kazimierczuk, "Analytical optimisation of solid-round-wire windings conducting dc and ac non-sinusoidal periodic currents," *IET Power Electron.*, vol. 6, no. 7, pp. 1462–1474, Jul. 2013.

- [16] D. Murthy-Bellur and M. K. Kazimierczuk, "Harmonic winding loss in buck DC-DC converter in discontinuous conduction mode," *IET Power Electron.*, vol. 3, no. 5, pp. 740–754, Sep. 2010.

- [17] D. Murthy-Bellur et al., "Transformer winding loss caused by skin and proximity effects including harmonics in PWM DC-DC flyback converter for continuous conduction mode," *IET Power Electron.*, vol. 4, no. 4, pp. 363–373, Apr. 2011.

- [18] J. D. Lavers and V. Bolborici, "Loss comparison in the design of high frequency inductors and transformers," *IEEE Trans. Magn.*, vol. 35, no. 5, pp. 3541–3543, Sep. 1999.

- [19] R. P. Wojda and M. K. Kazimierczuk, "Winding resistance of litz-wire and multi-strand inductors," *IET Power Electron.*, vol. 5, no. 2, pp. 257–268, Feb. 2012.

- [20] M. Bartoli, A. Reatti, and M. K. Kazimierczuk, "High-frequency models of ferrite inductors," in *Proc. 20th Int. Conf. IEEE Ind. Electron.*, Control Instrum., Bologna, Italy, Sep. 1994, pp. 1670–1675.

- [21] N. Simpson, R. Wrobel, and P. H. Mellor, "Multi-physics design of high-energy density wound components," in *Proc. IEEE Energy Convers. Congr. Expo.*, Montreal, QC, USA, Sep. 2015, pp. 3857–3864.

- [22] G. Grandi, M. K. Kazimierczuk, A. Massarini, U. Reggiani, and G. Sancineto, "Model of laminated iron-core inductors for high frequencies," *IEEE Trans. Magn.*, vol. 40, no. 4, pp. 1839–1845, Jul. 2004.

- [23] S. W. Pasko, M. K. Kazimierczuk, and B. Grzesik, "Self-capacitance of coupled toroidal inductor for EMI filters," *IEEE Trans. Electromagn. Compat.*, vol. 57, no. 2, pp. 216–223, Apr. 2015.

- [24] A. Ayachit and M. K. Kazimierczuk, "Self-capacitance of single-layer inductors with separation between conductor turns," *IEEE Trans. Electromagn. Compat.*, vol. 59, no. 5, pp. 1642–1645, Oct. 2017.

- [25] A. F. Witulski, "Introduction to modeling of transformers and coupled inductors," *IEEE Trans. Power Electron.*, vol. 10, no. 3, pp. 349–357, May 1995.

- [26] M. K. Kazimierczuk, Radio-Frequency Power Amplifiers, 2nd Ed. Chichester, U.K.: Wiley, 2015.

- [27] S. H. Lee and R. D. Lorenz, "Development and validation of model for 95%-efficiency 220-W wireless power transfer over a 30 cm air gap," *IEEE Trans. Industry Appl.*, vol. 47, no. 6, pp. 2495–2504, Nov. 2011.

- [28] Q. Deng et al., "Frequency-dependent resistance of litz-wire square solenoid coils and quality factor optimization for wireless power transfer," *IEEE Trans. Ind. Electron.*, vol. 63, no. 5, pp. 2825–2837, May 2016.

- [29] M. Mu, Q. Li, D. J. Gilham, F. C. Lee, and K. D. T. Ngo, "New core loss measurement method for high-frequency magnetic materials," *IEEE Trans. Power Electron.*, vol. 29, no. 8, pp. 4374–4381, Aug. 2014.

- [30] A. Ayachit, D. K. Saini, M. K. Kazimierczuk, and A. Reatti, "Design of choke inductor in class-E ZVS power amplifier," in *Proc. 42nd Annu. Conf. IEEE Ind. Electron. Soc.*, Florence, Italy, Oct. 23–26, 2016, pp. 5621–5626.

- [31] American Wire Gauge (AWG) Datasheet, 2007. [Online]. Available: https://www.micrometals.com

- [32] Magnetics Ferrite Cores, 2013 Catalog. [Online]. Available: htttps://www.mag-inc.com

**Dalvir K. Saini** received the B.S. and M.S. degrees in electrical engineering from Wright State University, Dayton, OH, USA, in 2013 and 2015, respectively. She is currently working towards the Ph.D. degree in electrical engineering at Wright State University, Dayton, OH, USA.

She has served as an intern at Air Force Research Lab, Dayton, OH, USA and Graduate Research Assistant at Wright State University. She is also serving as a Graduate Teach-

ing Assistant in the Department of Electrical Engineering, Wright State University. Her research interests include high-frequency magnetic component design, RF power amplifiers, modeling and control of power electronic converters, and wide-band gap semiconductor devices.

Mrs. Saini received the Graduate Student Excellence Award in 2015 for her outstanding academic record.

Agasthya Ayachit received the B.S degree in electrical and electronics engineering from a Visvesvaraya Technological University-affiliated institution in Bangalore, India, in 2009, the M.S. degree in electrical engineering from Wright State University, Dayton, OH, USA, in 2010. He is currently working towards the Ph.D. degree in electrical engineering at Wright State University.

After 2010 he served as a Lecturer at Pennsylvania State University. He has interned at GE Global Research, Mediatek, Inc., and Google,

Inc., where he worked on the design, development, and testing of high-frequency power systems. He is currently serving as Graduate Teaching Assistant in the Department of Electrical Engineering. His research interests include modeling of dc–dc PWM and resonant converters, wireless power charging, magnetic component design, and RF power amplifiers.

Alberto Reatti (M'91–00 and M'13) received the Masters degree in electronics engineering from the University of Florence, Florence, Italy, in 1988 and the Ph.D. degree in high-frequency resonant power converters from the University of Bologna, Bologna, Italy, 1993.

In 1992, he was an Associate Researcher in the Department of Electrical Engineering, Wright State University, Dayton, OH, USA. In 1994, he was a Visiting Professor in the Department of Electronics, University of Siena, Siena, Italy. For

several years, he has also been a Visiting Professor in the Department of Electronics, University of Florence, where he is currently an Associate Professor in the Department of Information Engineering. His research interests include high-frequency, resonant and pulse-width modulated dc–dc power converters, dc–ac inverters, high-frequency rectifiers, electronic ballasts, modeling and control of converters, high-frequency magnetic, and power semiconductor devices, and renewable power sources. He is also responsible for agreement of cultural and scientific cooperation. He has published more than 100 technical papers, including papers appeared in IEEE Transactions and Journals. He also holds two patents. One of this patents allowed him to be selected as a member of a University of Florence spinoff company.

Dr. Reatti served as a Chairman of the Power Electronic and Power Systems Committee of IEEE CAS Society and as an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: REGULAR PAPERS.

Marian K. Kazimierczuk (M'91–SM'91–F'04) received the M.S., Ph.D., and D.Sci. degrees in electronics engineering from the Department of Electronics, Warsaw University of Technology, Warsaw, Poland, in 1971, 1978, and 1984, respectively.

From 1972 to 1978, he was a Teaching and Research Assistant in the Department of Electronics, Institute of Radio Electronics, Warsaw University of Technology, where he was an Assistant Professor from 1978 to 1984. In 1984, he

was a Project Engineer with Design Automation, Inc., Lexington, MA, USA. From 1984 to 1985, he was a Visiting Professor in the Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University, Blacksburg, VA, USA. Since 1985, he has been in the Department of Electrical Engineering, Wright State University, Dayton, OH, USA, where he is currently a University Distinguished Professor. He is the author/coauthor of 7 books, 200 journal papers, and 250 conference papers, and holds 8 patents. His research interests include high-frequency high-efficiency switching-mode tuned power amplifiers, resonant and pulsewidth-modulated dc/dc power converters, dc/ac inverters, high-frequency rectifiers, electronic ballasts, modeling and control of converters, high-frequency magnetics, wireless power transfer, renewable energy sources, and wide-band gap power semiconductor devices.

Dr. Kazimierczuk served as an Associate Editor for the IEEE TRANS-ACTIONS ON CIRCUITS AND SYSTEMS and the *Journal of Circuits, Systems* and *Computers*, and serves as an Associate Editor for the IEEE TRANS-ACTIONS ON INDUSTRIAL ELECTRONICS, the *International Journal of Circuits Theory and Applications*, and *IET Circuits, Devices and Systems*.