Analysis and Optimization of Accumulation-Mode Varactor for RF ICs

T. Soorapanth, C.P. Yue, D.K. Shaeffer, T.H. Lee, and S.S. Wong

> Center for Integrated Systems Stanford University, CA, USA

# Outline

- Introduction

- Operation

- Characterization

- Optimization

- Conclusion

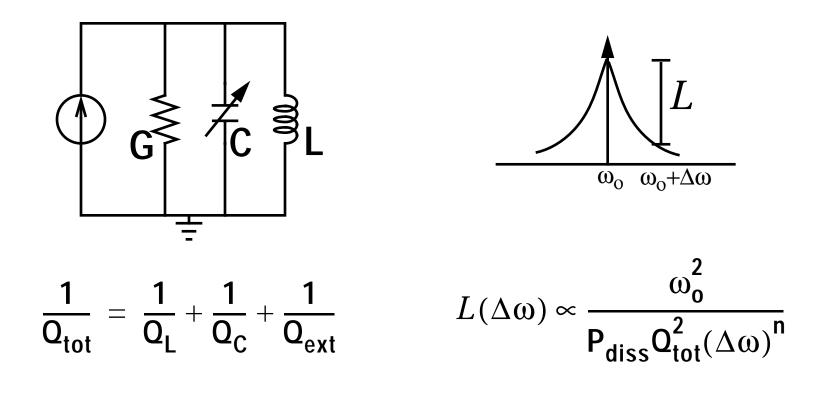

## **Phase Noise in VCOs**

- Q<sub>L</sub> ~ 4-8 for 1-10 nH spiral inductor.

- Need  $Q_C > 40-80$  to minimize  $Q_{tot}$  degradation.

# **Conventional IC Varactors**

|                 | <b>PN junction</b>                  | MOS capacitor                                 |

|-----------------|-------------------------------------|-----------------------------------------------|

| Bias            | reverse                             | depletion-inversion                           |

| С               | moderate (0.4 fF/um <sup>2</sup> )* | high (2-7 fF/um <sup>2</sup> )                |

| Q               | low (5-7 for 1-10 pF) <sup>*</sup>  | moderate (14/GHz/pF)*                         |

| Tuning<br>range | small (33%) <sup>*</sup>            | moderate (parasitic S/D junction cap limited) |

| f <sub>SR</sub> | 4-13 GHz <sup>*</sup>               | 8 GHz for 2 pF <sup>*</sup>                   |

| TC              | high (200-1000 ppm/C)               | moderate (30 ppm/C)                           |

\* [Burghartz, et.al., TED '96]

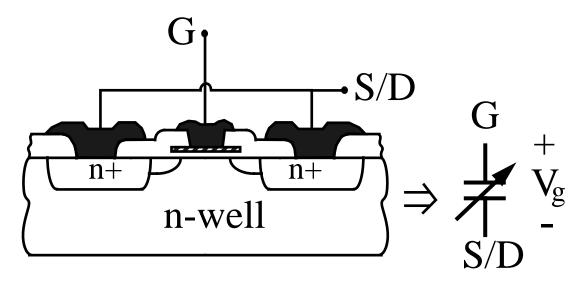

# **Accumulation-Mode Varactor**

- Standard CMOS process

- Reduce parasitic S/D junction capacitance

- High C per area (increases with technology scaling)

- High Q (increases with technology scaling)

- High tuning range (improves with technology scaling, 200% maximum limit)

- Moderate TC

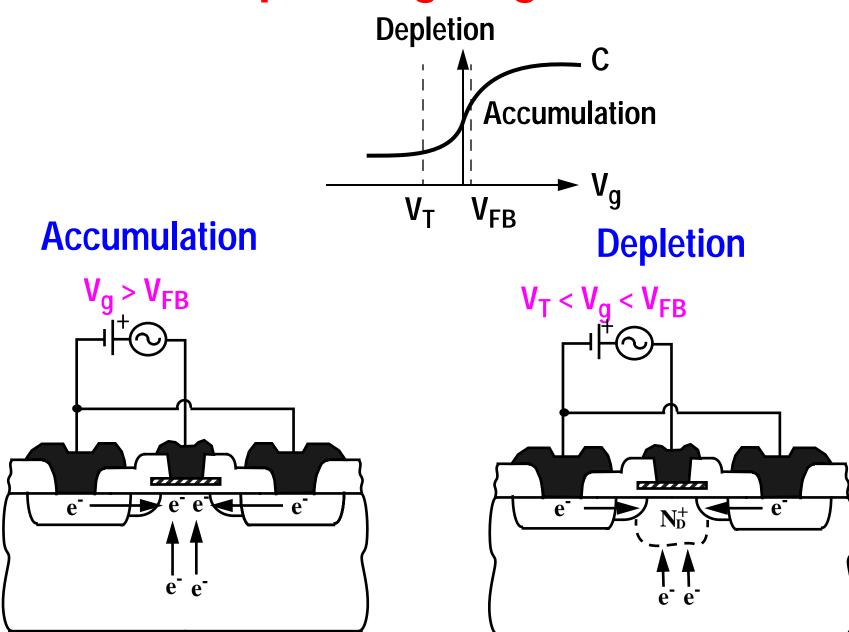

# **Operating Regimes**

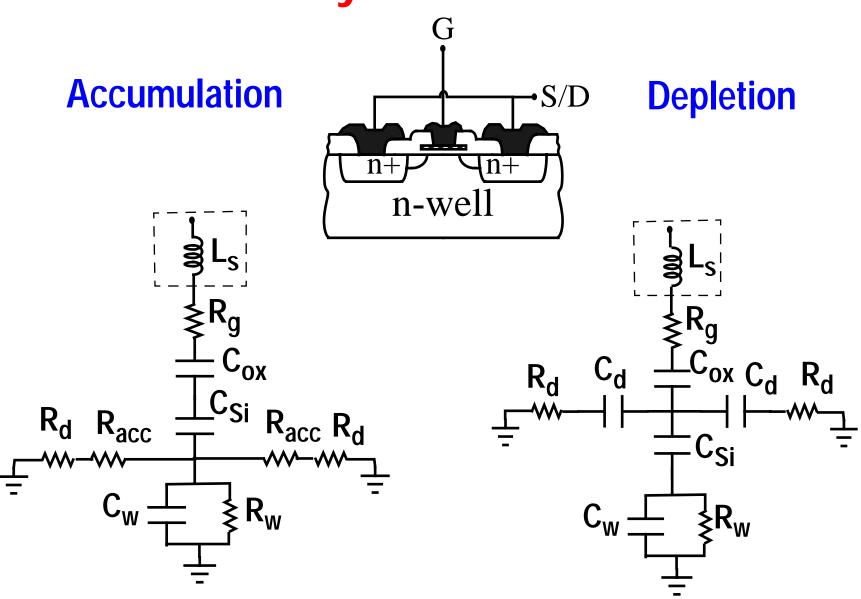

### **Physical Model**

# **Physical Model Parameters**

| <b>Parameters</b>                                 | Expression                                                                                                                                                                          | Description                       |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| C <sub>ox</sub>                                   | NWL <sub>eox</sub><br>tox                                                                                                                                                           | oxide capacitance                 |

| C <sub>Si</sub> (u <sub>s</sub> ,u <sub>b</sub> ) | $\frac{NWL\epsilon_{Si}}{L_{di}} \left(\frac{\sinh(u_s) - \sinh(u_b)}{F(u_s, u_b)}\right)$ $F(u_s, u_b) = \sqrt{2} \left[\sinh u_b(u_b - u_s) - \cosh u_b - \cosh u_s\right]^{1/2}$ | semiconductor<br>capacitance      |

| C <sub>d</sub>                                    | NWX <sub>jldd</sub> Csi <sup>(u</sup> s <sup>, u</sup> ldd <sup>)</sup>                                                                                                             | channel-to-S/D<br>depletion cap   |

| R <sub>acc</sub>                                  | $Q_{acc} = \varepsilon_{Si} \left(\frac{kT}{qL_{di}}\right) F(u_{s}, u_{b})$                                                                                                        | accumulation-<br>layer resistance |

| R <sub>g</sub> , R <sub>w</sub>                   | $\frac{R_{gsq}W}{3NL}, \frac{R_{wsq}L_{w}}{2NW}$                                                                                                                                    | gate and well<br>resistance       |

| R <sub>d</sub>                                    | $\frac{R_{Iddsq}^{L}Idd}{NW} + R_{contact}$                                                                                                                                         | LDD and contact<br>resistance     |

## **Series Capacitance**

┝━╱┉╱┥╞━●

$C_{\varsigma}$

**Accumulation**

$$C_s = \frac{C_{ox}C_{si}}{C_{ox} + C_{si}}$$

C<sub>Si</sub> in accumulation is associated with accumulation-layer charge (e<sup>-</sup>).

$$C_{s} = \frac{C_{ox}(C_{si} + 2C_{d})}{C_{ox}(C_{si} + 2C_{d})}$$

C<sub>Si</sub> in depletion is depletion capacitance associated with fixed donor charge (N<sub>D</sub><sup>+</sup>).

$C_s$  varies with bias voltage as  $C_{Si}$ ,  $C_d$  are bias-dependent.

## **Series Resistance (Varactor Loss)** R<sub>s</sub> **Accumulation Depletion** $R_{s} \cong \left( R_{g} + \left[ \frac{1}{2} (R_{acc} + R_{d}) || R_{w} \right] \right) \qquad R_{s} \cong R_{g} + R_{w} \left( \frac{C_{si}}{C_{si} + 2C_{d}} \right)^{2}$ $\cong \frac{R_{acc}}{2} \| R_{W}$ $\cong R_{W} \left( \frac{C_{Si}}{C_{Ci} + 2C_{i}} \right)^{2}$

• R<sub>s</sub> can be reduced by controlling device geometry.

R<sub>s</sub> varies with bias voltage as R<sub>acc</sub>, C<sub>Si</sub>, and C<sub>d</sub> are bias-dependent.

# Quality Factor (Q) $R_{s} C_{s}$ $M \rightarrow H$ $Q = \frac{1}{\omega R_{s} C_{s}}$

- Frequency-dependent.

- Bias-dependent as R<sub>s</sub>, C<sub>s</sub> varies with bias.

# **Tuning Range**

- Tuning range =  $\frac{2C_{ox}}{C_{ox} + 2C_{Si, min}} \Rightarrow 200\%$  @ maximum limit.

- As technology scales, tuning range increases towards the limit.

- When used with low-TC capacitor (eg. MIM capacitor) temperature stability can be improved by trading-off with tuning range.

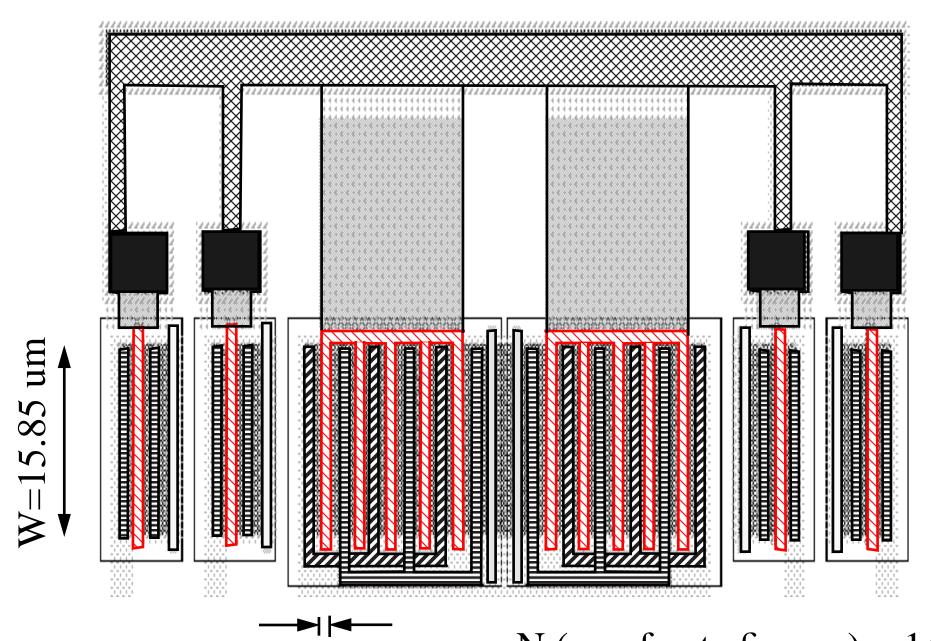

#### **Test Structure**

L=1.95 um

N (no of gate fingers) = 14

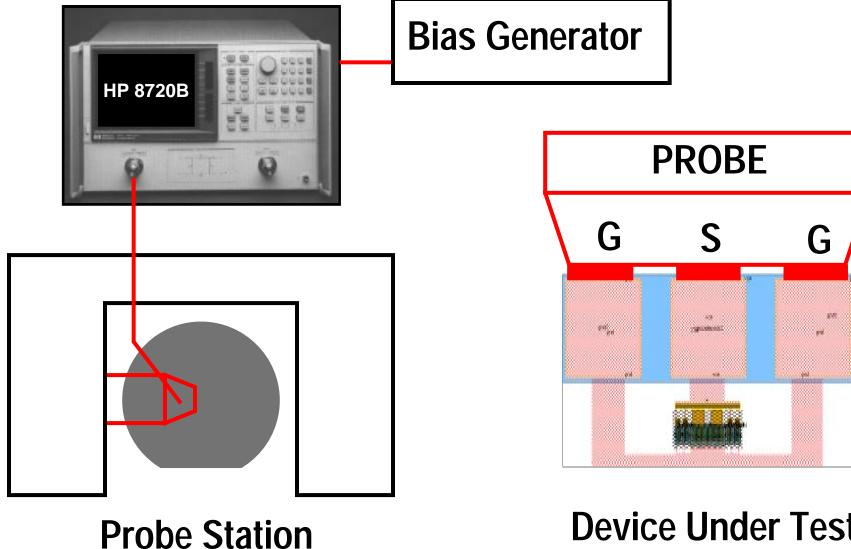

# **Measurement Setup**

**Device Under Test**

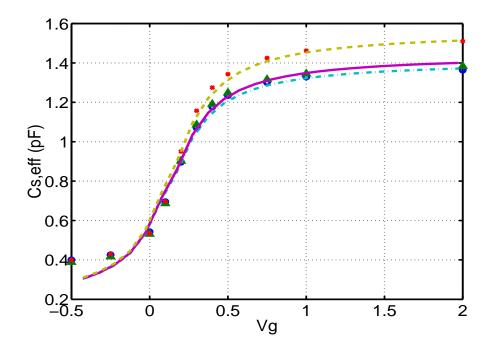

## Measured Series Capacitance

- Measured 1 GHz 0 0

- Measured 2.5 GHz

- Measured 5 GHz XX

- Modeled 1 GHz

- Modeled 2.5 GHz

- Modeled 5 GHz

- At V<sub>g</sub> >> V<sub>FB</sub>, C  $\approx$  C<sub>ox</sub> At V<sub>g</sub> < V<sub>FB</sub>, C  $\approx \frac{C_{ox}C_{Si}}{C_{ox} + C_{Si}}$

- Exhibit frequency dependence associated with parasitic

inductance =>

$$C_{s, eff} = \frac{C_s}{1 - \omega^2 L_s C_s}$$

$f_{SR} \ge 15 GHz$

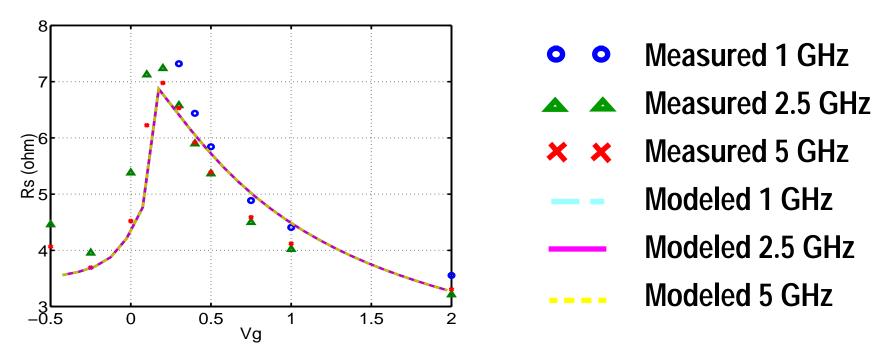

## **Measured Series Resistance**

- In accumulation, R<sub>s</sub> increases as V<sub>g</sub> is swept from deep accumulation towards flatband due to extraction of accumulation-layer charges.

- In depletion, R<sub>s</sub> decreases beyond flatband due to the decrease of C<sub>Si</sub> which reduces the effect of R<sub>w</sub>.

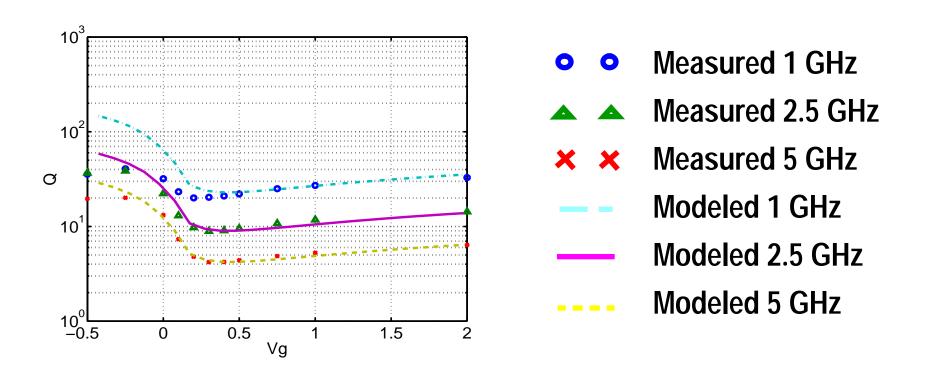

# **Measured Quality Factor**

- Q reaches minimum at flatband voltage where changes in capacitance is large.

- ==> trade-off between Q and capacitance tuning.

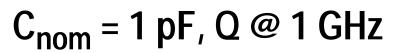

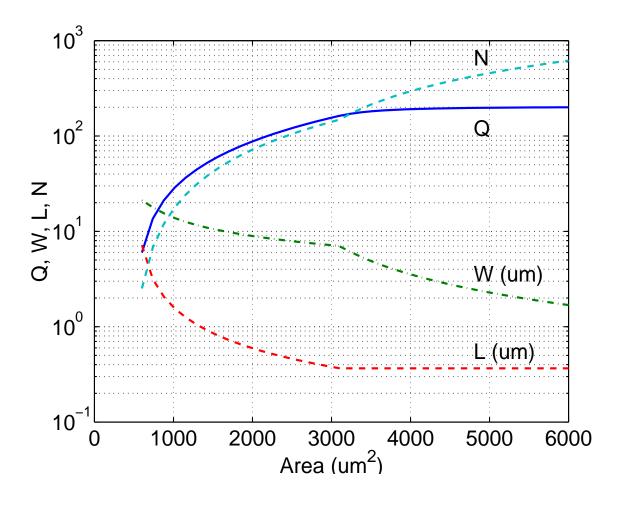

# **Optimization Formulation**

**Objective : maximize Q subject to following constraints**

- C = nominal desired capacitance (1 pF)

- Area < max allowed area

- Tuning range > min required tuning range (+/- 30%)

- W > min allowed channel width (0.6 um)

- L > min allowed channel length (0.4 um)

- N > min no of gate finger (1)

- Biased in accumulation mode (to minimize substrate effect) ( $V_g > V_{FB}$ )

**Optimization variables : W, L, N, V**<sub>g</sub>

# **Optimization Results (0.5 µm CMOS)**

Q<sub>max</sub>=200!!

# Conclusions

- Standard CMOS implementation.

- Varactor model has been developed and used for device optimization.

- Substrate effect can be mitigated by operating in accumulation mode.

- Wide tuning range allows trade-off with temperature stability.

- Performance improves with technology scaling.