Open access • Journal Article • DOI:10.1109/TCSVT.2004.842620

# Analysis, fast algorithm, and VLSI architecture design for H.264/AVC intra frame coder — Source link ☑

Yu-Wen Huang, Bing-Yu Hsieh, Tung-Chien Chen, Liang-Gee Chen

Institutions: National Taiwan University

Published on: 01 Mar 2005 - IEEE Transactions on Circuits and Systems for Video Technology (IEEE)

Topics: Context-adaptive variable-length coding, Macroblock, Discrete cosine transform, Intra-frame and

Hadamard transform

# Related papers:

- Overview of the H.264/AVC video coding standard

- Fast mode decision algorithm for intraprediction in H.264/AVC video coding

- Rate-constrained coder control and comparison of video coding standards

- A Fast Mode Decision Algorithm and Its VLSI Design for H.264/AVC Intra-Prediction

- · A High-Definition H.264/AVC Intra-Frame Codec IP for Digital Video and Still Camera Applications

# Analysis, Fast Algorithm, and VLSI Architecture Design for H.264/AVC Intra Frame Coder

Yu-Wen Huang, Bing-Yu Hsieh, Tung-Chien Chen, and Liang-Gee Chen, Fellow, IEEE

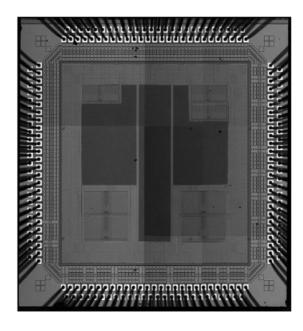

Abstract-Intra prediction with rate-distortion constrained mode decision is the most important technology in H.264/AVC intra frame coder, which is competitive with the latest image coding standard JPEG2000, in terms of both coding performance and computational complexity. The predictor generation engine for intra prediction and the transform engine for mode decision are critical because the operations require a lot of memory access and occupy 80% of the computation time of the entire intra compression process. A low cost general purpose processor cannot process these operations in real time. In this paper, we proposed two solutions for platform-based design of H.264/AVC intra frame coder. One solution is a software implementation targeted at low-end applications. Context-based decimation of unlikely candidates, subsampling of matching operations, bit-width truncation to reduce the computations, and interleaved full-search/partial-search strategy to stop the error propagation and to maintain the image quality, are proposed and combined as our fast algorithm. Experimental results show that our method can reduce 60% of the computation used for intra prediction and mode decision while keeping the peak signal-to-noise ratio degradation less than 0.3 dB. The other solution is a hardware accelerator targeted at high-end applications. After comprehensive analysis of instructions and exploration of parallelism, we proposed our system architecture with four-parallel intra prediction and mode decision to enhance the processing capability. Hadamard-based mode decision is modified as discrete cosine transform-based version to reduce 40% of memory access. Two-stage macroblock pipelining is also proposed to double the processing speed and hardware utilization. The other features of our design are reconfigurable predictor generator supporting all of the 13 intra prediction modes, parallel multitransform and inverse transform engine, and CAVLC bitstream engine. A prototype chip is fabricated with TSMC 0.25-\(\mu\mathrm{m}\) CMOS 1P5M technology. Simulation results show that our implementation can process 16 mega-pixels (4096  $\times$  4096) within 1 s, or namely  $720 \times 480$  4:2:0 30 Hz video in real time, at the operating frequency of 54 MHz. The transistor count is 429 K, and the core size is only  $1.855 \times 1.885$  mm<sup>2</sup>.

Index Terms—Intra frame coder, ISO/IEC 14496-10 AVC, ITU-T Rec. H.264, Joint Video Team (JVT), VLSI architecture.

Manuscript received November 6, 2003; revised February 9, 2004. The work of Y.-W. Huang was supported by SiS Education Foundation Scholarship Program. This paper was recommended by Associate Editor S. Chen.

Y.-W. Huang and B.-Y. Hsieh are with the DSP/IC Design Laboratory, Graduate Institute of Electronics Engineering, Department of Electrical Engineering, National Taiwan University, Taipei 106, Taiwan, R.O.C., and also with MediaTek Incorporated, Hsinchu, Taiwan, R.O.C. (e-mail: yuwen@video.ee.ntu.edu.tw; BY\_Hsieh@mtk.com.tw).

T.-C. Chen and L.-G. Chen are with the DSP/IC Design Laboratory, Graduate Institute of Electronics Engineering, Department of Electrical Engineering, National Taiwan University (NTU), Taipei 106, Taiwan, R.O.C. (e-mail:djchen@video.ee.ntu.edu.tw; lgchen@cc.ee.ntu.edu.tw).

Digital Object Identifier 10.1109/TCSVT.2004.842620

#### I. Introduction

he ITU-T Video Coding Experts Group (VCEG) and ISO/IEC 14496-10 AVC Moving Picture Experts Group (MPEG) formed the Joint Video Team (JVT) in 2001 to develop the new video coding standard, H.264/Advanced Video Coding (AVC) [1]. Compared with MPEG-4 [2], H.263 [3], and MPEG-2 [4], H.264/AVC can achieve 39%, 49%, and 64% of bit-rate reduction, respectively [5]. The improvement in coding performance comes mainly from the prediction part. Inter prediction is enhanced by motion estimation with quarter-pixel accuracy, variable block sizes, multiple reference frames, and improved spatial/temporal direct mode. Moreover, unlike the previous standards, prediction must be always performed before texture coding not only for inter macroblocks but also for intra macroblocks. When motion estimation fails to find a good match, intra prediction still has a good chance to further reduce the residues. Intra prediction also significantly improves the coding performance of H.264/AVC intra frame coder.

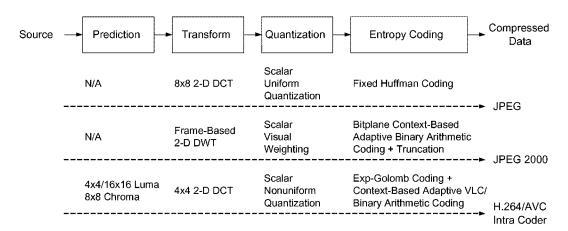

In 1992, the Joint Photographic Experts Group (JPEG) [6], the first international image coding standard for continuous-tone natural images, was defined. Nowadays, JPEG is a well-known image compression format in everyone's daily life because of the population of digital still camera, digital image scanner, and Internet. In 2001, the latest image coding standard, JPEG2000 [7], was finalized. Different from its preceding generation, JPEG, which is a Discrete Cosine Transform (DCT)-based Huffman coder, JPEG2000 adopts a wavelet-based arithmetic coder for better coding efficiency. Actually, JPEG2000 not only enhances the compression but also includes many new features, such as quality scalability, resolution scalability, region of interest, lossy, and lossless coding in a unified framework. In 2003, H.264/AVC was finalized and it provides a new way of still image coding. Fig. 1 shows the three image coding standards' core techniques and architectures. The prediction part is the most special part in H.264/AVC. A macroblock must be always predicted by its neighboring reconstructed pixels before texture coding.

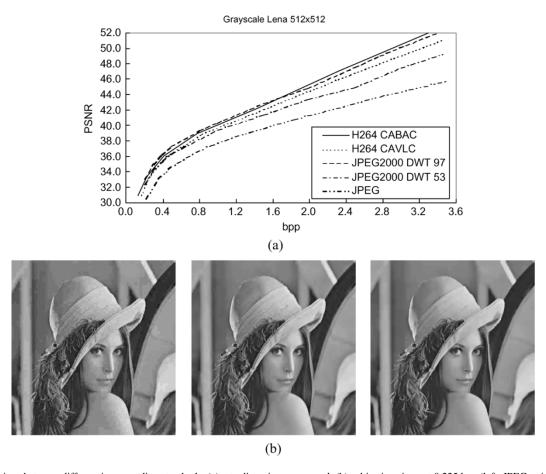

We first compare the compression performance between JPEG, JPEG2000, and H.264/AVC intra frame coder. The results are shown in both objective and subjective manners. Fig. 2(a) is the peak signal-to-noise ratio (PSNR) results under several different bit-rate. The test image is grayscale Lena, and the size is  $512 \times 512$ . Note that because H.264/AVC baseline/main profile only supports 4:2:0 format, we set the chroma components as zero. As can be seen from the rate-distortion curves, the performance of H.264/AVC intra frame coder using context-based adaptive binary arithmetic coding (CABAC) and high complexity mode decision is about the same as that of JPEG2000 using DWT 97 filter, and their performances are

Fig. 1. Core techniques adopted in different image coding standards under the basic coding architecture.

Fig. 2. Comparison between different image coding standards: (a) rate distortion curves and; (b) subjective views at 0.225 bpp (left: JPEG, middle: JPEG 2000 DWT53, right: H.264/AVC I-Frame CAVLC).

the best. H.264/AVC intra frame coder using context-based adaptive variable length coding (CAVLC) and low complexity mode decision is 0.5–1.0 dB worse than JPEG2000 DWT 97, but it is 0.1–1.8 dB better than JPEG2000 DWT 53. The coding performance of JPEG is significantly lower than other standards. Fig. 2(b) shows the subjective views at 0.225 bit/pixel (bpp). The block artifact of JPEG image is very obvious, and the other two images gives acceptable qualities without block artifact. JPEG2000 eliminates the block artifact by adopting DWT while H.264/AVC achieves it by deblocking. The image quality of H.264/AVC is very close to that of

TABLE I COMPARISON OF COMPUTATIONAL COMPLEXITY

| Standard  | Encode | Decode |

|-----------|--------|--------|

| JРЕG      | 544    | 298    |

| JPEG2000  | 3430   | 3180   |

| H.264/AVC | 3648   | 584    |

Units in million instructions

Test image: Bike,  $2048 \times 2560 \times 8b$

JPEG2000. Now we compare the computational complexities of the three standards. The instruction profiles are shown in Table I. The test image is  $2048 \times 2560$  grayscale Bike. The

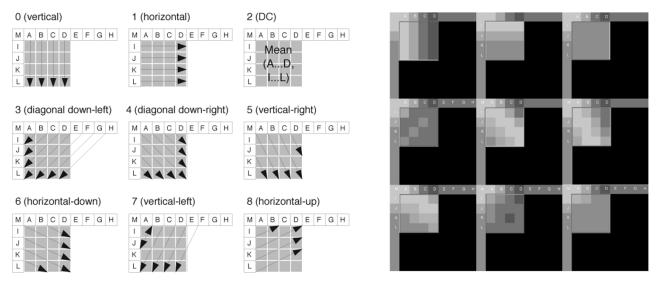

Fig. 3. I4MB; left: illustration of nine 4 × 4-luma prediction modes; right: examples of real images.

ratio of the encoder complexities for JPEG, JPEG2000 (DWT 53), and H.264/AVC intra frame coder (CAVLC and low complexity mode decision), respectively, is about 1:6:6, and the ratio of decoder complexities is about 1:10:2. The encoding complexity of H.264/AVC intracoder is about the same as that of JPEG2000, but the decoding complexity of H.264/AVC is much lower than that of JPEG2000. Moreover, H.264/AVC is a block-based algorithm, which is more hardware-friendly than JPEG2000. DWT is a frame-based transform and thus requires a huge amount of memory. The entropy coder of JPEG2000, embedded block coding with optimized truncation (EBCOT), is a sequential bitplane processing and requires a high operating frequency to meet the real-time constraint. JPEG2000 sequential mode can be replaced by parallel mode (arithmetic coder terminates at the end of each bitplane) in order to decrease the operating frequency with several bit-plane processing engines in parallel, but this may suffer 0.5–1.0-dB quality loss. Thus, for applications whose key functionality is compression instead of scalability, such as digital camera and digital scanner, H.264/AVC intra frame coder may be a more attractive solution. Besides, it can be directly reused for integration of H.264/AVC video coding.

In this paper, two solutions for platform-based design of H.264/AVC intra frame coder are proposed. One is a software implementation targeted at low-end applications, and the other is a hardware accelerator targeted at high-end applications. The rest of this paper is organized as follows. In Section II, the related background including the flow of mode decision in the reference software is reviewed. Section III describes our fast algorithm. Three speed-up methods are proposed. In Section IV, the architecture design of H.264/AVC intra frame coder including reconfigurable predictor generation, transform/inverse transform, quantization, CAVLC, and macroblock pipelining, is discussed. Finally, conclusions are drawn in Section V.

# II. FUNDAMENTALS

In this section, technical overview of H.264/AVC intra coding will be introduced.

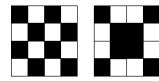

#### A. Intraprediction Modes

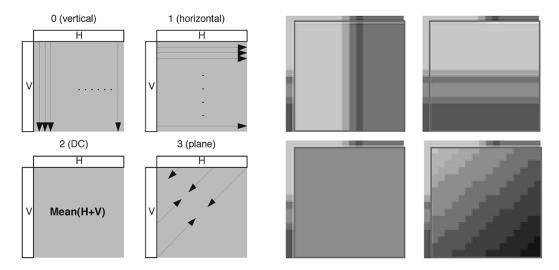

In H.264/AVC intra coding, two intramacroblock modes are supported. One is intra  $4 \times 4$  prediction mode, denoted as I4MB, and the other is intra  $16 \times 16$  prediction mode, denoted as I16MB. For I4MB, each  $4 \times 4$ -luma block can select one of nine prediction modes. In additional to dc prediction, eight directional prediction modes are provided. Fig. 3 shows the illustration of 4 × 4-luma prediction modes and their examples of intra predictor generation from real image. The 13 boundary pixels from previously coded blocks are used for predictor generation. Fig. 4 shows the illustration of 16 × 16-luma prediction modes and their real image examples. For I16MB, each 16 × 16-luma macroblock can select one of the four modes. Mode 3 is called plane prediction, which is an approximation of bilinear transform with only integer arithmetic. Chroma intra prediction is independent of-luma. Two chroma components are simultaneously predicted by one mode only. The allowed chroma prediction modes are very similar to those of I16MB except different block size  $(8 \times 8)$ and some modifications of dc prediction mode. The mode information of I4MB requires more bits to represent than that of I16MB. I4MB tends to be used for highly textured regions while I16MB tends to be chosen for flat regions.

#### B. Mode Decision

Mode decision is not specified in H.264/AVC standard. It is left as an encoder issue and is the most important step at the encoder side because it affects the coding performance most. The reference software of H.264/AVC [8] recommends two kinds of mode decision algorithm, low/high complexity mode decision. Both mode decision methods choose the best macroblock mode by considering a Lagrangian cost function, which includes both distortion and rate. Let the quantization parameter (QP) and the Lagrange parameter  $\lambda_{\text{MODE}}$  (a QP dependent variable) be given. The Lagrangian mode decision for a macroblock  $MB_k$  proceeds by minimizing

$J_{\text{MODE}}(\text{MB}_k, I_k \mid \text{QP}, \lambda_{\text{MODE}})$

= Distortion(MB<sub>k</sub>,  $I_k \mid QP$ ) +  $\lambda_{MODE} \cdot Rate(MB_k, I_k \mid QPP)$

(1)

Fig. 4. I16MB; left: illustration of four  $16 \times 16$ -luma prediction modes; right: examples of real images.

$$\begin{bmatrix} \mathbf{F}_0 \\ \mathbf{F}_1 \\ \mathbf{F}_2 \\ \mathbf{F}_3 \end{bmatrix} = \begin{bmatrix} \mathbf{1} & \mathbf{1} & \mathbf{1} & \mathbf{1} \\ 2 & \mathbf{1} & -\mathbf{1} & -2 \\ \mathbf{1} & -\mathbf{1} & -1 & \mathbf{1} \\ \mathbf{1} & -2 & 2 & -1 \end{bmatrix} \begin{bmatrix} \mathbf{X}_0 \\ \mathbf{X}_1 \\ \mathbf{X}_2 \\ \mathbf{X}_3 \end{bmatrix} \begin{bmatrix} \mathbf{X}'_0 \\ \mathbf{X}'_1 \\ \mathbf{X}'_2 \\ \mathbf{X}'_3 \end{bmatrix} = \begin{bmatrix} \mathbf{1} & \mathbf{1} & \mathbf{1} & \mathbf{1} & \mathbf{1} & \mathbf{1} \\ \mathbf{1} & \mathbf{1} & \mathbf{1} & -1 & -1 \\ \mathbf{1} & -\mathbf{1} & 2 & -1 & -1 \\ \mathbf{1} & -\mathbf{1} & 2 & -1 & -1 \end{bmatrix} \begin{bmatrix} \mathbf{F}'_0 \\ \mathbf{F}'_1 \\ \mathbf{F}'_2 \\ \mathbf{F}'_3 \end{bmatrix} \begin{bmatrix} \mathbf{F}_0 \\ \mathbf{F}_1 \\ \mathbf{F}_2 \\ \mathbf{F}_3 \end{bmatrix} = \begin{bmatrix} \mathbf{1} & \mathbf{1} & \mathbf{1} & \mathbf{1} & \mathbf{1} \\ \mathbf{1} & \mathbf{1} & -1 & -1 & -1 \\ \mathbf{1} & -1 & -1 & 1 & -1 \end{bmatrix} \begin{bmatrix} \mathbf{X}_0 \\ \mathbf{X}_1 \\ \mathbf{X}_2 \\ \mathbf{X}_3 \end{bmatrix}$$

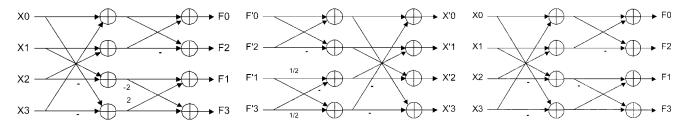

Fig. 5. Left: 1-D 4 × 4 DCT; middle: 1-D 4 × 4 IDCT; right: 1-D 4 × 4 Hadamard transform/inverse transform.

where the macroblock mode  $I_k$  is varied over all possible coding modes. Experimental selection of Lagrangian multipliers is discussed in [9]–[12]. In the low complexity mode decision, distortion is evaluated by sum of absolute differences (SAD) or sum of absolute transformed differences (SATD) between the predictors and original pixels. Usually, the coding performance by selecting SATD is 0.2–0.5 dB better. The rate is estimated by the number of bits required to code the mode information. In the high complexity mode decision, distortion is evaluated by sum of square differences (SSD) between the original samples and the reconstructed pixels (original pixels plus prediction residues after DCT/Q/IQ/IDCT). The rate is estimated by the number of bits required to code the mode information and the residue. The high complexity mode decision method is less suitable for real-time applications. The high complexity mode requires the most computation but leads to the best performance. Note that when processing I4MB, DCT/Q/IQ/IDCT must be performed right after a 4 × 4-block is mode decided in order to get the reconstructed boundary pixels as the predictors of the following  $4 \times 4$ -blocks.

#### C. Transform and Quantization

H.264/AVC still adopts transform coding for the prediction error signals. The block size is chosen as  $4 \times 4$  instead of  $8 \times 8$ . The  $4 \times 4$  DCT is an integer approximation of original floating point DCT transform. An additional  $2 \times 2$  transform is applied to the four dc-coefficients of each chroma component. If a-luma macroblock is coded as I16MB, two dimensional (2-D)  $4 \times 4$  Hadamard transform will be further applied on the 16 dc coefficients of-luma blocks. Fig. 5 shows the matrix representation

for  $4 \times 4$  one-dimensional (1-D) DCT, IDCT, and Hadamard transform. Note that due to the orthogonal property and diagonal symmetry, the inverse Hadamard transform is the same as its forward one. The scaling of the transform is combined with quantization. H.264/AVC uses scalar quantization without dead-zone. The quantization parameter QP ranges from 0 to 51. An increase in QP approximately reduces 12.5% of the bit-rate. The quantized transform coefficients of a block are scanned in a zigzag fashion. The decoding process can be realized with only additions and shifting operations in 16-b arithmetic. For more details, please refer to [13].

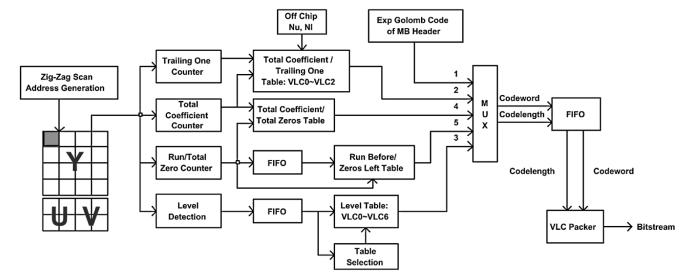

#### D. Entropy Coding

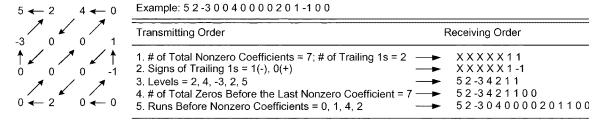

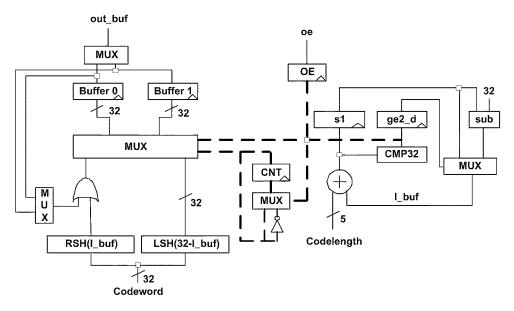

In H.264/AVC, two entropy coding schemes are supported. One is VLC-based coding, and the other is arithmetic coding [14]. In this subsection, VLC-based coding will be introduced. In the baseline profile, a single infinite-extension codeword set (Exp-Golomb code) is used for all syntax elements except the quantized transform coefficients. Thus, instead of designing a different VLC table for each syntax element, only a mapping to the single codeword table is customized according to the data statistics. For transmitting the quantized transform coefficients, a more sophisticated method called context-based adaptive variable length coding (CAVLC) is employed. In this scheme, VLC tables for various syntax elements are dependent on previous symbols. Since the VLC tables are well designed to match the corresponding conditioned symbol statistics, the entropy coding performance is improved in comparison to schemes using a single fixed VLC table. Let us take Fig. 6 as an example of coding a 4 × 4-block by CAVLC. At first,

Fig. 6. Example of encoding a  $4 \times 4$ -block by CAVLC.

| Instruction Type  | MIPS   | %     | Category      |

|-------------------|--------|-------|---------------|

| Arithmetic        | 1,785  | 16.5  | Computing     |

| Logic             | 83     | 0.77  | Computing     |

| Rotate and Shift  | 279    | 2.58  | Computing     |

| Jump & Compare    | 1,558  | 14.4  | Controlling   |

| Stack Instruction | 3,154  | 29.15 | Memory Access |

| Data Instruction  | 3,961  | 36.6  | Memory Access |

| Total             | 10,820 | 100   |               |

Fig. 7. Instruction profile of H.264/AVC Baseline Profile intra frame coder with low complexity mode decision for  $720 \times 480$  4:2:0 30-Hz Video (QP = 30).

the  $4 \times 4$ -block is backward zigzag scanned. The number of total nonzero coefficients and the number of tailing ones are transmitted as a joint symbol. The following symbols are signs of trailing ones, levels, number of total zeros before the last nonzero coefficient, and runs before nonzero coefficients. Each symbol has corresponding context-based adaptive VLC tables. The decoding process is shown at the right side. Note that run information of a level is not transmitted for the last nonzero coefficient or when the total runs have reached the number of total zeros before the last nonzero coefficient as shown in the example.

#### III. FAST ALGORITHM

In this section, a fast algorithm for software implementation will be described according to our analysis. The proposed complexity reduction methods are simple and effective.

# A. Analysis of Computational Complexity

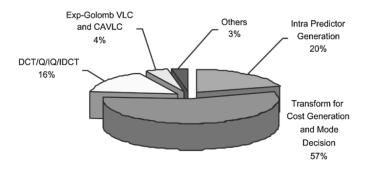

The instruction profile of H.264/AVC Baseline Profile intra frame coder with low complexity mode decision for SDTV specification (720 × 480 4:2:0 30 Hz) is shown in Fig. 7. Real-time processing requires 10829 million instructions per second (MIPS), which is far beyond the capability of today's general purpose processor (GPP). The instructions are classified as three categories: computing, controlling, and memory access. It is shown that memory access operations are the most highly demanded. This reveals that for DSP-based implementation, the speed of DRAM and the size of cache affect the performance considerably, and for ASIC-based accelerator, local SRAMs and registers are critical to reduce the bus bandwidth. Fig. 8

Fig. 8. Run-time percentages of various functional modules.

shows the run-time percentages of several major functional modules. As can be seen, transform for cost generation (SATD computation) and mode decision take the largest portion of computation, and intra predictor generation is the second. These two functions take 77% of computation and obviously are the processing bottleneck of the H.264/AVC intra frame coder. This result is quite reasonable because intra prediction has to generate 13 kinds of different predictors for each-luma sample and 4 kinds for each chroma sample. Also, the residues of each prediction mode also need to be 2-D Hadamard transformed into cost value for accumulation. After mode decision, only the decided modes and its corresponding residues are processed by DCT/Hadamard transform, quantization, inverse quantization, inverse DCT/Hadamard transform, and entropy coding. Exp-Golomb VLC and CAVLC are bit-level processing with complex controlling, but their computational load is not very large. Note that the run-time percentage of CAVLC will vary according to different QP values.

#### B. Analysis of Computation Reduction Techniques

As mentioned before, there are nine prediction modes for I4MB, and their numbers are shown in Fig. 3. Statistically, the smaller the number is, the more possible the mode will occur. Thus, this global statistics of I4MB modes can be used to save computation by searching only some modes with smaller numbers. How many modes should be searched is a tradeoff between computation and image quality. Clearly, global statistics cannot reflect the correlation of local modes. It may suffer severe PSNR degradation. Therefore, we tried a context-based approach considering the local statistics of neighboring blocks. Table II lists the most probable I4MB mode followed by other modes with gradually decreasing possibilities when the left and top neighboring  $4 \times 4$ -blocks are given. This is obtained by modifying the previous version of Working Draft [15]. Mode decision process can be accelerated

| B/A     | Outside | 0         | 1         | 2         | 3         | 4         | 5         | 6         | 7         | 8         |

|---------|---------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Outside | 2       | 02        |           | 20        |           |           |           |           |           |           |

| 0       |         | 071542368 | 012758364 | 021753468 | 071235486 | 021547368 | 057412368 | 012765843 | 075314286 | 701238564 |

| 1       | 12      | 108764523 | 168027345 | 162083475 | 168732054 | 160245873 | 105476832 | 168024753 | 107836542 | 186207345 |

| 2       | 21      | 015742368 | 210687534 | 210736584 | 127038564 | 210456738 | 501476238 | 126043758 | 071253486 | 123870654 |

| 3       |         | 071235684 | 123086745 | 120378645 | 317205864 | 312705648 | 071356248 | 123650874 | 730125864 | 318270654 |

| 4       |         | 015476382 | 126048537 | 120465387 | 310276458 | 415603782 | 540176382 | 641502387 | 107563428 | 132640875 |

| 5       |         | 051746328 | 120563784 | 205174638 | 015274586 | 540167328 | 504712638 | 102654738 | 075142368 | 102657834 |

| 6       |         | 018643512 | 168023475 | 162084357 | 168370452 | 164502873 | 150476328 | 164283075 | 107638452 | 168302475 |

| 7       |         | 072135846 | 127038654 | 207138564 | 732018546 | 072135648 | 075123486 | 107263584 | 703218546 | 173082564 |

| 8       |         | 108726534 | 186025374 | 182036745 | 183720654 | 182053674 | 180752643 | 186327054 | 183705264 | 183267054 |

TABLE II CONTEXT-BASED MOST PROBABLE MODES

Fig. 9. Subsampled pixels in a  $4 \times 4$ -block: left: pattern one and right: pattern two.

by searching only a few modes with higher possibilities. This method somewhat improves the quality of previous method but still suffers considerable PSNR loss compared with full search. This is caused by error propagation. When a block chooses a suboptimal mode instead of optimal mode, it will affect its following right and bottom blocks. Thus, we should find a way to detect the suboptimal modes and prevent them from propagating too far to make the neighboring blocks fail to find the best mode. Our improvement will be shown in the next subsection.

Single instruction multiple data (SIMD) is common in today's GPP and DSP. We can reduce the computation by reducing the data bit-width. For example, Philips TriMedia [16] is a 32-b VLIW/SIMD multimedia processor. Each of the five issue slots can simultaneously process two 16-b data or four 8-b data. The difference between original 8-b pixel and its predictor requires 9-b representation, which is over 8 b, so we can compute two differences in parallel. If the pixel bit-width is reduced to 7 b, the difference value can be represented within 8 b. In this way, four differences can be computed at the same cycle in one issue slot. Although the speed is doubled, some degradation of image quality may occur. Bit-width reduction can be also utilized in hardware design to save area and power as long as the PSNR drop can be tolerated.

Simplification of matching operations is also utilized. Intramode decision requires generation of predictor and difference operation for each pixel, and 2-D  $4 \times 4$  Hadamard transform for blocks to compute SATD. If the pixels are subsampled by two, 50% of computation can be reduced. The subsampled patterns are shown in Fig. 9. Given a prediction mode, originally 16 prediction pixels have to be generated, 16 difference operations have to be performed, and the SATD has to be computed.

Now only eight prediction pixels have to be generated, and only eight difference operations have to be performed for each  $4 \times 4$ -block. As for the SATD computation, if we replace the omitted pixels by zero, 50% of computation reduction cannot be attained. The definition of SATD of a  $4 \times 4$ -block is defined in Fig. 10. There are 48 (3×16) addition operations in the horizontal transform, 48 addition operations in the vertical transform, 16 absolute value operations, 15 additions in accumulation, and one shift operation. Replacing the omitted pixels by zero, as shown in Fig. 11, requires 16 addition operations in the horizontal transform, 48 addition operations in the vertical transform, 16 absolute value operations, 15 additions in accumulation, and one shift operation. The number of operations is reduced from 128 to 96. Only 25% of the SATD computation is reduced. What is more, replacing the omitted pixels by zero will enhance the high frequency components, which will affect the result of mode decision. Therefore, we replace the omitted pixels by its neighboring pixels, as shown in Fig. 12. In this way, only 24 addition operations are required in the horizontal transform because the result of the first column will be exactly the same as the second column, and the third will also be the same as the fourth. In the vertical transform, only 24 addition operations are required because the output of the third and fourth columns are all zero. Since there are only eight nonzero terms, only eight absolute value operations, seven addition operations, and one shift operation are further executed to get the SATD. The total number of operations becomes 64, and percentage of complexity reduction for SATD computation is also 50%.

#### C. Proposed Algorithm

In this subsection, a fast algorithm for H.264/AVC intracoder is proposed based on the reduction techniques previously discussed. First, no matter the intramacroblock mode is I4MB or I16MB, the computation of Lagrangian cost for each  $4 \times 4$ -block is performed under subsampled resolution by using pattern one shown in Fig. 9. Second, it was mentioned in the previous subsection that the context-based skipping of unlikely candidates for I4MB suffers from error propagation problem. We propose two techniques to handle this problem, periodic

Fig. 10. Original definition of SATD for a  $4 \times 4$ -block.

Fig. 11. Replacing the subsampled pixels by zero.

insertion of full-search  $4 \times 4$ -block and adaptive threshold on the distortion. As shown in Fig. 13, F stands for a full search  $4 \times 4$ -block, and P stands for a partial search  $4 \times 4$ -block. In an  $8 \times 8$ -block, the top left  $4 \times 4$ -block adopts full search while the other three  $4 \times 4$ -blocks utilize context-based partial search stated in the previous subsection. In this way, we can stop propagating the error too far. How long the period should be depends upon the tradeoff between computation and image quality. The three partial search blocks in an  $8 \times 8$ -block may

still miss the optimal modes. In these cases, the SATD values of these partial search blocks are much larger than the corresponding full search block. Therefore, we apply an adaptive local threshold on the minimum SATD of partial search blocks. If the minimum SATD of a partial search block is too large, rest I4MB modes still need to be searched. The threshold is defined as follows:

$$TH_{MinSATD} = \beta \cdot MinSATD_{FS}$$

(2)

Fig. 12. Proposed SATD for subsampling.

| F | Р | F | Р | F | Р | F | P | F | Р | F | Р     | F | Р | F | Р | F | Р    | F | Р |

|---|---|---|---|---|---|---|---|---|---|---|-------|---|---|---|---|---|------|---|---|

| Р | Р | Р | Р | Р | Р | Р | Р | Р | Р | Р | Р     | Р | Р | Р | Р | Р | Р    | Р | Р |

| F | Р | F | Р | F | Р | F | Р | F | Р | F | Р     | F | Р | F | Р | F | Р    | F | Ρ |

| Р | P | P | Р | Р | Р | Р | P | Р | Р | Р | Р     | Р | Р | P | Р | Р | Р    | Р | Р |

| F | Р | F | Ρ | F | Р | F | Р |   |   |   | ····· |   |   |   |   |   | ···· |   | ` |

| Р | Р | Р | Р | Р | Р | Р | P |   |   |   |       |   |   |   |   |   |      |   |   |

| F | P | F | Р | F | Р | F | Р |   |   |   |       |   |   |   |   |   |      |   |   |

| Р | Р | Р | Р | Р | Р | Р | Р |   |   |   |       |   |   |   |   |   |      |   |   |

Fig. 13. Corresponding positions between full search blocks and partial search blocks for I4MB.

where MinSATD<sub>FS</sub> denotes the minimum SATD of the top left full search  $4 \times 4$ -block in an  $8 \times 8$ -block. In this way, the threshold is adaptive to local statistics of the image. Also,  $\beta$ , a constant scalar, is set as 2.0 in our algorithm and can be used as a tradeoff between computation and image quality. Theoretically, the average saved computation is stated as follows:

$$Computation_{\rm saved}$$

$$= \left(1 - \left(\frac{9}{15} \cdot \frac{\text{AvgSearched I4MB}}{9} + \frac{4}{15} + \frac{2}{15}\right) \cdot \frac{1}{2}\right)\% \quad (3)$$

where Computation $_{\rm saved}$  is percentage of saved computation for intra prediction and mode decision, and AvgSearchedI4MB denotes the average number of searched I4MB modes. As mentioned before, there are nine, four, and four modes for I4MB, I16MB, and chroma intra prediction, respectively. Since the number of chroma pixels is half of the number of-luma pixels, the ratio of their computational complexities is 9:4:2. The (1/2) factor is due to subsampling by two.

# TABLE III SAVED COMPUTATION

| Sequence (CIF)      | Percentage (%) |

|---------------------|----------------|

| Coastguard          | 59.97          |

| Foreman             | 58.93          |

| Mobile Calendar     | 58.58          |

| Mother and Daughter | 59.88          |

| Silent              | 59.10          |

| Stefan              | 59.45          |

| Table Tennis        | 60.05          |

| Weather             | 59.45          |

#### D. Experimental Results

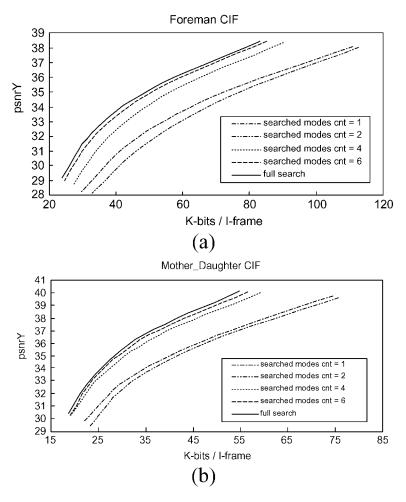

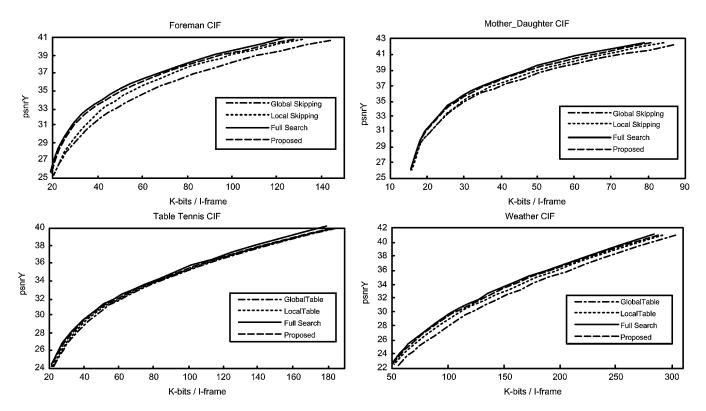

Table III shows the experimental results of average saved computation for intra prediction and mode decision. Eight standard sequences were tested with many QP values. As can be seen, the average saved computation is about 60%. According to the previous analysis, intra prediction and mode decision take 77% of the total computation of H.264/AVC intra frame coder. Therefore, the proposed fast algorithm can reduce 45% of the total complexity. Subsampling contributes most to the computation reduction while context-based skipping of unlikely I4MB candidates with periodic insertion of full search blocks and adaptive threshold checking can further reduce more computation with little quality loss. Fig. 14 shows the rate-distortion curves under different numbers of searched I4MB modes using context-based skipping of unlikely candidates without insertion of full-search blocks. The PSNR degradation is very severe when the number of searched I4MB modes is equal or less than two. Performance of searching one I4MB mode is even better than searching two I4MB modes. This is because

Fig. 14. Rate-distortion curves under different numbers of searched I4MB modes using context-based skipping of unlikely candidates for CIF videos. (a) Foreman. (b) Mother and Daughter.

searching one mode happens to select mode two (dc prediction) for all the  $4 \times 4$ -luma blocks in a frame, and searching two modes suffers from severe error propagation. By experimental results, searching the most possible four I4MB candidates, which is finally used in our experiments, is a reasonable choice to avoid too much loss of image quality. We did not use pixel bit-width truncation in our simulation because it is platform dependent. The rate-distortion curves of our final algorithm are illustrated in Fig. 15. Four sequences are shown. The other four sequences show the same trend and are omitted due to the limited spaces. The PSNR drop of the proposed algorithm is less than 0.3 dB in all sequences. Subsampling and searching only four globally most possible I4MB modes (mode 0–3) or four locally (context-based) most possible modes shows a significant loss of image quality, which indicates that periodic insertion of full search blocks effectively improves the image quality while subsampling together with context-based partial search greatly decreases complexity.

#### IV. HARDWARE ARCHITECTURE

In this section, a parallel H.264/AVC intra frame coding architecture with efficient macroblock pipelining is proposed for SDTV specification ( $720 \times 480 \ 4:2:0 \ 30$ -Hz video), which requires to encode about 16 Mega-pixels within one cycle. The

implemented algorithm is the same as the reference software except that Hadamard-based mode decision is changed to DCT-based. The detailed analysis and system/module designs are described in the following subsections.

#### A. Exploration of Parallelism

From the complexity analysis in Section III, it is known that intra prediction and mode decision place the heaviest computational load on processor. Parallel architecture is urgently demanded to accelerate this critical function. In this subsection, we will analyze the H.264/AVC intra prediction algorithm to obtain the most suitable degree of parallelism required for intra prediction and mode decision to meet the SDTV specification. Because transform for Lagrangian cost generation (SATD computation) is highly dependent on intra predictor generation and must be performed right after intra predictor generation, the parallelism of intra prediction unit should be the same as the transformation unit. Thus, we start the exploration of parallelism from intra predictor generation.

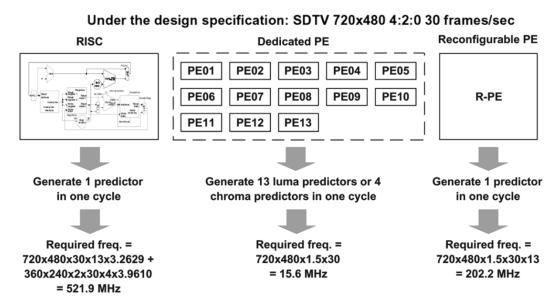

First, two assumptions are made. One is that a reduced instruction set computer (RISC) is able to execute one instruction in one cycle with an exception of multiplication requiring two cycles, and the other is that a processing element (PE) is capable of generating the predictor of one pixel in one cycle. Next,

Fig. 15. Rate-distortion curves of proposed algorithm (subsampling + context-based partial search + periodic insertion of full search + adaptive SATD threshold) compared with full search, global method (subsampling + partial search utilizing global statistics), and local method (subsampling + context-based partial search).

we compute the average instruction counts required for intra predictor generation. The instructions includes arithmetic computing and data transfer from memory unit to execution unit. For example, the operation "c = a + b" requires two load instructions and one add instruction. The actual instruction count for RISC is higher than the provided data because the address generation (AG) is excluded for two reasons. For software implementations, different coding styles and compilers will lead to very different results. On the hardware accelerator, AG belongs to controlling circuits, which usually occupy a very small portion of chip area, and it has nothing to do with the design of intra predictor generation. Table IV shows the analysis of instructions for intra predictor generation. I16MB plane prediction mode demands the most cycles than other prediction modes because two multiplication operations are required for one pixel. Detailed explanation is omitted for simplicity, and interested readers can refer to [1] for checking. In sum, we conclude that it takes 3.2629 and 3.9610 cycles for a RISC to generate one-luma predictor and one chroma predictor, respectively, in average.

To design the hardware architecture of intra predictor generation unit, we first bring up three possible solutions, as shown in Fig. 16. The first one is a RISC solution. In the era of system on chip, embedded RISC becomes essential in chip design. However, the RISC must work at the frequency higher than 521.9 MHz to meet the real-time requirement of SDTV specification. Consequently, RISC implementation seems to be impractical, not to mention transform, entropy coding, and other system jobs such as real-time operation system (RTOS), camera control, network, and others. The second possible solution is a set of dedicated hardware PEs for intra predictor generation. Suppose 13

kinds of PE are developed, and each one is dedicated for one kind of intra prediction mode. The hardware can generate 13 kinds of-luma predictors or four kinds of chroma predictors in one cycle. The architecture only needs to operate at 15.6 MHz under our specification. However, this solution does not consider the correlation between different prediction modes and has high hardware cost. The third choice is to design a reconfigurable PE to generate all the intra predictors with different configurations. This solution targets at higher area-speed efficiency. Nevertheless, implementation of a reconfigurable PE is not straightforward. It requires several design techniques to reach resource sharing. Moreover, reconfigurable PE still requires to operate at 202.2 MHz to meet our target. For these reasons, parallel reconfigurable PEs become the most promising solution. Table V lists the hardware complexity and required frequency of the three solutions under different degrees of parallelism. Although the assumption that the hardware complexity of one PE is similar to those of RISC and one dedicated PE is quite rough, it is still proper to reflect the fact that RISC is too slow, dedicated PEs are too expensive, and reconfigurable PE is a good tradeoff between area and speed. Finally, we conclude this subsection by adopting four-parallel reconfigurable PE for intra predictor generation in our design.

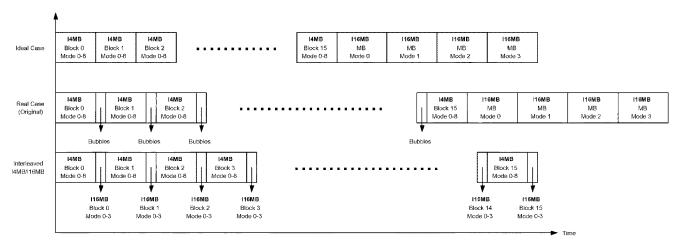

# B. Initial System Architecture

In conventional video coding standards, prediction engine and block engine (DCT/Q/IQ/IDCT/VLC) can be clearly separated. After prediction engine finishes processing a macroblock, block engine takes over this macroblock, and prediction engine goes on processing the next macroblock. However, H.264/AVC

TABLE IV

ANALYSIS OF INSTRUCTIONS FOR INTRA PREDICTOR GENERATION

|               | Intra Prediction<br>Modes    | Average Cycles to Generate the<br>Predictor of a Pixel |  |  |  |  |  |

|---------------|------------------------------|--------------------------------------------------------|--|--|--|--|--|

|               | Intra4x4 Vertical            | (0+0+0+4 x4)/16 = 1                                    |  |  |  |  |  |

|               | Intra4x4 Horizontal          | (0+0+0+4 x4)/16 = 1                                    |  |  |  |  |  |

|               | Intra4x4 DC                  | (8+1+0+4 x4)/16 = 1.5625                               |  |  |  |  |  |

|               | Intra4x4 Diagonal Down/Left  | (6x6+4+7+12+4x4)/16 = 4.6875                           |  |  |  |  |  |

|               | Intra4x4 Diagonal Down/Right | (3x7+7+7+4x4)/16 = 3.1875                              |  |  |  |  |  |

| _             | Intra4x4 Vertical Left       | (2x4+3x6+10+6+4x4)/16 = 3.625                          |  |  |  |  |  |

| L             | Intra4x4 Horizontal Down     | (2x4+3x6+10+6+4x4)/16 = 3.625                          |  |  |  |  |  |

| M             | Intra4x4 Vertical Right      | (2x4+3x4+6x2+10+9+4x4)/16 = 4.1875                     |  |  |  |  |  |

| A             | Intra4x4 Horizontal Up       | (2x4+3x4+6x2+10+9+4x4)/16 = 4.1875                     |  |  |  |  |  |

|               | Intra16x16 DC                | (15x2+2+1+0+16x16)/256 = 1.1289                        |  |  |  |  |  |

|               | Intra16x16 Vertical          | (0+0+0+16x16)/256 = 1                                  |  |  |  |  |  |

|               | Intra16x16 Horizontal        | (0+0+0+16 x16)/256 = 1                                 |  |  |  |  |  |

|               | Intra16x16 Plane             | (8x3x2+2x2+2+2+(3+2x2+2+2)x256+16x16)/256 = 12.2266    |  |  |  |  |  |

|               | Average                      | 3.2629 (cycles/pixel required for RISC)                |  |  |  |  |  |

| C             | DC                           | (3x4+4+4+0+8x8)/64 = 1.3125                            |  |  |  |  |  |

| H             | Vertical                     | (0+0+0+8 x8)/64 = 1                                    |  |  |  |  |  |

| R             | Horizontal                   | (0+0+0+8 x8)/64 = 1                                    |  |  |  |  |  |

| О<br><b>м</b> | Plane                        | (4x3x2+2x2+2+2+(3+2x2+2+2)x64+8x8)/64 = 12.5313        |  |  |  |  |  |

| A             | Average                      | 3.9610 (cycles/pixel required for RISC)                |  |  |  |  |  |

- 1. Addition, Shift, Scaling, Data Assignment => one cycle

- 2. Multiplication => two cycles

- 3. Cycles for address calculation is not counted

utilizes intra prediction in the spatial domain, which destroys the traditional macroblock pipelining. After prediction of a macroblock and before corresponding reconstructed pixels at the output of the DCT/Q/IQ/IDCT loop are produced, next macroblock cannot be predicted. The situation is even worse for I4MB prediction modes. Prediction and mode decision of a  $4 \times 4$ -block cannot be performed until the previous  $4 \times 4$ -block is reconstructed. If the number of processing cycles for DCT/Q/IQ/IDCT loop is too large, prediction circuits must be stalled to wait for reconstruction, and the hardware utilization will be significantly decreased.

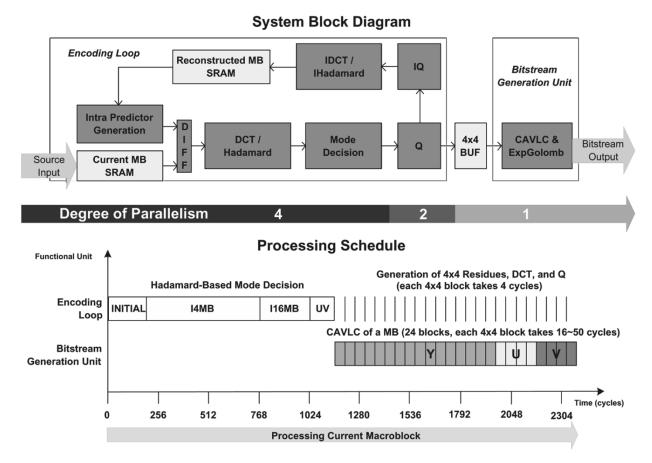

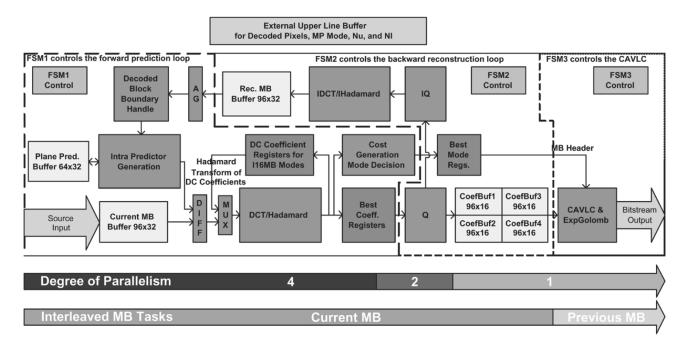

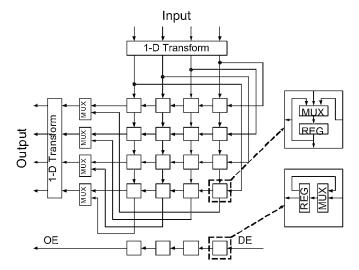

We divide our system into two main parts, the encoding loop and the bitstream generation unit, as illustrated in Fig. 17. The system block diagram is shown in the upper part while the processing schedule is in the bottom part. First, the system encodes a frame macroblock by macroblock in progressive order, and we buffer one row of reconstructed pixels (720-luma pixels and  $360 \times 2$  chroma pixels) in the external DRAM. At the beginning of a macroblock, current macroblock pixels ( $16 \times 16 + 8 \times 8 \times 2 = 384$ ) and upper reconstructed pixels (17) are loaded from external DRAM to on-chip SRAM. The reconstructed pixels of the previous (left) macroblock can be directly kept in registers to save bus bandwidth. Assume the bus bit-width is 32, loading data requires 101 cycles. The initialization of a macroblock also includes loading of some coding information from neighboring macroblocks (intra prediction modes and number of nonzero

Fig. 16. Three possible solutions and the required working frequency to meet the real-time requirement of SDTV specification.

TABLE V

HARDWARE COMPLEXITY AND OPERATING FREQUENCY FOR INTRAPREDICTOR GENERATION

| Parallelism       | No Par                 | allelism               | Two-                   | Parallel               | Four-                  | Parallel               | Eight-Parallel         |                        |  |

|-------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|--|

| Solution          | Hardware<br>Complexity | Operating<br>Frequency | Hardware<br>Complexity | Operating<br>Frequency | Hardware<br>Complexity | Operating<br>Frequency | Hardware<br>Complexity | Operating<br>Frequency |  |

| RISC              | ~A                     | >>521.9 MHz            | ~2A                    | >>261.0 MHz            | ~4A                    | >>130.5 MHz            | ~8A                    | >>65.2 MHz             |  |

| Dedicated PE's    | <13A                   | 15.6 MHz               | <26A                   | 7.8 MHz                | <52A                   | 3.9 MHz                | <104A                  | 1.9 MHz                |  |

| Reconfigurable PE | Α                      | 202.2 MHz              | 2A                     | 101.1 MHz              | 4A                     | 50.6 MHz               | 8A                     | 25.3 MHz               |  |

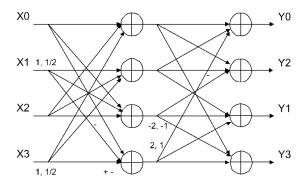

coefficients) on the upper row for entropy coding. The coding information of the left macroblock can be also saved in registers for entropy coding of current macroblock. With on-chip SRAM, the bus bandwidth is reduced from hundreds of MB to about 20 MB/s. Among the data transfer between external DRAM and our accelerator, the input pixel rate contributes to 15.55 MB/s ( $720 \times 480 \times 1.5 \times 30$ ), the output data rate ranges from 5% to 20% of the input pixel rate, saving, and loading of reconstructed pixels of upper rows requires 2.6 MB/s ((720 +  $360+360 \times 30 \times 30 \times 2$ ), and the data amount of coding information is very small. Then, we start the intra prediction block by block. According to the analysis in Subsection IV.A, given a 4 × 4-luma block and a prediction mode, four pixels are required to be processed (predictor generation and transform) in one cycle. Therefore, the number of cycles required for-luma intra prediction and mode decision is  $832(4 \times 13 \times 16)$ , and that for chroma is  $128(4 \times 4 \times 8)$ . As previously discussed, before DCT/Q/IQ/IDCT finishes the previous 4 × 4-block, current 4 × 4-block cannot proceed to intra prediction, so the required time for intra prediction is actually longer. We intended to adopt two-parallel architectures for DCT/Q/IQ/IDCT. However, Four-parallel transform unit doubles the speed of two-parallel transform unit with only a little area overhead (discussed in Section IV-G), so four-parallel DCT/IDCT is adopted at last. CAVLC is a sequential algorithm and its computational loading

is not very large. Hence, parallel processing is not a must. In sum, the initial system architecture needs about 2400 cycles to encode one macroblock. Also, with the straightforward data flow, the residues are generated twice. One time is used for intra predictor generation and mode decision while the other is for entropy coding of the best mode. On-chip memory access is 113.17 MB/s.

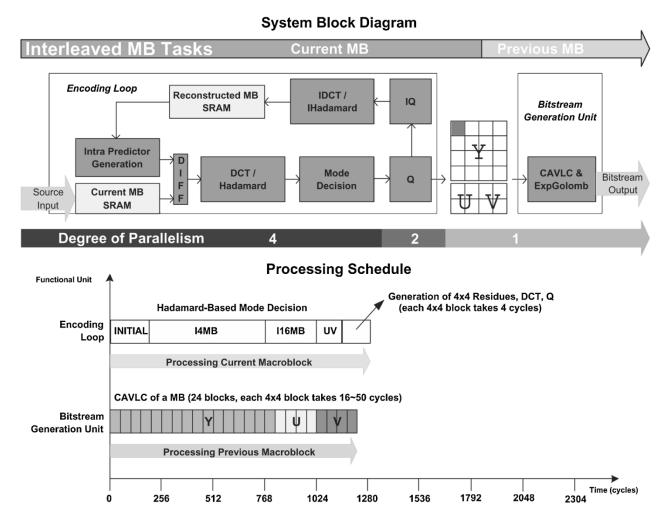

# C. System Architecture With Macroblock Pipelining

In the previous subsection, it is observed that the number of processing cycles for encoding loop is about the same as that for bitstream generation unit in the worst case. These two procedures are separable because there is no feedback loop between them. Therefore, a task-level interleaving scheme, i.e., macroblock pipelining, is incorporated into our design to accelerate the processing speed at the cost of coefficient buffer for a macroblock, as illustrated in Fig. 18. The data flow is the same with that of initial system architecture except the two stages process different macroblocks. After intra prediction and mode decision, the residues are generated again, sent to DCT/Q, and stored in the coefficient buffer. The buffer is composed of four memory banks, and the size of each bank is 96 words by 16 b. The buffer is indispensable for macroblock pipelining. When current macroblock is processed by encoding loop, CAVLC processes previous macroblock simultaneously. The bus bandwidth

Fig. 17. Illustration of initial system architecture.

and the amount of on-chip memory access are still the same as before while the processing throughput is reduced to less than 1300 cycles/macroblock.

#### D. System Architecture With DCT-Based Mode Decision

In the H.264/AVC reference software, Hadamard transform is involved in generating cost for mode decision. The quantized transform coefficients in the mode decision phase cannot be reused for CAVLC. Thus, we modify the mode decision algorithm by using DCT instead of Hadamard transform to generate Lagrangian costs so that the transform coefficients can be reused. Luma mode decision is performed block by block, and 13 kinds of predictors are generated for each  $4 \times 4$ -block. The former nine prediction modes decide the best I4MB mode, and the quantized transform coefficients will be stored in the coefficient buffer right after mode decision and reconstruction of a 4 × 4-block. In this way, if I4MB mode is better than I16 MB, re-generation of-luma quantized transform residues can be avoided. The improvement will be significant in high quality applications for almost all macroblocks select I4MB. In our experience, when QP is smaller than 25, the percentage of I16MB mode is less than 10%. The amount of on-chip memory access can thus be reduced from 113.17 to 72.25 MB/s. Also, the proposed mode decision does not suffer any quality loss compared with the mode decision in the reference software. Fig. 19 shows the final system block diagram of our proposed H.264/AVC intra frame encoder. The system is partitioned into three independently-controlled parts: forward encoding part,

backward reconstruction part, and bitstream generation part. The system buffers one row of reconstructed pixels and one row of coding information at the external DRAM. The coding information includes I4MB modes for most probable mode prediction, number of nonzero coefficients for CAVLC. The external DRAM size is proportional to the width of image.

## E. Evaluation of System Performance

Table VI shows the comparison of the three developed architectures. The first version is a parallelism optimized architecture with straightforward data flow design and Hadamard-based mode decision. The second architecture evolves from the first version by considering macroblock pipelining. The third version replaces the Hadamard-based mode decision by DCT-based mode decision. We can see from the table that the last version has the fewest processing cycles and the least memory access. Compared with software implementation on RISC, which requires 0.28 M cycles to encode one macroblock, the performance of proposed architecture is 215.4 times faster than the software implementation. The chip only needs to operate at about 50 MHz to meet the SDTV specification.

#### F. Intra Predictor Generation Unit

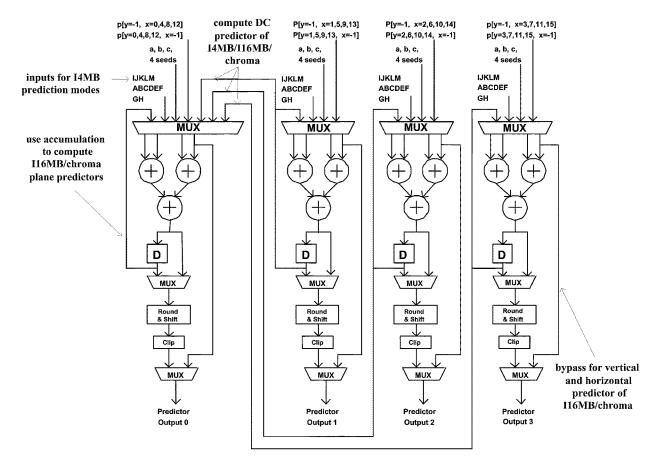

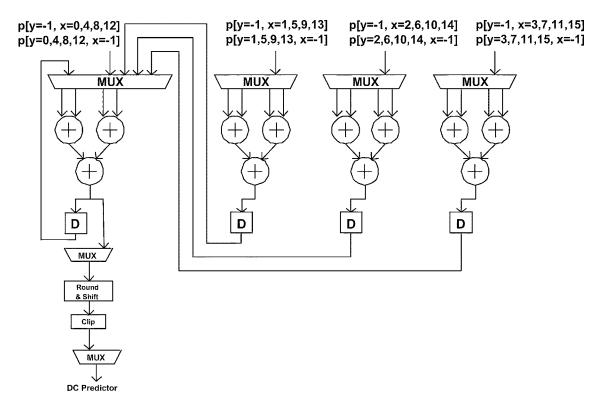

In this subsection, a reconfigurable intra predictor generator to support all of the prediction modes will be discussed. The proposed hardware is a four-parallel architecture to meet the target specification. Four predicted pixels are generated in one cycle

Fig. 18. Illustration of system architecture with proposed macroblock pipelining.

except for the most complicated prediction mode, I16MB plane prediction mode. We will introduce a decomposition technique to reduce the complexity of PE. Before entering the following subsections, please recall the analysis in Table V. Four reconfigurable PEs will be used to generate  $4\times 1$  predictors in one cycle.

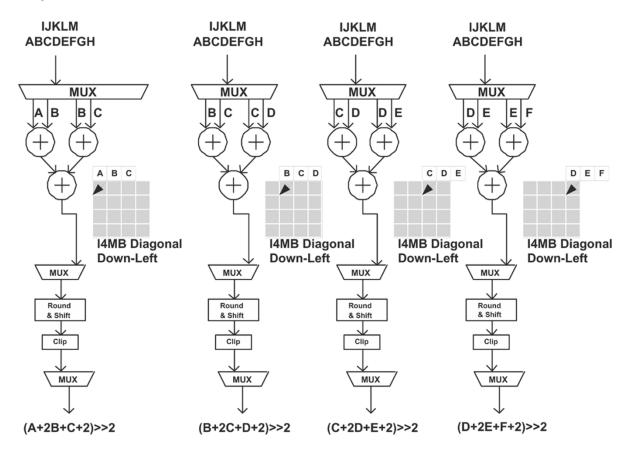

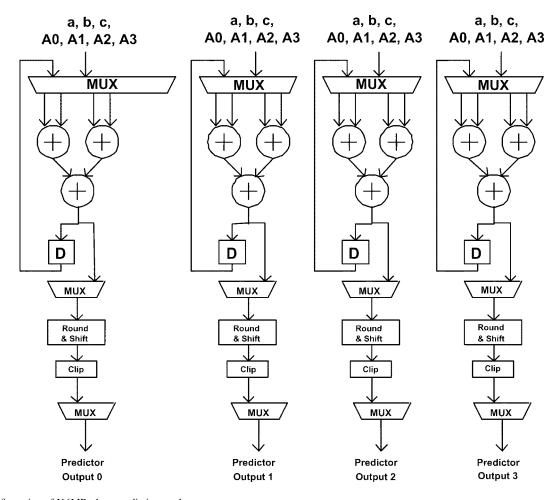

1) I4MB Prediction Modes: I4MB prediction is arranged in a three-loop fashion. The outer loop is the  $16.4 \times 4$ -luma blocks, the middle loop is the nine I4MB modes, and the inner loop is the four rows of  $4 \times 1$  pixels in a block. Totally  $576 (16 \times 9 \times 4)$ cycles are required to generate all kinds of I4MB predictors for a whole macroblock, and a row of  $4 \times 1$  pixels is predicted in one cycle. Frequent access of neighboring reconstructed pixels (A-H and I-M shown in Fig. 3) is inevitable, so we buffer these pixels in registers and update the registers before starting I4MB prediction of a 4 × 4-block, as corresponded with the "Decoded Block Boundary Handle" (DBBH) in Fig. 19. Let us denote the top left, top right, bottom left, and bottom right positions of a  $4 \times 4$ -block as (0, 0), (0, 3), (3, 0), and (3, 3), respectively. The detailed definitions of I4MB predictors are shown in Table VII. For example, diagonal down-left type predictor at position (0,0)is  $(A+B+B+C+2) \gg 2$ . Except for dc mode, only three or fewer neighboring reconstructed pixels are involved in the generation of a predictor, and two 8-b adders, one 9-b adder, and one

rounding adder (four adders in total) are required to generate a predictor in one cycle. Multiplexers are required to select proper neighboring reconstructed pixels. The selection can be viewed as a sliding window ( $3 \times 1$  pixels) shifting between "LKJ" to "FGH." If we want to generate the dc predictor in one cycle, the required circuits will expand to four 8-b adders, two 9-b adders, one 10-b adder, and one rounding adder, and the utilization of the extra two 8-b adders, one 9-b adder, and one 10-b adder will be extremely low for they are only useful when dc mode is in process. For a single PE design, it is better to compute the dc predictor using more cycles with fewer adders and save the dc value in the register for later reuse. As for a four-parallel design, since the dc mode has the same predictors at all positions, four PEs can be joined together to compute the dc predictor in one cycle.

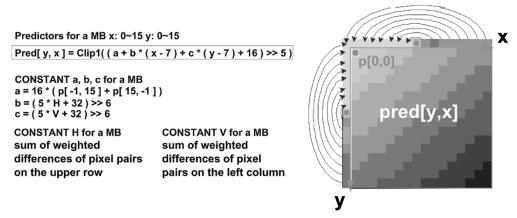

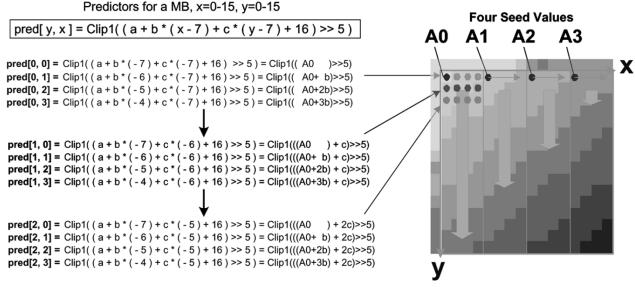

2) I16MB Prediction Modes: The predictors of I16MB vertical mode and horizontal mode can be directly acquired from the neighboring reconstructed pixels by DBBH. Like I4MB dc predictor, I16MB dc predictor can be calculated in several cycles by few adders. The detailed definition of I16MB plane prediction mode, which is an approximation of bilinear transform, is described in the following:

$$Pred[y, x] = Clip1((a + b \cdot (x - 7) + c \cdot (y - 7)) \gg 5)$$

(4)

Fig. 19. Illustration of final system architecture.

TABLE VI COMPARISON OF SYSTEM ARCHITECTURES

| Architecture           | Initial           | MB Pipelining     | MB Pipelining and<br>DCT-Based Mode<br>Decision |  |

|------------------------|-------------------|-------------------|-------------------------------------------------|--|

| Parallelism Optimized  | YES               | YES               | YES                                             |  |

| Task Schedule          | Sequential        | Interleaved       | Interleaved                                     |  |

| Mode Decision Method   | Hadamard-Based    | Hadamard-Based    | DCT-Based                                       |  |

| Processing Cycles / MB | < 2400 (cycles)   | < 1300 (cycles)   | < 1300 (cycles)                                 |  |

| Required Frequency     | 97.2 MHz          | 52.7 MHz          | 52.7 MHz                                        |  |

| Bus Bandwidth          | ~20 (Mbytes/s)    | ~20 (Mbytes/s)    | ~20 (Mbytes/s)                                  |  |

| On-Chip SRAM Access    | 113.17 (Mbytes/s) | 113.17 (Mbytes/s) | 72.25 (Mbytes/s)                                |  |

| Coefficient Buffer     | 16x16 (bits)      | 96x64 (bits)      | 96x64 (bits)                                    |  |

$$a = 16 \cdot (p[-1, 15] + p[15, -1]) \tag{5}$$

$$b = (5 \cdot H + 32) \gg 6 \tag{6}$$

$$c = (5 \cdot V + 32) \gg 6 \tag{7}$$

$$c = (5 \cdot V + 32) \gg 6$$

$$H = \sum_{x'=0}^{7} (x'+1) \cdot (p[-1, 8+x'] - p[-1, 6-x']) (8)$$

$$V = \sum_{y'=0}^{7} (y'+1) \cdot (p[8+y', -1] - p[6-y', -1]) (9)$$

$$V = \sum_{y'=0}^{\ell} (y'+1) \cdot (p[8+y',-1] - p[6-y',-1])$$

(9)

where [y, x] denotes the position ([0, 0], [0, 15], [15, 0], and [15, 15] are the top left, top right, bottom left, and bottom right of a-luma macroblock, respectively), p represents the neighboring reconstructed pixel value, Pred indicates the generated predictor value, and Clip1 is to clip the result between 0 and

255. Fig. 20 may help understand I16MB plane prediction mode better. As shown in (4), two multiplications, five additions, and one shift are required. Assume we are going to reuse those adders, which were planned to generate one I4MB predictor in one cycle, to produce one I16MB plane predictor, it is obvious that the required processing cycles will be quite longer. Besides, the control signals of the multiplexers for selecting adder inputs will be very complex. Therefore, we propose a more efficient method to decompose plane predictors by using only accumulation operation. Firstly, for each 16 × 16-luma macroblock, there will be a short setup period to find the values of a, b, c, H, and V and buffer them in registers. The multiplications in (8) and (9) can be replaced by additions as follows. For example, when  $x' = 2, (x' + 1) \cdot (p[-1, 8 + x']$ p[-1, 6-x']) can be calculated as accumulating (p[-1, 8+

TABLE VII DEFINITIONS OF I4MB PREDICTORS

| I4MB Mode       | L        | K          | J        | I                                                | M                                                | A          | B                                                | C                                                | D        | E        | F        | G        | Н                                   | Round | Shift        | Positions (y, x)                   |

|-----------------|----------|------------|----------|--------------------------------------------------|--------------------------------------------------|------------|--------------------------------------------------|--------------------------------------------------|----------|----------|----------|----------|-------------------------------------|-------|--------------|------------------------------------|

|                 |          |            |          |                                                  |                                                  | 1          |                                                  |                                                  |          |          |          |          |                                     | 0     | >> 0         | (0,0) (1,0) (2,0) (3,0)            |

| Vertical        |          |            |          |                                                  |                                                  |            | 1                                                |                                                  |          |          |          |          |                                     | 0     | >> 0         | (0,1) (1,1) (2,1) (3,1)            |

| vertical        |          |            |          |                                                  |                                                  |            |                                                  | 1                                                |          |          |          |          |                                     | 0     | >> 0         | (0,2) (1,2) (2,2) (3,2)            |

|                 |          |            |          |                                                  |                                                  |            |                                                  |                                                  | 1        |          |          |          |                                     | 0     | >> 0         | (0,3) (1,3) (2,3) (3,3)            |

|                 |          |            |          | 1                                                |                                                  |            |                                                  |                                                  |          |          |          |          |                                     | 0     | >> 0         | (0,0) (0,1) (0,2) (0,3)            |

|                 |          |            | 1        | Ė                                                |                                                  |            |                                                  |                                                  |          |          |          |          |                                     | 0     | >> 0         | (1,0) (1,1) (1,2) (1,3)            |

| Horizontal      |          | 1          |          |                                                  |                                                  |            |                                                  |                                                  |          |          |          |          |                                     | 0     | >> 0         | (2,0) (2,1) (2,2) (2,3)            |

|                 | 1        |            |          |                                                  |                                                  |            |                                                  |                                                  |          |          |          |          |                                     | 0     | >> 0         | (3,0) (3,1) (3,2) (3,3)            |

| DC              | 1        | 1          | 1        | 1                                                |                                                  | 1          | 1                                                | 1                                                | 1        |          |          |          |                                     | 4     | >> 3         | ALL                                |

|                 | i        |            |          |                                                  |                                                  | 1          | 2                                                | 1                                                |          | 1        |          | I        |                                     | 2     | >> 2         | (0,0)                              |

|                 |          |            |          |                                                  |                                                  | <u> </u>   | 1                                                | 2                                                | 1        |          |          |          |                                     | 2     | >> 2         | (0,1) (1,0)                        |

|                 |          |            |          |                                                  |                                                  |            | Ė                                                | 1                                                | 2        | 1        |          |          |                                     | 2     | >> 2         | (0,2) (1,1) (2,0)                  |

| Diagonal Down-  |          |            |          |                                                  |                                                  |            |                                                  | ┝                                                | 1        | 2        | 1        |          |                                     | 2     | >> 2         | (0,3) (1,2) (2,1) (3,0)            |

| Left            |          |            |          |                                                  |                                                  |            |                                                  |                                                  | Ė        | 1        | 2        | 1        |                                     | 2     | >> 2         | (1,3) (2,2) (3,1)                  |

|                 |          |            |          |                                                  |                                                  |            |                                                  |                                                  |          | Ė        | 1        | 2        | 1                                   | 2     | >> 2         | (2,3) (3,2)                        |

|                 |          |            |          |                                                  |                                                  |            |                                                  |                                                  |          |          | † †      | 1        | 3                                   | 2     | >> 2         | (3,3)                              |

|                 |          |            |          |                                                  |                                                  |            |                                                  |                                                  |          |          |          |          |                                     |       |              |                                    |

|                 | 1_       | 2          | 1        | <u> </u>                                         |                                                  |            | <u> </u>                                         |                                                  |          | <u> </u> |          | <u> </u> | $ldsymbol{ldsymbol{ldsymbol{eta}}}$ | 2     | >> 2         | (3,0)                              |

|                 |          | 1          | 2        | 1                                                | <u> </u>                                         |            | <u> </u>                                         | <u> </u>                                         |          | <u> </u> | <u> </u> | ⊢        | $\vdash$                            | 2     | >> 2         | (2,0) (3,1)                        |

| Diagonal Down-  | <u> </u> |            | 1        | 2                                                | 1                                                | lacksquare |                                                  |                                                  |          |          | <u> </u> | <u> </u> | lacksquare                          | 2     | >> 2         | (1,0) (2,1) (3,2)                  |

| Right           |          | <u> </u>   | <u> </u> | 1                                                | 2                                                | 1          |                                                  | <u> </u>                                         |          |          | <u> </u> | Ь—       | lacksquare                          | 2     | >> 2         | (0,0) (1,1) (2,2) (3,3)            |

|                 | <u> </u> | Ь_         | <u> </u> | <u> </u>                                         | 1                                                | 2          | 1                                                | <u> </u>                                         |          | <u> </u> | Ь.       | Ь_       | $ldsymbol{ldsymbol{ldsymbol{eta}}}$ | 2     | >> 2         | (0,1) (1,2) (2,3)                  |

|                 |          |            |          |                                                  |                                                  | 1          | 2                                                | 1                                                |          |          |          |          |                                     | 2     | >> 2         | (1,3)                              |

|                 |          |            |          |                                                  |                                                  |            | 1                                                | 2                                                | 1        |          |          |          |                                     | 2     | >> 2         | (0,3)                              |

|                 |          |            |          |                                                  | 1                                                | 1          |                                                  |                                                  |          |          |          |          |                                     | 1     | >> 1         | (0,0) (2,1)                        |

|                 |          |            |          |                                                  |                                                  | 1          | 1                                                |                                                  |          |          |          |          |                                     | 1     | >> 1         | (0,1) (2,2)                        |

|                 |          |            |          |                                                  |                                                  |            | 1                                                | 1                                                |          |          |          |          |                                     | 1     | >> 1         | (0,2) (2,3)                        |

|                 |          |            |          |                                                  |                                                  |            |                                                  | 1                                                | 1        |          |          |          |                                     | 1     | >> 1         | (0,3)                              |

| Vertical Right  |          | 1          | 2        | 1                                                |                                                  |            |                                                  |                                                  |          |          |          |          |                                     | 2     | >> 2         | (3,0)                              |

| Vertical reight |          |            | 1        | 2                                                | 1                                                |            |                                                  |                                                  |          |          |          |          |                                     | 2     | >> 2         | (2,0)                              |

|                 |          |            |          | 1                                                | 2                                                | 1          |                                                  |                                                  |          |          |          |          |                                     | 2     | >> 2         | (1,0) (3,1)                        |

|                 |          |            |          |                                                  | 1                                                | 2          | 1                                                |                                                  |          |          |          |          |                                     | 2     | >> 2         | (1,1) (3,2)                        |

|                 |          |            |          | ļ                                                | _                                                | 1          | 2                                                | 1                                                | _        | _        | -        | _        |                                     | 2     | >> 2         | (1,2) (3,3)                        |

|                 |          |            |          |                                                  | <u> </u>                                         |            | 1                                                | 2                                                | 1        |          |          |          |                                     | 2     | >> 2         | (1,3)                              |

|                 | 1_       | 1          |          |                                                  |                                                  |            |                                                  |                                                  |          |          |          |          |                                     | 1     | >> 1         | (3,0)                              |

|                 |          | 1          | 1        |                                                  |                                                  |            |                                                  |                                                  |          |          | L        | <u> </u> |                                     | 1     | >> 1         | (2,0) (3,2)                        |

|                 |          |            | 1        | 1                                                |                                                  |            |                                                  |                                                  |          |          |          |          |                                     | 1     | >> 1         | (1,0) (2,2)                        |

|                 |          |            |          | 1                                                | 1                                                |            |                                                  |                                                  |          |          |          |          |                                     | 1     | >> 1         | (0,0) (1,2)                        |

| Horizontal Down | 1        | 2          | 1        |                                                  |                                                  |            |                                                  |                                                  |          |          |          |          |                                     | 2     | >> 2         | (3,1)                              |

|                 |          | 1          | 2        | 1                                                |                                                  |            |                                                  |                                                  |          |          |          | <u> </u> |                                     | 2     | >> 2         | (2,1) (3,3)                        |

|                 |          |            | 1        | 2                                                | 1                                                |            |                                                  |                                                  |          |          |          | _        |                                     | 2     | >> 2         | (1,1) (2,3)                        |

|                 |          |            |          | 1                                                | 2                                                | 1          | <u> </u>                                         |                                                  |          |          |          |          |                                     | 2     | >> 2         | (0,1) (1,3)                        |

|                 | -        |            |          |                                                  | 1                                                | 2          | 1                                                | ļ.,                                              |          | _        | _        | _        |                                     | 2     | >> 2         | (0,2)                              |

|                 |          |            |          |                                                  |                                                  | 1          | 2                                                | 1                                                |          |          |          |          |                                     | 2     | >> 2         | (0,3)                              |

|                 |          |            |          |                                                  |                                                  | 1          | 1                                                |                                                  |          |          |          |          |                                     | 1     | >> 1         | (0,0)                              |

|                 |          |            |          |                                                  |                                                  |            | 1                                                | 1                                                |          |          |          |          |                                     | 1     | >> 1         | (0,1) (2,0)                        |

|                 |          |            |          |                                                  |                                                  |            |                                                  | 1                                                | 1        |          |          |          |                                     | 1     | >> 1         | (0,2) (2,1)                        |