# Analysis of a Synergetically Controlled Two-Stage Three-Phase DC/AC Buck-Boost Converter

Michael Antivachis, Jon Azurza Anderson, Dominik Bortis, and Johann Walter Kolar

Abstract—Three-phase DC/AC power electronics converter systems used in battery-powered variable-speed drive systems or employed in three-phase mains-supplied battery charger applications usually feature two power conversion stages. In both cases, typically a DC/DC stage is attached to a three-phase DC/ AC stage in order to enable buck-boost functionality and/or a wide input-output voltage operating range. However, a two-stage solution leads to a high number of switched bridge-legs and hence, results in high switching losses, if the degrees of freedom available for controlling the overall system are not utilised. If the DC/DC stage is used to vary the DC link voltage with six times the ACside frequency, a pulse width modulation (PWM) of always only one phase of the DC/AC stage is sufficient to achieve three-phase sinusoidal output currents. The clamping of two phases (denoted as 1/3 PWM) leads to a drastic reduction of the DC/AC stage switching losses, which is further accentuated by a DC link voltage which is lower than for the conventional modulation schemes. This paper details the operating principle of a three-phase buck-boost converter system using 1/3 PWM and outlines an appropriate control system design. Subsequently, the switching losses and the voltage/current stresses on the converter components are analytically derived. There, a more than 66% reduction of the DC/ AC stage switching losses is calculated without any increase of the stress on the remaining converter components. The theoretical considerations are finally verified on a hardware demonstrator, where the proposed modulation strategy is experimentally compared against several conventional modulation techniques and its clear performance advantages are validated.

*Index Terms*—Battery charger, control system design, modulation strategy, variable-speed drives, wide input-output voltage range.

## I. INTRODUCTION

THREE-PHASE DC/AC converter systems for E-mobility applications are currently in high demand. Such threephase converters appear either in inverter systems, such as variable-speed motor drives [1], [2], or in three-phase pulse width modulation (PWM) rectifier systems, used for fast battery charging [3], [4]. Since both power electronics systems are typically installed on a vehicle, it is required that the converters are highly efficient while maintaining a high power density. At the same time, three-phase inverters and/or rectifiers in E-mobility applications have to cope with a wide inputoutput voltage range.

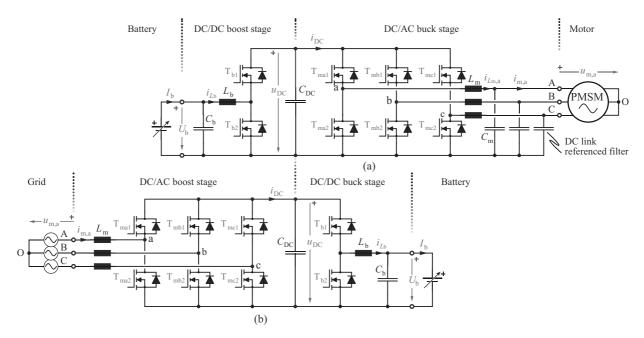

In particular, a motor drive supplied by a battery must generate a controllable three-phase output AC voltage in an amplitude range  $\hat{U}_{\rm m} = 0...\hat{U}_{{\rm m,max}}$ . Simultaneously, the input battery DC voltage varies depending on the state-ofcharge, loading and temperature between  $U_{\rm b} = U_{\rm b,min}...U_{\rm b,max}$ . Accordingly, the operation area of the inverter system is defined by all possible combinations of the DC input and the AC output voltage. As the motor line-to-line voltage amplitude  $\hat{U}_{\rm m,LL} = \sqrt{3} \hat{U}_{\rm m}$  can exceed the battery voltage  $U_{\rm b}$ , a boost-type DC/DC converter stage that generates an adequately high DC link voltage  $u_{\rm DC}$ , is typically placed in front of the buck-type three-phase DC/AC converter stage as shown in Fig. 1(a).

In analogy, three-phase fast battery chargers also have to operate within a wide voltage operating area. There, the output DC battery voltage varies in a range  $U_{\rm b} = U_{\rm b,min}...U_{\rm b,max}$ depending on the vehicle type and charging status, while the input three-phase grid AC voltage can also fluctuate in a range  $\hat{U}_{\rm m} = \hat{U}_{\rm m,min} \dots \hat{U}_{\rm m,max}$ . The level of  $U_{\rm b}$  can be lower than the input grid line-to-line voltage amplitude  $\hat{U}_{m,LL} = \sqrt{3} \hat{U}_{m}$ . Therefore, a buck-type DC/DC stage that adapts the DC link voltage  $u_{DC}$ to  $U_{\rm b}$  is typically placed after the three-phase boost-type PFC rectifier stage as is shown in Fig. 1(b). All in all, both systems, i.e., the variable-speed motor drive and the battery charging system, feature the same two-stage converter structure, just with opposite direction of the power flow. Unfortunately, this two-stage solution suffers from high switching losses and large heatsink volume originating from the fact that both converter stages are typically independently modulated with a high switching frequency. In the following, the example of a variable-speed motor drive system shown in Fig. 1(a) is analysed in detail, however, the same considerations also apply to the battery charging system of Fig. 1(b).

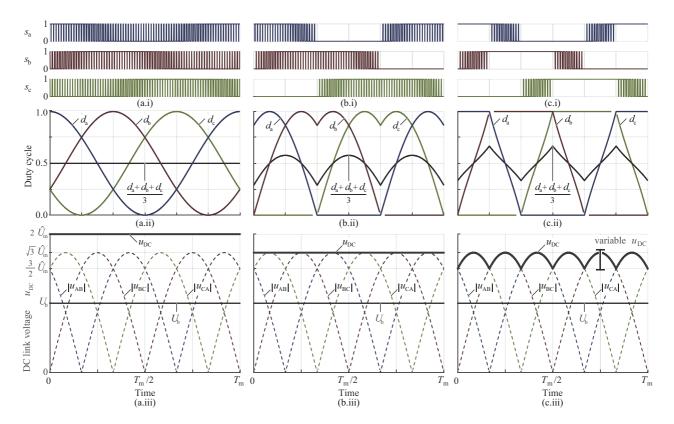

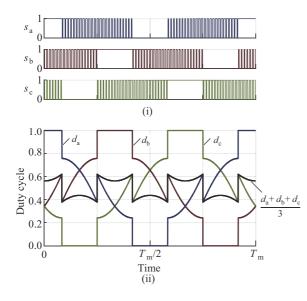

For conventional sinusoidal PWM [5] of the DC/AC stage shown in Fig. 1(a), purely sinusoidally varied duty cycles are employed for all phases (i.e., no third harmonic component [6] is injected), as illustrated in Fig. 2(a.ii). This modulation strategy results in continuous switching of all three DC/AC stage half-bridges (in the following denoted as 3/3 PWM) and accordingly leads to high switching losses (cf., Fig. 2(a.i)). At the same time, 3/3 PWM requires a high DC link voltage  $u_{DC}$ equal or larger than  $2\hat{U}_m(\hat{U}_m$  denotes the motor phase voltage

Manuscript received August 12, 2019; revised October 25, 2019; accepted November 27, 2019. Date of publication March 31, 2020; date of current version February 8, 2020.

All authors are with the Power Electronic Systems Laboratory, ETH Zurich, Switzerland (e-mail: antivachis@lem.ee.ethz.ch).

Digital Object Identifier 10.24295/CPSSTPEA.2020.00004

Fig. 1. For a variable speed motor drive application (a) supplied by a battery, a DC/DC boost-type converter stage is typically placed in front of the DC/AC converter stage in order to adapt the battery voltage  $U_b$  to the DC link voltage  $u_{DC}$  required for generating the (speed dependent) motor voltage  $\hat{U}_m$ . For a battery charging application (b) supplied from a three-phase AC grid, the battery voltage  $U_b$  can be higher or lower than the grid line-to-line voltage  $\sqrt{3} \hat{U}_m$ . For this reason, a buck-type DC/DC stage is placed after the boost-type DC/AC (rectifier) stage in order to generate a DC output voltage  $U_b$  lower than the DC link voltage  $u_{DC}$ .

Fig. 2. Different PWM strategies of a three-phase two-level DC/AC inverter. (i) Gate signals of the three DC/AC stage bridge-legs. (ii) Duty cycles of the bridge-legs. (iii) DC link voltage  $u_{DC}$ . In (a) the characteristic waveforms of 3/3 PWM are shown, which is characterized by purely sinusoidally varying duty cycles, continuous switching of all three-phases and a high DC link voltage  $u_{DC} = 2\hat{U}_m$ . In (b) the properties for 2/3 PWM are depicted, which allow for the switching of always only two out of three-phases and leaves the third phase clamped to the negative DC link rail. The DC link voltage is varying over time, has a six-pulse shape (resulting from proper control of the DC/DC stage) and is equal to the largest instantaneous motor line-to-line voltage.

amplitude) which is generated by the DC/DC stage, as shown in Fig. 2(a.iii). In order to reduce the switching losses, different clamping methods have been proposed in literature such as discontinuous PWM [7], [8], which always operates only two out of the three DC/AC half-bridges (denoted as 2/3 PWM, cf., Fig. 2(b.i)) and results at least in a 33% reduction of the DC/AC stage switching losses [9]. Typical duty cycles for 2/3 PWM are illustrated in Fig. 2(b.ii). There, negative clamping is used, i.e., at any given point in time, one of the low-side switches of the DC/AC stage is permanently turned-on and clamps the corresponding phase to the negative DC rail. It is noted that 2/3PWM employs non-sinusoidal duty cycles and/or output phase voltages of the DC/AC stage (measured against the negative DC rail) but still allows to generate a purely sinusoidal threephase line-to-line voltage system thanks to the open motor star point O (cf., Fig. 1(a)). Besides lower switching losses, 2/3 PWM results in a lower DC link voltage requirement for the same output voltage modulation range, compared to 3/3 PWM and accordingly leads to a lower voltage stress on the converter components. In particular, the DC link voltage in the case of 2/3 PWM should be equal or higher than the line-to-line motor voltage amplitude  $u_{\rm DC} \ge \sqrt{3} \hat{U}_{\rm m}$  as depicted in Fig. 2(b.iii).

Both, 3/3 PWM and 2/3 PWM, employ a constant DC link voltage  $u_{\rm DC}$  and the DC/DC stage and DC/AC stage are controlled independently. However, a constant DC link voltage  $u_{\rm DC}$  is actually not required. As shown in [10]– [14] the modulation of the DC/DC and DC/AC stages can be synergetically combined which results in a significant performance improvement. If the DC/DC stage is used to vary the DC link voltage with six times the output frequency  $f_{\rm m}$ , a PWM of always only one phase of the DC/AC stage is sufficient to achieve three-phase sinusoidal output currents. The clamping of two phases (denoted as 1/3 PWM in the following) leads to a 66% reduction of the DC/AC stage switching losses compared to 3/3 PWM [15]-[18], and the corresponding DC link voltage is lower than, the conventional modulation schemes. The gating signals and the duty cycles for 1/3 PWM are plotted in Fig. 2(c.i) and (c.ii) respectively, while the timevarying DC link voltage is depicted in Fig. 2(c.iii).

In the following, the 1/3 PWM strategy is explained in more detail (Section II) and an appropriate control structure for the overall converter system is presented. Subsequently, the switching losses of 1/3 PWM are analytically derived and compared against traditional PWM modulation strategies in Section III. Furthermore, the voltage and/or current stresses on the different converter components are calculated in order to allow a complete assessment of the 1/3 PWM scheme. In Section IV, a versatile hardware demonstrator is assembled and tested, employing either 1/3 PWM, 2/3 PWM or 3/3 PWM which enables a comprehensive comparison among the different modulation strategies. Accordingly, the drastic switching loss reduction achieved by means of 1/3 PWM is experimentally verified. Finally, conclusions are drawn in Section V.

#### II. OPERATION PRINCIPLE

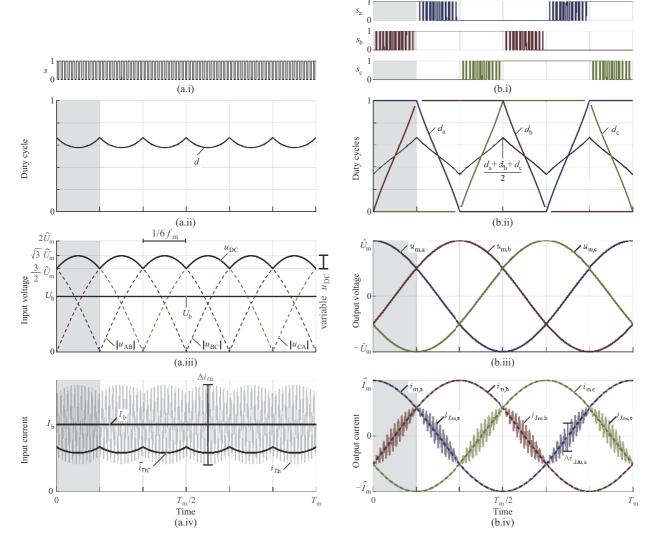

The DC/AC stage operated with 1/3 PWM generates the three-phase sinusoidal motor voltages which are plotted in Fig. 3(b.iii)

$$u_{m,a} = u_{AO} = \hat{U}_{m} \cos \left(2\pi f_{m} t\right)$$

$$u_{m,b} = u_{BO} = \hat{U}_{m} \cos \left(2\pi f_{m} t - \frac{2\pi}{3}\right)$$

$$u_{m,c} = u_{CO} = \hat{U}_{m} \cos \left(2\pi f_{m} t + \frac{2\pi}{3}\right),$$

(1)

where  $f_m$  is the fundamental motor frequency. The 1/3 PWM features a variable DC link voltage  $u_{DC}(t)$  generated by the preceding DC/DC stage, whose shape is always defined by the largest absolute motor line-to-line voltage  $u_{AB}$ ,  $u_{BC}$  or  $u_{CA}$ . Therefore, the DC link voltage has a six-pulse shape that varies between a minimum value of  $\sqrt{3} \hat{U}_m \cos(\pi/6) = 3/2 \hat{U}_m$  and a maximum value of  $\sqrt{3} \hat{U}_m$ . The accordingly required duty cycle *d* of the DC/DC stage high-side switch is shown in Fig. 3(a.ii) and the gating signal is plotted in Fig. 3(a.i). In Fig. 3(a.iv) the battery current  $I_b$  and the DC link current  $\bar{i}_{DC}$  are depicted. The local average value of the DC link current  $\bar{i}_{DC}$  are also fluctuates because the DC link voltage  $u_{DC}$  is not constant. The product  $p(t) = u_{DC}(t) \cdot \bar{i}_{DC}(t)$  of DC link voltage and current is constant in order to ensure a constant instantaneous power delivery p(t) to the motor.

Using the 1/3 PWM scheme, the DC/AC stage is controlled by the duty cycles  $d_a$ ,  $d_b$ ,  $d_c$  depicted in Fig. 3(b.ii). For the first 60° interval of the fundamental period, (highlighted in grey, cf., Fig. 3), where the line-to-line voltage  $|u_{CA}|$  is the largest, the duty cycle of phase *a* is  $d_a = 1$  (i.e., phase a is clamping to the positive DC link rail), the duty cycle of phase c is  $d_c = 0$ (i.e., phase c is clamping to the negative DC link rail), while only the duty cycle of the middle phase b varies within  $d_{\rm b} = 0$ , 1. This means that the six-pulse shaped DC link voltage  $u_{DC}$ is directly applied between phases a and c i.e.,  $u_{ac} = u_{DC}$  and only phase b i.e., the phase with the middle voltage value, is actively switched with PWM. Hence, neglecting the reactive voltages/currents of the  $L_m$ - $C_m$  filter, the motor line-to-line voltage results as  $u_{AC} \sidesimeq u_{ac} = u_{DC}$ . Therefore, during the first 60° an appropriate sinusoidal line-to-line voltage is applied between the motor terminals A and C, even though in the DC/ AC stage no switching action for the corresponding phases a and c is taking place. Accordingly, only the remaining motor terminal B voltage must be actively generated by the DC/ AC stage by means of switching phase b. It is noted that, the open star connection of the motor O,  $u_{m,a} + u_{m,b} + u_{m,c} = 0$ , is a prerequisite for 1/3 PWM, since it allows to generate a threephase voltage system by actively controlling only two voltages at any point in time. For the considered example, only the line-to-line voltage  $u_{\rm ac}$  and the phase voltage  $u_{\rm b}$  are actively controlled. The same principle applies for the remaining 60° intervals of the fundamental period  $T_{\rm m}$ , while the roles of phases a, b and c are exchanged. The sinusoidal motor currents and currents in the filter inductor  $L_{\rm m}$  are plotted in Fig. 3(b. iv). As can be noticed, always only the inductor current of the middle (PWM operated) phase exhibits a pronounced high-

Fig. 3. Characteristic waveforms for 1/3 PWM operation of the converter system of Fig. 1(a), where (a) corresponds to the DC/DC stage and (b) refers to the DC/ AC stage and low switching frequency  $f_s$  is assumed for the visualisation. In (a.i) the gate signal of the DC/DC stage high-side switch and in (a.ii) the duty cycle are depicted. In (a.iii) the variable DC link voltage  $u_{DC}$  featuring a six-pulse shape is highlighted and in (a.iv) the battery current and DC link current are plotted. The gate signals and the duty cycles of the DC/AC stage are illustrated in (b.i) and (b.ii), respectively. Finally, the motor terminal voltages are plotted in (b.iii), while the motor phase currents and filter inductor currents are shown in (b.iv).

frequency current ripple, while the two other inductors conduct smooth sinusoidal motor currents, which in turn also reduces the high-frequency losses in the filter inductors. The DC/ AC stage inductor current ripple shape is unique to the DC link referenced filter of Fig. 1(a), i.e., for filter capacitors  $C_{\rm m}$ connected to the negative DC link rail [19].

In the following, the analytic calculation of fundamental quantities and/or waveforms for the 1/3 PWM is performed. In a first step, the time behaviour of the DC link voltage  $u_{DC}$  is formulated. To this end, the maximum instantaneous line-to-line motor voltage is required which based on (1) has a sixpulse shape and is

$$u_{m,LL,max}(t) = u_{m,max}(t) - u_{m,min}(t),$$

(2)

where  $u_{m,max}(t) = \max \{u_{m,a}, u_{m,b}, u_{m,c}\}$  and  $u_{m,min}(t) = \min \{u_{m,a}, u_{m,c}\}$

$u_{m,b}$ ,  $u_{m,c}$ }. The DC link voltage is subsequently derived (cf., Fig. 3(a.iii)) as

$$u_{\rm DC}(t) = \begin{cases} U_{\rm b} & \text{for } u_{\rm m,LL,max}(t) \leq U_{\rm b} \\ u_{\rm m,LL,max}(t) & \text{for } u_{\rm m,LL,max}(t) > U_{\rm b} \end{cases}.$$

(3)

As long as the actual maximum line-to-line motor voltage  $u_{m,LL,max}(t)$  is below the battery voltage  $U_b$ , the boost-type DC/DC converter cannot control the DC link voltage to a sixpulse shape and thus clamps the DC link voltage  $u_{DC} = U_b$  by permanently turning-on the high-side switch  $T_{b1}$ . On the other hand, as soon as the line-to-line motor voltage amplitude  $\sqrt{3} \hat{U}_m$  exceeds the battery voltage  $U_b$  (for higher speeds), the DC/DC stage can control the DC link voltage to the six-pulse voltage  $u_{DC} = u_{m,LL,max}(t)$ . The duty cycle of the high-side switch

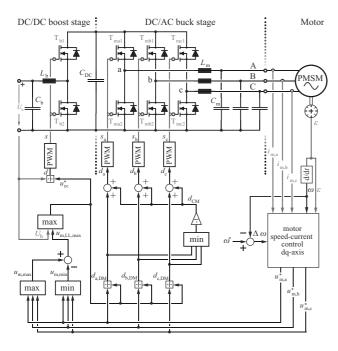

Fig. 4. Block diagram of the proposed control scheme. A cascaded control of the motor speed  $\omega^*$  with an underlying motor torque and/or motor phase current control (reference values  $i^*_{m, [ab,c]}$ ) is assumed, which finally outputs the three machine terminal voltage references  $u^*_{m, [ab,c]}$  which must be generated. Subsequently, the corresponding duty cycles of the DC/DC stage and DC/AC stage are derived and are translated into gating signals.

T<sub>b1</sub> of the DC/DC stage is then given as (cf., Fig. 3(a.i) and (a.ii))

$$d(t) = \frac{U_{\rm b}}{u_{\rm DC}(t)}.\tag{4}$$

In a second step, the duty cycles  $d_a$ ,  $d_b$  and  $d_c$  of the DC/ AC stage for 1/3 PWM are calculated, which is based on the same algorithm as used for 2/3 PWM [20] (cf., Fig. 2(b)). The duty cycle of each phase ranges within 0–1 and is split into a differential-mode (DM) and a common-mode (CM) part. The DM part is purely sinusoidal and is calculated for phases a, b and c based on (1), (3) as

$$d_{\text{{a,b,c}},\text{DM}}(t) = \frac{U_{\text{m,{a,b,c}}}(t)}{u_{\text{DC}}(t)}.$$

(5)

The CM part or offset of the duty cycle, which is common to all three phases, is

$$d_{\rm CM}(t) = -\min\{d_{\rm aDM}(t), d_{\rm bDM}(t), d_{\rm cDM}(t)\}.$$

(6)

The total duty cycle is the sum of both components

$$d_{\{a,b,c\}}(t) = d_{\{a,b,c\},DM}(t) + d_{CM}(t).$$

(7)

Based on these duty cycle calculations, when the instantaneous motor line-to-line voltage is lower than the battery voltage  $u_{m,LL,max}(t) \leq U_b$ , the DC/DC stage clamps the DC link voltage to the battery voltage  $u_{DC} = U_b$ . Then, the DC/ AC stage operates with 2/3 PWM resulting in the waveforms shown in Fig. 2(b). On the other hand, for  $u_{m,LL,max}(t) \geq U_b$ , the

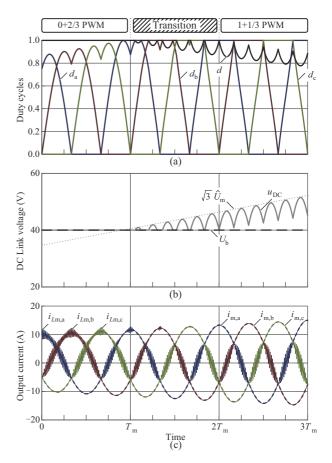

Fig. 5. Simulation results showing a smooth transition from 2/3 PWM to 1/3 PWM, where the motor voltage is gradually increased. When the motor voltage is low  $(\hat{U}_{\rm m} \leq U_{\rm b}/\sqrt{3})$ , 2/3 PWM is employed. When the motor voltage is high  $(\hat{U}_{\rm m} > 2U_{\rm b}/3)$ , exclusively 1/3 PWM is used. During the transition, where  $U_{\rm b}/\sqrt{3} < \hat{U}_{\rm m} \leq 2U_{\rm b}/3$  is valid, 2/3 PWM and 1/3 PWM are occurring alternately.

DC/DC stage is activated and generates a DC link voltage  $u_{DC} = u_{m,LL,max}(t)$ , which in case of  $\hat{U}_m \ge 2U_b/3$  shows a six-pulse shape. Then, the DC/AC stage is operating with 1/3 PWM (cf., Fig. 3(b.ii)). In other words, the 1/3 PWM results from the generalization of 2/3 PWM, since the same algorithm (cf., Fig. 4) is used for the calculation of the DC/AC stage duty cycles throughout the whole DC link operation range. Depending on the relationship between the battery voltage  $U_b$  and the motor voltage  $\hat{U}_m$ , the converter can transition continuously from 2/3 PWM to 1/3 PWM and vice-versa.

The 1/3 PWM is incorporated in a block diagram of a cascaded motor speed control in Fig. 4. There, the threephase motor currents  $i_{m,a}$ ,  $i_{m,b}$ ,  $i_{m,c}$  as well as the motor rotation angle  $\varepsilon$  and the motor speed  $\omega$  are measured and fed as input to the motor controller. A standard cascaded speedtorque/ current motor controller in a d-q reference frame is employed. The motor controller defines the motor terminal AC voltage references  $u_{m,a}^*$ ,  $u_{m,b}^*$ ,  $u_{m,c}^*$  which must be generated. According to the reference voltages, the DC/DC stage duty cycle *d* is calculated employing (2)–(4). At the same time, the DC/AC stage duty cycles  $d_a$ ,  $d_b$  and  $d_c$  are derived based on (5)–(7).

A transition example from 2/3 PWM to 1/3 PWM is shown in Fig. 5. There, the motor voltage and current is gradually

increased, as highlighted in Fig. 5(c). During  $t < T_{\rm m}$ , the motor voltage is low,  $\hat{U}_{\rm m} \leq U_{\rm b}/\sqrt{3}$ , therefore exclusively 2/3 PWM is employed. In particular, the DC/DC stage is deactivated, which means that the battery is directly connected to the DC link  $u_{\rm DC} = U_{\rm b}$ . This operating regime is denoted as 0+2/3 PWM in Fig. 5, '0' indicating that the DC/DC stage is not switched and '2/3' denoting that two out of three DC/AC half-bridges are switched. In contrast, for  $t > 2T_m$ , the motor voltage is high,  $\hat{U}_{\rm m} \ge 2U_{\rm b}/3$ , therefore exclusively 1/3 PWM is employed. In this case, the DC/DC stage is activated and controls the DC link voltage to  $u_{DC} = u_{m,LL,max}(t)$ . This operating regime is denoted as 1+1/3 PWM, with '1' indicating that the DC/DC stage is switched. During  $T_{\rm m} < t \leq 2T_{\rm m}$ , the motor voltage is  $U_{\rm b}/\sqrt{3} < \hat{U}_{\rm m} \leq 2U_{\rm b}/3$  and both modulation schemes are alternatively employed, while a smooth transition between the two modulation regimes is achieved without unwanted transients.

It is noted that during 1/3 PWM operation of the DC/AC stage, the motor voltage cannot be abruptly increased. In order to increase the motor line-to-line voltage, a higher, six-pulse shaped DC link voltage  $u_{DC}(t)$  must first be generated by the DC/DC stage. Therefore, the maximum rate at which the motor line-to-line voltage can be increased is defined by the dynamic response of the DC/DC stage. Consequently, 1/3 PWM exhibits a limited control bandwidth of the motor line-to-line voltage, depending on the value of the DC link capacitor  $C_{\rm DC}$ . A large  $C_{\rm DC}$  value would slow down the dynamics of the DC/ DC stage and hence would impede the converter from quickly changing the motor line-to-line voltage. For this reason, a careful selection of the DC link capacitor  $C_{\rm DC}$  is necessary, as described later in Section III-E. The 1/3 PWM is hence not suitable for drive systems where high dynamic response of the motor torque/speed is required. Instead, 1/3 PWM is more suitable for drive systems with low dynamics that are mostly operated under steady state conditions, as compressor drives.

#### **III. COMPONENT STRESSES**

In this section, the switching losses and the voltage/current stresses on the different converter components are calculated for the drive system with the specifications of Table I. The analysis is performed for the 1/3 PWM modulation strategy as well as for the conventional 2/3 PWM and 3/3 PWM over the whole operating range of the motor. For the considered application example, the battery voltage ranges within  $U_{\rm b}$ = 40...60 V, however, for the following analysis the lowest battery voltage  $U_{\rm b} = 40$  V is considered, where the highest current stress in the DC/DC stage appears. The motor voltage ranges within  $\hat{U}_{\rm m} = 0...40$  V (phase amplitude), while the maximum motor voltage  $\hat{U}_{\rm m} = 40$  V operation yields the highest component stresses. For the sake of simplicity a resistive load  $R = 3\hat{U}_{m,max}/2P_{max} = 4.8 \ \Omega$  is assumed and hence a unity power factor (PF),  $\cos(\varphi) = 1$ , is obtained. A comprehensive analysis of the component stresses for a PF  $\cos(\varphi) < 1$  is given

TABLE I

MOTOR DRIVE SPECIFICATIONS. THE WORST CASE OPERATING CONDITION OF THE TWO-STAGE DC/AC CONVERTER, WHERE THE HIGHEST COMPONENT STRESSES APPEAR, IS HIGHLIGHTED IN BOLD.

| Parameter                                                                         | Value                               |

|-----------------------------------------------------------------------------------|-------------------------------------|

| Battery voltage (Ub)                                                              | <b>40</b> -60 V                     |

| Battery current $(I_b)$                                                           | $0-12.5$ A (for $U_{\rm b} = 40$ V) |

| Motor fundamental frequency $(f_m)$                                               | 0- <b>400</b> Hz                    |

| Motor voltage amplitude $(\hat{U}_m)$                                             | 0- <b>40</b> V(phase)               |

| Motor current amplitude $(\hat{I}_m)$                                             | 0- <b>8.3</b> A                     |

| Modulation index $\left(M = \frac{\hat{U}_{\rm m}}{\frac{1}{2} U_{\rm b}}\right)$ | $0-2$ (for $U_{\rm b} = 40$ V)      |

| Power (P)                                                                         | 0– <b>500</b> W                     |

in Appendix A. In order to further simplify the analysis, the current ripple of the DC/DC stage inductor  $L_{\rm b}$  and the DC/AC stage filter inductors  $L_{\rm m}$  is neglected, unless stated otherwise.

In a typical DC/AC two-level inverter, the modulation index is defined as the ratio between motor phase voltage amplitude and half the DC link voltage,  $M_{\rm m} = 2\hat{U}_{\rm m}/u_{\rm DC}$  and ranges within 0–1.15. However, since a DC/DC stage precedes the DC/ AC stage in the case at hand, it is desirable to relate  $\hat{U}_{\rm m}$  to the battery supply voltage  $U_{\rm b}$  instead of  $u_{\rm DC}$ . Therefore, the modulation index is redefined as the ratio between motor and half of the battery voltage

$$M = \frac{U_{\rm m}}{\frac{1}{2}U_{\rm b}}.$$

(8)

The modulation index *M* can exceed the value of 1.15 thanks to the DC/DC stage that can boost the supplying battery voltage. For the system at hand (cf., Table I) the modulation index ranges within M = 0...2. Thereby, the transferred power *P*, battery current  $I_b$  and motor fundamental phase current amplitude  $\hat{I}_m$  can be derived as a function of the modulation index

$$P = M^2 \frac{3U_{\rm b}^2}{8R}, I_{\rm b} = M^2 \frac{3U_{\rm b}}{8R}, \hat{I}_{\rm m} = M \frac{U_{\rm b}}{2R}.$$

(9)

#### A. Semiconductor Voltage Stress

Firstly, the voltage stress on the power semiconductor devices is analysed. The semiconductors of the DC/DC and of the DC/ AC stage are blocking and/or switching the DC link voltage  $u_{DC}$ . A higher DC link voltage  $u_{DC}$  results in higher switching losses and hence a higher thermal stresses on the semiconductor devices. Furthermore, the maximum DC link voltage  $u_{DC,max}$ with some additional safety margin dictates the voltage rating of the employed semiconductor devices. The maximum DC link voltage always appears for the maximum motor voltage (in the case at hand represented by ( $M=M_{max}=2$ ), and is

$$U_{\rm DC,max} \Big|_{3/3 \text{ PWM}} = 2\hat{U}_{\rm m,max} = M_{\rm max} U_{\rm b}$$

$$U_{\rm DC,max} \Big|_{2/3 \text{ PWM}} = \sqrt{3} \hat{U}_{\rm m,max} = M_{\rm max} \frac{\sqrt{3}}{2} U_{\rm b} \qquad (10)$$

$$U_{\rm DC,max} \Big|_{1/3 \text{ PWM}} = \sqrt{3} \hat{U}_{\rm m,max} = M_{\rm max} \frac{\sqrt{3}}{2} U_{\rm b}.$$

Therefore, both the 1/3 PWM and 2/3 PWM schemes lead to a 13% voltage stress reduction compared to 3/3 PWM.

## B. Semiconductor Switching Losses

The reduction of the switching losses  $P_{sw}$  of the DC/AC stage is the main advantage of the 1/3 PWM modulation, compared to conventional 2/3 PWM. In the following, the switching losses for the 1/3 PWM are analytically derived and compared against the conventional modulation strategies. To this end, the switching energy dissipation  $E_{sw}$  for each hard switching transition is approximated as a linear function of the commutation current  $I_{sw}$  as

$$E_{\rm sw}(I_{\rm sw}) = k_0 + k_1 I_{\rm sw}.$$

(11)

Accordingly, the switching power dissipation for a switching frequency  $f_s$  is

$$P_{\rm sw}(I_{\rm sw}) = f_{\rm s}E_{\rm sw} = f_{\rm s}(k_0 + k_1I_{\rm sw}).$$

(12)

The parameters  $k_0$  and  $k_1$  depend on the switched voltage  $U_{sw}$ . Namely the parameter  $k_0$  represents the constant part of the switching losses and is calculated in literature [21] (assuming unipolar power semiconductors) as

$$k_0(U_{\rm sw}) = Q_{\rm oss}(U_{\rm sw}) \cdot U_{\rm sw}, \qquad (13)$$

where  $Q_{oss}$  is the electric charge stored in the non-linear output parasitic capacitance  $C_{oss}$  of the MOSFET

$$Q_{\rm oss}(U_{\rm sw}) = \int_{0}^{U_{\rm sw}} C_{\rm oss}(u) \mathrm{d}u. \tag{14}$$

For the case at hand, the parameter  $k_1(U_{sw})$  depends on the semiconductor technology and the gate driver configuration [22], [23]. Since the DC link voltage does not drastically change for the different modulation strategies as shown in (10), it can be assumed for a first step worst case consideration that the parameters  $k_0$  and  $k_1$  are the same regardless of the modulation strategy.

The expression given in (12) is used for the calculation of the switching losses of the DC/DC stage, which are the same regardless of the modulation strategy

$$P_{\rm sw} = f_{\rm sb} \left( k_0 + k_1 I_{\rm b} \right). \tag{15}$$

Subsequently the expression (12) for the switching losses is applied to the DC/AC stage, where the commutation current varies over time in a sinusoidal fashion. In order to account for

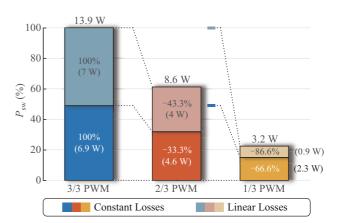

Fig. 6. Switching losses of the DC/AC stage under maximum motor voltage, i.e., M = 2 for the case at hand. For the calculations a unity power factor cos ( $\varphi$ ) = 1 is assumed. Numerical values are derived for the worst case operating conditions of Table I and the parameters of Table VI.

the sinusoidal current waveform, an integration of (12) over the fundamental period  $T_{\rm m}$  is performed. In the case of 3/3 PWM, the resulting sum of the switching losses for all three bridge-legs of the DC/AC stage (for assumed unity power factor  $\cos(\varphi) = 1$  load condition) is

$$P_{\rm sw} |_{3/3 \rm PWM} = 3f_{\rm s,m} \left( k_0 + k_1 \frac{2}{\pi} \hat{I}_{\rm m} \right).$$

(16)

The switching losses comprise two components, a constant part  $3f_{s,m}k_0$  which is independent of the converter load and a linear part  $3f_{s,m}k_12/\pi \hat{I}_m$  (proportional to the average value of a sinusoidal current half cycle) which increases linearly with the output current  $\hat{I}_m$  and is used to characterise the load state. The maximum switching losses of the DC/AC stage occur for maximum motor voltage/power i.e., M = 2 and are illustrated in Fig. 6. Similarly, the switching losses of the DC/AC stage employing the 2/3 PWM are derived using (12)

$$P_{\rm sw} \Big|_{2/3 \, \rm PWM} = 3f_{\rm sm} \left[ \frac{2}{3} k_0 + \underbrace{\left(1 - \frac{\sqrt{3}}{4}\right)}_{-43.3\%} k_1 \frac{2}{\pi} \hat{I}_{\rm m} \right]. (17)$$

The 2/3 PWM yields a reduction of the constant part of the switching losses by 33.3% and of the linearly current dependent part of the switching losses by 43.3%, compared to 3/3 PWM, since each phase is switched for  $2T_m/3$  of the fundamental period  $T_m$ . Finally, the switching losses for 1/3 PWM are calculated,

$$P_{\rm sw} \Big|_{1/3 \text{ PWM}} = 3f_{\rm sm} \left[ \frac{1}{3} k_0 + \underbrace{\left(1 - \frac{\sqrt{3}}{2}\right)}_{-86.6\%} k_1 \frac{2}{\pi} \hat{I}_{\rm m} \right]. (18)$$

With 1/3 PWM a drastic reduction of the switching losses is achieved, since each phase is switched only for  $T_m/3$  of the fundamental period  $T_m$ . Namely, a 66.6% reduction of the constant part and a 86.6% reduction of the linear part is possible compared to 3/3 PWM. Furthermore, 1/3 PWM notably outperforms 2/3 PWM in terms of switching losses. The switching losses of 2/3 PWM and 1/3 PWM for maximum motor voltage/current and M = 2 are plotted in Fig. 6. It is noted, that the switching losses reduction achieved by means of 1/3 PWM, simultaneously enables a lower semiconductor heatsink volume [24].

# C. Semiconductor Current Stress

For the calculation of the conduction losses, the current ripple of the DC/DC stage inductor  $L_{\rm b}$  and DC/AC stage filter inductor  $L_{\rm m}$  is neglected. Accordingly, the resulting total conduction losses are independent of the modulation strategy of both stages and are equal to

$$P_{\rm cd} = I_{\rm b}^2 R_{\rm Tb,on} + \frac{3}{2} I_{\rm m}^2 R_{\rm Tm,on},$$

(19)

where  $R_{\text{Tb,on}}$  and  $R_{\text{Tm,on}}$  are the on-state resistances of the DC/ DC and DC/AC stage (unipolar) power semiconductor devices, respectively. However, the sharing of the conduction losses among the semiconductor devices, i.e., the sharing of the RMS current stress between the high-side and low-side switches, changes depending on the modulation strategy. It is therefore important to analyse the current stress for each semiconductor device individually in order to provide a basis for the proper selection of the components in the design process.

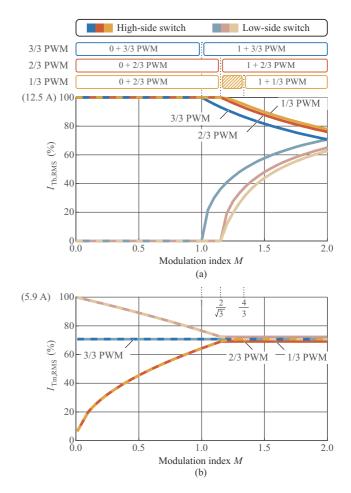

The RMS current stress of  $T_{b1}$  and  $T_{b2}$  of the DC/DC stage is analytically derived for the different modulation techniques over the whole modulation range and results as

$$I_{\rm Tb1,RMS} \Big|_{3/3 \text{ PWM}} = \begin{cases} I_{\rm b} & \text{for } M \leq 1 \\ I_{\rm b} \sqrt{\frac{1}{M}} & \text{for } M > 1 \end{cases}$$

(20)

$$I_{\text{Tb2,RMS}} \Big|_{3/3 \text{ PWM}} = \begin{cases} 0 & \text{for } M \leq 1 \\ I_{\text{b}} \sqrt{1 - \frac{1}{M}} & \text{for } M > 1 \end{cases}$$

(21)

$$I_{\text{Tb1,RMS}}\Big|_{2/3 \text{ PWM}} = \begin{cases} I_{\text{b}} & \text{for } M \leq \frac{2}{\sqrt{3}} \\ I_{\text{b}}\sqrt{\frac{2}{\sqrt{3}M}} & \text{for } M > \frac{2}{\sqrt{3}} \end{cases} (22)$$

$$I_{\text{Tb2,RMS}}\Big|_{2/3 \text{ PWM}} = \begin{cases} 0 & \text{for } M > \frac{2}{\sqrt{3}} \\ I_{\text{b}}\sqrt{1 - \frac{2}{\sqrt{3}M}} & \text{for } M > \frac{2}{\sqrt{3}} \end{cases} (23)$$

$$I_{\text{Tb1,RMS}}\Big|_{1/3 \text{ PWM}} = \begin{cases} I_{\text{b}} & \text{for } M \leq \frac{2}{\sqrt{3}} \\ I_{\text{b}}\sqrt{\frac{6\ln(3)}{\sqrt{3}\pi M}} & \text{for } M > \frac{4}{3} \end{cases} (24)$$

$$\begin{bmatrix} 0 & \text{for } M \leq \frac{2}{\sqrt{3}} \end{bmatrix} (24)$$

$$I_{\text{Tb2,RMS}} \Big|_{1/3 \text{ PWM}} = \begin{cases} \sqrt{3} & \sqrt{3} \\ I_{\text{b}} \sqrt{1 - \frac{6 \ln(3)}{\sqrt{3} \pi M}} & \text{for } M > \frac{4}{3} \end{cases} .(25)$$

Fig. 7. Semiconductor device current stress for the three modulation strategies over the whole operating range, M = 0...2 considered in the case at hand. (a) Normalized RMS current of DC/DC stage high- and low-side semiconductor devices, with respect to the DC/DC stage RMS inductor current  $I_{Lb,RMS}$ . (b) Normalized RMS current of DC/AC stage high-and low-side semiconductor devices, with respect to the DC/AC stage RMS inductor current  $I_{Lm,RMS}$ . Numerical values are derived for the worst case operating conditions of Table I and the parameters of Table VI.

The semiconductor devices current stresses, normalized with respect to the DC/DC stage inductor ( $L_b$ ) RMS current  $I_{Lb,RMS} = I_b$ , are shown in Fig. 7(a). It should be noted that the sum of the instantaneous currents of the T<sub>b1</sub> and T<sub>b2</sub> semiconductor devices is equal to the  $L_b$  inductor current

$$\dot{i}_{\text{Tb1}}(t) + \dot{i}_{\text{Tb2}}(t) = \dot{i}_{Lb}(t).$$

(26)

However, the relationship between the RMS currents is nonlinear,

$$I_{\rm Tb1,RMS}^2 + I_{\rm Tb2,RMS}^2 = I_{\rm Lb,RMS}^2.$$

(27)

When the modulation index is low and the DC/DC stage is deactivated (e.g., 1/3 PWM and  $M \le 2/\sqrt{3}$ ), the highside switch T<sub>b1</sub> of the DC/DC stage is clamped and therefore experiences the whole RMS current stress. However, this is typically not a problem since for low modulation indexes (low DC/AC stage output voltage and/or motor speed) the power P and thus battery current  $I_b$  is anyway low. The 1/3 PWM leads to asymmetric current distribution between the high-side and the low-side switches similar to the 2/3 PWM, while the asymmetry reduces as the modulation index and/or the transferred power increases. In summary, the asymmetric current distribution caused by 1/3 PWM for low modulation index M, does not require over-dimensioning of the DC/DC stage semiconductor devices. The (symmetric) stresses for high modulation indexes M are higher than the (asymmetric) stresses for low values of M, and hence dominate the dimensioning of the DC/DC stage semiconductors.

Similarly, the RMS current stress of the semiconductor devices  $T_{m1}$  and  $T_{m2}$  of the DC/AC stage is analytically calculated as

$$I_{\rm Tm1,RMS} \Big|_{3/3 \text{ PWM}} = I_{\rm Tm2,RMS} \Big|_{3/3 \text{ PWM}} = \frac{\hat{I}_{\rm m}}{\sqrt{2}} \frac{1}{\sqrt{2}} \quad (28)$$

$$I_{\rm Tm1,RMS} \Big|_{2/3 \text{ PWM}} = \begin{cases} \frac{\hat{I}_{\rm m}}{\sqrt{2}} \sqrt{\frac{3\sqrt{3}}{4\pi}} & \text{for } M \leq \frac{2}{\sqrt{3}} \\ \frac{\hat{I}_{\rm m}}{\sqrt{2}} \sqrt{\frac{3}{2\pi}} & \text{for } M > \frac{2}{\sqrt{3}} \end{cases} \quad (29)$$

$$I_{\rm Tm2,RMS} \Big|_{2/3 \text{ PWM}} = \begin{cases} \frac{\hat{I}_{\rm m}}{\sqrt{2}} \sqrt{\frac{3\sqrt{3}}{2\pi}} & \text{for } M > \frac{2}{\sqrt{3}} \\ \frac{\hat{I}_{\rm m}}{\sqrt{2}} \sqrt{1 - \frac{3\sqrt{3}}{4\pi}} & \text{for } M \leq \frac{2}{\sqrt{3}} \\ \frac{\hat{I}_{\rm m}}{\sqrt{2}} \sqrt{1 - \frac{3}{2\pi}} & \text{for } M > \frac{2}{\sqrt{3}} \end{cases} \quad (30)$$

$$I_{\text{Tm1,RMS}} \Big|_{1/3 \text{ PWM}} = \begin{cases} \frac{\hat{I}_{\text{m}}}{\sqrt{2}} \sqrt{\frac{3\sqrt{3} M}{4\pi}} & \text{for } M \leq \frac{2}{\sqrt{3}} \\ \frac{\hat{I}_{\text{m}}}{\sqrt{2}} \frac{1}{\sqrt{2}} & \text{for } M > \frac{4}{3} \end{cases}$$

(31)

$$I_{\text{Tm2,RMS}} \Big|_{1/3 \text{ PWM}} = \begin{cases} \frac{\hat{I}_{\text{m}}}{\sqrt{2}} \sqrt{1 - \frac{3\sqrt{3} M}{4\pi}} & \text{for } M \leq \frac{2}{\sqrt{3}} \\ \frac{\hat{I}_{\text{m}}}{\sqrt{2}} \frac{1}{\sqrt{2}} & \text{for } M > \frac{4}{3} \end{cases}$$

(32)

The semiconductor devices current stresses, normalized with respect to the DC/AC stage inductor ( $L_{\rm m}$ ) RMS current  $I_{Lm,RMS} = \hat{I}_{\rm m}/\sqrt{2}$ , are shown in Fig. 7(b). The 3/3 PWM modulation results in symmetric current sharing between the high-side and low-side semiconductor devices of the DC/AC stage (28). In contrast, 2/3 PWM and 1/3 PWM both lead to a similar asymmetric current stress on the semiconductor devices (29)–(32). In particular, higher current stress appears on the low-side switch of the DC/AC stage T<sub>ma2</sub> when the modulation index is low (e.g.,  $M \leq 2/\sqrt{3}$  and 1/3 PWM). As the modulation index increases (e.g., M > 4/3 and 1/3 PWM) the RMS current

sharing becomes symmetric. The asymmetric current stress for low modulation indexes (i.e., low motor voltage  $\hat{U}_{\rm m}$  and/or motor speed) is critical. Care has to be taken with the thermal design of the low-side switches T<sub>m2</sub>, such that they can conduct the nominal motor current  $\hat{I}_{\rm m}$  and hence ensure nominal motor torque during motor acceleration, starting from standstill. It is noted that there is an alternative 1/3 PWM and 2/3 PWM implementation which ensures symmetric current distribution for the whole operating range and is analysed in Appendix B.

#### D. Inductive Components

The inductor losses are investigated, in a first step. It is assumed that a two-stage DC/AC converter system is designed for conventional 3/3 PWM (e.g., features a cooling system that can withstand the high switching losses of the 3/3 PWM) and that the inductive components cannot be changed. In particular, the DC/DC stage features an inductance  $L_{\rm b}$  and the DC/AC stage employs an inductance  $L_{\rm m}$ , regardless of the modulation scheme.

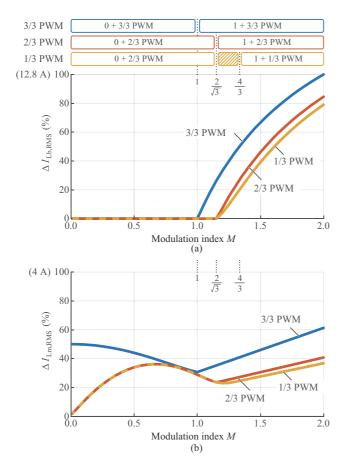

In general, there is a direct relation between the inductor losses and the RMS inductor current ripple  $\Delta I_{L,RMS}$ , as a high RMS current ripple results in a high frequency RMS flux density and hence substantial core losses [25]. In addition, high RMS current ripple causes high-frequency winding losses due to skin and proximity effect. Therefore, the RMS inductor current ripple  $\Delta I_{L,RMS}$  is a reasonable performance indicator for the design of the inductive components and is calculated in the following for the different modulation strategies over the whole operating range.

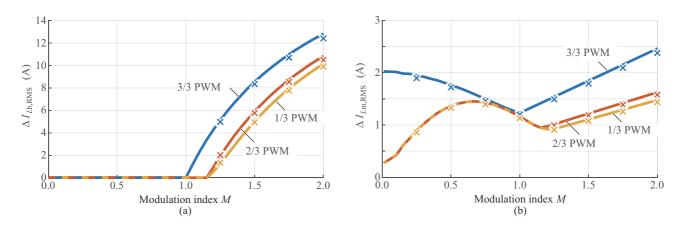

For the DC/DC stage the same inductance value  $L_b$  is considered regardless of the modulation strategy. Subsequently, the RMS inductor current ripple  $\Delta I_{Lb,RMS}$  is calculated for the considered modulation strategies based on a numeric solver (i.e., no analytical solution). The RMS inductor current ripple, normalized with respect to the worst case local RMS current ripple,

$$\Delta I_{Lb,RMS,max} = \frac{\hat{U}_{m,max}}{4\sqrt{3}f_{sb}L_{b}},$$

(33)

is plotted in Fig. 8(a). When the modulation index is low and the DC/DC stage is deactivated (e.g., 1/3 PWM for  $M \le 2/\sqrt{3}$ ), the high-side switch T<sub>b1</sub> of the DC/DC stage is clamped and therefore no current ripple appears on the inductor  $L_b$ . As the modulation index increases (e.g., 1/3 PWM for  $M > 2/\sqrt{3}$ ) the inductor gradually conducts a current with increasing ripple. Due to the lower DC link voltage for the same DC/AC stage output voltage, 1/3 PWM exhibits significantly lower RMS inductor current ripple compared to 3/3 PWM but only slightly lower ripple compared to 2/3 PWM.

Similarly, for the DC/AC stage the same inductance value  $L_{\rm m}$  is considered independent of the modulation strategy. The RMS inductor current ripple  $\Delta I_{Lm,RMS}$  is calculated for all modulation strategies over the complete operating range based on a numeric solver (i.e., no analytic solution). The RMS

Fig. 8. Inductor RMS current ripple for different modulation strategies over the whole operating range M = 0, ..., 2 considered in the case at hand. (a) The normalized RMS current ripple of the DC/DC stage inductor  $L_b$  is depicted. (b) The normalized RMS current ripple of the DC/AC stage filter inductor  $L_m$  is plotted. Numerical values are derived for the worst case operating conditions of Table I and the parameters of Table VI.

inductor current ripple, normalized with respect to the worst case local RMS current ripple

$$\Delta I_{Lm,RMS,max} = \frac{\hat{U}_{m,max}}{4\sqrt{3} f_{sm} L_m},$$

(34)

is depicted in Fig. 8(b). In particular for 1/3 PWM, when the modulation index is low,  $M \leq 2/\sqrt{3}$ , the DC link voltage is constant and equal to the battery voltage  $u_{\rm DC} = U_{\rm b}$ . As the modulation index gradually increases (i.e.,  $M = 0 \rightarrow 2/\sqrt{3}$ ), the current ripple RMS value initially increases, reaches a local maximum value and then decreases [19]. When the modulation index exceeds the threshold value of  $M = 2/\sqrt{3}$ , the DC/DC stage is activated and the DC link voltage increases. Accordingly, the ripple of the DC/AC filter inductor which is proportional to the DC link voltage also increases. In general, 1/3 PWM yields similar current ripple RMS value as the 2/3 PWM but lower current ripple compared to 3/3 PWM (21% reduction of  $\Delta I_{Lm,RMS}$ % occurs for M = 2).

In a more general case, where there is not a pre-existing converter designed for 3/3 PWM, different inductance values

can be advantageously selected for the different modulation strategies. Besides a smaller heatsink volume for the DC/AC stage (thanks to the low switching losses), the 1/3 PWM allows for smaller inductance values, which translates into further volume reduction [26]. Accordingly, the minimum required inductance value  $L_b$  of the DC/DC stage and the inductance  $L_m$  of the DC/AC stage are analytically calculated.

In order to calculate the required inductance  $L_b$ , a worst case current ripple amplitude  $\Delta I_{Lb,PK}$  (single side peak value) is assumed. The same current ripple limit applies regardless of the modulation strategy and the required inductance is given by

$$L_{\rm b} \ge \frac{d_{\rm min}(1 - d_{\rm min})U_{\rm DC,max}}{2\Delta I_{Lb,\rm PK}f_{\rm s,b}}, \ d_{\rm min} = \frac{U_{\rm b}}{U_{\rm DC,max}},$$

(35)

where  $f_{s,b}$  is the switching frequency of the DC/DC stage. Applying (35) to 3/3 PWM, where  $U_{DC,max} = 2\hat{U}_{m,max}$  (10), the required inductance is

$$L_{\rm b}|_{\rm _{3/3 \ PWM}} \ge \frac{\hat{U}_{\rm m,max}}{4\Delta I_{\rm Lb,PK} f_{\rm s,b}}.$$

(36)

Subsequently, (35) is applied to 1/3 PWM and 2/3 PWM. The 1/3 PWM and 2/3 PWM schemes require the same inductance value because both modulation schemes feature the same maximum instantaneous DC link voltage  $U_{\text{DC,max}} = \sqrt{3}$   $\hat{U}_{\text{m,max}}$  (10). The inductance is calculated as

$$L_{\rm b}|_{1/3 \text{ PWM}} = L_{\rm b}|_{2/3 \text{ PWM}} \ge \frac{\left(1 - \frac{1}{\sqrt{3}}\right)\hat{U}_{\rm m,max}}{2\Delta I_{Lb,\rm PK}f_{\rm s,b}}.$$

(37)

Consequently, 2/3 PWM and 1/3 PWM require 15% lower inductance compared to 3/3 PWM for the DC/DC stage, resulting in an accordingly higher power density.

For the calculation of the DC/AC stage filter inductance  $L_{\rm m}$ , a worst case current ripple amplitude  $\Delta I_{Lm,PK}$  (single side peak value) is considered. The same limit applies for all possible modulation strategies and the required inductance is given by

$$L_{\rm m} \ge \frac{U_{\rm DC,max}}{8\Delta I_{Lm,\rm PK} f_{\rm s,m}},\tag{38}$$

where  $f_{s,m}$  is the switching frequency of the DC/AC stage. Applying (38) to 3/3 PWM, the required inductance is

$$L_{\rm m}|_{\rm 3/3 \ PWM} \ge \frac{\hat{U}_{\rm m,max}}{4\Delta I_{Lm,\rm PK} f_{\rm s,m}}.$$

(39)

The 2/3 PWM and 1/3 PWM schemes require the same DC/ AC stage inductance  $L_{\rm m}$ , which based on (38) is

$$L_{\rm m}|_{1/3 \text{ PWM}} = L_{\rm m}|_{2/3 \text{ PWM}} \ge \frac{\sqrt{3} \hat{U}_{\rm m,max}}{8\Delta I_{Lm,\rm PK} f_{\rm s,m}}.$$

(40)

Accordingly, 2/3 PWM and 1/3 PWM are reducing the DC/AC stage filter inductance requirement by 13% and hence yield a smaller inductor volume compared to 3/3 PWM.

#### E. DC Link Capacitor

The DC link capacitor  $C_{\rm DC}$  must be carefully selected. On the one hand, the capacitance value should be small in order to allow the DC/DC stage to accurately control the DC link voltage to a six-pulse shape during 1/3 PWM operation (cf., Fig. 3(a.iii)). In particular, the resonant frequency of the  $L_{\rm b}$  $-C_{\rm DC}$  filter  $f_{\rm r,DC}$ , must be  $a_{\rm f} \sim 10$  times higher compared to the repetition frequency  $6f_{\rm m}$  of the six-pulse shaped DC link voltage, under 1/3 PWM operation

$$f_{\text{rDC}} \ge a_{\text{f}} \cdot 6f_{\text{m}}, \text{ where } f_{\text{rDC}} = \frac{1}{2\pi\sqrt{L_{\text{b}}C_{\text{DC}}}}.$$

(41)

Solving the inequality for  $C_{\rm DC}$  provides an upper bound for the DC link capacitance

$$C_{\rm DC} \leq \frac{1}{144\pi^2 L_{\rm b} a_{\rm f}^2 f_{\rm m}^2}.$$

(42)

On the other hand, the capacitance value should be large enough in order to limit the DC link voltage ripple amplitude  $\Delta U_{\rm DC}$  to a sufficiently low value. In particular, the capacitor  $C_{\rm DC}$  conducts the switched output current of the DC/DC stage as well as the switched input current of the DC/AC stage, both contributing to the DC link voltage ripple  $\Delta u_{\rm DC}(t)$ . Therefore, the DC link capacitance value must be

$$C_{\rm DC} \ge \frac{I_{\rm h,max}}{8f_{\rm sb}\Delta U_{\rm DC}} + \frac{\hat{I}_{\rm m,max}}{8f_{\rm sm}\Delta U_{\rm DC}}, \qquad (43)$$

independent of the modulation strategy, in order to ensure a DC link voltage ripple amplitude less or equal to  $\Delta U_{\rm DC}$ . The design constraints of (42) and (43) define a design space within which the capacitance  $C_{\rm DC}$  must be selected. The resulting DC link capacitance value is typically small since there is no need for energy storage in a three-phase system (in contrast to a single-phase system). An upper bound for the DC link capacitor RMS current stress is

$$I_{C_{\rm DC},\rm RMS,max} = \sqrt{\frac{I_{\rm b,max}^2}{4} + \frac{\hat{I}_{\rm m,max}^2}{4}}.$$

(44)

A detailed analysis of the DC link capacitor current stress can be found in [27]. In summary, the DC link capacitor must conduct a high-frequency switched current with high peak values, while a low capacitance value is typically required. For this reason, ceramic or film capacitors are suggested for the DC link implementation.

#### F. Motor Common-Mode Voltage

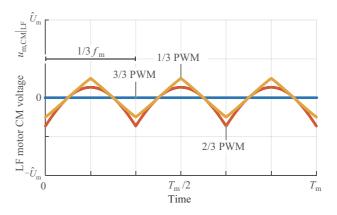

The motor CM voltage resulting from the different modulation

Fig. 9. Low-frequency component of the motor CM voltage  $u_{m,CM|LF}(t)$ , for the three examined modulation strategies cf., Fig. 2(a)–(c). Waveforms shown for maximum motor voltage, i.e., M = 2 for the case at hand.

strategies is now analysed. A motor CM voltage with high du/dt would results in parasitic CM currents which would partly flow through the motor bearings and could result in bearing damage [28]. For this reason, a DC link referenced output filter  $L_m-C_m$  is employed (cf., Fig. 1(a)) which protects the motor against CM (and differential-mode) voltages with high du/dt [29]–[33]. In particular, the DC link referenced output filter directly attenuates the switching frequency CM voltage generated by the DC/AC stage and hence only a small residual high-frequency (HF) motor CM voltage with an amplitude

$$\hat{U}_{\rm m,CM}|_{\rm HF} = \frac{1}{64} \frac{U_{\rm DC,max}}{L_{\rm m} C_{\rm m} f_{\rm s,m}^2}$$

(45)

remains at the motor terminals, where  $U_{\text{DC,max}}$  is given by (10). When a DC link referenced output filter is employed,  $\hat{U}_{\text{m,CM}}|_{\text{HF}}$  is noncritical concerning bearing currents and is marginally higher for 3/3 PWM as opposed to 2/3 PWM and 1/3 PWM because of the marginally higher DC link voltage  $U_{\text{DC,max}}$  of the former.

Furthermore, the motor CM voltage can feature a lowfrequency (LF) component

$$u_{m,CM}|_{LF}(t) = u_{DC}(t) \cdot \left(\frac{d_{a} + d_{b} + d_{c}}{3} - \frac{1}{2}\right),$$

(46)

depending on the employed modulation scheme, as depicted in Fig. 9. In particular, 3/3 PWM features zero LF motor CM voltage  $u_{m,CM}|_{LF}(t) = 0$ , because the sum of the three-phase DC/ AC stage duty cycles is constant over time (cf., Fig. 2(a.ii)). In contrast, 2/3 PWM and 1/3 PWM feature a time varying LF motor CM voltage [9] with a repetition frequency equal to  $3f_m$ , since the sum of the three-phase DC/AC stage duty cycles is different from 0 (cf., Fig. 2(b.ii) and (c.ii), respectively). The LF motor CM voltage is also noncritical concerning motor bearing currents.

#### G. Design Guidelines

For designing the two-stage DC/AC converter shown in Fig.

TABLE II

DC/DC STAGE SEMICONDUCTOR DESIGN/STRESS SUMMARY FOR THE WORST CASE OPERATING CONDITIONS OF TABLE I. NUMERICAL VALUES ARE DERIVED FOR THE PARAMETERS OF TABLE VI

| DC/DC stage |                                                |                                           |                                                                  |                                                                       |

|-------------|------------------------------------------------|-------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------|

|             | $U_{\rm DC,max}$                               | $P_{\rm sw}^{-1}$                         | $I_{\rm Tb1,RMS}^{1}$                                            | I <sub>Tb2,RMS</sub> <sup>1</sup>                                     |

| 3/3 PWM     | $2\hat{U}_{\mathrm{m}} = 80 \mathrm{V}$        | $f_{s,b}(k_0 + k_1 I_b) = 10.1 \text{ W}$ | $I_{\rm b} \sqrt{\frac{1}{M}} = 8.8 \mathrm{A}$                  | $I_{\rm b} \sqrt{1 - \frac{1}{M}} = 8.8 \mathrm{A}$                   |

| 2/3 PWM     | $\sqrt{3}\hat{U}_{\mathrm{m}} = 69 \mathrm{V}$ | $f_{s,b}(k_0 + k_1 I_b) = 10.1 \text{ W}$ | $I_{\rm b} \sqrt{\frac{2}{\sqrt{3}M}} = 9.5 \mathrm{A}$          | $I_{\rm b} \sqrt{1 - \frac{2}{\sqrt{3}M}} = 8.1  {\rm A}$             |

| 1/3 PWM     | $\sqrt{3}\hat{U}_{\rm m}{=}69{\rm V}$          | $f_{s,b}(k_0 + k_1 I_b) = 10.1 \text{ W}$ | $I_{\rm b} \sqrt{\frac{6\ln{(3)}}{\sqrt{3}\pi M}} = 9.7 {\rm A}$ | $I_{\rm b} \sqrt{1 - \frac{6\ln(3)}{\sqrt{3}\pi M}} = 7.8 \mathrm{A}$ |

<sup>1</sup> DC/DC stage inductor  $L_{\rm b}$  current ripple is neglected for the calculations.

#### TABLE III

DC/AC STAGE SEMICONDUCTOR DESIGN/STRESS SUMMARY FOR THE WORST CASE OPERATING CONDITIONS OF TABLE I. NUMERICAL VALUES ARE DERIVED FOR THE PARAMETERS OF TABLE VI.

| DC/AC stage |                                                                                                           |                                                                            |                                                                               |  |

|-------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|

|             | $P_{sw}^{1}$                                                                                              | I <sub>Tm1,RMS</sub> <sup>1</sup>                                          | I <sub>Tm2,RMS</sub> <sup>1</sup>                                             |  |

| 3/3 PWM     | $3f_{\rm s,m} (k_0 + k_1 \frac{2}{\pi} \hat{I}_{\rm m}) = 13.9  {\rm W}$                                  | $\frac{\hat{I}_{\rm m}}{\sqrt{2}} \frac{1}{\sqrt{2}} = 4.2  {\rm A}$       | $\frac{\hat{I}_{\rm m}}{\sqrt{2}} \frac{1}{\sqrt{2}} = 4.2 \mathrm{A}$        |  |

| 2/3 PWM     | $3f_{s,m}\left[\frac{2}{3}k_0 + (1 - \frac{\sqrt{3}}{4})k_1\frac{2}{\pi}\hat{I}_m\right] = 8.6 \text{ W}$ | $\frac{\hat{I}_{\rm m}}{\sqrt{2}} \sqrt{\frac{3}{2\pi}} = 4.1  \mathrm{A}$ | $\frac{\hat{I}_{\rm m}}{\sqrt{2}} \sqrt{1 - \frac{3}{2\pi}} = 4.3 \mathrm{A}$ |  |

| 1/3 PWM     | $3f_{s,m}\left[\frac{1}{3}k_0 + (1 - \frac{\sqrt{3}}{2})k_1\frac{2}{\pi}\hat{I}_m\right] = 3.3 \text{ W}$ | $\frac{\hat{I}_{\rm m}}{\sqrt{2}}\frac{1}{\sqrt{2}}=4.2{\rm A}$            | $\frac{\hat{I}_{\rm m}}{\sqrt{2}} \frac{1}{\sqrt{2}} = 4.2 \mathrm{A}$        |  |

<sup>1</sup> DC/AC stage filter inductor  $L_{\rm m}$  current ripple is neglected for the calculations.

TABLE IV INDUCTOR DESIGN SUMMARY FOR A PRE-EXISTING DRIVE SYSTEM DESIGNED FOR 3/3 PWM. NUMERIC RESULTS DERIVED FOR THE WORST CASE OPERATING CONDITIONS OF TABLE I AND THE PARAMETERS OF TABLE VI.

|         | DC/DC stage                                                                  |                         | DC/AC stage                                                                        |                         |

|---------|------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------|-------------------------|

|         | Lb                                                                           | $\Delta I_{Lb,RMS}^{1}$ | $L_{\rm m}$                                                                        | $\Delta I_{Lm,RMS}^{1}$ |

| 3/3 PWM | $\frac{\hat{U}_{\rm m}}{4\Delta I_{Lb,\rm PK}f_{\rm s,b}} = 1.5 \ \mu \rm H$ | 12.8 A                  | $\frac{\hat{U}_{\rm m}}{4\Delta I_{L{\rm m},{\rm PK}}f_{\rm s,m}} = 4.7\mu{\rm H}$ | 2.5 A                   |

| 2/3 PWM | 1.5 μH                                                                       | 10.8 A                  | $4.7 \mu\mathrm{H}$                                                                | 1.6 A                   |

| 1/3 PWM | 1.5 μH                                                                       | 10.1 A                  | $4.7 \mu\mathrm{H}$                                                                | 1.5 A                   |

<sup>1</sup>The values are based on numerical solver.

1(a), the worst case stresses on the DC/DC stage and the DC/ AC stage must be identified. The worst case component stress appears for maximum motor voltage and/or transferred power as shown in Table I. In Table II the analytic expressions for the semiconductor voltage/current stresses and the switching losses are summarized for the DC/DC stage. Accordingly, in Table III the analytic expressions are provided for the DC/ AC stage. Numerical values are given for the application at hand with the parameters of Table VI. Note that the analytic expressions are general and thus can be easily used for the selection of semiconductor devices of a system with different specifications.

If a drive system designed for conventional 3/3 PWM preexists, then 1/3 PWM can be retrofitted to the system by means of a firmware update. In this case, the drive system features a cooling system that can withstand the high DC/ AC stage switching losses of the 3/3 PWM and there is no possibility to change the DC/DC stage inductor  $L_{\rm b}$  and the DC/AC stage filter inductors  $L_{\rm m}$ . The use of the 1/3 PWM scheme leads to a significant switching losses reduction and thus a substantial overall efficiency  $\eta$  improvement. The inductor losses also decrease, since 1/3 PWM results in an RMS current ripple reduction of the DC/DC stage inductor  $L_{\rm b}$ and DC/AC stage inductor  $L_{\rm m}$ . The inductor performance is summarized in Table IV.

In a more general case, where there is not a pre-existing drive system designed for 3/3 PWM, different inductance values can be selected for the different modulation strategies. Besides a smaller semiconductor heatsink volume of the DC/ AC stage, thanks to the low switching losses, the 1/3 PWM allows for smaller inductance values. The inductor values and the resulting inductor RMS current ripple are summarized in

| TABL | ΕV |

|------|----|

|------|----|

INDUCTOR DESIGN SUMMARY FOR A SYSTEM WHICH IS PURPOSELY DESIGNED FOR THE EMPLOYED MODULATION. NUMERIC RESULTS DERIVED FOR THE WORST CASE OPERATING CONDITIONS OF TABLE I AND THE PARAMETERS OF TABLE VI.

|         | DC/DC stage                                                                                        |                         | DC/AC stage                                                                            |                         |

|---------|----------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------|-------------------------|

|         | $L_{\mathfrak{b}}$                                                                                 | $\Delta I_{Lb,RMS}^{1}$ | $L_{\rm m}$                                                                            | $\Delta I_{Lm,RMS}^{1}$ |

| 3/3 PWM | $\frac{\hat{U}_{\rm m}}{4\Delta I_{Lb,{\rm PK}}f_{\rm s,b}} = 1.5\ \mu{\rm H}$                     | 12.8 A                  | $\frac{\hat{U}_{\rm m}}{4\Delta I_{\rm Lm, PK}f_{\rm s,m}} = 4.7 \ \mu {\rm H}$        | 2.5 A                   |

| 2/3 PWM | $\frac{(1-\frac{1}{\sqrt{3}})\hat{U}_{\rm m}}{2\Delta I_{\rm Lb,PK}f_{\rm s,b}} = 1.27\ \mu\rm{H}$ | 12.8 A                  | $\frac{\sqrt{3}\hat{U}_{\rm m}}{8\Delta I_{\rm Lm,PK}f_{\rm s,m}} = 4.1 \ \mu {\rm H}$ | 1.8 A                   |

| 1/3 PWM | $\frac{(1-\frac{1}{\sqrt{3}})\hat{U}_{m}}{2\Delta I_{Lb,PK}f_{s,b}} = 1.27 \ \mu H$                | 11.9 A                  | $\frac{\sqrt{3}\hat{U}_{\rm m}}{8\Delta I_{\rm Lm,PK}f_{\rm s,m}} = 4.1 \ \mu {\rm H}$ | 1.7 A                   |

<sup>1</sup> The values are based on numerical solver.

TABLE VI Parameter Values of the Hardware Prototype Shown in Fig. 10 Corresponding to the Schematic Diagram Notation of Fig. 1(a).

| Parameter                       | Value                                                         |

|---------------------------------|---------------------------------------------------------------|

| DC/DCstage                      |                                                               |

| Switching frequency $(f_{s,b})$ | 300 kHz                                                       |

| Switches (2 in parallel)        | 200 V EPC 2034                                                |

| Switching parameters [23]       | $k_0 = 15 .4 \mu\text{J},  k_1 = 1 .5 \mu\text{J} / \text{A}$ |

| Inductance $(L_b)$              | 1.5 µH                                                        |

| Capacitance ( $C_b$ )           | 10 µF                                                         |

| Capacitance ( $C_{DC}$ )        | 25 $\mu$ F, ( $\Delta U_{\rm DC} = 0.8$ V, $a_{\rm f} = 10$ ) |

| DC/ACstage                      |                                                               |

| Switching frequency $(f_{s,m})$ | 300 kHz                                                       |

| Switches                        | 200 V EPC 2034                                                |

| Switching parameters [23]       | $k_0 = 7.7 \mu \text{J},  k_1 = 1.5 \mu \text{J} / \text{A}$  |

| Inductance $(L_m)$              | 4.7 μH                                                        |

| Capacitance $(C_m)$             | $2 \mu F$                                                     |

Table V. There, the 1/3 PWM not only employs a smaller DC/DC stage inductance  $L_{\rm b}$  and DC/AC inductance  $L_{\rm m}$ , but also features lower RMS current ripples. Therefore, the inductors  $L_{\rm b}$  and  $L_{\rm m}$  can be realised in a more compact way, which translates into a lower overall volume for 1/3 PWM compared to 3/3 PWM.

Finally, the DC link capacitor value must be selected considering a maximum allowed DC link voltage ripple amplitude of  $\Delta U_{\rm DC} = 0.8$  V (~ 1% of the DC link voltage) and the operating parameters of Tables I and VI. Based on (42) and (43) this results in 11  $\mu$ F  $\leq C_{\rm DC} \leq 29 \mu$ F and/or finally selected value of  $C_{\rm DC} = 25 \mu$ F.

# **IV. HARDWARE VERIFICATION**

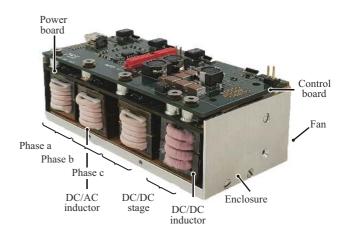

In order to verify the performance potential of 1/3 PWM modulation, a hardware demonstrator has been built according to the specifications of Table I. The demonstrator system is shown in Fig. 10, while the selected parameter values are summarized in Table VI. The hardware prototype comprises a power and a control board. The power board includes the DC/AC stage and the DC/DC stage half-bridges and the respective gate drivers. Each half-bridge of the DC/AC stage features two 200 V rated EPC 2034 semiconductor devices (i.e., single device per switch) while the DC/DC stage half-bridge employs four EPC 2034 semiconductor devices (i.e., two devices in parallel per switch). The four inductors as well as a custom aluminium heatsink which is optimally designed for the given

Fig. 10. Three-phase converter hardware prototype employed for experimentally verifying the main characteristics of 3/3, 2/3 and 1/3 PWM. The system comprises a boost-type DC/DC stage and a buck-type DC/AC stage (cf., Fig. 1(a)) and is thus suitable for drive applications with a wide input-output voltage variation. Furthermore, modulation can be easily switched between the different modulation strategies. Dimensions  $35 \times 50 \times 106$  mm<sup>3</sup> (11.32 in<sup>3</sup>).

application, are placed below the power board. Four 25 mm fans are used for forced air cooling. A custom control board which is used for the generation of the appropriate gating signals and the current/voltage measurements is placed on top of the power board.

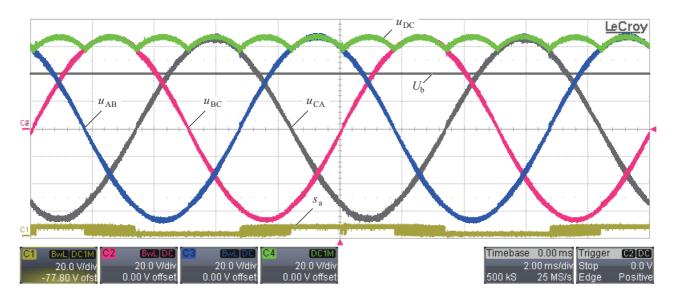

The 1/3 PWM modulation strategy is implemented in software and tested according to the control diagram of Fig. 4. The experimentally measured waveforms are shown in Fig. 11 for maximum transferred power P = 500 W and maximum motor phase voltage amplitude  $\hat{U}_m = 40$  V, i.e., modulation index M = 2. There, the six-pulse shape of the DC link voltage  $u_{\rm DC}$  is clearly visible. Furthermore, the three motor line-toline voltages are depicted. The DC link voltage is equal to the highest instantaneous motor line-to-line voltage. In addition, the gate signal of phase a of the DC/AC stage is shown, which reveals that the corresponding half-bridge is switched only for 1/3 of the fundamental period  $T_m$ .

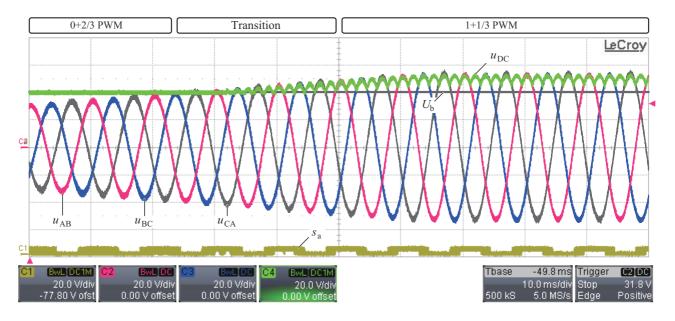

Subsequently, a transition from 2/3 PWM to 1/3 PWM is shown in Fig. 12. There, the output motor line-to-line voltages are gradually increased and a seamless transition (without unwanted transients) from 2/3 PWM to 1/3 PWM is achieved.

The experimental measurements are verifying the theoretical

Fig. 11. Experimentally measured waveforms of 1/3 PWM for maximum power P = 500 W, maximum motor voltage  $\hat{U}_m = 40$  V, modulation index M = 2 and a fundamental frequency of  $f_m = 100$  Hz. The motor line-to-line voltages  $u_{AB}$ ,  $u_{BC}$  and  $u_{CA}$ , the DC link voltage  $u_{DC}$  and the gating signal of phase a  $(s_a)$  are also depicted. The line-to-line voltage  $u_{CA}$  is not directly measured, but instead is reconstructed based on the two other measured line-to-line voltages  $u_{AB}$  and  $u_{BC}$ .

Fig. 12. Experimentally measured transition from 2/3 PWM to 1/3 PWM, where the modulation index (and hence the output AC voltage) is gradually increased:  $M = 0.5 \rightarrow 1.5$ . The motor line-to-line voltages  $u_{AB}$ ,  $u_{BC}$  and  $u_{CA}$ , the DC link voltage  $u_{DC}$  and the gating signal of phase a ( $s_a$ ) are also depicted. The line-to-line voltage  $u_{CA}$  is not directly measured, but instead is reconstructed based on the two other measured line-to-line voltages  $u_{AB}$  and  $u_{BC}$ .

consideration of Section II. It should be pointed out that 1/3 PWM can be applied on existing converter systems as a firmware update. That is, no hardware modifications are needed in order to accommodate the 1/3 PWM scheme.

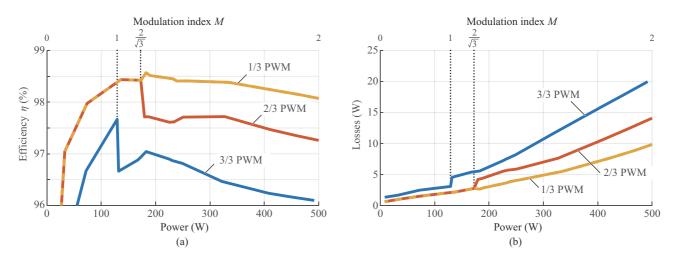

The converter efficiency characteristic is now measured over the whole output power range, P = 0...500 W, in order compare 1/3 PWM against the conventional modulation strategies 2/3 PWM and 3/3 PWM. The results are illustrated in Fig. 13(a). The 3/3 PWM exhibits the worst performance of  $\eta \le 96\%$ nominal efficiency due to the continuous switching of all three DC/AC stage half-bridges. Furthermore, when the modulation index exceeds M > 1, the DC/DC stage is activated, resulting in additional losses due to the DC/DC stage semiconductor devices and inductor. Therefore, a sharp decrease in efficiency appears for M > 1. The 2/3 PWM out-performs 3/3 PWM with a nominal efficiency of  $\eta \simeq 97.2\%$ . When the modulation index exceeds  $M > 2/\sqrt{3}$ , the DC/DC stage is activated causing a steep drop in efficiency. The 1/3 PWM features the highest nominal efficiency,  $\eta \simeq 98\%$ , thanks to the drastic reduction of the DC/AC stage switching losses. Note that 1/3 PWM does not suffer from an efficiency reduction for  $M > 2/\sqrt{3}$  when the DC/DC stage is activated. This is attributed to the continuous transition between the 0+2/3 and the 1+1/3 modulation regimes of Fig. 5. Namely, for 0+2/3 modulation

Fig. 13. (a) Efficiency of the hardware prototype employing the 1/3 PWM modulation strategy in the whole operating power range P = 0...500 W. The efficiency measurement is also performed for the conventional 2/3 PWM and 3/3 PWM, and a clear comparative advantage in favour of the 1/3 PWM is deduced. (b) Corresponding losses of the hardware prototype for the different modulation strategies. The converter operating parameters are given in Table VI.

regime the DC/DC stage is not operated, while two phases of the DC/AC stage are switching. For 1+1/3 modulation regime the DC/DC stage half-bridge is switching, while only one phase of the DC/AC stage is operated. Therefore, in any case in total two half-bridges (including the DC/DC and DC/AC stage) are switching, resulting in a smooth efficiency curve. In Fig. 13(b), the losses associated with each modulation strategy are plotted.

There, a 10 W (50%) reduction of the overall converter losses is experimentally achieved with 1/3 PWM compared to 3/3 PWM. It can be assumed that this 10 W losses reduction originates mainly from the DC/AC stage switching losses reduction under 1/3 PWM, while the rest of the loss contributions either remain the same (e.g., DC/DC stage semiconductor switching/conduction losses and DC/AC stage semiconductor conduction losses), or slightly decrease (e.g., DC/DC stage and DC/AC stage inductor losses), compared to 3/3 PWM. Therefore, the experimentally measured 10 W reduction of the DC/AC stage switching looses with 1/3 PWM, matches well with the respective theoretically calculated value of 10.7 W from Fig. 6.

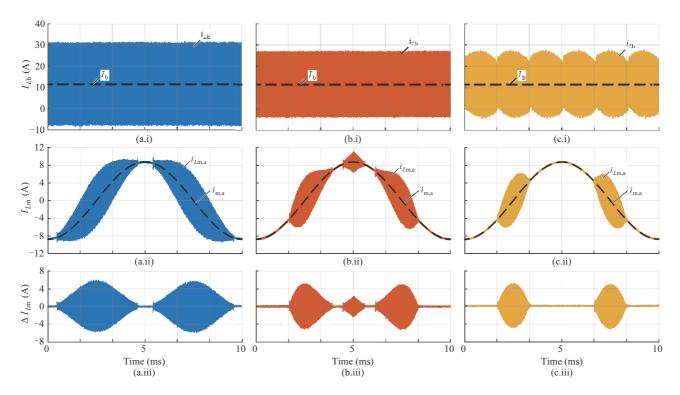

Experimentally measured waveforms of the DC/DC stage inductor ( $L_b$ ) current are shown in Fig. 14(i), while the DC/ AC stage inductor ( $L_m$ ) current and the inductor current ripple component are depicted in Fig. 14(ii) and (iii), respectively. The results are plotted for the three considered modulation strategies and for a modulation index of M = 1.75. It should be noted that the DC/AC stage inductor current ripple shape is unique to the DC link referenced filter of Fig. 1(a), i.e., for filter capacitors  $C_m$  connected to the negative DC link rail [19]. The 3/3 PWM induces the highest current ripple for both the DC/ DC stage inductor  $L_b$  and for the DC/AC stage inductors  $L_m$ . On the contrary, 1/3 PWM generates the lowest overall current ripple and hence the lowest inductor losses. The 2/3 PWM current ripple performance lies in between the values achieved for 1/3 PWM and 3/3 PWM.

Finally, the experimentally measured RMS inductor current

ripple is compared against the theoretically calculated values of Fig. 8. The results are shown in Fig. 15(a) and (b) for the DC/DC and DC/AC stage, respectively. An excellent matching between the theoretical analysis and the experimental measurements is verified.

# V. CONCLUSIONS

As shown in this paper, 1/3 PWM can be applied to threephase DC/AC converter systems which feature a separate DC/ DC and DC/AC stage and are designed to cope with a wide input-output voltage variation. 1/3 PWM utilizes a variable DC link voltage instead of a constant DC link voltage used in conventional PWM modulation schemes. Thereby, it is possible to generate three-phase sinusoidal line-to-line output voltages by switching always only one out of the three DC/AC stage half-bridges. A main advantage of the 1/3 PWM modulation is that it can be easily retrofitted to existing three-phase converter systems by means of a firmware update. In order to quantify the performance advantage of 1/3 PWM, the semiconductor switching losses are analytically calculated and the remaining converter component stresses are comprehensively analysed. It is deduced that 1/3 PWM reduces the switching losses of the DC/AC stage by more than 66% compared to the conventional 3/3 PWM modulation strategy. The 1/3 PWM also outperforms the more advanced 2/3 PWM by reducing the switching losses of the latter by at least a factor of two. Besides the lower switching losses, 1/3 PWM exhibits similar if not slightly lower current and/or voltage stresses on the remaining converter components compared to the 2/3 PWM modulation strategy. Therefore, 1/3 PWM is a promising modulation technique with substantial advantages over state-of-the-art approaches. Finally, a hardware demonstrator is assembled and tested. There, the uncomplicated operation of 1/3 PWM is experimentally validated. Furthermore, 3/3 PWM, 2/3 PWM and 1/3 PWM are applied to the same hardware demonstrator and the corresponding losses are measured over a wide power

Fig. 14. Inductor currents for different modulation strategies measured using the hardware demonstrator of Fig. 10 for a modulation index of M = 1.75 (P = 460 W) and a fundamental frequency of  $f_m = 100$  Hz. (i) The DC/DC stage inductor  $L_b$  current is shown. (ii) The current in an output filter inductor of the DC/AC stage  $L_m$  is plotted. (iii) The respective DC/AC stage inductor current ripple is illustrated. (a), (b) and (c) refer to the 3/3 PWM, 2/3 PWM and 1/3 PWM, respectively.

Fig. 15. Theoretically calculated inductor RMS current ripple (continuous lines) compared against experimental measurements (x marks). (a) Corresponds to the DC/DC stage while (b) refers to the DC/AC stage.

range. A 2% increase of efficiency, i.e., a loss reduction of 50% is measured for the 1/3 PWM compared to 3/3 PWM for the considered application.

# APPENDIX A: COMPONENT STRESSES FOR $\cos(\varphi) < 1$

The impact of a low load PF on the overall design of the two-stage converter system is discussed. A converter system that can operate under any load voltage-current phase shift  $\varphi$  is desirable in this case study. Therefore, the stresses on the different system components are now analysed for a PF cos  $(\varphi) < 1$ . In particular, the load current is assumed to either lead

or lag the load voltage by a phase shift angle  $\varphi = -90^{\circ}...90^{\circ}$ (i.e., capacitive or inductive load behaviour). Accordingly, the transferred apparent power S = 0...500 W, active power P, battery current  $I_{\rm b}$  and load fundamental phase current amplitude  $\hat{I}_{\rm m}$  can be derived as a function of the modulation index M and PF cos ( $\varphi$ ) as

$$S = M^{2} \frac{3U_{\rm b}^{2}}{8R}, \quad P = M^{2} \frac{3U_{\rm b}^{2}}{8R} \cos{(\varphi)},$$

$$I_{\rm b} = M^{2} \frac{3U_{\rm b}}{8R} \cos{(\varphi)}, \quad \hat{I}_{\rm m} = M \frac{U_{\rm b}}{2R},$$

(47)

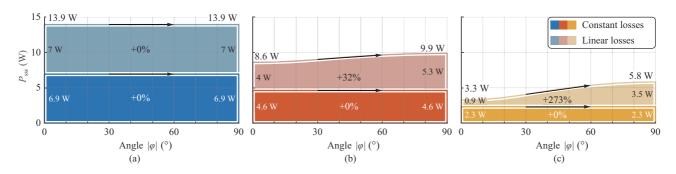

Fig. 16. Switching losses of the DC/AC stage as a function of the voltage-current phase shift  $\varphi$  of the load and the modulation scheme. (a) 3/3 PWM. (b) 2/3 PWM. (c) 1/3 PWM. There, the worst case operating point with the maximum motor voltage (M = 2 for the case at hand) is considered, while numerical values are derived for the worst case operating conditions of Table I and the parameters of Table VI.

where  $R = 3\hat{U}_{\text{m,max}}/2S_{\text{max}} = 4.8 \Omega$ .

The switching losses of the DC/DC stage can directly be derived by substituting  $I_b$  from (47) in (15). Since the battery current  $I_b$  decreases as the PF reduces, the DC/DC stage switching losses also decrease. The switching losses of the DC/AC stage for 3/3 PWM are independent from the PF and are therefore given by using (16). On the other hand, the switching losses of the DC/AC stage for 2/3 PWM and 1/3 PWM depend on the PF and hence the phase shift  $\varphi$  has to be considered in the derivation of the local switching losses (12) of the DC/AC stage as

$$p_{\rm sw}(\theta) = f_{\rm sm} \left[ k_0 + k_1 \hat{I}_{\rm m} \left| \cos \left( \theta - \varphi \right) \right| \right]. \tag{48}$$

By averaging  $p_{sw}(\theta)$  over a  $2\pi$  wide fundamental period the global average switching losses can be derived. For 2/3 PWM, the switching losses are calculated as

$$P_{\rm sw}|_{2/3 \rm PWM} = \frac{3}{2\pi} \left[ \int_{0}^{\frac{2\pi}{3}} p_{\rm sw}(\theta) d\theta + \int_{\frac{4\pi}{3}}^{2\pi} p_{\rm sw}(\theta) d\theta \right], (49)$$

for a voltage-current phase shift of  $|\varphi| \leq 30^\circ$  results in

$$P_{\rm sw} \Big|_{23 \,\rm PWM} = 3f_{\rm s,m} \Big[ \frac{2}{3} k_0 + \Big( 1 - \frac{\sqrt{3} \cos |\varphi|}{4} \Big) k_1 \frac{2}{\pi} \hat{I}_{\rm m} \Big],$$

(50)

and for  $|\varphi| > 30^\circ$  gives

$$P_{\rm sw}|_{2/3 \rm PWM} = 3f_{\rm sm} \left[ \frac{2}{3} k_0 + \left( \frac{1}{2} + \frac{\sin|\varphi|}{4} \right) k_1 \frac{2}{\pi} \hat{I}_{\rm m} \right]. (51)$$

The same procedure can be applied to calculate the DC/AC stage switching losses for 1/3 PWM where

$$P_{\rm sw} \Big|_{1/3 \text{ PWM}} = \frac{3}{2\pi} \left[ \int_{\frac{\pi}{3}}^{\frac{2\pi}{3}} p_{\rm sw}(\theta) d\theta + \int_{\frac{4\pi}{3}}^{\frac{5\pi}{3}} p_{\rm sw}(\theta) d\theta \right], (52)$$

for a voltage-current phase shift of  $|\varphi| \leq 30^{\circ}$  results in

$$P_{\rm sw} \Big|_{1/3 \text{ PWM}} = 3f_{\rm s,m} \Big[ \frac{1}{3} k_0 + \Big( 1 - \frac{\sqrt{3} \cos |\varphi|}{2} \Big) k_1 \frac{2}{\pi} \hat{I}_{\rm m} \Big],$$

(53)

while for  $|\varphi| > 30^\circ$  gives

$$P_{\rm sw} \big|_{1/3 \text{ PWM}} = 3f_{\rm sm} \left( \frac{1}{3} k_0 + \frac{\sin|\varphi|}{2} k_1 \frac{2}{\pi} \hat{I}_{\rm m} \right).$$

(54)

In Fig. 16, the switching losses for all modulation schemes depending on the phase shift  $\varphi$  of the load are plotted. Compared to the load independent losses obtained with 3/3 PWM, the losses for 2/3 PWM and 1/3 PWM slightly increase with increasing phase shift, since in the middle phase a higher current has to be switched than with  $\cos(\varphi) = 1$ . It is noted, that the switching losses are symmetric with respect to  $\varphi$ , i.e., the losses for a voltage-current phase shift +  $\varphi$  are equal to the respective losses for  $-\varphi$ . It can be deduced from Fig. 16, that although the switching losses for 2/3 PWM and 1/3 PWM increase as the PF reduces, both still generate by far lower overall switching losses compared to 3/3 PWM.