© 2017 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Digital Object Identifier (DOI): <u>10.1109/TPEL.2017.2704293</u>

IEEE Transaction on Power Electronics (Volume: 33, Issue: 4, April 2018) Analysis of DC-Link Current Influence on Temperature Variation of Capacitor in a Wind Turbine Application

Youngjong Ko Holger Jedtberg Giampaolo Buticchi Marco Liserre

# Suggested Citation

Y. Ko, H. Jedtberg, G. Buticchi and M. Liserre, "Analysis of DC-Link Current Influence on Temperature Variation of Capacitor in a Wind Turbine Application," in *IEEE Transactions on Power Electronics*, vol. 33, no. 4, pp. 3441-3451, April 2018.

# Analysis of DC-Link Current Influence on Temperature Variation of Capacitor in a Wind Turbine Application

Young jong Ko<sup>®</sup>, *Student Member, IEEE*, Holger Jedtberg<sup>®</sup>, *Student Member, IEEE*, Giampaolo Buticchi<sup>®</sup>, *Senior Member, IEEE*, and Marco Liserre, *Fellow, IEEE*

Abstract-Back-to-back converters for wind turbine systems feature capacitors in the dc-link to maintain a stable voltage and to decouple a generator from the electric grid. The electrolytic capacitors are typically chosen for their advantages; a higher energy density and a higher capacitance at lower costs. Long-term field experiences and recorded failure data revealed that the capacitors are one of the most frequent failure reasons for the wind turbine system. The current profile of the capacitors is highly responsible for this degradation, since it determines the dissipated power of the capacitor. This paper analyzes the actual current profile in the dc-link capacitor of a back-to-back converter for wind turbine application. A power converter is also designed to generate sinusoidal current at arbitrary frequency and arbitrary dc bias voltage for testing purposes. The experimental results confirm that the proposed power converter enables us to derive the correlation between the current frequency and the temperature variation of capacitor.

*Index Terms*—Back-to-back converter, electrolytic capacitor, reliability, wind turbine, ripple current stress.

#### I. INTRODUCTION

**H** IGH reliability has become the most important requirement for wind turbine installation, in order to reduce maintenance costs and ensure a high system availability. The failures are mostly located in the power converter part and the capacitors are responsible for 60% of the failures [1]–[3]. Therefore, condition monitoring methods have been proposed to evaluate the capacitor health status by estimating the internal parameters [4]–[7]. Furthermore, the useful lifetime estimation methods have been proposed in [8]–[11] for a scheduled maintenance, which are based on the lifetime model derived by the Physics of Failure approach [12], [13].

On the other hand, core temperature is the most influencing factor for the capacitors lifetime [14]–[17], and it depends

The authors are with the Chair of Power Electronics, Christian-Albrechts Universität zu Kiel, Kiel 24143, Germany (e-mail: yoko@tf.uni-kiel.de; hje@tf. uni-kiel.de; gibu@tf.uni-kiel.de; ml@tf.uni-kiel.de).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2017.2704293

on the ambient as well as the power losses inside the capacitor, which are depending mainly on the current profile. Therefore, many research works investigated the current spectrum [18]–[21] and the current reduction by synchronization of carrier signals in a back-to-back converter [22], [23]. However, a clear correlation between the current harmonics and the lifetime (or core temperature variation) in such research works is still missing.

After analyzing the capacitor current spectra under different operating conditions, this paper proposes a power converter to perform capacitor testing. The idea is to individuate via simulations the capacitor current spectrum and to reproduce them with the realized test setup. To define the frequency range, the dclink capacitor current in the two-level back-to-back converter is identified, with consideration of different power and power factors in Section II. Then, in Section III, the impact on the lifetime is discussed taking the typical model of electrolytic capacitor to highlight the motivation. Before demonstrating the temperature variation in Section V, the power converter is proposed to inject sinusoidal current at various frequencies, which are obtained based on a real operation, to the capacitor under test (CUT) in Section IV. The challenge in its design is to achieve a low total harmonic distortion (THD) to derive further clear correlation. Moreover, it is as well required to control the bias voltage on the CUT; the parallel control strategy is proposed and verified by the experimental results. Finally, this paper is concluded in Section VI.

## II. ANALYSIS OF DC-LINK CAPACITOR CURRENT IN BACK-TO-BACK CONVERTER

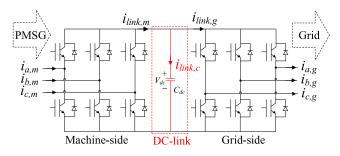

In this section, the dc-link capacitor current is identified in accordance with operating points to provide the information of the current spectrum. The capacitor current  $(i_{\text{link},c})$  can be calculated by the subtraction between the machine-side current  $(i_{\text{link},m})$  and the grid-side current  $(i_{\text{link},g})$  as (1), considering the two-level back-to-back converter shown in Fig. 1

$$f_{\text{link},c}(t) = i_{\text{link},m}(t) - i_{\text{link},g}(t)$$

(1)

where the subscript c denotes the capacitor-side, the subscript m is the machine-side, and the subscript g is the grid-side. Then, referring [18], the capacitor current can be mathematically expressed as (2), shown at the bottom of the next page. The

i

0885-8993 © 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received October 17, 2016; revised March 30, 2017; accepted May 6, 2017. Date of publication May 15, 2017; date of current version January 3, 2018. This work was supported in part by the European Union/Interreg V-A—Germany-Denmark under PE:Region Project and in part by the Gesellschaft für Klimaschutz Schleswig-Holstein GmbH within the framework of the "LIFE-WIND" project. This paper was presented in part at the *IEEE Applied Power Electronics Conference and Exposition*, Long Beach, CA, USA, March 20–24, 2016. Recommended for publication by Associate Editor P. Bauer. (*Corresponding author: Youngjong Ko.*)

Fig. 1. Two-level back-to-back converter used as a case study.

derivation of machine- and grid-side equations is also presented in Appendix B.

In the following analysis, the three currents  $(i_{\text{link},m}, i_{\text{link},g}, i_{\text{link},c})$  of 2 MW wind turbine, whose specification is shown in Table A-1 (see Appendix A), is simulated under four operating points in Table II (see Appendix A). It is assumed that the carriers of machine- and grid-side are synchronized to cancel the first harmonics of switching frequency as well as the power factor of the machine-side is set to 0.98 since no magnetizing current needs to be provided to permanent magnet synchronous generator (PMSG) [24], [25].

On the other hand, the power factor of the grid-side could be controlled within a defined boundary by the German grid code [26], [27]. Following the definition of variant 1, the boundary of the power factor angle in the grid-side, which is presented in (3), is considered

$$-48.99^{\circ} \le \varphi_{0,q} \le 67.38^{\circ}. \tag{3}$$

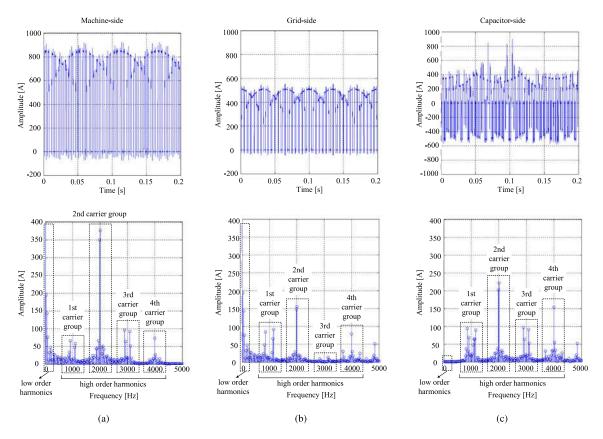

The current waveforms of the machine-, grid-, and capacitorside under the operating point 2 (see Table A-2 in Appendix A) are simulated in Fig. 2, along with their harmonic spectrum. Focusing on the harmonic spectrum, while the machineand grid-side current contain both low-order harmonics and high-order harmonics as shown in Fig. 2(a) and (b), it can be observed that the harmonics of the capacitor-side current are dominantly distributed at high-order harmonics, as shown in Fig. 2(c).

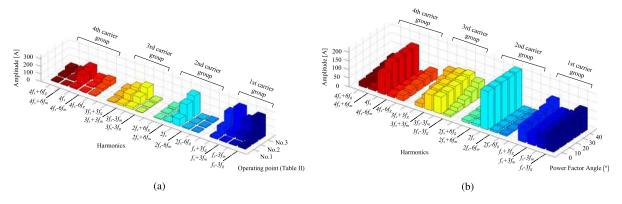

In Fig. 3, the harmonics variation of the capacitor current is shown in accordance with the operating point (generated power) and the power factor of the grid-side. The harmonics amplitude accordingly increases by the increased power as shown in Fig. 3(a). Fig. 3(b) shows the influence of the power factor on the capacitor-side current spectrum, and the side-band harmonics are increased with the lower power factor.

As a conclusion, the high-order harmonics of around  $a \cdot f_s$  mainly affects the lifetime of dc-link capacitors, where the  $f_s$  is the switching frequency and the a is the integer.

## III. LIFETIME CONSIDERATIONS FOR ELECTROLYTIC CAPACITORS

## A. Electrolytic Capacitor Model

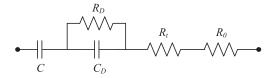

A simplified model of an electrolytic capacitor is depicted in Fig. 4, where C is the terminal capacitance,  $C_D$  and  $R_D$  account for the losses caused by the dielectric,  $R_0$  is the combined constant resistance of terminals, tabs, and foils, respectively, and  $R_t$  is the resistance of the electrolyte [28]. It should be

$$\begin{split} i_{\mathrm{link},c}(t) &= \sum_{\eta=1}^{3} I_m \cdot \cos\left(\omega_m t + \varphi_{\eta,m} - \varphi_{0,m}\right) \\ &\left[ \frac{1}{2} + \frac{2}{\pi} \cdot \sum_{n=1}^{\infty} \frac{1}{n \left(\frac{\omega_m}{\omega_{sw}}\right)} \cdot J_n \left( n \left(\frac{\omega_m}{\omega_{sw}}\right) \frac{\pi}{2} m_{a,m} \right) \cdot \sin\left(n\frac{\pi}{2}\right) \cdot \cos\left(n \left(\omega_m t + \varphi_{\eta,m}\right)\right) \right) \\ &+ \frac{2}{\pi} \cdot \sum_{m=1}^{\infty} \frac{1}{m} \cdot J_0 \left(m\frac{\pi}{2} m_{a,m}\right) \cdot \sin\left(m\frac{\pi}{2}\right) \cdot \cos\left(m \left(\omega_{sw} t + \varphi_{\mathrm{pwm},m}\right)\right) \\ &+ \frac{2}{\pi} \cdot \sum_{m=1}^{\infty} \sum_{n=-\infty}^{\infty} \frac{1}{q} \cdot J_n \left(q\frac{\pi}{2} m_{a,m}\right) \cdot \sin\left((m+n)\frac{\pi}{2}\right) \cdot \cos\left(m \left(\omega_{sw} t + \varphi_{\mathrm{pwm},m}\right) + n \left(\omega_m t + \varphi_{\eta,m}\right)\right) \right] \\ &- \sum_{\eta=1}^{3} I_g \cdot \cos\left(\omega_g t + \varphi_{\eta,g} - \varphi_{0,g}\right) \\ &\left[ \frac{1}{2} + \frac{2}{\pi} \cdot \sum_{n=1}^{\infty} \frac{1}{n \left(\frac{\omega_g}{\omega_{sw}}\right)} \cdot J_n \left(n \left(\frac{\omega_g}{\omega_{sw}}\right) \frac{\pi}{2} m_{a,g}\right) \cdot \sin\left(n\frac{\pi}{2}\right) \cdot \cos\left(n \left(\omega_g t + \varphi_{\eta,g}\right)\right) \\ &+ \frac{2}{\pi} \cdot \sum_{m=1}^{\infty} \frac{1}{m} \cdot J_0 \left(m\frac{\pi}{2} m_{a,g}\right) \cdot \sin\left(m\frac{\pi}{2}\right) \cdot \cos\left(m \left(\omega_{sw} t + \varphi_{\mathrm{pwm},g}\right) + n \left(\omega_g t + \varphi_{\eta,g}\right)\right) \\ &+ \frac{2}{\pi} \cdot \sum_{m=1}^{\infty} \sum_{n=-\infty}^{\infty} \frac{1}{q} \cdot J_n \left(q\frac{\pi}{2} m_{a,g}\right) \cdot \sin\left((m+n)\frac{\pi}{2}\right) \cdot \cos\left(m \left(\omega_{sw} t + \varphi_{\mathrm{pwm},g}\right) + n \left(\omega_g t + \varphi_{\eta,g}\right)\right) \\ &\left(2\right) \end{aligned}$$

Fig. 2. Simulated current waveform and its harmonic spectrum in (a) machine-side, (b) grid-side, and (c) capacitor under operating point no. 2 of Table II in Appendix A.

Fig. 3. Harmonics distribution of dc-link capacitor current depending on (a) generated power and (b) power factor angle of grid-side.

noted that the capacitor model is also containing an inductive part in series. For the following analysis, this inductance will be neglected, following the assumption that the capacitor is operated well below its resonance frequency. The equivalent series resistance (ESR) represents the real part of the capacitor's impedance. Therefore, it can be expressed as

$$R_{\rm ESR} = R_0 + R_f + R_t \tag{4}$$

where  $R_f$  represents the frequency-dependent resistance of the dielectric layer, which is composed by  $C_D$  and  $R_D$ , and  $R_t$  is the temperature-dependent part due to the characteristics of the

employed electrolyte [17], [28]. Since with increasing temperature the viscosity of the electrolyte changes, its conductivity increases, which in turn leads to a reduction in ESR due to  $R_t$ . This effect can be modeled by applying (5), where  $R_{t,b}$  is  $R_t$ at base temperature  $T_b$ ,  $T_s$  is the hotspot temperature of the capacitor, and SF denotes a capacitor-dependent temperature sensitivity factor [28]

$$R_t = R_{t,b}(T_b) \cdot e^{\frac{T_b - T_s}{SF}}.$$

(5)

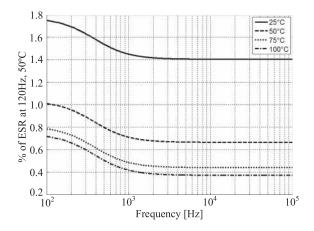

In Fig. 5, the ESR is plotted against frequency for different temperatures in accordance to [28]. As discussed before, it can

Fig. 4. Equivalent model of electrolytic capacitor.

Fig. 5. Variation of ESR with respect to ripple current frequency and temperature [28].

be seen that the ESR decreases as temperature increases. Moreover, it can be noted that increasing frequencies also lead to a decrease in ESR due to  $R_f$ .

#### B. Impact of Capacitor Current on Lifetime

As stated before, the capacitor's current modifies the capacitor's temperature, affecting the lifetime. The hotspot temperature of the capacitor can be estimated by applying (6), where  $T_a$  denotes the ambient temperature,  $\Delta T$  is the additional heating caused by the power dissipation  $P_d$ , and the thermal resistance from hotspot to ambient of the capacitor  $R_{\rm th}$

$$T_s = T_a + \Delta T = T_a + P_d \cdot R_{\text{th}}.$$

(6)

Since the ESR exhibits a frequency-dependent behavior, for the correct calculation of  $P_d$  the knowledge of the RMS capacitor current at the corresponding frequencies is needed [19], [22]. Therefore, the spectral analysis of the previous paragraph can be adopted for the calculation of the different harmonic components. By knowing the capacitor current harmonics,  $P_d$ can be calculated by

$$P_d = \sum_{i=1}^n I_{R,i}^2 \cdot R_{\text{ESR},i} \tag{7}$$

where  $I_{R,i}$  and  $R_{\text{ESR},i}$  denote the RMS ripple current and the ESR at frequency harmonic *i*, respectively, with i = 1, 2, ..., n

$$L = L_0 \cdot 2^{\frac{T_{\max} - T_a}{10K}} \cdot 2^{1 - \left(\frac{I_a}{I_0}\right)^2 \cdot \frac{\Delta T_0}{A}} \cdot \left(\frac{V_a}{V_0}\right)^{-m}.$$

(8)

The lifetime model of an electrolytic capacitor is shown in (8), where  $L_0$  denotes the lifetime at nominal values as given

in the manufacturer's datasheets,  $T_{max}$  is the maximum permissible temperature,  $I_a$  is the applied capacitor current,  $I_0$  is the rated capacitor current,  $\Delta T_0$  is the temperature increase when  $I_0$  is applied, A is the temperature coefficient,  $V_a$  is the applied voltage,  $V_0$  is the nominal voltage, and m accounts for the manufacturer-dependent voltage factor as discussed in [29]. The model consists of three parts, where each part is considered as one of the three major stressors. The impact of the ambient temperature follows the Arrhenius rule, which constitutes a doubling in lifetime for each 10 K temperature decrease. Moreover, the applied voltage is taken into account in this model, since an increasing voltage level causes degradation due to electrolyte evaporation effects, which in turn affects the lifetime of the capacitor. As mentioned above, the ripple current is influencing the capacitor's lifetime by acting on the temperature rise  $\Delta T$ , which is also taken into account in (8). The factor A accounts for the higher impact of  $\Delta T$  on the lifetime, since it is evaluated experimentally by some manufacturers that the lifetime is bisected by an increase of, e.g., 7-10 K in  $\Delta T$  [12].

Degradation of the capacitor is not included in (8). Since the heat rise due to the capacitor current causes electrolyte evaporation, it leads to the degradation of the capacitor's parameters, being the ESR and the capacitance C, respectively. As discussed in [30], the ESR will increase with time, whereas C might decrease.

As can be seen from the analysis in Section II, the overall capacitor current is independent from the capacitor parameters. Nevertheless, since the capacitor parameters change over time due to degradation, the lifetime of the capacitor will be affected. An increase in ESR will lead to an increase of the hotspot temperature, which in turn may lead to a faster degradation due to increased electrolyte evaporation. In the case of a dc-link capacitor tank with several branches in parallel sharing the overall current, degradation will still lead to an increasing ESR of the respective capacitor, but since the impedance of the respective branch will increase accordingly, the current sharing within the capacitor tank will change. The current will not be shared equally anymore, but branches with less aged capacitors, and therefore, lower impedance values will carry more current than branches with more aged capacitors. Thereby, the aging of the more stressed capacitors will be increased due to the higher power dissipation and the subsequent increased temperature stress, leading to a reduction in lifetime of the overall capacitor tank. Thus, in order to better understand and predict the lifetime of capacitors employed in dc-link applications, it is necessary to quantify the impacts of mission profile oriented stresses on capacitor hotspot temperature.

## IV. POWER CONVERTER FOR CAPACITOR TEST [29]

#### A. Topology Selection

The power converter in this section aims at injecting the electrical stress to a CUT in order to stress the CUT with sinusoidal currents having different frequencies obtained in Section II.

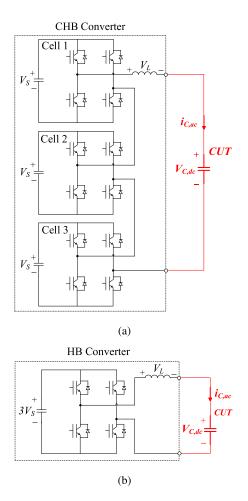

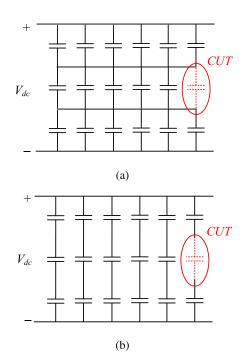

Fig. 6. Possible converters for capacitor test; (a) CHB and (b) HB.

Two possible converters, which are the cascaded H-bridge (CHB) and the H-bridge (HB) shown in Fig. 6, are discussed in terms of structure complexity, THD, filter size, and source voltage. The major challenge is to achieve the given test requirements of the high-frequency sinusoidal currents with a low THD and the high dc bias voltage on the CUT. It is worth noting that the low THD is beneficial to the further clear correlation between the frequency and the temperature variation.

The CHB converter in Fig. 6(a) is composed of three H-bridge cells connected in series, allowing the multilevel output voltage with the six times higher equivalent switching frequency by the phase shifted modulation, and the three times lower source voltage for each cell [31], as shown in Fig. 7(a). These features make the filter inductance to be reduced (by the multilevel voltage and the high equivalent switching frequency) and the commercially available switching devices to be acceptable to generate the high dc bias voltage on the CUT (by the lower source voltage of each cell). On the other hand, the HB converter in Fig. 6(b) is considered for the system complexity point of view, since this can be realized with 1/3 less number of switching devices and voltage sources in comparison with the CHB converter; nevertheless, the advantages of the CHB converter cannot be matched by the HB converter, as shown in Fig. 7(b).

Fig. 7. Output voltage and its harmonic spectrum of (a) CHB and (b) HB.

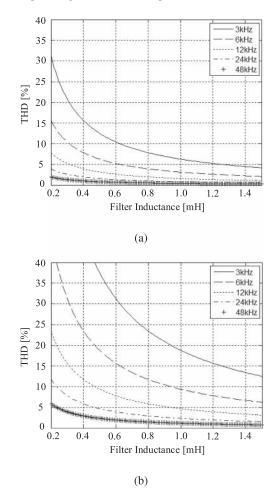

Fig. 8. THD as a function of filter inductance under different switching frequencies in case of (a) CHB and (b) HB.

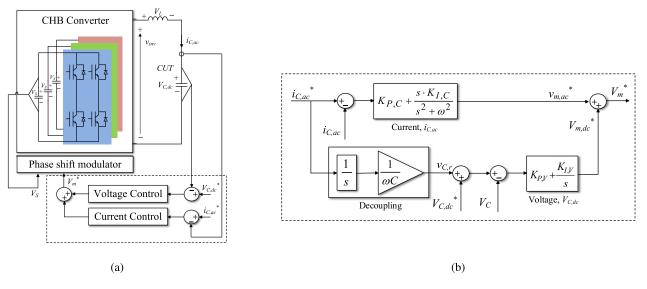

Fig. 9. (a) Concept of parallel control strategy and (b) its control block diagram.

Fig. 10. Typical schemes of capacitor bank in a back-to-back converter; (a) internally paralleled and (b) not internally paralleled.

In the following, the THD performance of each converter is evaluated by a mathematically derived equation, which is a function of the filter inductance and the switching frequency. The dc bias voltage of the CUT can be defined as

$$V_{C,dc} = 6 \cdot V_S \cdot (D - 0.5) \tag{9}$$

where  $V_S$  is the source voltage and D represents the duty ratio whose range is from zero to one. The voltage drop across the filter inductor is determined by a relation between  $V_S$  and  $V_{C,dc}$ as

$$V_L = 3 \cdot V_S - V_{C,dc}. \tag{10}$$

Then, the switching ripple current is given as

$$\Delta I_L = \frac{V_L \cdot D}{L \cdot f_S} \quad \text{(CHB)}$$

$$\Delta I_L = \frac{3 \cdot V_L \cdot D}{L \cdot f_S} \quad \text{(HB)} \tag{11}$$

where L is the filter inductance and  $f_S$  denotes the device switching frequency.

By substituting (9) and (10) into (11), the switching ripple current can be defined as a function of L,  $f_S$ , and D, assuming that  $V_S$  is constant

$$\Delta I_L(L, f_S, D) = \frac{V_S \cdot (1 - D) \cdot D}{L \cdot f_S} \quad \text{(CHB)}$$

$$\Delta I_L(L, f_S, D) = \frac{3 \cdot V_S \cdot (1 - D) \cdot D}{L \cdot f_S} \quad \text{(HB)}. \quad (12)$$

Consequently, the THD can be determined by (12) and amplitude of the capacitor current as

$$\text{THD} = \frac{\Delta I_L(L, f_S, D)}{|i_{C, \text{ac}}|}.$$

(13)

The THD of each converter is shown in Fig. 8 as a function of the filter inductance with different switching frequencies, where D is fixed to 0.5 for simplicity. In order to achieve the same THD performance with the HB, either a bigger filter inductance or a higher switching frequency needs to be chosen. However, the bigger filter inductance leads a lower effective dc bias voltage on the CUT due to a higher voltage drop across the filter, which implies a higher source voltage to be required. Even though the filter inductance can be reduced by employing the higher switching frequency, this is limited by the commercially available switching devices. The relation between the total source voltage and the voltage drop on the filter inductor is presented in (14), and this should be satisfied in order to provide the  $i_{C,ac}$ in combination with the  $V_{C,dc}$

$$V_S \ge V_{C,dc} + 2 \cdot \pi \cdot f_{I_C} \cdot L \cdot i_{C,ac} \tag{14}$$

where  $f_{Ic}$  denotes the fundamental frequency of  $i_{C,ac}$ .

Consequently, the CHB converter is reasonable solution for this purpose, since the better THD performance can be achieved with the lower filter inductance and the slower switching frequency, then, in turn, this leads the lower source voltage and the lower block voltage of the switching devices.

## B. Parallel Control Strategy

As stated before, the sinusoidal current  $(i_{C,ac})$  and the dc bias voltage  $(V_{C,dc})$  on the CUT should be simultaneously controlled and this can be done by the proposed parallel control strategy shown in Fig. 9(a). As shown in Fig. 9(b), the current and the voltage control are accomplished by means of the proportional resonance (PR) and the proportional integral (PI) loop, respectively, and the final reference  $(V_m^*)$  is obtained by the summation of their output as

$$V_{m}^{*} = V_{m,dc}^{*} + v_{m,ac}^{*}$$

=  $V_{m,dc}^{*} + V_{m,ac}^{*} \cdot \cos(\omega t + \varphi)$  (15)

where  $V_{m,dc}^*$  is the output of the voltage control loop,  $v_{m,ac}^*$  is the output of the current control loop,  $\omega$  is the angular frequency, and  $\Phi$  denotes the initial phase. The proposed control strategy also features to decouple the two paralleled control loops in order to prevent a conflicting target, since the current ( $i_{C,ac}$ ) through the CUT causes a ripple voltage on the dc bias voltage ( $V_{C,dc}$ ) as

$$V_C = V_{C,dc} + v_{C,r} \tag{16}$$

where  $v_{C,r}$  is the ripple component that is coupled with the current. Hence, this component should be eliminated and can be expressed by the capacitance of the CUT and the current reference as

$$v_{C,r} = \frac{1}{s} \cdot \frac{1}{\omega C} \cdot i_{C,\mathrm{ac}}^*. \tag{17}$$

By adding the above-mentioned equation to the reference of the dc bias voltage  $(V_{C,dc}^*)$  and, then, substituting it by the measured voltage  $(V_C)$ , only dc component can be fed to the voltage controller.

To conclude the section, it is worth noting that the proposed control block in Fig. 9(b) provides single sinusoidal currents in order to analyze the effect of each single frequency based on the decomposition of considered current profile. However, the real current profile could be synthesized with additional PR current controllers to combine the impacts of several harmonic components. Moreover, the feedback controller could be mathematically designed with consideration of the system nonlinearity for precise and stable performance in [32]. Finally, the presented analysis can be adopted to other applications that feature dc-link capacitors, like the uninterrupted power supplies [33].

## V. EXPERIMENTAL RESULTS

The typical configuration of a dc-link capacitor bank in a back-to-back converter is shown in Fig. 10 [34]. In this experiment, a single capacitor in the capacitor bank is targeted for the purpose of this paper.

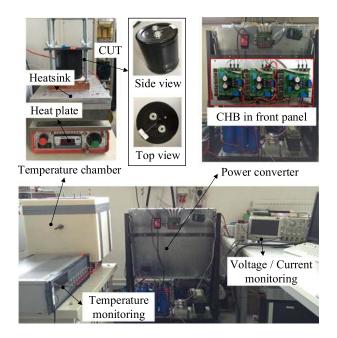

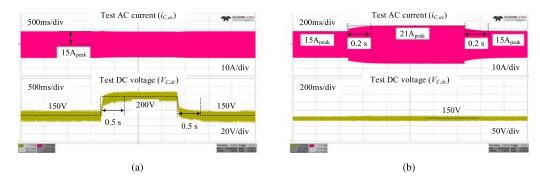

Fig. 11. Configuration of entire experimental setup; seven-level CHB converter, monitoring systems, temperature chamber, and CUT integrated with fiber optic sensor.

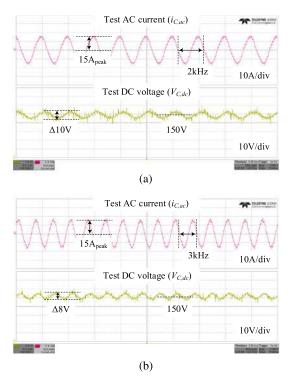

Fig. 12. High-frequency sinusoidal current of (a) 2 kHz and (b) 3 kHz at dc bias voltage of 150 V [29].

As shown in Fig. 11, the developed setup is composed of the seven-level CHB converter controlled by a microprocessor "MPC5643L," the monitoring system for current and voltage on the CUT, and the temperature chamber to keep the ambient temperature at a same level during a test. Moreover, a temperature sensor is integrated into the CUT in order to measure directly the core temperature variation, which brings more precise re-

Fig. 13. Dynamic characteristic of (a) dc bias voltage control and (b) sinusoidal current control [29].

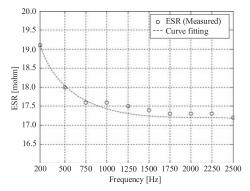

Fig. 14. ESR measurement of CUT.

sults than estimating methods through a case temperature and a thermal impedance [4], [5]. The core temperature of the CUT is measured by fiber optic sensors "OTG-A" and recorded by the signal conditioner "ProSens."

As stated in the previous section, the challenge of this work is to generate the high-frequency sinusoidal current in few kHz and to regulate the dc bias voltage simultaneously. The proposed control strategy is verified in Fig. 12(a) and (b) with controlled currents of 2 kHz and 3 kHz at the bias voltage of 150 V, respectively.

The paralleled control strategy allows basically the two parameters (the sinusoidal current and the dc bias voltage) to be controlled and the decoupling feed-forward term serves the ability of the completely separated control. This is confirmed through showing the dynamic characteristic in Fig. 13. Fig. 13(a) shows the case of the voltage control from 150 V to 200 V with the fixed current at 15  $A_{\text{peak}}$ . The opposite case that the current is regulated from 15  $A_{\text{peak}}$  to 21  $A_{\text{peak}}$  while the voltage is fixed at 150 V is shown in Fig. 13(b). As it can be seen in both the cases, the change of one parameter does not affect the control performance of another parameter.

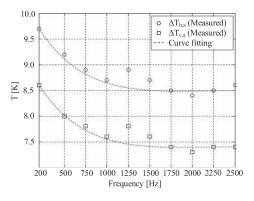

In Fig. 14, the ESR of the CUT (aluminum electrolytic capacitor 4500  $\mu$ F, 500 V) measured at different frequencies is depicted and this is done with an *LCR* meter. As it can be seen, the ESR shows the frequency-dependent behavior as described in Section III. In order to verify the capabilities of the test setup at room temperature, constant amplitude ripple currents (14.3  $A_{\rm rms}$ ) are applied to the CUT at different fundamental frequencies and the resulting hotspot temperatures are measured. The temperature differences between hotspot and am-

Fig. 15. Measurement of differences between core and ambient temperatures  $(\Delta T_{h,a})$  and case and ambient temperatures  $(\Delta T_{c,a})$  at constant amplitude sinusoidal currents at different fundamental frequencies.

bient  $\Delta T_{h,a}$  and case and ambient  $\Delta T_{c,a}$ , respectively, are shown in Fig. 15. In this context, case temperature refers to the temperature measured at the side of the capacitor can. Since the amplitude of the applied ripple current is fixed, it is expected that the curve of the hotspot temperature shows a proportional behavior to the measured curve of the ESR as shown in Fig. 14. As can be seen from Fig. 15, the progression of the measured temperature curves of both,  $\Delta T_{h,a}$  and  $\Delta T_{c,a}$ , respectively, matches well the expectations. The measurements can be repeated for capacitors at different aging stages. Since the ESR of the capacitor will increase with increasing degradation, a higher hotspot temperature is to be expected in the experiments.

#### VI. CONCLUSION

This paper proposed a capacitor test setup to control sinusoidal currents at variable frequency and different dc bias voltages to reproduce the operating condition of the dc-link of a wind turbine system. This leads to the better understanding of relation between current harmonics and the capacitor hotspot temperature. To consider a real operating condition, the dc-link current in a back-to-back converter was decomposed as case study, and it was pointed out that the current harmonics are mainly distributed around the switching frequency harmonics. It was confirmed that this test requirement of high-frequency current in combination with dc voltage offset can be performed by the proposed converter and the control strategy. Finally, the capability of the test setup to provide sinusoidal test currents for a broad range of frequencies was demonstrated by means of temperature measurements of case to ambient and hotspot to ambient in a test capacitor. Therefore, with the proposed setup it is possible to quantify impacts of wind turbine dc-link capacitor operating conditions on the capacitor lifetime.

APPENDIX A. System Specification and Simulation Condition

TABLE A-1 Specification of Wind Turbine System

|                     | Rated power                 | 2 MW   |

|---------------------|-----------------------------|--------|

|                     | Rated voltage               | 690 V  |

| Machine-side (PMSG) | Rated frequency $(f_m)$     | 50 Hz  |

|                     | Number of poles             | 4      |

|                     | Switching frequency         | 1 kHz  |

| DC-Link             | Capacitance $(C_{dc})$      | 10 mF  |

|                     | Voltage ( $V_{\rm dc}$ )    | 1100 \ |

| Grid-side           | Line-to-line voltage        | 690 V  |

|                     | Frequency $(f_g)$           | 50 Hz  |

|                     | Switching frequency $(f_s)$ | 1 kHz  |

TABLE A-2 Considered Operating Points to Identify Their Impact on Current Spectrum

| No. | Power (kW) | Machine-side (PMSG)                                                 |                      | Grid-side                         |      |

|-----|------------|---------------------------------------------------------------------|----------------------|-----------------------------------|------|

|     |            | Rotating speed<br>(r/min)<br>Current per phase<br>$(A_{rm s})$      | 600 (20 Hz)<br>266   | Current per phase $(A_{\rm rms})$ | 106  |

| 2   | 432        | Rotating speed<br>(r/min)<br>Current per phase<br>$(A_{\rm rm s})$  | 900 (30 Hz)<br>600   | Current per phase $(A_{\rm rms})$ | 360  |

| 3   | 1024       | Rotating speed<br>(r/min)<br>Current per phase<br>$(A_{rms})$       | 1200 (40 Hz)<br>1066 | Current per phase $(A_{\rm rms})$ | 853  |

| 4   | 2000       | Rotating speed<br>(r/min)<br>Current per phase<br>$(A_{\rm rm  s})$ | 1500 (50 Hz)<br>1666 | Current per phase $(A_{\rm rms})$ | 1666 |

# B. CALCULATION OF DC-LINK CURRENT IN BACK-TO-BACK CONVERTER

The time varying switched dc-link machine- and grid-side currents are expressed as a summation of each phase currents multiplied by their corresponding switching function as

$$i_{\text{link},m}(t) = \sum_{\eta=1}^{3} I_m \cos\left(\omega_m t + \varphi_{\eta,m} - \varphi_{0,m}\right)$$

$$\cdot S_{\eta,m}\left(t, \omega_m, \omega_{sw}, \varphi_{\eta,m}, \varphi_{\text{pwm},m}\right)$$

$$i_{\text{link},g}(t) = \sum_{\eta=1}^{3} I_g \cos\left(\omega_g t + \varphi_{\eta,g} - \varphi_{0,g}\right)$$

$$\cdot S_{\eta,g}\left(t, \omega_g, \omega_{sw}, \varphi_{\eta,g}, \varphi_{\text{pwm},g}\right).$$

(A-1)

TABLE A-3 DEFINITION OF USED SYMBOLS

| Symbol                    | Description                                                   |  |  |

|---------------------------|---------------------------------------------------------------|--|--|

| $\omega_{sw}$             | sw Switching frequency                                        |  |  |

| $J_n(X)$                  | First kind Bessel function order n                            |  |  |

| $I_m$                     | Magnitude of the machine-side current                         |  |  |

| $\omega_m$                | Fundamental angular frequency of machine-side                 |  |  |

| $\varphi_{\eta,m}$        | Phase of three-phase voltages $(a, b, and c of machine-side)$ |  |  |

| $\varphi_{0,m}$           | Phase between ac voltage and current of machine-side          |  |  |

| $\varphi_{\text{pwm}, m}$ | Phase of machine-side PWM carrier signal                      |  |  |

| $m_{m,a}$                 | Modulation index of machine-side                              |  |  |

| $I_q$                     | Magnitude of the grid-side current                            |  |  |

| $\omega_q$                | Fundamental angular frequency of grid-side                    |  |  |

| $\varphi_{\eta,q}$        | Phase of three-phase voltages (a, b, and c of grid-side)      |  |  |

| $\varphi_{0,q}$           | Phase between ac voltage and current of grid-side             |  |  |

| $\varphi_{\text{pwm}, q}$ | Phase of grid-side PWM carrier signal                         |  |  |

| $m_{a,q}$                 | Modulation index of grid-side                                 |  |  |

| $\eta$                    | 1, 2, and 3 for phases a, b, and c                            |  |  |

The switching function of each phase can be formed by the phase voltage function as

$$S_{\eta,m} (t, \omega_m, \omega_{sw}, \varphi_{\eta,m}, \varphi_{\text{pwm},m})$$

$$= \frac{v_{\eta,m}(t, \omega_m, \omega_{sw}, \varphi_{\eta,m}, \varphi_{\text{pwm},m})}{V_{\text{dc}}}$$

$$S_{\eta,g} (t, \omega_g, \omega_{sw}, \varphi_{\eta,g}, \varphi_{\text{pwm},g})$$

$$= \frac{v_{\eta,g}(t, \omega_g, \omega_{sw}, \varphi_{\eta,g}, \varphi_{\text{pwm},g})}{V_{\text{dc}}}.$$

(A-2)

The  $v_{\eta,m}$  and  $v_{\eta,g}$  are expressed as a function of the time, the fundamental frequency, the switching frequency, the phase of three-phase voltages, and the phase of the PWM carrier signal by

$$\begin{split} \frac{v_{\eta,m}(t,\omega_m,\omega_{sw},\varphi_{\eta,m},\varphi_{\mathrm{pwm},m})}{V_{\mathrm{dc}}} &= \frac{1}{2} + \frac{2}{\pi} \sum_{n=1}^{\infty} \frac{1}{n\left(\frac{\omega_m}{\omega_{sw}}\right)} \\ &\times J_n\left(n\left(\frac{\omega_m}{\omega_{sw}}\right) \frac{\pi}{2} m_{a,m}\right) \sin\left(n\frac{\pi}{2}\right) \cos\left(n\left(\omega_m t + \varphi_{\eta,m}\right)\right) \\ &+ \frac{2}{\pi} \sum_{m=1}^{\infty} \frac{1}{m} J_0\left(m\frac{\pi}{2} m_{a,m}\right) \sin\left(m\frac{\pi}{2}\right) \cos\left(m\left(\omega_{sw} t + \varphi_{\mathrm{pwm},m}\right)\right) \\ &+ \frac{2}{\pi} \sum_{m=1}^{\infty} \sum_{n=-\infty}^{\infty} \frac{1}{q} J_n\left(q\frac{\pi}{2} m_{a,m}\right) \sin\left((m+n)\frac{\pi}{2}\right) \\ &\times \cos\left(m\left(\omega_{sw} t + \varphi_{\mathrm{pwm},m}\right) + n\left(\omega_m t + \varphi_{\eta,m}\right)\right) \\ &\frac{v_{\eta,g}(t,\omega_g,\omega_{sw},\varphi_{\eta,g},\varphi_{\mathrm{pwm},g})}{V_{\mathrm{dc}}} &= \frac{1}{2} + \frac{2}{\pi} \sum_{n=1}^{\infty} \frac{1}{n\left(\frac{\omega_g}{\omega_{sw}}\right)} \\ &\times J_n\left(n\left(\frac{\omega_g}{\omega_{sw}}\right)\frac{\pi}{2} m_{a,g}\right) \sin\left(n\frac{\pi}{2}\right) \cos\left(n\left(\omega_g t + \varphi_{\eta,g}\right)\right) \end{split}$$

$$+\frac{2}{\pi}\sum_{m=1}^{\infty}\frac{1}{m}J_0\left(m\frac{\pi}{2}m_{a,g}\right)\sin\left(m\frac{\pi}{2}\right)\cos\left(m\left(\omega_{sw}t+\varphi_{\mathrm{pwm},g}\right)\right)$$

$$+\frac{2}{\pi}\sum_{m=1}^{\infty}\sum_{n=-\infty}^{\infty}\frac{1}{q}J_n\left(q\frac{\pi}{2}m_{a,g}\right)\sin\left((m+n)\frac{\pi}{2}\right)$$

$$\cos\left(m\left(\omega_{sw}t+\varphi_{\mathrm{pwm},g}\right)+n\left(\omega_gt+\varphi_{\eta,g}\right)\right)$$

(A-3)

where  $q = m + n(\omega_m / \omega_{sw})$ . Finally, by substituting (A-2) and (A-3) into (A-1), the  $i_{\text{link},m}$  and  $i_{\text{link},q}$  are obtained.

#### REFERENCES

- A. M. Regheb and M. Ragheb, "Wind turbine gearbox technologies, fundamental and advanced topics in wind power," 2011. [Online]. Available: http://www.intechopen.com/books/fundamental-and-advancedtopics-in-wind-power/wind-turbine-gearbox-technologies

- [2] P. Venet, F. Perisse, M. H. El-Husseini, and G. Rojat, "Realization of a smart electrolytic capacitor circuit," *IEEE Ind. Appl. Mag.*, vol. 8, no. 1, pp. 16–20, Jan. 2002.

- [3] H. Wang, M. Liserre, and F. Blaabjerg, "Toward reliable power electronics: Challenges, design tools, and opportunities," *IEEE Ind. Electron. Mag.*, vol. 7, no. 2, pp. 17–26, Jun. 2013.

- [4] A. M. Imam, T. G. Habetler, R. G. Harley, and D. M. Divan, "LMS based condition monitoring of electrolytic capacitor," in *Proc. 31st Annu. Conf. IEEE Ind. Electron. Soc.*, Nov. 2005, pp. 848–853.

- [5] E. Aeloiza, J.-H. Kim, P. Enjeti, and P. Ruminot, "A real time method to estimate electrolytic capacitor condition in PWM adjustable speed drives and uninterruptible power supplies," in *Proc. 2005 IEEE 36th Power Electron. Spec. Conf.*, Jun. 2005, pp. 2867–2872.

- [6] H. Givi, E. Farjah, and T. Ghanbari, "Switch fault diagnosis and capacitor lifetime monitoring technique for dc-dc converters using a single sensor," *IET Sci. Meas. Technol.*, vol. 10, no. 5, pp. 513–527, 2016.

- [7] H. Soliman, H. Wang, and F. Blaabjerg, "A review of the condition monitoring of capacitors in power electronic converters," *IEEE Trans. Ind. Appl.*, vol. 52, no. 6, pp. 4976–4989, Nov. 2016.

- [8] J. Chen, W. Chen, J. Li, X. Zhang, and P. Sun, "Lifetime assessment of dc link electrolytic capacitor of wind power converter based on operational condition," in *Proc. 2016 IEEE Int. Conf. High Voltage Eng. Appl.*, Sep. 2016, pp. 1–4.

- [9] S. Ma, H. Wang, J. Tang, G. Zhu, and H. Wang, "Lifetime estimation of dc-link capacitors in a single-phase converter with an integrated active power decoupling module," in *Proc. 42nd Annu. Conf. IEEE Ind. Electron. Soc.*, Oct. 2016, pp. 6824–6829.

- [10] D. Zhou, H. Wang, and F. Blaabjerg, "Lifetime estimation of electrolytic capacitors in a fuel cell power converter at various confidence levels," in *Proc. 2016 IEEE 2nd Annu. Southern Power Electron. Conf.*, Dec. 2016, pp. 1–6.

- [11] S. Xue, Q. Zhou, J. Li, C. Xiang, and S. Chen, "Reliability evaluation for the dc-link capacitor considering mission profiles in wind power converter," in *Proc. 2016 IEEE Int. Conf. High Voltage Eng. Appl.*, Sep. 2016, pp. 1–4.

- [12] Rubycon Corporation, "Technical notes for electrolytic capacitor," 2015.

[Online]. Available: http://www.rubycon.co.jp/de/products/alumi/pdf /Life.pdf

- [13] H. Wang *et al.*, "Transitioning to physics-of-failure as a reliability driver in power electronics," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 2, no. 1, pp. 97–114, Mar. 2014.

- [14] F. Boattini and C. M. Genton, "Accelerated lifetime testing of energy storage capacitors used in particle accelerators power converters," in *Proc. 2015 17th Eur. Conf. Power Electron. Appl.*, Sep. 2015, pp. 1–10.

- [15] H. Wang, P. D. Reigosa, and F. Blaabjerg, "A humidity-dependent lifetime derating factor for dc film capacitors," in *Proc. 2015 IEEE Energy Convers. Congr. Expo.*, Sep. 2015, pp. 3064–3068.

- [16] P. Kreczanik, P. Venet, A. Hijazi, and G. Clerc, "Study of supercapacitor aging and lifetime estimation according to voltage, temperature, and rms current," *IEEE Trans. Ind. Electron.*, vol. 61, no. 9, pp. 4895–4902, Sep. 2014.

- [17] H. Wang and F. Blaabjerg, "Reliability of capacitors for dc-link applications in power electronic converters; an overview," *IEEE Trans. Ind. Appl.*, vol. 50, no. 5, pp. 3569–3578, Sep. 2014.

- [18] P. D. Evans and R. J. Hill-Cottingham, "DC link current in PWM inverters," *IEE Proc. B Elect. Power Appl.*, vol. 133, no. 4, pp. 217–224, Jul. 1986.

- [19] H. Zhang, N. Wheeler, and D. Grant, "Switching harmonics in the dc link current in a PWM ac-dc-ac converter," in *Proc. Conf. Rec.* 1995 IEEE Ind. Appl. Conf./30th IAS Annu. Meeting, vol. 3, Oct. 1995, pp. 2649–2655.

- [20] J. W. Kolar and S. D. Round, "Analytical calculation of the rms current stress on the dc-link capacitor of voltage-PWM converter systems," *IEE Proc. Elect. Power Appl.*, vol. 153, no. 4, pp. 535–543, Jul. 2006.

- [21] M. H. Bierhoff and F. W. Fuchs, "DC-link harmonics of threephase voltage-source converters influenced by the pulse width modulation strategy-an analysis," *IEEE Trans. Ind. Electron.*, vol. 55, no. 5, pp. 2085–2092, May 2008.

- [22] L. G. Gonzalez, G. Garcera, E. Figueres, and R. Gonzalez, "Effects of the PWM carrier signals synchronization on the dc-link current in back-to-back converters," *Appl. Energy*, vol. 87, no. 8, pp. 2491–2499, Mar. 2010.

- [23] Z. Qin, H. Wang, F. Blaabjerg, and P. C. Loh, "Investigation into the control methods to reduce the dc-link capacitor ripple current in a backto-back converter," in *Proc. 2014 IEEE Energy Convers. Congr. Expo.*, Sep. 2014, pp. 203–210.

- [24] N. Heng, L. Jiao, and H. Yikang, "Research on the unit power factor control of directly-driven PM wind generator," in *Proc. 2008 Int. Conf. Elect. Mach. Syst.*, Oct. 2008, pp. 2311–2315.

- [25] A. Venkataraman, A. I. Maswood, N. Sarangan, and O. H. P. Gabriel, "An efficient UPF rectifier for a stand-alone wind energy conversion system," *IEEE Trans. Ind. Appl.*, vol. 50, no. 2, pp. 1421–1431, Mar. 2014.

- [26] K. Ma, M. Liserre, and F. Blaabjerg, "Reactive power influence on the thermal cycling of multi-MW wind power inverter," *IEEE Trans. Ind. Appl.*, vol. 49, no. 2, pp. 922–930, Mar. 2013.

- [27] M. Tsili and S. Papathanassiou, "A review of grid code technical requirements for wind farms," *IET Renewable Power Gener.*, vol. 3, no. 3, pp. 308–332, Sep. 2009.

- [28] M. L. Gasperi, "Life prediction modeling of bus capacitors in ac variablefrequency drives," *IEEE Trans. Ind. Appl.*, vol. 41, no. 6, pp. 1430–1435, Nov. 2005.

- [29] Y. Ko, H. Jedtberg, G. Buticchi, and M. Liserre, "Topology and control strategy for accelerated lifetime test setup of dc-link capacitor of wind turbine converter," in *Proc. 2016 IEEE Appl. Power Electron. Conf. Expo.*, Mar. 2016, pp. 3629–3636.

- [30] A. Albertsen, "Electrolytic capacitor lifetime estimation." 2012. [Online]. Available: http://jianghai-europe.com/wp-content/uploads/1-Jianghai-Europe-E-Cap-Lifetime-Estimation-long-AAL-2012-10-30.pdf

- [31] B. Wu and M. Narimani, Cascaded H-Bridge Multilevel Inverters. Hoboken, NJ, USA: Wiley, 2017. [Online]. Available: http://ieeexplore. ieee.org/xpl/articleDetails.jsp?arnumber=7827420

- [32] M. M. J. de Vries, M. J. Kransse, M. Liserre, V. G. Monopoli, and J. M. A. Scherpen, "Passivity-based harmonic control through series/parallel damping of an H-bridge rectifier," in *Proc. 2007 IEEE Int. Symp. Ind. Electron.*, Jun. 2007, pp. 3385–3390.

- [33] K. Abdennadher, P. Venet, G. Rojat, J. M. Retif, and C. Rosset, "A realtime predictive-maintenance system of aluminum electrolytic capacitors used in uninterrupted power supplies," *IEEE Trans. Ind. Appl.*, vol. 46, no. 4, pp. 1644–1652, Jul. 2010.

- [34] V. Najmi, J. Wang, R. Burgos, and D. Boroyevich, "High reliability capacitor bank design for modular multilevel converter in MV applications," in *Proc. 2014 IEEE Energy Convers. Congr. Expo.*, Sep. 2014, pp. 1051–1058.

Youngjong Ko (S'16) received the B.Sc. and M.Sc. degrees in electronic engineering from Ajou University, Suwon, South Korea, in 2009 and 2012, respectively. Since 2015, he has been working toward the Ph.D. degree at the Chair of Power Electronics, University of Kiel, Kiel, Germany.

His research interests include grid-connected power converter and reliability in power electronics.

**Holger Jedtberg** (S'14) received the B.Sc. and M.Sc. degrees in electrical engineering and business administration from Christian-Albrechts-Universität zu Kiel, Kiel, Germany, in 2011 and 2013, respectively. Since 2014, he has been working toward the Ph.D. degree at the Chair of Power Electronics, Christian-Albrechts-Universität zu Kiel.

His research interests include control of power converters and robust design and reliability of power electronic systems.

Marco Liserre (S'00–M'02–SM'07–F'13) received the M.Sc. and Ph.D. degrees in electrical engineering from , Bari, Italy, in 1998 and 2002, respectively.

He was an Associate Professor at Bari Polytechnic and a Professor of reliable power electronics at Aalborg University, Denmark. He is currently a Full Professor and is the Chair of Power Electronics at Christian-Albrechts-University of Kiel, Kiel, Germany. He has published more than 300 technical papers (more than 70 of them in international peerreviewed journals), 4 chapters of a book, and a book

titled *Grid Converters for Photovoltaic and Wind Power Systems* (IEEE-Wiley, second reprint, also translated in Chinese). These works have received more than 20 000 citations.

Dr. Liserre is listed in the ISI Thomson report "The world's most influential scientific minds" in 2014. He received an ERC Consolidator Grant for the project "The Highly Efficient And Reliable smart Transformer (HEART), a new Heart for the Electric Distribution System." He is a member of the IAS, the PELS, the PES, and the IES. He is an Associate Editor of the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, the IEEE INDUSTRIAL ELECTRONICS MAGAZINE, the IEEE TRANSACTIONS ON INDUSTRIAL INFORMATICS, where he is currently the Co-EiC, the IEEE TRANSACTIONS ON POWER ELECTRONICS, and the IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS. He was the Founder and Editor-in-Chief of the IEEE INDUSTRIAL ELECTRONICS MAGAZINE, the Founder and the Chairman of the Technical Committee on Renewable Energy Systems, the Co-Chairman of the International Symposium on Industrial Electronics (ISIE 2010), the IES Vice-President responsible of the publications. He received the IES 2009 Early Career Award, the IES 2011 Anthony J. Hornfeck Service Award, the 2014 Dr. Bimal Bose Energy Systems Award, the 2011 Industrial Electronics Magazine best paper award, and the Third Prize paper award by the Industrial Power Converter Committee at ECCE 2012, in 2012. He is a senior member of the IES AdCom.

**Giampaolo Buticchi** (S'10–M'13–SM'17) was born in Parma, Italy, in 1985. He received the Master's degree in electronic engineering and the Ph.D. degree in information technologies from the University of Parma, Italy, in 2009 and 2013, respectively.

In 2012, he was a Visiting Researcher at the University of Nottingham, Nottingham, U.K. He is currently a Postdoctoral Research Associate at the University of Kiel, Kiel, Germany. His research interests include power electronics for renewable energy systems, smart transformer-fed microgrids, and reliability in power electronics.