Seo, J., Lee, J. and Shin, M. (2014) Analysis of drain-induced barrier rising in short-channel negative-capacitance FETs and Its applications. *IEEE Transactions on Electron Devices*, 64(4), pp. 1793-1798. (doi:10.1109/TED.2017.2658673)

This is the author's final accepted version.

There may be differences between this version and the published version. You are advised to consult the publisher's version if you wish to cite from it.

http://eprints.gla.ac.uk/143025/

Deposited on: 26 June 2017

Enlighten – Research publications by members of the University of Glasgow http://eprints.gla.ac.uk33640

# Analysis of Drain-Induced Barrier Rising in Short-Channel Negative Capacitance FETs and Its Applications

Junbeom Seo, Jaehyun Lee, and Mincheol Shin

Abstract—We investigate the performance of hysteresis-free short-channel negative-capacitance field-effect transistors (NCFETs) by combining quantum mechanical calculations with the Landau-Khalatnikov equation. When the subthreshold swing (SS) becomes smaller than 60 mV/dec, a negative value of drain-induced barrier lowering (DIBL) is obtained. This behavior, drain-induced barrier rising (DIBR), causes negative differential resistance (NDR) in the output characteristics of NCFETs. We also examine the performance of an inverter composed of hysteresis-free NCFETs to assess the effects of DIBR at the circuit level. Contrary to our expectation, although hysteresis-free NCFETs are used, hysteresis behavior is observed in the transfer properties of the inverter. Furthermore, it is expected that the NCFET inverter with hysteresis behavior can be used as a Schmitt trigger inverter.

Index Terms—Subthreshold swing, ferroelectric, negative capacitance FET, hysteresis behavior, drain-induced barrier lowering, Schmitt trigger inverter

#

Fig. 1. (a) Schematic structure of the UTB NCFET and (b) a series of ferroelectric  $(C_{FE})$ , dielectric  $(C_{ox})$ , and semiconductor capacitors  $(C_s)$ . The gate capacitance  $(C_G)$  is modeled as a series capacitance of  $C_{FE}$  and  $C_{ox}$

### I. INTRODUCTION

S conventional metal-oxide-semiconductor field-effect-transistors (MOSFETs) are reduced to a nanometer scale, the subthreshold swing (SS) reaches the fundamental thermal limit of 60 mV/dec [1]. It is well-known that this limitation is an obstacle to achieving high-performance and low-power consumption devices. To solve this issue, new device concepts, such as impact ionization MOS (I-MOS) [2] and tunneling FETs (TFETs) [3] have been suggested. Despite their outstanding features, I-MOS suffers from reliability issues and is not suitable for low-power consumption devices because of their high applied voltages. In the case of TFETs, ON-state current ( $I_{ON}$ ) is restricted due to tunneling probability, even though sub-60 mV/dec switching behavior occurs [3]-[6].

In recent years, negative capacitance FETs (NCFETs), proposed by Salahuddin  $et\ al.$  [7], have received much attention as a new type of steep switching device. NCFETs are capable of achieving steep SS and high  $I_{ON}$  by amplification of the gate voltage  $(V_{GS})$  through the ferroelectric material. Unlike I-MOS and TFETs, the  $I_{ON}$  of NCFETs strongly depends on the thermionic currents. According to recent experimental studies on NCFETs, they have successfully achieved very steep SS values of 18 and 11.3 mV/dec as well as a high ON/OFF current ratio with low drain volgate  $(V_{DS})$  [8]-[10].

$(Corresponding\ author\ :\ Mincheol\ Shin.)$

The authors are with the School of Electrical Engineering, Korea Advanced Institute of Science and Technology, Daejeon 34141, South Korea (e-mail: jbseo@kaist.ac.kr; jaehyun.lee@kaist.ac.kr; mshin@kaist.ac.kr).

There has been growing interest in the evaluation and optimization of NCFETs. Kobayashi  $et\ al.\ [11]$  suggested exploiting the ferroelectric properties to design low-power NCFETs. The dependences of NCFET performances on ferroelectric thickness  $(T_{FE})$  have been studied extensively [12]-[16]. Khan  $et\ al.\ [17]$  provided guidelines for parameters to develop low-power NCFETs. Since NCFETs are based on conventional MOSFETs, they may be vulnerable to short-channel effects (SCEs). Recently, Li  $et\ al.\ [18]$  pointed out the coupling effects between gate and drain on the device performance of short-channel bulk NCFETs. Except for Li's work, SCEs on NCFETs have never been reported.

In this work, we investigated the performance of short-channel NCFETs through quantum mechanical simulations with the Landau-Khalatnikov (LK) equation. We especially focused our attention on the SCEs associated with  $V_{DS}$  and drain-induced barrier lowering (DIBL). Furthermore, we explored the influence of SCEs on the inverter to verify the viability of NCFETs at the circuit level.

The remainder of this paper is organized as follows. Section II describes our simulation approach based on the LK theory and quantum transport. In Section III, the basic properties of NCFETs are presented focusing on the SCEs. We discuss the characteristics of the NCFET inverter and propose a new application in Section IV, followed by a summary and conclusions in Section V.

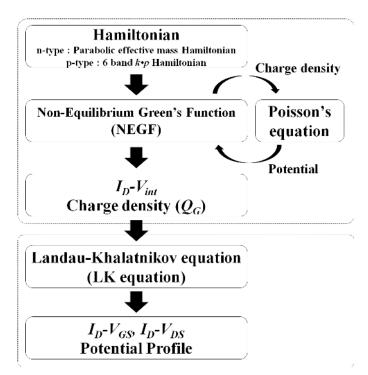

Fig. 2. Flowchart of the NCFET simulation.

### II. SIMULATION APPROACH

A schematic diagram of the ultra-thin body (UTB) double-gate (DG) NCFETs simulated in this work is shown in Fig. 1(a). The key difference between the structure of NCFETs and conventional MOSFETs is the presence of a ferroelectric material in the gate stack. As in the case of recent experiments [8][9], the ferroelectric and baseline MOSFET in our work are supposed to be spatially separated, but connected by a metal layer with the same contact area, which provides the same gate charge density  $(Q_G)$  to both the internal gate and ferroelectric surfaces. The channel length  $(L_{ch})$  and  $T_{FE}$  are subject to variation, whereas the channel thickness  $(T_{Si})$  and equivalent oxide thickness (EOT) are assumed to be 5 and 2 nm, respectively.

Fig. 1(b) describes the equivalent capacitance model. An NCFET can be depicted with three capacitances, including ferroelectric, dielectric, and semiconductor capacitors. The total gate capacitance  $(C_G)$  consists of a series combination of oxide  $(C_{ox})$  and ferroelectric  $(C_{FE})$  capacitances. The internal voltage  $(V_{int})$  indicates the voltage amplified by the ferroelectric, and it acts as  $V_{GS}$  in the conventional MOSFET.

The overall simulation procedure shown in Fig. 2 consists of two parts: electronic calculation and ferroelectric capacitor modeling.

First, we solve the non-equilibrium Greens function (NEGF) and Poisson equation self-consistently in the ballistic transport regime for the conventional MOSFET with the same dimensions as those of NCFETs [19]. In the channel region, the effective mass Hamiltonian and 6 bands  $k \cdot p$  Hamiltonian for n-type and p-type devices are used to describe the conduction and valence bands, respectively. The effective masses are calibrated from the  $sp^3d^5s^*$  tight-binding method [20]. The

Luttinger parameters are adjusted from the  $sp^3s^*$  tight-binding method [21]. From the self-consistent calculation, we obtain  $Q_G$  and drain current  $(I_D)$  as a function of  $V_{GS}$ .

Next, the ferroelectric capacitor is modeled as follows. The LK equation [22][23] which describes the dynamics of polarization in response to time is given as

$$\rho \frac{dP}{dt} + \nabla_{\vec{P}} U = 0, \tag{1}$$

where  $\rho$ , P, and t are resistivity, polarization, and time, respectively. Here, U represents the free energy of the ferroelectric material and is defined by the Landau-Devonshire (LD) theory [24] as

$$U = \alpha P^2 + \beta P^4 + \gamma P^6 - \vec{E} \cdot \vec{P}, \tag{2}$$

where E is an external electric field and  $\alpha$ ,  $\beta$ , and  $\gamma$  are the order parameters. In the case of the ferroelectric material,  $\alpha$  is always negative. In this work, the ferroelectric material is assumed to be SrTiO3 with the parameters of  $\alpha=-6.5\times10^7$  m/F ,  $\beta=3.75\times10^9$  m<sup>5</sup>/F/C², and  $\gamma=0$  m<sup>9</sup>/F/C⁴ [25]. We note that the use of bulk order parameters in this work may be justified considering the supposed spatial separation between the ferroelectric and baseline MOSFET. However, in an ultimate integration of ferroelectric into the gate stack, the size of ferroelectric should affect the ferroelectricity [26]-[28] and thus leads to different order parameters than the bulk ones. We nevertheless believe that the overall trend as predicted from the results of this work might not change in nature.

We assume that the ferroelectric is in steady-state polarization (dP/dt=0). Substituting Eq. (2) into Eq. (1), the electric field is given as

$$E = 2\alpha P + 4\beta P^3,\tag{3}$$

which can be further derived as

$$V_{int} = V_{GS} - \left[2\alpha P + 4\beta P^3\right]T_{FE},\tag{4}$$

where  $V_{int}$ ,  $V_{GS}$ , and  $T_{FE}$  are the internal voltage, gate bias, and ferroelectric thickness, respectively. Since  $Q_G$  can be expressed as  $Q_G = P + \epsilon_0 E \approx P$  because P of the ferroelectric is larger than  $\epsilon_0 E$ , Eq. (4) is approximated as

$$V_{int} = V_{GS} - [2\alpha Q_G + 4\beta Q_G^3] T_{FE}.$$

(5)

Finally, the drain current at a particular gate voltage  $(V_{GS}^{NCFET})$  in NCFETs,  $I_D^{NCFET}(V_{GS}^{NCFET})$ , is obtained by looking up the drain current in the conventional MOSFET which was precalculated in the previous step,  $I_D^{MOSFET}(V_{GS})$ , as follows:

$$I_D^{NCFET}(V_{GS}^{NCFET}) = I_D^{MOSFET}(V_{GS}),$$

where  $V_{GS} = V_{int}(V_{GS}^{NCFET})$  as given by Eq. (5).

# III. CHARACTERISTICS OF NCFET

# A. Dependence on $T_{FE}$

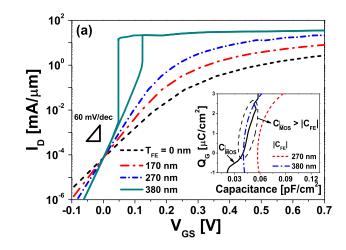

Fig. 3 presents the transfer characteristics of conventional MOSFETs and NCFETs with  $L_{ch}=20$  nm, respectively. As  $T_{FE}$  increases,  $I_{ON}$  increases and SS decreases. For instance, NCFETs with  $T_{FE}=270$  nm provide larger  $I_{ON}$  (12.9 mA/ $\mu$ m) and lower SS (43.5 mV/dec) than conventional

Fig. 3. Transfer characteristics of the conventional MOSFET ( $T_{FE}=0$  nm) and NCFETs with  $T_{FE}=170,\,270$  and 380 nm. Inset shows  $Q_G$  versus the capacitance of NCFETs with  $T_{FE}=270$  and 380 nm.

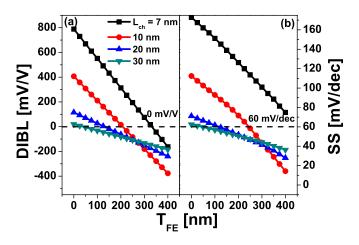

Fig. 4. (a) DIBL and (b) SS as a function of  $T_{FE}$  for  $L_{ch}$  = 7, 10, 20, and 30 nm.

MOSFETs (1.1 mA/ $\mu$ m and 71.5 mV/dec). However, in the case of NCFETs with  $T_{FE}$  = 380 nm, the hysteresis behavior is observed. Inset of Fig. 3 shows the MOS capacitance ( $C_{MOS}$ ) and  $C_{FE}$  as a function of  $Q_G$  for NCFETs with  $T_{FE}$  = 270 and 380 nm. For  $T_{FE}$  = 270 nm,  $C_G$  is positive in the all range of  $Q_G$ , because  $|C_{FE}|$  is larger than  $C_{MOS}$ . For  $T_{FE}$  = 380 nm, on the other hand,  $|C_{FE}| > C_{MOS}$  in a certain range of  $Q_G$  and so  $C_G$  becomes negative in the range only. In this condition, NCFETs become unstable, resulting in the hysteresis behavior [17]. Such a trade-off between high performance and hysteresis agrees well with previous results [12][17]. Since hysteresis behavior is not desirable, we consider only hysteresis-free NCFETs hereafter.

The dependence of DIBL and SS on  $T_{FE}$  is shown in Fig. 4. Regardless of the hysteresis behavior, we can extract SS and DIBL for the forward sweep. SS is defined as the minimum inverse slope near threshold voltage  $(V_{th})$ , which is defined as the gate voltage at which  $I_D=0.1~\mu\text{A}/\mu\text{m}$  for the forward sweep. It is interesting to note that in the cases of devices with  $L_{ch}=20$  and 30 nm, DIBL has a value of 0 mV/V when

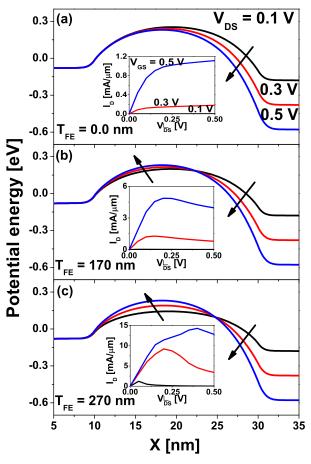

Fig. 5. Potential profile at  $V_{GS}$  = 0.0 V for (a) the conventional MOSFET and NCFETs with (b)  $T_{FE}$  = 170 and (c) 270 nm. Insets show the output characteristics of each device.

SS becomes 60 mV/dec. This behavior can be explained by the fundamental semiconductor theory as follows. First, SS is defined as

$$SS = \frac{dV_{GS}}{dlog_{10}I_D} = \frac{dV_{GS}}{d\phi_s} \frac{d\phi_s}{dlog_{10}I_D} = (1 + \frac{C_s}{C_G}) \times \frac{k_BT}{q} ln10,$$

(6)

where  $\phi_s$ ,  $k_B$ , T, and q are the surface potential, Boltzmann constant, temperature, and electronic charge, respectively. Secondly, DIBL is expressed as

$$DIBL = \frac{V_{th}^{high} - V_{th}^{low}}{V_{DS}^{high} - V_{DS}^{low}},\tag{7}$$

where  $V_{th}^{low(high)}$  is the threshold voltage at low (high)  $V_{DS}^{low(high)}$ . From the fundamental theory of bulk transistors,  $V_{th}$  is written as

$$V_{th} = \phi_{MS} + 2\phi_{bi} + \frac{Q_G}{C_G},\tag{8}$$

where  $\phi_{MS}$  is the work function difference between the gate metal and semiconductor and  $\phi_{bi}$  is the built-in potential [29]. Assuming that  $\phi_{MS}$  and  $\phi_{bi}$  are not affected by the ferroelectric,  $V_{th}$  only depends on  $Q_G/C_G$ . That is, if the value

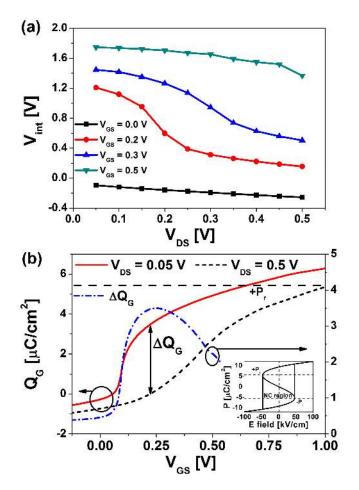

Fig. 6. (a)  $V_{int}$  versus  $V_{DS}$  for the n-type NCFETs with  $T_{FE}$  = 270 nm and (b)  $Q_G$  versus  $V_{GS}$ . Inset of (b) shows the polarization versus electric field for SrTiO<sub>3</sub>, where the remanent polarization  $(P_r)$  and coercive electric field  $(E_c)$  are 5.2  $\mu$ C/cm<sup>2</sup> and 46.6 kV/cm, respectively.

of  $C_G$  is very large (it can be infinite when  $C_{ox} = -C_{FE}$  for NCFETs), DIBL becomes 0 mV/V. At the same time, the first term of SS, called the body factor, becomes 1, thus, SS becomes 60 mV/dec at room temperature.

When  $L_{ch}=7$  and 10 nm, we cannot find the specific  $T_{FE}$  to satisfy DIBL = 0 mV/V and SS = 60 mV/dec simultaneously. This is because, as  $L_{ch}$  decreases, the direct source-to-drain tunneling current increases. Thus, SS no longer can be described by Eq. 6. Therefore, when DIBL = 0 mV/V, SS  $\neq$  60 mV/dec in short-channel devices.

# B. Drain-Induced Barrier Raising (DIBR)

In the previous subsection, we showed that when SS becomes less than 60mV/dec, DIBL has a negative value. This behavior is in good agreement with Li's work [18]. To investigate it in details, we first compare the potential profile in the channel region of conventional MOSFETs and NCFETs with  $T_{FE}=170$  and 270 nm, respectively, as shown in Fig. 5. Here,  $L_{ch}$  is assumed to be 20 nm for these devices. In the case of the conventional MOSFET, the potential barrier is lowered with increasing  $V_{DS}$ , which indicates a typical DIBL. However, NCFETs show the opposite trend, which we call drain-induced barrier rising (DIBR).

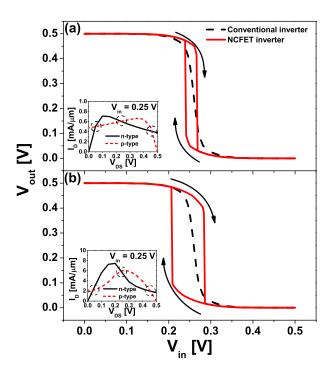

Fig. 7. Voltage transfer characteristics of the NCFET inverters with (a)  $T_{FE}$  = 170 (n-type) and 140 (p-type) nm and (b)  $T_{FE}$  = 270 (n-type) and 280 (p-type) nm. Dashed lines represent the voltage transfer characteristics of the conventional MOSFET. Insets show the road line of the n-type and p-type NCFETs at  $V_{in}$  = 0.25 V.

The  $V_{int}$  values of NCFETs are plotted as a function of  $V_{DS}$  with various  $V_{GS}$  values in Fig. 6(a). To exhibit DIBR clearly,  $T_{FE}$  and  $L_{ch}$  of NCFETs are assumed to be 270 and 20 nm, respectively. From Fig. 6(a), we can see that, as  $V_{DS}$  increases,  $V_{int}$  decreases. In particular, when  $V_{GS}$  = 0.2 V,  $V_{int}$  undergoes a steep variation. This behavior can be elucidated by Fig. 6(b) and Eq. (6). In this case, the NCFET is operated in the NC region because  $Q_G$  is less than remanent polarization  $(P_r)$  of 5.2  $\mu$ C/cm<sup>2</sup>, as seen in Fig. 6(b) and its inset. Due to the small  $Q_G$  in the NC region, the second term in Eq. (5) is more dominant than the third term. Moreover, Fig. 6(b) shows that  $Q_G$  for  $V_{DS} = 0.05$  V is higher than that for  $V_{DS}$  = 0.5 V. As a consequence,  $Q_G$  reduction with increasing  $V_{DS}$  leads to a decrease in  $V_{int}$ , resulting in DIBR as seen in Fig. 5(b). In addition, variation in  $V_{int}$  with respect to  $V_{DS}$  is well in accordance with the change in  $Q_G$ ,  $\triangle Q_G(Q_G(V_{DS} = 0.05 \text{ V}) - Q_G(V_{DS} = 0.5 \text{ V}).$

As seen in the insets of Fig. 5(b) and (c), NCFETs show negative differential resistance (NDR) [16][30], which is a distinctive feature that is not seen in the conventional MOSFET. In a Gunn diode, known as a transferred-electron device, NDR is induced by the transition of electrons from a high-mobility valley to a low-mobility valley [31]. In the case of NCFETs, however, it occurs due to the reduction of current caused by DIBR. For instance, when  $T_{FE}$  = 270 nm,  $V_{int}$  is reduced from 1.45 to 0.5 V with increasing  $V_{DS}$  from 0.05 to 0.5 V as shown in Fig. 6(a), and NDR is induced as a consequence. Moreover, since DIBR is associated with  $C_{FE}$ , NDR can be controlled

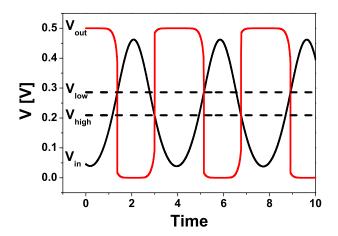

Fig. 8. Transient response of NCFET inverters with  $T_{FE}$  = 270 (n-type) and 280 (p-type) nm.  $V_{in(out)}$  and  $V_{low(high)}$  are input (output) signal and low (high) threshold voltage, respectively.

by  $T_{FE}$ . Despite NDR, NCFETs still deliver a larger current than the conventional MOSFET.

In recent experimental works where SS less than 60 mV/dec was achieved [9][32], DIBR and NDR behaviors were not observed. In [9],  $Q_G$  shows only a weak dependence on  $V_{DS}$  which makes DIBL more predominant than DIBR. In a different setting where  $Q_G$  becomes a stronger function of  $V_{DS}$ , we may expect appearance of both NDR and DIBR.

### IV. NCFET INVERTERS

### A. Voltage transfer characteristics of NCFET inverters

Fig. 7 shows the voltage transfer characteristic (VTC) of NCFET inverters. The VTC of NCFET inverters is extracted from cross points of n-type and p-type NCFET load curves at each  $V_{in}$ . Insets of Fig. 7 show the load lines of n-type and p-type NCFETs at  $V_{in}$  = 0.25 V. The  $T_{FE}$  values of n-type and p-type NCFETs without hystresis behavior are adjusted to have similar  $I_{ON}$ . As seen in this figure, however, unexpected hysteresis loops are observed. In common load lines of the conventional MOSFETs, there is a cross point for one input voltage, but in the case of NCFETs with NDR, two or three cross points are observed as shown in the insets. This induces the hysteresis behavior in VTC of NCFET inverters. hysteresis loop can be modified by adjusting  $T_{FE}$ . In the case of NCFET inverters with  $T_{FE} = 170$  (n-type) and 140 (ptype) nm as shown in Fig. 7, the hysteresis window  $(V_{hys})$ , low threshold  $(V_{low})$ , and high threshold  $(V_{high})$  are 0.0198, 0.243, and 0.262 V, respectively. As the  $T_{FE}$  values of NCFETs become thicker, the hysteresis loop becomes more apparent due to stronger NDR; for example, in the NCFET inverter with  $T_{FE}$  = 270 (n-type) and 280 (p-type) nm,  $V_{hys}$ ,  $V_{low}$ , and  $V_{high}$  become 0.0743, 0.272, and 0.332 V, respectively (See Fig. 7).

### B. Schmitt trigger inverter

The transient response of NCFET inverters is shown in Fig. 8. The transient response of NCFET inverters is the

same as that of the Schmitt trigger inverter described in [33] and [34]. The Schmitt trigger inverter, which consists of 4 to 6 MOSFETs, acts as a filter of noise and disturbance in an analog circuit, which exhibits hysteretic characteristics [33]-[35], while the NCFET Schmitt trigger inverters requires just two transistors. Further, since NCFETs outperform the conventional MOSFETs with regard to  $I_{ON}$  and SS, it is concluded that NCFET inverters are superior to conventional Schmitt trigger inverters. If one makes use of the hysteresis behavior of NCFETs as suggested in this work, it is expected that the application of NCFETs can be extended to functional circuits.

### V. Conclusion

In this paper, we assessed the performance of UTB short-channel NCFETs by combining quantum-mechanical transport calculations with LD theory. Since  $C_G$  increases with  $T_{FE}$ , both SS and DIBL decrease due to strong gate controllability. When SS becomes less than 60 mV/dec, unexpected behaviors, such as DIBR and NDR, emerge in NCFETs, whose origin was analyzed by investigating the potential profile and the dependence of  $Q_G$  on  $V_{DS}$  and  $V_{GS}$ .

We found that, even if both the n-type and p-type NCFETs are hysteresis-free, the inverter shows hysteresis behavior due to NDR. Together with the fact that NDR accompanies hysteresis behavior in the inverters, it is difficult for the inverter composed of steep SS devices to avoid the hysteresis behavior. However, NCFET inverters with hysteresis behavior can be used as a noise filter, such as the Schmitt trigger inverter, which suggests an expansion of the application area of NCFETs.

### ACKNOWLEDGMENT

This research was supported by the EDISON program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology under Grant NRF-2012M3C1A6035303.

### REFERENCES

- [1] V. V. Zhirnov and R. K. Cavin, "Nanoelectronics: negative capacitance to the rescue?" *Nat. Nanotechnol.*, vol. 3, no. 2, pp. 77-78, 2008.

- [2] K. Gopalakrishnan, P. B. Griffin, and J. D. Plummer, "I-MOS: a novel semiconductor device with a subthreshold slope lower than kT/q," in Proc. IEEE IEDM, pp. 289-292, 2002.

- [3] A. M. Ionescu and H. Riel, "Tunnel field-effect transistors as energy efficient electronic switches," *Nature*, vol. 479, no. 7373, pp. 329-337, 2011.

- [4] W. Y. Choi, B. G. Park, J. D. Lee, and T. J. K. Lui, "Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60mV dec," *IEEE Electron Dev. Lett.*, vol. 28, no. 8, pp. 743-745, 2007.

- [5] B. Rajamohanan, R. Pandey, V. Chobpattana, C. Vaz, D. Gundlach, K. P. Cheung, J. Suehle, S. Stemmer, and S. Datta "0.5 V supply voltage operation of In<sub>0.65</sub>Ga<sub>0.35</sub>As/GaAs<sub>0.4</sub>Sb<sub>0.6</sub> tunnel FET", *IEEE Electron Dev. Lett.*, vol. 36, no. 1, pp. 20-22, 2015.

- [6] G. Han, Y. Wang, Y. Liu, C. Zhang, Q. Feng, M. Liu, S. Zho, B. Cheng, J. Zhang, and Y. Hao, "GeSn quantum well p-channel tunneling FETs fabricated on Si (001) and (111) with improved subthreshold swing," *IEEE Electron Dev. Lett.*, vol. 37, no. 6, pp. 701-704, 2016.

- [7] S. Salahuddin and S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," *Nano Lett.*, vol. 8, no. 2, pp. 405-410, 2008.

- [8] J. Jo, W. Y. Choi, J.-D. Park, J. W. Shim, H.-Y. Yu, and C. Shin, "Negative capacitance in organic/ferroelectric capacitor to implement steep switching MOS devices," *Nano Lett.*, vol. 15, no. 7, pp. 4553-4556, 2015.

- [9] A. I Khan, Chatterjee, J. P. Duarte, J. P., Z. Lu, A. Sachid, S. Khandelwal, R. Ramanoorthy, H. Chenming, and S. Salahuddin, "Negative capacitance in short channel FinFETs Externally connected to an epitaxial ferroelectric capacitor," *IEEE Electron Dev. Lett.*, vol. 37, no. 1, pp. 111-114, 2015.

- [10] S. Dasgupta, A. Rajashekhar, K. Majumdar, N. Agrawal, A. Razavieh, S. Trolier-Mckinstry, and S. Datta, "Sub-kT/q switching in strong inversion in PbZr<sub>0.52</sub>Ti<sub>0.48</sub>O<sub>3</sub> gated negative capacitance FETs," *IEEE J. Exploratory Solid-State Comput. Devices Circuits*, vol. 1, pp. 43-48, 2015.

- [11] M. Kobayashi and T. Hiramoto, "Device design guideline for steep slope ferroelectric FET using negative capacitance in sub-0.2 V operation: operation speed, material requirement and energy efficiency," *In VLSI Symp. Tech.*, 2015, pp. 212-213.

- [12] C. I. Lin, A. I. Khan, S. Salahuddin, and C. Hu, "Effects of the variation of ferroelectric properties on negative capacitance FET characteristics," *IEEE Trans. on Electron devices*, vol. 63, no. 5, pp. 2197-2199, 2016.

- [13] J. Chunsheng, L. Renrong, W. Jing, and X. Jun, "Simulation-based study of negative capacitance double-gate junctionless transistors with ferroelectric gate dielectric", *Solid-State Electronics*, 2016.

- [14] A. D. Es-Sakhi and M. H. Chowdhury, "Partially depleted siliconon-ferroelectric insulator field effect transistor - parameterization and design optimization for minimum subthreshold swing", *Microelectronics Journal*, vol. 46, pp. 981-987, 2015.

- [15] M. Hema and K. Harsupreet, "Modeling and simulation study of novel double gate ferroelectric junctionless (DGFJL) transistor", *Superlattices and microstructures*, vol. 97, pp. 536-547, 2016.

- [16] G. Pahwa, T. Dutta, A. Agarwal, S. Khandelwal, S. Salahuddin, C. Hu, and Y. S. Chauhan, "Analysis and compact modeling of negative capacitance transistor with high on-current and negative output differential resistance Part II: Model validation," *IEEE Trans. on Electron Devices*, vol. 64, no. 12, pp. 4986-4992, Dec. 2016.

- [17] A. I. Khan, C. W. Yeung, C. Hu, and S. Salahuddin, "Ferroelectric negative capacitance MOSFET: capacitance tuning & antiferroelectric operation," in Proc. IEEE IEDM, pp. 255-258, 2011.

- [18] Y. Li, Y. Lian, K. Yao, and G. S. Samudra, "Evaluation and optimization of short channel ferroelectric MOSFET for low power circuit application with BSIM4 and Landau theory," *Solid-State Electronics*, vol.114, pp. 17-22, 2015

- [19] M. Shin, "Full-quantum simulation of hole transport and band-to-band tunneling in nanowires using the  $k \cdot p$  method," *J. Appl. Phys.*, vol. 106, no. 5, pp. 054505-1-054505-10, Sep. 2009.

- [20] W. Choi, J. Lee, and M. Shin, "P-type nanowire schottky barrier MOS-FETs comparative study of Ge and Si-channel devices," *IEEE Trans. on Electron devices*, vol. 61, no. 1, pp. 37-43, Jan. 2014.

- [21] J. Lee, and M. Shin, "The performance assessment of III-V channel ultra-thin-body Schottky-barrier (SB) MOSFETs," J. Appl. Phys., vol. 35, no. 7, pp. 726-728, 2015.

- [22] L. D. Landau and I. M. Khalatnikov. "On the anomalous absorption of sound near a second order phase transition point," *Dokl. Akad. Nauk* SSSR., vol. 96, pp 469-472, 1954.

- [23] V. C. Lo, "Simulation of thickness effect in thin ferroelectric films using Landau-Khalatnikov theory," *J. Appl. Phys.*, vol. 94, no. 5, pp. 3353-3359, Sep. 2003.

- [24] A. M. F. Neto and S. R. Salinas, "The physics of ferroelectrics-a modern perspective", Springer, 2007.

- [25] A. Jain and M. A. Alam, "Stability constraints define the minimum subthreshold swing of a negative capacitance field-effect transistor," *IEEE Trans. on Electron devices*, vol. 61, no. 7, pp. 2235-2242, 2014.

- [26] J. Hong and D. Fang, "Size-dependent ferroelectric behavior of BaTiO<sub>3</sub> nanowires," Appl. Phys. Lett., vol. 92, no. 1, pp. 012906-1-012906-3, Jan. 2008

- [27] G. Pilania, S. P. Alpay, and R. Ramprasad, "Ab initio study of ferroelectricity in BaTiO<sub>3</sub> nanowires," Phys. Rev. B, vol. 80, pp. 014113-1-014113-7, July 2009.

- [28] N. A. Pertsev, J. R. Contreras, V. G. Kukhar, B. Hermanns, H. Kohlstedt, and R. Waser, "Coercive field of ultrathin Pb(Zr<sub>0.52</sub>Ti<sub>0.48</sub>)O<sub>3</sub> epitaxial films," *Appl. Phys. Lett.*, vol. 83, no. 16, pp. 3356-3358, Aug. 2003.

- [29] S. M. Sze, "Physics of semiconductor devices," 3rd ed. New York, NY, USA: Wiley, 2007.

- [30] J. Zhou, G. Han, Q. Li, Y. Peng, X. Lu, C. Zhang, J. Zhang, Q. Sun, D. W. Zhang, and Y. Hao, "Ferroelectric HfZrO<sub>x</sub> Ge and GeSn PMOSFETs with sub-60 mV/decade subthreshold swing, negligible

- hysteresis, and improved  $I_{DS}$ ," in Proc. IEEE IEDM, pp. 12.2.1-12.2.4, 2016

- [31] K. Hess, H. Morkoc, H. Shichijo, and B. G. Streetman, "Negative differential resistance through realspace electron transfer," *Appl. Phys. Lett.*, vol. 35, no. 6, pp. 469-471, 1979.

- [32] K. S. Li, P. G. Chen, T. Y. Lai, C. H. Lin, C. C. Cheng, C. C. Chen, Y. J. Wei, Y. F. Hou, M. H. Liao, M. H. Lee, M. C. Chen, J. M. Sheih, W. K. Yeh, F. L. Yang, S. Salahuddin, and C. Hu, "Sub-60mV-swing negative-capacitance FinFET without hysteresis," in Proc. IEEE IEDM, pp. 22.6.1-22.6.4, 2015.

- [33] S. L. Chen and M. D. Ker, "A new Schmitt trigger circuit in a 0.13μm 1/2.5-V CMOS process to receive 3.3-V input signals," *IEEE Trans. Circuits Syst. II: Express Briefs*, vol. 52, no. 7, pp. 361-365, 2005

- [34] W. M. Kader, H. Rashid, M. Mamun, and M. A. S. Bhuiyan, "Advance-ment of CMOS Schmitt trigger circuits," *Modern Applied Science*, vol. 6, pp. 51-58, 2012.

- [35] V. Katyal, R. L. Geiger and D. J. Chen, "Adjustable hysteresis CMOS Schmitt triggers," *IEEE ISCAS*, pp. 1938-1941, 2008.

Junbeom Seo received the B.S. degree in the department of electronic material engineering from Kwangwoon university, Seoul, Korea, in 2014 and the M.S. degree in school of electrical engineering from Korea Advanced Institute of Science and Technology, Daejeon, Korea, in 2016. His research interests are the quantum transport in nanoscale electronic devices.

Jaehyun Lee received B.S., M.S., and Ph.D degrees in electrical engineering from Korea Advanced Institute of Science and Technology in 2006, 2008, and 2016, respectively. From 2008 to 2012, he was involved in low power DRAM development at SK Hynix. His research interest is in the area of computational nanoelectronics based on density functional theory.

Mincheol Shin received the B.S. degree in physics from Seoul National University, Seoul, Korea, in 1988 and the Ph.D. degree in physics from Northwestern University, Evanston, IL, in 1992. From 1993 to 2002, he was a Senior Researcher at Electronics and Telecommunications Research Institute, Korea. He is currently a Professor of Electrical Engineering at Korea Advanced Institute of Science and Technology. His expertise lies in modeling and simulations of nano-scale semiconductor devices, development of quantum-mechanical simulators, and

electron, phonon, and spin transport theory in nano-scale electronic devices.