G472

Analysis of Silicon Nanowires Grown by Combining SiO **Evaporation with the VLS Mechanism**

F. M. Kolb,<sup>a,z</sup> H. Hofmeister,<sup>a</sup> R. Scholz,<sup>a</sup> M. Zacharias,<sup>a</sup> U. Gösele,<sup>a,\*</sup> D. D. Ma,<sup>a,b</sup> and S.-T. Lee<sup>b</sup>

<sup>a</sup>Max Planck Institute of Microstructure Physics, Weinberg 2, 06110 Halle (Saale), Germany <sup>b</sup>Center of Super-Diamonds and Advanced Films and Department of Physics and Materials Science, The City University of Hong Kong, Hong Kong SAR, China

Silicon nanowires have received increasing attention as potential building blocks for nanoscale devices. We report the growth and analysis of silicon nanowires consisting of a crystalline silicon core and a thick oxide shell, which were grown by evaporation of silicon monoxide (SiO) in an inert gas atmosphere using a gold-coated silicon wafer as a substrate. This method combines SiO evaporation with the vapor-liquid-solid (VLS) nanowire growth mechanism. The resulting nanowires were analyzed using scanning electron microscopy, transmission electron microscopy (TEM), and energy-dispersive X-ray spectroscopy (EDXS). The thick oxide shell was determined to be the product of the SiO evaporation and subsequent phase separation into Si and SiO2. The EDXS measurements confirmed the silicon core/oxide shell structure of the nanowires and the existence of a gold dot on the nanowire tip as required by the VLS mechanism. An explanation is proposed for growth of the nanowires by combination of the VLS mechanism and SiO disproportionation. High-resolution TEM micrographs show the crystalline structure of the nanowire silicon core. Some of the nanowires were found to show an oscillation in diameter.

© 2004 The Electrochemical Society. [DOI: 10.1149/1.1759365] All rights reserved.

Manuscript submitted August 19, 2003; revised manuscript received December 18, 2003. Available electronically May 27, 2004.

During recent years, semiconductor nanowires have received increasing attention as potential building blocks for nanoscale electronic and optical devices. For the manufacturing of these nanowires, a variety of methods has been employed. These methods include chemical vapor deposition (CVD), e.g., using silane or silicon tetrachloride),<sup>1-3</sup> pulsed laser deposition (PLD),<sup>4</sup> chemical beam epitaxy (CBE),<sup>5</sup> metallorganic vapor phase epitaxy (MOVPE),<sup>6</sup> and thermal evaporation methods.<sup>7</sup> Frequently, they require complicated experimental setups or do not permit the desired degree of growth control with respect to the position and size of the wires. In this paper we present the analysis of silicon nanowires grown by combining the evaporation of silicon monoxide (SiO) with the vaporliquid-solid (VLS) growth mechanism.<sup>3</sup> This combination may have the possibility of a high level of growth control while being relatively easy to realize. The growth of silicon nanowires based on this combination was reported by Peng et al.8 and very recently by Zhang et al.9

Evaporation of silicon monoxide has been used before in the preparation of silicon nanoparticles<sup>10,11</sup> and nanowires.<sup>7,9</sup> At elevated temperatures the SiO vapor is stable, but the metastable solid SiO undergoes a disproportionation and subsequent phase separation, yielding silicon and silicon dioxide according to the following reaction

$$2SiO \rightarrow Si + SiO_2$$

thereby providing the silicon required for growth of the nanowires following the VLS mechanism.<sup>3</sup> The VLS mechanism also requires the existence of a (catalyst) metal particle (Au in our experiments) on the surface of the substrate on which the nanowires are grown, with the metal particle serving as a defined starting point for the growth of the nanowires. Small gold islands can easily be obtained on an oxide-free silicon wafer by evaporating or sputtering a thin layer of gold and heating the sample. Heating of the gold-coated silicon wafer leads to the formation of a Au-Si alloy, which becomes supersaturated with silicon due to the constant supply of silicon from the disproportionation of SiO. Silicon nanowires then grow from the supersaturated Au-Si alloy dots.

# Experimental

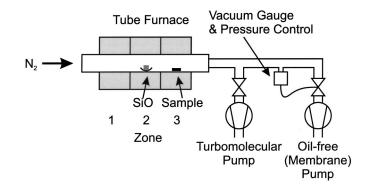

Two slightly different methods for the preparation of the substrates were used without any noticeable difference in the results. Some samples were grown on pieces of n-doped Si(111) wafers with a resisitivity of 8–20  $\Omega$  cm. Whole wafers were first cleaned using a standard RCA process. In a sputter coater (Denton Vacuum) a plasma etching step was used to remove the surface oxide before a thin film of gold (approximately 8 nm) was sputtered on the wafer. Some samples were grown on pieces of p-doped Si(111) wafers with a resistivity of 10–20  $\Omega$  cm. After removing the surface oxide with buffered HF solution (12.5%), the wafer was transferred into a vacuum chamber, where an about 5-7 nm thick layer of gold was thermally evaporated onto the wafer. A piece of the gold-coated wafer was then put on a quartz boat and introduced into a quartz tube inside a three-zone tube furnace (Fig. 1). A few grains of SiO granulate (99.99%, Chempur, Germany) were similarly put on a quartz boat located in the middle zone of the tube furnace.

The quartz tube inside the furnace was evacuated using a turbomolecular pump to a pressure below  $1 \times 10^{-5}$  mbar, and then a constant flow of 50 sccm nitrogen as an inert transport gas was introduced through mass flow controllers and pumped through the system using an oil-free vacuum pump. The nitrogen pressure inside the system was kept constant at 25 mbar with an electronically controlled valve located between the quartz tube and the membrane pump.

Figure 1. Schematic diagram of the experimental setup used for Si nanowire growth.

<sup>\*</sup> Electrochemical Society Active Member.

<sup>&</sup>lt;sup>z</sup> E-mail: fkolb@mpi-halle.mpg.de

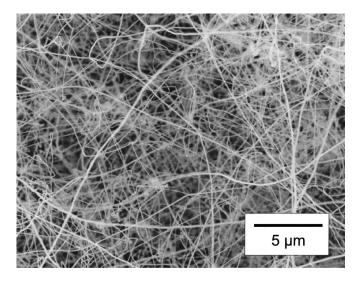

Figure 2. SEM micrograph of silicon nanowires grown using the goldcoated silicon wafer.

The SiO and the gold/silicon substrate were then heated from room temperature to about 1125 and 950°C, respectively, at a rate of about 10 K/min, although above *ca.* 900°C the heating rate fell considerably to <5 K/min because of technical restrictions of the tube furnace. After keeping the desired temperatures for 15 min, the furnace was allowed to cool at a rate of 10 K/min.

Scanning electron microscopy (SEM) micrographs of the samples after the growth procedure were taken using a JEOL JSM-6300F scanning electron microscope with an acceleration voltage of 5 kV. Transmission electron microscopy (TEM) samples were prepared by removing the nanowires mechanically and ultrasonically in propanol, then putting a few drops of the suspension on a carbon film TEM grid. TEM micrographs were taken with a JEOL JEM-1010 operating at 100 kV and a JEOL JEM-4010 operating at 400 kV. Energy-dispersive X-ray spectroscopy (EDXS) with a resolution of about 3 nm was done with a 200 kV Philips CM-20 system equipped with a field emission gun (FEG) and an IDFix EDXS system by SAMx (France). For the EDXS measurements the scanning TEM mode of the microscope was used. High-resolution TEM micrographs were obtained with the JEOL JEM-4010.

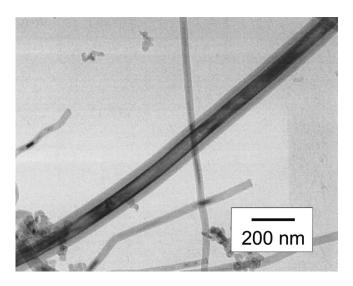

Figure 3. TEM micrograph of a thick silicon nanowire with its crystalline silicon core and the thick amorphous oxide shell.

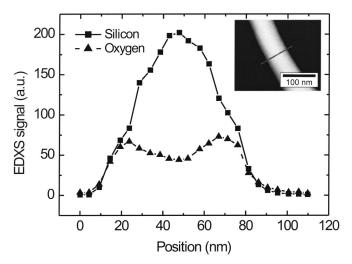

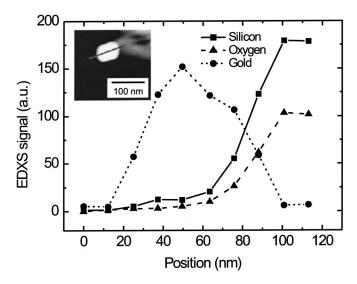

**Figure 4.** EDXS line scan across a nanowire. The graph confirms the existence of a silicon oxide shell and a silicon core. The inset shows a dark field scanning TEM (STEM) micrograph with the direction of the line scan. The lines were added to guide the eye.

#### **Results and Discussion**

After the nanowire growth process the gold-coated samples show a gray-light brown-yellow color. Uncoated silicon wafer pieces do not show any growth of nanowires. This might be due to the relatively short duration of the experiments, which was not long enough to grow nanowires without a metal catalyst according to the oxideassisted growth method. It can be concluded that the gold islands can define the preferred growth sites for the silicon nanowires and a control of the nanowire position can be possible.

SEM micrographs confirm a large yield of extremely long silicon nanowires (tens of micrometers), as can be seen in Fig. 2. The resulting nanowires have been examined in detail using TEM. Figure 3 shows that the nanowires consist of a crystalline silicon core covered by a thick amorphous oxide shell. The oxide shell is much thicker than what would be expected for a so-called native oxide layer (approximately 2 nm) caused by oxidation of the silicon in ambient air, *e.g.*, for silicon nanowires grown using silane or dichlorosilane CVD.<sup>12</sup>

**Figure 5.** EDXS line scan along a nanowire tip. The existence of a gold dot on the nanowire tip is confirmed. The inset shows an STEM micrograph with the direction of the line scan. The lines were added to guide the eye.

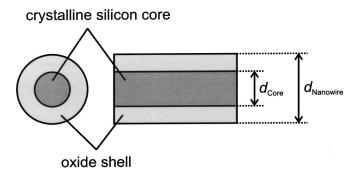

Figure 6. Schematic drawing of a nanowire cross section and longitudinal section.

The structure of the nanowire consisting of a silicon core and an oxide shell was confirmed by EDXS measurements. An EDXS line scan across a nanowire (Fig. 4) yields a higher oxygen amount for the shell regions compared to the core region, as well as a higher silicon amount for the core region (where some oxygen is detected due to the oxide shell directly above and below the silicon core).

EDXS measurements have also been used to confirm the existence of a gold dot on the nanowire tip. A line scan along the nanowire tip (Fig. 5) shows first an increase in the gold signal and then the beginning of the actual nanowire with a decrease in the gold signal and an increase in the silicon (and oxygen) signal. This result suggests that the nanowires indeed grow via the VLS mechanism.

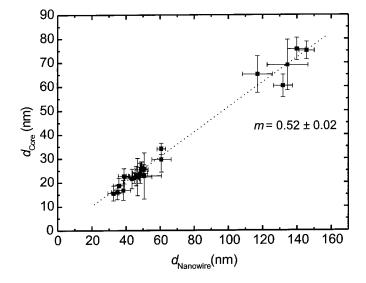

To confirm the growth of the nanowires from silicon monoxide evaporation and to explain the thick oxide shell, the diameters of the nanowires  $d_{\text{nanowire}}$  and the crystalline core  $d_{\text{core}}$  (Fig. 6) were measured from TEM micrographs. Figure 7 shows a linear dependence between these two diameters. For this diagram, only nanowires with a clearly visible crystalline core were considered. Therefore, Fig. 7 does not necessarily give an exact representation of the nanowire diameter distribution. Fitting a linear function to the data yields a ratio of

$$\frac{d_{\rm core}}{d_{\rm nanowire}} = (0.52 \pm 0.02)$$

**Figure 7.** Diameter of the crystalline nanowire core  $d_{\rm core}$  in relation to the total diameter of the nanowire  $d_{\rm nanowire}$  including the oxide shell. The linear relation with the proportionality factor of  $m = 0.52 \pm 0.02$  between these two values indicates that the growth of the silicon core and the oxide shell occur through the same process.

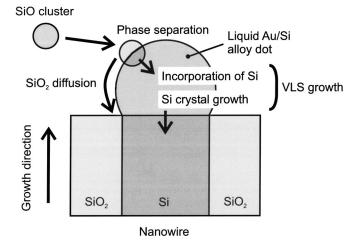

**Figure 8.** Schematic illustration of a possible growth mechanism. A silicon monoxide cluster sticks to the gold/silicon alloy dot. After the phase separation process the silicon is absorbed by the alloy dot, which causes the growth of the nanowire according to the VLS mechanism. The silicon oxide stays at the surface and builds up the oxide shell around the silicon core.

This result indicates that the crystalline silicon core and the silicon oxide shell grow through the same process, namely, the disproportionation of silicon monoxide which yields the same number of moles for both silicon and silicon dioxide. Therefore, the silicon and the silicon dioxide are expected to appear in the nanowires at a constant ratio. Even if a certain percentage of the oxygen would be lost into the gas phase, there would still be a constant ratio, although of a different value.

With this value the ratio of the volumes of the silicon core  $V_{\rm core}$  and oxide shell  $V_{\rm shell}$  can be calculated

$$\frac{V_{\text{shell}}}{V_{\text{core}}} = \left(\frac{d_{\text{nanowire}}}{d_{\text{core}}}\right)^2 - 1$$

which is also constant.

If we suppose that the shell consists of amorphous SiO<sub>2</sub>,<sup>c</sup> it is also possible to estimate the density  $\rho_{SiO_2}$  of the SiO<sub>2</sub>, taking the density of silicon  $\rho_{Si}$  to be 2.328 g/cm<sup>3</sup>

$$\rho_{\rm SiO_2} = \frac{m_{\rm SiO_2}}{m_{\rm Si}} \rho_{\rm Si} \frac{d_{\rm core}^2}{d_{\rm nanowire}^2 - d_{\rm core}^2}$$

with  $m_{\rm SiO_2}$  and  $m_{\rm Si}$  being the specific masses of SiO<sub>2</sub> and Si, respectively. The result of the calculation gives a density of (1.85  $\pm$  0.20) g/cm<sup>3</sup> for the SiO<sub>2</sub> shell. This is slightly lower than the density of thermal silicon dioxide films, which ranges from 2.15 to 2.25 g/cm<sup>3</sup>.<sup>14</sup> However, the result corresponds well to the density of 1.97 g/cm<sup>3</sup> for "fibrous SiO<sub>2</sub>," a modification resulting from SiO oxidation, although this modification is expected to react with the humidity in ambient air to form other silicon compounds.<sup>15</sup> Altogether, it can be concluded from these results that the nanowires indeed grow according to the SiO disproportionation process.

To explain the growth of the silicon nanowires from a combination of SiO disproportionation and the VLS mechanism we suggest the following growth mechanism (Fig. 8). Inert gas evaporation of silicon monoxide produces nanosized SiO clusters,<sup>10</sup> which stick to the gold/silicon alloy dots on the substrate surface. The temperature of the substrate is high enough to allow the phase separation process

$<sup>^{\</sup>rm c}$  Preliminary results from electron energy-loss spectrometry (EELS) and electron energy-loss near-edge structure (ELNES) seem to support the fact that the shell indeed consists of a low-density SiO\_2 modification.  $^{\rm 13}$

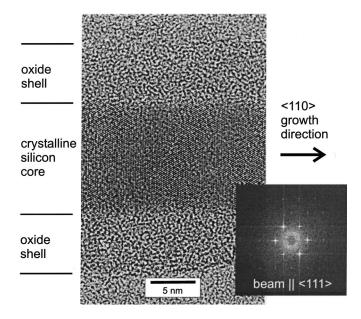

Figure 9. HRTEM micrograph of a thin silicon nanowire on a carbon film. The inset shows an FFT of the crystal lattice, indicating transmission parallel Si  $\langle 111 \rangle$ . From the FFT image the nanowire growth direction of  $\langle 110 \rangle$  can be recognized.

into silicon and silicon oxide to take place. In a continous process, the silicon is absorbed into the alloy dot, whereas the oxide stays at the surface of the dot. The silicon core of the nanowire then grows from the alloy dot according to the VLS mechanism, whereas the silicon oxide does not cover the surface of the gold dot completely but is deposited as a shell around the silicon core.

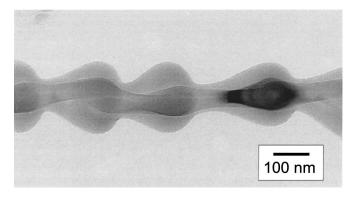

High-resolution TEM (HRTEM) micrographs were taken to confirm the crystalline nature of the silicon core and to determine the growth direction. Figure 9 shows the HRTEM micrograph of a nanowire with a silicon core thickness of about 13 nm. The fast Fourier transformation (FFT) of the crystalline core yields an electron-beam direction parallel to a silicon  $\langle 111 \rangle$  direction and a growth direction of  $\langle 110 \rangle$ , although there are indications from our TEM investigations that other growth directions may also exist. This question of growth directions (see, e.g., Ref. 16) is currently under investigation. The  $\langle 110 \rangle$  growth direction is different from the  $\langle 111 \rangle$ growth direction generally reported for metal-catalytic VLS-grown silicon nanowires, although other growth directions than (111) have been found for nanowires grown by the oxide-assisted method,<sup>8</sup> including the (110) growth direction.<sup>9</sup> Some nanowires show an oscillation in diameter (Fig. 10), a phenomenon that has been explained by a self-oscillation process during the VLS growth of the nanowires.<sup>17,18</sup> Silicon nanowires with similar oscillations have also been observed for nanowires grown with the oxide-assisted method.8,19

### Conclusion

In summary, we report the successful growth of a large yield of crystalline silicon nanowires surrounded by an amorphous oxide shell using the evaporation and disproportionation of silicon monoxide combined with the VLS growth mechanism. Gold dots on a silicon substrate serve as starting points for the nanowire growth; it might therefore be possible in the future to obtain a positioncontrolled growth of the nanowires by intentionally arranging the

Figure 10. TEM micrograph of a nanowire with an oscillating diameter.

gold dots on the substrate surface. To achieve this goal, the growth mechanism and the conditions for epitaxial growth with respect to the wafer substrate need to be investigated further. We found that some of the nanowires possess an oscillation in diameter. Growth of the nanowires from SiO evaporation and disproportionation was confirmed. The existence of a gold dot at the nanowire tip was confirmed by EDXS, which suggests growth of the nanowires through the VLS mechanism. HRTEM micrographs show a crystalline silicon core of the nanowires. We observed a  $\langle 110 \rangle$  growth direction for several analyzed nanowires, but other growth directions also seem to exist. This also shows the need for further clarification of the SiO-VLS growth process.

## Acknowledgments

We thank H. Stenzel for help with TEM-EDXS measurements. S. T. Lee thanks the Humboldt Foundation for a Senior Research Award which made his stay at the MPI Halle possible. He also appreciates the support of the Research Grants Council of Hong Kong SAR (grant no. CityU 3/01).

The Max Planck Institute of Microstructure Physics assisted in meeting the publication costs of this article.

#### References

- 1. G. A. Bootsma and H. J. Gassen, J. Cryst. Growth, 10, 223 (1971).

- J. Westwater, D. P. Gosain, S. Tomiya, S. Usui, and H. Ruda, J. Vac. Sci. Technol. 2. B, 15, 554 (1997)

- R. S. Wagner and W. C. Ellis, Appl. Phys. Lett., 4, 89 (1964).

- A. M. Morales and C. M. Lieber, *Science*, 279, 208 (1998).

B. J. Ohlsson, M. T. Björk, M. H. Magnusson, K. Deppert, L. Samuelson, and L. R. 5. Wallenberg, Appl. Phys. Lett., 79, 3335 (2001).

- K. Hiruma, M. Yazawa, K. Haraguchi, K. Ogawa, T. Katsuyama, M. Koguchi, and Kakibayashi, J. Appl. Phys., 74, 3162 (1993).

S. T. Lee, N. Wang, Y. F. Zhang, and Y. H. Tang, MRS Bull., 24, 36 (1999).

- H. Y. Peng, Z. W. Pan, L. Xu, X. H. Fan, N. Wang, C. S. Lee, and S. T. Lee, Adv. 8.

- Mater. (Weinheim, Ger.), 13, 317 (2001). 9. R. Q. Zhang, Y. Lifshitz, and S. T. Lee, Adv. Mater. (Weinheim, Ger.), 15, 635 (2003).

- 10. H. Hofmeister, P. Ködderitzsch, and J. Dutta, J. Non-Cryst. Solids, 232-234, 182 (1998).

- 11. M. Zacharias, J. Heitmann, R. Scholz, U. Kahler, M. Schmidt, and J. Bläsing, Appl. Phys. Lett., 80, 661 (2002).

- 12. T. I. Kamins, R. Stanley Williams, T. Hesjedal, and J. S. Harris, Physica E (Amsterdam), 13, 995 (2002). 13. E. Pippel, Private communication.

- 14. S. K. Gandhi, in VLSI Fabrication Principles, 2nd ed., p. 453, John Wiley & Sons, New York (1994).

- 15. Al. Weiss and Ar. Weiss, Naturwissenschaften, 41, 12 (1954).

- 16. T. Y. Tan, S. T. Lee, and U. Gösele, Appl. Phys. A: Mater. Sci. Process., 74, 423 (2002).

- 17. E. I. Givargizov, J. Cryst. Growth, 20, 217 (1973).

- 18. H. Kohno and S. Takeda, J. Cryst. Growth, 216, 185 (2000).

- 19. H. Y. Peng, N. Wang, W. S. Shi, Y. F. Zhang, C. S. Lee, and S. T. Lee, J. Appl. Phys., 89, 727 (2001).