KTH Industrial Engineering and Management

# Analysis of task scheduling for multi-core embedded systems

Analys av schemaläggning för multikärniga inbyggda system

# JOSÉ LUIS GONZÁLEZ-CONDE PÉREZ, MASTER THESIS

Examiner: Martin Törngren, KTH Supervisor: De-Jiu Chen, KTH Detlef Scholle, XDIN AB Barbro Claesson, XDIN AB

MMK 2013:49 MDA 462

# Acknowledgements

I would like to thank my supervisors Detlef Scholle and Barbro Claesson for giving me the opportunity of doing the Master thesis at XDIN. I appreciate the kindness of Barbro chatting with me in Spanish and the support of Detlef no matter how much time it was required. I want to thank Sebastian, David and the other people at XDIN for the nice environment I lived in during these 20 weeks. I would like to thank the support and guidance of my supervisor at KTH DJ Chen and the help of my examiner Martin Törngren in the last stage of the thesis.

I want to thank very much the other thesis colleagues at XDIN Joanna, Cheuk, Amir, Robin and Tobias. You have done this experience a lot more enriching. I would like to say merci! to my friends from Tyresö Benoit, Perrine, Simon, Audrey, Pierre, Marie-Line, Roberto, Alberto, Iván, Vincent, Olivier, Achour, Maxime, Simon, Emilie, Adelie, Siim and all the others. I have had great memories with you during the first year at KTH. I thank Osman and Tarek for this year in Midsommarkransen.

I thank all the professors and staff from the Mechatronics department Mike, Bengt, Chen, Kalle, Jad and the others for making this programme possible, especially Martin Edin Grimheden for his commitment with the students. I want to thank my friends from Mechatronics Eidur, René, Erik, Joanna, Marcus, Andreas, Mazda, Henrik, Oskar, Daniel and all the others. I would also like to thank other friends at KTH Lars, Hari, Maria, Sofia, Carl-Johan, Magnus, Ali and my tandem Daniel.

I want to thank my friends from Spain Héctor, Javi, Dani, Rubén, Raúl, Silvia, Jesús, Emilio, Carolina, Marga, Belén, Juanjo, David, Luis and all the others because you are a big part of my life.

Finally, I would like to thank the support of my parents Joselé and Maite and my grandparents Domingo and Carmen because it makes me stronger in the difficult times. The love of my sisters Raquel and Cristina reminds me how lucky I am. I want to thank all my family because you have always given me the best.

# Abstract

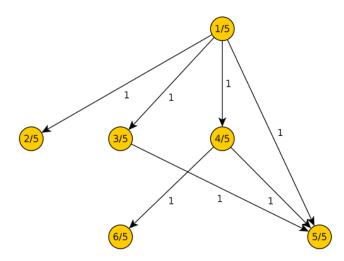

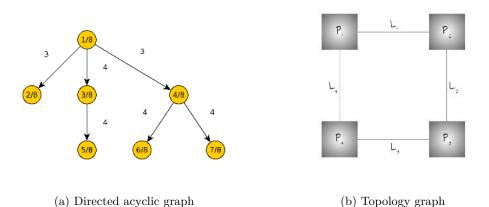

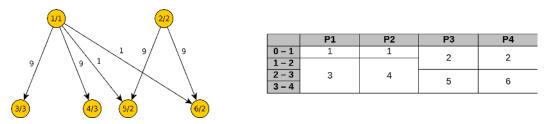

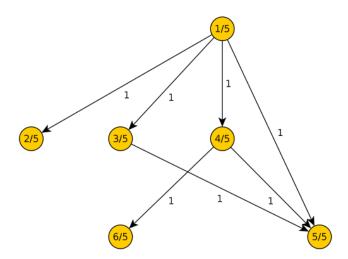

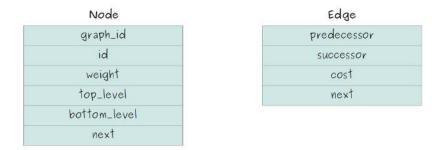

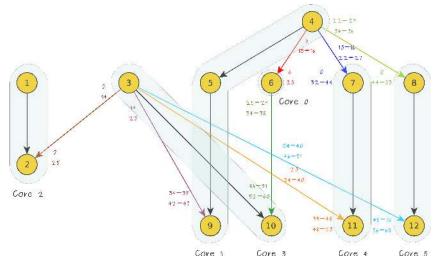

This thesis performs a research on scheduling algorithms for parallel applications. The main focus is their usage on multi-core embedded systems' applications. A parallel application can be described by a directed acyclic graph. A directed acyclic graph is a mathematical model that represents the parallel application as a set of nodes or tasks and a set of edges or communication messages between nodes.

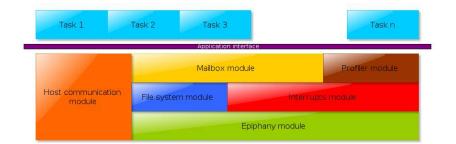

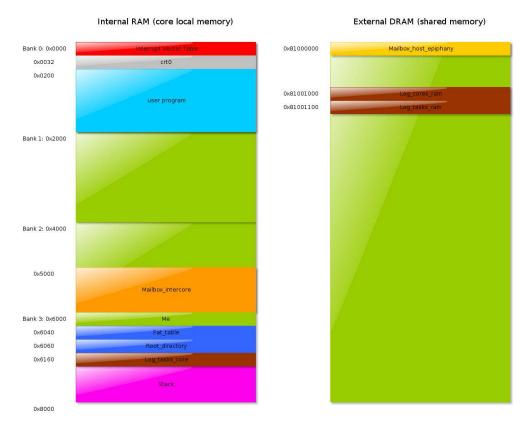

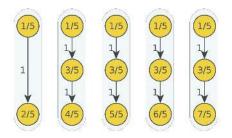

In this thesis scheduling is limited to the management of multiple cores on a multi-core platform for the execution of application tasks. Tasks are mapped onto the cores and their start times are determined afterwards. A toolchain is implemented to develop and schedule parallel applications on a Epiphany E16 developing board, which is a low-cost board with a 16 core chip called Epiphany. The toolchain is limited to the usage of offline scheduling algorithms which compute a schedule before running the application.

The programmer has to draw a directed acyclic graph with the main attributes of the application. The toolchain then generates the code for the target which automatically handles the inter-task communication. Some metrics are established to help evaluate the performance of applications on the target platform, such as the execution time and the energy consumption. Measurements on the Epiphany E16 developing board are performed to estimate the energy consumption of the multi-core chip as a function of the number of idle cores.

A set of 12 directed acyclic graphs are used to verify that the toolchain works correctly. They cover different aspects: join nodes, fork nodes, more than one entry node, more than one exit node, different tasks weights and different communication costs.

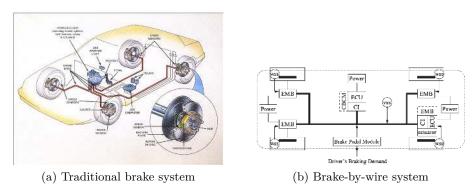

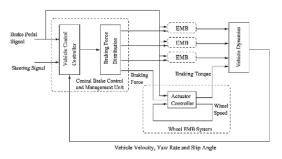

A use case is given, the development of a brake-by-wire demonstration platform. The platform aims to use the Epiphany board. Three experiments are performed to analyze the performance of parallel computing for the use case. Three brake-by-wire applications are implemented, one for a single core system and two for a multi-core system. The parallel application scheduled with a list-based algorithm requires 266% more time and 1346% more energy than the serial application. The parallel application scheduled with a task duplication algorithm requires 46% less time and 134% more energy than the serial application.

The toolchain system has proven to be a useful tool for developing parallel applications since it automatically handles the inter-task communication. However, future work can be done to automatize the decomposition of serial applications from the source code. The conclusion is that this communication system is suitable for coarse granularity, where the communication overhead does not affect so much. Task duplication is better to use for fine granularity since inter-core communication is avoided by doing extra computations.

# Sammanfattning

Detta examensarbete utför en studie av om schemaläggningsalgoritmer för parallella applikationer. Huvudfokus är deras användning för flerkärniga inbyggda systemapplikationer. En parallell applikation kan beskrivas genom en riktad acyklisk graf. En riktad acyklisk graf är en matematisk modell som representerar den parallella applikationen som en uppsättning av noder, eller uppgifter, och en uppsättning av pilar, eller meddelanden, mellan noder.

I denna uppsats är schemaläggning begränsad till hanteringen av flera kärnor på en multikärnig plattform för genomförandet av applikationens uppgifter. Uppgifter mappas på kärnorna och deras starttider bestäms efteråt. En speciell verktygskedja kallad ett "toolchain system" har tagits fram för att utveckla och schemalägga parallella applikationer på ett Epiphany E16 kort, vilket är ett billigt kort med ett 16-kärnigt chip som kallas Epiphany. Toolchain systemet är begränsat till användningen av offline schemaläggningsalgoritmer som beräknar ett schema innan du kör programmet.

Programmeraren måste rita en riktad acyklisk graf med de viktigaste attributen. Toolchain systemet genererar därefter kod som automatiskt hanterar kommunikationen mellan uppgifterna. Ett antal prestandamått defineras för att kunna utvärdera applikationer på målplattformen, såsom genomförandetid och energiförbrukning. Mätningar på Epiphany E16 kortet genomförs för att uppskatta energiförbrukningen som en funktion av antalet lediga kärnor.

En uppsättning av 12 riktade acykliska grafer används för att kontrollera att toolchain systemet fungerar korrekt. De täcker olika aspekter: noder som går ihop, noder som går isär, fler än en ingångsnod, fler än en utgångsnod, olika vikter på uppgifterna och olika kommunikationskostnader.

Ett användningsfall ges, utveckling av en brake-by-wire demonstrations plattform. Plattformen syftar till att använda Epiphany kortet. Tre experiment utförs för att analysera resultatet av parallella beräkningar för användningsfallet. Tre brake-by-wire applikationer genomförs, en för ett enda kärnsystem och två för ett multikärnigt system. Den parallella applikationen som var schemalagd med en algoritm baserad på listor kräver 266% mer tid och 1346% mer energi än den seriella applikationen. Den parallella applikationen som var schemalagd med en uppgiftsduplicerings-algoritm kräver 46% mindre tid och 134% mer energi än den seriella applikationen.

Toolchain systemet har visat sig att vara ett användbart verktyg för att utveckla parallella applikationer eftersom det automatiskt hanterar kommunikation mellan uppgifter. Däremot kan framtida arbete göras för att automatisera nedbrytningen av seriella program från källkod. Slutsatsen är att detta kommunikationssystem är lämpligt för grovkorning parallellism, där kommunikationskostnaden inte påverkar lika mycket. Uppgiftsdupliceringen är bättre att använda för finkorning parallellism eftersom kommunikation mellan kärnor undviks genom att göra extra beräkningar.

# Contents

Contents

List of Figures

List of Tables

List of Abbreviations

| Ι        | Ana                                                       | alytical phase                                                                                                                                                                      | 1                                                  |

|----------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1        | Intr                                                      | oduction                                                                                                                                                                            | 3                                                  |

|          | 1.1                                                       | Background                                                                                                                                                                          | 3                                                  |

|          | 1.2                                                       | Problem statement                                                                                                                                                                   | 4                                                  |

|          | 1.3                                                       | System requirements                                                                                                                                                                 | 5                                                  |

|          | 1.4                                                       | Team goal                                                                                                                                                                           | 5                                                  |

|          | 1.5                                                       | Method                                                                                                                                                                              | 6                                                  |

|          |                                                           | 1.5.1 Analytical phase                                                                                                                                                              | 6                                                  |

|          |                                                           | 1.5.2 Practical phase                                                                                                                                                               | 6                                                  |

|          | 1.6                                                       | Delimitation                                                                                                                                                                        | 6                                                  |

| <b>2</b> | τī                                                        | ····· description of a sector sector                                                                                                                                                | ~                                                  |

| 4        | Use                                                       | case description and requirements                                                                                                                                                   | 9                                                  |

| 4        | Use<br>2.1                                                |                                                                                                                                                                                     | <b>9</b><br>10                                     |

| 4        |                                                           | Case description and requirements         Introduction to brake-by-wire         Use case description                                                                                | Ŭ                                                  |

| 2        | 2.1                                                       | Introduction to brake-by-wire                                                                                                                                                       | 10                                                 |

| 4        | 2.1                                                       | Introduction to brake-by-wire                                                                                                                                                       | 10<br>11                                           |

| 2        | 2.1                                                       | Introduction to brake-by-wire                                                                                                                                                       | 10<br>11<br>11                                     |

| 2        | 2.1<br>2.2                                                | Introduction to brake-by-wire                                                                                                                                                       | 10<br>11<br>11<br>12                               |

| 2        | 2.1<br>2.2                                                | Introduction to brake-by-wire                                                                                                                                                       | 10<br>11<br>11<br>12<br>12                         |

| 2        | 2.1<br>2.2                                                | Introduction to brake-by-wire                                                                                                                                                       | 10<br>11<br>11<br>12<br>12<br>12                   |

| 2        | 2.1<br>2.2                                                | Introduction to brake-by-wire                                                                                                                                                       | 10<br>11<br>11<br>12<br>12<br>12<br>12<br>12       |

| 3        | <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li></ul> | Introduction to brake-by-wireUse case description2.2.1Control view2.2.2Physical viewUse case requirements2.3.1Real-time guarantees2.3.2Fault-tolerance2.3.3Energy efficiencySummary | 10<br>11<br>11<br>12<br>12<br>12<br>12<br>12<br>13 |

### CONTENTS

|   |                                                          | 3.1.1                                                                                                                                                        | Parallel system                                                               | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.2                                                      | Task r                                                                                                                                                       | nodels                                                                        | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                          | 3.2.1                                                                                                                                                        | Task model for independent tasks                                              | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

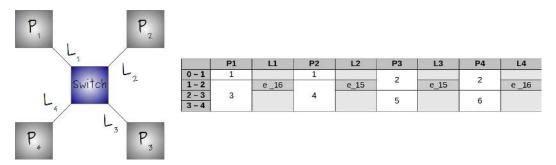

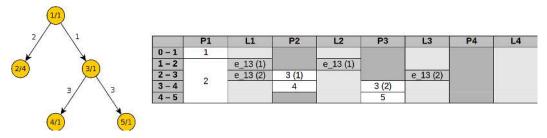

|   |                                                          | 3.2.2                                                                                                                                                        | Task model for interdependent tasks with communication costs                  | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 3.3                                                      | Exam                                                                                                                                                         | ples of parallel applications                                                 | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

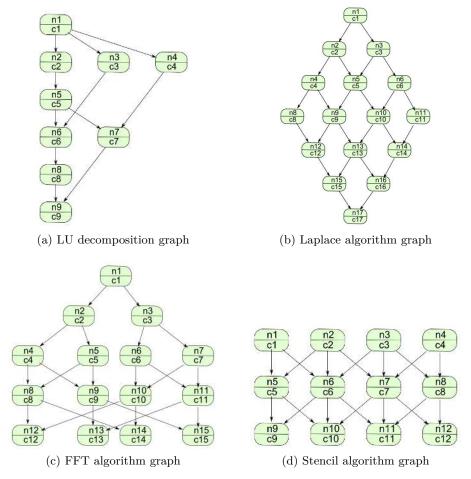

|   |                                                          | 3.3.1                                                                                                                                                        | LU decomposition graph                                                        | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                          | 3.3.2                                                                                                                                                        | Laplace algorithm graph                                                       | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                          | 3.3.3                                                                                                                                                        | FFT algorithm graph                                                           | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                          | 3.3.4                                                                                                                                                        | Stencil algorithm graph                                                       | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 3.4                                                      | Applic                                                                                                                                                       | ation decomposition and dependency analysis                                   | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 3.5                                                      | Task s                                                                                                                                                       | cheduling                                                                     | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                          | 3.5.1                                                                                                                                                        | Task mapping onto processing elements                                         | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                          | 3.5.2                                                                                                                                                        | Task temporal arrangement                                                     | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                          | 3.5.3                                                                                                                                                        | Scheduling metrics                                                            | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                          | 3.5.4                                                                                                                                                        | Optimality, feasibility and schedulability                                    | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 3.6                                                      | Relate                                                                                                                                                       | d technology                                                                  | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

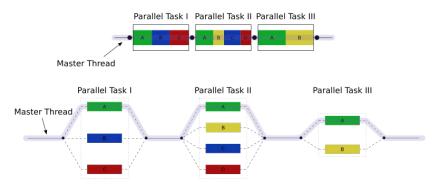

|   |                                                          | 3.6.1                                                                                                                                                        | OpenMP                                                                        | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                          | 3.6.2                                                                                                                                                        | MPI                                                                           | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

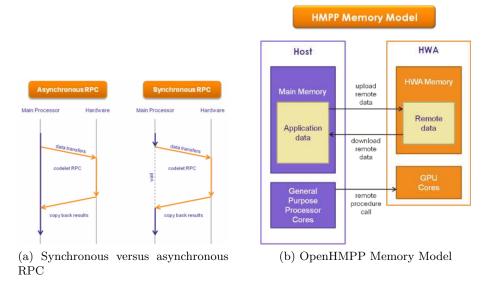

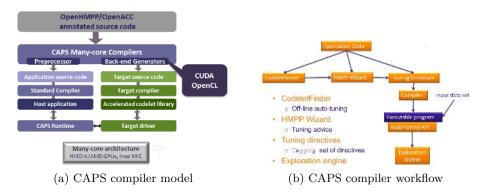

|   |                                                          | 3.6.3                                                                                                                                                        | OpenHMPP                                                                      | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                          | 3.6.4                                                                                                                                                        | OpenACC                                                                       | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

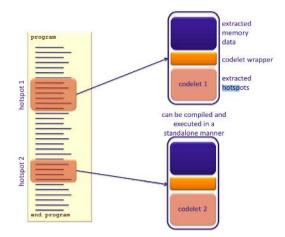

|   |                                                          | 3.6.5                                                                                                                                                        | CAPS compilers and CodeletFinder                                              | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 3.7                                                      | Summ                                                                                                                                                         | ary                                                                           | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 0.1                                                      | Samin                                                                                                                                                        | ary                                                                           | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4 |                                                          |                                                                                                                                                              | •                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4 |                                                          | edulin                                                                                                                                                       | g for interdependent tasks with communication costs                           | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4 | $\mathbf{Sch}$                                           | e <b>dulin</b> g<br>List-ba                                                                                                                                  | g for interdependent tasks with communication costs ased algorithms           | <b>29</b><br>30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4 | $\mathbf{Sch}$                                           | edulin                                                                                                                                                       | <b>g for interdependent tasks with communication costs</b><br>ased algorithms | <b>29</b><br>30<br>30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4 | $\mathbf{Sch}$                                           | e <b>dulin</b> g<br>List-ba<br>4.1.1                                                                                                                         | <b>g for interdependent tasks with communication costs</b><br>ased algorithms | <b>29</b><br>30<br>30<br>30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4 | $\mathbf{Sch}$                                           | eduling<br>List-ba<br>4.1.1<br>4.1.2<br>4.1.3                                                                                                                | g for interdependent tasks with communication costs<br>ased algorithms        | <b>29</b><br>30<br>30<br>30<br>31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4 | $\mathbf{Sch}$                                           | eduling<br>List-ba<br>4.1.1<br>4.1.2                                                                                                                         | g for interdependent tasks with communication costs<br>ased algorithms        | <b>29</b><br>30<br>30<br>30<br>31<br>31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4 | $\mathbf{Sch}$                                           | eduling<br>List-ba<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                                                                                       | g for interdependent tasks with communication costs<br>ased algorithms        | <b>29</b><br>30<br>30<br>30<br>31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4 | $\mathbf{Sch}$                                           | eduling<br>List-ba<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5                                                                                              | g for interdependent tasks with communication costs<br>ased algorithms        | <ol> <li>29</li> <li>30</li> <li>30</li> <li>31</li> <li>31</li> <li>31</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

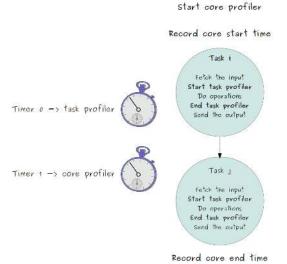

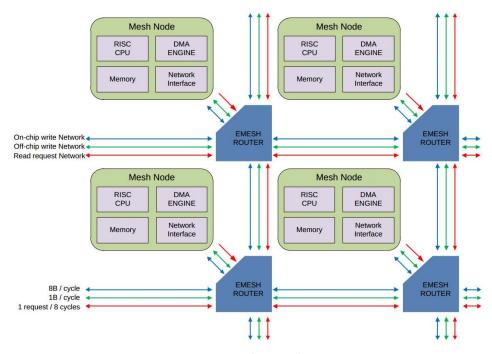

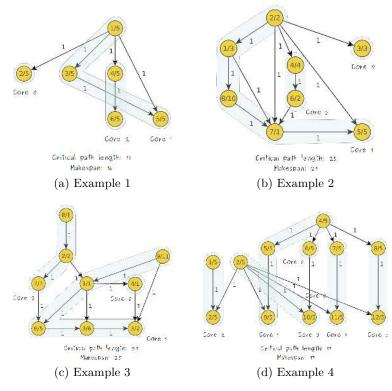

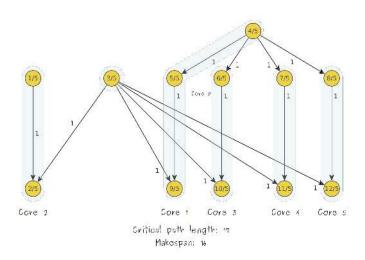

| 4 | $\mathbf{Sch}$                                           | eduling<br>List-ba<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6                                                                            | g for interdependent tasks with communication costs<br>ased algorithms        | <ul> <li>29</li> <li>30</li> <li>30</li> <li>31</li> <li>31</li> <li>31</li> <li>31</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |