# Analytic Description of Short-Channel Effects in Fully-Depleted Double-Gate and Cylindrical, Surrounding-Gate MOSFETs

Sang-Hyun Oh, Student Member, IEEE, Don Monroe, Member, IEEE, and J. M. Hergenrother, Member, IEEE

Abstract—Short-channel effects in fully-depleted double-gate (DG) and cylindrical, surrounding-gate (Cyl) MOSFETs are governed by the electrostatic potential as confined by the gates, and thus by the device dimensions. The simple but powerful evanescent-mode analysis shows that the length  $\lambda$ , over which the source and drain perturb the channel potential, is  $1/\pi$  of the effective device thickness in the double-gate case, and 1/4.810 of the effective diameter in the cylindrical case, in excellent agreement with PADRE device simulations. Thus for equivalent silicon and gate oxide thicknesses, evanescent-mode analysis indicates that Cyl-MOSFETs can be scaled to 35% shorter channel lengths than DG-MOSFETs.

Index Terms—Double-gate MOSFET, MOSFET scaling, shortchannel effect, surrounding-gate MOSFET.

#### I. INTRODUCTION

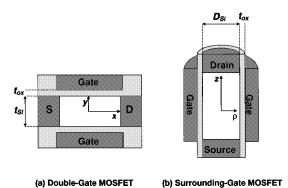

'N CONVENTIONAL bulk MOSFETs, immunity from  $\blacksquare$  short-channel effects such as  $V_T$ -rolloff and DIBL requires increasing doping to reduce the depletion depth in the substrate. Even when retrograde channel profiles are used to reduce mobility degradation and threshold mismatch, this approach intrinsically trades the improved short-channel immunity for increased substrate-bias sensitivity and degraded long-channel subthreshold swing. However, by replacing the substrate with another gate to form a fully-depleted, double-gate (DG) MOSFET [Fig. 1(a)], short-channel immunity can be achieved with ideal subthreshold swing. When the gate completely surrounds a channel as in the cylindrical, surrounding-gate (Cyl) MOSFET [Fig. 1(b)], the electrostatic control is even better. If the channel doping is uniform, it can be neglected in the short-channel analysis. If we ignore quantum effects that become important for extremely thin (<10 nm) channels, then fully-depleted DG and Cyl devices represent an ideal situation for simple electrostatic analysis. In previous analyses [1], [2], the electrostatic potential  $\psi$  in the channel is unjustifiably assumed to be a parabolic function of the transverse position (defined as y for DG and as  $\rho$  for Cyl). Then, although the free carriers are irrelevant to the electrostatics, the Laplace equation  $(d^2\psi/dx^2 + d^2\psi/dy^2) = 0$  for DG) is solved along the path of the dominant subthreshold current (i.e., at the Si/SiO<sub>2</sub> interface in [1] and at the center of the channel in [2]). The resulting potential decays exponentially along the

The authors are with Bell Laboratories, Lucent Technologies, Murray Hill, NJ 07974 USA (e-mail: osang@physics.bell-labs.com).

Publisher Item Identifier S 0741-3106(00)07229-3.

channel,  $\psi(x, y) \propto \exp(\pm x/\lambda)$ , where the characteristic length  $\lambda$  depends on the transverse curvature of the potential at the chosen position. Shorter transverse dimensions (i.e., smaller  $t_{\rm Si}$  and  $t_{ox}$ ) lead to shorter values of  $\lambda$ , resulting in better short-channel characteristics. The minimum acceptable channel length  $L_{\rm min}$  is between  $3\lambda$  and  $7\lambda$ , depending on the magnitude of short-channel effects that can be tolerated and on details of the device doping geometry.

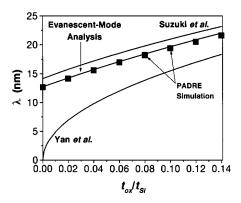

Unfortunately, when the solution is determined at the Si/SiO<sub>2</sub> interface as in [1], the transverse curvature  $[(d^2\psi/dy^2)/\psi]$  in the parabolic approximation differs significantly from that of the correct sinusoidal solution, resulting in a severe underestimation of  $\lambda$  for thin gate oxides. In the DG-MOSFET, Yan *et al.* [1] give  $\lambda_1 = \sqrt{(\kappa/2)t_{\rm Si}t_{ox}}$ , where  $\kappa = \varepsilon_{\rm Si}/\varepsilon_{ox} \approx 3$ . Suzuki *et al.* [2] who use the same technique but solve Laplace's equation along the center of the DG channel, give  $\lambda_2 = \sqrt{(\kappa/2)t_{\rm Si}t_{ox}(1 + t_{\rm Si}/4\kappa t_{ox})}$ .  $\lambda_1$  and  $\lambda_2$  differ significantly when  $t_{ox} < t_{\rm Si}/4\kappa$ .  $\lambda_2$  obtained by Suzuki *et al.* agrees reasonably well with device simulations; however, this agreement is fortuitous because it is only at the channel center that the transverse curvature obtained from the parabolic approximation provides a reasonable estimate of the actual curvature.

# II. EVANESCENT-MODE ANALYSIS AND THE DOUBLE-GATE MOSFET

Evanescent-mode analysis [3]–[6] is a powerful, new method for understanding short-channel effects. It properly deals with the two-dimensional (2-D) nature of the electrostatics and provides qualitatively different scaling predictions than analyses based on the parabolic approximation. Here, we apply it first to the DG-MOSFET. The channel potential is divided into two different pieces,  $\psi(x, y) = \psi_L(y) + \psi^*(x, y)$ . The long-channel solution  $\psi_L$  satisfies the Poisson equation as well as the appropriate gate-bias boundary conditions. Since the doping term in the Poisson equation is taken care of in  $\psi_L$ , the short-channel potential  $\psi^*$  satisfies the Laplace equation.  $\psi^*$  is zero at the Si/SiO<sub>2</sub> interfaces and it must also accommodate the source and drain bias conditions and workfunction differences. In the symmetric DG-MOSFET,  $\psi^*$  can be represented as a Fourier expansion of modes, each with its own characteristic decay length, as follows:

$$\psi^*(x, y) = \sum_{n=1}^{\infty} A_n \cos(ny/\lambda)$$

$$\cdot [B_{n+} \exp(nx/\lambda) + B_{n-} \exp(-nx/\lambda)]. (1)$$

Manuscript received September 29, 1999; revised May 23, 2000. The review of this letter was arranged by Editor E. Sangiorgi.

Fig. 1. Cross sections of device structures and coordinates. Double-gate (DG) and cylindrical, surrounding-gate (Cyl) structures are shown. Uniform channel doping and metal-like source/drain regions are used in all simulations.

Woo *et al.* [5] applied this series expansion to fully-depleted SOI devices. Rather than using this long series expansion from which it is difficult to gain critical physical insight, we approximate  $\psi^*$  by retaining only the lowest-order mode [3], [4]

$$\psi^*(x, y) \approx A_1 \cos(y/\lambda) \cdot [B_{1+} \exp(x/\lambda) + B_{1-} \exp(-x/\lambda)].$$

(2)

Since the higher order modes decay very quickly, this lowest-mode approximation is very accurate, especially near the channel center.  $\lambda$  is determined by satisfying the boundary conditions that  $\psi^* = 0$  at the Si/SiO<sub>2</sub> interfaces, i.e., by fitting a half period of  $\cos(y/\lambda)$  between the gate electrodes. If  $t_{ox} \ll t_{Si}$ , we obtain  $\lambda = (t_{Si} + 2\kappa t_{ox})/\pi$ , where the oxide is scaled to its effective electrical thickness  $\kappa t_{ox}$ . Therefore, the transverse confinement of the device determines  $\lambda$ . In the general case of a thicker oxide, we use the electrostatic boundary condition that at each Si/SiO<sub>2</sub> interface, the potential and the component of  $\varepsilon \cdot \vec{E}$  perpendicular to the interface should be continuous. This provides an implicit equation for  $\lambda$  [3]

$$\kappa \cdot \tan(t_{\rm Si}/2\lambda) \cdot \tan(t_{ox}/\lambda) = 1. \tag{3}$$

If  $t_{ox} \ll t_{Si}$ ,  $\lambda = (t_{Si} + 2\kappa t_{ox})/\pi$  satisfies (3) as expected. Equation (3) was originally derived by Frank *et al.* [3] and its related form applicable in SOI structures was derived by Monroe *et al.*[4].

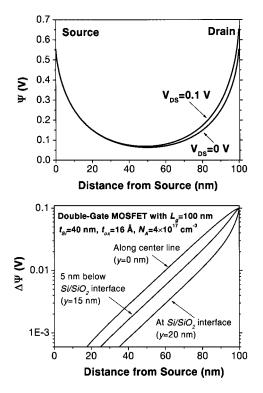

The evanescent mode is a property of the whole structure rather than just the Si/SiO<sub>2</sub> interface or the channel center, and as such,  $\lambda$  does not depend on transverse position within the channel. We have used the PADRE device simulator [7] to calculate  $\psi(x, y)$  and to obtain  $\lambda$  in the following manner. The potential along the channel center for  $V_{DS} = 0$  V and 0.1 V is shown in Fig. 2(a). The difference,  $\Delta \psi(x, y) = \psi(V_{DS} = 0.1 \text{ V}) - \psi(V_{DS} = 0 \text{ V})$ , is shown on a semi-log plot in Fig. 2(b). Since  $\Delta \psi \propto \exp(\pm x/\lambda)$ ,  $\lambda$  can be obtained directly from the slope of the linear region of each curve in Fig. 2(b). As we can clearly see,  $\lambda$  is independent of the transverse position. This is in direct contrast to predictions of other analyses based on the parabolic approximation.

In Fig. 3, we vary  $t_{ox}$  and compare  $\lambda$  predicted by each analytic model with the PADRE results.  $\lambda$  from evanescent-mode analysis was calculated by solving (3), and  $\lambda$  from simulation was extracted using the method of Fig. 2(b). The analytic results from evanescent-mode analysis agree extremely well with the PADRE results. Note that in the analysis of Yan *et al.*,  $\lambda \rightarrow 0$  as

Fig. 2. (a) Potential along the channel of a DG-MOSFET with applied source-drain biases of 0 V and 0.1 V. Parameters used are  $L_g = 100$  nm, uniform channel doping of  $N_A = 4 \times 10^{17}/\text{cm}^3$ ,  $t_{\rm Si} = 40$  nm,  $t_{ox} = 16$  Å, and a 4.17 eV workfunction for the source and drain. The potential is extracted along the Si/SiO<sub>2</sub> interface at  $y = t_{\rm Si}/2$ . (b) The difference between the channel potential with applied source-drain biases of 0 V and 0.1 V shown on a semi-log plot along lines at three transverse positions in the channel. The equivalent slopes of these lines indicate that the characteristic length  $\lambda$  is independent of transverse position.

$t_{ox} \rightarrow 0$ . This is *qualitatively* different from evanescent-mode analysis, which indicates that  $\lambda$  is nonzero even as  $t_{ox} \rightarrow 0$  due to the nonzero thickness of the silicon channel.

## III. APPLICATION TO THE CYLINDRICAL, SURROUNDING-GATE MOSFET

Evanescent-mode analysis was previously applied to device structures such as DG, fully-depleted SOI, and super-steep retrograde bulk [4]. Here, we extend this analysis to the case of the cylindrical, surrounding-gate (Cyl) MOSFET [8] of Fig. 1(b). The channel potential is again divided into two pieces,  $\psi_L(\rho)$ and  $\psi^*(\rho, z)$ , where  $\psi^*$  is a solution of the Laplace equation. The general solution of the Laplace equation in cylindrical coordinates with a finite potential at  $\rho = 0$  is [9]

$$\psi^{*}(\rho, \phi, z) = \sum_{m=0}^{\infty} \sum_{n=1}^{\infty} J_{m}(k_{mn}\rho) \cdot (A_{mn} \cos m\phi + B_{mn} \sin m\phi) \\ \cdot (C_{mn+}e^{k_{mn}z} + C_{mn-}e^{-k_{mn}z})$$

(4)

where  $J_m$  is the Bessel function of order m. Keeping only terms with m = 0 (since the potential cannot depend on  $\phi$  due to cylindrical symmetry) and defining  $\lambda_{Cyl} \equiv 1/k_{01}$ , the lowestorder (n = 1) mode is given by

$$\psi^{*}(\rho, z) \approx A_{01} \cdot J_{0}(\rho/\lambda_{\text{Cyl}}) \cdot \left(C_{01+}e^{z/\lambda_{\text{Cyl}}} + C_{01-}e^{-z/\lambda_{\text{Cyl}}}\right).$$

(5)

Fig. 3. Comparison of  $\lambda$  from three different analytic models and the results of PADRE simulations using the same  $L_g$ ,  $N_A$ , and  $t_{\rm Si}$  of Fig. 2. Evanescent-mode analysis predicts a characteristic length  $\lambda$  that agrees extremely well with PADRE simulations.

$\lambda_{\text{Cyl}}$  is fixed by fitting the first zero of  $J_0(x)$  at the gate electrode located at  $\rho = (D_{\text{Si}} + 2t_{ox})/2$ .

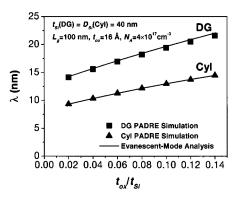

For  $t_{ox} \ll D_{Si}$ , as in the DG case, the different dielectric constants are taken into account by using the effective electrical oxide thickness  $\kappa t_{ox}$ . Since the first zero of  $J_0(x)$  occurs at x = 2.405, we obtain  $\lambda_{Cvl} = (D_{Si} + 2\kappa t_{ox})/4.810$ . We now compare this result with that for the DG-MOSFET for the case of  $t_{\rm Si} = D_{\rm Si}$  and equivalent  $t_{ox}$ . Since  $\lambda_{DG} = (t_{\rm Si} + t_{\rm Si})$  $2\kappa t_{ox})/\pi$ , we find that  $\lambda_{Cyl} = 0.653 \lambda_{DG}$ . Thus,  $\lambda_{Cyl}$  is about 35% smaller than  $\lambda_{DG}$ , assuming the same silicon dimensions,  $t_{ox}$ , and doping geometry. This can be understood to result from the tighter confinement present in the Cyl-MOSFET-whereas the DG structure has only one small transverse dimension, the cylindrical structure offers confinement from all transverse directions. This tighter confinement leads to a faster exponential decay of the potential along the channel length. The ratio  $\lambda_{\rm Cvl}/\lambda_{DG}$  obtained with evanescent-mode analysis is in reasonable agreement with previous work by Auth and Plummer [10]. However, the Auth–Plummer result is based on the parabolic approximation and is only intended to provide an estimate of  $\lambda$  in the special case in which the dominant subthreshold current occurs at the center of the channel. In contrast, the characteristic length  $\lambda_{Cvl}$  determined from evanescent-mode analysis is quite general and has a firm physical basis.

When  $t_{ox}$  is not very small, we solve the Laplace equation separately in the silicon and oxide regions. In cylindrical coordinates, the Bessel function  $J_0(\rho)$  and the Neumann function  $Y_0(\rho)$  are linearly independent solutions of the Laplace equation. The electrostatic boundary condition that the perpendicular component of  $\varepsilon \cdot \vec{E}$  is conserved at the Si/SiO<sub>2</sub> interface gives an implicit equation for  $\lambda_{Cvl}$ , as follows:

$$\frac{Y_0'(D_{\rm Si}/2\lambda_{\rm Cyl})}{J_0'(D_{\rm Si}/2\lambda_{\rm Cyl})} = \kappa \frac{Y_0(D_{\rm Si}/2\lambda_{\rm Cyl})}{J_0(D_{\rm Si}/2\lambda_{\rm Cyl})} + (1-\kappa) \frac{Y_0((D_{\rm Si}+2t_{ox})/2\lambda_{\rm Cyl})}{J_0((D_{\rm Si}+2t_{ox})/2\lambda_{\rm Cyl})}.$$

(6)

In Fig. 4, we compare  $\lambda$  for a DG- and a Cyl-MOSFET as a function of  $t_{ox}$ . We can clearly see the advantage of the cylindrical structure, which gives a 35% smaller  $\lambda$  compared to the DG structure. We also plot PADRE results which match very well with predictions from evanescent-mode analysis.

Fig. 4. Comparison of DG- and Cyl-MOSFET results.  $\lambda$  as obtained from evanescent-mode analysis is compared with PADRE simulation results for both DG- and Cyl-MOSFETs and shows excellent agreement.

### IV. CONCLUSION

Short-channel analyses based on the parabolic approximation provide inaccurate results for the characteristic length  $\lambda$  as well as the electrostatic potential in the channel. Evanescent-mode analysis, which properly deals with the 2-D electrostatic effects, provides solutions which accurately represent the potential in the entire device channel. One of the main physical insights provided by evanescent-mode analysis is that  $\lambda$  is directly related to the *transverse confinement provided by the device*. We have extended this analysis to the cylindrical case, and conclude that when compared to the DG-MOSFET, the tighter confinement from all directions allows the Cyl-MOSFET to be scaled to 35% shorter channel lengths.

#### ACKNOWLEDGMENT

The authors would like to thank Dr. S. Hillenius for management support. S.-H. Oh acknowledges Prof. J. D. Plummer of Stanford University for guidance and support.

### REFERENCES

- R.-H. Yan, A. Ourmazd, and K. F. Lee, "Scaling the Si MOSFET: From bulk to SOI to bulk," *IEEE Trans. Electron Devices*, vol. 39, pp. 1704–1710, July 1992.

- [2] K. Suzuki et al., "Scaling theory for double-gate SOI MOSFETs," IEEE Trans. Electron Devices, vol. 40, pp. 2326–2329, Dec. 1993.

- [3] D. J. Frank, Y. Taur, and H.-S. P. Wong, "Generalized scale length for two-dimensional effects in MOSFETs," *IEEE Electron Device Lett.*, vol. 19, pp. 385–387, Oct. 1998.

- [4] D. Monroe and J. M. Hergenrother, "Evanescent-mode analysis of shortchannel effects in fully depleted SOI and related MOSFETs," in *Proc. Int. IEEE SOI Conf.*, Oct. 1998, pp. 157–158.

- [5] J. C. S. Woo, K. W. Terrill, and P. K. Vasudev, "Two-dimensional analytic modeling of very thin SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 37, pp. 1999–2005, Sept. 1990.

- [6] T. N. Nguyen, "Small-geometry MOS transistors: Physics and modeling of surface- and buried-channel MOSFETs," Ph.D. dissertation, Stanford Univ., Stanford, CA, 1984.

- [7] M. R. Pinto *et al.*, "Three-dimensional characterization of bipolar transistors in a submicron BiCMOS technology using integrated process and device simulation," in *IEDM Tech. Dig*, 1992, pp. 923–926.

- [8] H. Takato *et al.*, "Impact of surrounding gate transistor (SGT) for ultrahigh-density LSIs," *IEEE Trans. Electron Devices*, vol. 38, pp. 573–577, Mar. 1991.

- [9] J. D. Jackson, *Classical Electrodynamics*. New York: Wiley, 1975, ch. 3.

- [10] C. P. Auth and J. D. Plummer, "Scaling theory for cylindrical, fully-depleted, surrounding-gate MOSFETs," *IEEE Electron Device Lett.*, vol. 18, pp. 74–76, Feb. 1997.