# Analytical drain current and performance evaluation for inversion type InGaAs gateall-around MOSFET

Cite as: AIP Advances 11, 065108 (2021); https://doi.org/10.1063/5.0052718 Submitted: 01 April 2021 • Accepted: 18 May 2021 • Published Online: 03 June 2021

🔟 I. K. M. Reaz Rahman, 🔟 Md. Irfan Khan and 🔟 Quazi D. M. Khosru

# COLLECTIONS

Paper published as part of the special topic on Mathematical Physics

# **ARTICLES YOU MAY BE INTERESTED IN**

An analytical drain current model for symmetric double-gate MOSFETs AIP Advances 8, 045125 (2018); https://doi.org/10.1063/1.5024574

Design optimization of sub-5nm node nanosheet field effect transistors to minimize selfheating effects

Journal of Vacuum Science & Technology B 39, 013201 (2021); https:// doi.org/10.1116/6.0000675

Surface potential calculation and drain current model for junctionless double-gate polysilicon TFTs

AIP Advances 4, 087107 (2014); https://doi.org/10.1063/1.4892609

# **AIP Advances**

Mathematical Physics Collection

READ NOW

AIP Advances 11, 065108 (2021); https://doi.org/10.1063/5.0052718 © 2021 Author(s).

11, 065108

r٦

Export Citation

View Online

# Analytical drain current and performance evaluation for inversion type InGaAs gate-all-around MOSFET

Cite as: AIP Advances 11, 065108 (2021); doi: 10.1063/5.0052718 Submitted: 1 April 2021 • Accepted: 18 May 2021 • Published Online: 3 June 2021

I. K. M. Reaz Rahman, a) 🔟 Md. Irfan Khan, 🔟 and Quazi D. M. Khosru 🔟

# **AFFILIATIONS**

Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology, Dhaka 1205, Bangladesh

<sup>a)</sup>Author to whom correspondence should be addressed: ikmreazrahman@eee.buet.ac.bd

# ABSTRACT

This paper presents an analytical investigation of the drain current model for symmetric short channel InGaAs gate-all-around (GAA) MOSFETs valid from depletion to strong inversion using a continuous expression. The development of the core model is facilitated by the solution of the quasi-2D Poisson equation in the doped channel, accounting for interface trap defects and fixed oxide charges. Correction to short channel effects such as threshold voltage roll-off, drain induced barrier lowering, and subthreshold slope degradation is later introduced, complemented with channel length modulation, velocity saturation, and mobility degradation from surface roughness, leading to accurate mobile charge density for electrostatic capacitance–voltage and transport characterization. The effect of physical process parameters such as fin width, oxide thickness, and channel length scaling is thoroughly investigated in both on and off states of the transistor. The robustness of the model is reflected by the precise match with published experimental reports in the literature. An R<sub>on</sub> of 1160  $\Omega \mu m$  is obtained from output characteristics and a switching efficiency improvement of 2.5 times is estimated by incorporating a high- $\kappa$  dielectric into the GAA transistor. Numerical 3D simulations from TCAD corroborate the validity of the proposed model in all regions of operation.

© 2021 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/5.0052718

### I. INTRODUCTION

Electrostatic control in three dimensions has become imperative to reduce the short channel effects (SCEs) in deeply scaled transistors beyond the 22 nm technology node. The gate-all-around (GAA) MOSFET has proven to provide the greatest immunity to SCEs with the shortest natural length ( $\lambda$ ) and impose stronger gate control over surface carriers.<sup>1–3</sup> Tremendous effort expended behind silicon nanowires and the incorporation of strain engineering reveal the potential of silicon as a favorable channel material for CMOS technology.<sup>4–6</sup> However, phonon scattering and surface roughness from the wrap-around gate configuration limit the mobility to subpar levels, impeding the performance of silicon nanowires from reaching near ballistic limits. This opens room for further improvement in carrier transport by utilizing high mobility III–V semiconductor channel materials. To this end, InGaAs has attracted the attention of researchers as a viable candidate for providing superior drain current in both on and off states.<sup>7-9</sup> On one hand, intense research in the past four decades has ushered significant progress on the use of atomic layer deposition (ALD) to integrate a thermodynamically stable high- $\kappa$ dielectric on a III–V semiconductor, which drastically reduces gate leakage current of InGaAs based transistors, offering better effective oxide thickness (EOT) for minimization of static power dissipation.<sup>10</sup> On the other hand, the inherent high mobility of a III–V semiconductor as the active channel material truncates dynamic power dissipation in the transistor, offering the same drive current at a reduced supply voltage.<sup>11</sup> This favored InGaAs gate-all-around MOSFETs to gain popularity in switching and logic applications.<sup>9</sup>

Although both cylindrical nanowires and rectangular GAA MOSFETs have exhibited excellent transport and subthreshold performance recently,<sup>12,13</sup> the rectangular geometry offers an additional

advantage in terms of the fabrication viewpoint. First, the seamless integration of rectangular MOSFETs with FinFET technology is possible because lateral nanowires bear strong resemblance with the FinFET architecture. This minimal deviation in the fabrication process encourages the semiconductor industry to reap the benefits provided by rectangular GAA MOSFETs over its cylindrical counterparts. Moreover, rectangular GAA MOSFETs can be grown epitaxially into thin nanosheets unlike cylindrical nanowire MOSFETs, which are grown by the vapor-liquid-solid (VLS) method.<sup>14</sup> This enables precise control of nanowire height in the rectangular geometry. One of the challenges in fabricating cylindrical nanowire is controlling the shape of the nanowire since the transport properties rely heavily on the nanowire diameter.<sup>15</sup> This difficulty is circumvented in rectangular GAA MOSFETs with etching techniques, allowing exact control of nanosheet width. Monolithic 3D stacking has persuaded researchers to explore the prospect of stacked nanosheets with a goal to achieve higher current drive while ensuring more  $\mathrm{W}_{\mathrm{eff}}$ under the same footprint as FinFETs.<sup>16,17</sup>

There have been numerous experimental reports on InGaAs MOSFETs exhibiting high drain current and excellent subthreshold characteristics.<sup>3,7,8,18</sup> Recently, short channel InGaAs GAA nanowire has been studied via top down approach, and numerical simulation of such a device illustrated volume inversion inside the active region for a fin width as low as 30 nm, which otherwise would require deca-nanometer dimensions for silicon counterparts.<sup>19,20</sup> Quantum mechanical simulations were carried out by Khan et al. to determine electrostatic charge and carrier transport under the uncoupled mode space approach, which is computationally expensive and often depends on the numerical convergence of the solution.<sup>21,22</sup> Existing analytical models developed for double-gate MOSFETs cannot be extrapolated to GAA geometry without involving proper physics into the Poisson equation. Compact models developed for silicon nanowires use a constant difference in potential between the center and the surface, which results in deviations near the threshold region and cannot be applied to the strong inversion operation.<sup>23</sup> Moreover, in InGaAs MOSFETs, a saturation of the decrease in subthreshold current is observed due to high drain junction leakage, which is not reflected by silicon based analytic reports.<sup>11</sup> Besides, fixed oxide charge and interface trap defects are neglected in these models, which are significant in high- $\kappa$  oxide/semiconductor interfaces and crucial for device performance evaluation. An efficient analytical model is, therefore, due for characterizing the electrostatic and transport behavior of depletion mode GAA MOSFETs that would predict the performance metrics with scaling of process parameters.

In this paper, an analytical drain current model is proposed for symmetric operation of short channel InGaAs GAA MOSFETs that accurately predicts the carrier density under electrostatic conditions as well as computes drain current from depletion to strong inversion under applied drain bias, incorporating interface traps and volume oxide charges. In Sec. II, a quasi-2D Poisson equation is solved in the active region with appropriate boundary conditions to determine the mobile carrier density, facilitating the determination of the quasistatic capacitance–voltage (CV) profile. The drain current is evaluated in Sec. III under the classical drift-diffusion formalism with the inclusion of certain short channel effects such as drain induced barrier lowering (DIBL), threshold voltage roll-off, subthreshold slope degradation, series resistance, channel length modulation, velocity saturation, and mobility degradation due to vertical and lateral electric fields to implicate the underlying physics of short channel operation. The impact of physical process parameters is rigorously investigated with channel length scaling in Sec. IV. The feasibility of high- $\kappa$ dielectrics to enhance device subthreshold characteristics will also be explored in this section. The excellent match between model results and published experimental reports highlights the accuracy of the proposed model in conjunction with numerical TCAD simulation to validate scaling properties. Section V systematically draws the conclusion of this work.

# **II. ELECTROSTATIC MODEL DESCRIPTION**

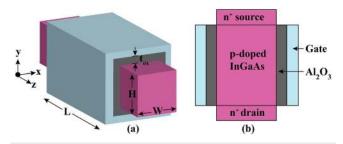

### A. Charge modeling

The symmetric gate-all-around MOSFET under consideration has acceptor doping concentration  $N_A$  in the  $In_{1-x}Ga_xAs$  channel with equal width (*W*) and height (*H*), gate length *L*, and ALD Al<sub>2</sub>O<sub>3</sub> having thickness  $t_{0x}$ , as shown in Fig. 1. The Ga-composition is 0.47 where not stated, and the central nanowire axis is taken as the origin so that the oxide/semiconductor interface is at  $x = y = \mp W/2$ .

Under the normal operating regime, the majority of carriers can be neglected, and the gradual channel approximation applies to the quasi-2D Poisson equation of a long channel GAA MOSFET,<sup>24</sup>

$$\frac{\mathrm{d}^2\phi}{\mathrm{d}x^2} + \frac{\mathrm{d}^2\phi}{\mathrm{d}y^2} = \frac{qN_{\mathrm{A}}}{\varepsilon_{\mathrm{s}}} \bigg( \mathrm{e}^{\frac{\phi-2\phi_{\mathrm{f}}-V}{\phi_{\mathrm{t}}}} + 1 \bigg). \tag{1}$$

Here,  $\varepsilon_s$  is the semiconductor permittivity, V is the electron quasifermi level with reference to the source,  $\phi_t = kT/q$  is the thermal voltage,  $\phi_f = \phi_t \ln(N_A/n_i)$ ,  $n_i$  is the intrinsic carrier density of In<sub>0.53</sub>Ga<sub>0.47</sub>As, and *x* and *y* represent the width and height directions, respectively. Due to the symmetric cross section, the electric field is identical in magnitude in both *x* and *y* directions, verified by 3D numerical simulations. Thus, the simplifying assumption  $\frac{d\phi}{dx} = \frac{d\phi}{dy}$ applies to (1) leading to

$$\frac{\mathrm{d}}{\mathrm{d}\phi} \left(\frac{\mathrm{d}\phi}{\mathrm{d}x}\right)^2 = \frac{qN_{\mathrm{A}}}{\varepsilon_{\mathrm{s}}} \left(\mathrm{e}^{\frac{\phi-2\phi_{\mathrm{f}}-V}{\phi_{\mathrm{t}}}} + 1\right). \tag{2}$$

Since (2) does not possess a closed form solution, by integrating once from the central nanowire axis to the oxide/semiconductor interface with appropriate boundary conditions,<sup>24,25</sup> which are

**FIG. 1.** Schematic view of a GAA MOSFET. The source/drain is heavily doped for Ohmic contacts, and the  $In_{0.53}Ga_{0.47}As$  channel is p-doped. (a) Perspective view. (b) Lateral view.

$\phi = \phi_0$ ,  $\frac{d\phi}{dx} = 0$  at the central nanowire axis,  $\phi = \phi_s$ , and  $\frac{d\phi}{dx} = E_s$  at the interface, we get

$$E_{\rm s} = \sqrt{\frac{qN_{\rm A}}{\varepsilon_{\rm s}}\phi_{\rm t}} \sqrt{e^{\frac{\phi_{\rm s} - 2\phi_{\rm t} - V}{\phi_{\rm t}}} \left(1 - e^{-\frac{\phi_{\rm s} - \phi_{\rm 0}}{\phi_{\rm t}}}\right) + \frac{\phi_{\rm s} - \phi_{\rm 0}}{\phi_{\rm t}}}, \qquad (3)$$

where  $\phi_s$  and  $\phi_0$  are the surface and center potential of the nanowire MOSFET, respectively. For the sake of simplicity, we consider  $\alpha = (\phi_s - \phi_0)/\phi_t$  as the normalized difference of potential, which, in deep depletion, takes a constant value ( $\alpha_{st}$ ) under the full depletion approximation (FDA) in the Poisson equation,

$$\alpha_{\rm st} = \frac{q N_{\rm A} W^2}{16\varepsilon_{\rm s} \phi_{\rm t}} = \frac{Q_{\rm b}}{16\varepsilon_{\rm s} \phi_{\rm t}},\tag{4}$$

where  $Q_b$  is the total fixed charge per unit length.

Although the use of constant  $\alpha_{st}$  well above the threshold is a crude approximation,<sup>23</sup> by relying on a coarse finite difference method, an exact expression of the normalized difference of potential above the threshold can be written in terms of the principle branch of the Lambert function,<sup>26</sup>

$$\alpha(\phi_{s}) = \alpha_{st} + LW\left(\alpha_{st}e^{-\alpha_{st}}e^{\frac{\phi_{s}-2\phi_{t}-V}{\phi_{t}}}\right).$$

(5)

Using Eq. (5) in (3) helps reduce the surface electric field in terms of  $\phi_s$  only,

$$E_{\rm s}(\phi_{\rm s}) = \sqrt{\frac{qN_{\rm A}}{\varepsilon_{\rm s}}}\phi_{\rm t} \sqrt{e^{\frac{\phi_{\rm s}-2\phi_{\rm f}-V}{\phi_{\rm t}}} + \left(1 - \frac{1}{\alpha_{\rm st}}\right)\alpha + 1}.$$

(6)

Since the space charge density per unit length in the semiconductor is given by  $Q_s = 4W\varepsilon_s E_s$ , the mobile charge density per unit length follows from the difference in space charge density and fixed charge density.

Despite advancement in ALD techniques, significant trap defects exist at the high- $\kappa$  oxide/semiconductor interface, which are accounted from the flat D<sub>*it*</sub> profile through the relation<sup>22</sup>

$$Q_{\rm it} = \int_{E_i}^{E_j} D_{\rm it} \, \mathrm{d}E,\tag{7}$$

where  $E_i = E_0$  and  $E_j = E_F$  if  $E_F$  lies above  $E_0$  and vice versa.  $E_0$  is the charge neutrality level of interface defects (~ 0.27 eV), which are mainly of donor type for Al<sub>2</sub>O<sub>3</sub>.<sup>27</sup> The presence of positive fixed oxide charges  $Q_f$  distributed throughout the gate dielectric affects the flat-band voltage  $V_{fb}$  by

$$V_{\rm fb} = \phi_{\rm ms} - \frac{Q_{\rm f}}{C_{\rm ox}},\tag{8}$$

where  $\phi_{ms}$  is the metal–semiconductor work function difference and  $C_{ox}$  is the oxide capacitance per unit length defined as

$$C_{\rm ox} = \frac{4W\varepsilon_{\rm ox}}{t_{\rm ox}} + 8C_{\rm fr}.$$

(9)

Here,  $C_{\rm fr} = 2(\varepsilon_{\rm ox}/\pi)\ln(1 + d_1/d_2)$  is the fringing capacitance resulting from the perpendicular plate alignment in the corners of the GAA MOSFET.<sup>28</sup>

Applying Gauss's law to the oxide/semiconductor interface and using (6) relate the gate voltage to the surface potential by

$$C_{\rm ox}(V_{\rm G} - V_{\rm fb} - \phi_{\rm s}) = 4W\varepsilon_{\rm s}E_{\rm s}.$$

(10)

The solution of (10) facilitates the evaluation of surface potential necessary for determining mobile charge that is modulated under electrostatic conditions and takes part in carrier transport,

$$Q_{\rm n} = Q_{\rm s} - Q_{\rm b} + Q_{\rm it}.\tag{11}$$

The approximation of the Lambert function given by (12) remarkably improves the speed of the solution in (10) with only a minor error introduced in the threshold region, as will be discussed in Sec. IV,<sup>29</sup>

$$LW(\gamma) \approx \ln(1+\gamma) \left( 1 - \frac{\ln(1+\ln(1+\gamma))}{2+\ln(1+\gamma)} \right).$$

(12)

#### B. Capacitance-voltage characteristics

The quasi-static capacitance–voltage profile is obtained from gated mobile charge density by differentiating  $Q_n$  with respect to gate voltage,

$$C_{\rm G} = \frac{\mathrm{d}Q_{\rm n}(V_{\rm G})}{\mathrm{d}V_{\rm G}},\tag{13}$$

where  $C_{\rm G}$  depends implicitly on physical dimensions, material properties, and the gate dielectric.

#### **III. TRANSPORT MODEL DESCRIPTION**

The core drain current of the short channel GAA transistor is expressed in terms of the following integral:

$$I_{\rm D} = \frac{\mu_{\rm eff}}{L_{\rm eff}} \int_{V_{\rm S}}^{V_{\rm D}} Q_{\rm n} (V_{\rm G} + \Delta \phi_{\rm min}) \, \mathrm{d}V, \qquad (14)$$

where  $\mu_{\rm eff}$  and  $L_{\rm eff}$  are effective mobility and channel length, respectively, after accounting for mobility degradation and channel length modulation and  $\Delta\phi_{\rm min}$  is the minimum potential barrier change in the conduction channel as elaborated below.

#### A. SCE correction

The potential barrier along the conduction path is minimum in the leakiest path of the transistor, which lies in the central nanowire axis of the MOSFET. The degree of SCE affecting threshold voltage ( $V_{\text{th}}$ ) roll-off, DIBL, and subthreshold slope degradation of the short channel transistor can be modeled by the change in this minimum potential obtained from the solution of the quasi-2D Poisson equation written in terms of  $\phi_0$  under FDA as follows:<sup>30</sup>

$$\frac{\mathrm{d}^2\phi_0(z)}{\mathrm{d}z^2} + \frac{V_\mathrm{G} - V_\mathrm{fb} - \phi_0}{\lambda^2} = \frac{qN_\mathrm{A}}{\varepsilon_\mathrm{s}},\tag{15}$$

AIP Advances 11, 065108 (2021); doi: 10.1063/5.0052718 © Author(s) 2021 where the characteristic natural length of the symmetric GAA MOSFET is defined as  $^{2}$

$$\lambda = \sqrt{\frac{\varepsilon_{\rm s} W t_{\rm ox}}{4\varepsilon_{\rm ox}} \left(1 + \frac{\varepsilon_{\rm ox} W}{4\varepsilon_{\rm s} t_{\rm ox}}\right)}.$$

(16)

Here, the natural length of the GAA MOSFET has been derived from the parabolic potential model, which was proposed by Suzuki *et al.*<sup>31</sup> and Auth and Plummer<sup>32</sup> and further corroborated by the authors of Refs. 30, 33, and 34. By applying boundary conditions  $\phi_0(0) = V_{bi}$  at the source end and  $\phi_0(L) = V_{bi} + V_{DS}$  at the drain end, (15) is solved to obtain

$$\phi_{0}, \min = \frac{A \sinh\left(\frac{L-z_{\min}}{\lambda}\right) + B \sinh\left(\frac{z_{\min}}{\lambda}\right)}{\sinh\left(\frac{L}{\lambda}\right)} + V_{SL}, \quad (17)$$

where the point of minimum potential is given by

$$z_{\min} = \frac{\lambda}{2} \ln \left( \frac{A e^{\frac{L}{\lambda}} - B}{B - A e^{-\frac{L}{\lambda}}} \right).$$

(18)

Here, the built-in potential  $V_{\rm bi} = \phi_{\rm t} \ln(N_{\rm D}N_{\rm A}/n_{\rm i}^2)$  depends on the concentration of the heavily doped source/drain region  $N_{\rm D}$ ,

$$A = V_{\rm bi} - V_{\rm SL},\tag{19}$$

$$B = V_{\rm bi} - V_{\rm SL} + V_{\rm DS},\tag{20}$$

$$V_{\rm SL} = V_{\rm G} - V_{\rm fb} - \frac{qN_{\rm A}}{\varepsilon_{\rm s}}\lambda^2. \tag{21}$$

It is to be noted that (18) is valid in the subthreshold region only. Hence, to determine  $z_{min}$ , the gate voltage is limited to threshold voltage.

At low  $V_{\text{DS}}$ , the approximation  $A \approx B$  leads to  $z_{\min} = L/2$  and facilitates the determination of threshold voltage for short channel GAA transistors ( $V_{\text{th,SC}}$ ) given by

$$V_{\rm th,SC} = V_{\rm th,LC} - \phi_{\rm min,th}, \qquad (22)$$

where  $V_{\text{th,LC}}$  is the threshold voltage of the long channel GAA MOS-FET obtained from the double derivative method in Ref. 25 and  $\phi_{\min, \text{th}}$  is the threshold voltage roll-off due to scaling of the gate length, evaluated by considering  $\phi_{\min, \text{th}}$  as the difference between the long channel minimum potential and the shift in minimum potential induced by the SCE,<sup>33</sup>

$$\phi_{\min,\text{th}} = \frac{2V_{\text{SL}}\sinh\left(\frac{L}{2\lambda}\right)}{2\sinh\left(\frac{L}{2\lambda}\right) + \sinh\left(\frac{L}{\lambda}\right)}.$$

(23)

The difference between (17) and (21) provides the change in minimum potential barrier  $\Delta \phi_{\min}$  necessary for SCE correction in the core transport model (14).

#### **B.** Velocity saturation

The drain saturation voltage of long channel devices  $V_{\text{GT}} = V_{\text{GS}} - V_{\text{th,LC}}$  is no longer followed by short channel transistors due to velocity saturation. An empirical relation, derived from numerous simulations for channel lengths lower than 300 nm, models the drain saturation voltage as<sup>35</sup>

$$V_{\rm DS,sat(SC)} = -0.36 + \eta (Lv_{\rm sat})^{\frac{1}{3}} V_{\rm GT}^{\frac{1}{2}},$$

(24)

where  $\eta$  is an adjusting parameter and  $v_{sat}$  is the saturation velocity. The drain saturation voltage  $V_{DS,sat(SC)}$  is gradually limited from its long channel counterpart by the relation

$$V_{\text{DS,sat}} = \frac{1}{2} V_{\text{DS,sat(SC)}} (1 + \tanh(3V_{\text{GT}})) + \frac{1}{2} V_{\text{GT}} (1 - \tanh(3V_{\text{GT}})).$$

(25)

An effective drain voltage is used in the core model where the drain voltage from the terminal is restricted to drain saturation voltage by the continuous expression

$$V_{\rm DS,eff} = V_{\rm DS,sat} \frac{1 - \ln \left( e^{8 \left( 1 - \frac{V_{\rm DS}}{V_{\rm DS,sat}} \right)} + 1 \right)}{\ln (e^8 + 1)}.$$

(26)

#### C. Mobility degradation

The degradation in mobility in the active region, resulting from the high lateral field due to proximity of the drain terminal to source end and surface scattering induced by the vertical electric field, is incorporated into the transport model by the effective mobility expression given by

$$\mu_{\rm eff} = \frac{\mu_1}{\left[1 + \left(\frac{\mu_1 V_{\rm DS,eff}}{v_{\rm su}L}\right)^{\sigma}\right]^{\frac{1}{\sigma}}}.$$

(27)

Here,  $\sigma$  is a constant parameter, which takes into account the carrier–carrier scattering in the channel region arising from the high lateral field, and  $\mu_1$  is the vertical field mobility degradation expressed in terms of low field mobility  $\mu_0$  and mobility degradation coefficient  $\theta$  as

$$\mu_{1} = \frac{\mu_{0}}{1 + \frac{1}{2}\theta(V_{\rm GS} - V_{\rm th,SC})[1 + \tanh(8(V_{\rm GS} - V_{\rm th,SC}))]}.$$

(28)

The mobility degradation coefficient is calibrated with experimental reports<sup>19</sup> such that contributions from surface scattering are incorporated into the model. Consequently, the corner effect in the GAA structure becomes strong at high overdrive voltage. The hyperbolic tangent factor in the denominator of (28) brings about this degradation at high gate field, thus mitigating the complexity of the numerical simulation.

#### D. Channel length modulation

As drain voltage exceeds saturation voltage, the short channel device suffers from reduced *L* due to extension of the drain-channel

depletion region. For  $V_{\rm DS}>V_{\rm DS,sat},$  the effective channel length then follows  $^{33}$

$$L_{\rm eff} = L - \sqrt{\frac{\kappa \varepsilon_{\rm s} \beta}{q N_{\rm A}} (1 + \tanh(10\beta))},$$

(29)

where  $\kappa$  is a fitting parameter and  $\beta = V_{DS} - V_{DS,sat}$ .

## E. Series resistance

The reduction in drain current in the saturation regime is attributed to the presence of parasitic resistance causing a voltage drop between the gate–source and the drain–source region. The total resistance can then be expressed in terms of channel resistance  $R_{\rm ch}$ and parasitic resistance  $R_{\rm S}(R_{\rm D})$  at the source (drain) end as<sup>36</sup>

$$R_{\rm T} = R_{\rm ch} + R_{\rm S} + R_{\rm D} = \frac{V_{\rm DS,eff}}{I'_{\rm D}}.$$

(30)

Taking (14) to be the drain current without parasitic resistance and using  $R_{ch} = V_{DS,eff}/I_D$ , we get the final drain current model  $(I'_D)$  in the form

$$I'_{\rm D} = \left[\frac{1}{I_{\rm D}} + \frac{R_{\rm S} + R_{\rm D}}{V_{\rm DS,eff}}\right]^{-1}.$$

(31)

### **IV. RESULTS AND DISCUSSION**

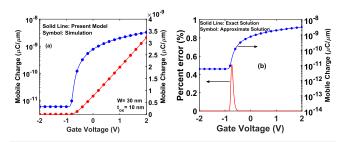

The results derived from the analytical model in Secs. II and III were compared with the experimental demonstration in Ref. 19 and further corroborated with 3D numerical simulations using the Synopsis tool.<sup>38</sup> In order to capture the physical effects inherent in the inversion mode operation of the short channel GAA MOSFET, various models were used in the TCAD simulation. This includes mobility degradation at the interface due to surface roughness and surface phonon and carrier-carrier scattering, which stem from the doping within the channel region. Apart from mobility degradation, the velocity saturation model and trap charge specification at the semiconductor-oxide interface and fixed oxide charges distributed throughout the gate dielectric were utilized. Generation-recombination processes account for exchange of carriers between the conduction and valence band. They are very important for device physics, hence these were implemented during device simulation. As oxide thickness, channel width, and gate length are scaled toward the deca-nanometer regime, certain nonideal effects come into play and degrade subthreshold characteristics. These effects are included by invoking the density gradient quantization model for important quantum effects. Table I lists the relevant physical process parameters used throughout this work for validation. As can be seen in Fig. 2(a), the mobile charge density predicted by the model, after inclusion of interface trap defects and a positive fixed oxide charge of ~  $9 \times 10^{18}$  cm<sup>-3</sup> distributed throughout the volume of oxide, matches well with that extracted at midchannel from simulation. The use of (12) in the solution of mobile charge dramatically enhances the computation speed of the model with only an error of about 0.51% error introduced in the transition from threshold to weak inversion.

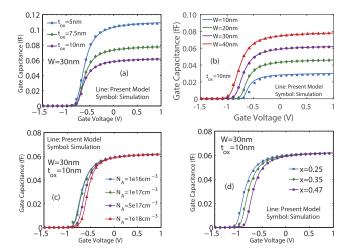

The effect of physical dimension and material properties on CV characteristics is illustrated in Fig. 3. The model accounts for

| Parameter description (unit)                            | Value                                 |

|---------------------------------------------------------|---------------------------------------|

| Fin width (nm)                                          | 20-40                                 |

| Oxide thickness (nm)                                    | 2.5-10                                |

| Acceptor concentration $(cm^{-3})$                      | $1 \times 10^{16} - 1 \times 10^{18}$ |

| Mole fraction                                           | 0.25-0.47                             |

| Gate metal work function (eV)                           | 4.6                                   |

| Midgap $D_{it}$ (cm <sup>-2</sup> eV <sup>-1</sup> )    | $5.6 \times 10^{12}$                  |

| Relative permittivity of $In_{1-x}Ga_xAs$               | 13.9-14.2                             |

| Relative permittivity of Al <sub>2</sub> O <sub>3</sub> | 9.3 <sup>a</sup>                      |

| Relative permittivity of LaAlO <sub>3</sub>             | 17 <sup>b</sup>                       |

| Relative permittivity of HfO <sub>2</sub>               | 25 <sup>c</sup>                       |

<sup>a</sup>Reference 18.

<sup>b</sup>Reference 37.

<sup>c</sup>Reference 38.

minority carrier concentration only with the CV profile decreasing to zero in the depletion mode and saturating to oxide capacitance in the strong inversion regime. As dictated by (9), the oxide capacitance is highest for a larger fin width and the thinnest gate oxide. Figure 3(b) reveals that the electrostatic behavior of a GAA MOSFET depends strongly on fin width in comparison to oxide thickness. The analysis of devices with a fin width smaller than 10 nm is restricted from the proposed model due to negligence of the quantum effect. With inclusion of the density gradient quantization model in TCAD, the simulation results reflect a rightward shift in the CV curve for a fin width of 10 nm, indicating the impact of quantum effect in threshold voltage shift near the subthreshold region and a degradation of gate capacitance in the strong inversion regime. On the contrary, channel doping and the Ga-mole fraction affects the CV profile in the depletion region only. For channel doping above  $1 \times 10^{17}$  cm<sup>-3</sup>, the shift in the CV curve is more prominent. At higher doping levels, the GAA MOSFET may enter partial depletion, requiring greater gate bias to create channel inversion. A decrease in the Ga mole fraction causes a leftward shift in CV transition, which is expected from the decreased bandgap of  $In_{1-x}Ga_xAs$ , facilitating the electron transition from the valence band to the conduction band at a reduced gate bias, as shown in Fig. 3(d).

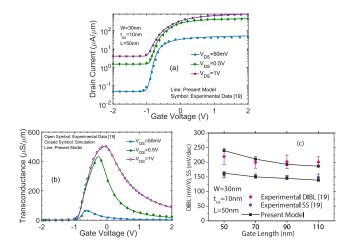

The transfer characteristics obtained from the proposed model are displayed in Fig. 4. The drain current and extrinsic

**FIG. 2.** Mobile charge density as a function of gate bias for a GAA MOSFET at  $N_A = 2 \times 10^{16} \, \mathrm{cm^{-3}}$ . (a) Comparison between the model and simulated charge density in both linear and log scales at low V<sub>DS</sub>. (b) Error in charge density from using (12) instead of the Lambert function. The largest error occurs near the threshold region.

**FIG. 3.** Effect of device dimensions and material properties on capacitance–voltage characteristics of a nanowire MOSFET (a) for various oxide thicknesses and (b) for various fin widths. The fin width has a greater impact on CV characteristics than oxide thickness, which is reflected by a shift in threshold voltage. The impact of quantum effect on the CV profile is seen for a fin width of 10 nm where simulation results reflect a rightward shift in CV arising from the threshold voltage shift in the subthreshold region and gate capacitance degradation in the strong inversion region. (c)–(d) The impact of channel doping (x = 0.47) and the Ga-mole fraction ( $N_A = 2 \times 10^{16}$  cm<sup>-3</sup>) on electrostatic behavior of the same device. The saturated oxide capacitance is independent of channel doping and the mole fraction of Ga. High channel doping (above 1 × 10<sup>17</sup> cm<sup>-3</sup>) affects the CV profile to a greater extent.

transconductance  $g_m$  are normalized by the active region perimeter (2W + 2H). Some of the transport model parameters used to calibrate the model with published experimental reports are shown in Table II, which accounts for velocity saturation, mobility degradation, channel length modulation, and series resistance.

**FIG. 4.** Transfer characteristics of a 50 nm GAA MOSFET. (a) Drain current as a function of gate voltage. (b) Extrinsic transconductance. (c) DIBL and the sub-threshold slope extracted from the  $I_D-V_G$  plot. Experimental data have been extracted from Ref. 19.

| TABLE II. Relevant | parameters | used in the | transport model. |

|--------------------|------------|-------------|------------------|

|--------------------|------------|-------------|------------------|

| Parameter description (unit)                                                                   | Value              |

|------------------------------------------------------------------------------------------------|--------------------|

| Parasitic source (drain) resistance ( $k\Omega$ )                                              | 0.5–5              |

| Saturation velocity (10 <sup>5</sup> m/s)<br>Low field electron mobility (cm <sup>2</sup> /Vs) | 3 <sup>a</sup>     |

| Mobility degradation parameter, $\sigma$                                                       | 903<br>1.5         |

| Mobility degradation coefficient, $\theta$                                                     | 1.5                |

| Velocity saturation parameter, $\eta$                                                          | 4.14               |

| Channel length modulation parameter, $\kappa$                                                  | $1 \times 10^{-5}$ |

<sup>a</sup>Reference 39.

The numerical solution of (10) provides a smooth transition in the threshold regime, which is further confirmed by continuous  $g_m$ , producing distinct peaks near the threshold point [Fig. 4(b)]. The incorporation of interface trap charge is essential in evaluating sub-threshold performance metrics, as portrayed in Fig. 4(c). The threshold voltage in DIBL evaluation is extracted from the  $I_D-V_G$  plot at a constant current level of 2  $\mu A/\mu m$  due to high drain junction leak-age current. The subthreshold slope (SS) obtained from the inverse of the steepest slope of transfer characteristics and DIBL at different gate lengths falls in the range of reported data, providing a precedent for comparing off-state performance of next generation GAA transistors.

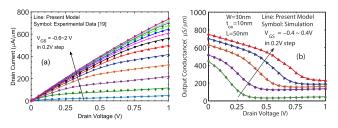

The output characteristics of the GAA transistor match well with the published report<sup>19</sup> in both linear and saturation regimes. From Fig. 5(a), it can be seen that an on-resistance of 1160  $\Omega \mu m$  is obtained from the initial slope of the I<sub>D</sub>–V<sub>D</sub> curve at V<sub>GS</sub> = 2 V. The continuity of the output characteristics is reflected from the gradual transition in output conductance, as illustrated in Fig. 5(b).

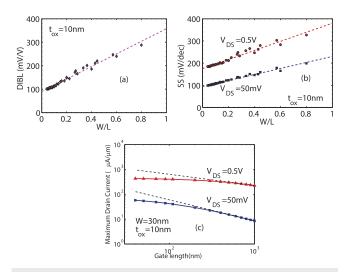

Before delving into the scaling properties of GAA transistors, the degree of SCE affecting such devices are explored semianalytically in both on and off states. Double-gate MOSFETs suffer from severe SCEs as the W/L ratio approaches unity.<sup>40</sup> Gate-allaround MOSFETs, on the other hand, provide better off-state performance in this regard, with DIBL and SS demonstrating roughly a proportional variation with the W/L ratio. As shown in Fig. 6, for the range of fin width shown in Table I, the maximum W/L ratio studied was 0.8 after which the DIBL and SS stray away from the linear relation. The impact of SCE on the subthreshold slope is even more at higher drain bias, which is evident from the sparsity of SS from the best fit linear graph in Fig. 6(b). The scaling behavior of drain

**FIG. 5.** (a) Output characteristics of a 50 nm GAA MOSFET. An R<sub>on</sub> of 1160  $\Omega \mu m$  is obtained from the slope at V<sub>GS</sub> = 2 V. (b) Output conductance of the same device, showing that drain current remains continuous from the linear to the saturation region. Experimental data have been extracted from Ref. 19.

**FIG. 6.** On-state and off-state characteristics of an InGaAs GAA transistor. Variation in (a) DIBL and (b) SS with the W/L ratio. Best fit straight lines are also plotted based on least square regression to highlight the proportional relation with W/L. (c) Maximum on-current as a function of gate length obtained at V<sub>GS</sub> = 2 V and different drain biases. For comparison, the dotted line shows when the drain current starts to saturate due to non-ideal effects in the short channel MOSFET.

current in the on-state of the transistor is displayed by tracing the maximum drain current from submicron to long channel lengths, as shown in Fig. 6(c). In the absence of non-ideal effects, the GAA transistor could reach drain current as high as 1 mA/ $\mu$ m at a gate length of around 40 nm. However, saturation induced by the SCE limits the channel current from reaching near ideal values.

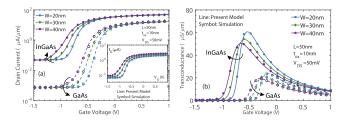

The proposed model accurately describes the transport phenomenon of III–V channel devices with scaling of physical process parameters. The transfer characteristics of III–V GAA MOSFETs for various fin widths are presented in Fig. 7. The saturation levels of the normalized drain current in the strong inversion region is less dependent on fin width, although fin width scaling affects threshold characteristics strongly and indicates an improvement in threshold behavior by shifting the transition from threshold to weak inversion to the right. This is attributed to volume inversion of the III–V channel caused by confinement of charge carriers at sub-nanometer

**FIG. 7.** Transfer characteristics of III–V channel GAA MOSFETs for various fin widths having  $N_A = 2 \times 10^{16} \text{ cm}^{-3}$ . (a) Normalized drain current as a function of gate voltage. The inset figure is for InGaAs GAA MOSFETs, showing that the total current of the wider nanowire is more, as expected. (b) Transconductance as a function of gate voltage. The solid lines and closed symbols are for InGaAs channel material, whereas the dashed lines and open symbols are for GaAs.

dimensions, which otherwise would require further reduction in fin width for silicon technology. The GaAs gate-all-around MOSFET has a lower off-current and better Ion/Ioff ratio, arising from larger effective mass along the transport direction than InGaAs, which suppresses the drain-junction leakage current.<sup>41</sup> On the contrary, the lower saturation current of similar GaAs devices in the strong inversion region can be elaborated by the proportional dependence of drive current  $(I_D)$  on the product of channel mobility and inversion capacitance  $(\mu C_{inv})$ <sup>42</sup> Although the larger density of states favors GaAs devices with a greater inversion capacitance, it is offset by the lower channel mobility of the GaAs channel, resulting in a low onstate current, as depicted in Fig. 7(a). These results are in coherence with previous reports, thus corroborating the efficacy of the proposed model in determining the scaling trend of physical dimensions for a range of III-V compounds as channel materials in GAA transistors. The inset figure reveals the finding that that the total current of a wider nanowire MOSFET is more, as expected, due to increased surface carriers near the oxide/semiconductor interface. There is only a slight increase in the  $g_m$  peak for both InGaAs and GaAs channels, as evidenced from Fig. 7(b), which can be further enhanced by scaling to deca-nanometer dimension, the analysis of which is restricted from the proposed model due to negligence of quantum effects.<sup>20</sup> Nevertheless, the excellent match between numerical simulations having a quantization model and analytical results justify the relaxation of quantum effect incorporation into the proposed model for the range of dimension under study.

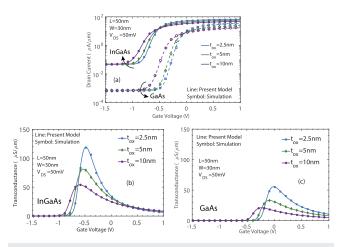

Figure 8 explores the trend in transfer characteristics with oxide thickness variation. For the sake of benchmarking, an initial oxide thickness of 10 nm was used for a gate length of 50 nm, resulting in an EOT of 4.5 nm, which is much larger than the ITRS guideline for device dimension.<sup>43</sup> However, we explored the trend of oxide scaling with EOT around 1 nm in compliance with the proposition of

**FIG. 8.** Transfer characteristics of the III–V channel GAA MOSFET for various oxide thicknesses having  $N_A = 2 \times 10^{16} \text{ cm}^{-3}$ . (a) Drain current as a function of gate bias. The cross-over of the curves indicates an invariant point where the effect of oxide thickness variation due to process limitation is minimized. The solid lines and closed symbols are for the InGaAs channel material, whereas the dashed lines and open symbols are for GaAs. (b) Transconductance as a function of gate bias for the InGaAs GAA MOSFET. (c) Transconductance as a function of gate bias for the GAAs GAA MOSFET.

ITRS. It was found that increasing the gate oxide thickness induces a reduction in channel current, besides lowering the threshold voltage. The existence of a cross-over in the transfer characteristics was previously observed for long channel devices with a wrap-around gate.<sup>44</sup> This phenomenon is extant in short channel transistors as well, regardless of the III–V channel material, occurring near the threshold region of doped nanowire MOSFETs, and serves as an invariant point, particularly important where oxide thickness variation could not be strictly controlled due to process limitations. The g<sub>m</sub> peak increases by 2.4 times by reducing the gate dielectric thickness from 10 nm to 2.5 nm, as portrayed in Figs. 8(b) and 8(c). This highlights a potential scope for EOT scaling, which, alternately, can be achieved by introducing high-κ dielectrics into the MOS transistor.

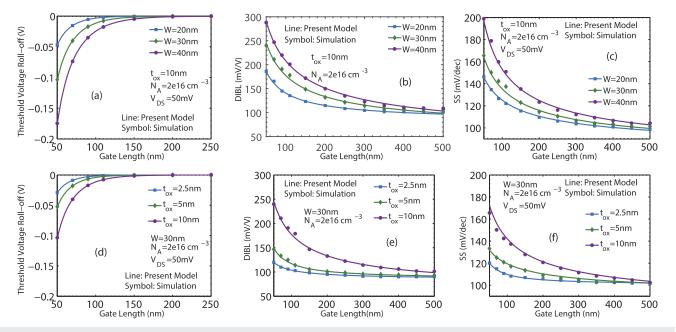

Figure 9 gives us an elaborate comparative analysis of the impact of dimension scaling on the subthreshold performance of GAA nanowire MOSFETs. Due to the presence of SCE, the minimum gate bias required for turning on the MOSFET is lowered as the channel length is scaled down. From Figs. 9(a) and 9(d), it is observed that fin width causes a greater threshold voltage roll-off at sub-nanometer gate lengths. The loss of gate control over electrostatic charges in thicker nanowire means that threshold voltage decreases drastically with gate length reduction. The effect of scaling on DIBL for various fin width and oxide thicknesses is displayed in Figs. 9(b) and 9(e). The effect of DIBL is severe for nanowires with a larger fin width, which is particularly inherited from the aggravated threshold voltage roll-off described earlier, and only slight improvement is obtained by reduction of fin width to practical limits. On the other hand, a dramatic enhancement of DIBL is identified for GAA MOSFETs with thinner oxide thicknesses. A similar variation in SS is observed from dimension scaling, where the minimum slope of the InGaAs MOSFET is far from the ideal SS of 60 mV/dec. The poor DIBL and SS are attributed to the high interface trap density between the  $Al_2O_3/InGaAs$  interface. This could be overcome by stacking the gate oxide with LaAlO<sub>3</sub>, as was successfully demonstrated in Ref. 3.

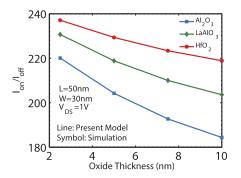

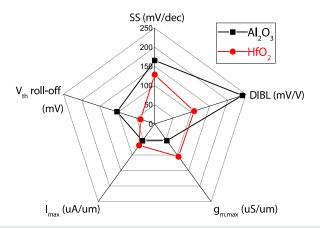

It is evident that the ultimate scalability of GAA MOSFETs can be achieved by incorporating high- $\kappa$  dielectrics having suitable integrability with the channel material. Although ALD Al<sub>2</sub>O<sub>3</sub> is reported to have the best interface quality with InGaAs, the performance of such GAA transistors is limited by a poor  $I_{on}/I_{off}$  ratio resulting from high drain junction leakage current. The switching efficiency (Q = gm/SS) is an important figure of merit to quantify the potential of inserting III-V channel material in CMOS technology that evaluates the Ion-vs-Ioff metric to capture the trade-off between dynamic switching speed and standby power.<sup>45</sup> The incorporation of LaAlO<sub>3</sub> or HfO<sub>2</sub> results in better switching efficiency, as clarified by Fig. 10. A high  $D_{it}$  of 12 ×10<sup>12</sup>/cm<sup>2</sup>eV at ~ 0.15 eV below the conduction band was adopted for HfO2 from published reports into the analytical framework.<sup>46,47</sup> Figure 11 illustrates a radar plot comparing the key features and benefits of using HfO<sub>2</sub> over Al<sub>2</sub>O<sub>3</sub> as the gate dielectric. At low drain bias, the subthreshold behavior is remarkably improved by replacing the gate oxide with HfO<sub>2</sub>, reducing DIBL, subthreshold slope, and threshold voltage roll-off to a greater extent. An increase in Imax indicates the superior current drivability in the on-state of the GAA transistor with a high- $\kappa$  dielectric. A switching figure of merit  $Q(=g_m/SS)$  of 0.82  $(\mu s/\mu m)/(mV/dec)$  is obtained from using HfO<sub>2</sub>, resulting in an improvement of 2.5 times over Al<sub>2</sub>O<sub>3</sub>. The high switching efficiency indicates InGaAs MOS-FETs as a potential candidate for switching application and logic devices.

FIG. 9. (a) Threshold voltage roll-off, (b) drain induced barrier lowering, and (c) subthreshold slope degradation due to gate length scaling at various fin widths. (d) Threshold voltage roll-off, (e) drain induced barrier lowering, and (f) subthreshold slope degradation due to gate length scaling at various oxide thicknesses. The subthreshold properties are affected to a greater extent due to fin width variation.

**FIG. 10.**  $I_{on}/I_{off}$  ratio as a function of oxide thickness for various gate dielectrics.  $I_{on(off)}$  is defined as the drain current at maximum (minimum) V<sub>GS</sub> and high drain bias. The high drain junction leakage current of InGaAs GAA MOSFETs results in a small on–off ratio.

**FIG. 11.**  $I_{on}/I_{off}$  ratio as a function of oxide thickness for various gate dielectrics.  $I_{on(off)}$  is defined as the drain current at maximum (minimum) V<sub>GS</sub> and high drain bias. The high drain junction leakage current of InGaAs GAA MOSFETs results in a small on–off ratio.

#### V. CONCLUSION

A capacitance-voltage and analytical drain current model is proposed in this work, catered for InGaAs with inclusion of interface defects and trap charges existing near the oxide/semiconductor interface. Certain non-ideal effects are included to emulate the SCEs in ultrascaled transistors. The model parameters have been calibrated with published reports based on symmetric InGaAs MOS-FETs. An extensive analysis of the GAA transistor is presented with variation in physical process parameters. Subthreshold performance metrics such as threshold voltage roll-off, DIBL, and subthreshold slope have been thoroughly investigated. Furthermore, the benefits of EOT scaling and integration of a high- $\kappa$  dielectric are explored to realize the scalability of GAA MOSFETs in the sub-nanometer domain, making them a potential candidate for switching and logic applications. The analysis presented in this work will provide the necessary platform for examination of more complex nanosheet structures.

#### ACKNOWLEDGMENTS

This work was carried out in the Department of Electrical and Electronic Engineering, Bangladesh University of Engineering and Technology (BUET). The authors gratefully acknowledge the support and facilities provided by BUET.

# DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### REFERENCES

<sup>1</sup>I. Ferain, C. A. Colinge, and J.-P. Colinge, "Multigate transistors as the future of classical metal-oxide-semiconductor field-effect transistors," Nature **479**, 310–316 (2011).

<sup>2</sup>C.-W. Lee, S.-R.-N. Yun, C.-G. Yu, J.-T. Park, and J.-P. Colinge, "Device design guidelines for nano-scale MuGFETs," Solid-State Electron. **51**, 505–510 (2007).

<sup>3</sup>J. J. Gu, X. W. Wang, H. Wu, J. Shao, A. T. Neal, M. J. Manfra, R. G. Gordon, and P. D. Ye, "20–80 nm channel length InGaAs gate-all-around nanowire MOSFETs with EOT = 1.2 nm and lowest SS = 63 mV/dec," in *2012 International Electron Devices Meeting* (IEEE, 2012), pp. 27.6.1–27.6.4.

<sup>4</sup>N. Singh, K. D. Buddharaju, S. K. Manhas, A. Agarwal, S. C. Rustagi, G. Q. Lo, N. Balasubramanian, and D.-L. Kwong, "Si, SiGe nanowire devices by top–down technology and their applications," IEEE Trans. Electron Devices **55**, 3107–3118 (2008).

<sup>5</sup>R. Wang, H. Liu, R. Huang, J. Zhuge, L. Zhang, D.-W. Kim, X. Zhang, D. Park, and Y. Wang, "Experimental investigations on carrier transport in Si nanowire transistors: Ballistic efficiency and apparent mobility," IEEE Trans. Electron Devices 55, 2960–2967 (2008).

<sup>6</sup>T.-Y. Liow, K.-M. Tan, H.-C. Chin, R. T. P. Lee, C.-H. Tung, G. S. Samudra, N. Balasubramanian, and Y.-C. Yeo, "Carrier transport characteristics of sub-30 nm strained N-channel FinFETs featuring silicon-carbon source/drain regions and methods for further performance enhancement," in *2006 International Electron Devices Meeting* (IEEE, 2006), pp. 1–4.

<sup>7</sup>O.-P. Kilpi, J. Svensson, and L.-E. Wernersson, "Sub-100-nm gate-length scaling of vertical InAs/InGaAs nanowire MOSFETs on Si," in 2017 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2017), pp. 17.3.1–17.3.4.

<sup>8</sup>X. Zhao, C. Heidelberger, E. Fitzgerald, W. Lu, A. Vardi, and J. Del Alamo, "Sub-10 nm diameter InGaAs vertical nanowire MOSFETs," in 2017 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2017), pp. 17.2.1–17.2.4.

<sup>9</sup>J. A. Del Alamo, D. A. Antoniadis, J. Lin, W. Lu, A. Vardi, and X. Zhao, "Nanometer-scale III-V MOSFETs," IEEE J. Electron Devices Soc. 4, 205–214 (2016).

<sup>10</sup>L. K. Chu, C. Merckling, A. Alian, J. Dekoster, J. Kwo, M. Hong, M. Caymax, and M. Heyns, "Low interfacial trap density and sub-nm equivalent oxide thickness in  $In_{0.53}Ga_{0.47}As$  (001) metal-oxide-semiconductor devices using molecular beam deposited  $HfO_2/Al_2O_3$  as gate dielectrics," Appl. Phys. Lett. **99**, 042908 (2011).

<sup>11</sup>Y. Q. Wu, W. K. Wang, O. Koybasi, D. N. Zakharov, E. A. Stach, S. Nakahara, J. C. M. Hwang, and P. D. Ye, "0.8-V supply voltage deep-submicrometer inversion-mode In<sub>0.75</sub>Ga<sub>0.25</sub>As MOSFET," IEEE Electron Device Lett. **30**, 700–702 (2009).

<sup>12</sup>H. Mertens, R. Ritzenthaler, A. Chasin, T. Schram, E. Kunnen, A. Hikavyy, L.-Å. Ragnarsson, H. Dekkers, T. Hopf, K. Wostyn *et al.*, "Vertically stacked gate-all-around Si nanowire CMOS transistors with dual work function metal gates," in 2016 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2016), pp. 19.7.1–19.7.4.

<sup>13</sup>N. Waldron, S. Sioncke, J. Franco, L. Nyns, A. Vais, X. Zhou, H. Lin, G. Boc-

<sup>13</sup>N. Waldron, S. Sioncke, J. Franco, L. Nyns, A. Vais, X. Zhou, H. Lin, G. Boccardi, J. Maes, Q. Xie *et al.*, "Gate-all-around InGaAs nanowire FETS with peak transconductance of 2200  $\mu$ s/ $\mu$ m at 50nm Lg using a replacement Fin RMG flow," in 2015 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2015), pp. 31–1.

<sup>14</sup>C. Zhang and X. Li, "III–V nanowire transistors for low-power logic applications: A review and outlook," IEEE Trans. Electron Devices 63, 223–234 (2015). <sup>15</sup>A. C. Parker and L. Lunardi, Women in Microelectronics (Springer, 2020).

<sup>16</sup>N. Loubet, T. Hook, P. Montanini, C.-W. Yeung, S. Kanakasabapathy, M. Guillom, T. Yamashita, J. Zhang, X. Miao, J. Wang *et al.*, "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET," in 2017 Symposium on VLSI Technology (IEEE, 2017), pp. T230–T231.

<sup>17</sup>R. Chau, "Process and packaging innovations for Moore's Law continuation and beyond," in 2019 IEEE International Electron Devices Meeting (IEDM) (IEEE, 2019), p. 1.

<sup>18</sup>Y. Xuan, Y. Q. Wu, and P. D. Ye, "High-performance inversion-type enhancement-mode InGaAs MOSFET with maximum drain current exceeding 1 A/mm," IEEE Electron Device Lett. **29**, 294–296 (2008).

<sup>19</sup>J. J. Gu, Y. Q. Liu, Y. Q. Wu, R. Colby, R. G. Gordon, and P. D. Ye, "First experimental demonstration of gate-all-around III-V MOSFETs by topdown approach," in 2011 International Electron Devices Meeting (IEEE, 2011), pp. 33.2.1–33.2.4.

<sup>20</sup>J. J. Gu, H. Wu, Y. Liu, A. T. Neal, R. G. Gordon, and P. D. Ye, "Size-dependent-transport study of In<sub>0.53</sub>Ga<sub>0.47</sub>As gate-all-around nanowire MOSFETs: Impact of quantum confinement and volume inversion," IEEE Electron Device Lett. **33**, 967–969 (2012).

<sup>21</sup> S. U. Z. Khan, M. S. Hossain, F. U. Rahman, R. Zaman, M. O. Hossen, and Q. D. M. Khosru, "Uncoupled mode space approach towards transport modeling of gate-all-around  $In_xGa_{1-x}As$  nanowire MOSFET," in *8th International Conference on Electrical and Computer Engineering* (IEEE, 2014), pp. 100–103.

<sup>22</sup>S. U. Z. Khan, M. S. Hossain, F. U. Rahman, R. Zaman, M. O. Hossen, and Q. D. M. Khosru, "Impact of high-κ gate dielectric and other physical parameters on the electrostatics and threshold voltage of long channel gate-all-around nanowire transistor," Int. J. Numer. Modell.: Electron. Networks, Devices Fields **28**, 389–403 (2015).

<sup>23</sup>O. Moldovan, A. Cerdeira, D. Jiménez, J.-P. Raskin, V. Kilchytska, D. Flandre, N. Collaert, and B. Iñiguez, "Compact model for highly-doped double-gate SOI MOSFETs targeting baseband analog applications," Solid-State Electron. 51, 655–661 (2007).

<sup>24</sup>R. D. Trevisoli, R. T. Doria, M. de Souza, and M. A. Pavanello, "Threshold voltage in junctionless nanowire transistors," Semicond. Sci. Technol. 26, 105009 (2011).

<sup>25</sup>P. Francis, A. Terao, D. Flandre, and F. Van de Wiele, "Modeling of ultrathin double-gate nMOS/SOI transistors," IEEE Trans. Electron Devices **41**, 715–720 (1994).

<sup>26</sup>J.-M. Sallese, N. Chevillon, C. Lallement, B. Iniguez, and F. Prégaldiny, "Chargebased modeling of junctionless double-gate field-effect transistors," IEEE Trans. Electron Devices 58, 2628–2637 (2011).

<sup>27</sup> P. K. Hurley, E. O'Connor, V. Djara, S. Monaghan, I. M. Povey, R. D. Long, B. Sheehan, J. Lin, P. C. McIntyre, B. Brennan, R. M. Wallace, M. E. Pemble, and K. Cherkaoui, "The characterization and passivation of fixed oxide charges and interface states in the Al<sub>2</sub>O<sub>3</sub>/InGaAs MOS system," IEEE Trans. Device Mater. Reliab. **13**, 429–443 (2013).

<sup>28</sup>S. S. Rodriguez, J. C. Tinoco, A. G. Martinez-Lopez, J. Alvarado, and J.-P. Raskin, "Parasitic gate capacitance model for triple-gate FinFETs," IEEE Trans. Electron Devices **60**, 3710–3717 (2013).

<sup>29</sup>S. Winitzki, "Uniform approximations for transcendental functions," in *International Conference on Computational Science and Its Applications* (Springer, 2003), pp. 780–789.

<sup>30</sup>J.-P. Colinge, *Finfets and Other Multi-gate transistors* (Springer, 2008), pp. 137-140.

<sup>31</sup>K. Suzuki, T. Tanaka, Y. Tosaka, H. Horie, and Y. Arimoto, "Scaling theory for double-gate SOI MOSFET's," IEEE Trans. Electron Devices 40, 2326–2329 (1993).

<sup>32</sup>C. P. Auth and J. D. Plummer, "Scaling theory for cylindrical, fully-depleted, surrounding-gate MOSFET's," IEEE Electron Device Lett. 18, 74–76 (1997).

<sup>33</sup>B. C. Paz, F. Ávila-Herrera, A. Cerdeira, and M. A. Pavanello, "Double-gate junctionless transistor model including short-channel effects," Semicond. Sci. Technol. **30**, 055011 (2015).

<sup>34</sup>T. K. Chiang, "A scaling theory for fully-depleted, surrounding-gate MOSFET's: Including effective conducting path effect," Microelectron. Eng. 77, 175–183 (2005).

<sup>35</sup>F. Ávila-Herrera, B. C. Paz, A. Cerdeira, M. Estrada, and M. A. Pavanello, "Charge-based compact analytical model for triple-gate junctionless nanowire transistors," Solid-State Electron. **122**, 23–31 (2016).

<sup>36</sup>R. Trevisoli, R. Doria, M. De Souza, and M. Pavanello, "Accounting for series resistance in the compact model of triple-gate junctionless nanowire transistors," in 2018 33rd Symposium on Microelectronics Technology and Devices (SBMicro) (IEEE, 2018), pp. 1–4.

<sup>37</sup>N. Goel, P. Majhi, W. Tsai, M. Warusawithana, D. G. Schlom, M. B. Santos, J. S. Harris, and Y. Nishi, "High-indium-content InGaAs metal-oxide-semiconductor capacitor with amorphous LaAlO<sub>3</sub> gate dielectric," Appl. Phys. Lett. **91**, 093509 (2007).

<sup>38</sup>S. D. U. Guide and G. Version, Synopsys Inc., Mountain View, CA, USA, June 2012.

<sup>39</sup>J. A. Del Alamo, "Nanometre-scale electronics with III-V compound semiconductors," Nature **479**, 317-323 (2011).

<sup>40</sup>A. Tsormpatzoglou, C. A. Dimitriadis, R. Clerc, Q. Rafhay, G. Pananakakis, and G. Ghibaudo, "Semi-analytical modeling of short-channel effects in Si and Ge symmetrical double-gate MOSFETs," IEEE Trans. Electron Devices 54, 1943–1952 (2007).

<sup>41</sup>P. Razavi and G. Fagas, "Electrical performance of III–V gate-all-around nanowire transistors," Appl. Phys. Lett. **103**, 063506 (2013).

<sup>42</sup> A. Lubow, S. Ismail-Beigi, and T. P. Ma, "Comparison of drive currents in metaloxide-semiconductor field-effect transistors made of Si, Ge, GaAs, InGaAs, and InAs channels," Appl. Phys. Lett. **96**, 122105 (2010).

<sup>43</sup>J. S. Meena, S. M. Sze, U. Chand, and T.-Y. Tseng, "Overview of emerging nonvolatile memory technologies," Nanoscale Res. Lett. 9, 526 (2014).

<sup>44</sup>F. Lime, O. Moldovan, and B. Iñiguez, "A compact explicit model for longchannel gate-all-around junctionless MOSFETs. Part I: DC characteristics," IEEE Trans. Electron Devices **61**, 3036–3041 (2014).

<sup>45</sup>G. Doornbos and M. Passlack, "Benchmarking of III–V n-MOSFET maturity and feasibility for future CMOS," IEEE Electron Device Lett. **31**, 1110–1112 (2010).

$^{46}$ H. Zhao, J. H. Yum, Y.-T. Chen, and J. C. Lee, "In\_{0.53}Ga\_{0.47}As n-metal-oxide-semiconductor field effect transistors with atomic layer deposited Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and LaAlO<sub>3</sub> gate dielectrics," J. Vac. Sci. Technol. B **27**, 2024–2027 (2009).

<sup>47</sup>R. Suzuki, N. Taoka, M. Yokoyama, S. Lee, S. H. Kim, T. Hoshii, T. Yasuda, W. Jevasuwan, T. Maeda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, "1-nm-capacitance-equivalent-thickness HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/InGaAs metal-oxide-semiconductor structure with low interface trap density and low gate leakage current density," Appl. Phys. Lett. **100**, 132906 (2012).