# Analytical Surface-Potential Calculation in UTBSOI MOSFETs with Independent Back-gate Control

S. Khandelwal<sup>1,2</sup>, Y. S. Chauhan<sup>2</sup>, Darsen D. Lu<sup>2</sup>, M. A. Karim<sup>2</sup>, S. Venugopalan<sup>2</sup>, A. Sachid<sup>2</sup>, A. Niknejad<sup>2</sup>, and C. Hu<sup>2</sup>

<sup>1</sup>Dept. of Electronics and Telecommunications, Norwegian University of Science and Technology, Trondheim, Norway, sourabh.khandelwal@ntnu.no

<sup>2</sup>Dept. of Electrical Engg. and Comp. Science, University of California, Berkeley, USA

## **ABSTRACT**

We present an analytical calculation for surfacepotential in UTBSOI MOSFETs. The developed surfacepotential calculation advances the previous work in terms of computational efficiency and accuracy. The surfacepotential can be calculated with independent back-gate control which is an important requirement for UTBSOI devices. The accuracy of our surface-potential calculation is of the order of nano-volts for full range of bias voltage without use of any empirical or fitting parameter.

Keywords: UTBSOI, FDSOI, Compact Models

## 1 INTRODUCTION

Recent literature [1,2] makes it very clear that ultra-thin body silicon on insulator (UTBSOI) devices are being used at production level by leading semiconductor manufactures for advanced technology nodes. These devices are attractive candidates for advanced IC technologies because of their superior control of short channel effects [3, 4]. They also offer the interesting possibility of dynamic threshold voltage control by use of the back-gate bias [5]. In low power and high performance designs, multiple threshold voltage devices are needed in the same circuit and typically, this is achieved by using different channel doping concentrations. But in case of UTBSOI devices, the same can be achieved by use of the back-gate bias instead of the channel doping. This reduces the problem of variability due to random dopant fluctuations [6]. To explore and exploit the benefits of UTBSOI transistors, accurate and fast simulation of circuits based on these devices is required. The accuracy and speed of such simulations depend heavily on the compact model used to describe the behavior of the device. This explains the importance of an efficient and precise compact model for these devices.

The primary requirements for a compact model of UTBSOI MOSFETs are analytical nature, accuracy and preservation of source-drain symmetry. Surface potential based models are preferred as they are more physical, but the calculation of surface potential almost always involves implicit functions, making the analytical solution difficult. In our earlier work [7], we presented an analytical solution for surface potential in these devices. The model in [7] finds the initial solution by a simplifying approximation for

the back-gate electric field and then uses perturbation technique to refine the solution. Although, the solution in [7] is analytical, the charge at the back-gate is neglected in [7], which reduces the accuracy. We propose an improved solution for the surface potential in these devices which has higher accuracy and increases the computational efficiency of the model.

The paper is arranged as follows. In section 2, we present the details of the surface-potential calculations. The developed calculations are verified by comparing with numerical solution in section 3. In section 4, we conclude the paper.

## 2 MODEL DESCRIPTION

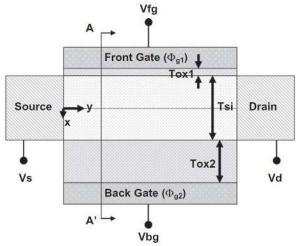

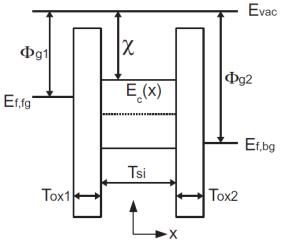

The calculation of the surface-potential in UTBSOI devices is based on the 2-dimensional cross-section of the device shown in Fig. 1. A silicon channel with thickness  $T_{Si}$  is sandwiched between the front- and the back-gate stacks. The two gate stacks are allowed to have different gate work functions ( $\Phi_{g1}$ ,  $\Phi_{g2}$ ), dielectric thicknesses ( $T_{oxI}$ ,  $T_{ox2}$ ) and dielectric constants ( $\varepsilon_I$  and  $\varepsilon_2$ ). The energy-band diagram of this system at flat-band condition is shown in Fig. 2.

The silicon body is assumed to be fully-depleted and lightly doped. The threshold voltage in these devices is controlled by back-gate bias or work-function adjustment, and low doping in silicon body is used to minimize the random dopant fluctuation.

The quasi Fermi-level at the source is taken as the reference for surface-potential since there is no neutral body in these devices. We define the potential  $\psi$  as,

$$\psi = -\frac{E_c - E_{f(source)}}{q} \tag{1}$$

where  $E_c$  is the conduction-band energy and  $E_{f(source)}$  is the quasi Fermi level at the source. The surface-potentials  $\psi_{s1} = \psi\big|_{x=-T_{Si}/2}$  and  $\psi_{s2} = \psi\big|_{x=T_{Si}/2}$  are the potentials at the

front- and back silicon/oxide interfaces respectively.

Poisson's equation in the silicon body assuming ideal long channel case is,

$$\varepsilon_{Si} \frac{d^2 \psi(x, y)}{dx^2} = q N_c \exp\left(\frac{\psi(x, y) - V_{ch}(y)}{V_{th}}\right)$$

(2)

Figure 1. Schematic cross-section of double gate UTBSOI MOSFET. Energy band-diagram for cutline A-A' is shown in Fig. 2.

Figure 2. Energy band diagram at flat-band condition corresponding to the A-A' cutline in Fig. 1.  $\chi$  is electron affinity.

where  $\varepsilon_{Si}$  is the dielectric permittivity of Silicon,  $N_c$  is the conduction band density of states of Silicon,  $V_{ch}$  is the channel potential at any position y in the channel and  $V_{th}$  is the thermal-voltage. Multiplying  $\frac{d\psi}{dx}$  on both sides of (2)

and integrating from  $-T_{Si}/2$  to  $T_{Si}/2$  we obtain,

$$E_{s1}^{2} - E_{s2}^{2} = \frac{2qN_{c}V_{th}}{\varepsilon_{si}} \left\{ \exp\left(\frac{\psi_{s1} - V_{ch}}{V_{th}}\right) - \exp\left(\frac{\psi_{s2} - V_{ch}}{V_{th}}\right) \right\}$$

where  $E_{s1}$  and  $E_{s2}$  are the electric fields at the front- and back-gate interface respectively.

The continuity of displacement field at the front- and back-interfaces gives the following relation between surface-potentials and electric fields,

$$C_{ox1(2)} \left( V_{fg(bg)} - \Delta \Phi_{1(2)} - \psi_{s1(2)} \right) = \varepsilon_{Si} E_{s1(2)}$$

(4)

where  $C_{ox1(2)} = \varepsilon_{ox1(2)} / T_{ox1(2)}$  are the front- and back-gate oxide capacitances,  $V_{fg(bg)}$  are the front- and back-gate voltages and  $\Delta\Phi_{1(2)}$  are the work function differences of the front-gate (back-gate) and the n+ source. Using (4) in (3) a relation between  $\psi_{s1}$ ,  $\psi_{s2}$ ,  $V_{fg}$  and  $V_{bg}$  can be obtained as,

$$\left\{ C_{ox1} \left( \frac{V_{fg} - \Delta \varphi_1 - \psi_{s1}}{\varepsilon_{Si}} \right) \right\}^2 - \left\{ C_{ox2} \left( \frac{V_{bg} - \Delta \varphi_2 - \psi_{s2}}{\varepsilon_{Si}} \right) \right\}^2 = \frac{2qN_cV_{th}}{\varepsilon_{Si}} \left\{ \exp\left( \frac{\psi_{s1} - V_{ch}}{V_{th}} \right) - \exp\left( \frac{\psi_{s2} - V_{ch}}{V_{th}} \right) \right\}$$

(5)

The function in (5) is an implicit relation in  $\psi_{s1}$  and  $\psi_{s2}$ . A relation between  $\psi_{s1}$  and  $\psi_{s2}$  can be obtained by assuming the back-gate to be in weak-inversion and equating the displacement vector at the back interface [8],

$$\psi_{s2} = \frac{C_{Si}}{C_{Si} + C_{av2}} \psi_{s1} + \frac{C_{ox2}}{C_{Si} + C_{av2}} (V_{bg} - \Delta \phi_2)$$

(6)

where  $C_{Si} = \varepsilon_{Si}/T_{Si}$  with  $T_{Si}$  as the silicon body thickness. Using (6) in (5) we find an implicit relation in  $\psi_{s1}$  which is given by,

$$\left\{ C_{ox1} \left( \frac{V_{fg}^* - \psi_{s1}}{\varepsilon_{Si}} \right) \right\}^2 - \left\{ \frac{V_{bg}^* - \psi_{s1}}{T_{Si} + \frac{\varepsilon_{Si}}{\varepsilon_{ox}} T_{ox2}} \right\}^2 =$$

(7)

$$\frac{2qN_cV_{th}}{\varepsilon_{Si}}\exp\left(\frac{\psi_{s1}-V_{ch}}{V_{th}}\right)\left\{1-\exp\left(\frac{(\alpha_{Si}-1)\psi_{s1}+\alpha_{ox}V_{bg}^*}{V_{th}}\right)\right\}$$

where  $V_{fg}^* = V_{fg} - \Delta\Phi_1$ ,  $V_{bg}^* = V_{bg} - \Delta\Phi_2$ ,  $\alpha_{Si} = C_{Si}/(C_{Si} + C_{ox2})$  and  $\alpha_{ox} = C_{ox2}/(C_{Si} + C_{ox2})$ . The implicit function (7) resembles the implicit relation for surface potential in bulk MOSFETs [9], but it is more complicated in this case because of the additional terms due to the back-gate. We have developed method to calculate  $\psi_{si}$  analytically from (7). Our method is described in the next sub-section.

## 2.1 Surface Potential Calculations

The implicit relation (7) in  $\psi_{s1}$  is expressed in a mathematically more convenient form as,

$$\left(\frac{x_{fg} - x}{G}\right)^2 - \left\{B\left(x_{bg} - x\right)\right\}^2 = \exp\left(x - x_n\right) - \exp\left(\alpha_{Si}x + \alpha_{ax}x_{be} - x_n\right)$$

(8)

A description of all the symbols used in (8) is given in Table 1.

The solution of (8) for x is computed in the following manner:

1. Compute the solution of (8)  $x_0$ , by assuming the electric field  $E_{s2}$  as [7],

$$E_{s2} = \frac{V_{fg}^* - V_{bg}^*}{\frac{\mathcal{E}_{Si}}{\mathcal{E}_{ox}} (T_{ox1} + T_{ox2}) + T_{Si}}$$

(9)

| Symbol          | Description                                                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------------------|

| $X_{fg/bg}$     | $rac{V_{fg/bg}^*}{V_{th}}$                                                                                          |

| G               | $rac{T_{ox1}}{arepsilon_{ox1}}\sqrt{rac{2qN_{_{c}}arepsilon_{_{Si}}}{V_{_{th}}}}$                                  |

| В               | $\frac{1}{T_{Si} + \frac{\varepsilon_{Si}}{\varepsilon_{ox}} T_{ox2}} \sqrt{\frac{\varepsilon_{Si} V_{th}}{2q N_c}}$ |

| X               | $rac{{{\psi _{s1}}}}{{{V_{th}}}}$                                                                                   |

| $\mathcal{X}_n$ | $V_{\scriptscriptstyle ch}$ / $V_{\scriptscriptstyle th}$                                                            |

Table 1. List of symbols used

and neglecting the second exponent term of the charge at the back-gate. This will change the second term on the left hand side of (8) from being function of x to an expression only involving  $x_{fg}$  and  $x_{bg}$  with constants. This solution is essentially the approximation used in the previous work [7]. The approach described in [7] is used to calculate  $x_0$ .

2. Next we compute the quantities  $\xi_1$ ,  $\xi_2$ , p, q, r and s defined by,

$$\xi_1 = \exp\left(x_0 - x_n\right) \tag{10}$$

$$\xi_2 = \exp\left(\alpha_{Si} x_0 + \alpha_{ox} x_{bg} - x_n\right) \tag{11}$$

$$p = \left(\frac{x_{fg} - x_0}{G}\right)^2 - B^2 (x_{bg} - x_0)^2 - \xi_1 + \xi_2 \quad (12)$$

$$q = \frac{-2}{G^2} (x_{fg} - x_0) + 2B^2 (x_{bg} - x_0) - \xi_1 + \alpha_{Si} \xi_2$$

(13)

$$r = \frac{2}{G^2} - 2B^2 - \xi_1 + \alpha_{Si}^2 \xi_2 \tag{14}$$

$$s = -\xi_1 + \alpha_{Si}^3 \xi_2 \tag{15}$$

3. Then we calculate  $x_1$  using the method described in [10] as,

$$x_1 = x_0 - \frac{p}{q} \left\{ 1 + \frac{pr}{2q^2} + \frac{p^2 (3r^2 - qs)}{6q^4} \right\}$$

(16)

We recalculate (10) - (16) once more using  $x_1$  as the input in place of  $x_0$  and finally obtain the output  $x_{sp1}$  from (16). This is done to improve accuracy of the solution. Then  $\psi_{s1}$  is simply given by,  $\psi_{s1} = x_{sp1}V_{th}$ . The calculated  $\psi_{s1}$  can be used to obtain  $\psi_{s2}$  using (6) and  $E_{s1}$  and  $E_{s2}$  using (4). A comparison between the developed analytical solution and numerical solution is shown in next section.

#### 3 RESULTS AND DISCUSSIONS

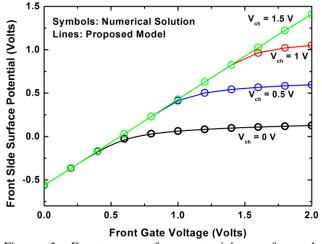

The calculation developed for  $\psi_{s1}$  is compared against numerical solution in Fig. 3 for different values of channel potential. An excellent agreement between numerical solution and the developed calculations is apparent from Fig. 3. The surface-potential calculation does not include any empirical or fitting parameters. The model correctly predicts the surface-potential from sub-threshold to strong-inversion using a single expression.

Figure 3. Front-gate surface potential  $\psi_{s1}$  from the numerical solution and the proposed model for different values of channel potentials.  $\psi_{s1}$  is measured relative to the quasi Fermi level at the source side.  $V_{bg} = 0$  V.

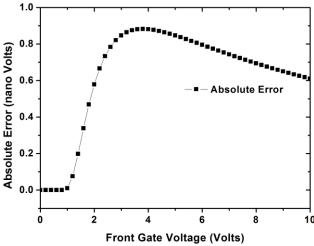

The error between the developed calculation and numerical solution is shown in Fig. 4, for extended range of bias voltage. To develop a surface-potential-based compact model in these devices, the accuracy of surface-potential calculations should be in the order of nano-volts and it is clear from Fig. 4, that the developed calculations achieve this requirement for full range of bias voltage. The maximum error between the analytical calculations of surface-potential and numerical solution is 0.9 nV. The developed calculations are successfully implemented in BSIM-IMG [11] model, resulting in an improvement in model accuracy and speed.

#### 4 CONCLUSIONS

We have presented a fully analytical calculation for surface-potential in UTBSOI devices. The accuracy of our calculation is in the order of nano-volts for full range of bias voltage. The developed calculations are more accurate and computationally more efficient as compared to previous work. These calculations can be used as the core for the development of a complete compact model for UTBSOI devices.

Figure 4. Absolute error between the numerical solution and the proposed model of  $\psi_{s1}$  for extended range of  $V_{fg}$ . The maximum error observed is 0.9 nV.  $V_{ch} = 0$ ,  $V_{bg} = 0$  V.

#### 5 ACKNOWLEDGEMENTS

The work was carried out with support by the SRC under contract number 2055.001.

#### REFERENCES

- [1] Press Article, Available on SOI Consortium Website <a href="http://www.soiconsortium.org/news-events/press-releases.php?id=34">http://www.soiconsortium.org/news-events/press-releases.php?id=34</a>

- [2] T. Skotnicki, "Competitive SOC with UTBB SOI" *IEEE SOI Conference*, Tempe, pp. 1-61, Oct. 3-6, 2011.

- [3] Z. Ren, S. Mehta, J. Cai, S. Wu, Y. Zhu, T. Kanarsky, S. Kanakasabapathy, L.F. Edge, R. Zhang, P. Lindo, J. Koshy, K. Tabakman, P. Kulkarni, V. Sardesai, K. Cheng, A. Khakifirooz, B. Doris, H. Bu, D.-G. Park, "Assesment of fully-depleted planar CMOS for low power complete circuit operation" *IEDM Technical Digest*, Washington DC, December 5-7, 2011.

- [4] Y-K. Choi, Y-C. Jeon, P. Ranade, H. Takeuchi, T-J. King, J. Bokor, C. Hu, "30nm Ultra-Thin-Body SOI MOSFET with Selectively Deposited Ge raised S/D," 58th Device Research Conference, Denver, CO, pp. 23-24, June 19-21, 2000.

- [5] O. Faynot, F. Andrieu, O. Weber, C. Fenouillet-Beranger, P. Perreau, J. Mazurier, T. Benoist, O. Rozeau, T. Poiroux, M. Vinet, L. Grenouillet, J. P. Noel, N. Posseme, S. Barnola, F. Martin, C. Lapeyre, M. Casse, X. Garros, M –A Jaud, O. Thomas, G. Cebarario, L. Tosti, L. Brevard, C. Tabone, P. Gaud, S. Barraud, T. Ernst, and S. Delonibus, "Planar fully depleted SOI technology: a powerful architecture for 20nm and beyond", IEDM Technical Digest, San Francisco, December 6-8, 2011.

- [6] A. Asenov, "Random Dopant Induced Threshold Voltage Lowering and Fluctuations in Sub-0.1∟m MOSFET's: A 3-D 'Atomistic' Simulation Study," IEEE Transaction on Electron Devices, vol. 45, no. 12, pp. 2505-2513, Dec 1996..

- [7] Darsen D. Lu, Mohan V. Dunga, Chung-Hsun Lin, Ali M. Niknejad, and Chenming Hu, "A computationally efficient compact model for fully-depleted SOI MOSFETs with independent controlled front and back-gates," Solid State Electronics, vol. 62, pp. 31-39, Feb. 2011.

- [8] A. S. Roy, J. M. Sallese and C. C. Enz, "A closed-form charge-based expression for drain current in symmetric and asymmetric double gate MOSFET," Solid State Electronics, vol. 50, issue 4, pp. 687-693, Apr. 2006.

- [9] T. L. Chen and G. Gildenblat, "Analytical approximation for the MOSFET surface potential," Solid State Electronics, vol. 45, issue 2, pp. 335-339, Feb 2001.

- [10] Bo Yu, H. Lu, M. Liu, and Y. Taur, "Explicit continuous models for double gate and surrounding gate MOSFETs", IEEE Trans. Elect. Dev. vol. 54, no. 10, Oct. 2007.

- [11] BSIM-IMG Manual, BSIM Group, Available: <a href="http://www-device.eecs.berkeley.edu/">http://www-device.eecs.berkeley.edu/</a>