# Analytical Switching Loss Model for Superjunction MOSFET With Capacitive Nonlinearities and Displacement Currents for DC–DC Power Converters

Ignacio Castro, Student Member, IEEE, Jaume Roig, Ratmir Gelagaev, Student Member, IEEE, Basil Vlachakis, Filip Bauwens, Diego G. Lamar, Member, IEEE, and Johan Driesen, Senior Member, IEEE

Abstract—A new analytical model is presented in this study to predict power losses and waveforms of high-voltage silicon superjunction MOSFET during hard-switching operation. This model depends on datasheet parameters of the semiconductors, as well as the parasitics obtained from the printed circuit board characterization. It is important to note that it also includes original features accounting for strong capacitive nonlinearities and displacement currents. Moreover, these features demand unusual extraction of electrical characteristics from regular datasheets. A detailed analvsis on how to obtain this electrical characteristic is included in this study. Finally, the high accuracy of the model is validated with experimental measurements in a double-pulse buck converter setup by using commercial SJ MOSFET, as well as advanced device prototypes under development.

Index Terms- Power MOSFET, analytical Models, capacitors, nonlinear circuit and current measurements.

## I. INTRODUCTION

- IGH-VOLTAGE superjunction (SJ) MOSFET in the range of 600 V have been in the market for around 20 years. As frequencies of operation increase to miniaturize passive components of the system, the prediction of switching losses in power converters is becoming more complex and necessary. A deep understanding of the transients is crucial to achieve proper models with realistic reproduction of the measured waveforms. Hence, the aim of this study is to provide an accurate and physically meaningful analytical model to estimate switching losses in SJ MOSFET.

In prior literature, a large number of piecewise analytical models address the dynamic behavior of the power switches [1]–[5]. All these models have in common the segmentation of

Manuscript received January 5, 2015; revised March 24, 2015; accepted May 3, 2015. Date of publication May 13, 2015; date of current version November 16, 2015. This work was supported by the Asturian Gobernment through the grant Beca Predoctoral "Severo Ochoa" BP14-140. This work was also supported by the project E2 SG, cofunded by grants from Belgium, Italy, Austria, Germany, Spain, The Netherlands, Portugal, Slovakia, The U.K., and the ECSEL Joint Undertaking. Recommended for publication by Associate Editor Y. C. Liang.

I. Castro and D. G. Lamar are with the Departamento de Ingeniería Eléctrica, Electrónica, Universidad de Oviedo, Gijón 33204, Spain (e-mail: castroignacio@uniovi.es; gonzalezdiego@uniovi.es).

J. Roig, B. Vlachakis, and F. Bauwens are with Power Technology Centre, Corporate R&D, ON Semiconductor, Oudenaarde 9700, Belgium (e-mail: jaume.roig@onsemi.com; basil.vlachakis@onsemi.com; filip. bauwens@onsemi.com).

R. Gelagaev and J. Driesen are with the Department of Electrical Engineering, KU Leuven, Heverlee 3001, Belgium (e-mail: ratmir. gelagaev@esat.kuleuven.be; johan.driesen@esat.kuleuven.be).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2015.2433017

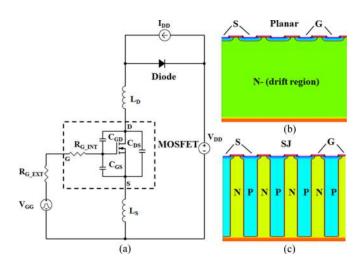

Fig. 1. (a) Circuit scheme to derive the analytical model and to perform mixedmode simulations. (b) Cross section of Planar MOSFET. (c) Cross section of SJ MOSFET built by using TCAD tools. In the performed simulations, only a half of the basic cells in (b) or (c) are combined with the circuit in (a).

a single operation cycle in different time intervals. In this sense, the turn-on and turn-off are constituted by multiple intervals. Each one of these intervals has an associated equivalent circuit in reference to the switch action within an inductive switching topology like the one plotted in Fig. 1(a). Some of these models [3]-[5] are mainly focused on the low voltage range (<40 V), thus being specialized in emulating features related to highspeed switching rather than replicating the details related to the architecture of the device. Other works [1], [2] provide dedicated models for high-voltage MOSFET (>500 V). However, these models are actually designed for Planar technologies [see Fig. 1(b)] meaning some characteristics of SJ MOSFET [see Fig. 1(c)] are not taken into consideration.

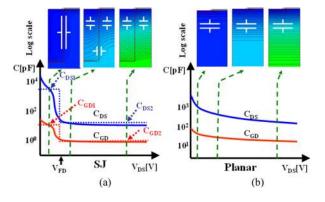

Among the peculiar features of the SJ MOSFET, the nonlinear parasitic capacitances appear as a major hindrance in analytical models. As a matter of fact,  $C_{DS}$  and  $C_{GD}$  show a reduction of several orders of magnitude when sweeping  $V_{\rm DS}$  from zero to more than a hundred volts [see Fig. 2(b)]. Many works model this effect by an effective constant capacitance  $(C_{\text{eff}})$  extracted by integrating the capacitance along the voltage range of interest [6]. This approach can be really inefficient in a piecewise model like the one presented in this study due to the consideration of several values of capacitance in order to obtain the analytical model. Other models propose a capacitive decay that is linear with  $V_{\rm DS}$  [7] or proportional to  $(1 + V_{\rm DS}/\Phi)^{-1/2}$ , where  $\Phi$  is an

See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 2. Schematic dependence of  $C_{\rm DS}$  and  $C_{\rm GD}$  with  $V_{\rm DS}$  in (a) SJ MOSFET and (b) Planar. Equipotential lines and equivalent capacitances are plotted in the MOSFET drift region for three  $V_{\rm DS}$  values. Dotted lines in (a) indicate  $C_{\rm DS1,2}$ and  $C_{\rm GS1,2}$ , as well as the step function that is used to approximate nonlinear capacitances in the new theoretical model.

adjustment parameter [3], [4]. These two approaches increase the accuracy of the circuit analysis with respect to  $C_{\rm eff}$  in the analysis of Planar MOSFET; however, their precision could be insufficient for SJ MOSFET. Finally, recent work suggests the use of multiple constant capacitances for different intervals of time [1]. Nevertheless, the extraction of the different capacitances does not follow an established methodology neither a physical meaning is attributed.

Inspired by the model in [1], a new analytical model that defines two separated values of capacitance ( $C_{DS1,2}$  and  $C_{GD1,2}$ ) has been developed schematically defined by dotted lines in Fig. 2(a). It should be noted that the model presented in this paper is a black-box and does not take into account the architecture of the MOSFET but the behavior of its capacitances. The relation between C and  $V_{DS}$  has been studied in previous works [12]. The transition from one capacitive value to the other is determined by the relative value of  $V_{\rm DS}$  with respect to a  $V_{\rm FD}$ . The latter has the physical meaning of being the voltage at which the MOSFET drift region is fully depleted. Aside from the nonlinear capacitances, extensively described in Section II, the new model also includes a correction to the displacement currents inside the MOSFET. Despite a few papers mentioning the impact of the displacement current on the power dissipation [8]–[10], this effect has never been included before in an analytical model. The details for the current displacement modeling will be found in Section III. Further discussion on minor elements of the model and the deployment of the complete formulation are the contents of Section IV. Section V presents the experimental validation and discussion of the model, and eventually, Section VI is devoted to draw conclusions and to define future lines of work.

#### **II. NONLINEAR CAPACITANCES**

The dynamic effects caused by the nonlinear capacitances need to be taken into account in order to have an accurate analytical model. In order to tackle these effects, two different values of  $C_{\rm DS}$  and  $C_{\rm GD}$  are defined for voltages above and below a newly defined  $V_{\rm FD}$  voltage. As shown in Fig. 2(a), a step function sets  $C_{\rm DS1}$  and  $C_{\rm GD1}$  when  $V_{\rm DS} < V_{\rm FD}$ , whereas  $C_{\rm DS2}$  and  $C_{\text{GD2}}$  are activated when  $V_{\text{DS}} > V_{\text{FD}}$ . The inset pictures in Fig. 2 display the equipotential line distribution in the cross section of a half-pitch cell in Planar and SJ MOSFET. Both structures are built using TCAD tools [11]. From them, it can be inferred that  $C_{DS1}$  represents the horizontal capacitance when the vertical PN pillar starts depleting charge to the lateral direction. The accumulation of potential lines in a relatively thin (<10  $\mu$ m per half pitch) and large capacitive area (>40  $\mu$ m per half pitch) result in a very high capacitance. Differently,  $C_{DS2}$ incarnates the vertical capacitance after the charge between pillars is completely depleted. In this case, the potential lines are stacked vertically in a relatively thick (>40  $\mu$ m per half pitch) and small capacitive area (<10  $\mu$ m per half pitch), thus giving a very small capacitance. Since the MOS gates lay above the N pillars, the full depletion of these pillars enables the potential lines to be relieved from the gate oxide toward the silicon undemeath. Subsequently, the transition from  $C_{\text{GD1}}$  to  $C_{\text{GD2}}$  will be correlated with the transition from  $C_{DS1}$  to  $C_{DS2}$ .

From a waveform perspective, the full depletion of the drift region in SJ MOSFET is translated into a steep variation of the  $dV_{\rm DS}/dt$  when  $V_{\rm DS}$  is equal to  $V_{\rm FD}$ . As it will be further described in Section IV,  $V_{\rm DS}$  reaches  $V_{\rm FD}$  at the beginning of the Miller Plateau during the turn-on and, oppositely, at the end of the Miller Plateau during the turn-off. It is important to note that, in prior literature [1], the inflection point during the  $V_{\rm DS}$  raise or fall was never related to  $V_{\rm FD}$  but confused with the voltage drop during conduction. Furthermore, this phenomenology, genuine to SJ MOSFET, does not appear in planar MOSFET. As shown in Fig. 2(b), the depletion from the p-n junction at the silicon surface is always extending vertically toward the bottom of the drift region. This implies that the capacitive area for  $C_{\rm DS}$  and  $C_{\rm GD}$  is always the same one and it only increases with the depth when a certain voltage is applied. It is this effect, the one that causes  $V_{\rm DS}$  to rise and drop progressively during transients when working with planar MOSFET.

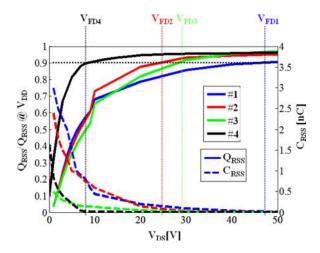

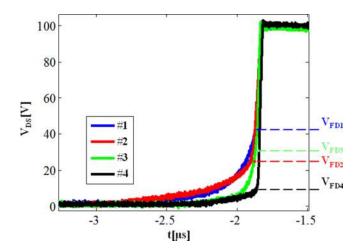

The  $C_{\rm DS}$  and  $C_{\rm GD}$  transition from high to low values has been discussed above for an ideal SJ MOSFET structure. However, this transition could be more or less abrupt depending on the charge balance between N and P pillars, the different cell pitch at the termination and many other technological factors. Consequently, sometimes, it becomes difficult to define an effective  $V_{\rm FD}$  that separates the two levels of capacitance. In this paper, we propose a methodology to extract  $V_{\rm FD}$  based on the  $V_{\rm DS}$  value at which  $Q_{\rm RSS}$  reaches 90% of  $Q_{\rm RRS}$  at  $V_{\rm DD}$  (maximum reverse voltage). In a similar fashion as in other datasheet standards (e.g., definition of reverse recovery charge or  $Q_{\rm RR}$ ), a percentage below 100% avoids issues related to large saturation tails for  $Q_{RSS}$ . In order to validate this method, four different SJ MOSFETs have had  $V_{\rm FD}$  calculated from datasheets and also extracted from  $V_{\rm DS}$  waveforms (see Figs. 3 and 4). It is important to note that samples #1, #2, and #3 are commercially available, whereas sample #4 is a prototype produced by ON Semiconductor. A comparison between the  $V_{\rm FD}$  calculated from the datasheet capacitance graphs and the  $V_{\rm FD}$  estimated from transient  $V_{\rm DS}$  waveforms (inflection point) is shown in Table I proving the validity of this method. It is worth remarking that  $V_{\rm FD}$  tends to lower values in ultimate SJ MOSFET generations.

Fig. 3.  $Q_{\rm RSS}$  and  $C_{\rm RSS}$  versus  $V_{\rm DS}$  for four different SJ MOSFETs.  $Q_{\rm RSS}$  is normalized to  $Q_{\rm RSS} @V_{\rm DD}$  for illustrative purposes. Dotted lines indicate  $V_{\rm FD}$  when  $Q_{\rm RRS}$  reaches 90% of  $Q_{\rm RSS} @V_{\rm DD}$ .

Fig. 4. Measured  $V_{\rm DS}$  versus time for four different SJ MOSFETs. The measurements are performed by using a double-pulse setup in a similar circuit as Fig. 1(a) ( $V_{\rm DD} = 100$  V,  $I_{\rm DD} = 4$  A). The  $V_{\rm DS}$  inflection point is perfectly correlated with the  $V_{\rm FD}$  definition in Fig. 3.

This fact, related to the smaller cell pitch, has interesting advantages to reduce the switching MOSFET power losses ( $P_{SW}$ ), as it will be discussed in Section V.

#### **III. CURRENT DIVERSION**

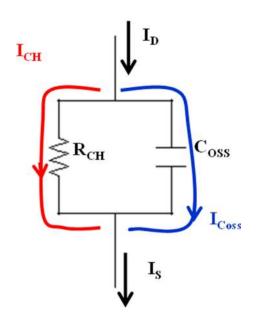

The current diversion phenomenon, triggered by the existence of displacement currents which internally charge and discharge the capacitances within the device, consists on the division of the MOSFET source current  $(I_S)$  into two components: the current that flows through the channel  $(I_{\rm CH})$  and the current that flows through the output capacitance  $(I_{\rm COSS})$ .

This effect, experimentally proven in [10], only takes place during some specific periods of time within fast turn-on and turnoff events. An alternative method used in this paper to study the current diversion is the mixed-mode simulation. Mixed-mode simulation combines the TCAD structures in Fig. 1(b) with the SPICE circuit depicted in Fig. 1(a). Hence, the physical effects

TABLE I

TESTED SJ MOSFETS WITH THEIR  $R_{\rm ON}$  and  $V_{\rm FD}$

|        | Device           | $R_{ m ON}$ [m $\Omega$ ] | $V_{\rm FD}$ [V] |            |  |

|--------|------------------|---------------------------|------------------|------------|--|

| Sample |                  |                           | Measured         | Analytical |  |

| #1     | IPA60 R190 C6    | 170                       | 46               | 47         |  |

| #2     | STF23 NM60 ND    | 150                       | 23               | 24         |  |

| #3     | FCPF22 N60 NT    | 140                       | 31               | 28         |  |

| #4     | ON Semiprototype | 145                       | 8                | 8          |  |

Fig. 5. Simplified model of the MOSFET to explain current diversion effect.

in the SJ MOSFETs are captured with more accuracy than using SPICE-based models. A direct consequence is the recognition of current due to hole or electron flow, corresponding to  $I_{\rm COSS}$  and  $I_{\rm CH}$ , respectively. For the specific case of SJ MOSFET #4 (ON Semiconductor prototype), the technological and geometrical parameters are perfectly detailed in the TCAD structure. This structure is, therefore, selected to exemplify the current diversion effect as well as to calibrate the same effect in the analytical model.

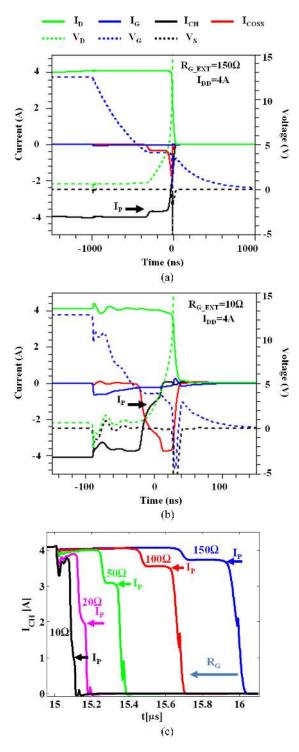

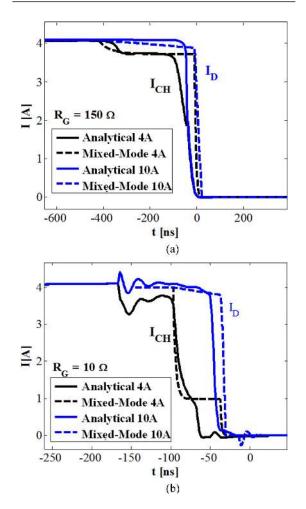

The simulated waveforms during the turn-off, calculated by SDEVICE from Sentaurus [11], are plotted in Fig. 6 for two different values of external gate resistance ( $R_{G_{\rm EXT}}$ ). The selection of 150 and 10  $\Omega$  for  $R_{G_{\rm EXT}}$  allows the analysis of slow and fast transitions. In both cases, an  $I_{\rm CH}$  fall is observed at the start of the Miller plateau. The remaining current level after the current fall is defined as current plateau ( $I_P$ ), and it becomes a fundamental piece of our analytical model. Interestingly,  $I_{\rm CH}$ falls down to  $I_P$  due to the charging of  $C_{\rm OSS}$  by  $I_{\rm COSS}$ , as it can be seen in Fig. 5. Note that this occurs in parallel to  $V_{\rm DS}$ rise. It is therefore deduced that, for small  $R_{G_{\rm EXT}}$ , the need to charge  $C_{\rm OSS}$  in a short time demands high  $I_{\rm COSS}$ , temporally diverted from  $I_{\rm CH}$ . The reduction of  $I_P$  at small  $R_{G_{\rm EXT}}$ is more prominent for values below 20  $\Omega$ , as it is observed in Fig. 6(c). A similar phenomenology occurs in a lesser extent

Fig. 6. Simulated current and voltage waveforms during the turn-off for (a)  $R_{G_{\rm EXT}} = 150 \ \Omega$  and (b)  $R_{G_{\rm EXT}} = 10 \ \Omega$  ( $I_{\rm DD} = 4$  A). The  $I_{\rm CH}$  value during the Miller plateau, otherwise named  $I_P$ , is indicated in both cases. (c) Variation of  $I_{\rm CH}$  with  $R_G$ , in order to show the effect over the current plateau ( $I_P$ ).

to charge  $C_{\text{ISS}}$  when part of  $I_S$  diverts to  $I_G$ . Such a secondorder current diversion, only noticeable in the case of 10  $\Omega$  for  $R_{G\text{-}EXT}$ , is neglected in this model for simplification.

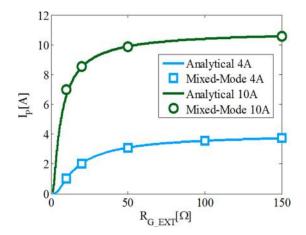

The key to obtain accurate  $I_{\text{COSS}}$  and  $I_{\text{CH}}$  waveforms in this analytical model is  $I_P$  value. In order to model  $I_P$  with accuracy,

Fig. 7.  $I_P$  versus  $R_{G\_EXT}$  extracted from analytical model (lines) and simulations (symbols).  $I_{DD}$  is 4 and 10 A.  $I_P = I_{CH} = I_{DD}$  for large  $R_{G\_EXT}$ .

it needs to be taken into account that there is a high dependence of this value with  $R_{G\_EXT}$ . Therefore, by taking that into account and relating  $I_P$  also with circuit behavior and device data, a general analytical formula has been developed empirically by observing  $I_P$  patterns in the simulated waveforms. This analytical formula is provided as

$$I_p = I_{\rm DD} e^{-k \frac{Q_{\rm DS} v_{\rm GG}}{Q_{\rm GD} I_{\rm DD} R_G}} \tag{1}$$

where the dependences with  $I_{\rm DD}$ , which is the current in the MOSFET when is turned ON,  $R_G$  that is the sum of  $R_{G\_EXT}$  and  $R_{G\_INT}$ ,  $V_{\rm GG}$  which is the driving voltage of the MOSFET,  $Q_{\rm GD}$  and  $Q_{\rm GS}$ , are taken into account and where k is a parameter of adjustment. The value of k is adjusted to 1.2 empirically to match the analytical and simulated  $I_P$  for SJ MOSFET #4. It is noteworthy that this value remains constant for different current  $(I_{\rm DD})$  conditions. A good correlation for  $I_P$  versus  $R_{G\_EXT}$  is demonstrated in Fig. 7 comparing analytical and simulated values for  $I_{\rm DD}$  4 and 10 A.

In the context of our piecewise model,  $I_P$  becomes relevant in the second and third stages of the turn-off as explained in the following section. During the turn-off plateau region,  $I_P$ calculated in (1) is subtracted from  $I_{\rm CH}$ , which represents the unique current able to generate losses by Joule effect. Conversely, during the turn-on plateau region,  $I_P$  is added to  $I_{\rm CH}$ . The latter, perfectly counterbalances the lower MOSFET power loss at the turn-off ( $P_{\rm SW,OFF}$ ) by a higher MOSFET power loss at the turn-on ( $P_{\rm SW,ON}$ ) [9]. Hereafter, for practical reasons, our model automatically adds the difference between  $P_{\rm SW,OFF}$ calculated by  $I_D$  and  $I_{\rm CH}$  to  $P_{\rm SW,ON}$  calculated by  $I_D$ .

### IV. ANALYTICAL MODEL DESCRIPTION

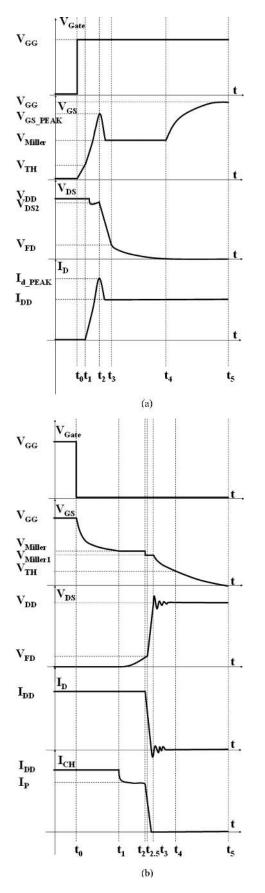

The proposed piecewise analytical model is divided in multiple stages in both the turn-on [see Fig. 8(a)] and turn-off [see Fig. 8(b)]. Each one of these total ten stages is defined by observing patterns in the measured waveforms of different SJ MOSFETs in a dc/dc converter. Hence, this model reliability has only been tested for dc/dc converter under normal operating conditions for the MOSFET. It should be noted that turn-on and

Fig. 8. Piecewise analysis of current and voltage waveforms for SJ MOSFETs during (a) turn-on and (b) turn-off.

turn-off are completely independent. In order to estimate the waveforms, the equations need to be used sequentially, always calculating all the parameters from the previous stage before proceeding to the next stage (e.g., stage 1 parameters need to be calculated before proceeding into stage 2).

### A. Turn-On (Stages 1–5)

Stage 1 ( $t_0 - t_1$ ): At the start of this stage, the voltage applied between the gate and the source ( $V_{\rm GS}$ ) is 0. By increasing  $V_{\rm GG}$ , both  $C_{\rm GS}$  and  $C_{\rm GD}$  will start being charged, thus increasing  $V_{\rm GS}$ exponentially, as shown in (2) with  $\tau_{\rm iss} = R_G \cdot [C_{\rm GS2} + C_{\rm GD2}]$ . At this stage, the MOSFET is supporting high voltage; therefore,  $C_{\rm GS2}$  and  $C_{\rm GD2}$  are going to be used

$$V_{\rm GS}(t) = V_{\rm GG} \left[ 1 - e^{-(t-t_0)/\tau_{\rm iss}} \right].$$

(2)

During this stage, the diode will still be conducting until  $V_{\rm GS}$  reaches the threshold voltage value  $(V_{\rm th})$  that is reached by the end of this stage. Therefore, the MOSFET is not conducting and the voltage between drain and source  $(V_{\rm DS})$  is equal to  $V_{\rm DD}$ .

Stage 2  $(t_1 - t_2)$ : In this stage,  $V_{\rm GS}$  surpasses the threshold voltage which means that the current will start increasing from zero. Thus, making  $V_{\rm DS}$  to start dropping. In this case  $t_2 - t_1$ is defined as the time it takes the current to go from 0 A to  $I_{D\_{\rm PEAK}}$ , where  $I_{D\_{\rm PEAK}}$  is the peak current reached thanks to the reverse recovery of the diode. Therefore, it is important to be able to characterize the reverse recovery effect of the diode correctly. For this reason, an approximation similar to the one explained in [1] is going to be used, considering the  $Q_{\rm RR}$  of the diode and the *di/dts* in order to obtain  $I_{D\_{\rm PEAK}}$ .  $V_{\rm GS}$  also reaches a peak by the end of this stage that is defined by

$$V_{\rm GS\_PEAK} = \frac{I_{D\_PEAK}}{g_{\rm fs}} + V_{\rm th},$$

(3)

where  $g_{\rm fs}$  is the transconductance of the MOSFET.

It is important to take into account that during this stage, the FET can either be working in the ohmic region or in the saturation region. In this analytical model, only the saturation region is going to be considered, due to the characteristics of the application.

In the case under study, the current starts increasing following  $V_{\text{GS}}$ .  $V_{\text{GS}}$  is obtained from the Laplace transformation of the equivalent circuit of the stage as done in previous works [1], [2]

$$V_{\rm GS}(t) = V_{\rm GS\_PEAK} - (V_{\rm GS\_PEAK} - V_{\rm th}) \left[ e^{-(t-t_1)/\beta} \right]$$

(4)

$$I_D(t) = g_{\rm fs} \left[ V_{\rm GG} - V_{\rm th} \right] \left\{ 1 - \frac{1}{\tau_a - \tau_b} \cdot \left( \tau_a \left( e^{-(t-t_1)/\tau_a} \right)^q - \tau_b \left( e^{-(t-t_1)/\tau_b} \right)^q \right) \right\}$$

(5)

$$V_{\rm DS}\left(t\right) = V_{\rm DD} - \left(L_s + L_d\right) \frac{dI_D}{dt},\tag{6}$$

where  $L_S$  and  $L_D$  are parasitic inductances that are depicted in the circuit of Fig. 1(a). The following parameters are to be applied to (5):

$$\tau_n = R_G \left( C_{\rm GS2} + C_{\rm GD2} \right) + g_{\rm fs} \cdot L_s \tag{7}$$

$$\tau_m = \sqrt{R_G \cdot C_{\text{GS2}} \cdot g_{fs} \left( L_s + L_d \right)} \tag{8}$$

$$\tau_a = \frac{2\tau_m^2}{\left(\tau_n - \sqrt{\tau_n^2 - 4\tau_m^2}\right)} \tag{9}$$

$$\tau_b = \frac{2\tau_m^2}{\left(\tau_n + \sqrt{\tau_n^2 - 4\tau_m^2}\right)}.$$

(10)

It is important to note that in (5), q is a fixed value that was experimentally adjusted to fit SJ MOSFET di/dt, and it has the same value for the four MOSFET under study. Also,  $g_{\rm fs}$  is nonlinear and it varies with  $I_D$ .  $g_{\rm fs}$  will be considered constant for the value of  $I_{\rm DD}$  under study, even though the current through the MOSFET changes during the switching stage.

Stage 3 ( $t_2 - t_3$ ): At this time, the MOSFET  $V_{DS}$  starts dropping until it reaches  $V_{FD}$  and the current drops to zero in the diode, meaning it is equal to  $I_{DD}$  in the MOSFET. Therefore, the amount of time required for this stage is not as simple to calculate as in other stages, mainly because  $t_3$  can either be considered as the time  $V_{DS}$  reaches  $V_{FD}$  or the time it takes for  $I_D$  to reach  $I_{DD}$ . For this analysis, both times will be calculated, and  $t_3$  will be taken as the time it takes longer to achieve. This is the reason  $t_{2.5}$  is defined in this stage,  $t_{2.5}$  will always be considered as the time  $V_{DS}$  reaches  $V_{FD}$ . So in the case, it takes longer for  $V_{DS}$  to reach  $V_{FD}$ ,  $t_3$  will be equal to  $t_{2.5}$ . During this stage,  $I_D$  reaches  $I_{DD}$ , in order to model this slope, the frequency of oscillation of the ringing is going to be taken into account considering a sinusoidal waveform for the ringing of the current. Therefore,  $I_D$  is modeled as followed:

$$f_{\rm osc} = \frac{1}{2\pi\sqrt{(L_d + L_s)(C_{\rm GD2} + C_{\rm DS2})}}$$

(11)

$$I_D(t) = [I_{d}_{\text{PEAK}} - I_{\text{DD}}] \cos(\omega_{\text{osc}}(t - t_2)) + I_{\text{DD}}.$$

(12)

If  $I_{\rm DD}$  is reached before  $V_{\rm FD}$ ,  $I_D$  is kept constant at  $I_{\rm DD}$  value and  $V_{\rm FD}$  will eventually be reached in the next stage. Otherwise,  $V_{\rm FD}$  will be defined by (13) until the time is  $t_{2.5}$ . From  $t_{2.5}$  till  $t_3$ ,  $V_{\rm DS}$  will be defined by (14)

$$V_{\rm DS}\left(t\right) = V_{\rm DS2} - \left[\frac{V_{\rm GG} - V_{\rm miller}}{R_G \cdot C_{\rm GD2}}\right] \left(t - t_2\right),\tag{13}$$

where  $V_{\text{miller}} = \frac{I_{\text{D}\,\text{D}}}{g_{\text{fs}}} + V_{\text{th}}$

$$V_{\rm DS}(t) = V_{\rm FD} \cdot \left[ e^{-(t - t_{2.5})/\alpha} \right].$$

(14)

In (14),  $\alpha$  is the value that allows  $V_{\rm DS}$  to be equal to  $V_{\rm ds\_on}$  at  $t_4$ . The time  $t_4$  can be defined as  $t_4 = t_2 + t_{\rm mp}$ , where  $t_{\rm mp}$  is the time of the Miller Plateau that is obtained as

$$t_{\rm mp} = \frac{(V_{\rm FD} - V_{\rm ds\_on}) \cdot (R_{G\_ext} + R_{G\_int}) \cdot C_{\rm GD1}}{(V_{\rm GG} - V_{\rm th})}.$$

(15)

Finally, for this stage,  $V_{GS}$  is defined as shown in (16). When  $V_{\text{miller}}$  is reached,  $V_{GS}$  is kept constant at that value

$$V_{\rm GS}\left(t\right) = V_{\rm GS\_PEAK} + \frac{1}{g_{\rm fs}} \cdot \frac{di}{dt} \cdot (t - t_2). \tag{16}$$

Stage 4  $(t_3 - t_4)$ : The time this stage lasts is determined by (15) as explained before.  $V_{\rm DS}$  is given by (14) and the current is kept constant at  $I_{\rm DD}$  value. It should be noted that from this point onwards the model is no longer working in the high voltage range and  $C_{\rm GD1}$  and  $C_{\rm DS1}$  are going to be used.

Stage 5  $(t_4 - t_5)$ : At this stage, the MOSFET is in the onstate; therefore,  $V_{\rm DS}(t)$  is kept at  $V_{\rm ds\_on}$  and  $I_D(t)$  is kept at  $I_{\rm DD}$ . In terms of  $V_{\rm GS}$ , it continues to charge up the output capacitance ( $C_{\rm OSS}$ ) following the next equation, where  $\tau_{\rm oss} = R_G \cdot (C_{\rm GD1} + C_{\rm DS1})$ :

$$V_{\rm GS}(t) = V_{\rm miller} + (V_{\rm GG} - V_{\rm miller})(1 - (e^{-(t - t_4)/\tau_{\rm oss}})).$$

(17)

#### B. Turn-Off (Stages 6–10)

Stage 6  $(t_0 - t_1)$ : During this stage,  $V_{\rm GS}$  starts at  $V_{\rm GG}$  value. The moment  $V_{\rm GG}$  is set to zero,  $V_{\rm GS}$  starts decreasing steadily, due to the discharge of the parasitic capacitances of the MOSFET, as shown in (18), where  $\tau_{\rm iss} = R_G (C_{\rm GS1} + C_{\rm GD1})$ . At this stage, the MOSFET is supporting low voltage; therefore,  $C_{\rm GS1}$  and  $C_{\rm GD1}$  are going to be used.

The MOSFET is still in conduction mode in this stage; therefore,  $I_D$  and  $V_{DS}$  are both kept at  $I_{DD}$  and  $V_{DD}$  respectively, and  $I_{CH}$  is kept at  $I_{DD}$

$$V_{\rm GS}(t) = V_{\rm GG} \cdot e^{-(t-t_0)/\tau_{\rm iss}}.$$

(18)

The end of this stage is set when  $V_{\text{GS}}$  reaches the level of the Miller Plateau,  $V_{\text{miller}}$ .

Stage 7  $(t_1 - t_2)$ : In this stage,  $V_{\rm DS}$  begins to increase, as stated by (19), not necessarily reaching  $V_{\rm FD}$  by the end of this stage. The duration of this stage is defined by the Miller Plateau time. This duration can be calculated by using (20)

$$V_{\rm DS}\left(t\right) = V_{\rm ds\_on} \cdot e^{-(t-t_1)/\gamma} \tag{19}$$

$$t_{\rm mp} = \frac{(R_{G\_ext} + R_{G\_int}) (V_{\rm FD} - V_{\rm ds\_on}) C_{\rm GD1}}{V_{\rm th}}.$$

(20)

During this time,  $I_D$  is still constant at  $I_{DD}$  level and  $V_{GS}$  is constant at  $V_{miller}$  voltage. Although the drain current is constant, the current going through the channel ( $I_{CH}$ ) starts to drop reaching the current plateau level ( $I_P$ ) and keeping this current during the whole duration of this stage.  $I_P$  is calculated as shown in (1). As for the drop of  $I_{CH}$ , it is calculated as shown in (21), taking into account that it is  $C_{GD}$  the capacitance that needs to be discharged through the channel of the MOSFET at this stage

$$I_{\rm CH}(t) = (I_P - I_{\rm DD}) e^{-(t-t_1)/(R_G C_{\rm GD1})} - I_P.$$

(21)

Stage 8  $(t_2 - t_3)$ : During this stage,  $V_{\text{DS}}$  will continue to increase until it reaches  $V_{\text{DD}}$ , meaning  $C_{\text{DS}2}$  and  $C_{\text{GD}2}$  are going to be used from this stage until the end of the turn-off.  $I_D$  will start to drop and it should reach zero before  $V_{\text{DD}}$  is reached

in an SJ MOSFET.  $I_{CH}$  will also drop and in this case with the same slope  $I_D$  drops until it reaches zero.

As it was done in stage 3, the moment in time when  $V_{\rm DS}$  reaches  $V_{\rm FD}$  will be defined as  $t_{2.5}$ . Thus,  $V_{\rm DS}$  will be defined by (19) until this value is reached and then  $V_{\rm DS}$  will follow (22) until it reaches  $V_{\rm DD}$ :

$$V_{\rm DS}(t) = V_{\rm FD} + \frac{(V_{\rm GG} - V_{\rm FD})}{R_G C_{\rm GD2}} (t - t_{2.5})$$

(22)

$$I_D(t) = g_{\rm fs} \left[ \frac{V_{\rm miller}}{(\tau_a - \tau_b)} (\tau_a (e^{-(t - t_1)/\tau_a}) - \tau_b (e^{-(t - t_1)/\tau_b})) - V_{\rm th} \right].$$

(23)

In this scenario,  $V_{\text{GS}}$  is constant at a lower level than the Miller Plateau that can be defined as  $V_{\text{Miller1}}$ , which is dependent of the IP previously calculated

$$V_{\rm miller1} = \frac{I_P}{g_{\rm fs}} + V_{\rm th}.$$

(24)

Stage 9  $(t_3 - t_4)$ : In SJ devices,  $I_D$  should be zero by the start of this stage due to *di/dts* being much higher than in planar MOSFET, thus implying that the MOSFET will not enter this stage and could be considered as part of stage 8.

Stage 10  $(t_4 - t_5)$ : In this final stage of the turn-off,  $V_{GS}$  will drop from  $V_{miller1}$  until it reaches zero while  $C_{OSS}$  is being discharged. As for  $V_{DS}$  and  $I_D$ , both remain constant at  $V_{DD}$ and zero, respectively. For the sake of completion, parasitic effects of the circuit can be used in order to add overshoot and ringing to the waveforms, as it was done in previous works [1]. It is important to note that these effects are not going to have a dramatic influence over the losses and they will improve the matching of the experimental and analytical waveforms to an extent

$$V_{\rm DS}(t) = V_{\rm DD} + V_{\rm max} \cdot e^{-\alpha(t-t_4)}$$

$$V_{\rm GS}(t) = \frac{V_{\rm miller1}}{\tau_a - \tau_b} (\tau_a (e^{-(t-t_4)/\tau_a}) - \tau_b (e^{-(t-t_4)/\tau_b}))$$

(26)

$$I_D(t) = -(C_{\text{GD2}} + C_{\text{DS2}}) \cdot V_{\text{max}} e^{-\alpha(t-t_4)} \cdot \omega$$

$$\cdot \sin(\omega(t-t_4)) + \alpha \cdot \cos(\omega(t-t_4))$$

(27)

$$\alpha = \frac{R_{G\_int}}{2 \cdot (L_s + L_d)}$$

(28)

$$\omega = \sqrt{\frac{1}{(C_{\rm GD2} + C_{\rm DS2})(L_d + L_s)} - \alpha^2}.$$

(29)

#### V. EXPERIMENTAL VALIDATION AND DISCUSSION

The experimental validation of the analytical model is carried out by means of a dc/dc buck converter where the device under test (DUT) is switched by a double pulse ( $V_{DD} = 100$  V and  $I_{DD} = 4$  A). In order to obtain the waveforms of the current through the DUT, a shunt resistor is placed in series to its source to measure the source current ( $I_S$ ). Moreover, voltage probes

TABLE II OPERATION CONDITIONS AND PCB INDUCTANCES

| Parameter          |       | Value |

|--------------------|-------|-------|

| R <sub>G_EXT</sub> | [Ω]   | 150   |

| $L_S$              | [nH]  | 16    |

| $L_D$              | [nH]  | 12    |

| $V_{G G}$          | [V]   | 12    |

| $V_{\rm DD}$       | [V]   | 100   |

| $I_{\rm DD}$       | [A]   | 3     |

| f                  | [kHz] | 100   |

TABLE III SJ MOSFET PARAMETERS IN THE ANALYTICAL MODEL

| Parameter          |             |      | MOSFE | T Sample | s      |

|--------------------|-------------|------|-------|----------|--------|

|                    |             | #1   | #2    | #3       | #4     |

| $C_{GD1}$          | [pF]        | 2000 | 2200  | 500      | 920    |

| $C_{\mathrm{GD2}}$ | [pF]        | 15   | 9.5   | 18       | 12     |

| $C_{GS}$           | [pF]        | 1500 | 2000  | 2000     | 1720   |

| $C_{\mathrm{DS1}}$ | [pF]        | 7000 | 6700  | 6500     | 29 000 |

| $C_{\mathrm{DS2}}$ | [pF]        | 70   | 60    | 70       | 65     |

| $V_{\rm FD}$       | [V]         | 47   | 24    | 28       | 8      |

| $R_{G \_INT}$      | $[\Omega]$  | 8.5  | 4     | 4        | 6.5    |

| gfs                | [S]         | 3    | 5     | 6.5      | 3      |

| R <sub>ds_on</sub> | $[m\Omega]$ | 170  | 150   | 140      | 150    |

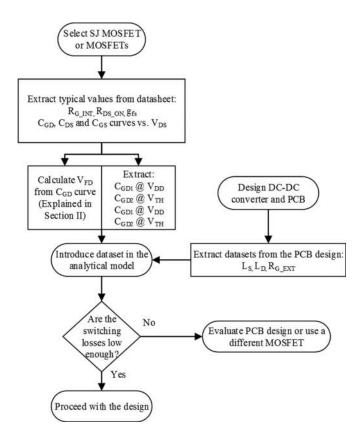

are placed to sense  $V_{\rm GS}$  and  $V_{\rm DS}$ . Even though diverse operation conditions were tested, the set of conditions in Table II is selected for the validation of the model. This selection is optimal with respect to the reduction of the current ringing as well as identification of  $V_{\rm FD}$ . There are also included in Table II the parasitic inductances of the PCB board, thus completing the dataset corresponding to the setup, that have been obtained by using finite element on the PCB design, as well as, adding the parasitic inductance from the TO-220 package. Aside from the data in Table II, a second group of data, summarized in Table III, is related to the electrical characteristics of the SJ MOSFET used as a DUT. These electrical characteristics are collected from the datasheet of SJ MOSFET for all the samples under analysis shown in Table III. Fig. 9 explains thoroughly the process it needs to be followed to extract the parameters correctly. Both datasets are the essential inputs that our analytical model requires. The model has been implemented in MATLAB in order to generate waveforms and to compute the dissipated powers in a time range of a few seconds.

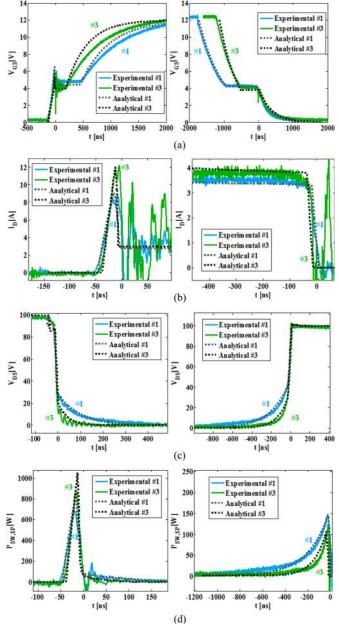

The waveforms calculated with the analytical model and measured in the test setup are compared in Fig. 10 for samples #1 and #3 which are the samples with more different switching waveforms for both transients, since sample #2 has similar waveforms to sample #1 and sample #3 has similar waveforms to sample #4. These waveforms correspond to the dynamic evolution of  $V_{\rm DS}$  [see Fig. 10(c)],  $V_{\rm GS}$  [see Fig. 10(a)] and  $I_D$ [see Fig. 10(b)] during turn-on and turn-off (considering the measured  $I_S$  equal to  $-I_D$ ). Furthermore, the instantaneous dissipated power ( $P_{\rm SW,SP}$ ), defined as  $V_{\rm DS}I_D$ , is represented in Fig. 10(d) to identify the position of the power peaks during

Fig. 9. Flowchart explaining the parameter extraction process for the analytical model.

the transients. It should be noted that the time scale differs in order to show the reliability of the analytical model during the transients.

By simple comparison of the waveforms, it can be seen that the analytical model is able to match the experimental waveforms with accuracy. The consideration of  $V_{\rm FD}$  helps greatly in this task in the case of  $V_{\rm DS}$ , and especially in  $V_{\rm GS}$ , improving the match between stage times and Miller plateau levels. In spite of this,  $I_D$  continues showing some discrepancies during the turn-on due to the modeling of the reverse recovery. In this sense, the value of *di/dt* matches but the reverse recovery peak introduces some error in the power loss calculation.

These waveforms are used in order to estimate the losses during the switching stage, formerly called  $P_{\rm SW}$ . The  $P_{\rm SW}$  calculation is done by integration of  $P_{\rm SW,SP}$  in Fig. 10(d), or by using the following equation:

$$P_{\rm sw} = f \int V_{\rm DS}\left(t\right) I_D\left(t\right) dt.$$

(30)

The intervals of integration are delimited by the start of  $V_{\rm DS}$  fall and the end of  $V_{\rm GS}$  raise, for  $P_{\rm SW,ON}$ , and by the start of the  $V_{\rm GS}$  fall and the end of the  $V_{\rm DS}$  raise, for  $P_{\rm SW,OFF}$  ( $P_{\rm SW} = P_{\rm SW,ON} + P_{\rm SW,OFF}$ ). Note that, at this point, the effect of the current diversion is not yet considered, due to the fact that it cannot be compared with experimental data.

After applying (30), all the analytical and measured  $P_{\rm SW,ON}$  and  $P_{\rm SW,OFF}$  are summarized in Table IV for samples #1, #3, and #4. A maximum of 21% error in a separated

Fig. 10. Comparison between measured (solid lines) and analytical (dotted lines) waveforms for (a)  $V_{\rm GS}$  (b)  $I_D$ , (c)  $V_{\rm DS}$ , and (d) the instantaneous dissipated power ( $P_{\rm SW,SP}$ ).

transient event is observed, which proves the good accuracy of the model. Even more, this percentage falls below the 20% when considering the error over  $P_{\rm SW}$ .

In a more advanced analysis of  $P_{SW}$ , the current diversion explained in Section III is considered by replacing (30) with (31) during the applicable time intervals

$$P_{\rm sw} = -f \int V_{\rm DS}\left(t\right) I_{\rm CH}\left(t\right) dt.$$

(31)

This modification is not expected to vary  $P_{\rm SW}$  but the distribution of power loss between  $P_{\rm SW,ON}$  and  $P_{\rm SW,OFF}$ . Before calculating the new power losses, the precision of the model in reproducing  $I_{\rm CH}$  is exemplified in Fig. 11 by comparing

TABLE IV SWITCHING POWER LOSS COMPARISON (CURRENT DIVERSION NOT INCLUDED)

|        |                      | Method         |                  |       |  |

|--------|----------------------|----------------|------------------|-------|--|

| Sample |                      | Analytical [W] | Experimental [W] | Error |  |

|        | P <sub>SW</sub> , on | 2.96           | 2.46             | +17%  |  |

| #1     | PSW.OFF              | 2.99           | 3.42             | -13%  |  |

|        | $P_{\rm SW}$         | 5.95           | 5.88             | +3%   |  |

|        | Psw,on               | 3.01           | 2.65             | +12%  |  |

| #2     | PSW, OFF             | 2.91           | 3.04             | -4%   |  |

|        | $P_{\rm SW}$         | 5.92           | 5.69             | +4%   |  |

|        | $P_{\rm SW,ON}$      | 2.29           | 1.99             | +13%  |  |

| #3     | PSW,OFF              | 1.38           | 1.09             | +21%  |  |

|        |                      | 3.08           | +16%             |       |  |

| #4     | $P_{\rm SW,ON}$      | 2.82           | 2.32             | +20%  |  |

|        | $P_{\rm SW,OFF}$     | 0.91           | 0.82             | +10%  |  |

|        | $P_{\rm SW}$         | 3.73           | 3.14             | +15%  |  |

Fig. 11. Comparison between simulated (solid lines) and analytical (dashed lines) current waveforms for  $I_{\rm CH}$  (black) and  $I_D$  (blue).  $R_{G\_\rm EXT}$  is (a) 150  $\Omega$  and (b) 10  $\Omega$ , whereas  $I_{\rm DD}$  is fixed to 4 A in all cases.

analytical with simulated waveforms. The simulated  $I_{\rm CH}$  and  $I_D$  waveforms in Fig. 11 correspond to a zoom of the curves in Fig. 6 for sample #4 with an  $R_{G\_\rm EXT}$  of 10 and 150  $\Omega$ . It is observed that, although  $I_P$  matches perfectly, the duration of the plateau is larger in the analytical curves. Subsequently, a second-order

TABLE VIMPACT OF CURRENT DIVERSION ON POWER LOSSES(SAMPLE #4,  $R_{G \perp EXT} = 150 \ \Omega$ )

|              | Withou                    | Without current diversion  |                        |                           | current diversi            | on                     |

|--------------|---------------------------|----------------------------|------------------------|---------------------------|----------------------------|------------------------|

|              | P <sub>SW,ON</sub><br>[W] | P <sub>SW,OFF</sub><br>[W] | P <sub>SW</sub><br>[W] | P <sub>SW,ON</sub><br>[W] | P <sub>SW,OFF</sub><br>[W] | P <sub>SW</sub><br>[W] |

| Experimental | 2.32                      | 0.82                       | 3.14                   | _                         | _                          | _                      |

| Mixed-Mode   | 2.53                      | 1.03                       | 3.56                   | 3.27                      | 0.29                       | 3.56                   |

| Analytical   | 2.82                      | 0.91                       | 3.73                   | 3.24                      | 0.49                       | 3.73                   |

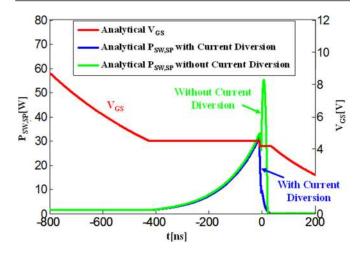

Fig. 12. Analytical  $P_{\rm SW,SP}$  versus time for the cases with and without current diversion. Analytical  $V_{\rm GS}$  is introduced as a reference to identify the Miller plateau. (Sample #4,  $R_{G\,\rm EXT} = 150~\Omega$ )

overestimation of  $P_{\rm SW,OFF}$  is expected. A comparison of waveforms during the turn-on is not presented because of the intricate current identification. As a matter of fact, the reverse recovery current flows from the power diode to the MOSFET, thus masking the displacement current. For practical reasons, the model does not recalculate  $I_{\rm CH}$  during the turn-on; it proceeds by directly adding the power loss reduction during the turn-off into the turn-off power loss.

The impact of the current diversion on the power losses is inferred from Table V for sample #4 with an  $R_{G\_EXT}$  of 150  $\Omega$ . Even though  $P_{SW}$  is preserved, both analytical and simulated methods show dissimilar  $P_{SW,ON}$  and  $P_{SW,OFF}$ . More precisely, the cases without current diversion underestimate  $P_{\rm SW,ON}$  by 25% and overestimate  $P_{\rm SW,OFF}$  by 200%. The origin of the new power distribution is understood by Fig. 12, where the analytical  $P_{SW,SP}$  for the cases with and without current diversion are compared. In the case without current diversion, a 30% of  $P_{SW,OFF}$  is added at the end of the Miller plateau during a short time (i.e., when the  $I_D V_{DS}$  crossing takes place during less than 50 ns). The fast plummeting of  $I_{\rm CH}$  with respect to  $I_D$  avoids the additional power loss when considering current diversion. This effect, evidenced in Fig. 10, results in a sort of zero-current switching (ZCS) at the turn-off. Another observation is the utter importance of the power dissipated during the Miller plateau ( $P_{SW,MP}$ ). For large  $R_{G\_EXT}$ ,  $P_{SW,MP}$  constitutes the larger part of  $P_{SW,OFF}$  and it is scarcely impacted by current diversion. Besides the well-known dependencies of  $P_{\rm SW,MP}$  with  $R_{G\_EXT}$  and  $Q_{\rm GD}$ , the effect of  $V_{\rm FD}$  is also included in the new model. Effectively, among other electrical parameters, a low  $V_{\rm FD}$  contributes in reducing  $P_{\rm SW,MP}$ . The current diversion effect can be of utter importance when using soft switching techniques, such as ZCS or zero-voltage switching where only one transient is removed.

Finally, it is important to note that testing of the analytical model has been done for different values of  $R_{G\_EXT}$  from a range of 10–150  $\Omega$  and compared to their respective experimental waveforms in order to validate the model. It was decided in the end to use the waveform comparison of 150  $\Omega$  in this study because they are more representative in order to visualize the different stages proposed in the analytical mode, even though a much smaller value is normally used in this kind of application.

## VI. CONCLUSION

A major breakthrough toward an accurate analytical model for high-voltage SJ MOSFETs is reported and experimentally proven in this paper. The nonlinear approximation of the capacitances, as well as the newly defined  $V_{\rm FD}$ , contributes to the accuracy of this model, proving the importance and the need of a good characterization of nonlinear parameters in analytical models. A first-order approach to the calculation of  $I_{\rm CH}$ by considering the current diversion effect is introduced for the first time in an analytical model. As forthcoming work, we expect to improve the compactness and precision of the model, as well as to extend testing the predictability of our model to other commercial SJ MOSFET and other circuit topologies.

#### REFERENCES

- W. Jianjing, S.-H. Henry, and R.T.-H. Li, "Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance" *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 573–590, Mar. 2013.

- [2] H. Raee, A. Rabiei, and T. Thirnger, "Analytical prediction of switching losses in MOSFETs for variable drain-source voltage and current applications," in *Proc. 8th IEEE Conf. Ind. Electron. Appl.*, 2013, pp. 705–709.

- [3] M. Rodriguez, A. Rodriguez, P. F. Miaja, D. G. Lamar, and J. S. Zúñiga, "An insight into the switching process of power MOSFET: An improved analytical loss model," *IEEE Trans. Power Electron.*, vol. 25, no. 6. pp. 1626–1640, Jun. 2010.

- [4] Y. Ren, M. Xu, J. Zhou, and F. C. Lee, "Analytical loss model of power MOSFET," *IEEE Trans. Power Electron.*, vol. 21, no. 2, pp. 310–319, Mar. 2006.

- [5] W. Eberle, Z. Zhang, Y.-F. Liu, and P. C. Sen, "A simple analytical switching loss model for buck voltage regulators," in *Proc. 23rd Ann. IEEE Appl. Power Electron. Conf. Expo.*, 2008, pp. 36–42.

- [6] M. Hartmann, M. Ertl, and J. W. Kolar, "On the tradeoff between input current quality and efficiency of high switching frequency PWM rectifiers" *IEEE Trans. Power Electron.*, vol. 27, no. 7, pp. 3137–3149, Jul. 2012.

- [7] D. Costinett, D. Maksimovic, and R. Zane, "Circuit-oriented treatment of nonlinear capacitances in switched-mode power supplies," *IEEE Trans. Power Electron.*, vol. 30, no. 2, pp. 985–995, Feb. 2015.

- [8] T. Meade, D. O'Sullivan, R. Foley, C. Achimescu, M.G. Egan, and P. McCloskey, "Parasitic inductance effect on switching losses for a high frequency dc-dc converter," in *Proc. Appl. Power Electron. Conf. Expo.*, 2008, pp. 3–9.

- [9] Z. J. Shen, Y. Xiong, X. Cheng, Y. Fu, and P. Kumar, "Power MOSFET switching loss analysis: A new insight," in *Proc. IEEE IAS Meeting*, Tampa, FL, USA, Oct. 2006, pp. 1438–1442.

- [10] V. Hoch, J. Petzoldt, H. Jacobs, A. Schlogl, and G. Deboy, "Determination of transient transistor capacitances of high voltage MOSFETs from dynamic measurements," in *Proc. 21st Int. Symp. Power Semicond. Devices ICs*, 2009, pp. 148–151.

[11] Sentaurus TCAD Tools Suite., Synopsys, Mountain View, CA, USA, 2010.

[12] M. Bobde, G. Lingpeng, A. Bhalla, F. Wang, and M. Ho, "Analyzing super-junction C-V to estimate charge imbalance," in *Proc. 22nd Int. Symp. Power Semicond. Devices & ICs*, Jun. 2010, pp. 321–324.

**Ignacio Castro** (S'14) was born in Gijón, Spain, in 1989. He received the M.Sc. degree in telecommunication engineering from the University of Oviedo, Gijón, Spain, in 2014, where he is currently working toward the Ph.D. degree.

His research interests include low and medium power dc–dc converters, modeling, simulation, and control of dc–dc converters, and power-factor correction of ac–dc converters.

Jaume Roig received the B.S. degree in physics and the Ph.D. degree in microelectronics engineering from Universitat Autnoma de Barcelona, Barcelona, Catalonia, Spain, in 1999 and 2004, respectively.

From 2000 to 2005, he was with the CNM/CSIC labs in Barcelona performing research in new device concepts for silicon-on-insulator smart power technologies. He joined LAAS/CNRS, Toulouse, France, in 2005, to continue his investigations in advanced power devices. In LAAS/CNRS, he collaborated with Freescale and STMicroelectronics in several projects.

He is with ON-Semiconductor, Oudenaarde, Belgium, in 2006, where he is currently working on the design and development of discrete and integrated semiconductor devices. He has authored and coauthored more than 100 scientific articles in international journals and conferences in the fields of power electronics, optoelectronics, nonvolatile memories, and multigate nanodevices.

Dr. Roig has four issued and eight pending patents and regularly serves as a Reviewer for numerous IEEE journals and conferences.

verters.

**Ratmir Gelagaev** (S'07) was born in 1983 in Grozny. He received the M.Sc. degree in electrotechnical engineering in 2007, from the Catholic University of Leuven (K. U. Leuven), Leuven, Belgium, where he is currently working toward the Ph.D. degree in electrotechnical engineering with the Research Group ELECTA, K. U. Leuven.

His research interests include high-frequency power electronics, measurement techniques, modeling of active and passive components, and design and multiobjective optimization of power electronic con-

**Basil Vlachakis** was born in Johannesburg, South Africa, in 1965. He received the National High Diploma degree in electrical engineering light current from the Technikon Witwatersrand, Johannesburg, South Africa, in 1990, and a Professional Bachelor degree in information technology in 2005.

He joined Mietec microelectronics, Belgium, in 1991, which later became Alcatel Microelectronic, followed by AMI and is currently with ON Semiconductors, Oudenaarde, Belgium. He has 20 years of experience in a R&D characterization lab and at present actively involved in GaN and power MOSFET development.

Filip Bauwens received the M.Sc. degree in applied physics and the Ph.D. degree in nuclear physics from the University of Gent, Gent, Belgium, in 1995 and 2000, respectively.

In 2001, he joined ON Semiconductor, Oudenaarde, Belgium. He manages a team of five device engineers that are mainly involved in the prestudy of new smart power technologies and discrete power devices, including process specification and assessment of electrical and degradation behavior and their role in the application, and more detailed TCAD studies.

He is author or co-author of more than 20 international journal papers or conference proceedings and has been awarded several patents.

Johan Driesen (S'93–M'97–SM'12) was born in Belgium, in 1973. He received the M.Sc. degree in electrotechnical engineering and the Ph.D. degree in electrical engineering from the K. U. Leuven, Leuven, Belgium, in 1996 and 2000, respectively. His Ph.D. dissertation was focused on the finite-element solution of coupled thermal–electromagnetic problems and related applications in electrical machines and drives, microsystems, and power quality issues. From 2000 to 2001, he was a Visiting Researcher

with the Imperial College of Science, Technology,

and Medicine, London, U.K., and then was with the University of California, Berkeley, USA. He is currently a Full Professor with the K. U. Leuven where he teaches power electronics, renewables, and drives. He conducts research on distributed energy resources, including renewable energy systems and power electronics and its applications, for instance in renewable energy and electric vehicles.

**Diego G. Lamar** (M'08) was born in Zaragoza, Spain, in 1974. He received the M.Sc. and Ph.D. degrees in electrical engineering from the University of Oviedo, Oviedo, Spain, in 2003 and 2008, respectively.

He was a Research Engineer and an Assistant Professor with the University of Oviedo, Oviedo, Asturias, Spain, in 2003 and 2005, respectively, and has been an Associate Professor, since September 2011. His research interests include switching-mode power supplies, converter modeling, and power-

factor-correction converters.