Missouri University of Science and Technology Scholars' Mine

Electrical and Computer Engineering Faculty Research & Creative Works

**Electrical and Computer Engineering**

01 Jan 2003

### Application of the Cavity Model to Lossy Power-Return Plane Structures in Printed Circuit Boards

Minjia Xu

Hao Wang

Todd H. Hubing Missouri University of Science and Technology

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electrical and Computer Engineering Commons

### **Recommended Citation**

M. Xu et al., "Application of the Cavity Model to Lossy Power-Return Plane Structures in Printed Circuit Boards," *IEEE Transactions on Advanced Packaging*, Institute of Electrical and Electronics Engineers (IEEE), Jan 2003.

The definitive version is available at https://doi.org/10.1109/TADVP.2003.811552

This Article - Journal is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# Application of the Cavity Model to Lossy Power-Return Plane Structures in Printed Circuit Boards

Minjia Xu, Member, IEEE, Hao Wang, Member, IEEE, and Todd H. Hubing, Senior Member, IEEE

Abstract—Power-return plane pairs in printed circuit boards are often modeled as resonant cavities. Cavity models can be used to calculate transfer impedance parameters used to predict levels of power bus noise. Techniques for applying the cavity model to lossy printed circuit board geometries rely on a low-loss assumption in their derivations. Boards that have been designed to damp power bus resonances (e.g., boards with embedded capacitance) generally violate this low-loss assumption. This paper investigates the validity of the cavity model when applied to printed circuit board structures where the board resonances are significantly damped. Cavity modeling results for sample lossy power-return plane structures are validated using a three-dimensional full wave numerical code. A simple method is also established to check the validity of the cavity model for a power-return plane structure with imperfect conductors and lossy dielectric substrates.

*Index Terms*—Cavity theory, conductive loss, dielectric loss, embedded capacitance, model validation, power bus impedance, power bus modeling, power plane, propagation constant, return plane.

#### I. INTRODUCTION

WITH operational frequencies exceeding 1 GHz and working voltages continuing to decrease in high-speed digital products, power bus design and modeling are becoming more critical. Transient noise voltage due to sudden surges of the current drawn by active devices from the power bus can cause excessive delays, false switching, and other signal integrity problems. This noise voltage can also drive the printed circuit board and any attached cables resulting in radiated electromagnetic interference (EMI). In order to develop a systematic power bus design strategy, the fundamental properties of power bus structures commonly used in current high-speed products need to be explored.

Multilayer printed circuit boards (PCBs) and multichip modules (MCMs) often employ solid power-return plane pairs for power distribution. At low frequencies, the behavior of a powerreturn plane pair can be described by a lumped-element model [1]. At frequencies where the dimensions of the board are not electrically small, it is necessary to use complex distributed models. General full wave numerical methods such as FDTD,

M. Xu is with Hewlett-Packard, San Diego, CA 92127-1801 USA.

Digital Object Identifier 10.1109/TADVP.2003.811552

FEM, MoM, and PEEC have been applied to model PCBs and MCMs with power-return plane pairs successfully. However, these models are relatively complex, and they require a significant amount of time and expertise to implement properly.

Several investigators have used a resonant cavity model to characterize power-return plane structures [2]–[8]. Compared to full wave numerical modeling techniques, the cavity model is relatively simple and computationally efficient. Using the cavity model, the transfer impedance between any two locations on a power-return plane pair is expressed as a double infinite sum where each term corresponds to an eigenmode of the cavity. Equivalent circuits for the power-return plane structure can then be extracted and utilized in simulations of PCBs and MCMs involving power-return plane pairs. A populated printed circuit board can be modeled as a multi-port circuit network where components and devices are interconnected by an impedance matrix representing the power-return plane pair of the board [6], [7]. The cavity model has also been extended to analyze PCBs and MCMs with multiple solid planes in [8].

Previous research has demonstrated that the input and transfer impedance of a low-loss power-return plane structure can be approximately determined by the double infinite series expressions as long as the wave number in the expressions is replaced by a complex propagation constant, which incorporates the dielectric and conductive losses in the structure [5]-[8]. Okoshi derived the complex propagation constant by summing the attenuation constant due to the dielectric loss and the attenuation constant due to the conductive loss in a rectangular parallel plane structure [3]. Ramo derived the complex propagation constant by solving for the field distribution in a parallel plate transmission line [9]. Both derivations assumed a low-loss parallel plate structure composed of good conductors and good dielectric materials. Though it is commonly believed that the cavity model should not be used to analyze high-loss structures, the exact prerequisites for the validity of the cavity model have not been clearly established.

Embedded capacitance technology uses ultra-thin power-return plane pairs for power distribution [10]. Recent research has shown that embedded capacitance is a promising alternative to discrete decoupling capacitors for reducing power bus noise [11]. In particular, test boards with very thin (e.g., <10  $\mu$ m) dielectric materials were found to be the most effective in reducing power bus noise and radiated EMI [12].

This paper studies the validity of the cavity model for powerreturn plane structures with ultra-thin dielectric substrates that aren't necessarily low-loss, such as those used in embedded

Manuscript received December 1, 2002; revised March 6, 2003.

H. Wang is with Advanced Systems Research Laboratory, Micron Technology, Boise, ID, 83706 USA.

T. Hubing is with the Department of Electrical and Computer Engineering, University of Missouri-Rolla, Rolla, MO 65409 USA.

$\mathbf{Z}$

capacitance boards. Board resonances in these structures are significantly damped or essentially eliminated either by conductive losses in the planes or by dielectric losses in the substrates. A new method is proposed to calculate the complex propagation constant that incorporates these dielectric and conductive losses. Using this complex propagation constant, the cavity model can be adapted to power-return plane structures with imperfect dielectric substrates and imperfect conductors. The modeling results for sample lossy structures are corroborated by a three-dimensional (3-D) full-wave numerical code [13]. A simple method is proposed to check whether a power-return plane structure can be accurately modeled as a cavity. The validity of the cavity model for power-return plane structures with typical embedded capacitance materials is examined using this method.

#### II. CAVITY MODEL FOR POWER-RETURN PLANE PAIRS

When the spacing between the two solid planes is electrically thin, a rectangular power-return plane pair can be modeled as a  $TM_z$  cavity with two perfect electric conductor (PEC) walls and four perfect magnetic conductor (PMC) sidewalls. The input and transfer impedance of the power-return plane pair can be obtained using a mode-expansion method resulting in

$$Z_{ij} = j\omega\mu h \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} \frac{\chi_{mn}^2}{ab \left(k_{xm}^2 + k_{yn}^2 - k^2\right)} \\ \times \cos(k_{yn}y_i) \cos(k_{xm}x_i) \operatorname{sinc}\left(\frac{k_{yn}dy_i}{2}\right) \\ \times \operatorname{sinc}\left(\frac{k_{xm}dx_i}{2}\right) \times \cos(k_{yn}y_j) \cos(k_{xm}x_j) \\ \times \operatorname{sinc}\left(\frac{k_{yn}dy_j}{2}\right) \operatorname{sinc}\left(\frac{k_{xm}dx_j}{2}\right)$$

(1)

where a, b are dimensions of the board.  $k_{xm} = m\pi/a, k_{yn} = n\pi/b, k = \omega\sqrt{\varepsilon_0\varepsilon_r\mu}$ .  $\chi^2_{mn} = 1$  for m = n = 0;  $\chi^2_{mn} = 2$  for m = 0 or n = 0;  $\chi^2_{mn} = 4$  for  $m \neq 0, n \neq 0$  [3], [5], [14]. In (1), h is the spacing between two planes.  $(x_i, y_i)$  and  $(x_j, y_j)$  are the coordinates of the source and the observation ports, respectively.  $(dx_i, dy_i)$  and  $(dx_j, dx_j)$  are the dimensions of these ports. The dimensions of the ports must be small compared to a wavelength at the highest frequency of interest.

Equation (1) assumes that the structure is lossless. However, power-return plane pairs in real printed circuit boards exhibit losses due to the finite resistance of the copper walls, loss in the dielectric, radiation loss, losses due to surface waves induced on the outer surface of the copper, and losses due to the power dissipated in the components. Conductive and dielectric losses are generally more prominent than the radiation loss and the surface wave loss. To calculate the impedance of an unpopulated power-return plane pair, the real wave number,  $\mathbf{k}$ , in (1) has to be modified to incorporate the dielectric and conductive losses in the structure. Several investigators have proposed to replace  $\mathbf{k}$  with a complex wave number given by

$$K = \beta - j\alpha = k \left( 1 - j \frac{\tan \delta + (\delta_s/h)}{2} \right)$$

(2)

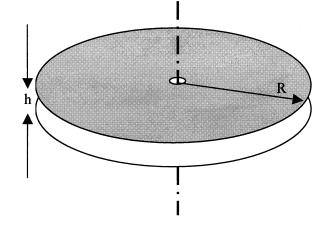

Fig. 1. Geometry of the circular parallel plate structure with a  ${\cal Z}$  directional feed.

where  $\tan \delta$  is the loss tangent of the dielectric substrate and  $\delta_s$  is the skin depth of the plane conductors [3], [5]. This model accounts for the attenuation but neglects any changes to the phase constant  $\beta$  caused by the nonideal conductor and dielectric substrate. The overall attenuation factor,  $\alpha$ , is calculated by summing the attenuation factor due to the dielectric loss with the attenuation factor due to the conductive loss.

Another method to modify the cavity model is to replace the real wave number with a complex propagation constant  $\gamma$ . An expression for  $\gamma$  can be obtained using a lumped-element model of a radial transmission line. As illustrated in Fig. 1, the two circular planes with the same radius R are separated by a thin layer of dielectric substrate with thickness equal to h. The structure is excited by a current source at its geometric center. The cross-section of the coaxial current feed is represented by an electrically small circle of radius  $r_0$ . When the spacing between the two planes is electrically small, the only modes that this structure can support are radial transmission line modes with no field variation in the Z or  $\Phi$  directions. For a lossless circular power-return plane pair, only the  $E_z$  and  $H_{\Phi}$  components are nonzero [9]. Due to the unique characteristics of the field components in radial transmission lines, the circular parallel plate structure can be modeled as a transmission line with per-unit-length inductance and capacitance that vary with the distance from the center [15]

$$L(r) = \frac{\mu h}{2\pi r}, \qquad C(r) = \frac{2\pi\varepsilon r}{h}.$$

(3)

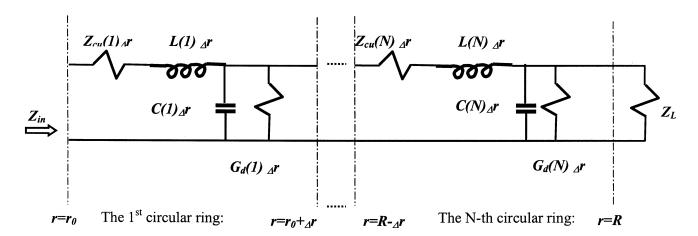

The circular parallel plane structure made of imperfect conductors and an imperfect dielectric substrate is discretized into an array of circular rings with the same width,  $\Delta \mathbf{r}$ . If  $\Delta \mathbf{r}$  is electrically small, each circular ring represents a short piece of the radial transmission line. Consequently, the circular parallel plate structure can be modeled by an array of lumped-element circuits as shown in Fig. 2. The per-unit-length inductance and capacitance are given in (3). The effect of the imperfect dielectric substrate is represented by the per-unit-length shunt conductance

Fig. 2. Lumped-element model for lossy circular parallel plates.

$G_d$  that varies with the radius.  $G_d$  can be expressed in terms of the loss tangent of the dielectric material as

$$G_d(r) = \frac{2\pi r}{h} \,\omega\varepsilon \tan \delta. \tag{4}$$

The effect of the imperfect conductor is represented by the per-unit-length series impedance  $Z_{cu}$ . For typical power-return plane structures in printed circuit boards, the dc resistance can be safely neglected above a couple of megahertz when compared to the skin-effect losses. If both planes are made of good conductors and the thickness of the planes is much greater than a skin depth, then  $Z_{cu}$  can be expressed in terms of the surface impedance of the conductor on the planes as

$$Z_{cu}(r) = \frac{Z_s}{\pi r} \tag{5}$$

where  $Z_s$  is the surface impedance given by

$$Z_s = (1+j)/\sigma\delta_s.$$

(6)

In (6),  $\sigma$  is the conductivity of the planes. The complex propagation constant  $\gamma$  can be calculated from the lumped-element circuit model as

$$\gamma = \sqrt{(Z_{cu} + j\omega L)(G_d + j\omega C)}.$$

(7)

Substituting the expressions for  $L, C, Z_{cu}$  and  $G_d$  from (3)–(6) into (7) yields

$$\gamma = j\omega\sqrt{\varepsilon\mu}\sqrt{\left(1 - \frac{j(1+j)\delta_s}{h}\right)(1-j\tan\delta)}.$$

(8)

If the dielectric substrate is low loss, and the spacing between the two planes is much thicker than the skin depth of the conductor on each plane, (8) can be approximated by the first two terms of its binomial expansion as

$$\gamma = \alpha + j\beta = k \frac{\tan \delta + \frac{\delta_s}{h}}{2} + jk\left(1 + 2\frac{\delta_s}{h}\right).$$

(9)

Notice that the attenuation factor given in (9) is identical to the attenuation factor in (2).

The expression for the complex propagation constant given in (8) depends on the frequency, the spacing between the two planes, and the material parameters. It is independent of the location, shape, and dimensions of the feed port. In addition, it is independent of the size and the shape of each conducting plane. In other words, although it was derived using a radial transmission line model, the expression can be applied to electrically thin parallel plane structures of arbitrary shapes with arbitrary excitations.

Applying the same mode-expansion procedure as we did for the lossless rectangular power-return plane structures while replacing the wave number with the complex propagation constant, the input and the transfer impedance of a power-return plane pair with imperfect dielectric and imperfect conductors can be expressed as

$$Z_{ij} = j\omega\mu\hbar \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} \frac{\chi_{mn}^2}{ab\left(k_{xm}^2 + k_{yn}^2 + \gamma^2\right)} \\ \times \cos(k_{yn}y_i)\cos(k_{xm}x_i)\operatorname{sinc}\left(\frac{k_{yn}dy_i}{2}\right) \\ \times \operatorname{sinc}\left(\frac{k_{xm}dx_i}{2}\right) \times \cos(k_{yn}y_j)\cos(k_{xm}x_j) \\ \times \operatorname{sinc}\left(\frac{k_{yn}dy_j}{2}\right)\operatorname{sinc}\left(\frac{k_{xm}dx_j}{2}\right).$$

(10)

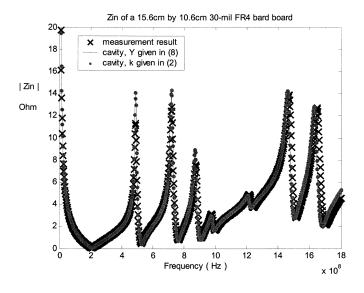

To validate the cavity model, the input impedance of a 15.6-cm by 10.6-cm double-sided FR4 board was calculated with the wave number given in (2) and the complex propagation constant given in (8), respectively. The dielectric layer between the two solid planes was 30 mils thick with a relative permittivity equal to 3.86. The loss tangent of the FR4 dielectric (according to the manufacturer) was 0.019 around 1 GHz. The board was fed by an SMA connector at location (4.6 cm, 2.6 cm). The radius of the center conductor for the SMA connector was 30 mils. The input impedance of this board was measured using an HP4291A impedance analyzer from 1 MHz to 1.8 GHz. The cavity model estimate for the magnitude of the input impedance using (2) and (8) agreed pretty well with the measurement as indicated in Fig. 3 [16]. At the cavity resonance frequencies, the calculated resonant peaks were slightly higher than the measurement results. This difference may have been due to the frequency-dependent character of the loss tangent or the PMC boundary assumption in the cavity model, which neglected the fringing field at the board edges.

10

6

5

O EMAP5

×

cavity, Y given in (8)

cavity, k given in (2)

| Zin |

(Ohm)

7.6 cm by 5.1 cm, er=4.0, Itan=0.5, con=5.8e7, h=20 mils

Fig. 3. Input impedance of a 30-mil thick 15.6-cm by 10.6-cm double-side FR4 test board fed by an SMA jack at location (4.6 cm, 2.6 cm): measurement versus lossy cavity modeling results.

### III. APPLICATION OF THE CAVITY MODEL TO LOSSY POWER-RETURN STRUCTURES

# A. Power-Return Plane Structures with Lossy Dielectric Materials

In the derivation of the complex propagation constant given in (8) and the impedance expression for a power-return plane pair with imperfect conductors and imperfect dielectric substrate given in (10), we have made the following assumptions.

- 1) The substrate between two planes is electrically thin so there is no field variation in the vertical direction within the dielectric region.

- The two planes are made of good conductors so that the conduction current is much greater than the displacement current within the conductor regions.

- 3) Each plane is much thicker than the skin depth of the conductor.

The resulting expression for the complex propagation constant given in (8) is identical to the expression given by Ramo in [9]. However, the derivation of (8) in Section II does not put specific limitations on the loss-tangent of the dielectric.

To check the validity of the cavity model for power-return plane pairs with lossy dielectric substrates, a 3-D hybrid FEM/MoM numerical code, EMAP5, is used to corroborate the input impedance calculated by expression (10). The details of the formulation and a description of EMAP5 can be found in [17]. In EMAP5, the source is generally modeled as a flat current strip. While in the cavity model, it is more convenient to treat the current source as a rectangular feed port. For a rectangular microstrip patch structure, an electrically small current strip of width w can be replaced by a cylindrical current source of radius equal to one-fourth of w [18]. Furthermore, it is suggested that for a rectangular power-return plane structure, a coaxial feed can be represented by a square port whose effective cross section is equal to the area of the circular feed port [19]. According to these relations, the current strip source of width  $\boldsymbol{w}$  centered at  $(x_i, y_i)$  used in EMAP5 is equivalent

Fig. 4. Input Impedance of a 20-mil 7.6-cm by 5.1-cm board with lossy dielectric substrate.

to a square current feed port with each side equal to 0.443 w in the cavity model.

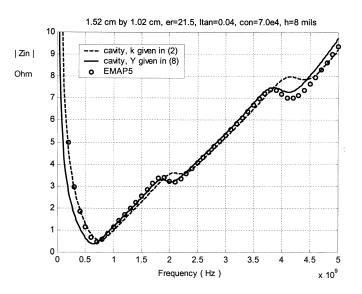

The input impedance of a 7.6-cm by 5.1-cm board was calculated by EMAP5 and the cavity model with the complex wave number given in (2) and the complex propagation constant given in (8), respectively. The dielectric substrate between the two copper planes was 20 mils thick with a relative permittivity equal to 4.0 and a loss tangent equal to 0.5. In EMAP5, the source was modeled as an 8-mil wide current strip that was parallel to the length of the board and centered at (2.8 cm, 2.6 cm). In the cavity model, the feed port was modeled as a square centered at the same location with each side equal to 3.545 mils. The calculated input impedance results are plotted in Fig. 4. Due to the high dielectric loss tangent of the substrate, the board resonances were essentially eliminated as indicated by all three curves in Fig. 4. The cavity model results agree nicely with the EMAP5 results up to 3 GHz. This demonstrates that the cavity model is valid for this power-return plane pair despite the very lossy dielectric substrate.

# *B. Ultra-Thin Power-Return Plane Structures in Embedded Capacitance Boards*

Besides the dielectric loss, the losses in the conductors on both planes can also significantly damp or even eliminate resonances in a power-return plane pair. For example, embedded capacitance boards generally employ ultra-thin power-return plane pairs to greatly enhance the board capacitance. It was found that the conductive loss in the planes is normally the dominant loss mechanism in these ultra-thin power-return plane structures. In fact, when the spacing between the two planes is on the order of a skin depth in the plane conductor, conductive losses alone can significantly damp or essentially eliminate board resonances [16].

As shown in Section II, the finite conductivity of the conductor on the planes affects both the real and the imaginary part of the complex propagation constant. By using the complex propagation constant given in (8) instead of the approximation given in (9), the impedance expression resulting from the cavity

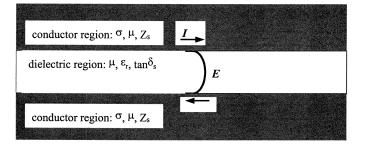

Fig. 5. Field pattern inside the dielectric substrate of a power-return plane pair with imperfect conductors.

model does not require the spacing between the planes to be much thicker than the skin depth of the plane conductors.

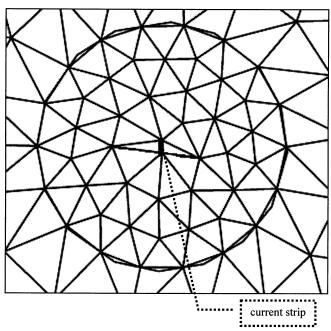

The 3-D full wave numerical code EMAP5 was used to validate the cavity model for ultra-thin power-return plane structures. The hypothetical board used for this study was 1.52-cm by 1.02-cm with two graphite planes. It was necessary to reduce the size of the board and exaggerate the loss in the planes in order to apply the full-wave model. These two planes were separated by an 8-mil layer of embedded capacitance material with a relative permittivity equal to 21.5 and a loss tangent equal to 0.04. With a conductivity of  $7.0 \times 10^4$  S/m for the graphite planes, the 8-mil spacing was less than six skin-depths at 3 GHz. The presence of the imperfect conductor planes created a finite tangential electric field,  $E_T$ , corresponding to the current flowing along the conductor. Consequently, the overall electric field at the boundary between the conductor and the dielectric substrate was no longer perpendicular to the conducting planes as illustrated in Fig. 5. In order to model this variation of the tangential electric field in the vertical direction, the dielectric substrate was divided into 3 layers and meshed into 20 600 tetrahedrons in the EMAP5 solution. The power and the return planes were discretized into 3732 triangular patches. The source was modeled as a 0.5-mil wide current strip parallel to the length of the board and centered at (0.56 cm, 0.52 cm). Fig. 6 illustrates the mesh employed around the current strip used in EMAP5. In the cavity model, the feed port was modeled as a square centered at the same location with each side equal to 0.2215 mils. Fig. 7 plots the input impedance calculated by EMAP5 as well as by the original cavity model with the complex wave number given in (2) and the lossy cavity model with the complex propagation constant given in (8). In all three curves, board resonances are significantly damped due to the conductive losses in both planes. Compared with the 3-D full wave modeling results, the curve generated by the cavity model with the complex wave number given in (2) was inaccurate near resonance frequencies. The cavity modeling results using the propagation constant given in (8) were in close agreement with the EMAP5 results.

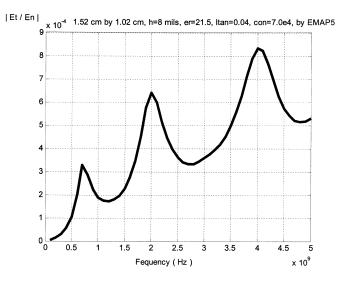

Using the data from EMAP5, the ratio of the tangential to the normal electric field at the boundary between the power plane and the dielectric substrate was calculated for the 8-mil board with graphite planes. Fig. 8 plots the magnitude of  $E_T/E_N$  as a function of frequency at one end of the current strip located at (0.5594 cm, 0.52 cm). The ratio reaches its maximum around

Fig. 6. EMAP5 mesh around the current strip source of the 8-mil 1.52-cm by 1.02-cm board made from graphite and embedded capacitance material.

Fig. 7. Input Impedance of an 8-mil 1.52-cm by 1.02-cm board made from graphite and embedded capacitance material.

700 MHz, 2 GHz, and 4 GHz corresponding to the nulls of the calculated input impedance shown in Fig. 7. Even at these frequencies, the magnitudes of the tangential electric field are trivial compared to the magnitudes of the normal electric field. At the boundary between the power plane and the dielectric substrate, the overall electric field was still nearly perpendicular to the plane. The field pattern only deviates slightly from the ideal field pattern supported by a structure made of perfect conducting planes. As a result, this board can still be safely approximated as a TM<sub>z</sub> cavity, and good agreement between the impedance calculated by the cavity model and the full wave modeling code should be expected.

Fig. 8. Ratio of the tangential to the normal electric field around the current source for an 8-mil 1.52-cm by 1.02-cm board made from graphite and embedded capacitance material.

### C. Validity of the Cavity Model for Lossy Power-Return Plane Structures

For cavity resonators with imperfect conductors and lossy dielectric materials, the ratio of the tangential to the normal electric field at any point is a complex function of the location due to the boundary conditions imposed at the sidewalls. To evaluate the impact of the finite conductivity on the field pattern, it is convenient to view a power-return plane pair as a closed section of a parallel plate waveguide. For a parallel plate waveguide, the ratio of the tangential to the normal electric field at the boundary between the power plane and the dielectric substrate (denoted as  $\rho$  in following discussion) can be calculated from a rigorous field solution in the structure. This ratio can be used as an indication of how far the field pattern deviates from the TEM mode supported by a parallel plate waveguide with perfect conducting planes. It can also be used to determine whether a power-return plane pair constructed by enclosing a section of the waveguide with PMC sidewalls can be modeled as a  $TM_z$  cavity.

Assuming each plane of a parallel plate waveguide is a good conductor and the plane is much thicker than the skin depth of the conductor, the tangential electric and magnetic field at the surface of the conducting planes is related by the surface impedance of the conductor as

$$E_{TC} = Z_s H_{TC}.$$

(11)

At any point inside the dielectric substrate, the normal electric field and the tangential magnetic field are related by

$$E_{ND} = \frac{\gamma}{j\omega\varepsilon_d} H_{TD} \tag{12}$$

where  $\varepsilon_d$  is the complex permittivity of the dielectric material given by

$$\varepsilon_d = \varepsilon_0 \varepsilon_r \left( 1 - j \tan \delta \right). \tag{13}$$

TABLE I

Embedded Capacitance Materials Evaluated in the Study

| Material | Thickness | ε,   | tan <b>δ</b> |

|----------|-----------|------|--------------|

| EC#1     | 2.1 mils  | 3.88 | 0.021        |

| EC#2     | 4.0 mils  | 36.4 | 0.013        |

| EC#3     | 1.4 mils  | 11.8 | 0.01         |

| EC#4     | 0.2 mils  | 21.1 | 0.081        |

At the boundary between the power plane and the dielectric substrate, the boundary conditions require that the tangential field components be continuous across the boundary

$$H_{TC} = H_{TD}, \qquad E_{TC} = E_{TD} = E_T. \tag{14}$$

So the ratio of the tangential to the normal electric field at the boundary between the power plane and the dielectric substrate,  $\rho$ , can be found as

$$\rho = \frac{E_T}{E_{ND}} = \frac{j\omega\varepsilon_d Z_s}{\gamma}.$$

(15)

Substituting (8) and (14) into (15) yields

$$\rho = \frac{Z_s}{\eta_d \sqrt{1 - \frac{j(1+j)\delta_s}{h}}} \tag{16}$$

where

$$\eta_d = \sqrt{\frac{\mu}{\varepsilon_0 \varepsilon_r \left(1 - j \tan \delta\right)}}$$

is the intrinsic impedance of the lossy dielectric material.

According to (16), no matter how lossy the dielectric substrate is,  $\rho$  is zero for a parallel plate waveguide made with perfect conductors. When the planes are not perfect conductors,  $\rho$ is a function of the surface impedance of the conductor, the intrinsic impedance of the dielectric substrate, and the ratio of the spacing between the planes to the skin-depth of the conductor. For boards where  $h \gg \delta_s$

$$\rho \approx Z_s / \eta_d. \tag{17}$$

Equation (17) indicates that the magnitude of  $\rho$  is proportional to the surface impedance in these relatively wide structures. For ultra-thin power-return plane structures where  $h \ll \delta_s$

$$\rho \propto \sqrt{h/\delta_s}.$$

(18)

The magnitude of  $\rho$  actually decreases with decreasing plane spacing. In general, for two power-return plane structures made of the same conductor and dielectric substrate, the field pattern in the thinner board has a smaller deviation from the rigorous TEM mode than the field pattern in the thicker board.

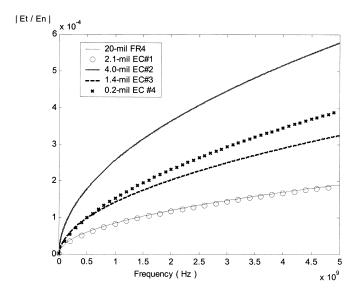

The ratio of the tangential to the normal electric field was calculated for parallel plane structures employing four commercially available embedded capacitance materials. These materials are listed in Table I. The relative permittivity and the loss tangent values were measured by the National Institute of Standards and Technology (NIST) around 1 GHz

Fig. 9. Magnitude of the tangential to the normal electric field ratio for parallel plane structures with embedded capacitance materials.

[12]. Assuming the power and the ground planes are made of copper and the effective conductivity is approximately  $3.0 \times 10^7$  ohms/m, the magnitude of  $\rho$  was calculated for each embedded capacitance structure as well as for a 20-mil spacing power-return plane pair with FR4 material ( $\varepsilon_r = 3.92$ ,  $\tan \delta = 0.021$  around 1 GHz). The results are plotted in Fig. 9. For all four types of embedded capacitance materials, the ratio of the tangential to the normal electric field at the boundary between the power plane and the dielectric substrate is well below  $10^{-3}$  up to 5 GHz.

### **IV. CONCLUSION**

A simple cavity model was used to characterize power-return plane structures where the board resonances are significantly damped or essentially eliminated due to dielectric losses or conductive losses. For power-return plane structures with imperfect conductor and imperfect dielectric substrates, the impedance expression must be modified by replacing the real-valued wave number with a complex propagation constant that incorporates the dielectric and conductive losses. The complex propagation constant for a parallel plate structure can be derived from the lumped-element circuit of a radial transmission line without specific limitations on the thickness and the loss tangent of the dielectric substrate. With this complex propagation constant, the cavity model can be applied to the lossy power-return plane structures that are found in boards employing embedded capacitance.

#### REFERENCES

T. H. Hubing, J. L. Drewniak, T. P. Van Doren, and D. M. Hockanson, "Power bus decoupling on multiplayer printed circuit boards," *IEEE Trans. Electromagn. Compat.*, vol. 37, pp. 155–166, May 1995.

- [2] Y. T. Lo, D. Solomon, and W. F. Richards, "Theory and experiment on microstrip antennas," *IEEE Trans. Antennas Propagat.*, vol. 27, pp. 137–145, Mar. 1979.

- [3] T. Okoshi, *Planar Circuits for Microwaves and Lightwaves*. New York: Springer-Verlag, 1985, ch. 2.

- [4] I. Novak, "Reducing simultaneous switching noise and EMI on ground/power planes by dissipative edge termination," *IEEE Trans. Adv. Packag.*, vol. 22, pp. 274–283, Aug. 1999.

- [5] G. T. Lei, R. W. Techentin, and B. K. Gilbert, "High-frequency characterization of power/ground-plane structures," *IEEE Trans. Microwave Theory Tech.*, vol. 47, pp. 562–569, May 1999.

- [6] O. Wada, Z. L. Wang, Y. Toyota, and R. Koga, "Local decoupling effects of decoupling capacitors on a multilayer PCB: Fast analysis by a closed-form expression," IEICE Tech. Rep. EMCJ2000-115, vol. 100, Dec. 2000.

- [7] X. Yang, Z. Li, and J. Mao, "Analysis of the bounces on the power/ground plane structures by planar circuit model and APA-E algorithm," *IEEE Trans. Adv. Packag.*, vol. 24, pp. 184–190, May 2001.

- [8] S. Chun, M. Swaminathan, L. D. Smith, J. Srinivasan, J. Zhang, and M. K. Iye, "Modeling of simultaneous switching noise in high speed systems," *IEEE Trans. Adv. Packag.*, vol. 24, pp. 132–142, May 2001.

- [9] S. Ramo and J. R. Whinnery, *Fields and Waves in Modern Radio*, 2nd ed. New York: Wiley, 1953, ch. 8 and 9.

- [10] J. Sisler, "Eliminating capacitors from multi-layer PCBs," *Printed Circuit Design*, vol. 8, no. 7, pp. 14–23, Jul. 1991.

- [11] M. Xu, T. H. Hubing, J. Chen, T. P. Van Doren, J. L. Drewniak, and R. E. DuBroff, "Power bus decoupling with embedded capacitance in printed circuit board design," IEEE Trans. Electromagn. Compat., submitted for publication.

- [12] "Embedded Decoupling Capacitance (EDC) project—Final report," National Center for Manufacturing Sciences, 3025 Boardwalk, Ann Arbor, MI 48 108-3266, NCMS Report 0091RE00, Dec. 2000.

- [13] Y. Ji and T. H. Hubing, "EMAP5: A 3-D hybrid FEM/MoM code," Appl. Computat. Electromagn. Soc. J., vol. 15, no. 1, pp. 1–12, Mar. 2000.

- [14] J. Helszajn, Green's Function, Finite Elements and Microwave Planar Circuits. New York: Wiley, 1996, ch. 5.

- [15] J. C. Packer, Jr., "Via coupling with parallel rectangular planes," *IEEE Trans. Electromagn. Compat.*, vol. 39, pp. 17–23, Feb. 1997.

- [16] M. Xu and T. H. Hubing, "Estimating the power bus impedance of printed circuit boards with embedded capacitance," IEEE Trans. Adv. Packag., to be published.

- [17] Y. Ji, "Development and application of a hybrid finite-element method/method-of-moment (FEM/MoM) tool to model electromagnetic compatibility and signal integrity problems in printed circuit boards," Ph.D. dissertation, Univ. of Missouri-Rolla, July 2000.

- [18] K. Lee and W. Chen, Advances in Microstrip and Printed Antennas. New York: Wiley, 1997, ch. 5.

- [19] K. R. Carver and J. W. Mink, "Microstrip antenna technology," *IEEE Trans. Antennas Propagat.*, vol. AP-29, pp. 2–24, Jan. 1981.

**Minjia Xu** (S'98–M'02) was born in China in 1972. She received the B.S. (with honors) and M.S. degrees in electrical engineering from Tsinghua University, Beijing, China, in 1994 and 1997, respectively, and the Ph.D. degree in electrical engineering from the University of Missouri-Rolla in 2001.

From 1998 to 2001, she was with the Electromagnetic Compatibility Laboratory, University of Missouri-Rolla. She then joined the Hewlett-Packard Company, San Diego, CA, as an EMC engineer in the All-in-One Personal Printing Division. Her

current research interests include numerical and experimental analysis of signal integrity and electromagnetic compatibility issues related to printing and faxing products, development of PCB and system level technology for noise and radiated emission mitigation, as well as design for immunity and ESD conformity.

Hao Wang (S'99–M'02) received the B.S. degree in electrical engineering from Tsinghua University, Beijing, China, in 1996, and the M.S. and Ph.D. degrees in electrical engineering from the University of Missouri-Rolla, in 2000 and 2002, respectively.

From 1999 to 2002, he was with the Electromagnetic Compatibility Laboratory, University of Missouri-Rolla. He then joined the Advanced Systems Research Laboratory, Micron Technology, Boise, ID, as a Signal Integrity Engineer. His research interests include numerical and experi-

mental analysis of signal integrity and electromagnetic compatibility issues related to memory products, development of PCB design as needed to define next-generation DRAMs.

**Todd Hubing** (S'82–M'82–SM'93) received the B.S.E.E. degree from the Massachusetts Institute of Technology, Cambridge, in 1980, the M.S.E.E. degree from Purdue University, West Lafayette, IN, in 1982, and the Ph.D. degree in electrical engineering from North Carolina State University, Raleigh, in 1988.

He is currently a Professor of electrical engineering at the University of Missouri-Rolla (UMR). Prior to joining UMR in 1989, he was an Electromagnetic Compatibility Engineer with IBM,

Research Triangle Park, NC. Since joining UMR, the focus of his research has been measuring and modeling sources of electromagnetic interference. He teaches courses on "Grounding and Shielding" and "High-Speed Digital Design" both on campus and via video.

Dr. Hubing has been an Associate Editor of the IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY and the *Journal of the Applied Computational Electromagnetics Society*. Currently, he is the 2002–2003 President of the IEEE Electromagnetic Compatibility Society.