SAND94-2375 • UC-706 Unlimited Release Printed December 1994

# Application Protocol, Initial Graphics Exchange Specification (IGES), Layered Electrical Product

# Edited by Lawrence J. O'Connell

SF2900Q(8-81)

DISTUBUTION OF THIS OBCUMENT IS UNLIMITED

Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof or any of their contractors or subcontractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from Office of Scientific and Technical Information PO Box 62 Oak Ridge, TN 37831

Prices available from (615) 576-8401, FTS 626-8401

Available to the public from National Technical Information Service US Department of Commerce 5285 Port Royal RD Springfield, VA 22161

NTIS price codes Printed copy: A12 Microfiche copy: A06

# DISCLAIMER

Portions of this document may be illegible in electronic image products. Images are produced from the best available original document.

## SAND 94-2375 Unlimited Release Printed December 1994

Distribution Category UC-706

# Application Protocol, Initial Graphics Exchange Specification (IGES), Layered Electrical Product

Committee Draft Lawrence J. O'Connell, Editor Project Development Department Sandia National Laboratories Albuquerque, NM 87185-0955

# Abstract

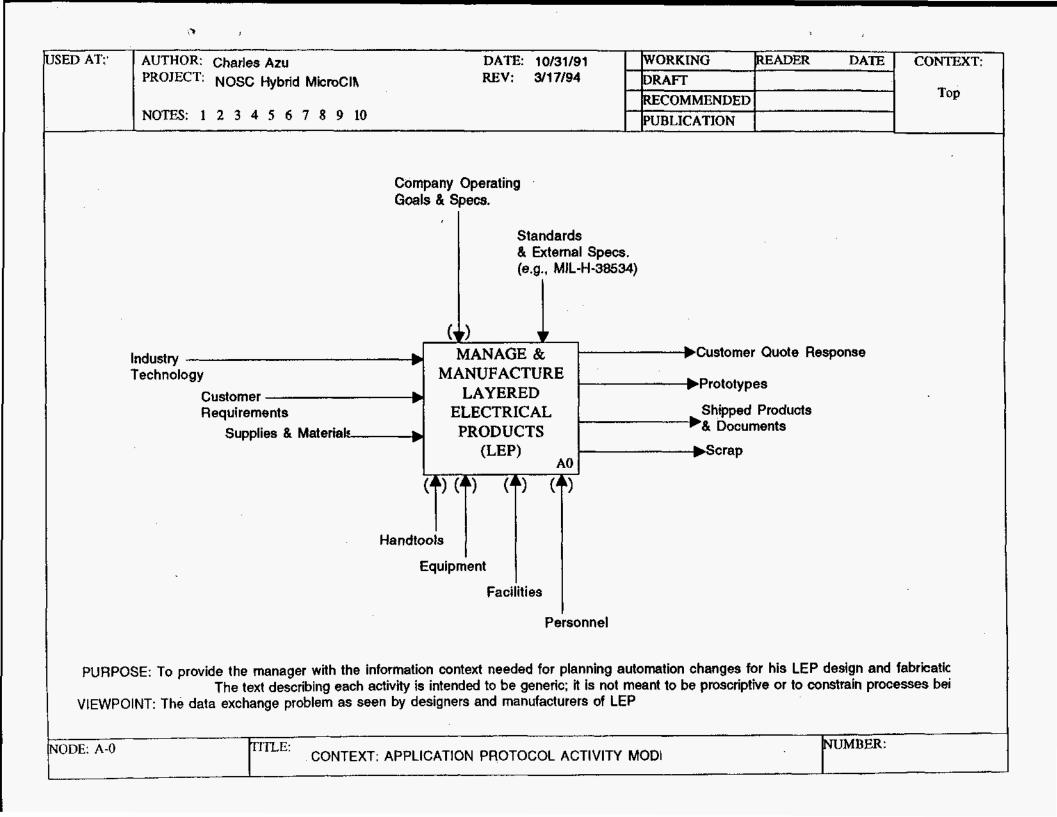

An application protocol is an information systems engineering view of a specific product. The view represents an agreement on the generic activities needed to design and fabricate the product, the agreement on the information needed to support those activities, and the specific constructs of a product data standard for use in transferring some or all of the information required.

This application protocol describes the data for electrical and electronic products in terms of a product description standard called the Initial Graphics Exchange Specification (IGES). More specifically, the Layered Electrical Product IGES Application Protocol (AP) specifies the mechanisms for defining and exchanging computer-models and their associated data for those products which have been designed in two dimensional geometry so as to be produced as a series of layers in IGES format. The AP defines the appropriateness of the data items for describing the geometry of the various parts of a product (shape and location), the connectivity, and the processing and material characteristics. Excluded is the behavioral requirements which the product was intended to satisfy, except as those requirements have been recorded as design rules or product testing requirements.

"Information is neither Matter nor Energy"

Norbert Wiener

# Initial Graphics Exchange Specification (IGES) LAYERED ELECTRICAL PRODUCT APPLICATION PROTOCOL (AP)

VERSION 1.0: This document is the IGES Electrical Applications Committee release of a complete application protocol for layered electrical products technology. Included is the collected set of design objects which the committee recommends for transfer of electronic product models and which are within the IGES domains of logical (e.g., schematic) and physical product drawing and computer presentation, data supporting manufacturing, and product testing. A broad range of electrical and electro-mechanical product models may be exchanged when this AP is applied together with the general product model exchange capabilities of IGES. The Committee recommends this AP version for translator development and encourages comments on the quality of the documentation and in particular the set of design data objects. The Committee further expects this AP to facilitate a transition into the Standard for the Exchange of Product Model Data (STEP) through the specification of consistent IGES usage for electrical applications.

### ABSTRACT

An application protocol is an information systems engineering view of a specific product. The view represents an agreement on the generic activities needed to design and fabricate the product, the agreement on the information needed to support those activities, and the specific constructs of a product data standard for use in transferring some or all of the information required.

This application protocol describes the data for electrical and electronic products in terms of a product description standard called the Initial Graphics Exchange Specification (IGES). More specifically, the Layered Electrical Product IGES Application Protocol (AP) specifies the mechanisms for defining and exchanging computer-models and their associated data for those products which have been designed in two dimensional geometry so as to be produced as a series of layers in IGES format. The AP defines the appropriateness of the data items for describing the geometry of the various parts of a product (shape and location), the connectivity, and the processing and material characteristics. Excluded is the behavioral requirements which the product was intended to satisfy, except as those requirements have been recorded as design rules or product testing requirements.

i

#### PREFACE

The Electricity Division of the Electronics and Electrical Engineering Laboratory and the Automated Manufacturing Research Facility of the Center for Manufacturing Engineering at the National Institute of Standards and Technology (NIST) completed a program in 1992 entitled "A Data Format Specification for Hybrid Microcircuit Assemblies." This project was sponsored by the Office of the Assistant Secretary of the Navy for Manufacturing Technology and was managed by the Naval Command, Control & Ocean Surveillance Center, Research Development Test & Evaluation Division (NCCOSC, RDT&E), San Diego, Contract No. N0001991IPAKC1R, MOD/ AMEND No. 0A-001. The project objective was the development of a specification for a neutral format to promote the exchange of design and manufacturing data for hybrid microcircuit products. The resulting document "Initial Graphics Exchange Specification (IGES) Hybrid Microcircuit Application Protocol," NIST TN 1295, January 1993 was distributed to Navy Contracting Officers, other program reviewers, and the Electrical Applications Committee (EAC) of the IGES Organization.

Reviews were held with industry, EAC, and the IGES Project from the Navy Program inception and throughout 1993. The discussions brought out the applicability of the Navy Hybrid Microcircuit work to a wide range of electrical product types. Following discussions in the EAC and with the Continuous Acquisition and Life Cycle Support (CALS) Interest Group, the editors of this document were tasked with bringing together the contributions of other authors and the NIST document contents mentioned above, resolving comments and experiences submitted during the years time.

The scope of this AP, formally stated in Section 1.3.2, includes the various aspects of all layered electrical products; the specification control drawings, circuitry and parts layout, and information concerning their fabrication. The specified data model is sufficiently detailed to support the design release, fabrication, and final assembly of a layered product system.

IGES is designed to support a broad range of applications and information, and it is recognized that few implementations will support all of the specification. An application protocol defines a logical subschema of the IGES specification, the usage of the subschema, and the necessary benchmarks for testing implementations. The application protocol for layered devices builds on the previous work of the Electrical Applications Committee of the IGES/PDES Organization. Such documents are seen as important for the development of STEP (Standard for the Exchange of Product Model Data) application protocols.

The data structures defined in this document are proposed in order to greatly improve the fidelity of layered electrical product applications data exchanged. The lack of fidelity has been termed "flavorings<sup>1</sup>" which occur from two primary sources. The first flavoring source is attributed to inconsistent use of computer aided design (CAD) systems, often because of differing ways to describe the product within different organizations. The second source of flavorings often results when the data structures of different CAD systems are converted to or from IGES data entities. Where an identified subset of the IGES entities did not address the flavoring issue, this document specifies product objects which constrain both sources of flavorings. This AP is proposed as a replacement of MIL-D-28000A<sup>2</sup> Class 3. This revision will define a new MIL-D-28000 class for the transfer of layered electrical product data by use of future versions of IGES.

ü

<sup>&</sup>lt;sup>1</sup>. The Sandia National Laboratories on behalf of the Department of Energy contributed a great deal of information on the flavorings problem and possible solutions during the mid 1980s.

The members of the EAC also note that other data formats may be employed. They would encourage continuation of work to achieve an industry consensus of the activity and reference model sections (Appendix A and 4.2 respectively) and additional interpretation (Section 5) models as needed for each additional format supported. Comments on this document should be sent to:

Sandia National Laboratories Larry O'Connell Mail Stop 0955 P. O. Box 5800 Albuquerque, NM 87185-0955

(505) 844-1061 E-Mail: ljoconn@sandia.gov

## **Future Directions**

The Application Activity Model (Appendix A) and Application Reference Model (Section. 4.2) contain sufficient detail to support design release, fabrication, and final assembly of electrical product system. The IGES models (Section 5) in this document, however, are not meant to fully support product testing, analysis, and manufacturing. A full life-cycle data standard—possibly based on the Standard for the Exchange of Product Model Data (STEP)—will be necessary to support all phases of product processing.

This document does not complete the fabrication definition in terms of the sequence of processing steps and the parameters used in those steps.

This AP AIM is currently limited to layered electronic product (LEP) information contained in electronic computer-aided design (ECAD) systems. These systems are in widespread use. Their ability to translate data between dissimilar systems is a high priority in the user community. IGES serves as the implementation for this information because most ECAD suppliers are familiar with the specification and support it in their software packages.

A broadened capability for this AP that includes manufacturing, test, simulation, behavior, and documentation is desired by users and manufacturers of hybrids. Much of this information is outside the scope identified in most ECAD systems and the IGES specification.

#### About the Document

The style, format, and much of the material for this application protocol was taken from the "3D Piping IGES Application Protocol." That AP specifies the mechanisms for defining and exchanging 3D piping system models in IGES format.<sup>3</sup> The "3D Piping IGES Application Protocol" was the first IGES AP to be delivered to industry and led to the development of STEP (Standard for the Exchange of Product Model Data) application protocols. The authors of this

iii

<sup>&</sup>lt;sup>2</sup> MIL-D-28000 is the Department of Defense specification that identifies the requirements to be met when product definition data is delivered in IGES format.

<sup>&</sup>lt;sup>3.</sup> See Section 2.4, Reference 16 (NOTE: This reference was the source of AP material, but is not the most current version of the IGES Piping AP.).

document are indebted to Mark Palmer for his work and the guidance that it provides. It is the authors' belief that if the CAD/CAM industry is to use application protocols consistently, we need consistent application protocols.

Preparation of this document is a tribute to the ability to move text and graphics between applications and computer systems.<sup>4</sup> The text was originated in WordPerfect<sup>™</sup> DOS<sup>™</sup> and filtered into FrameMaker<sup>™</sup> 2.1 on a Sun<sup>™</sup> workstation for the original formatting and some of the graphics. The AAM model was developed in Design/IDEF<sup>™</sup>, and glossary in Hypercard; both on the Macintosh<sup>™</sup>. The ARM was drawn in MacDraw II<sup>™</sup>. The AIM was developed at International TechneGroup Inc. (ITI) where the text was written in Word<sup>™</sup> for DOS and the graphics drawn in AutoCAD<sup>™</sup>. The graphics were transmitted to Raytheon in IGES format where they were edited and translated into FrameMaker<sup>™</sup> MIF format. Final document assembly was done in FrameMaker<sup>™</sup> 3.0/Mac, 4.0/PowerPC and LASER-printed from Frame's POSTSCRIPT<sup>™</sup> output.

#### ACKNOWLEDGMENTS

The editors thank the following individuals for contributions to the development of this document:

Authors and Contributors to the "IGES Hybrid Microcircuit Application Protocol":

Thomas Leedy—the author of the first work toward this document—and Curtis Parks, NIST; Roger McCollough and Charles Azu, NCCOSC; Larry Savage and Patrick Toomey, and Thomas Makoski, ITI, Inc. The product objects were developed by Diane Elmer, Scicards; Bernard Gilbert, Prime-ComputerVision; Dave Kehmeier, Mentor Graphics; Randy Lawson, Cadence Design Systems, Inc.; Thomas Makoski, ITI, Inc.; and Anthony Prince, Intergraph-Dazix.

Authors and Contributors to this Document:

Larry O'Connell (Chairman of the Electrical Applications Committee, IGES/PDES Organization), Sandia Laboratories; together with: Bill Loye, Loye & Associates; Curtis Parks, National Institute of Standards & Technology, John Russell, Honeywell Commercial Flight Systems; and the membership of the Electrical Applications Committee.

Special thanks to Gaye Garrison, PC Support Inc., for document editing and file preparations.

<sup>&</sup>lt;sup>4.</sup> Word and DOS are trademarked by Microsoft Corporation; WordPerfect is trademarked by the WordPerfect Corporation; Framemaker is trademarked by Frame Technology Corporation; Sun is trademarked by Sun Microsystems, Incorporated; Design/IDEF is trademarked by Meta Software Corporation; Hypercard and Macintosh are trademarked by Apple Computer, Incorporated; MacDraw is trademarked by Claris Corporation; AutoCAD is trademarked by Autodesk, Incorporated; and PostSCRIPT is trademarked by Adobe Systems, Incorporated. Trademarked products were mentioned in this document as examples of the range of possible products and are not necessarily endorsed by the contributors to this document.

# Table of Contents

Abstract i Preface ii Future Directions iii About the Document iii

## Acknowledgements iv

## 1. INTRODUCTION 1

1.1. Purpose 1

1.2. Background 1

1.2.1. Electrical Assembly Complexity 2

1.2.2. Consistent Information for Concurrent Engineering 3

1.3. APPLICATION PROTOCOL CONTENTS 4

1.3.1. Terms and Definitions 4

1.3.2. Scope 4

## 2. APPLICATION AND CORE REQUIREMENTS 6

2.1. Application Information Requirements 6

2.2. Application and ARM Correspondence 7

2.3. Normative References 9

2.4 Informative References 9

Contents

### 3. DEFINITIONS 11

3.1. IGES Application Protocol Definitions 11

3.2. LEP Application Definitions 13

## 4. INFORMATION REQUIREMENTS AND APPLICATION REFERENCE MODEL 31

4.1 Application Data Views 31

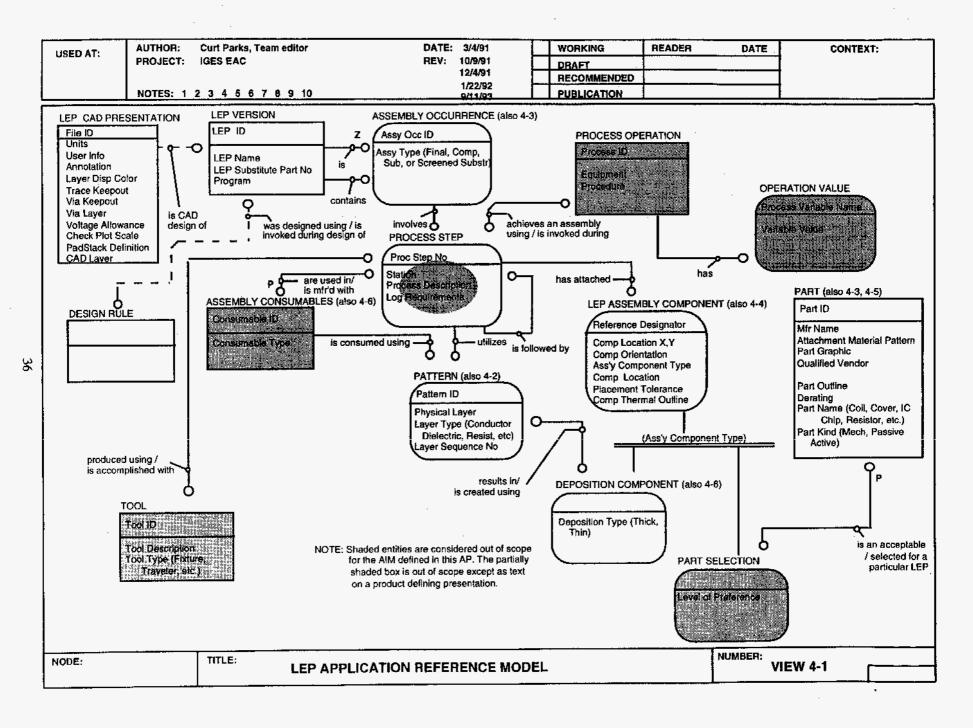

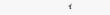

4.2. Application Reference Model 31

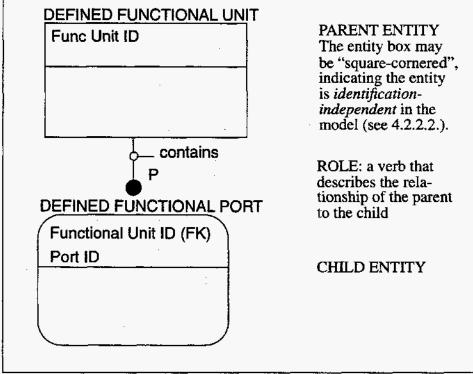

4.2.1. Descriptions of the ARM Data Constructs 31

4.2.1.1. ARM Methods and Language 31

4.2.2. Data Construct Definitions 33

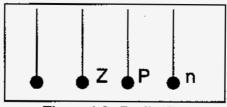

4.2.2.2. Data Construct Assertions 33

4.2.3. ARM Diagrams 34

#### 5. IGES APPLICATION INTERPRETED MODEL 43

5.1. ARM to AIM Mapping 44

5.2. IGES Structure and Syntax of the Application Interpreted Model 44

5.2.1. IGES File Structure 44

5.2.1.1. START Section 45

5.2.1.2. TERMINATE Section 45

5.2.1.3. GLOBAL Section 45

5.2.1.4. DIRECTORY ENTRY and PARAMETER DATA Sections 45

5.2.2. Global Values and Entity List 45 5.2.3. Basic Syntax used in the AIM 50

5.2.3.1. Object Definition Block 50

5.2.3.2. Object Instance Block 50

5.2.3.3. Object Value Block 51

5.2.3.4. Object Reference Mechanism 52

#### 5.3. AIM Object Models 53

5.3.1. Interface Object Models 54

5.3.1.1. LEP Part Library IGES File 54

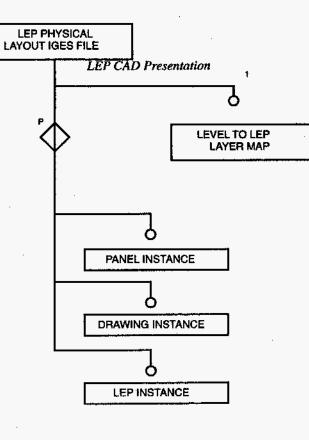

5.3.1.2. LEP Physical Layout IGES File 55

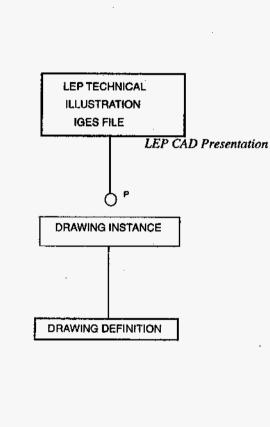

5.3.1.3. LEP Technical Illustration IGES File 56

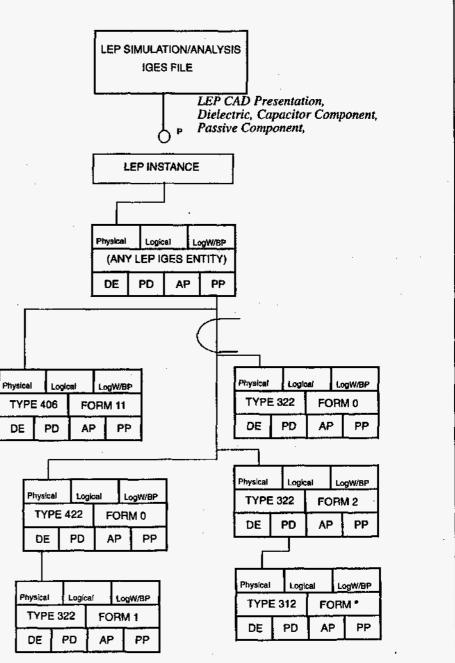

5.3.1.4. LEP Simulation/Analysis IGES File 57

#### 5.3.2. LEP Features 59

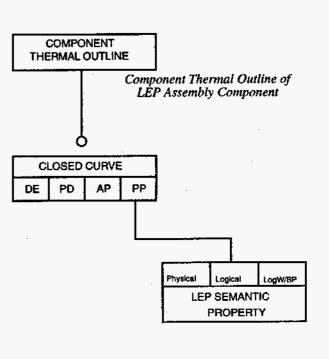

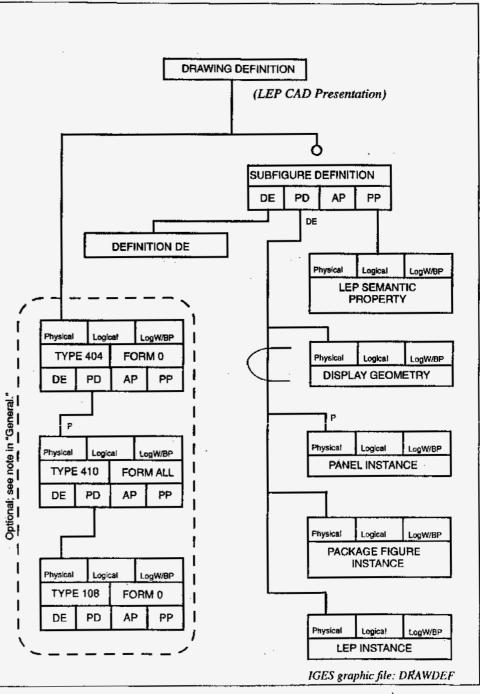

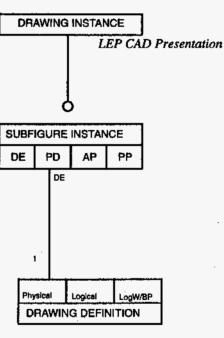

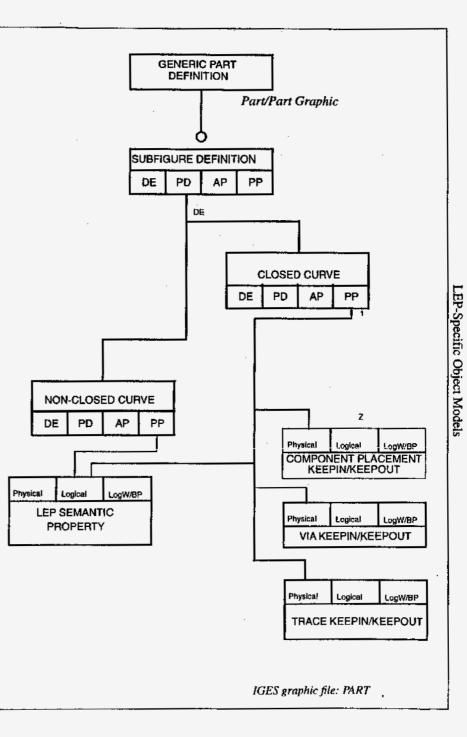

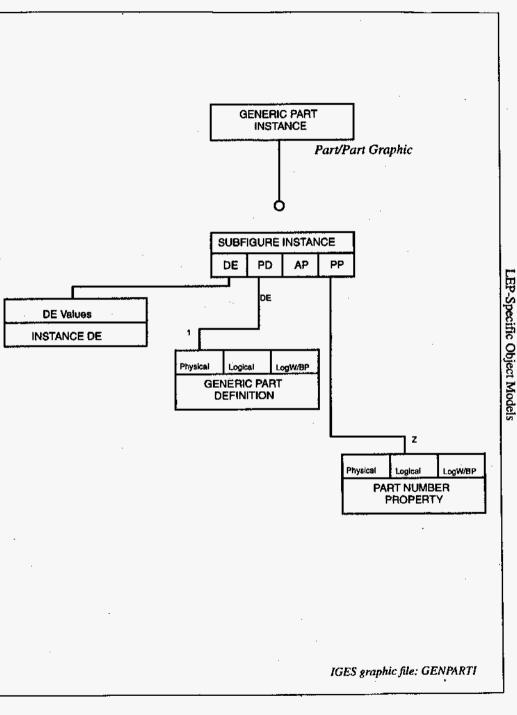

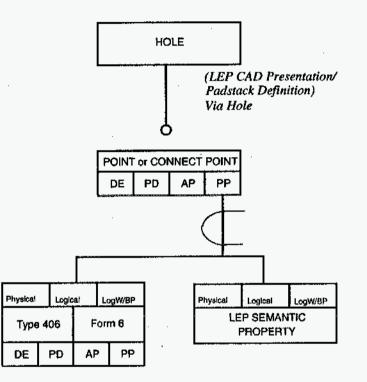

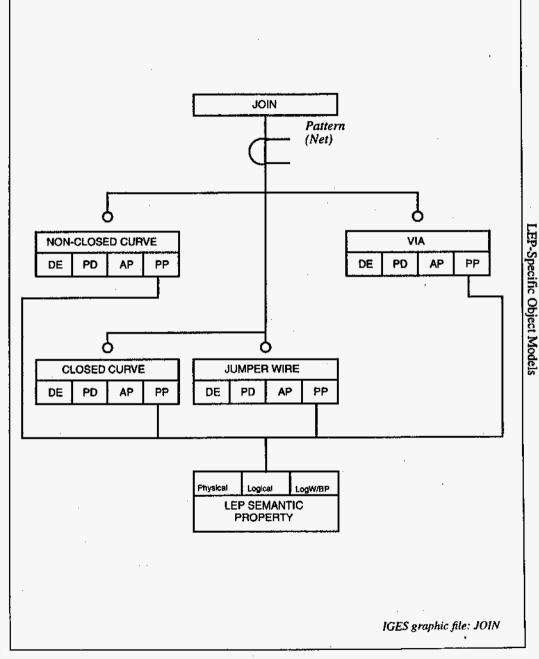

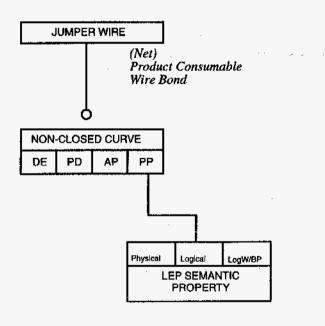

5.3.2.1. Component Placement Keepin/Keepout 60 5.3.2.2. Component Thermal Outline 61 5.3.2.3. Drawing Definition 62 5.3.2.4. Drawing Instance 63 5.3.2.5. Generic Part Definition 64 5.3.2.6. Generic Part Instance 65 5.3.2.7. Hole 66 5.3.2.8. Join 67 5.3.2.9. Jumper Wire 68 5.3.2.10. Keepin/Keepout 69

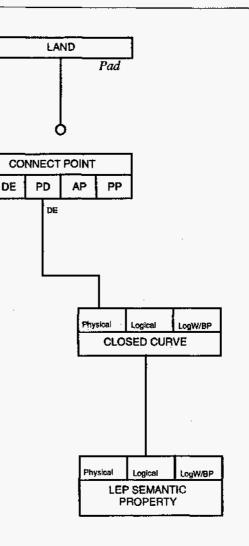

5.3.2.11. Land 70

vi

5.3.2.12. Layer Outline 71

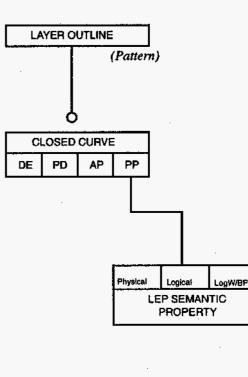

5.3.2.13. LEP Definition 72

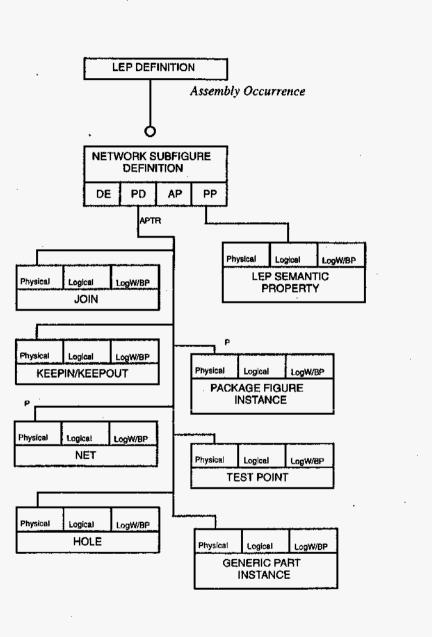

5.3.2.14. LEP Instance 73

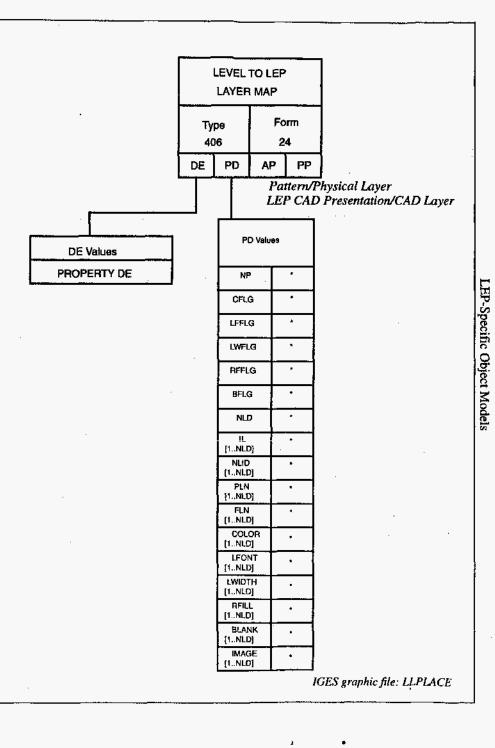

5.3.2.15. Level to LEP Layer Map Entity (Type 406 Form 24) 74

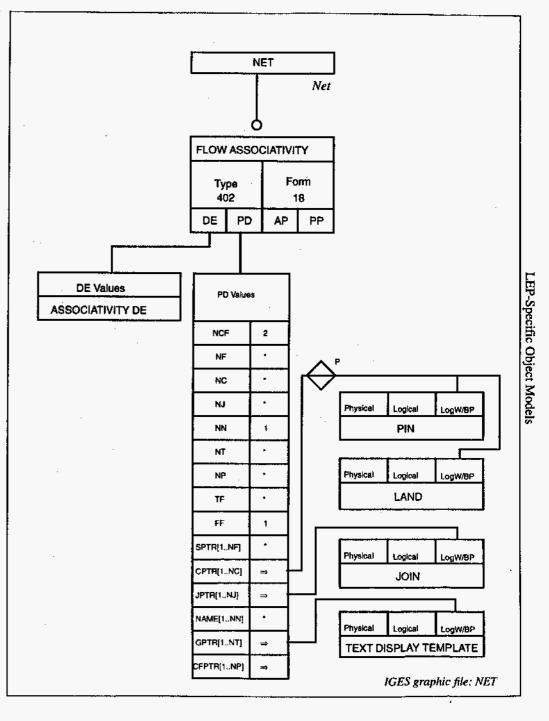

5.3.2.16. Net 75

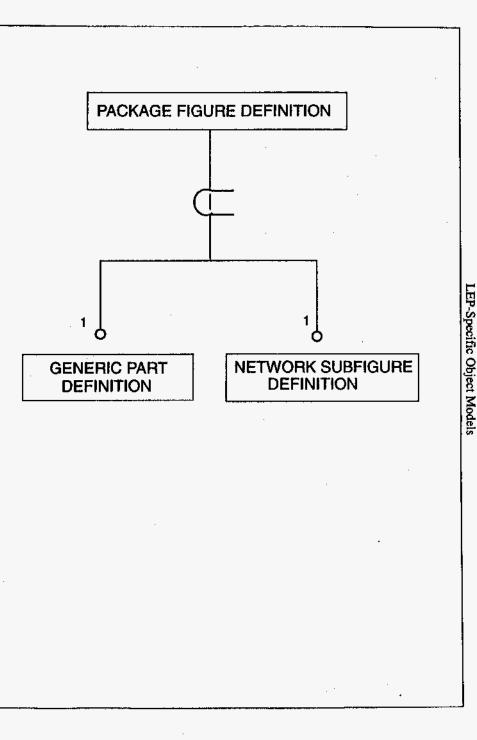

5.3.2.17. Package Figure Definition 77

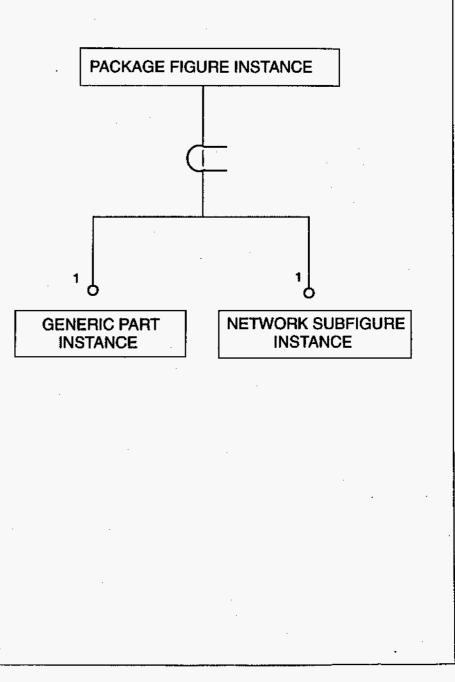

5.3.2.18. Package Figure Instance 79

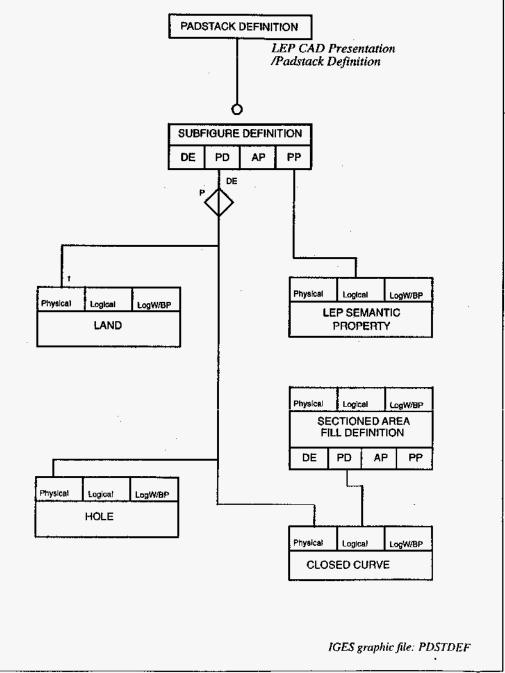

5.3.2.19. Padstack Definition 80

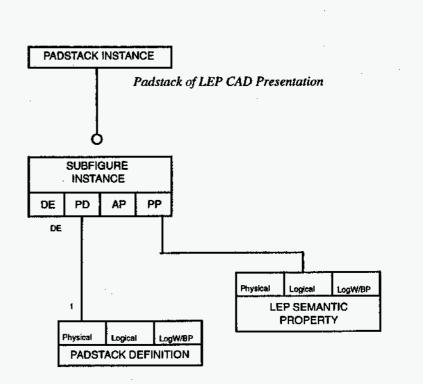

5.3.2.20. Padstack Instance 81

5.3.2.21. Panel Definition 82

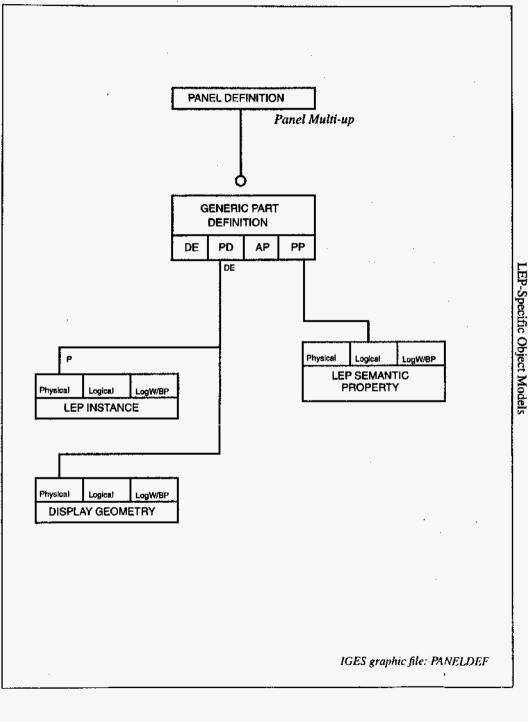

5.3.2.22. Panel Instance 83

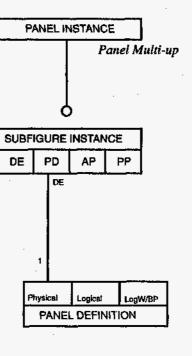

5.3.2.23. Part Placement Boundary 84

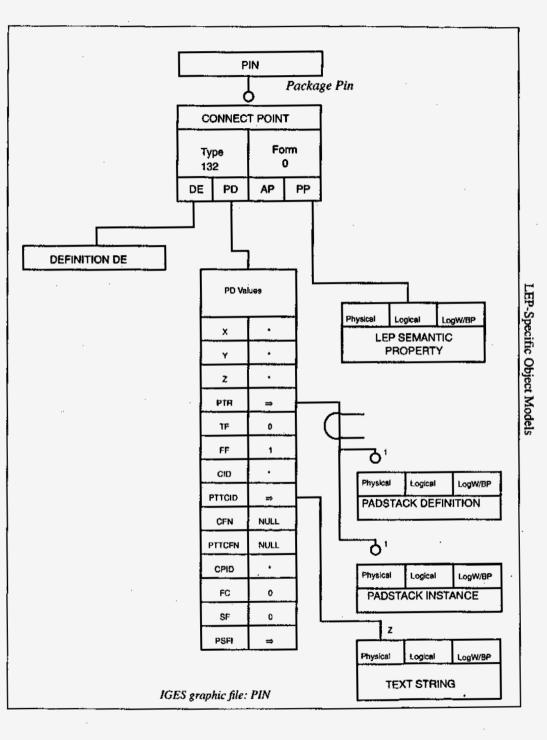

5.3.2.24. Pin 85

5.3.2.25. Routing Keepin/Keepout 86

5.3.2.26. Test Point 87

5.3.2.27. Trace Keepin/Keepout 88

5.3.2.28. Via 89

5.3.2.29. Via Keepin/Keepout 90

5.3.2.30. Wire Bond 91

#### 5.3.3. Display Geometry Object Models 93

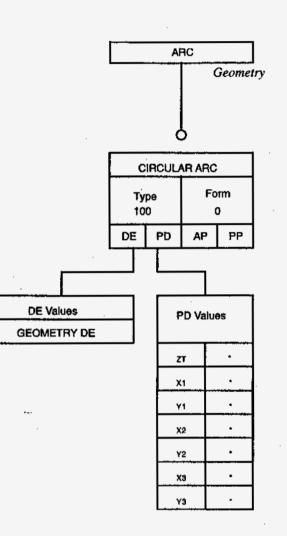

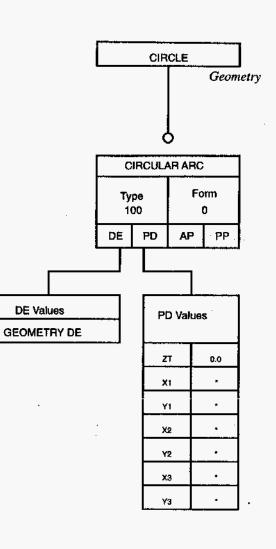

5.3.3.1. Arc 93

5.3.3.2. Circle 94

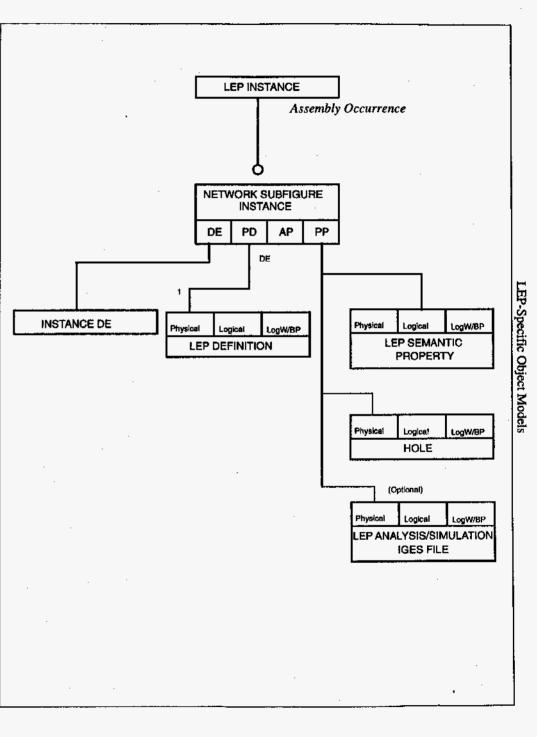

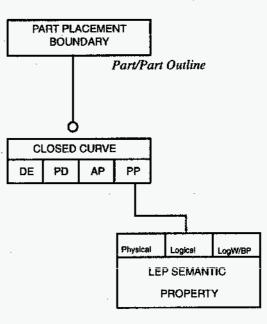

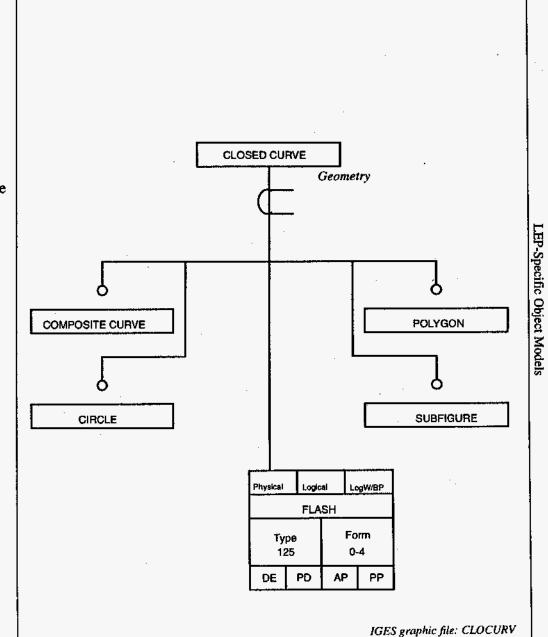

5.3.3.3. Closed Curve 95

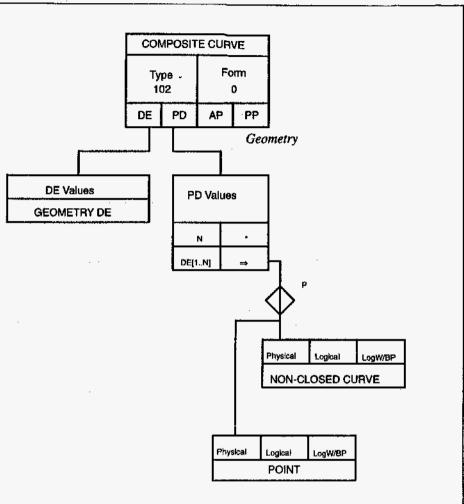

5.3.3.4. Composite Curve 96

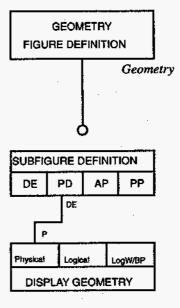

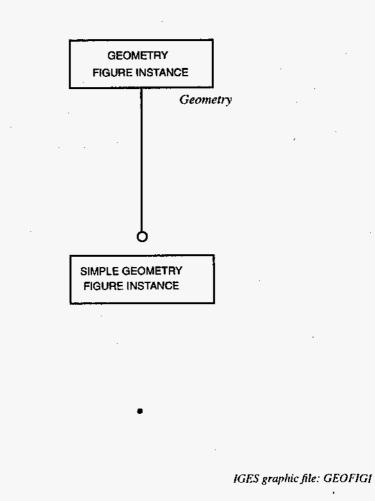

5.3.3.5. Geometry Figure Definition 97

5.3.3.6. Geometry Figure Instance 98

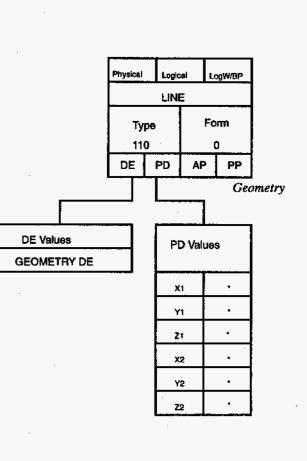

5.3.3.7. Line Entity (Type 110, Form 0) 99

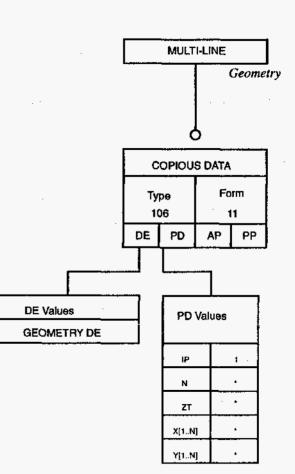

5.3.3.8. Multi-Line 100

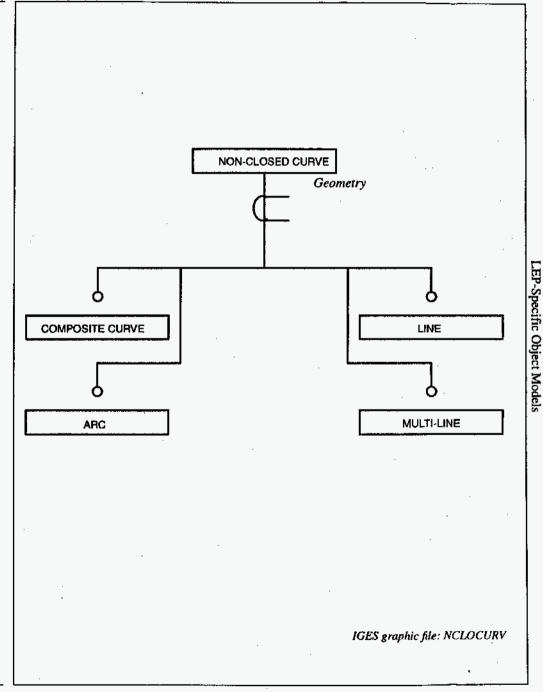

5.3.3.9. Non-Closed Curve 101

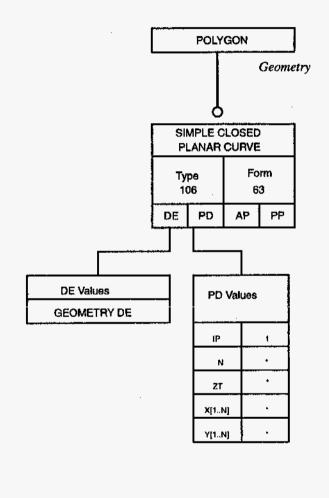

5.3.3.10. Polygon 102

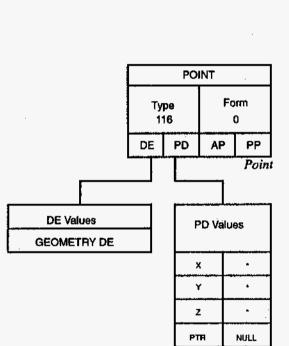

5.3.3.11. Point Entity (Type 116, Form 0) 103

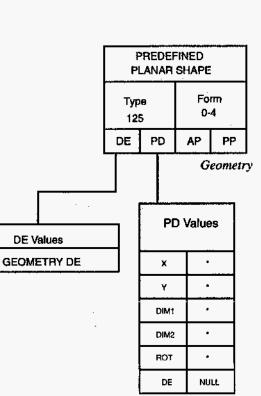

5.3.2.12. Predefined Planar Shape 104

#### 5.3.4. Miscellaneous Object Models 105

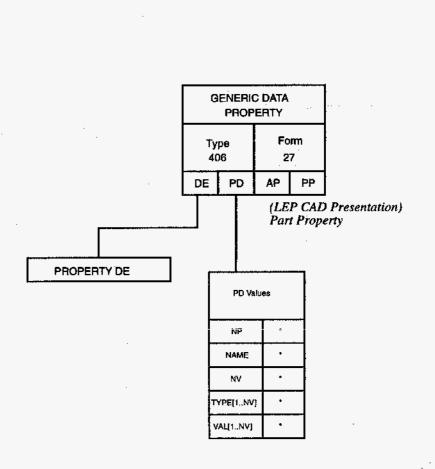

5.3.4.1. Generic Data Property (Type 406, Form 27) 106

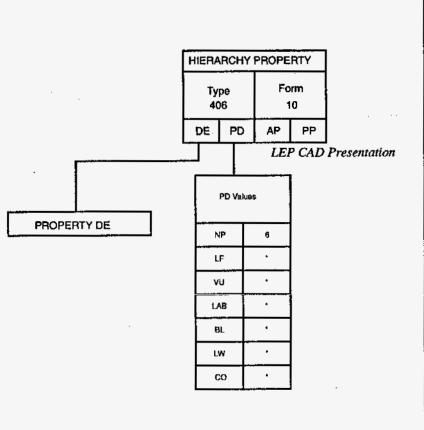

5.3.4.2. Hierarchy Property (Type 406, Form 10) 112

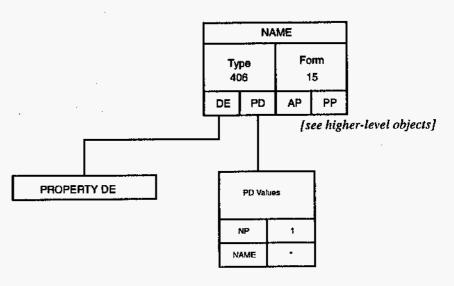

5.3.4.3. Name Property (Type 406 Form 15) 113

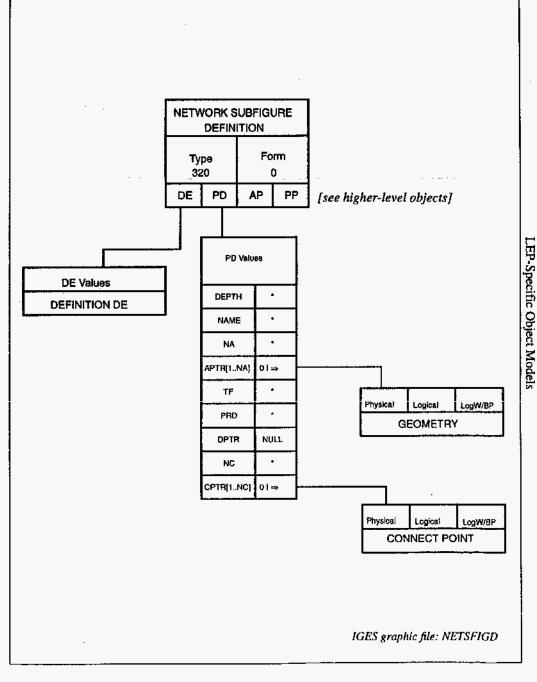

5.3.4.4. Network Subfigure Definition Entity (Type 320, Form 0) 114

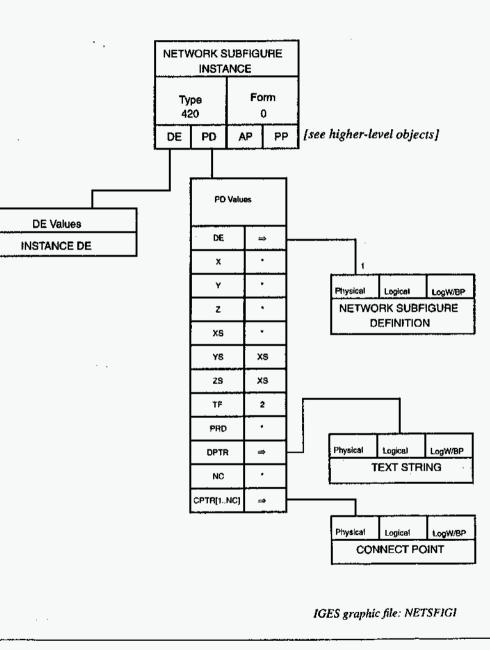

5.3.4.5. Network Subfigure Instance Entity (Type 420, Form 0) 115

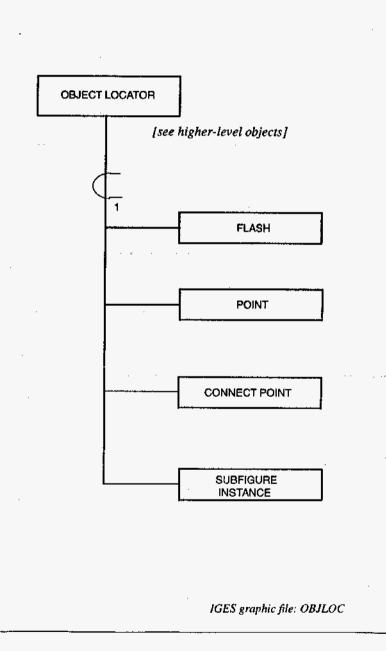

5.3.4.6. Object Locator 116

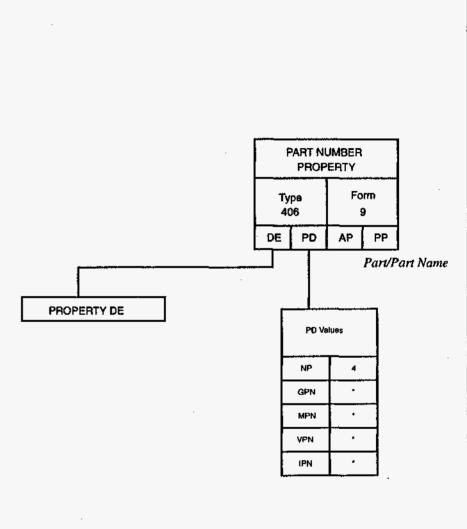

5.3.4.7. Part Number Property (Type 406, Form 9) 117

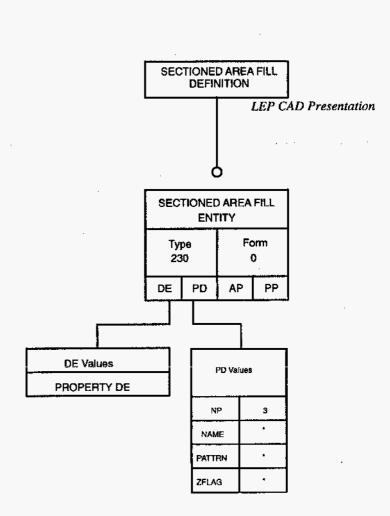

5.3.4.8. Sectioned Area Fill Definition 118

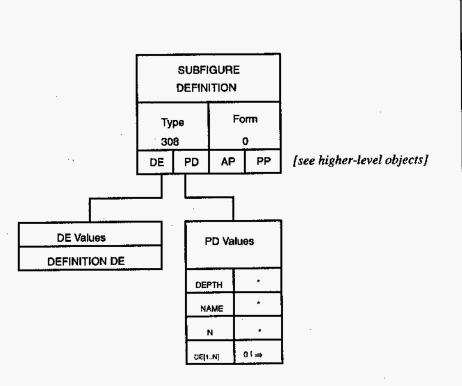

5.3.4.9. Subfigure Definition Entity (Type 308, Form 0) 119

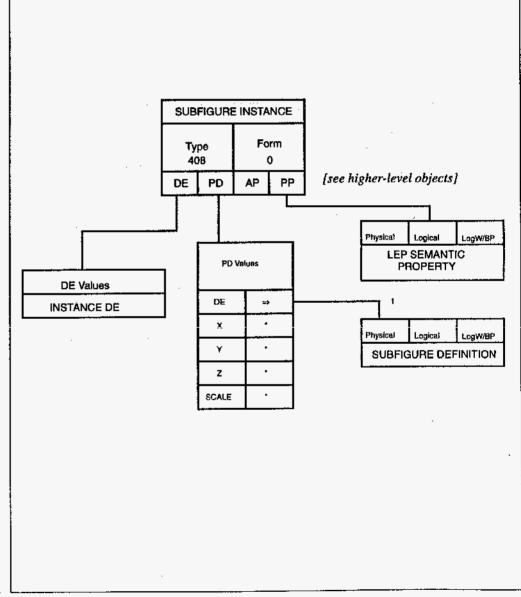

5.3.4.10. Subfigure Instance Entity (Type 408, Form 0) 120

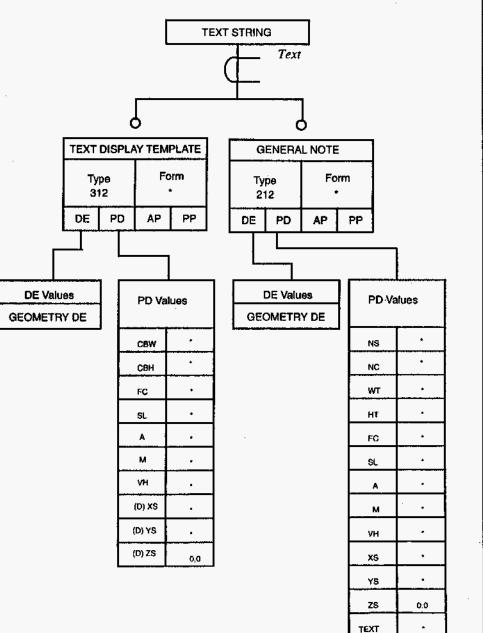

5.3.4.11. Text String 121

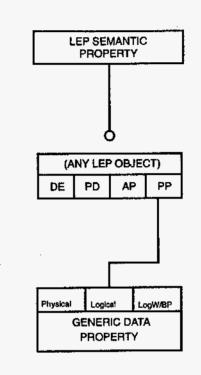

5.3.5. LEP Semantic Property 123

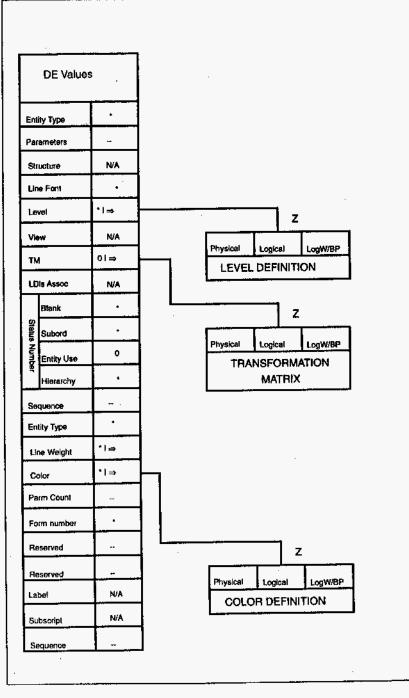

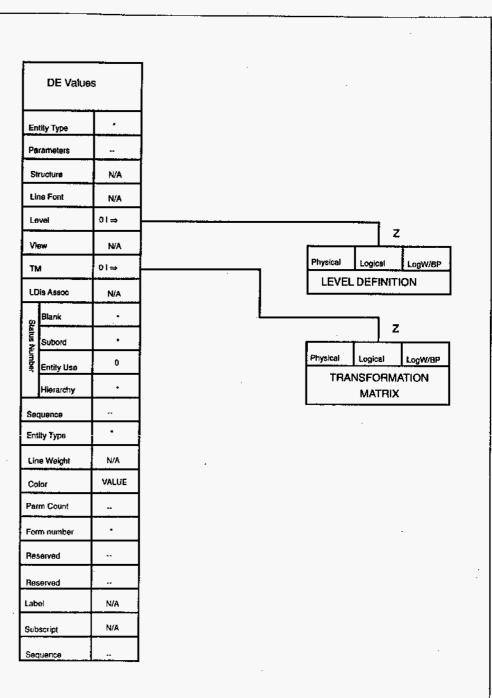

#### 5.3.6. DE Referenced Object Models 124

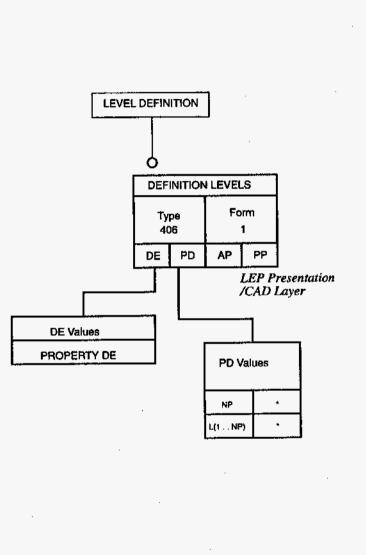

5.3.6.1. Level Definition 125

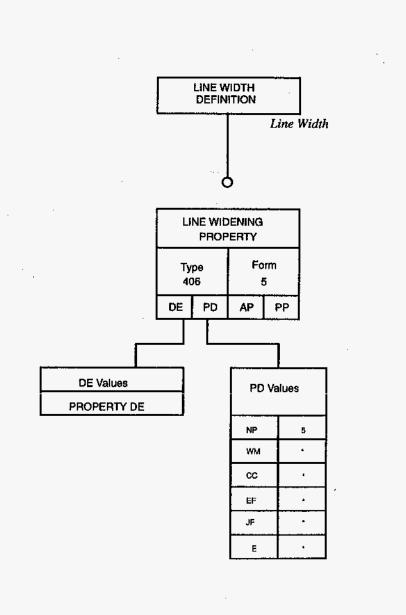

5.3.6.2. Line Width Definition 126

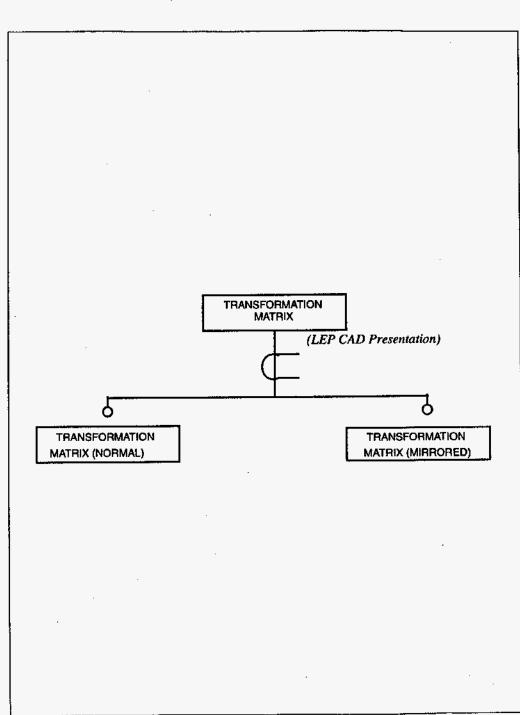

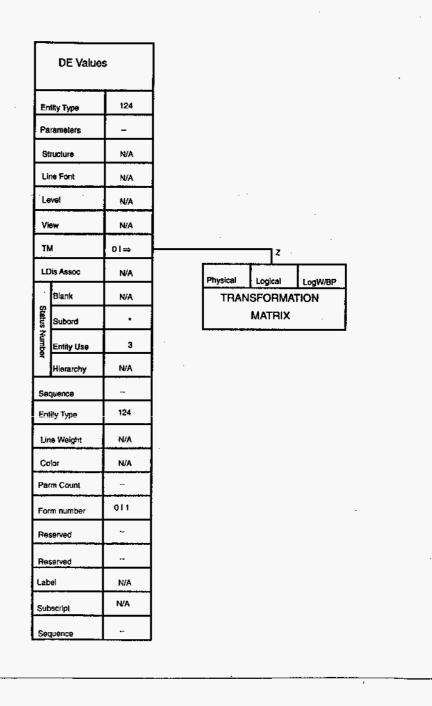

5.3.6.5. Transformation Matrix 127

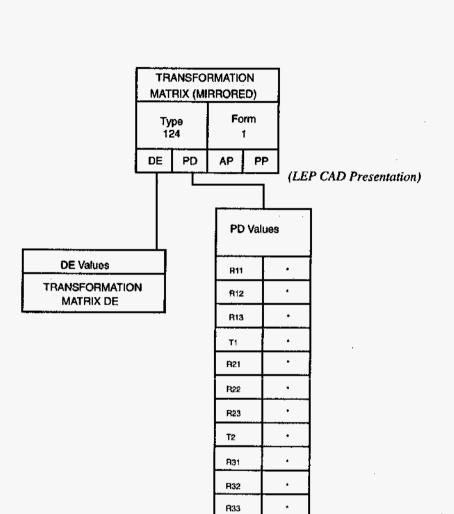

5.3.6.6. Transformation (Mirrored) Entity (Type 124, Form 1) 128

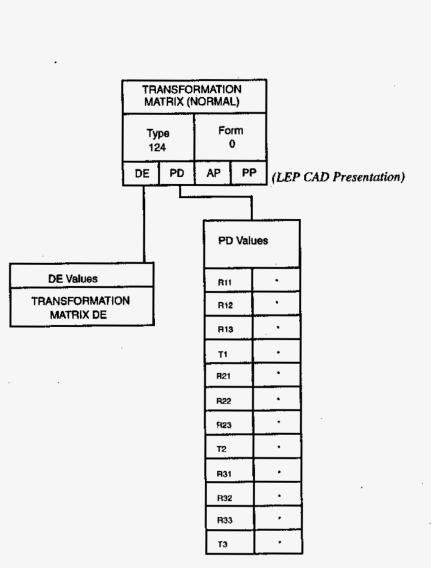

5.3.6.7. Transformation Matrix (Normal) Entity (Type 124, Form 0) 129

5.3.7. DE Section Object Models 131

5.3.7.1. Associativity DE 131

5.3.7.2. Definition DE 132

5.3.7.3. Geometry DE 133

5.3.7.4. Instance DE 134 5.3.7.5. Property DE 135 5.3.7.6. Transformation Matrix DE 136

# 6. Implementation and Conformance Testing Guidelines 139

#### 6.1. PROCESSOR CONFORMANCE REQUIREMENTS 139

6.1.1. Testing Considerations 140

6.1.2. Conformance Considerations 140

6.2. Test Purposes and Test Groups 142

#### 6.3. LEP Constructs 148

6.3.1. LEP Constructs Supporting Signal Conductivity 148

6.3.2. LEP Constructs Supporting a Physical Representation 149

6.3.3. LEP Constructs Supporting a Logical Representation 149

6.4. Entity Usage in a PDO LEP Representation 149

6.4.1 DE Fields are Not Expected to Convey Meaning 150

6.4.2. Entities Which May Appear in a PDQ LEP Representation 151

6.4.2.1. LEP Usage of Geometry 151

6.4.2.2. LEP Usage of Annotation 152

6.4.2.3. LEP Usage of Structure (Excluding Properties) 153

6.4.2.4.LEP Usage of Existing Specific Property Entities 154

6.4.2.5. LEP Usage of the (Augmented) Generic Data Property Entity 154

6.4.2.6. LEP Usage of Simulation/Analysis Entities 155

6.4.3. Entities Which Shall NOT be Used in a PDQ LEP Representation 155

6.5. LEP Entity Usage for Core Applications 155

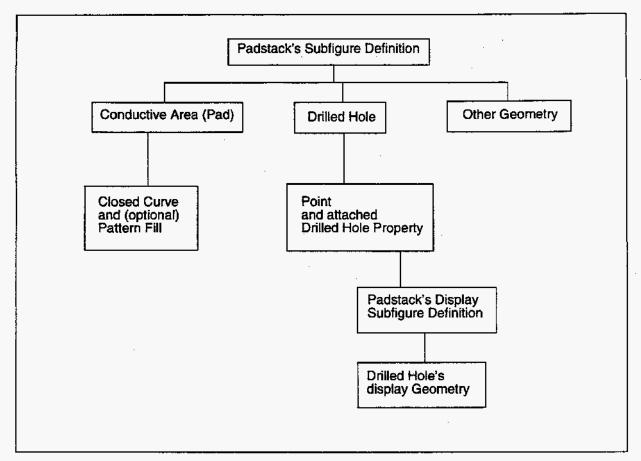

6.5.1. LEP Entity Usage for Padstack Representation 155

6.5.1.1. LEP Entity Usage for a Physical Padstack Definition 156

6.5.1.1. Entities Required to Add the Representation of Drilled Holes into a Padstack 156

6.5.1.1.2. Entities Required to Add Display Appearance of Holes in a Padstack 157

6.5.2. LEP Entity Usage for Physical Component Representation 159

6.5.2.1. LEP Entity Usage for Physical Component Definition 160

6.5.2.2. LEP Entity Usage for Physical Component Instance 161

6.5.2.3. LEP Usage for Physical Connect Point 162

6.5.2.4. LEP Entity Usage for Physical Via 163

6.5.3. LEP Entity Usage for Physical Mechanical Part Representation 165

6.5.4. LEP Entity Usage for Physical PWB Representation 166

6.5.4.1. LEP Physical PWB Definition 166

6.5.4.2. LEP Physical PWB Instance 167

6.5.4.3. LEP Constructs Supporting Conductivity 169

6.5.4.4. LEP Constructs Supporting Components 169

6.5.4.5. LEP Constructs Supporting Connectivity 170

6.5.4.6. LEP Constructs Supporting a Physical Representation 170 6.5.4.7. LEP Physical Flow Associativity (Signal/Netlist) 171

6.5.4.8. LEP Physical LEP Signal Carriers (Traces, Shapes) 172

6.5.4.9. LEP Physical PWB Features: Fiducials 173

6.6. LEP Entity Usage for Specific Applications 174

6.6.1. LEP Entity Usage for Design/Engineering Applications 174

6.6.1.1. LEP Entity Usage for Netlist Reports 174

6.6.1.2. LEP Entity Usage for Component Placement Reports 175

6.6.1.3. LEP Entity Usage for Bill of Materials Reports 176

6.6.2. LEP Entity Usage for Manufacturing Applications 177

6.6.2.1. LEP Entity Usage for Photo-lithography Tools 177

6.6.2.2. LEP Entity Usage for LEP Test Aids 178

6.6.2.3. LEP Entity Usage for Numerically Controlled (NC) Production Files 180

6.6.2.3.1. LEP Entity Usage for Component Insertion 180

6.6.2.3.2. LEP Entity Usage for Component Pick and Place 182

6.6.2.3.3. LEP Entity Usage for Component Verification 185

6.6.2.3.4. LEP Enitity Usage for Wire Wrap 185

6.6.2.3.5. LEP Entity Usage for Labelmaker 186

6.6.2.4. LEP Entity Usage for Panelization 186

6.6.3. LEP Entity Usage for Drafting/Documentation Applications 187

6.6.3.1. Major Differences Between the Documentation and the PDQ Model of a Conformant LEP AP 188

6.6.3.2. Changes and Additions to the PDQ LEP AP 188 6.6.3.3. LEP Entity Usage for Fabrication Documentation 188

6.6.3.4. LEP Entity Usage for Assembly Documentation 189

6.6.3.5. LEP Entity Usage for LEP Technical Illustrations 189

6.6.4. LEP Usage for CAD to CAD Exchange 189

6.6.4.1. LEP Entity Usage for Layer Assignment 190

6.6.4.2. LEP Entity Usage for Color 190

6.6.4.3. Semantic Properties for LEP Applications 190

6.6.4.4. Entity Usage for Presentation (Appearance) 198

6.6.5. Entity Usage for CAD Simulation/Analysis 198

### A. Activity Model Contents A-1

B. Application Protocol Usage Guide B-1

C. Technical Discussions C-1

. .

.

.

: . **x**

.

.

. .

.

# List of Figures & Diagrams

## 4. ARM Figures

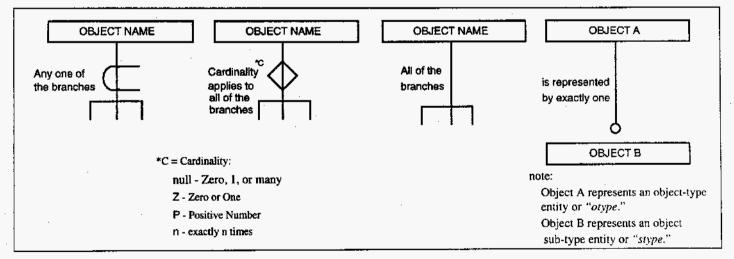

4-1. Component Parts of an IDEF Relationship 32

4-2. Cardinality 33

4-3. The Categorization Structure 34

#### 4. ARM Diagrams

View 4-1 Top-Level Entities 36

View 4-2 Expanded Dependents of Pattern 37

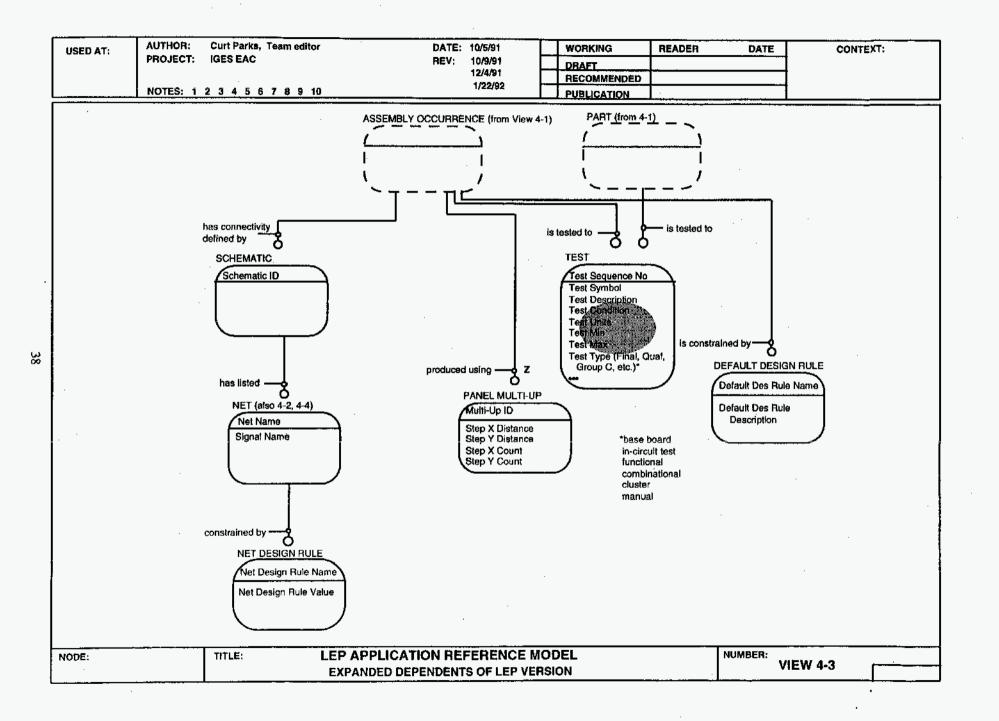

View 4-3 Expanded Dependents of LEP Version 38

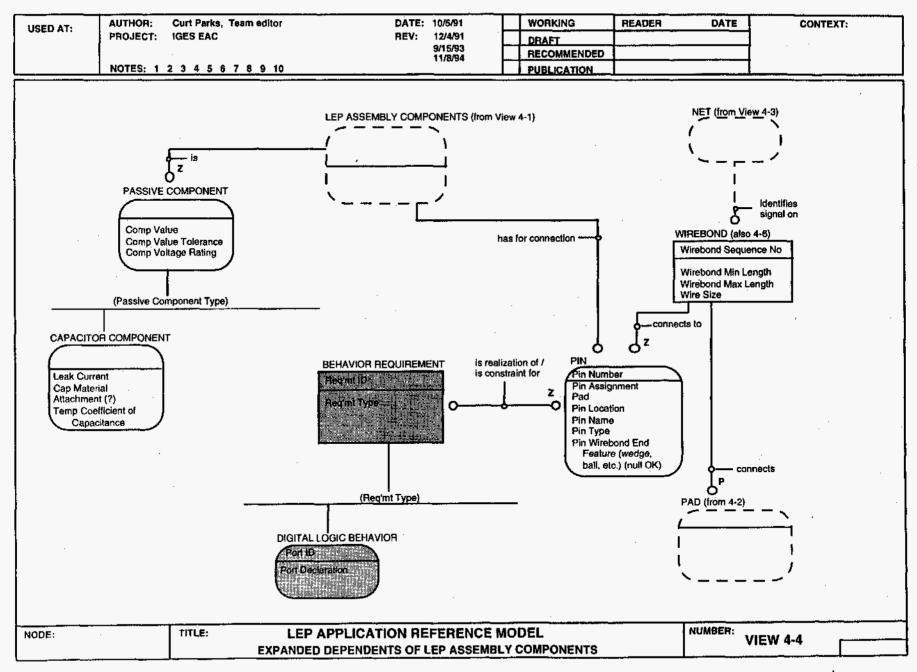

View 4-4 Expanded Dependents of LEP Assembly Occurrence 39

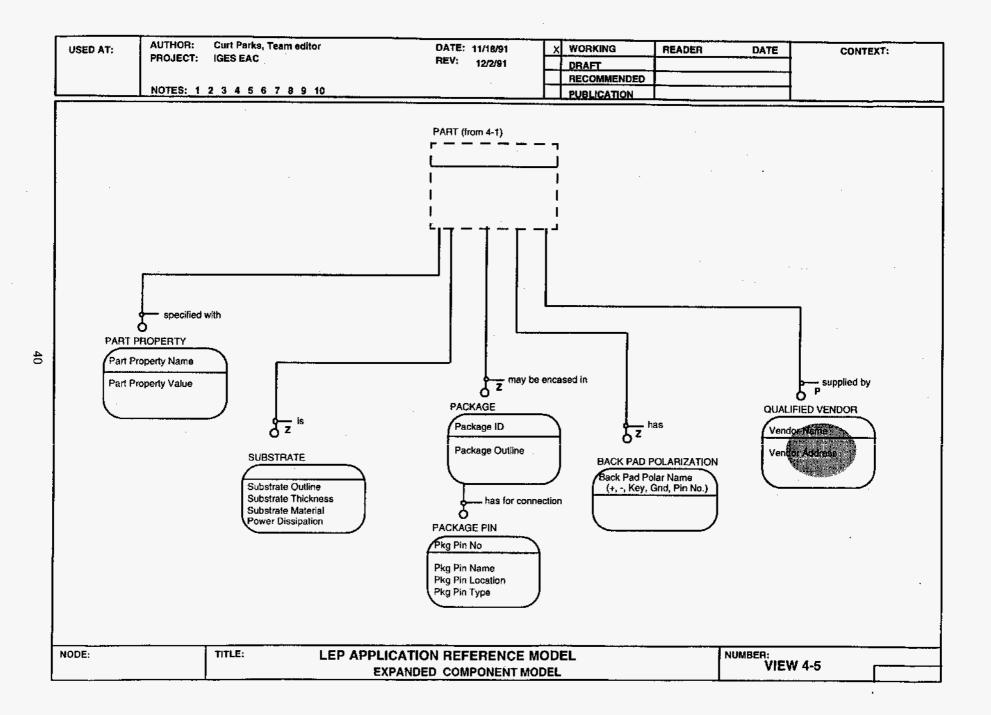

View 4-5 Expanded Component Model 40

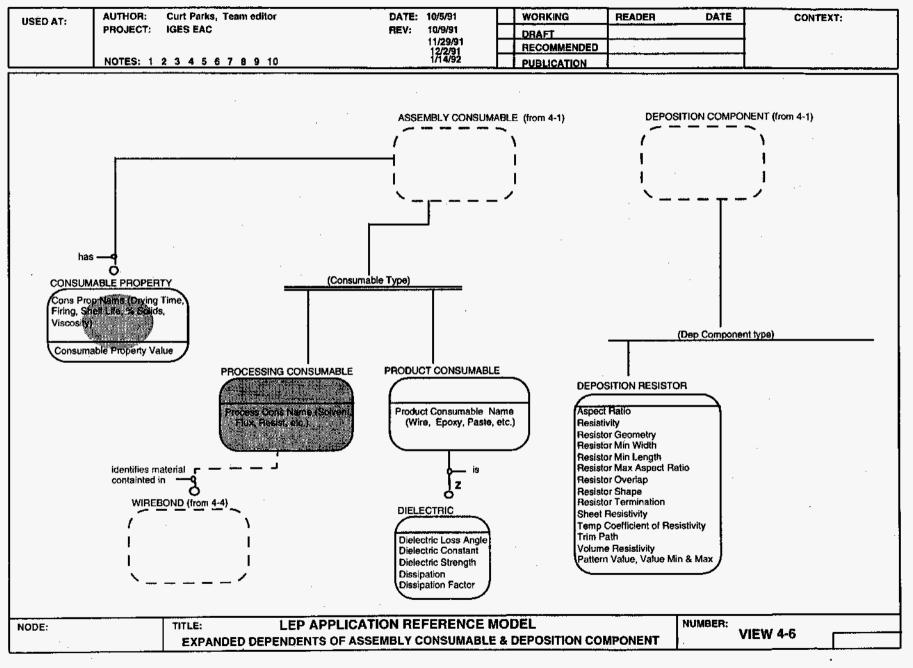

View 4-6 Expanded Dependents of Assembly Consumables and Deposition Component 41

### 5. AIM Figures (Note: AIM Objects are listed in Table of Contents)

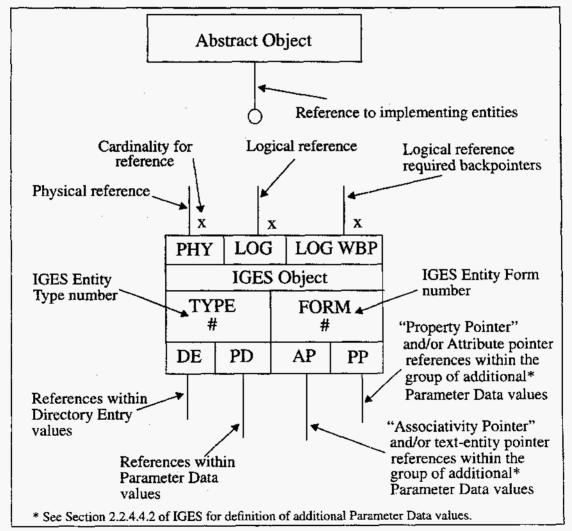

5-1. AIM Object and Referencing 48

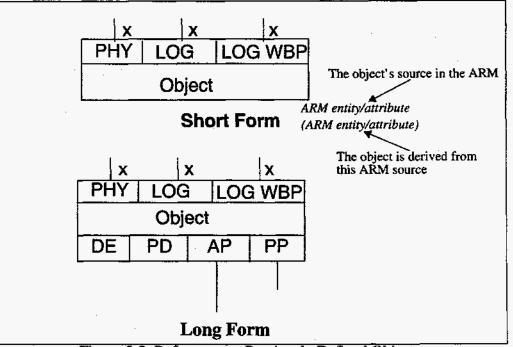

5-2. References to Previously Defined Object 49

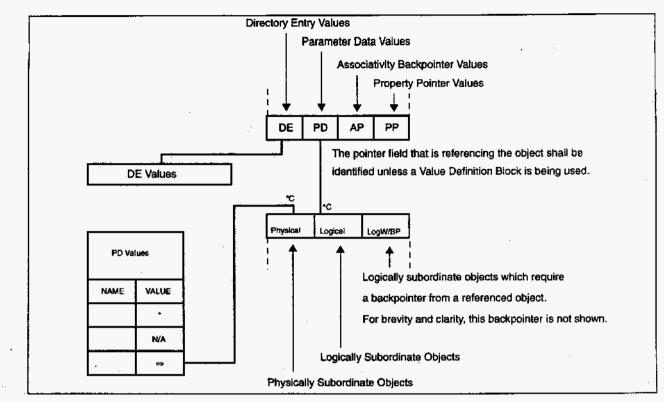

5-3. Object Field Value Restrictions 50

5.-4. Reference Mechanism 51

5-5. Representation Mechanism 51

## 6. Implementation and Conformance Testing Figures

6-1. LEP Information Interface Requirements 141

6-2. General Structure of Objects Found in a Padstack 159

6-3 LEP Semantic Features 190

#### Contents

List of Tables

2-1. Application to ARM Entity Correspondence 8

6-1. Overview of DE Settings for PDQ 151

6-2. DE Settings of Annotation Entities in a PDQ IGES File 153

6-3. IGES Data Fragments Showing Padstack Structures 158

6-4. DE Settings of Via Entities in a PDQ IGES File 164

6-5. DE Settings of LEP Instance Entities in a PDQ IGES File 169

6-6. Level Function Properties (Type 406, Form 3) 191

6-7. Semantic Properties of Top Level LEP 192

6-8. LEP Semanic Properties of Network 193

6-9. LEP Semanic Properties of Substrates 193

.6-10. Semantic Properties of Component and/or LEP 193

6-11. LEP Semantic Properties of Component Definitions (Type 308 or 320) 194

6-12. LEP Semantic Properties of Component Instances (Type 408 or 420) 194

6-13. LEP Semantic Properties of Connect Point (Type 132) 195

6-14. LEP Semantic Properties of Closed Curves 195

6-15. LEP Semantic Properties of Non-Closed Curves 196

6-16. LEP Semantic Properties of Feature Definitions 196

6-17. EP Semantic Properties of Vias 196

6-18. Production Engineering LEP Semantic Properties 197

6-19. Insertion Machinery LEP Semantic Properties 197

6-20. Placement Machinery LEP Semantic Properties 197

6-21. Wire Wrap Application LEP Semantic Properties 198

6-22. Production Test LEP Semantic Properties 198

# **BLANK PAGE**

xiv

# Initial Graphics Exchange Specification (IGES) LAYERED ELECTRICAL PRODUCT APPLICATION PROTOCOL

## **1. INTRODUCTION**

#### 1.1. Purpose

This application protocol (AP) for layered electrical product (LEP) assemblies and parts to be incorporated onto such assemblies specifies the structure of Initial Graphics Exchange Specification (IGES) data for the representation of the product definition and for the exchange of these definitions from one LEP defining application to another. Since the LEP application protocol makes use of a specific interpretation of entities in the IGES file, both the sending and receiving processors must conform to this AP with regard to the information they process. It will not suffice to simply use IGES entities listed in a subset in the AP or in IGES or other documents. Proper packaging of connectivity information, for example, is crucial to success of some subsequent operations.

## 1.2. Background

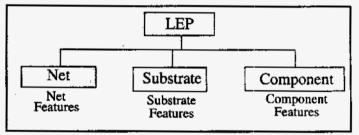

The layered electrical product is a complex assembly made up of both graphic and non-graphic information, interrelated through parent/child relations and associations.

LEPs are defined to be modules or subcircuits that are incorporated into larger electronic assemblies, in a hierarchy of devices for use in operational systems. The LEP may be either a monolithic device, such as an integrated circuit, or an assembly such as a hybrid microcircuit or printed circuit, or more than one assembly connected by means of a cable. Typically, an LEP is connected to the larger assembly with external leads or pins. An LEP assembly incorporates an insulating substrate onto which a mix of integrated circuits and other electronic components (such as thick- and thin-film devices) are interconnected.

A neutral data format serves several purposes: It permits the interchange of data between computer-aided design (CAD) and computer-aided manufacturing (CAM) systems. It allows the archiving of the LEP design in a format that can be used in the future, even if the original CAD or CAM systems or their software are no longer in use.

There are a number of motivations for developing a specified representation for LEPs. The most compelling motive is to reduce the errors created by different interpretations of a format as used for a particular product. A specified representation for LEPs can also minimize cost and maximize efficiency in the design and maintenance of translators. These uniform applications can provide means for coping with the increasing complexity of LEPs. In current practice, there is often the need for manual intervention in order to transfer the data between the CAD workstations and to the CAM stations that produce the LEP. Even in automated systems, the problem is compounded by the fact that a pair of data "translators" must be written for each pair of machines that must exchange data. If there are n machines in the system—*potentially*  $n^*(n-1)$ —translators are needed.

#### Data hub concept

A neutral format serves as a data "hub." Each station served must only translate data from its own format to the neutral format of the hub to be able to interchange with any other station interfacing with the hub. For example, data could be exported from a CAD workstation to the hub and be available there in neutral format for extraction by other CAD workstations and CAM machines. In this arrangement, for n machines in the system, there are *potentially 2\*n* translators needed, this is a substantial reduction if n is greater than four machines.

#### LEP Constructs Supporting Intelligent Representation

Intelligent Representation of a LEP includes the ability to uniquely identify different objects and attributes in the LEP. Subsequent applications may need to get "Product Data by Queries." Rather than refer to files and representations as "intelligent" we shall call them PDQ files or PDQ representations. For example, the ability to select the component by its reference designator of "R1" and its pin name of "1". This will be critical for all automated shop floor processes, such as inserters, testers, pick/place, inspection, and others.

Automated assembly graphics designed to facilitate production build need such PDQ intelligence. Nearly any automated (or partially automated) process needs the ability to query signals, Components, Pins, Pads, Test Points, Vias, fiducials, tooling holes, and mounting hardware. PDQ intelligence also relates to the organization of the semantic information in the file. Semantic properties indicate the context of the data. The LEP is conceptually the same as the "model" in a mechanical system. It reflects a real world physical structure, with an unscaled coordinate system, and reference points to align the product and various manufacturing with inspection equipment.

### **1.2.1. Electrical Assembly Complexity**

Assemblies have become increasingly complex in nature. One measure of this increased complexity is the ratio of the area of active elements (usually silicon chips) to the unoccupied area of the substrate of a hybrid microcircuit. In a single-chip package of a monolithic integrated circuit, the ratio is about 1:20; in today's typical hybrid, the ratio is from 1:10 to 1:6. Present engineering efforts have the goal of raising this ratio to 1:1, i.e., 50% of the substrate would be covered by silicon chips. These high-density hybrids are often referred to as multichip modules, or MCMs. To cope with this expanding complexity, hybrid manufacturing will increasingly depend on CAD and CAM techniques. For practical implementation of combined CAD and CAM techniques, it is important to have a single electronic representation of the CAD data available for interfacing with CAM environments. The representations described in this AP apply to MCM and conventional hybrid technology plus integrated circuits and printed boards and related products. The technologies of integrated circuits, printed wiring assemblies, flex cables and flex circuits have comparable density increases.

Many assembly manufacturers still use extensive paper documentation, such as prints and drawings, to document their product during manufacturing. Often, these drawings are produced on CAD stations that contain information that is not represented on the drawing and yet may be useful during the design process. As automated manufacturing methods become more available, such "paper" documentation will impede manufacturing. Further, as the complexity of electrical products increases, it will become much more necessary to convey this information to manufacturing machines in computer-comprehensible form.

### **1.2.2.** Consistent Information for Concurrent Engineering

Another benefit from a unified representation of the data describing a product is the ability to achieve concurrent engineering, which in the case of an LEP permits various automated and human resources to be applied to the design simultaneously. Since these resources share common data regarding the design, it is possible for various groups of engineers to refine the mechanical, electrical, thermal, and testability characteristics of the LEP in a much shorter time than would be required otherwise. In addition, concurrent engineering permits different application specialists to work in parallel with the designer. Thus, for example, those that are responsible for the manufacturing, assembly, quality, and reliability of an LEP design are able to provide suggestions concerning the design from its inception.

This method of business is in sharp contrast to the traditional methods where each department contributed sequentially to the design process of an LEP. Concurrent engineering methods promote a combined effort where all information builds on an existing model and changes can be easily accommodated through the separate functional areas. Since changes in the design are incorporated early in the design cycle, the costs of such changes is decreased. The result of effective concurrent engineering is a product at lower cost and with a shorter design cycle than would be realizable with traditional methods. Increased product quality results from accurate data transfer, as opposed to manual regeneration of CAD data on succeeding systems.

One of the ways in which the new method contrasts with the traditional methods is in the use of an architecture patterned after the ANSI-SPARC Three-Schema<sup>4</sup> structures. In this architecture, a "conceptual schema" is created which functions as a means for managing the coupling between the "user views" of the information (the external schema), and the "database implementation" needed (the internal schema) to support the information system. The language reference manual for a transfer format standard usually describes the internal format, and within the descriptions the internal schema—to varying degrees of formality— may be found. The AP provides the external schema (herein called the Application Reference Model or ARM) for a particular application area and the way the data structures (herein called the Application Interpreted Model or AIM) are to be built from the primitive constructs of the standard. In this case, as in many others, the conceptual schema is not provided explicitly. Lacking an explicit conceptual schema, the mappings between the ARM and AIM are subject to interpretation.

There are several existing neutral file specifications to describe electrical and electronic functions. These include specifications developed by the Institute for Interconnecting and Packaging Electronic Circuits (IPC), the Electronic Design Interchange Format (EDIF), the Initial Graphics Exchange Specifications (IGES), and the VHSIC Hardware Description Language (VHDL). These neutral file specifications may support many of the data elements needed to represent an LEP design. Adding these formats is encouraged, and may be accomplished by adding the appropriate models to Section 5 of this AP. During such additions, the remaining sections should be refined by agreement between the organizations that are responsible for the formats. Conflicting information requirements (e.g., Sections 3 and 4 of this document) among different formats are not considered appropriate to the goals of product data consistency.

<sup>&</sup>lt;sup>4</sup>. For more information on these data architectures see Reference 15.

# **1.3. APPLICATION PROTOCOL CONTENTS**

Section 2 of the AP provides a list of documents which are used in the construction of this protocol. Definitions of terms used in the AP are listed in alphabetical order in Section 3. Part 3.1 of this section lists terms contained in the text of the AP while part 3.2 has terms contained in the various models (AAM, ARM, AIM) of the AP. Terms in both sections are listed along with reference to the models in which they appear. Section 4 contains the ARM; an engineer's view of data about the product being designed. In Section 5, the "IGES-exchangeable" information of the ARM is defined as product model objects defined in terms of IGES entities. Section 6 defines the tests for conformance to the IGES and the object definitions as required for information uses.

The following typesetting conventions have been used to identify the particular model referred to by semantic terms in the text of this document:

Roman, Initial Cap (followed by Type, Form numbers)IGES entitiesItalic, Initial CapARM entitiesITALIC, ALL CAPAIM objects

## 1.3.1. Terms and Definitions

In addition to the definitions listed in Section 3, there are many terms associated with electrical product technologies as discussed below.

Products to which this AP apply are also distinguished by many "technology" terms. In particular, some of the terms which are associated with integrated circuits include custom, application specific integrated circuit (ASIC), gate array, digital, analog, mixed, and monolithic microwave integrated circuit (MMIC). Some of the terms which are associated with hybrid microcircuits include multi-chip module (MCM), single-chip module (SCM), microstrip assembly, thin film circuit, thick film circuit, green tape design, and surface mount technology. Some of the terms which are associated with printed circuit assembly (PCA) include printed circuit board (PCB), printed wiring board (PWB) or assembly (PWA), Flexible Circuits, Flexible Cables, and microstrip board.

The characteristics which distinguish the above domain of product types are their physical product model defined by features on one or more strata. Some features of various strata may be associated with a signal or signal bundle and/or various electrical properties.

The AP-applicable product types may also include features common to mechanical product types. Such features may include base plates, milled pockets, routed edges, threads or threaded inserts, mounting brackets, and heat sinks.

The AP information is applicable to the various ways that parts and components are defined. One way is the (external) package, usually as defined in Joint Electron Device Engineering Council (JEDEC) specifications, or the "footprint" for such a package. Another way may be the depiction of wire bonds electrically connecting a silicon chip to the leads of the package. Yet another way is the depiction of the part assembled as a component on another LEP such as an MCM or a PCA.

## 1.3.2 Scope

Layered Electrical Products include Flexible (Flex) Cables, Flex Circuits, Printed Circuit Assemblies, (includes Printed Wiring Boards), Hybrid Microcircuit Assemblies, Multi-Chip Modules, and Integrated Circuit die. The unifying element common to all these LEP technologies is the se-

ries of photomasks used in their manufacture. Practitioners<sup>5</sup> of each technology use some jargon different from all or most of the others, but the concepts are remarkably similar.

The scope of this Application Protocol includes:

- a reduced set of two-dimensional geometry sufficient to describe physical features of Layered Electrical Products, deposited components, and incorporated parts;

- connectivity of Traces, Conductive Areas, wirebonds, and Vias built into the LEP plus Pins, Pads, and Sockets of components incorporated into the LEP;

- patterns of photoplots and masks used in fabricating the LEP substrate;

- data plus context to support automated and semi-automated fabrication (such as numerically controlled drilling, panel layout, and automatic part insertion), testing of some kinds (such as bare board and in-circuit), technical illustrations (including process pictures and maintenance manuals), and Engineering Drawings (including schematics, netlists, bills of material, assembly drawings and layouts). Notice that this AP is not sufficient for these activities (for instance, a drafting AP may be needed to control dimensions and other annotation) but this AP controls the provision of much of the technical information needed by the activities.

The scope of this Application Protocol does not include:

- circuit simulation;

- behavior analysis;

- finite element analysis;

- drafting of engineering drawings;

- production of full color illustrations;

- control of process operations;

- selection of component parts;

- control of automated testing;

- vendor qualification; nor

- dispensing of consumable properties.

The AP may cover some of the activities within its scope in less detail than users might like. If so, such users are invited to send constructive suggestions to the editor of this AP.

<sup>&</sup>lt;sup>5.</sup> The Application Reference Model in 4.2.3 below was developed largely by people working in the domain of Hybrid Microcircuits. Some of the people involved had worked on the Cal Poly model years earlier. That model was developed by a team of people experienced with Printed Boards and Integrated Circuits.

## 2. APPLICATION AND CORE REQUIREMENTS

This AP applies to electrical designs which were originated in a computer program (herein called "ECAD" system) designed to capture electrical-specific information. (Technically, this term often refers to Electrical Computer Aided Engineering (CAE) systems as well as to Electrical Computer Aided Design (CAD) systems.) Some electrical designs, drawings, or descriptions may be originated on non-ECAD systems sometimes called MCAD systems; IGES files from these systems shall follow the guidelines established within the IGES Drafting Application Protocol. The following subsections provide guidelines for determining the content of those applications which depend on the electrical data (most importantly connectivity data) defined within ECAD systems.

This AP requires that non-ECAD systems either display the graphics associated with the Network Subfigure Instances and Connect Point IGES entities, or convert them to their internal version of IGES Subfigure Instance and Point entities. Non-ECAD systems are not required to write out IGES files with Network Subfigure Instances and Connect Point entities

#### **2.1. Application Information Requirements**

The core requirements were determined by examining a portion of the product life cycle. These life cycle tasks were:

- Physical Design Layout

- Manufacturing

- Visualization (for assembly, troubleshooting, etc.)

- Testing

- Logistic Support Documentation

A single LEP design file may be used as the source for several different kinds of processes. Each independent entity in the ARM may also constitute an application requirement. Further, the child entities of these entities may, together with their existence-dependent entities, be used in an application structure. For a view of the relationships between core requirements and the ARM, see table 1. The symbol "+" indicates that all child entities apply as well.

Parts are often involved in a lead preparation step such as lead bending and tinning prior to their being assembled on an LEP. Transfer of part models which specify these intermediate life cycle steps are considered within the domain of this AP.

During these life cycle stages there are data added such as pin swapping and netlist back annotation. These data are added within the CAD or CAE system; the IGES output file following such CAE operations is differentiated by a different file name. Different fabrication facilities have different capabilities and pre-defined processes. Thus it may be premature for the IGES file to contain detailed information governing the fabrication processes prior to the selection of a facility and receipt of a commitment at that facility. As concurrent engineering becomes a reality, this will be less of a concern because the fabrication planner will participate in the definition captured and then transferred using IGES.

This AP is not applicable to the electrical product life cycle phases preceding the capture of the structural design by way of a schematic drawing or netlist representation unless the behavior is presented as a graphic such as a waveform. Where product behavioral definition exists in a data format other than IGES, provisions will be defined for the association of behavior at a logical pin (or "port") with a schematic or physical pin defined within the IGES file. Such association is fre-

quently achieved in CAE systems by matching on the assembly component's reference designator and pin number occurring in each data definition.

The information for all life cycle phases may originate in a computer aided design (CAD) system. Some information may only be computer-processed within a Computer Aided Engineering (CAE) system. Or, part of the information for any category may be created by manual—non-CAD/ CAE— means. LEP information from any source must be constrained semantically for use within the AP, and further, the requirements for the IGES form defined herein is (syntactically) constrained by the constructs in the application interpretation model.

All functionality categories which have been originated in a CAD system are capable of being transmitted to another, or an intermediate CAD or CAE system. In this event, much of the information may be "exchanged" without distinction. When electrical-specific information has been added by a CAE system, such information may not be comprehensible by a CAD system. The CAD system receiving a CAE-created file is required to ignore (i.e., to not process) the connectivity and electrical property entities, but to process and display the physical product model.

All information originated from a CAE system shall be processed by another CAE system; whether through direct conversion into the CAE native data, or through display to the CAE operator in such a way that the information may be accommodated by manual entry means.

For example, a design exchanged between CAD systems may adopt a level of information content that is greater than the Drawing. The receiving CAD system would benefit by "knowing" the properties and rules defined in the source system in addition to the product as a drawing graphic.

#### LEP Entity Usage for Core Applications

Section 5. identifies objects, which in turn defines which entities are required to support a specific application. For example, production test requires Network Subfigure Instances (representing components) and Connect Points (representing pins), in order to identify each testable point uniquely.

Entities may not always map directly between various applications. Section 6.6. contains guidelines for specific applications. For example, within the photolithography application, some programs will accept complex geometry, text strings, tapered lines, and subfigure constructions. Other programs can understand no more than simple fixed width lines (no arcs), and a few predefined geometries called flashes.

There are two different ways of looking at this problem. One approach would have the LEP AP detail which entities may be found in conformant files, implying a method to process those entities into something the application would accept. The second approach would detail which entities will probably be accepted by the application. The LEP AP follows the first approach, and assumes there is a tool available to perform required tasks of simplifying and remapping entities from the LEP AP conformant file.

### 2.2. Application and ARM Correspondence

The LEP is defined in this AP by a combination of documents (called presentation) and CAD/ ECAD data (called representation). The CAD/ECAD data consists of the screen display data and the CAD/ECAD product model itself. The ARM reflects the data distinction. For example, the product may be defined through a drawing produced manually or on a CAD system, such as a Specification Control Drawing, CAD systems may be utilized in such a way as to produce a "pa-

per document" intended for human interpretation. Information such as the electrical schematic and waveforms are frequently treated as such drawing data. Some applications include the CAD or ECAD display information such as the color with which a particular system-layer is displayed. Some applications are developed such that lists may be extracted (e.g., net lists, test probe locations, and drill lists) from the ECAD or CAE model of the product.

For purposes of this AP, the following table indicates appropriate applications and the entities in the ARM which are related. The symbol "+" indicates that all child entities apply as well.

| Application                               | CAD/<br>CAE | ARM Entities                                 |  |

|-------------------------------------------|-------------|----------------------------------------------|--|

| Bill of Materials                         | both        | Component, Assembly Consumables, Substrate   |  |

| Package                                   | CAE         | Device Package                               |  |

| Visualization                             | CAE         | LEP Documentation +                          |  |

| Geometry                                  | both        | Geometry                                     |  |

| Artwork                                   | both        | Pattern +                                    |  |

| Surface mount pick & place                | both        | Area+, Flashed Geometry, Via Hole, Probe Pad |  |

| Panel                                     | both        | Panel MultiUp, LEP Assembly                  |  |

| Test programs                             | CAE         | LEP Assembly Component                       |  |

| Wire Wrap                                 | CAE         | Pin +                                        |  |

| Flex tape                                 | CAE         | Device Package                               |  |

| DITMCO (continuity test) support          | CAE         | Test, Net                                    |  |

| Thru-hole auto-insert                     | CAE         | Process Step, LEP Assembly Component         |  |

| Semi-automatic inser-<br>tion             | CAE         | Process Step, LEP Assembly Component         |  |

| Combination test pro-<br>grams & fixtures | CAE         | Tool, Test                                   |  |

| SMT LEP producibil-<br>ity                | CAE         | Process Step                                 |  |

| Adhesive dispensing                       | both        | Process Step                                 |  |

| In-work assy graphics                     | both        | LEP CAD Presentation                         |  |

| Table 2-1: Application | n to ARM Entity | Correspondence |

|------------------------|-----------------|----------------|

|------------------------|-----------------|----------------|

The Application Reference Model (ARM) is explained and presented in Section 4. The ARM is constructed in terms used within the electronic design and fabrication community (i.e., an external schema). For example Part and Component are used, and are given definitions appropriate to those found in engineering as related to the use of CAD systems and supporting libraries. The IDEF1X modeling technique is used to develop the ARM and a brief tutorial on how to read the model is included.

The ARM was constructed to depict the complete layout-to-manufacturing of the LEP; primarily to be understandable by the engineer and planner. The AIM, described below and closely related to the IGES file structures, may not contain all ARM structures but will be more detailed. The ARM entities which are not defined as AIM objects are graphically marked in the ARM.

The Application Interpretive Model (AIM) is described and presented in Section 5. The mapping of the ARM to AIM is explained. The objects declared in this section are associated to general and specific CAD data items (i.e., an internal schema). A description of the IGES file structure and the breakdown of its sections is given. A modeling syntax is used to develop the AIM and a brief tutorial on how to read the model is included.

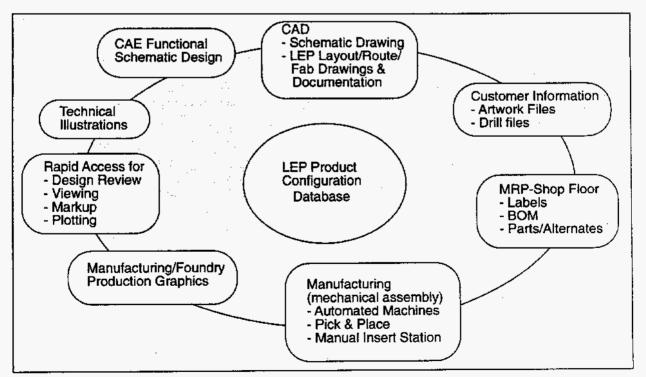

Section 6 details implementation and conformance guidelines for this Application Protocol. Process conformance requirements and testing purposes are given. Appendix A contains the Activity Model which indicates the processes which utilize ARM information. Appendix B has a parameter listing of typical LEP processing parameters/variables and their values.

#### 2.3. Normative References

This AP is specifically applicable to IGES version 5.2. The versions of IGES listed below include electrical product capability; any one of them may be cited in an exchange. Earlier versions of IGES may contain electrical product-defining objects compliant with this AP.

IGES versions 1.0, 3.0, 4.0, and 5.2 have been registered as an American National Standard (ANS) Y14.26M by the American National Standards Institute. Additionally, IGES version 4.0 is registered by NIST as a Federal Information Processing Standard; FIPS PUB 177. IGES electrical-related entities and the versions in which each was first published are identified in Section 5 of this document.

- IPC-T-50E, "Terms and Definitions for Interconnecting and Packaging Electronic Circuits," February, 1991, Institute for Interconnecting and Packaging Electronic Circuits, Lincolnwood, IL 60646.

- MIL-D-28000A, 10 February 1992, and Amendment 1, February 1993; Digital Representation for Communication of Product Data; IGES Application Subsets and IGES Application Protocols, Director, CALS Evaluation and Integration Office, Pentagon Room 3D833, Washington, DC 20301

- 3. MIL-H-38534, "Hybrid Microcircuits, General Specification for," 31 March 1989.

- <u>The Initial Graphics Exchange Specification (IGES) Version 5.2, an American National</u> <u>Standard</u>, US PRO/IPO-100, November, 1993. Available from the National Computer Graphics Association (NCGA) Technical Services and Standards, 2722 Merilee Drive Suite 200, Fairfax, Virginia 22031.

## **2.4 Informative References**

- Smith, B., Wellington, J., <u>The Initial Graphics Exchange Specification (IGES) Version 3.0</u>, NBSIR 86-3359, U.S. National Bureau of Standards, April 1986. Available from the National Technical Information Service (NTIS), Fairfax, VA 22031 as PB86-199759.

- Smith, B., Rinaudot, G., Wright, T.; Reed, K., <u>The Initial Graphics Exchange Specification</u> (IGES) Version 4.0, NBSIR 88-3813, U.S. National Bureau of Standards, June 1988. Available from the National Technical Information Service (NTIS), Fairfax, VA 22031 as PB88-235452.

- Reed, K., Harrod Jr., D., Conroy, W., <u>The Initial Graphics Exchange Specification (IGES)</u> <u>Version 5.0</u>, NISTIR 4412, National Institute of Standards & Technology, September 1990. Available from the National Computer Graphics Association (NCGA) Technical Services and Standards, 2722 Merilee Drive Suite 200, Fairfax, Virginia 22031.

- Reed, K.; Kelly, J.C., Harrod Jr., D., Conroy, W., <u>The Initial Graphics Exchange Specification</u> (IGES) Version 5.1, US PRO/IPO, September, 1991. Available from the National Computer Graphics Association (NCGA) Technical Services and Standards, 2722 Merilee Drive Suite 200, Fairfax, Virginia 22031.

- O'Connell, L., "Guide to the IGES Electrical Entities," EACP-2.3, unpublished, June 24, 1989, Available from IPO Office, National Institute of Standards and Technology, Bldg. 220, Room A-127, Gaithersburg, Maryland 20899

- Harrison, R.J. and Palmer, M. E., "Guidelines for the Specification and Validation of IGES Application Protocols" NISTIR 88-3646, January 1989. Available from the National Technical Information Service (NTIS), Springfield, VA 22161, October 1990, (110 pages).

- "Integration Definition for Information Modeling (IDEF1X)," FIPS PUB 184, National Institute of Standards and Technology, Computer Systems Laboratory, Gaithersburg, Maryland 20899, December 21, 1993.

- "Integration Definition for Function Modeling (IDEF0)," FIPS PUB 183, National Institute of Standards and Technology, Computer Systems Laboratory, Gaithersburg, Maryland 20899, December 21, 1993.

- 13. Parks, C., "Tutorial: Reading and Reviewing the Common Schema for Electrical Design and Analysis," Proceedings of the 24th Design Automation Conference; IEEE & ACM, June 30, 1987, paper 27.2.

- 14. Loomis, M., "Data Modeling The IDEF1X Technique," Proceedings of the IEEE 1986 Phoenix Conference on Computers and Communications, Phoenix Arizona, page 146-149.

- Tsichritzis, D.; Klug, A.; The ANSI/X3/SPARC DBMS Framework Report of the Study Group on Database Management Systems, X3 project 226, 1977, AFIPS Press, 210 Summit Avenue, Montvale, NJ 07645

- Palmer, M.E. and Reed, K.A., "3D Piping IGES Application Protocol, Version 1.0," NISTIR 4420 (257 pages), October 1990, Available from the National Technical Information Service (NTIS), Springfield, VA 22161.

- 17. ISO/IEC 10641-1993(E) Information Technology Computer Graphics and Image Processing - Conformance Testing of Implementations of Graphics Standards. First Edition, 31 pp., CH-1211 Genève 20, Switzerland.

### **3. DEFINITIONS**

Section 3.1 contains those definitions which apply to the notion of an application protocol; they are included as an assist in understanding the content of this document. Section 3.2 combines the definitions of the functions (in Appendix A), the entities (in Section 4.2.3), and the objects (in Section 5).

## **3.1. IGES Application Protocol Definitions**

APPLICATION: An enterprise process that puts product data to use. The scope of an application is defined by the class of product, the supported stages in the life cycle of the product, the uses of the product data, and the disciplines that participate in that use.

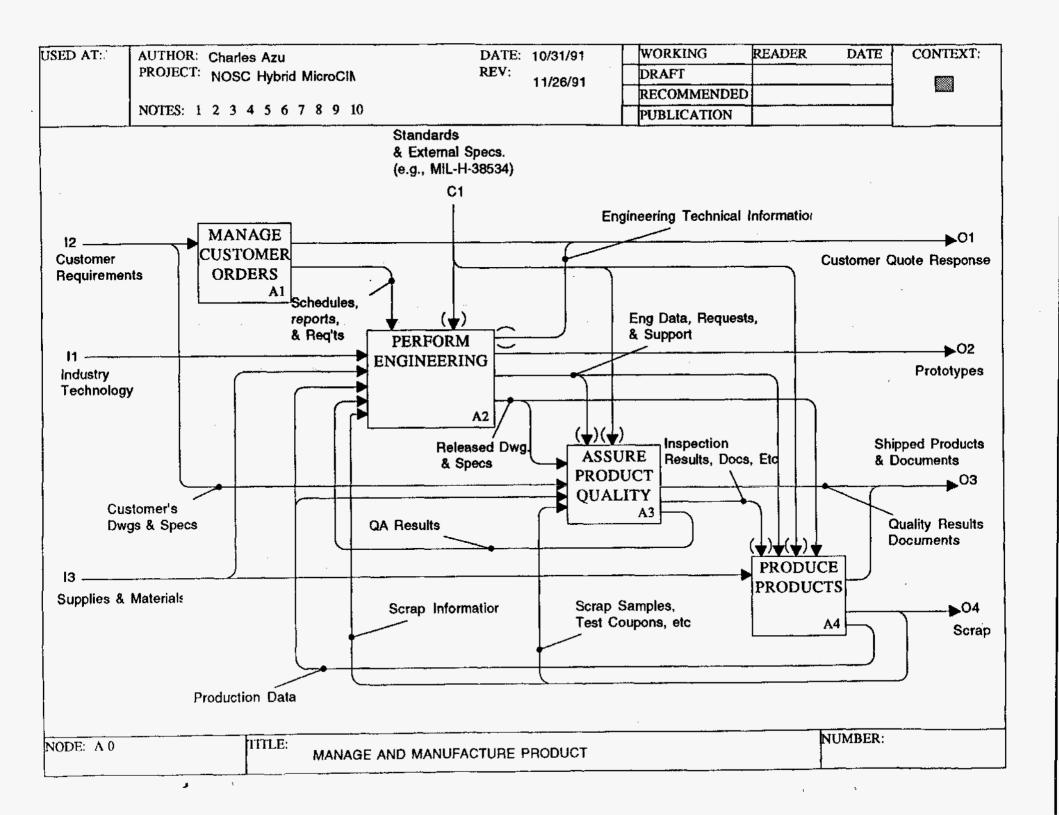

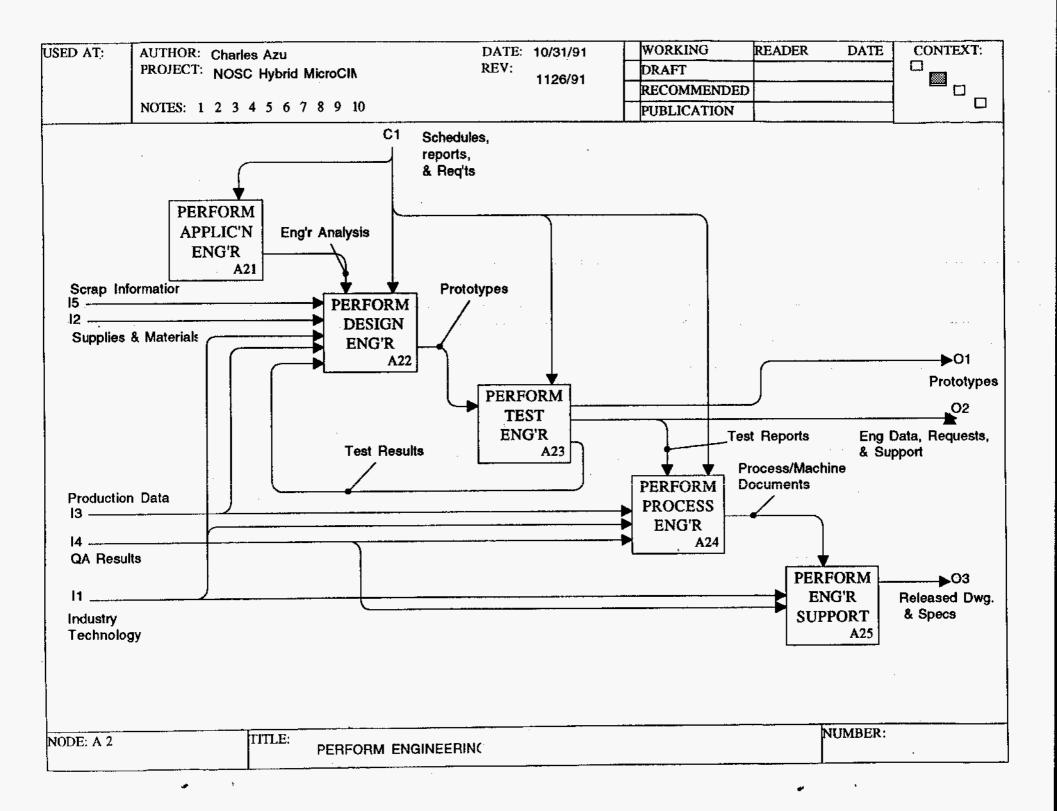

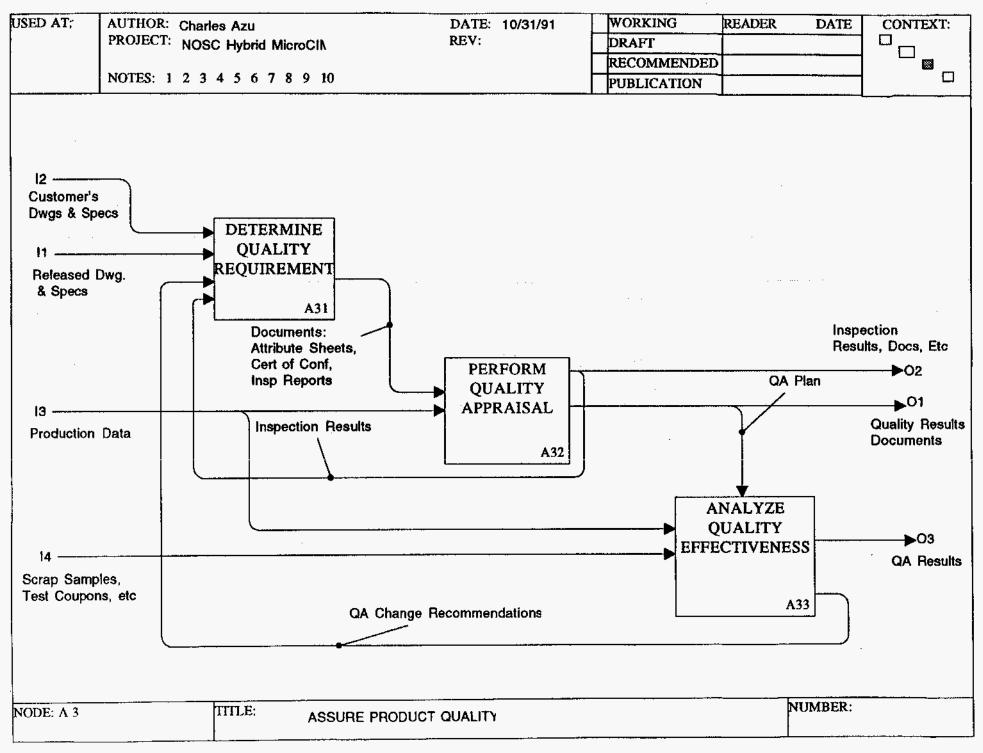

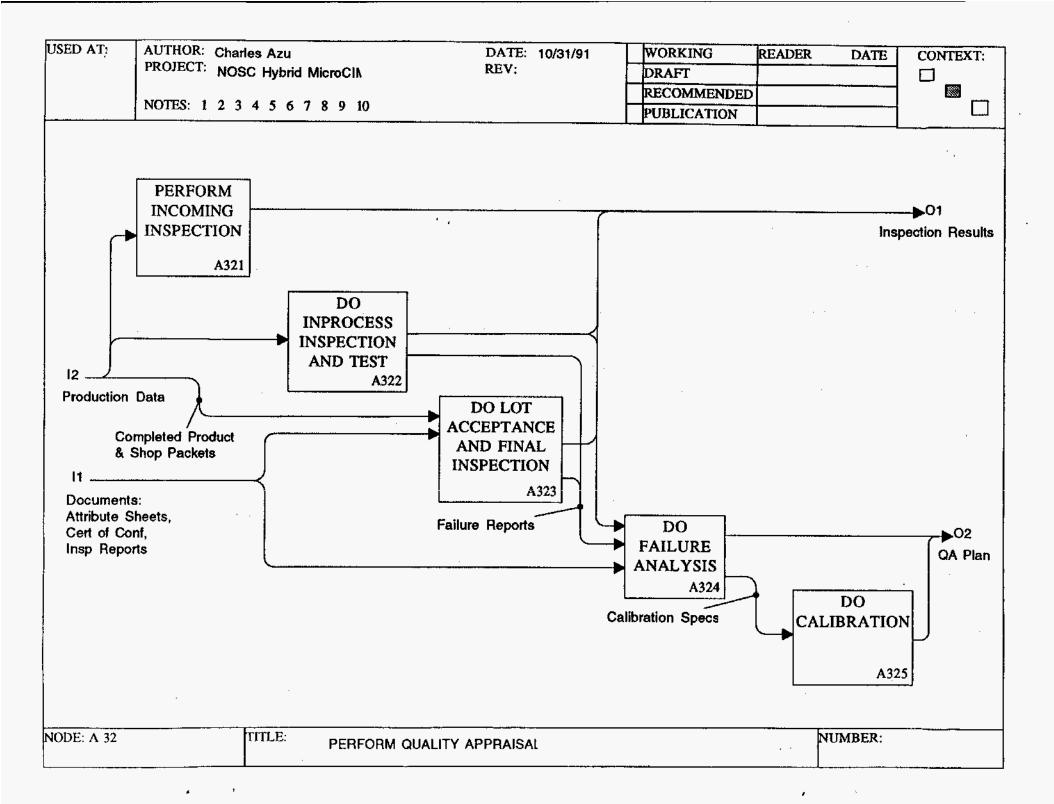

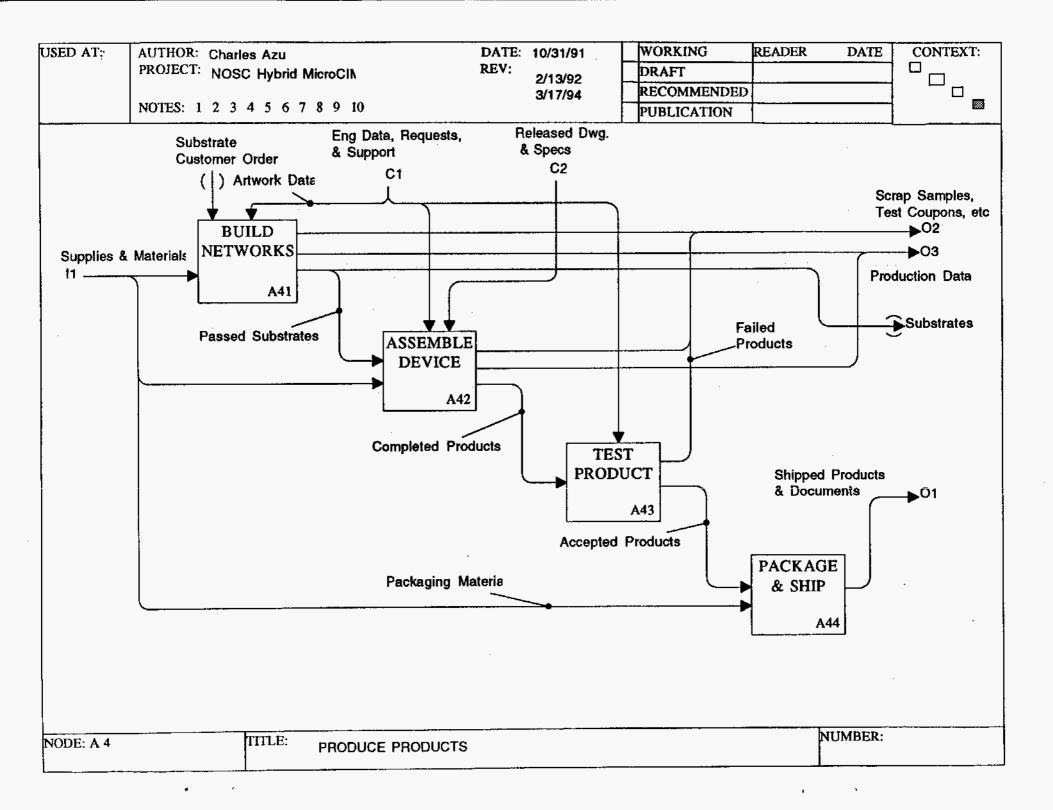

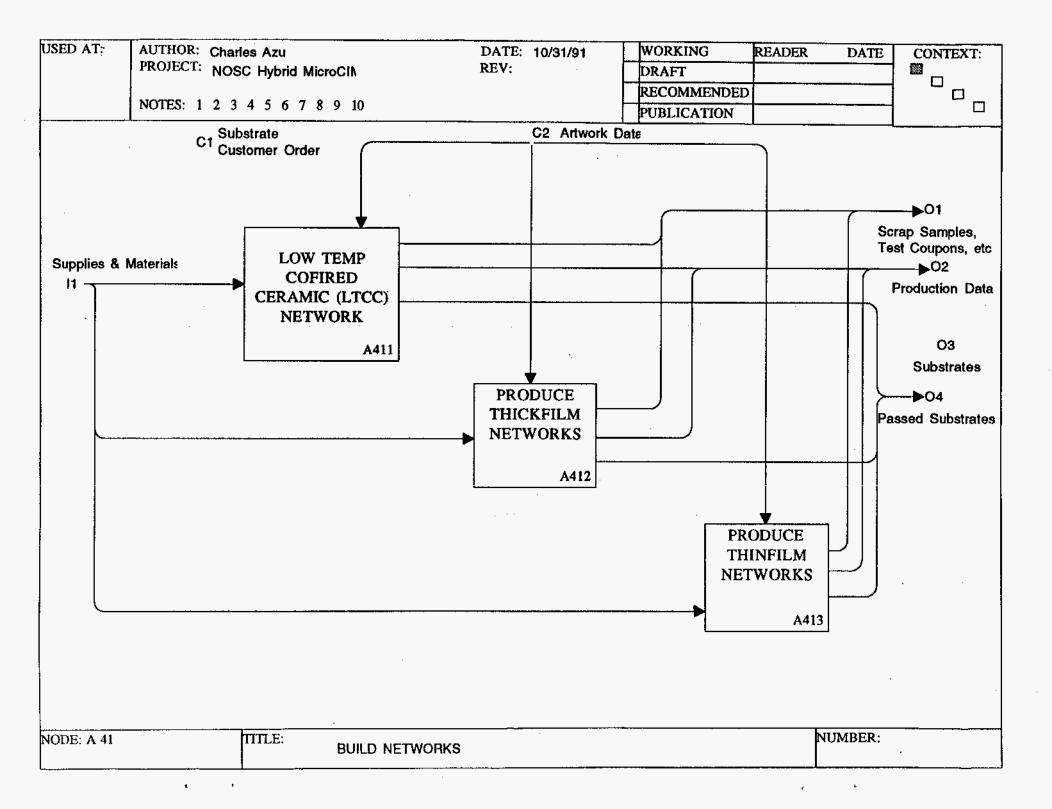

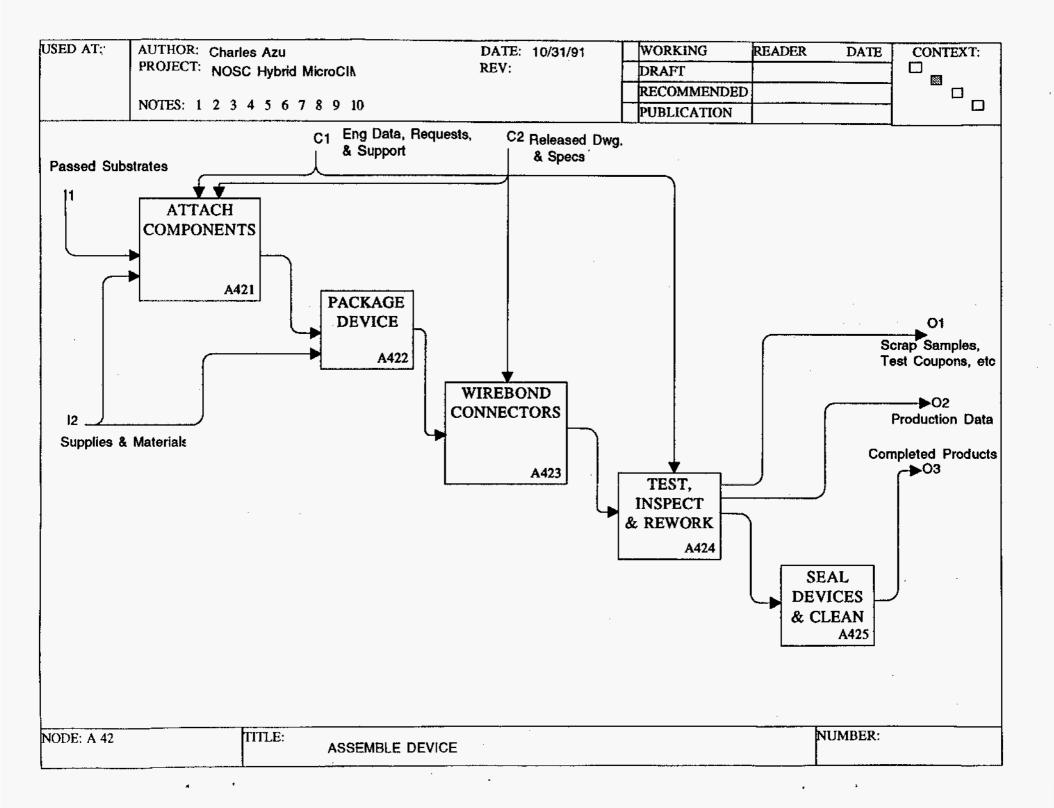

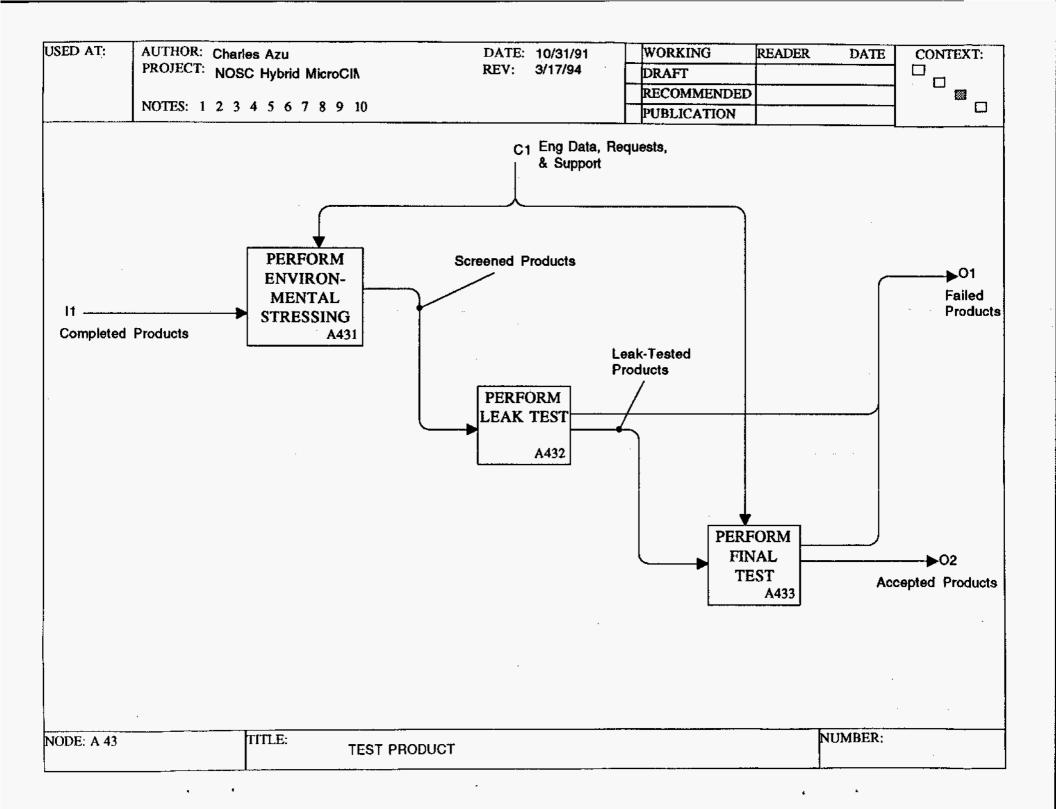

APPLICATION ACTIVITY MODEL (AAM) - A structured decomposition of the tasks which are followed to achieve the particular product defined by the AP. The AAM identifies the context of the AP as well as the activities which create and use the information being defined. The AAM is constructed to be generally representative of the industry, and includes processes which are, or could be, largely automated.

APPLICATION INTERPRETED MODEL (AIM) - An information model that identifies the information structures of a particular data format specification. The AIM is defined to accomplish a physical implementation of an associated application reference model (ARM). This AIM is prepared at a level of abstraction that is sufficient for selecting the necessary entities for an application.

APPLICATION PROTOCOL (AP): Defines the scope and information domain of an application and specifies the rules for using IGES, or some other standard, to enable unambiguous transfer of the application information, and the testing of those transfer implementations.

APPLICATION REFERENCE MODEL (ARM) - An information model that describes the information structures and constraints for an application area. The ARM is defined in terms of Entities, Attributes, and Relationships. The information model uses application specific terminology and rules familiar to an expert from the application area. The model is independent of any physical implementation and can be validated by an expert from the application area.

APPLICATION SUBSET - An unambiguous set of entities which span the data requirements of the specified application. The set of entities is determined on the basis of the Application Reference Model.

ASSEMBLY - In general (e.g., from Websters): Parts fitted together to make a whole. The assembly referred to in this AP is taken to mean parts placed on, and/or connected to, an interconnecting part generally in the form of a flat substrate on which has been deposited alternate layers of metalized patterns and insulation material; the whole of which has been defined as to provide a specified part of the function of a system. An assembly may be used as a part on another assembly.

ATTRIBUTE - A property or element of information associated with an Entity. An instance of the attribute must exist for any instance of the Entity to which it belongs.

CONFORMANCE - (Ref. 17) Adherence of an implementation to the requirements of one or more specific standards or technical specifications.

ENTITY - The basic unit of data classes in the ARM. Also the basic data types identified in the

AIM. The term applies to single units which may be individual elements of geometry, individual elements of annotation, or collections of geometry or annotation elements that are combined to form more complex data structures.

IGES POSTPROCESSOR - A software unit that transfers CAD information from the IGES format to the CAD database format of a particular system. The software is usually developed and maintained by a commercial CAD system vendor.

IGES PREPROCESSOR - A software unit that translates CAD information from the CAD database format of a particular CAD system to the IGES format. The software unit is usually developed and maintained by a commercial CAD system vendor.

INFORMATION - In mathematical communication theory<sup>1</sup>, a measure (strongly related to entropy) of the freedom of choice available when selecting a message to be sent. In the context of this AP, each message consists of graphics, or numeric quantities, or text strings, or various combinations of these three forms of data. The messages—in a particular data format—are augmented by definitions, usages, and context(s) supplied in separately communicated semantic proscriptions (e.g., IGES and this AP). Messages are required to transmit data accurately, to convey meaning precisely, and to prompt appropriate reactions at the destination by a human or a computer.

INFORMATION CONFIGURATION CONTROL - An approach that consists of specifying, documenting, and controlling both the creation and modification of information and the subsequent translation and exchange of the information between different systems and formats. The approach requires substantial documentation for both the syntax (the format) and the semantics (the meaning) attached to an item of information.

INSTANCE - In general (e.g., from Websters): A detail or circumstance. In this AP an instance indicates that a specific member of an object class is being referenced. An example of an object class may be the assembly as identified by a drawing number. An example of an instance may be a completed assembly identified by a serial number.

LAYERED ELECTRICAL PRODUCT (LEP) - A broad category of electronic product types which are characterized by a two or more laminar strata stacked in sequential order. The completed structure serves to conduct electrical signals and may contain passive or active electrical functional elements. The structure is usually designed using two-dimension (2-D) graphics which result in photo-process tooling. Additional components or other LEPs may be added to complete the assembly. Descriptions within this document which apply additionally to products such as integrated circuits, printed circuit boards, flex harnesses are labeled with this term.

OCCURRENCE - In general (e.g., from Websters): Anything that happens or takes place. In this AP the term is sometimes used to label an object class which exists as a result of a specific grouping of two or more other object classes.

PRODUCT - A result produced by specified activities or used for specified activities.

PRODUCT DATA - The set of data elements that is necessary to fully support a product over its expected life cycle. The set of data elements includes all of the product definition data plus other

<sup>1.</sup> See especially Shannon, C.E., Weaver, W., *The Mathematical Theory of Communication*, Urbana, University of Illinois Press, 1949. Shannon's work includes insights on both semantics and behavior.

data pertaining to the operation and maintenance of the product until it is removed from service.

PRODUCT DEFINITION DATA - The set of data elements that completely define a product for a certain discipline; a subset of product data. This set of data elements includes the geometry, topology, features, tolerances, and relationships necessary to completely define a component product or an assembly of products and is structured such that it can be used by one or more applications.

RELATIONSHIP - The identified association of two entities to each other. The two entities and their relationship taken together constitute a natural language *role* expressed in the data model. Example: Assuming the entities "Car" and "Person" are associated with relationship "Owned" in a data model Then the role may be expressed in natural language as: "A Car is owned by a person." The exact role stated depends on the modeling language's interpretation specifications.

SEMANTICS - The meaning that is given or assigned to an item of information. The meaning is assigned to an item of information on the basis of its application area.

SYNTAX - The structure of expressions in a language. [3] This structure is described in a specification such as IGES.

UNIT of FUNCTIONALITY - A collection of entities, attributes and relationships that conveys one or more well-defined concepts (within the scope of the AP) such that removal of any component would render the concept(s) incomplete or ambiguous. (See "Current Issues on STEP APs," 10/9/91.)

#### **3.2. LEP Application Definitions**

The bracketed character following the term indicates that the definition applies primarily to the AAM [A], AIM [I], or the ARM [R].

Note: definitions preceded by (T50) are from IPC-T-50E, December 1991.

ANNOTATION - [R] Text or legend pertinent to a design; text may appear as data related to legend on a multilayer substrate, lettering on a drawing, or other types of symbols.

APERTURE CODE - [R] Code representing aperture number used in plot file intended for a plotter such as a Gerber Plotter.

APERTURE NUMBER - The number for a photoplotter aperture setting, number used in pin and pad tables, and formatter table corresponding to a position on the aperture wheel.

APERTURE SHAPE - [R] Shape of aperture, such as one of the following: round, square, donut.

APERTURE SIZE - [R] The x,y dimensions of the aperture such as width or diameter where appropriate.

ART WORK (T50) - [R] An accurately-scaled configuration that is used to produce the artwork master used for production.

ART WORK GEOMETRY (target) (outside circuit) - [R] A collection of primitive shapes such as arcs, areas, and lines.

ART WORK TEXT - [R] Identifying text which calls out the product number and configuration number as well as program configuration for the art work. It identifies layer, revision, product number.

ASPECT RATIO (of Deposition Resistor) - [R] The ratio of the length of a thick or thin film resistor to its width, or the ratio between the resistance of the resistor and the sheet resistivity of the ink. This is also the number of effective "squares" in the design of a resistor.

ASSEMBLY CONSUMABLES - [R] A type of consumable that becomes part of the finished product. See also Consumable.

ASSEMBLY ID - [R] All information needed to uniquely identify a particular assembly, manufactured in-house or purchased. The identification may include, but is not limited to, the Drawing Number, Revision, Revision Status, Dash Number, Cage Number, case style, and other product notation.

ASSEMBLY OCCURRENCE - [R] Either a single product which is defined to become part of an assembly, or two products which are identified as items to be assembled into the next higher assembly. The occurrence identified may be noted in a bill of materials, or may be in-process work which must be identified for manufacturing tracking.

ASSEMBLY OCCURRENCE ID - [R] All information required to uniquely identify (ID) a product and the assembly it is assembled to. The identification may include, but is not limited to, the Drawing Number, Revision, Revision Status, Dash Number, Cage Number, case style, and other product notation.

ASSEMBLY TYPE - [R] The name of the class of assembly which indicated the general stage of completion of the electronic product. Examples are screened substrate, subassembly, component assembly, and final assembly.

ATTACHMENT - [R] Method used to describe how a component can be held on to the substrate such as solder, or epoxy.

ATTACH MATERIAL PATTERN - [R] Pattern associated with a component for the purpose of specifying the location and shape of an attachment medium or material.

AUTOINSERTION - An automated process by which through-hole components are selected, grasped, and positioned into the appropriate component holes in a PCB. Bonding of the component to the PCB may employ solder paste, glue or other consumables.

BACK PAD POLARIZATION - [R] Description of which pin of a component such as a diode or IC chip is surface-mounted to an LEP. (The terminal so mounted is the *back pad*.)

BACK PAD POLARIZATION NAME - [R] Name associated with the back pad such as anode.

BEHAVIOR REQUIREMENT - [R] The performance needed from a circuit (specified through the use of a "hardware description language") which is to be or has been packaged in an LEP.

BILL OF MATERIALS - [R] A formatted list of products (instances of LEP Assembly Components) used for a particular assembly.

BLIND VIA - A via that is visible from only one side or the other of a design. (Derived from Via attributes.)

BONDING PADS - [R] Areas of metallization on the component and the LEP substrate that permits connection of the wire or circuit elements.

BURIED VIA - A via hole not extending to the surface. A buried via is completely contained within the inner layers of a design and therefore is not visible from the outside layers. May be referred to as an interstitial via hole. (Derived from Via attributes.)

CAD LAYER - [R] A method of separating information in a CAD system for the purpose of display or processing. Some CAD layers correspond to artwork layers.

CAGE NUMBER - [R] The military-assigned identification of the manufacturer responsible for the product definition.

CAPACITOR COMPONENT - [R] A kind of component used to add capacitance to a circuit.

CAPACITOR MATERIAL - [R] The type-name for a capacitor derived from the dielectric material of the capacitor

CATCH PAD - [R] Metallization patterns on a conductive layer associated with a via which aid in the interconnection of a via with its associated traces.

CHECKPLOT SCALE (T50) - [R] Drawing scale used on interim drawing for graphical data verification. (called a check plot.)

COMPONENT - A Part which has been installed in an LEP, thereby acquiring a Reference Designator and a location within the LEP. The Component does not lose its Part characteristics as described in the catalogue of parts.

COMPONENT ATTACH - [A] The placing of a component (chip) on a substrate or header in a manner which causes it to mechanically bond.

COMPONENT LOCATION PLACEMENT TOLERANCE - [R] The amount of displacement form the specified location which is acceptable.

COMPONENT LOCATION X Y - [R] The coordinates specified for the location of a component within an assembly.

COMPONENT ORIENTATION (T50) - [R] The direction in which the components on a printed board or other assembly are lined up electrically with respect to the polarity of polarized components, with respect to one another, and with respect to the board outline.

COMPONENT PLACEMENT RESTRICTION - [R] An area on substrate where components can not be placed.

COMPONENT POSITION - [R] The location at which a component is placed.

COMPONENT TOLERANCE - [R] The range of acceptable component values; usually specified as a percentage of the nominal specified value.

COMPONENT VALUE - [R] The parameter associated with some component types which may be used in the fabrication of the components.

COMPONENT VALUE TOLERANCE - [R] A range of permissible product's values.

COMPONENT VOLTAGE RATING - [R] Maximum voltage specified that can be placed across a component.

CONDUCTIVE PATTERN - [R] The configuration or design of the conductive material on the substrate. For a lep, the pattern includes conductors, lands, and through connections (vias) when these connections are an integral part of the manufacturing process.

CONDUCTIVITY, ELECTRICAL - [R] The capability of a material to carry an electrical current. The reciprocal of resistivity.

CONSUMABLE - [R] An in-process or an end item material supplied in bulk form.

#### Definitions

CONSUMABLE ID - [R] All information needed to uniquely identify a particular consumable, manufactured in-house or purchased. The identification may include, but is not limited to, the Drawing Number, Revision, Revision Status, Dash Number, Cage Number, and other material notation.

CONSUMABLE NAME - [R] The name given to bulk-purchase materials used in the assembly process, such as solder, flux, etc.

CONSUMABLE PROPERTY - [R] Properties of a consumable such as shelf life, expiration date.

CONSUMABLE PROPERTY NAME - [R] The name of a Consumable Property.

CONSUMABLE PROPERTY VALUE - [R] The measurement value associated with a Consumable Property.

CONSUMABLE TYPE - [R] The generic classification given to consumables, such as epoxy.

CROSSOVER - The transverse crossing of metallization paths without mutual electrical contact achieved by the deposition of an insulating layer between the conducting paths at the area of crossing. Dielectrics can be used with crossover conductive patterns, acting as a bridge over previously screened conductive material. (derived from trace geometry.)

DEFAULT DESIGN RULE - [R] The specifications which are followed during layout of the patterns on the layers of an electronic assembly. Examples are the maximum trace width, or the minimum conductor spacing.

DEFAULT DESIGN RULE DESCRIPTION - [R] The description of a Design Rule that is employed when no other rule is specified.

DEFAULT DESIGN RULE NAME - [R] The name associated with a Design Rule.

DEPOSITION COMPONENT - [R] Components which are fabricated coincidentally with the interconnects as opposed to components which are attached to the substrate after the interconnect network is complete.

DEPOSITION RESISTOR - [R] The deposition of resistor material which is formed as part of the conductive circuitry on a substrate layer. The resistor is a component in the sense of the electrical function of the circuit, but not in the sense of a separate product to be assembled to the completed substrate.

DEPOSITION SEQUENCE NUMBER - [R] A particular layer's position on the LEP substrate with respect to the first layer.

DEPOSITION TYPE - [R] A category used to describe the technology used (THICK or THIN film) to create the component.

DERATING - [R] A factor which is applied to a product parameter to insure that reliability requirements are met; such as derate resistor power rating by 50%.

DESIGN RULE - [R] A guideline that determines behavior with respect to specified design parameters. Becomes a constraint on the functional and physical layout. An example is a rule that ensures that minimum distance between elements in a design file is maintained.

DESIGN RULE CHECK (DRC) - [R] A process to enforce the design rules.

DESIGN RULE VALUE - [R] The measurement assigned to a particular restriction for a product's design.

#### Definitions

DEVICE PIN ASSOCIATIVITY- [R] Functional relationships among pins that are needed to allow operations such as gate swapping or pin swapping to improve trace routing

DIE - [A] The uncased and normally leadless form of an electronic component that is either active or passive, discrete active device or integrated circuit.

DIE BONDING - [A] The attachment of an integrated circuit chip to a substrate or header.

DIELECTRIC - [R] An insulating material used to separate conductors.

DIELECTRIC CONSTANT - The ratio of the capacitance, Cx, of a given configuration of electrodes with a specified dielectric, to the capacitance Cv, of the same electrode configuration having a vacuum as a dielectric.

DIELECTRIC LOSS ANGLE - [R] The difference between 90 degrees and the dielectric phase angle given a set of operating conditions. May be referred to as the dielectric phase difference.

DIELECTRIC OUTLINE - [R] The boundary of an insulating layer.