# Purdue University Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

12-2016

# Approximate computing: An integrated cross-layer framework

Swagath Venkataramani Purdue University

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_dissertations Part of the <u>Computer Engineering Commons</u>, and the <u>Electrical and Computer Engineering</u> <u>Commons</u>

#### **Recommended** Citation

Venkataramani, Swagath, "Approximate computing: An integrated cross-layer framework" (2016). *Open Access Dissertations*. 1022. https://docs.lib.purdue.edu/open\_access\_dissertations/1022

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# PURDUE UNIVERSITY GRADUATE SCHOOL Thesis/Dissertation Acceptance

This is to certify that the thesis/dissertation prepared

By Swagath Venkataramani

Entitled Approximate Computing: An Integrated Cross-layer Framework

For the degree of \_\_\_\_\_ Doctor of Philosophy

Is approved by the final examining committee:

ANAND RAGHUNATHAN

CHENG-KOK KOH

KAUSHIK ROY

VIJAY RAGHUNATHAN

To the best of my knowledge and as understood by the student in the Thesis/Dissertation Agreement, Publication Delay, and Certification/Disclaimer (Graduate School Form 32), this thesis/dissertation adheres to the provisions of Purdue University's "Policy on Integrity in Research" and the use of copyrighted material.

Approved by Major Professor(s):

| Approved by: V. Balakrishnan | 10/03/2016 |

|------------------------------|------------|

|                              |            |

Head of the Department Graduate Program

Date

# APPROXIMATE COMPUTING:

# AN INTEGRATED CROSS-LAYER FRAMEWORK

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Swagath Venkataramani

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

December 2016

Purdue University

West Lafayette, Indiana

கற்றது கைமண் அளவு, கல்லாதது உலகளவு -- ஒளவையார்

What you have learned is a mere handful; What is yet to be learnt is the size of the world! – Auvayar

#### ACKNOWLEDGMENTS

The true highlight of my PhD, more than the projects I worked on, was the people I worked with. I had the opportunity to collaborate with people from diverse technical backgrounds ranging from devices to algorithms, and the unique perspective that each brought forward was truly an enriching learning experience, for which I am ever grateful. I truly relish the relationships I have developed with my collaborators over the years, and wish to take it forward in the same spirit, as I take the next step in my profession career.

The single most reason behind all I have learnt and achieved, both professionally and personally, is my advisor Prof. Anand Raghunathan. He had undisputedly cared for my development and put my interests first in all decisions. I have always looked up to him and emulate him in all aspects of research, right from what problems to choose, what unique angles I as a researcher can bring in, where to spend my effort so that it is most impactful, and how best to present my work such that it is as intuitive to others as it is to me. The sheer experience of spending over half a decade with him has immensely helped me to organically develop as a researcher. I thank him all the flexibility and he is undoubtedly my superhero, the epitome of kindness, work ethic and intelligence. In the same breath, I thank all my teachers, right from my childhood, for who I am is a direct result of the knowledge they imparted.

My lab, Integrated Systems Laboratory, could not have been a more productive environment. My longevity at Purdue allowed me to work with some uniquely amazing people, seniors Vinay, Jacques, Vivek, Rangha, Yue Du, Younghyun and juniors Shankar, Ashish, Younghoon Shubham, Sanchari, Junshi, Neel, Arnab, and Sanjay. Needless to say, our relationships transcend beyond the walls of the MSEE 337. We always had our backs in thick and thin, and I enjoyed and learned from every *bit* (pun intended) of interaction. I truly care about each one of their successes, continue to feel proud of their accomplishments and strive to imbibe their finest qualities in me. ISL is the prime example of a truly synergistic academic lab, its strength purely stemming from the mutual care and respect people show for each other.

I interacted significantly with Prof. Vijay Raghunathan and Prof. Kaushik Roy throughout my PhD. I thank them for their support and guidance at each important step in my development. I also worked closely with students from Nanoelectronics Research Labs, Embedded Systems Lab, Integrating Imaging Lab at Purdue. I equally cherish those relationships and look forward to continue working with them in future. I also thank those I collaborated with in the industry, specifically during my internships at Exa-scale computing research and parallel computing labs at Intel, and Sensing and energy research group at Microsoft. I thank my mentors for their support and trust in my abilities.

I spent most of my time outside lab at the badminton courts in Purdue. Badminton was so integral to me, and I thank the Purdue Badminton Club members and other badminton enthusiasts in the midwest region for all the fun and competition we had on and off court. I also thank my cricket buddies for the fun times we shared.

On the personal front, I am undeservedly fortunate to have met Vijay, Kaushik, Priyanka, Chandana, Shankar, Samyuktha and Tanmay at Purdue. The veracity in their characters demonstrated the true kinship I never felt over the years. They kept me honest and their care for me kept me unfazed. I attribute every smile I enjoyed and every pain I felt to them. I cannot understate the influence my roomate Ashiwan has had on me. I never felt a stranger when he was around, and eternal gratitude to him and Sanju. I also thank my friends, Leena, Anand and others at Bangalore for all the fond memories. I will be amiss not to thank my family in the US for their inspiration and incessant support.

Finally, I thank my parents, Chithra and Venkataramani, for unconditionally being there for me and imparting values that defines my very identity today. The following pages are a product their emboldened vision, unfettering hope, and countless scarifies, and for that I humbly dedicate what is rightly theirs to them.

# TABLE OF CONTENTS

|    |      |         |                                                                        | Page |

|----|------|---------|------------------------------------------------------------------------|------|

| LI | ST O | F TAB   | LES                                                                    | х    |

| LI | ST O | F FIGU  | URES                                                                   | xi   |

| AI | BBRE | EVIATI  | ONS                                                                    | XV   |

| AI | BSTR | ACT     |                                                                        | xvii |

| 1  | INT  | RODU    | CTION                                                                  | 1    |

|    | 1.1  | Intrins | sic Application Resilience                                             | 2    |

|    | 1.2  | Appro   | ximate Computing                                                       | 5    |

|    | 1.3  | Thesis  | Contributions                                                          | 7    |

|    |      | 1.3.1   | Approximate and Quality Configurable Circuits:<br>Design and Synthesis | 8    |

|    |      | 1.3.2   | Programmable Approximate Computing Architectures                       | 10   |

|    |      | 1.3.3   | Software and Algorithms for Approximate Computing                      | 11   |

|    | 1.4  | Thesis  | GOrganization                                                          | 13   |

| 2  |      |         | ND SYNTHESIS OF APPROXIMATE AND QUALITY CON-<br>LE CIRCUITS            | 14   |

|    | 2.1  | Introd  | luction                                                                | 14   |

|    | 2.2  |         | y Metrics                                                              | 17   |

|    |      | 2.2.1   | Metrics Constraining the Magnitude of Error                            | 17   |

|    |      | 2.2.2   | Metrics Constraining the Frequency of Error                            | 18   |

|    |      | 2.2.3   | Composite Metrics                                                      | 19   |

|    | 2.3  | SALS    | A: Don't Care based Logic Approximation                                | 20   |

|    |      | 2.3.1   | Preliminaries and Approach                                             | 21   |

|    |      | 2.3.2   | SALSA Methodology                                                      | 27   |

|    |      | 2.3.3   | Speedup techniques and other heuristics                                | 33   |

| Page |

|------|

|------|

vi

|   |     | 2.3.4  | Experimental Methodology                                                                     | 38 |

|---|-----|--------|----------------------------------------------------------------------------------------------|----|

|   |     | 2.3.5  | Results                                                                                      | 40 |

|   | 2.4 |        | MI: A Unified Circuit Transformation for Approximate and Qual-<br>onfigurable Circuit Design | 52 |

|   |     | 2.4.1  | SASIMI: Design Approach                                                                      | 53 |

|   |     | 2.4.2  | Quality Configurable circuit design using SASIMI                                             | 55 |

|   |     | 2.4.3  | SASIMI Methodology                                                                           | 59 |

|   |     | 2.4.4  | Experimental Methodology                                                                     | 63 |

|   |     | 2.4.5  | Results: Approximate Circuits                                                                | 65 |

|   |     | 2.4.6  | Results: Quality configurable circuits                                                       | 68 |

|   |     | 2.4.7  | Application-level evaluation of SASIMI circuits                                              | 69 |

|   | 2.5 | Summ   | nary                                                                                         | 70 |

| 3 | QUA | ALITY  | PROGRAMMABLE PROCESSORS                                                                      | 72 |

|   | 3.1 | Introd | luction                                                                                      | 72 |

|   | 3.2 | A Cas  | e for Quality Programmability                                                                | 74 |

|   | 3.3 | Qualit | y Programmable Processors: Concept & Overview                                                | 75 |

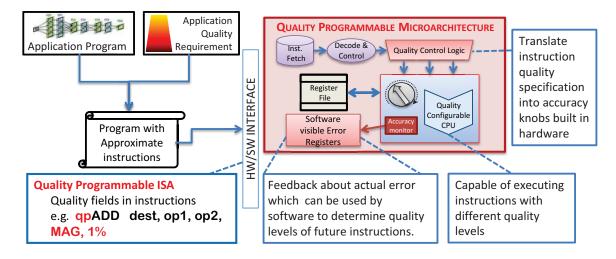

|   |     | 3.3.1  | QP-ISA: Quality Programmable ISA                                                             | 76 |

|   |     | 3.3.2  | QP-uArch: Micro-architecture with Accuracy-Energy Trade-off                                  | 77 |

|   |     | 3.3.3  | Quality Monitors: Error Feedback to Software                                                 | 78 |

|   |     | 3.3.4  | Programming QPPs                                                                             | 78 |

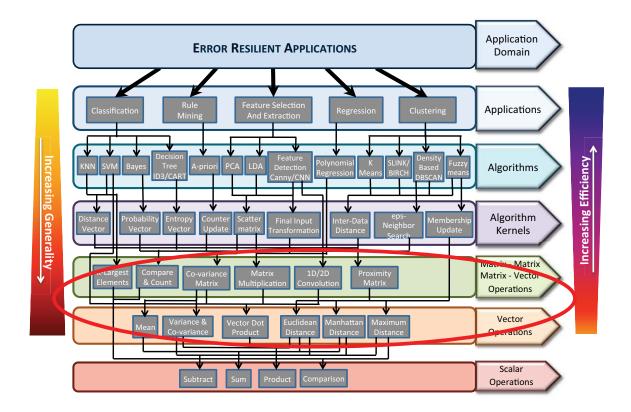

|   | 3.4 | Quo    | RA: A Quality Programmable Vector Processor                                                  | 79 |

|   |     | 3.4.1  | QUORA Instruction Set                                                                        | 80 |

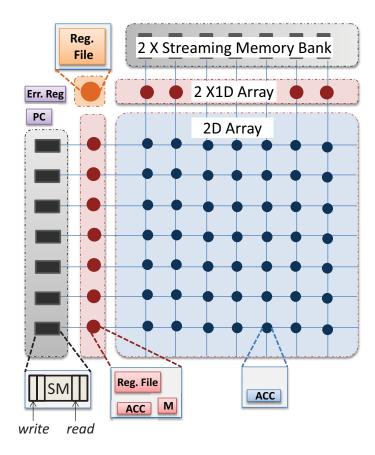

|   |     | 3.4.2  | QUORA Micro-architecture                                                                     | 86 |

|   | 3.5 | Micro  | -architectural Mechanisms for Quality Scaling                                                | 92 |

|   |     | 3.5.1  | Precision Scaling                                                                            | 92 |

|   |     | 3.5.2  | Array Level Organization of Precision Scaling Units                                          | 96 |

|   |     | 3.5.3  | Precision Scaling: Impact on Energy                                                          | 98 |

|   |     | 3.5.4  | Quality Translation and Error Estimation                                                     | 99 |

|   |     |        |                                                                                              |    |

|   |     |        |                                                            | Page  |

|---|-----|--------|------------------------------------------------------------|-------|

|   | 3.6 | Evalua | ation Methodology                                          | 101   |

|   |     | 3.6.1  | RTL Implementation                                         | 102   |

|   |     | 3.6.2  | Application Benchmarks                                     | 102   |

|   |     | 3.6.3  | Energy and Quality Measurements                            | 104   |

|   | 3.7 | Exper  | imental Results                                            | 105   |

|   |     | 3.7.1  | Energy Benefits                                            | 105   |

|   |     | 3.7.2  | Quality Programmability in Instructions                    | 106   |

|   |     | 3.7.3  | Energy Contribution of Quality Programmable Instructions . | 107   |

|   |     | 3.7.4  | Precision Scaling Mechanisms                               | 108   |

|   |     | 3.7.5  | Architectural Exploration                                  | 109   |

|   | 3.8 | Summ   | ary                                                        | 110   |

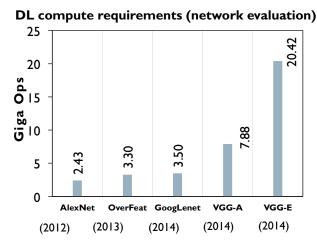

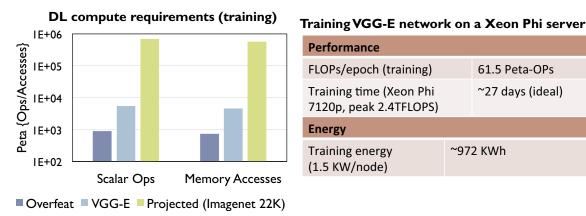

| 4 |     |        | EFFICIENT DEEP LEARNING USING APPROXIMATE COM              | - 111 |

|   | 4.1 | Introd | uction                                                     | 111   |

|   |     | 4.1.1  | Deep Learning Networks: Computational Challenges           | 111   |

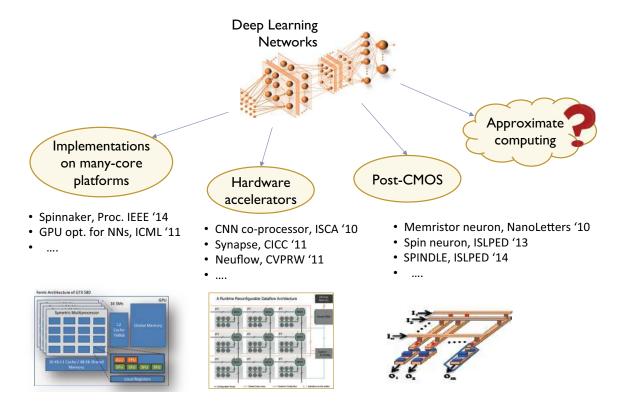

|   |     | 4.1.2  | Efficiency of DLNs: Prior Research Directions              | 113   |

|   |     | 4.1.3  | Deep Learning $\Leftrightarrow$ Approximate Computing      | 114   |

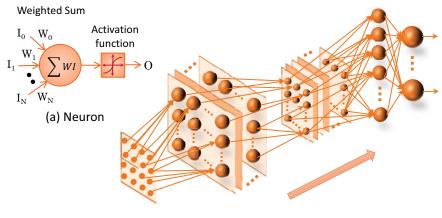

|   | 4.2 | Neura  | l Nets: Preliminaries                                      | 117   |

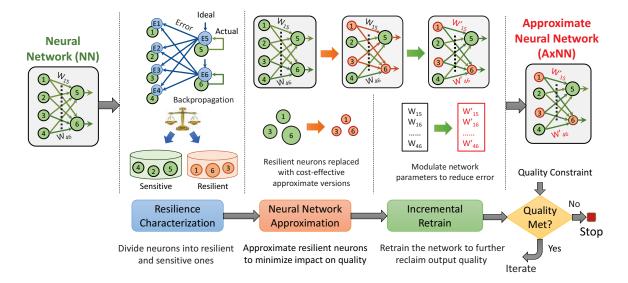

|   | 4.3 | AxNN   | I: Approach and Design Methodology                         | 119   |

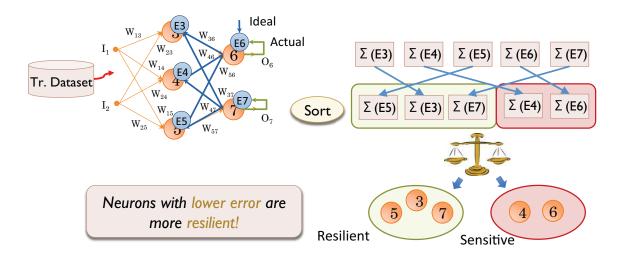

|   |     | 4.3.1  | AxNN: Design Approach                                      | 120   |

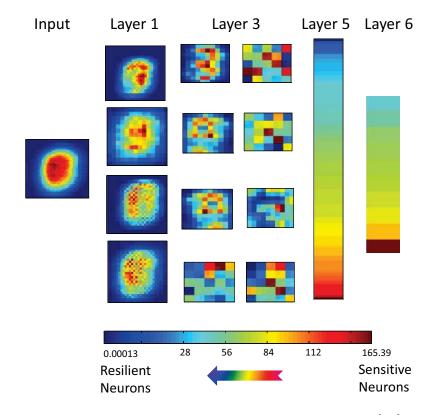

|   |     | 4.3.2  | AxNN Design Methodology                                    | 124   |

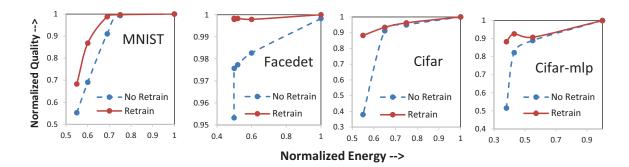

|   | 4.4 | Qualit | y Configurable Neuromorphic Processing Engine              | 126   |

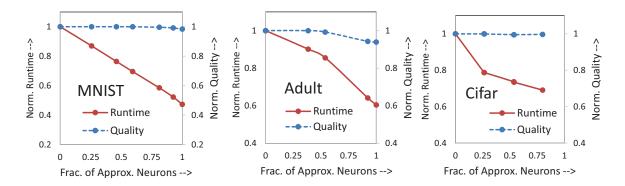

|   | 4.5 | Exper  | imental Methodology                                        | 128   |

|   | 4.6 | Result | S                                                          | 129   |

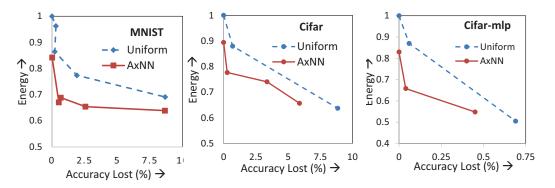

|   |     | 4.6.1  | Energy benefits of AxNN                                    | 129   |

|   |     | 4.6.2  | Uniform approximation: Comparison                          | 130   |

|   |     | 4.6.3  | Resilience Characterization: Insights                      | 131   |

|   |     | 4.6.4  | Impact of Retraining                                       | 132   |

|    |      |        |                                             | Page |

|----|------|--------|---------------------------------------------|------|

|    |      | 4.6.5  | AxNNs on Commodity Platforms                | 133  |

|    | 4.7  | Summ   | ary                                         | 134  |

| 5  | SCA  | LABLE  | E EFFORT CLASSIFIERS                        | 135  |

|    | 5.1  | Introd | uction                                      | 135  |

|    | 5.2  | Scalab | le effort Classifiers                       | 139  |

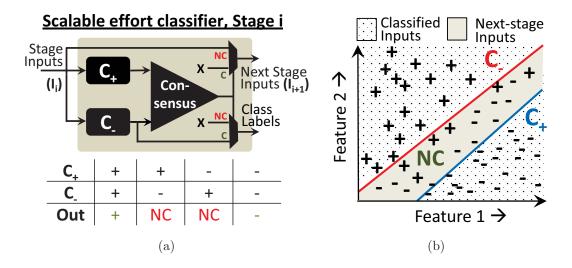

|    |      | 5.2.1  | Design of Scalable effort Classifier Stage  | 140  |

|    |      | 5.2.2  | Efficiency and Accuracy Optimization        | 141  |

|    |      | 5.2.3  | Multi-way Scalable effort Classifiers       | 144  |

|    | 5.3  | Design | Methodology                                 | 146  |

|    |      | 5.3.1  | Training Scalable effort Classifiers        | 146  |

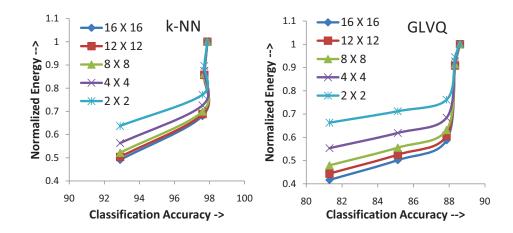

|    |      | 5.3.2  | Testing Scalable effort Classifiers         | 148  |

|    | 5.4  | Experi | mental Methodology                          | 148  |

|    |      | 5.4.1  | Application Benchmarks                      | 148  |

|    |      | 5.4.2  | Energy Evaluation                           | 150  |

|    | 5.5  | Result | S                                           | 151  |

|    |      | 5.5.1  | Energy Improvement                          | 151  |

|    |      | 5.5.2  | Impact of Hard Inputs on Efficiency         | 151  |

|    |      | 5.5.3  | Optimizing the Number of Classifier Stages  | 153  |

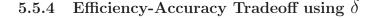

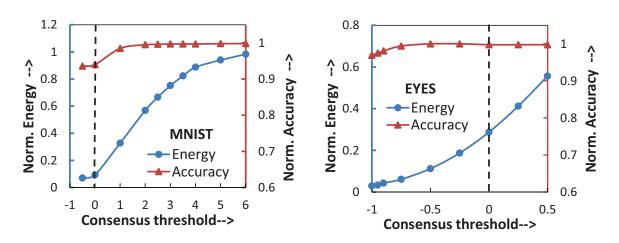

|    |      | 5.5.4  | Efficiency-Accuracy Tradeoff using $\delta$ | 154  |

|    | 5.6  | Summ   | ary                                         | 155  |

| 6  | REL  | ATED   | WORK                                        | 157  |

|    | 6.1  | Appro  | ximate Computing in Software                | 157  |

|    | 6.2  | Hardw  | are Design for Approximate Computing        | 157  |

|    | 6.3  | Appro  | ximate Circuits                             | 159  |

| 7  | CON  | ICLUSI | ON                                          | 161  |

|    | 7.1  | Thesis | Summary                                     | 162  |

|    | 7.2  | Resear | ch Challenges                               | 163  |

| RI | EFER | ENCES  | 5                                           | 166  |

viii

|--|

## LIST OF TABLES

| Tabl | Table                                                                                                                                                                                                                                               |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1  | Circuits used in experiments to evaluate SALSA                                                                                                                                                                                                      | 39  |

| 2.2  | Truth table comparison of original and approximate 3-bit adder for relative error $(S_{a1})$ , uni-directional relative error $(S_{a2})$ , error probability $(S_{a3})$ and unidirectional relative error with error probability $(S_{a4})$ metrics |     |

| 2.3  | Quality configurable circuits synthesized for average error magnitude with two quality modes                                                                                                                                                        | 67  |

| 2.4  | Quality configurable circuits synthesized for error probability metric with two quality modes                                                                                                                                                       | 68  |

| 3.1  | Representative instructions in QUORA's ISA                                                                                                                                                                                                          | 84  |

| 3.2  | Quality translation and error estimation for quality programmable instruc-<br>tions                                                                                                                                                                 | 100 |

| 3.3  | QUORA: Micro-architectural parameters and implementation metrics .                                                                                                                                                                                  | 102 |

| 3.4  | QUORA: List of application benchmarks                                                                                                                                                                                                               | 103 |

| 3.5  | Execution time and energy of instructions in QUORA's ISA                                                                                                                                                                                            | 105 |

| 4.1  | QCNPE parameters and metrics                                                                                                                                                                                                                        | 128 |

| 4.2  | NN benchmarks used to evaluate AxNN                                                                                                                                                                                                                 | 129 |

| 5.1  | Application benchmarks used to evaluate scalable effort classifiers                                                                                                                                                                                 | 150 |

## LIST OF FIGURES

| Figu | re                                                                                                    | Page |

|------|-------------------------------------------------------------------------------------------------------|------|

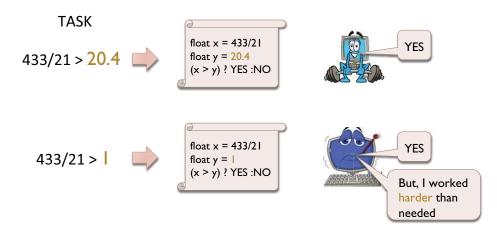

| 1.1  | Illustration: Inefficiency in viewing computers as precise calculators                                | 1    |

| 1.2  | Emerging applications requiring good-enough answers                                                   | 3    |

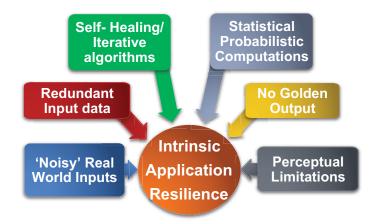

| 1.3  | Intrinsic Application Resilience: Sources                                                             | 4    |

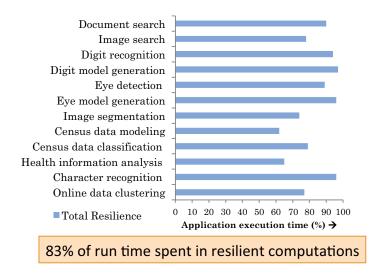

| 1.4  | Fraction of execution time contributed by resilient computations                                      | 4    |

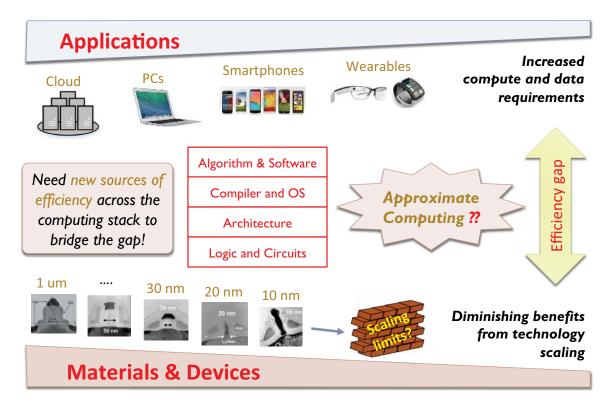

| 1.5  | Efficiency gap in Computing                                                                           | 5    |

| 1.6  | Approximate Computing: Design Principle                                                               | 6    |

| 1.7  | Contributions of the dissertation to approximate computing $\ldots$ .                                 | 7    |

| 2.1  | Approximate and quality configurable circuit design                                                   | 14   |

| 2.2  | Need for quality configurable circuits                                                                | 15   |

| 2.3  | Error Probability Distribution                                                                        | 19   |

| 2.4  | Quality constraint circuit                                                                            | 22   |

| 2.5  | Approximation don't cares                                                                             | 24   |

| 2.6  | Illustration: 2-bit multiplier circuit                                                                | 27   |

| 2.7  | Illustration: Quality function                                                                        | 28   |

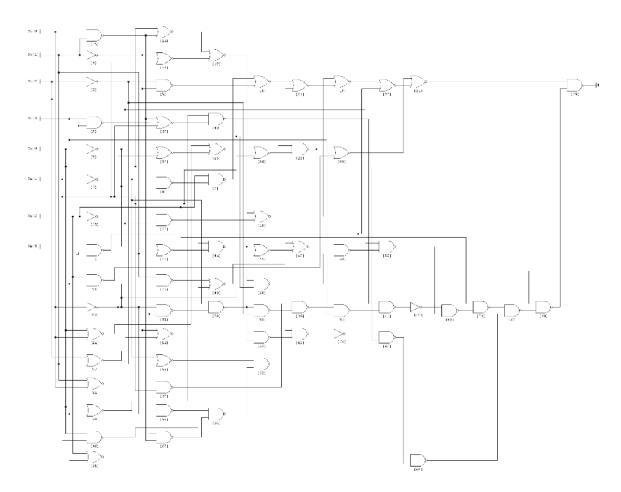

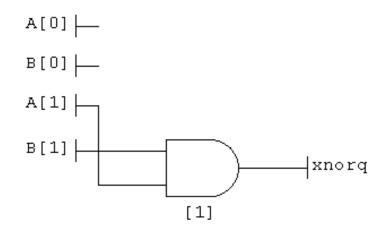

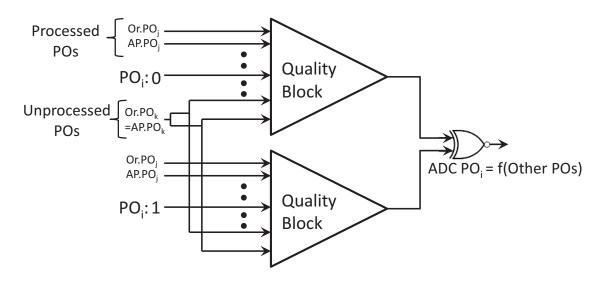

| 2.8  | STEP1 - Obtaining ADCs of a primary output in terms of other original and approximate circuit outputs | 30   |

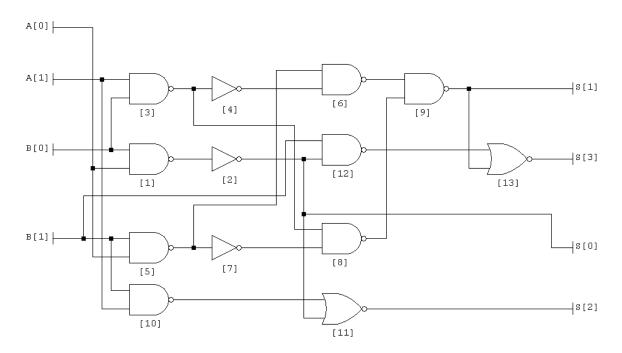

| 2.9  | Illustration: ADC-PO circuit when approximating output bit $S[1]$                                     | 31   |

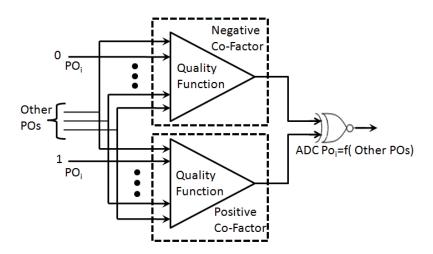

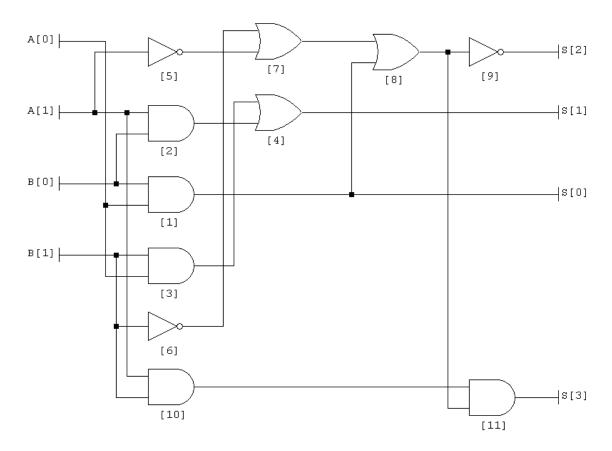

| 2.10 | STEP2 - Obtaining ADCs of a primary output in terms of primary inputs                                 | 31   |

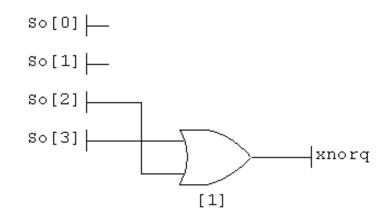

| 2.11 | Illustration: ADC circuit for output $S[1]$                                                           | 32   |

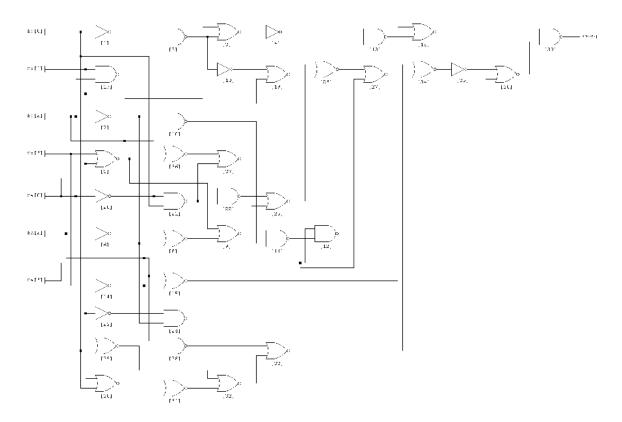

| 2.12 | Illustration: Approximate circuit with output $S[1]$ simplified $\ldots$ $\ldots$                     | 33   |

| 2.13 | Equating un-approximated output bits                                                                  | 34   |

| 2.14 | Illustration: ADC-PO circuit with un-approximated output bits equated                                 | 35   |

| 2.15 | Quality function decomposition                                                                        | 36   |

| 2.16 | Exploiting I/O dependencies and calculating subset of ADCs                                            | 38   |

| Figu | re                                                                                                       | Page |

|------|----------------------------------------------------------------------------------------------------------|------|

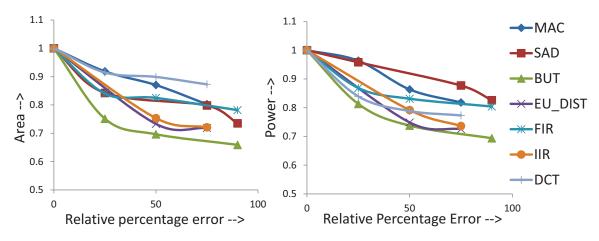

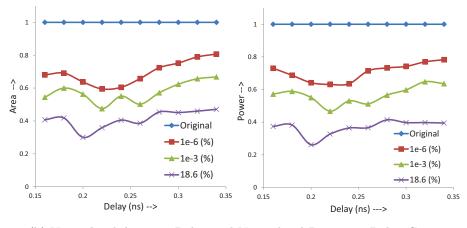

| 2.17 | Results for maximum error magnitude metric                                                               | 42   |

| 2.18 | Results for relative error metric                                                                        | 43   |

| 2.19 | Results for error probability metric                                                                     | 44   |

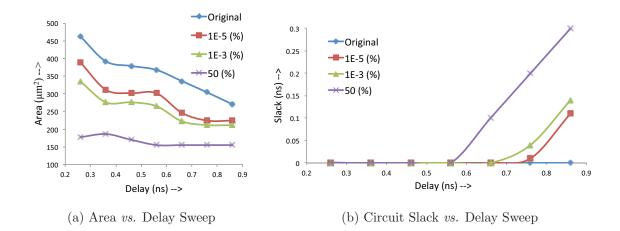

| 2.20 | Delay sweep of original and approximate circuits for a 32-bit kogge stone adder                          | 45   |

| 2.21 | Delay sweep of original and approximate circuits for a 32-bit ripple carry adder                         | 46   |

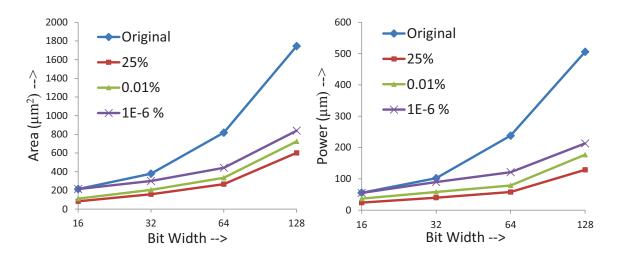

| 2.22 | Area and power scaling for adders of various bit widths                                                  | 46   |

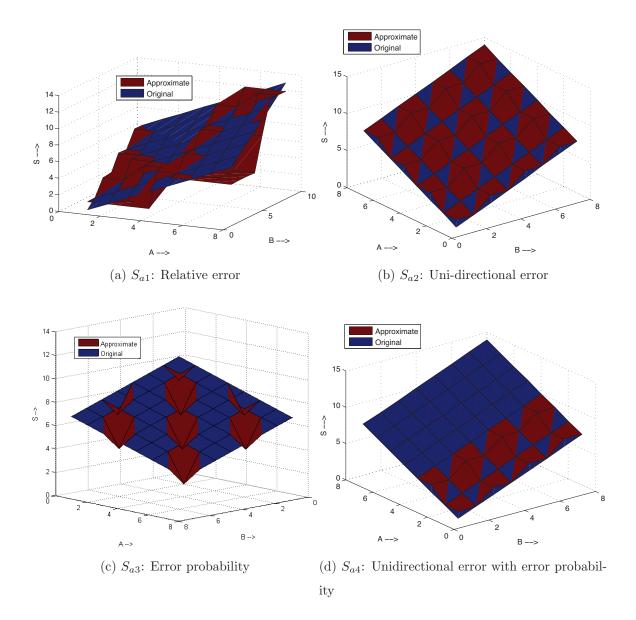

| 2.23 | Surface plots of exhaustive simulation on approximate circuits synthesized using various quality metrics | 49   |

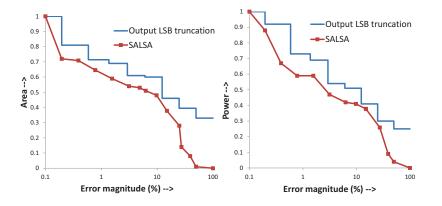

| 2.24 | Area and power comparison of SALSA with output LSB truncation for kogge-stone Adder                      | 50   |

| 2.25 | Area and power comparison of SALSA with output LSB truncation for array multiplier                       | 51   |

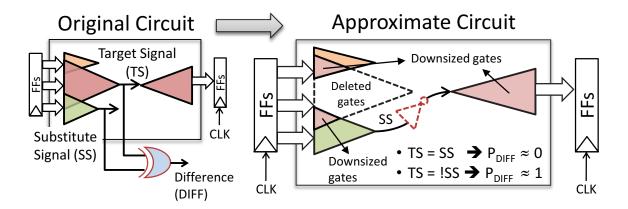

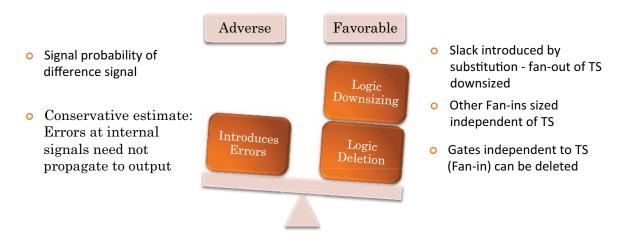

| 2.26 | Approximate circuit design using SASIMI                                                                  | 54   |

| 2.27 | Criteria for selecting substitution candidates                                                           | 54   |

| 2.28 | Quality configurable circuit design using SASIMI                                                         | 55   |

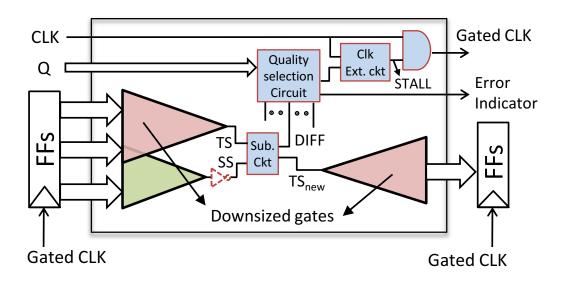

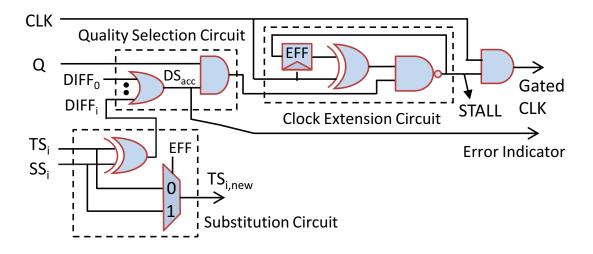

| 2.29 | Selective substitution, quality selection and clock extension circuits $\ . \ .$                         | 57   |

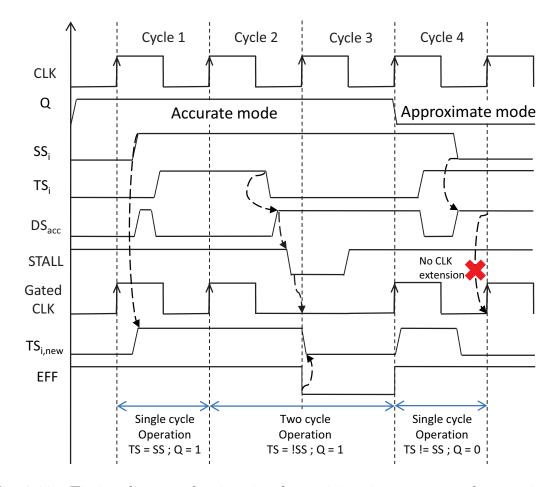

| 2.30 | Timing diagram showing signal transitions in accurate and approximate modes                              | 58   |

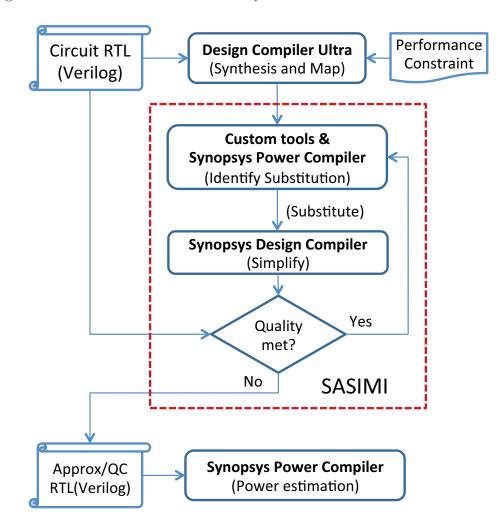

| 2.31 | CAD flow employed in the implementation of SASIMI                                                        | 64   |

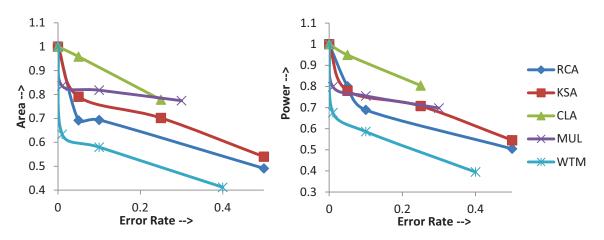

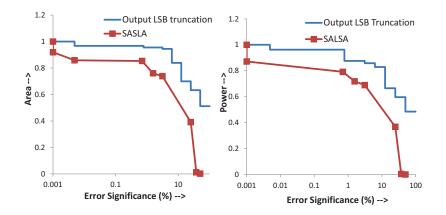

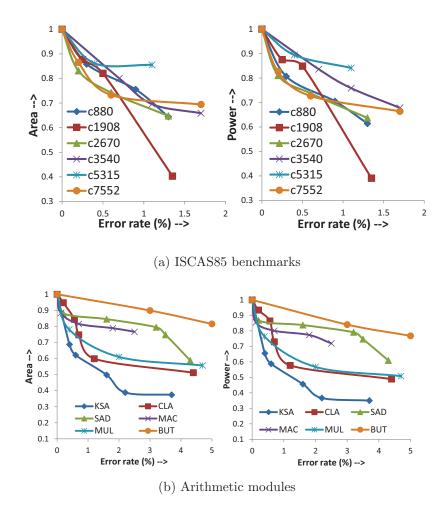

| 2.32 | Area and power benefits for error probability metric                                                     | 65   |

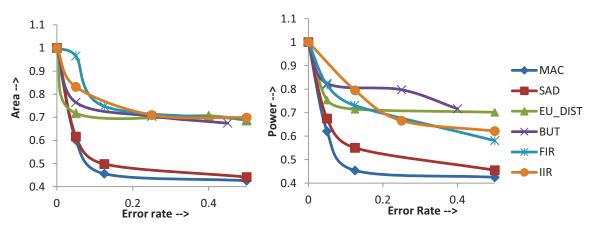

| 2.33 | Area and power benefits for average error magnitude metric                                               | 66   |

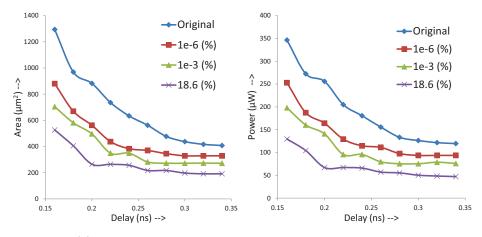

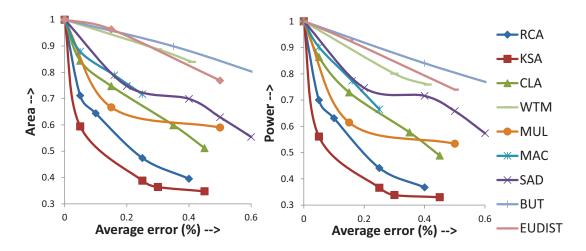

| 2.34 | Area and power of KSA with delay sweep                                                                   | 67   |

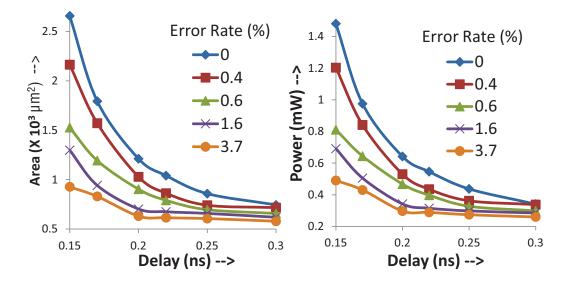

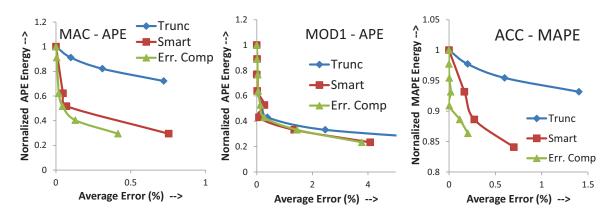

| 2.35 | Energy $v.s.$ accuracy trade-off in classification $\ldots \ldots \ldots \ldots \ldots$                  | 70   |

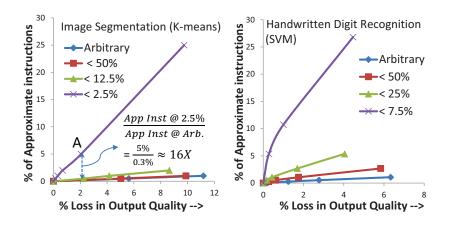

| 3.1  | Fraction of instructions that may approximated under arbitrary vs. con-<br>trolled approximations        | 75   |

| 3.2  | Conceptual overview of a quality programmable processor                                                  | 76   |

| 3.3  | Resursive breakdown of computations in error resilient applications                                      | 81   |

| 3.4  | Software visible micro-architectural state in QUORA                                                      | 82   |

| Figu | re                                                                                                                | Page |

|------|-------------------------------------------------------------------------------------------------------------------|------|

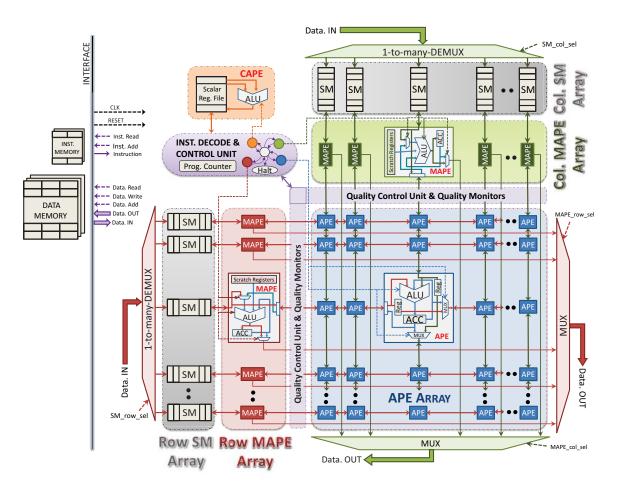

| 3.5  | QUORA micro-architecture                                                                                          | 87   |

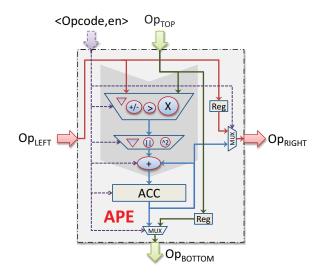

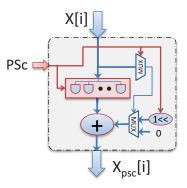

| 3.6  | Approximate processing element                                                                                    | 88   |

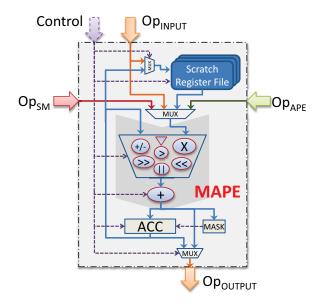

| 3.7  | Mixed accuracy processing element                                                                                 | 89   |

| 3.8  | Comparison of processing elements in QUORA                                                                        | 91   |

| 3.9  | Up/down precision scaling $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                          | 93   |

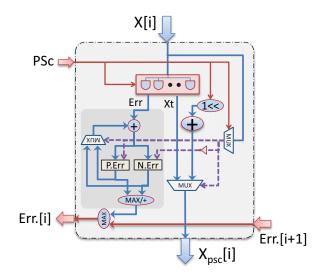

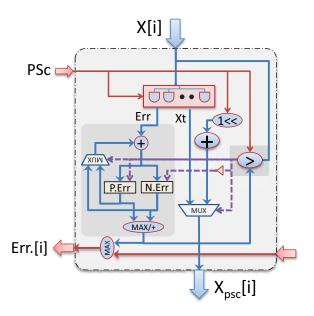

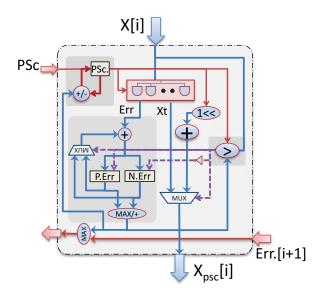

| 3.10 | Precision scaling with error monitoring                                                                           | 94   |

| 3.11 | Precision scaling with error compensation                                                                         | 95   |

| 3.12 | Dynamic precision scaling                                                                                         | 96   |

| 3.13 | Array level organization of precision scaling units                                                               | 97   |

| 3.14 | Energy benefits for different application-level quality constraints                                               | 106  |

| 3.15 | Energy reduction and application-level quality degradation for different instruction level quality specifications | 107  |

| 3.16 | Contribution of quality programmable instructions to dynamic instruction count, execution cycles and energy       | 108  |

| 3.17 | Energy <i>vs.</i> error curves for micro-benchmarks using different precision scaling mechanisms                  | 108  |

| 3.18 | Energy vs. quality curves for varying array dimensions                                                            | 109  |

| 4.1  | Computational requirements for embedding deep learning in low-power devices                                       | 112  |

| 4.2  | Computational requirements for training deep learning networks in the cloud                                       | 113  |

| 4.3  | Research directions to improve deep learning efficiency                                                           | 114  |

| 4.4  | Neural network preliminaries                                                                                      | 118  |

| 4.5  | Overview of the Approximate Neural Networks (AxNN) design approach                                                | 120  |

| 4.6  | Illustration: Neuron resilience characterization                                                                  | 121  |

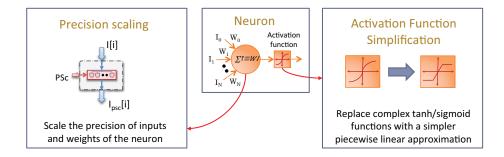

| 4.7  | Techniques used to approximate neurons                                                                            | 122  |

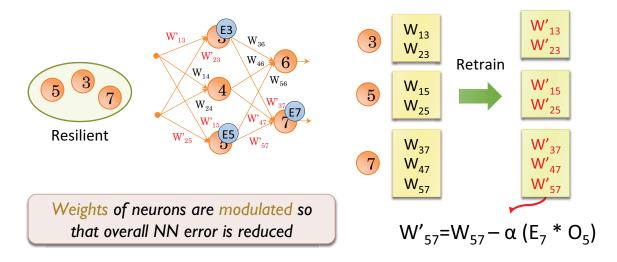

| 4.8  | Incremental retrain of AxNN                                                                                       | 123  |

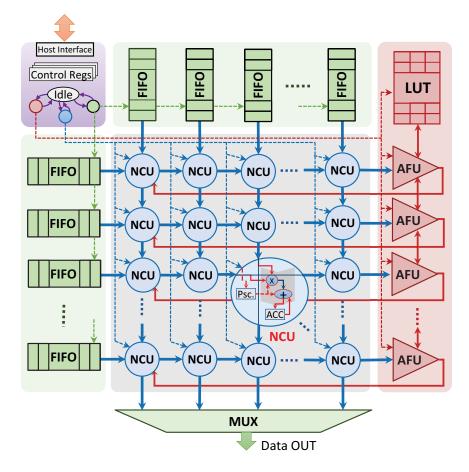

| 4.9  | Block diagram of QCNPE                                                                                            | 127  |

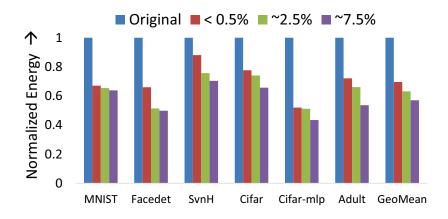

| 4.10 | Improvement in energy using AxNN                                                                                  | 130  |

| 4.11 | Quality $vs.$ energy trade-offs with uniform and AxNN approximations .                                            | 130  |

|      |                                                                                                                   |      |

| Figu | re                                                                                                                                                                                    | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.12 | Neuron average error maps in MNIST [39]                                                                                                                                               | 132  |

| 4.13 | Impact of retraining on energy and quality                                                                                                                                            | 133  |

| 4.14 | AxNN runtime on commodity platform                                                                                                                                                    | 134  |

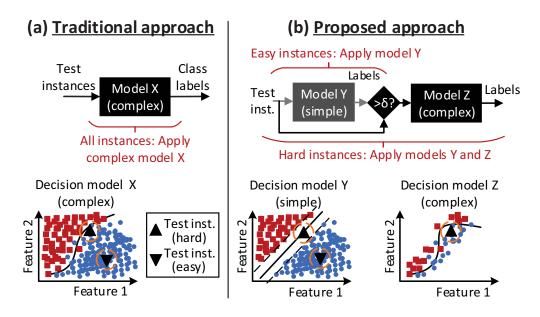

| 5.1  | Scalable effort classifiers: Approach                                                                                                                                                 | 136  |

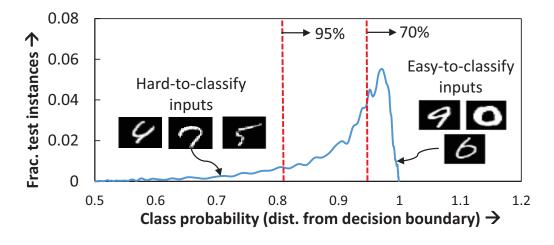

| 5.2  | Distribution of class probabilities for MNIST dataset                                                                                                                                 | 137  |

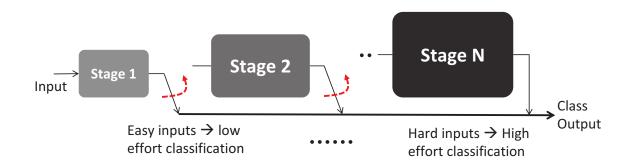

| 5.3  | A scalable effort classifier consists of a sequence of decision models, which grow progressively more complex                                                                         | 139  |

| 5.4  | Design of scalable effort classifier stage                                                                                                                                            | 140  |

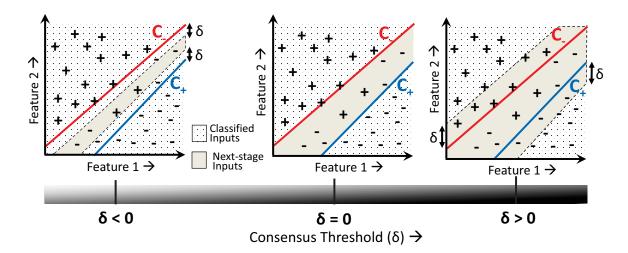

| 5.5  | $\delta$ controls the fraction of inputs classified by a stage. $\hdots$                                                                                                              | 143  |

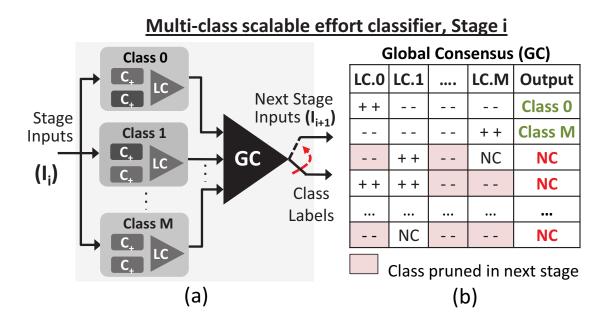

| 5.6  | One <i>vs.</i> rest approach is used for multi-way classification. GC can prune some classes in the next stage                                                                        | 145  |

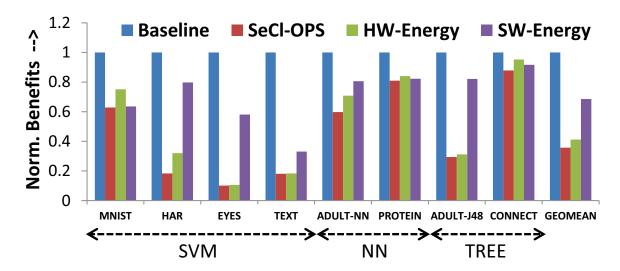

| 5.7  | Improvement in average OPS/input and energy for different applications.                                                                                                               | 152  |

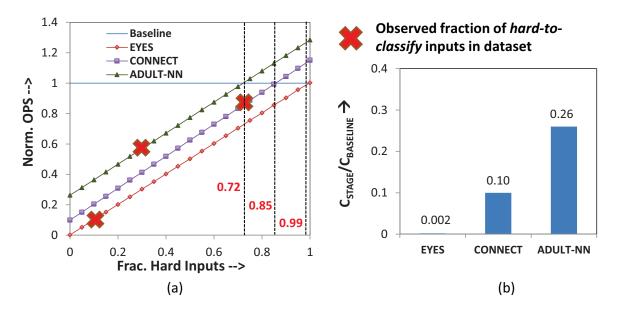

| 5.8  | (a) Normalized OPS consumed by the scalable-effort classifier with increasing fraction of hard inputs. (b) Total complexity of the added classifier stages for different applications | 153  |

| 5.9  | Normalized reduction in OPS with different numbers of classifier stages for the ADULT-J48 application                                                                                 | 154  |

| 5.10 | Energy $vs.$ accuracy trade-off by modulating consensus threshold $\ldots$                                                                                                            | 154  |

## ABBREVIATIONS

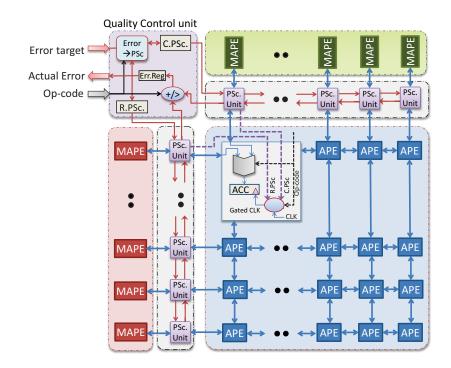

AxC Approximate Computing SALSA Systematic Automatic Logic Synthesis of Approximate circuits ALS Approximate Logic Synthesis QCC Quality Constraint Circuit ADC Approximation Don't Cares EXDC External Don't Cares SASIMI Substitute-And-SIMplIfy TSTarget Signal SSSubstitute Signal QPP Quality Programmable Processor QP-ISA Quality Prgrammable Instuction Set Architecture QP-uArch Quality Programmable Micro-architecture QUORA Quality Programmable 1D/2D Vector Processor APE Approximate Processing Element MAPE Mixed Accuracy Processing Element CAPE Completely Accurate Processing Element PScU Precision Scaling Units QCU Quality Control Unit SMStreaming Memory NN Neural Networks DLN Deep Learning Networks AxNN Approximate Neural Networks QCNPE Quality Configurable Neural Processing Engine NCU Neuron Computation Unit

AFUActivation Function UnitRTLRegister Transfer LevelHW/SWHardware/SoftwareMACMultiply And AccumulateSADSum of Absolute DifferencesDCTDiscrete Cosine Transform

#### ABSTRACT

Venkataramani, Swagath PhD, Purdue University, December 2016. Approximate Computing: An Integrated Cross-layer Framework. Major Professor: Anand Raghunathan.

We have witnessed a fundamental shift in the nature of workloads executed by computing platforms across the spectrum, from mobile and deeply-embedded devices to servers and data centers. Increasingly, computing platforms need to analyze, organize and search through large amounts of real-world data, intelligently interact with the physical world, be context-aware, and present more natural human interfaces. These tasks do not involve the computation of a golden answer or unique numerical result. Instead, they need to produce outputs that are good-enough or of sufficient quality. Such workloads possess *intrinsic application resilience*, or the ability to produce outputs of acceptable quality even when a large fraction of their computations are performed in an imprecise or approximate manner. Intrinsic application resilience offers an entirely new dimension along which computing platforms can be optimized. However, the design of computing platforms still continues to be guided by the dogma that every computation must be executed with the same strict notion of correctness. With the demand for computing performance growing unabated on the one hand, while traditional benefits due to technology scaling diminish on the other, it is important to leverage this new source of efficiency.

A new design approach, called *approximate computing* (AxC), leverages the flexibility provided by intrinsic application resilience to realize hardware or software implementations that are more efficient in energy or performance. Approximate computing techniques forsake exact (numerical or Boolean) equivalence in the execution of some of the application's computations, while ensuring that the output quality is acceptable. While early efforts in approximate computing have demonstrated great potential, they consist of ad hoc techniques applied to a very narrow set of applications, leaving in question the applicability of approximate computing in a broader context.

The primary objective of this thesis is to develop an integrated cross-layer approach to approximate computing, and to thereby establish its applicability to a broader range of applications. The proposed framework comprises of three key components: (i) At the circuit level, systematic approaches to design approximate circuits, or circuits that realize a slightly modified function with improved efficiency, (ii) At the architecture level, utilize approximate circuits to build programmable approximate processors, and (iii) At the software level, methods to apply approximate computing to machine learning classifiers, which represent an important class of applications that are being utilized across the computing spectrum. Towards this end, the thesis extends the state-of-the-art in approximate computing in the following important directions.

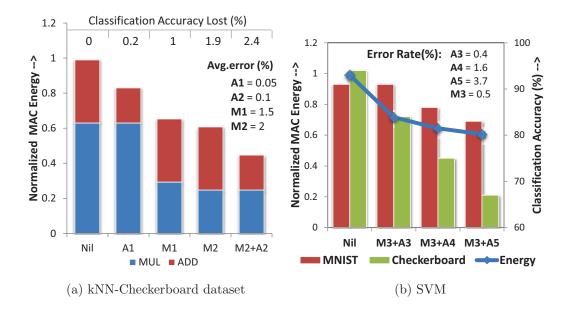

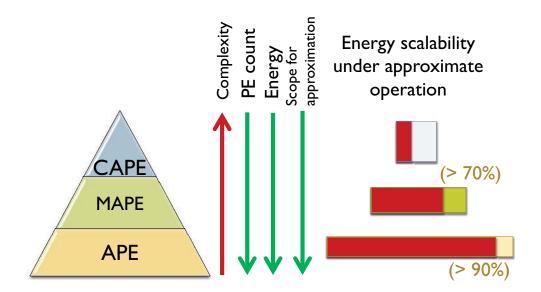

Synthesis of Approximate Circuits. First, the thesis proposes a rigorous framework for the automatic synthesis of *approximate circuits*, which are the hardware building blocks of approximate computing platforms. Designing approximate circuits involves making judicious changes to the function implemented by the circuit such that its hardware complexity is lowered without violating the specified quality constraint. Inspired by classical approaches to Boolean optimization in logic synthesis, the thesis proposes two synthesis tools called SALSA and SASIMI that are general, *i.e.*, applicable to any given circuit and quality specification. The framework is further extended to automatically design *quality configurable circuits*, which are approximate circuits with the capability to reconfigure their quality at runtime. Over a wide range of arithmetic circuits, complex modules and complete datapaths, the circuits synthesized using the proposed framework demonstrate significant benefits in area and energy. ing to the realm of programmable processors by introducing the concept of quality programmable processors (QPPs). A key principle of QPPs is that the notion of quality is explicitly codified in their HW/SW interface *i.e.*, the instruction set. Instructions in the ISA are extended with quality fields, enabling software to specify the accuracy level that must be met during their execution. The micro-architecture is designed with hardware mechanisms to understand these quality specifications and translate them into energy savings. As a first embodiment of QPPs, the thesis presents a quality programmable 1D/2D vector processor QP-VEC, which contains a 3-tiered hierarchy of processing elements. Based on an implementation of QP-VEC with 289 processing elements, energy benefits upto  $2.5 \times$  are demonstrated across a wide range of applications.

Software and Algorithms for AxC. Finally, the thesis addresses the problem of applying approximate computing to an important class of applications viz. machine learning classifiers such as deep learning networks. To this end, the thesis proposes two approaches—AxNN and scalable effort classifiers. Both approaches leverage domainspecific insights to transform a given application to an energy-efficient approximate version that meets a specified application output quality. In the context of deep learning networks, AxNN adapts backpropagation to identify neurons that contribute less significantly to the network's accuracy, approximating these neurons (e.q., by usinglower precision), and incrementally re-training the network to mitigate the impact of approximations on output quality. On the other hand, scalable effort classifiers leverage the heterogeneity in the inherent classification difficulty of inputs to dynamically modulate the effort expended by machine learning classifiers. This is achieved by building a chain of classifiers of progressively growing complexity (and accuracy) such that the number of stages used for classification scale with input difficulty. Scalable effort classifiers yield substantial energy benefits as a majority of the inputs require very low effort in real-world datasets.

In summary, the concepts and techniques presented in this thesis broaden the applicability of approximate computing, thus taking a significant step towards bringing approximate computing to the mainstream.

## 1. INTRODUCTION

Traditionally, computing platforms are viewed as calculators that execute tasks demanded by applications in a very precise manner. While the performance and efficiency of computing platforms have grown exponentially over the decades, their design continues to be guided by the principle that every computation they are tasked with is sacred and are carried out with a *strict (and unique) notion of correctness*. However, from a holistic application perspective, not all computations are equally important *i.e.*, a range of answers to underlying computations result in the same eventual application output. For example, consider the two tasks, shown in Figure 1.1, which are very similar to each other. In both cases, we wish to divide 433 by 21, but in the first case the output is compared to 20.4, while in the second, it is compared to 1. Computers today, due to their inability to understand the context in which the result

Fig. 1.1.: Illustration: Inefficiency in viewing computers as precise calculators

of the division operation is used, would expend the same effort to execute the tasks. However, as a high-level analogy, if the tasks were carried out by the human brain, it would find the second task to be much easier than the first, because it inherently possesses the ability to compute results to the desired level of precision [1]. Hence, viewing computers as precise calculators clearly leads to significant in-efficiency and an overkill for many applications that computing platforms execute today.

#### 1.1 Intrinsic Application Resilience

The landscape of computing applications has evolved over the years and we have witnessed a fundamental shift in the nature of workloads executed by computing platforms across the spectrum. With the ubiquity of the world wide web and the explosion in digital data of various forms, computing platforms in data centers and the cloud are used to analyze, interpret, and mine vast collections of raw data using semantic abstractions. At the other end of the spectrum, the need for intelligence and context-awareness in mobile and embedded devices implies that they too execute workloads that involve recognizing and interpreting data sensed from the physical world and their users. These workloads, which are of growing interest and expected to drive the usage of future computing platforms [2,3], do not expect a unique golden numerical answer. Rather, they are characterized by whether they produce an acceptable user experience, or results of sufficient quality. Even when a golden output is defined, the best known algorithms fall short of perfection (e.q., for most real worldrecognition and classification problems, achieving 100% accuracy remains a distant objective). Hence, in their context, functional correctness is redefined from obtaining precise numerical answers to producing outputs that are "good-enough" to the end user (Figure 1.2).

These emerging workloads invariably exhibit significant *intrinsic application resilience*, which is broadly defined as the ability of applications to produce outputs of acceptable quality despite some of their underlying computations being executed in an imprecise or approximate manner. As illustrated in Figure 1.3, this intrinsic resilience, which is also shared by many prevalent application domains such as multimedia, graphics, and signal processing, stems from various factors [4–6]:

Fig. 1.2.: Emerging applications requiring good-enough answers

- The algorithms are designed to handle noisy real-world inputs, which as a consequence equips them to tolerate errors introduced in the intermediate computations.

- The computation patterns employed in these applications are typically iterative and statistical in nature allowing for errors introduced by approximations to attenuate or self-heal over time.

- A range of outputs are considered equivalent since no golden answer exists, or small deviations in the output cannot be perceived by users.

Recent studies [4] of intrinsic resilience in a suite of 12 emerging recognition, mining, and search applications revealed that on average, 83% of the runtime was spent in computations that were tolerant to errors in their outputs. This reaffirms the qualitative observation that a broad range of application domains exhibit significant intrinsic resilience.

The growth in demands being placed on computing platforms is expected to continue unabated, while on the other hand the benefits due to technology scaling continue to diminish. As illustrated in Figure 1.5, this growing *efficiency gap* is challenging designers of computing platforms and pushing them to innovate in hitherto

Fig. 1.3.: Intrinsic Application Resilience: Sources

Fig. 1.4.: Fraction of execution time contributed by resilient computations

unexplored directions for improving the performance and energy efficiency. Some of the promising directions that are being explored include heterogeneous parallel architectures, near-threshold computing and accelerator-based computing. Optimizing designs by exploiting the intrinsic resilience of applications has the potential to become another dimension along which improvements in computing efficiency may be realized, since a large part of the growth in computing workloads can be attributed to application domains that possess significant resilience, including recognition, mining, synthesis, audio/video processing, data analytics, search, and graphics.

Fig. 1.5.: Efficiency gap in Computing

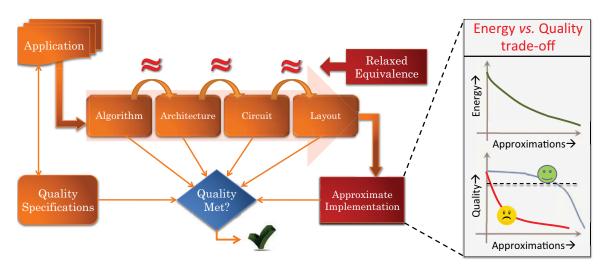

## 1.2 Approximate Computing

Approximate computing (AxC) is an emerging design approach that seeks to achieve new efficiencies in computing platforms by designing them such that they are capable of producing "good enough" results. Approximate computing platforms exploit the intrinsic resilience of applications by foregoing exactness or full correctness in the execution of selected computations, thereby improving performance or energy efficiency. Figure 1.6 illustrates the design principle behind approximate computing. Given the functional requirements of an application, the traditional design process involves several levels of design abstraction *viz*. developing the algorithm (or software), mapping the algorithmic computations to the desired hardware architecture, refining the architecture to circuit and layout to obtain the final implementation. One of the key invariants in the design process is that perfect equivalence (numerical or Boolean) is maintained as the design progresses across the different levels of abstraction. As shown in Figure 1.6, approximate computing challenges this long-held dogma. In addition to the functional requirements of the application, the quality desired at the application output is also provided. Given these output quality specifications, approximations can be introduced in any of the design abstraction layers, provided the resultant degradation in output quality is acceptable. The key to the efficiency of approximate computing is to obtain a favorable a energy (or performance) v.s. quality trade-off *i.e.*, the benefits in energy is disproportionately large compared to the quality sacrificed in the process.

Fig. 1.6.: Approximate Computing: Design Principle

There has been significant interest in the area of approximate computing in recent years, and several techniques for approximate computing in hardware [6-13] or software [5,14-18] have been proposed. While these efforts have established the potential for significant improvements from approximate computing, they have invariably been *explored in an application-specific context* — the techniques are often ad hoc and applicable to specific applications, or the end result is often application-specific custom hardware. Consequently, two key questions that are frequently asked of approximate computing are "Is the approach applicable to a broader range of applications and domains?" and "Is it possible to amortize design effort by creating approximate computing platforms that can be re-used across applications?" This dissertation aims to answer the above questions in the affirmative.

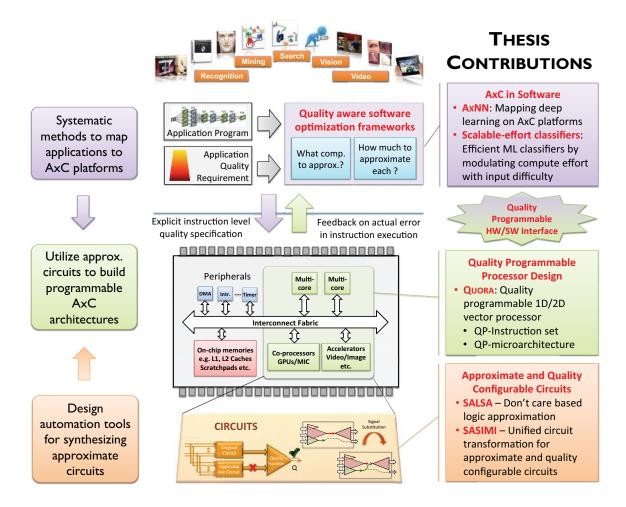

#### **1.3** Thesis Contributions

Fig. 1.7.: Contributions of the dissertation to approximate computing

To address the fundamental challenges associated with the broader adoption of approximate computing, this dissertation develops an integrated and systematic framework for approximate computing as outlined in Figure 1.7. The proposed framework comprises of three key components, which collectively involve developing approximate computing techniques at various layers of the computing stack. First, at the circuit level, the thesis develops techniques to design approximate circuits that are highly efficient in performance, area and power. To enable generality and scalability, the thesis embodies the fundamental approximate circuit design principles into synthesis frameworks that can automatically generate "correct-by-construction" approximate versions for any given circuit, and any desired accuracy bound specified at the circuit outputs. Next, at the architecture level, the approximate circuits are used to build approximate computing architectures that yield a favorable trade-off between efficiency and application output quality. Towards this end, the thesis investigates how approximate computing can be best leveraged in the context of programmable processors. Finally, at the software level, the thesis develops methodologies to systematically identify resilient computations within an application and map them to approximate computing platforms. An overview of the important contributions of the dissertation are described below.

# 1.3.1 Approximate and Quality Configurable Circuits: Design and Synthesis

Approximate circuits are the basic hardware building blocks of approximate computing platforms. Approximate circuits are highly efficient hardware implementations that realize a slightly modified logic function compared to the original specifications within a specified quality constraint. Most research efforts in the area of approximate circuits can be summarized as manual designs of simple arithmetic circuits such as adders [19–22] and multipliers [23]. However, the broader adoption of approximate circuits requires a systematic methodology to design approximate implementations for any arbitrary circuit. Moreover, it is critical that such a methodology enable the generation of "correct-by-construction" approximate circuits that are guaranteed to satisfy designer-specified quality constraints, which is often not the case for the aforementioned manual designs. Towards this objective, the thesis presents two synthesis methodologies *viz.* SALSA and SASIMI for the automatic design of approximate circuits. We further extend the methodology to synthesize quality configurable circuits, which possess the additional capability to reconfigure their quality at runtime. A brief summary of the methodologies are presented below.

### SALSA

The first methodology SALSA extends the classical don't care based optimization approach for Approximate Logic Synthesis (ALS). The key hallmark of SALSA is the rigorous formulation of the problem of ALS into an equivalent traditional logic synthesis problem, thereby allowing the capabilities of existing synthesis tools to be fully utilized for logic approximation. SALSA achieves this by forming a virtual Quality Constraint Circuit (QCC) that encodes the quality constraints using logic functions called *Q*-functions. It then captures the flexibility engendered by the relaxed quality specifications as *Approximation Don't Cares* (ADCs), which are used for circuit simplification using traditional don't care based optimization techniques.

## SASIMI

The second methodology SASIMI, introduces a new circuit transformation called Substitute-and-Simplify, for approximate circuit design. The key insight behind SASIMI is to identify signal pairs in the circuit that assume the same value with high probability, and substitute one for the other. While these substitutions introduce functional approximations, if performed judiciously, they result in some logic to be eliminated from the circuit while also enabling downsizing of gates on critical paths (simplification), resulting in significant power savings. SASIMI performs the substitution and simplification iteratively, while ensuring that a user-specified quality constraint is satisfied. SASIMI is extended to perform automatic synthesis of quality configurable circuits that can dynamically operate at different accuracy levels depending on application requirements. It is worthy to note that the quality configurable circuits synthesized by SASIMI do not incur any energy overheads even during the accurate mode of operation.

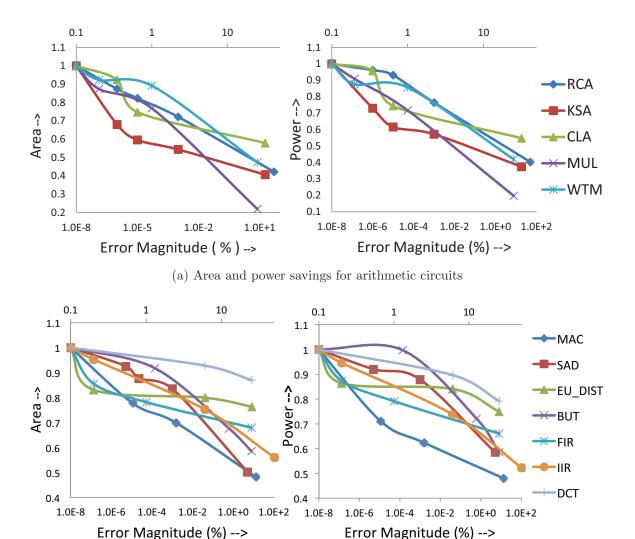

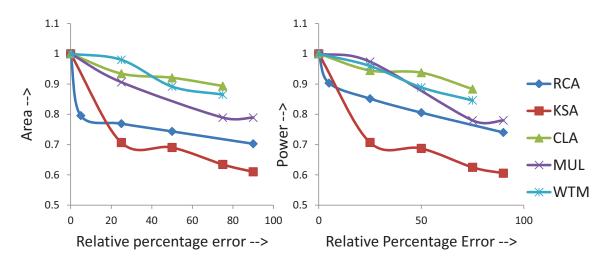

The synthesis tools, SALSA and SASIMI, were prototyped and utilized to synthesize approximate and quality configurable versions of a wide range of circuits comprised of arithmetic building blocks (adders, multipliers, MAC), ISCAS benchmarks and entire datapaths (DCT, FIR, IIR, SAD, FFT Butterfly, Euclidean distance), demonstrating scalability and significant improvements in area (1.1X to 1.85X for tight error constraints, and 1.2X to 4.75X for relaxed error constraints) and energy (1.15X to 1.75X for tight error constraints, and 1.3X to 5.25X for relaxed error constraints).

#### **1.3.2** Programmable Approximate Computing Architectures

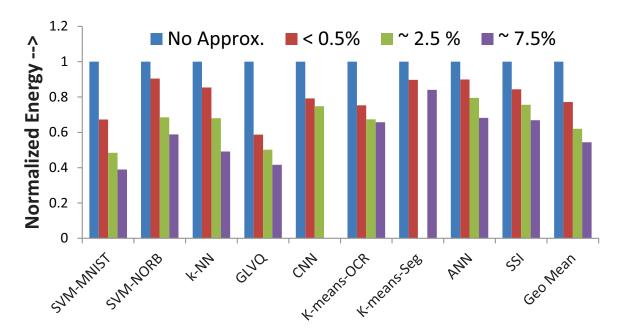

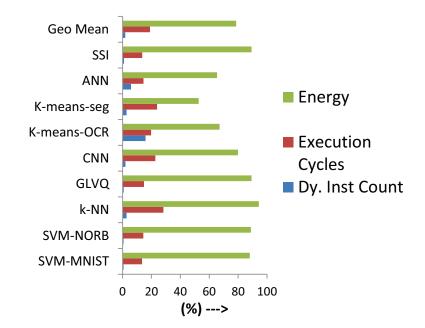

The thesis extends approximate computing to realm of programmable processors by introducing the concept of Quality Programmable Processors (QPPs). In QPPs, as shown in Figure 1.7, the conventional HW/SW interface, which allows specification of just the operation and the operands, is enhanced to explicitly embody the notion of quality. The ISA of a quality programmable processor contains instructions associated with quality fields to specify the accuracy level that must be met during their execution. It thus empowers software with the ability to specify not just what the operation is but also how significant it is in the context of the application. This ability to control the accuracy of instruction execution greatly enhances the scope of approximate computing, allowing it to be applied to larger parts of programs. The micro-architecture of a quality programmable processor contains hardware mechanisms that translate the instruction-level quality specifications into energy savings. Additionally, it may expose the actual error incurred during the execution of each instruction (which may be less than the specified limit) back to software. As a first embodiment of quality programmable processors, the thesis presents the design of QUORA, an energy efficient, quality programmable vector processor. QUORA utilizes a 3-tiered hierarchy of processing elements that provide distinctly different energy vs. quality trade-offs, and uses hardware mechanisms based on precision scaling with error monitoring and compensation to facilitate quality programmable execution. We evaluate an implementation of QUORA with 289 processing elements in 45nm technology. The results demonstrate that leveraging quality-programmability leads to  $1.05 \times -1.7 \times$  savings in energy for virtually no loss (<0.5%) in application output quality, and  $1.18 \times -2.1 \times$  energy savings for modest impact (<2.5%) on output quality.

#### **1.3.3** Software and Algorithms for Approximate Computing

At the software level, given an application and an application output quality requirement, the key challenge is to identify which computations to approximate and by how much. This requires quality-aware software optimization frameworks to identify resilient computations and quantitatively evaluate how approximations to these computations impact the application output. The dissertation addresses this problem in the context of an important class of applications *viz.* machine/deep learning classifiers. To this end, the thesis proposes the following approximation frameworks that leverage domain-specific insights to systematically transform a given application into its approximate version.

#### AxNN: Approximate Neural Networks

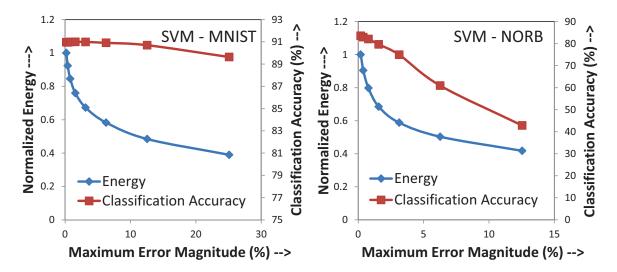

Large-scale neural networks or Deep Learning Networks (DLNs) have become popular due to their state-of-the-art performance on a wide range of machine learning problems. One of the key challenges with deep learning networks is their high computational complexity. To improve the efficiency of DLNs while preserving their functional performance, the thesis proposes a method to transform any given neural network (NN) into an Approximate Neural Network (AxNN). This is performed by (i) adapting the backpropagation technique, which is commonly used to train these networks, to quantify the impact of approximating each neuron to the overall network quality (*e.g.*, classification accuracy), and (ii) selectively approximating those neurons that impact network quality the least. Further, leveraging the key observation that training is a naturally error-healing process, the network is incrementally retrained with the approximations in-place, reclaiming a significant portion of the quality ceded by approximations. We evaluated the proposed approach by constructing AXNNs for 6 recognition applications (ranging in complexity from 12-47,818 neurons and 160-3,155,968 connections). Our results demonstrate  $1.14 \times -1.92 \times$  energy benefits for virtually no loss (< 0.5%) in output quality, and even higher improvements (upto  $2.3 \times$ ) when some loss (upto 7.5%) in output quality is acceptable.

#### Scalable Effort Classifiers

Scalable effort classifiers are a new approach to optimizing the energy efficiency of supervised machine-learning classifiers. Its efficiency stems from the observation that the inherent classification difficulty varies widely across inputs in real-world datasets; only a small fraction of the inputs truly require the full computational effort of the classifier, while the large majority can be classified correctly with very low effort. Yet, state-of-the-art classification algorithms expend equal effort on all inputs, irrespective of their difficulty. To address this inefficiency, scalable effort classifiers dynamically adjust their computational effort depending on the difficulty of the input data, while maintaining the same level of accuracy. Scalable effort classifiers are constructed by utilizing a chain of classifiers with increasing levels of complexity (and accuracy). Scalable effort execution is achieved by modulating the number of stages used for classifying a given input. Every stage in the chain contains an ensemble of biased classifiers, where each biased classifier is trained to detect a single class more accurately. The degree of consensus between the biased classifiers' outputs is used to decide whether classification can be terminated at the current stage or not. Thus any given classification algorithm can be transformed into a scalable effort chain. We build scalable effort versions of 8 popular recognition applications using 3 different classification algorithms. Our experiments demonstrate that scalable effort classifiers yield  $2.79 \times$  reduction in average operations per input, which translates to  $2.3 \times$  and  $1.5 \times$  improvement in energy for hardware and software implementations, respectively.

In summary, the dissertation outlines an integrated framework for approximate computing that includes automatic frameworks to synthesize approximate circuit blocks, a programmable architecture along with its HW/SW interface that explicitly embodies the notion of quality, and finally software methodologies to systematically identify resilient computations within an application in order maximize the benefits for a desired output quality.

#### 1.4 Thesis Organization

The rest of the thesis is organized as follows. Chapter 2 describes the synthesis methodologies proposed for approximate and quality configurable circuit design. Chapter 3 details the concept of quality programmable processors, and the key issues involved in their design. Chapter 4 describes AxNN, the approach proposed to systematically identify and approximate resilient computations in deep learning networks. Chapter 5 outlines the concept of scalable effort classifiers and the methodology employed to construct scalable effort versions of any given classification algorithm. Chapter 6 presents the previous related efforts in the area of approximate computing and places the contributions of this thesis in their context. Finally, Chapter 7 provides a summary and outlines the key directions for future research.

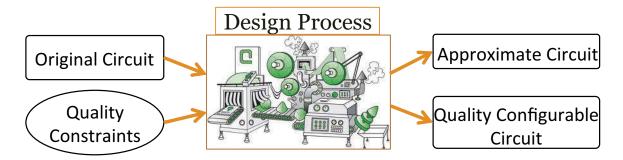

# 2. DESIGN AND SYNTHESIS OF APPROXIMATE AND QUALITY CONFIGURABLE CIRCUITS

# 2.1 Introduction

Approximate circuits, or circuits that have lower hardware complexity (switched capacitance, leakage, and critical path), while evaluating the required function within a desired accuracy, are key ingredients in the design of an approximate computing system. Given the golden specifications of a circuit and a quality constraint that denotes the type and amount of error that the implementation can accommodate, the objective of the approximate circuit design process, as illustrated in Figure 2.1, is to make judicious changes to the function to be implemented such that it translates to a more efficient implementation, while differing from the original specification in a manner bounded by the specified quality constraint. The quality constraint is typically dictated by the application based on the context in which the output of the circuit is used.

Fig. 2.1.: Approximate and quality configurable circuit design

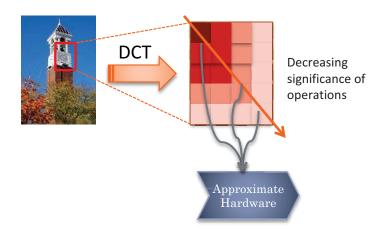

In many applications, the degree of resilience often varies across computations depending on the application context or the dataset being processed [4,8]. For example, consider the JPEG image compression application, shown in Figure 2.2, in which each 8x8 block of the image is converted to its frequency domain representation using 2-D Discrete Cosine Transform (DCT). It is well known that the output of the JPEG application is impacted the most by the DC component at the top-left corner of the image compared to to other high frequency components. Now, if the computations corresponding to each component are mapped to the same underlying hardware, then it is necessary to operate the hardware with different accuracies depending on the significance of the component. In such scenarios, it is desirable to construct a more sophisticated variant of approximate circuits, called *quality-configurable circuits*, which are capable of reconfiguring to adapt their accuracy at run-time. Quality configurable circuits typically contain additional inputs to indicate the current quality requirement and the circuits are embodied with the capability to dynamically adapt their accuracy and energy consumption accordingly. The quality constraint during their design process comprises of a series of quality levels that are desired during operation.

Fig. 2.2.: Need for quality configurable circuits

Traditionally, when it comes to the design of approximate circuits, there have been two major schools of thought: (i) Timing approximation, where the circuit is subject to voltage over-scaling resulting in timing errors [24, 25], and (ii) Functional approximation, where the circuit realizes a slightly different logic function than specified, resulting in a more efficient implementation [19–23, 26]. Currently, the design of approximate circuits is (perhaps too much of) an art, requiring significant manual effort. Previous efforts largely consist of manual designs of simple arithmetic circuits such as adders [19–22, 26] and multipliers [23]. However, a key requirement for their mainstream adoption is to develop systematic design techniques and synthesis tools that are general and scalable to arbitrary circuits and quality constraints. Ideally, tools should:

- Allow designers to simply specify the circuit and quality constraint, relieving them from the burden of how to perform the approximation.

- Generate "correct-by-construction" approximate and quality configurable circuits that are *guaranteed* to satisfy the imposed quality constraints.

- Effectively translate the flexibility engendered by the quality constraints into improvements in performance or energy consumption.

This chapter presents a rigorous framework for the automatic synthesis of approximate and quality configurable logic circuits that achieves the aforementioned objectives. Traditional Boolean optimization approaches in logic synthesis can be broadly classified into two categories [27]. One class of techniques performs local optimizations in the circuit by identifying don't care conditions on the circuit nodes [28, 29], while the other introduces perturbations in the circuit, *e.g.*, by adding wires, in-order to potentially enable the removal of redundant logic [30]. Drawing inspiration from such classical approaches, this chapter presents two approaches *viz*. SALSA [31] and SASIMI [32], for the automatic synthesis of approximate circuits. SALSA extends the classical approach of implicit don't care based optimization through *approximation don't cares*, an entirely new class of don't cares that represent the functional flexibility afforded by the specified quality constraint. SASIMI, on the other hand, adopts the circuit transformation approach and introduces *substitute-and-simplify* as a new transformation to generating approximate and quality configurable circuits.

The rest of the chapter is organized as follows. Section 2.2 presents an overview of the quality metrics commonly used in evaluating approximate circuits. A detailed description of the two design approaches SALSA and SASIMI and the methodology adopted in their respective implementations are then presented in the Sections 2.3 and 2.4. Finally, Section 2.5 provides a summary and concludes the chapter.

## 2.2 Quality Metrics

Before describing the approximate design techniques, we present an overview of the quality metrics that are typically employed in constraining the quality of the approximate circuit. As described in Section 2.1, quality metrics provide a bound on the type and amount of error that can be introduced in the implementation during the process of approximating the circuit function. They are typically a function of the original  $(O_{orig})$  and approximate  $(O_{approx})$  circuit implementations. Quality metrics can be classified into three broad categories'

## 2.2.1 Metrics Constraining the Magnitude of Error

The first class of quality metrics constrain the quantity or magnitude of error at the output of the circuit. The bound in the magnitude of error may be either absolute *i.e.* true for every input to circuit or statistical over all possible circuit inputs. Some of the most common quality metrics belonging to both the categories are described below.

Maximum Error Magnitude: The maximum error (MaxErr) metric, shown in Equation 2.1, bounds the absolute difference in magnitude between the outputs of the original and approximate circuits to be less than a specified threshold.

$$MaxErr = MAX_{\forall inputs}(|O_{acc} - O_{approx}|)$$

$$(2.1)$$

**Relative Error Magnitude:** The relative error (RelErr) metric, shown in equation 2.2, constraints the ratio of the original and approximate circuit outputs to differ from 1 by at most a certain margin.

$$RelErr = \left|\frac{O_{approx}}{O_{orig}}\right| \tag{2.2}$$

Average Error Magnitude: The average error (AveErr) metric, shown in Equation 2.3, bounds the absolute difference in magnitude between the original and approximate circuits, averaged over all possible inputs.

$$AveErr = \frac{\sum_{\forall inputs} |O_{orig} - O_{approx}|}{Total \ number \ of \ Inputs}$$

(2.3)

Mean Squared Error Magnitude: As shown in Equation 2.4, the mean squared error (MSErr) metric constrains the mean of the squared difference in magnitude between the outputs of the original and approximate circuits over all possible inputs to be less than a specified threshold.

$$AveErr = \frac{\sum_{\forall inputs} (O_{orig} - O_{approx})^2}{Total \ number \ of \ Inputs}$$

(2.4)

**Unidirectional Error:** In addition to constraining the absolute magnitude of error, unidirectional quality metrics place a restriction on the direction in which error occurs to be either positive or negative. Unidirectional variants can be conceived for each of the error magnitude based quality metrics described above.

## 2.2.2 Metrics Constraining the Frequency of Error

The second class of quality metrics constrain the frequency of error *i.e.* the number of inputs for which the circuit can an incorrect value. These metrics are particularly useful when the output of the circuit does not represent a numerical value. Few examples of quality metrics in this class are described below.

**Error Probability:** The most prominent quality metric in this class is the error probability (ErrProb) metric shown in Equation 2.5. It is defined as the fraction of inputs vectors for which the approximate circuit output differs from the original circuit.

$$ErrProb = \frac{Total \ Inputs \ for \ which \ O_{orig} \neq O_{approx}}{Total \ number \ of \ Inputs}$$

(2.5)

Bit Error Probability: The bit error probability (BitErrProb) metric, shown in Equation 2.6, is similar to the error probability metric, but in this case, the error probabilities of individual output bits are constrained separately.

$$BitErrProb^{i} = \frac{Total \ Inputs \ for \ which \ O^{i}_{orig} \neq O^{i}_{approx}}{Total \ number \ of \ Inputs}$$

(2.6)

#### 2.2.3 Composite Metrics

Composite quality metrics are a combination of both the above classes, wherein the approximate circuits are constrained in both the magnitude and the frequency of error.

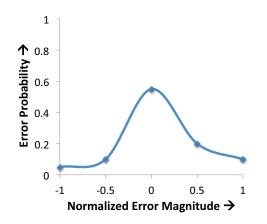

Fig. 2.3.: Error Probability Distribution

These metrics are commonly represented as an error probability distribution, shown in Figure 2.3, in which the X-axis represents the magnitude of error and the Y-axis provides the probability with which error of a given magnitude can occur in the approximate implementation.

## 2.3 SALSA: Don't Care based Logic Approximation

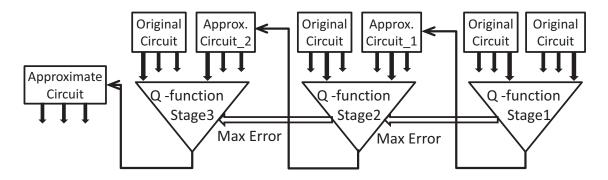

The first approximate design technique SALSA extends the concept of traditional don't cares to approximate logic synthesis. Starting with an RTL description of the exact circuit and a quality constraint that specifies the type and amount of error tolerable in the implementation, SALSA automatically synthesizes a functionally approximate version of the circuit that adheres to the pre-specified error constraints. The key steps involved in the proposed SALSA methodology are described below. First, SALSA constructs a virtual *Quality Constraint Circuit* (QCC) that encodes the specified quality constraints using logic functions called Q-functions. This enables SALSA to enforce the quality constraints during synthesis. Next, using the QCC, SALSA identifies Approximation Don't Cares (ADCs), an entirely new class of don't cares that are borne out of the quality specifications. These ADCs are then used for circuit simplification by leveraging standard don't care based optimization methodologies.

Thus SALSA rigorously reformulates the problem of Approximate Logic Synthesis (ALS) and maps it into a traditional logic synthesis problem. The problem formulation and the solution approach adopted in SALSA beget the following advantages:

- The proposed methodology provides an inherent guarantee that the specified bounds are never transgressed, thus enabling synthesis of correct-by-construction approximate circuits.

- The transformations are completely independent of the target error metric as well as the circuit considered for approximation. In essence, this decouples the synthesis procedure from the error metric, making this approach flexible and general. A variety of errors metrics can thus be specified based on the application requirements.

- Additionally, by virtue of transforming and mapping ALS to a traditional logic synthesis problem, existing off-the-shelf logic synthesis tools could just be re-used for approximate circuit synthesis. This obviates the need for developing

a custom tool for ALS, thus lowering the barrier to adoption. Further, this widens the scope of approximations that can be effected on the circuits, since the entire power of existing logic optimization algorithms can be leveraged.

SALSA is prototyped using two different logic synthesis tools *viz.* SIS [33] and Synopsys Design Compiler [34], thereby demonstrating generality and used it to synthesize a range of arithmetic circuits and datapaths. The approximate circuits synthesized by SALSA achieve significant reductions in area and power.

## 2.3.1 Preliminaries and Approach

The problem statement for approximate logic synthesis could be articulated as follows. Given the description of a logic circuit and a constraint on the errors that could be tolerated, the synthesis procedure should identify avenues for logic simplification and generate a functionally approximate version of the that satisfies the pre-defined error bounds. The following sections describes the approach used in SALSA to accomplish this objective.

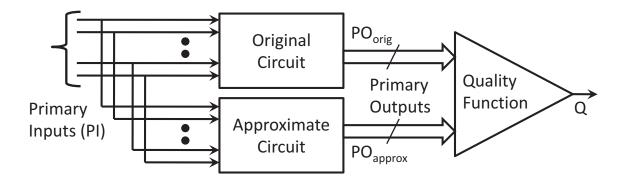

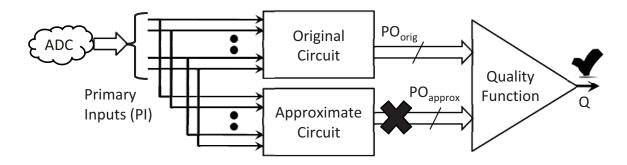

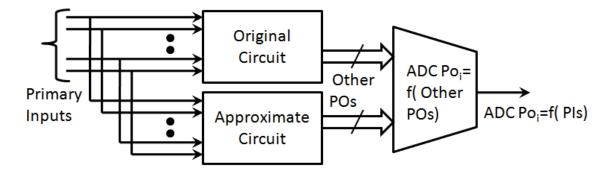

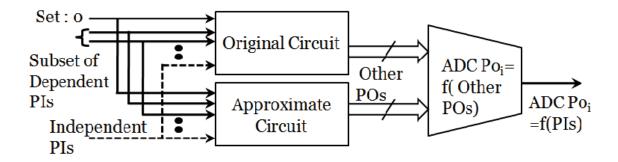

#### Quality constraint circuit

Figure 2.4 shows the Quality Constraint Circuit (QCC) that is used in SALSA to formulate the problem of approximate synthesis. The QCC is composed of three major blocks *viz.* the *Original circuit*, the *Approximate circuit* and the *Quality function* (Qfunction). The original circuit block contains a structural description of the circuit that needs to be approximated and the error constraints that are to be satisfied are encoded into the Q-function. From the problem definition, both these blocks are available as inputs to SALSA. The task of SALSA is to synthesize the approximate circuit, so that the constraints set in the Q-function are never violated.

The inputs to the QCC are the primary inputs of the circuit considered for approximation. The output of the QCC is a single bit Q that indicates whether the constraints encoded into the Q-function are satisfied. The Q-function takes outputs

Fig. 2.4.: Quality constraint circuit

from both the original circuit  $PO_{orig}$  and approximate circuit  $PO_{approx}$  and decides if the quality constraints are satisfied. A Q output of logic '1' means that the approximate circuit conforms to the imposed quality bounds whereas a logic '0' output indicates a transgression. Thus, the QCC determines the legitimacy of the approximate circuit. From a functional viewpoint, for the approximate circuit to be valid, we need to ensure that Q evaluates to '1' for all possible input combinations. Stated otherwise, the QCC with the synthesized approximate circuit should evaluate to a tautology. At all times during the approximate synthesis process, SALSA preserves this invariant.

## Quality function

As mentioned earlier, the Q-function takes in outputs from the original and approximate circuits and generates a single bit output indicating if the quality constraints are satisfied. In a circuit with M primary outputs, the Q-function maps 2M inputs into a one bit output. For example, consider the *maximum error magnitude* metric described in Section 2.2, in which the approximate output is constrained to differ from the correct output by no more than a specified value. In this case, the Q-function, as shown in Equation 2.7, is composed of a subtractor that evaluates

the difference between the original and approximate circuits outputs followed by a comparator circuit the compares the difference with a pre-determined threshold.

$$Q = \left( \left| PO_{orig} - PO_{approx} \right| \le K \right) \quad ? \quad 1:0 \tag{2.7}$$

Another example is the *relative error* metric for which the Q-function, as shown in Equation 2.8, is comprised of a divider that computes the ratio of the approximate and original circuit outputs followed by two comparators.

$$Q = \left(1 - K \le \frac{PO_{approx}}{PO_{orig}} \le 1 + K\right) \quad ? \quad 1:0 \tag{2.8}$$

Thus, in SALSA, any quality metric that could be expressed as a Boolean function of the original and approximate circuit output bits could be specified as the Q-function.

## Approximation don't cares