## Arrays of Optoelectronic Switching Nodes Comprised of Flip-Chip-Bonded MQW Modulators and Detectors on Silicon CMOS Circuitry

A. L. Lentine, *Member, IEEE, K. W. Goossen, Member, IEEE, J. A. Walker, L. M. F. Chirovsky, L. A. D'Asaro, Life Senior Member, IEEE, S. P. Hui, B. T. Tseng, R. E. Leibenguth, D. P. Kossives, D. W. Dahringer, D. D. Bacon, T. K. Woodward, <i>Member, IEEE, and D. A. B. Miller, Fellow, IEEE*

Abstract— We describe  $8\times 8$  arrays of smart pixels, designed and fabricated using MQW modulators and detectors flip-chip-solder-bonded to silicon CMOS circuits. The individual circuits implement 2 input, 1 output embedded control switching nodes. Four arrays from two different designs were fabricated and tested. For the array with the highest yield, 60 of 64 nodes functioned correctly at low speeds and were tested up to 250 Mb/s without re-adjusting individual bias voltages with the maximum speed of an individual node of 375 Mb/s. For the second-generation array, the center  $4\times 8$  section of the array was tested at data rates beyond 700 Mb/s with individual nodes having short term bit error rates below  $10^{-11}$ .

NE APPROACH to improving the performance of large processing or telecommunications switching systems is to interconnect integrated circuits using optics. Smart pixels, with integrated optical detectors, modulators, and electronic logic, could potentially be used in these systems. The FET-SEED, consisting of the monolithic integration of multiple quantum well (MQW) optical modulators and detectors with GaAs field effect transistors, is one design platform for these smart pixels [1], [2]. Another potential design platform uses the hybrid integration of MQW modulators and detectors with commercial electronic circuits [3]–[6]. This latter approach allows one to design circuits with greater complexity and circuit yield, because it uses available established VLSI processes.

We describe  $8 \times 8$  arrays of smart pixels, designed and fabricated using MQW modulators and detectors flip-chip-solder-bonded to silicon CMOS circuits. The modulators were designed for 850 nm operation and the substrate was removed to avoid excess absorption in the substrate [5]. The individual circuits implement 2 input–1 output embedded control switching nodes.

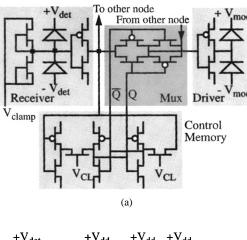

The CMOS circuit shown in Fig. 1 is functionally similar to switching nodes previously made using the monolithic FET-

Manuscript received August 9, 1995; revised October 25, 1995. This work was supported in part by ARPA under Air Force Rome Laboratories contract number F 30602-93-C-0166.

- A. L. Lentine is with AT&T Bell Laboratories, 2000 N. Naperville Rd., Naperville, IL 60566 USA.

- K. W. Goossen, J. A. Walker, T. K. Woodward, and D. A. B. Miller are with AT&T Bell Laboratories, 101 Crawfords Corner Rd., Holmdel, NJ 07733

- L. M. F. Chirovsky, L. A. D'Asaro, S. P. Hui, B. T. Tseng, D. P. Kossives, D. W. Dahringer, and D. D. Bacon are with AT&T Bell Laboratories, 600 Mountain Ave., Murray Hill, NJ 07974 USA.

- R. E. Leibenguth is with AT&T Bell Laboratories, 9999 Hamilton Blvd., Breinigsville, PA 18031 USA.

Publisher Item Identifier S 1041-1135(96)00944-5.

SEED technology [7]. Each node contains a single optical receiver. The first-generation arrays have two different receiver designs in alternating columns of the array, one with and one without voltage clamps on the receiver inputs. The secondgeneration arrays had four different transimpedence receiver designs with feedback elements shown in Fig. 1(b). The transimpedance receivers operated at lower optical powers and higher data rates. In both designs, the electrical output from a given receiver is connected to the data input of a first  $2 \times 1$ multiplexer physically located within the same node as the receiver and a second  $2 \times 1$  multiplexer physically located in a second node next to the first node. Each multiplexer has a pair of complementary electrical inputs, known as the control bit, that determines which input is regenerated as the optical output. In each node, a control memory (set-reset latch) stores this control bit. In the embedded control architecture, the format of the input optical signals consists of the control bits followed in time by the data bits. An electrical control load signal, common to all the nodes within the array, is held high to enable the writing of the control memories with the control bits. Once the control bits are loaded, the control load signal is held low to disable the writing of the memory, and the correct input data bits are regenerated at the output based upon the state of the memory. The output modulators are driven by an electrical inverter following the multiplexers. Other than the receivers, the circuit schematics were the same for the two designs, except that the FET's were wider in the secondgeneration design to provide increased current for operation at higher data rates.

The first- and second-generation circuits were designed using 1.2  $\mu$ m and 1.0  $\mu$ m CMOS. The center to center spacing of the nodes was 135  $\mu$ m  $\times$  120  $\mu$ m, so each node occupies an area equal to ~28% of that of the comparable monolithic circuit [7]. The bump-bond pad sizes and optical window sizes were 15  $\mu$ m  $\times$  15  $\mu$ m with a minimum space between two bump-bonds of 15  $\mu$ m. Transistors were located greater than 2  $\mu$ m from the bond pads, but recently circuits have been made with FET's directly under the pads [8]. The detector and modulator window spacings were 60  $\mu$ m and the spacings between detectors and modulators within a node were 75  $\mu$ m.

The MQW modulators were made using processes similar to the monolithic FET-SEED [2]. The layer structure consisted of 95 periods of 9 nm GaAs quantum wells with 3.5 nm  $Al_{0.3}Ga_{0.7}As$  barriers. Additional steps to the process included

Fig. 1. (a) Schematic diagram of embedded control  $2\times 1$  nodes of the first-generation design. T's are connected, and crosses are open unless indicated. n-fets are connected to GND, and p-fets are connected to  $V_{\rm dd}$ . Clamping transistors are present on alternate columns. (b) Receiver section for second-generation design (c) feedback elements for receivers in (b) for the different columns in the array.

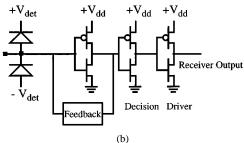

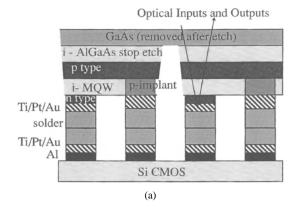

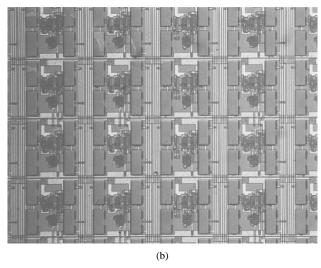

a deep mesa etch between diodes and the deposition of solder on the pads. After receiving the fabricated CMOS chips, additional metal layers (Ti, Ni, Au) and solder were deposited on the solder bump pads. After the GaAs chip was bonded to it, the GaAs substrate was removed, and the device was packaged and antirefletion coated. A more detailed description of the process is given in [5]. A cross sectional schematic and photograph of a section of a bonded chip is shown in Fig. 2. The total height of the front of the modulator from the surface of the CMOS chip is  $\sim \! 10~\mu m$ .

Three arrays of the first design and one of the second were fabricated and tested. During substrate removal, the etchent attacked some of the modulators on the end columns of the array. For one array (of the first design), all but 1 detector and 3 modulators out of 256 quantum well diodes were operational after substrate removal.

Reflectivity and responsivity were measured for this array as a function of voltage for the bonded MQW diodes. The peak responsivities varied between  $\sim$ 0.4 and  $\sim$ 0.45 A/W, the high and low state reflectivities varied from  $\sim$ 0.3- $\sim$ 0.4 and from  $\sim$ 0.06- $\sim$ 0.15 respectively at a fixed wavelength of  $\sim$ 850

Fig. 2. Cross sectional schematic (a) and photograph (b) of a section of the array. Rectangles are the individual MQW diode mesas, which measure  ${\sim}20~\mu m \times 50~\mu m$ .

nm, and the contrast ratios varied from  $\sim$ 1.8:1 to  $\sim$ 2.9:1 for a 5 V swing.

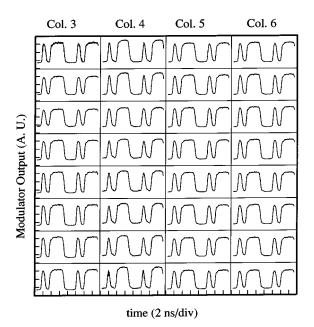

High-speed testing was done on the arrays by current modulating the two input laser diodes with complementary sets of nonreturn to zero (NRZ) data from a digital word generator and supplying these optical inputs to one receiver at a time in the array. The center  $4 \times 5$ ,  $6 \times 6$ , and  $6 \times 8$  sections of the first design operated above 250 Mb/s and individual nodes were tested to 375 Mb/s. Fig. 3 shows the one of the outputs from each node from the center 4 × 8 section of the second-generation array at 700 Mb/s, with the control set so that each  $2 \times 1$  node selected its own receiver. However, in all four arrays, we observed the same performance when either input of a given node was selected. At 700 Mb/s, the feedback resistors in columns 5 and 6 had too high of an impedance to affect the circuit, so the response was similar to column 3 that has FET clamps only. The nodes in column 4 with diode clamps required very asymmetric input powers, and the cause of this is unknown.

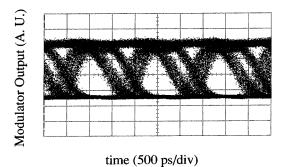

Fig. 4 shows one of the optical outputs from a node where the optical inputs to the receiver were modulated with a  $10^{-23}$  pseudorandom pattern at 700 Mb/s. There is noticeable pulsepattern dependency as evidenced by the separation of traces on the falling edges. This was likely caused by the nonlinear feedback resistor. With proper adjustment of the circuit supply

Fig. 3. Detected oscilloscope outputs from one modulator from each  $2 \times 1$  switching node from the center  $4 \times 8$  section of the second-generation array at a data rate of 700 Mb/s. The 8 bit repetitive data pattern incident on the smart pixel receivers was "0 0 0 1 0 1 1 1." The optical powers were equal to  $800~\mu\text{W}$  per beam (2.8 pJ) for columns 3, 5, and 6, but column 4 required asymmetric powers of  $800~\mu\text{W}$  and  $0~\mu\text{W}$ .

Fig. 4. Eye diagram of a particular node operating at 700 Mb/s. Individual nodes operated with short term bit-error rates below  $10^{-11}$ .

voltages and BER detector sampling point (in time), these nodes exhibited a short term bit error rate (BER) below 10<sup>-11</sup>. Laser mode-hopping prevented a long term BER measurement.

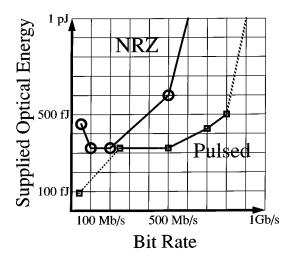

The third column of the second-generation array was particularly interesting in that it contained only feedback limiting transistors. This circuit could operate at optical powers well below 1  $\mu$ W (although slowly) and could dynamically hold its state in the absence of light. We have previously described how the diode-clamped receiver can make use of this fact to operate more efficiently with optical inputs of short duration [9], [10]. Our measurements on this receiver show the same trend.

In Fig. 5, we show the supplied input optical energy for that receiver as a function of bit-rate for both nonreturn to zero (NRZ) and short pulsed inputs. The NRZ data is based on a BER for pseudorandom signals below 10<sup>-11</sup>. For the pulsed data, we were unable to supply pseudorandom data, so the optical energies are based on visual inspection of the bit-pattern. We obtained clean patterns to 800 Mb/s and sightly

Fig. 5. Optical energy versus bit-rate for the nodes in the third column of the array for nonreturn to zero (NRZ) and return to zero (pulsed) data inputs.  $V_{\rm dd}$  was lowered to 3 V for data at 25 Mb/s.

degraded patterns to 1 Gb/s. We believe the speed in both chips was limited by the driver and multiplexer circuitry.

## REFERENCES

- D. A. B. Miller, M. D. Feuer, T. Y. Chang, S. C. Shunk, J. E. Henry, D. J. Burrows, and D. S. Chemla, "Field-effect transistor self-electrooptic effect device: Integrated photodiode, quantum well modulator and transistor," *IEEE Photon. Technol. Lett.*, vol. 1, pp. 61–64, 1989.

- [2] L. A. D'Asaro, L. M. F. Chirovsky, E. J. Laskowski, S. S. Pei, T. K. Woodward, A. L. Lentine, R. E. Leibenguth, M. W. Focht, J. M. Freund, G. D. Guth, and L. E. Smith, "Batch fabrication and operation of GaAs-AlGaAs field effect transistor self electro-optic effect device (FET-SEED's) smart pixel arrays," *IEEE J. Quantum Electron.*, vol. 29, pp. 670–677, 1993.

- pp. 670–677, 1993.

[3] J. Wieland, H. Melchoir, M. Q. Kearly, C. Morris, A. J. Mosley, M. G. Goodwin, and R. C. Goodfellow, "Optical receiver array in silicon bipolar technology with self aligned, low parasitic III–V detectors for DC-1 Gb/s parallel data links," *Electron. Lett.*, vol. 27, p. 2211, 1991.

- [4] C. Camperi-Ginestet, M. Hargis, N. Jokerst, and M. Allen, "Alignable epitaxial lift-off of GaAs materials with selective deposition using polyimide diaphrams," *IEEE Photon. Technol. Lett.*, vol. 3, p. 1123, 1991.

- [5] K. W. Goossen, J. A. Walker, L. A. D'Asaro, S. P. Hui, B. Tseng, R. Leibenguth,, D. Kossives, L. M. F. Chirovsky, A. L. Lentine, and D. A. B. Miller, "GaAs MQW modulators integrated with silicon CMOS," *IEEE Photon. Technol. Lett.*, vol. 7, pp. 360–362, 1995.

- [6] T. L. Worchesky, R. J. Ritter, R. Martin, and B. Lane, "Large arrays of spatial light modulators hybridized to silicon integrated circuits," OSA Topical Meeting on Spatial Light Modulators, Salt Lake City, UT 1995, Postdeadline paper PD3.

- [7] A. L. Lentine, R. A. Novotny, T. J. Cloonan, L. M. F. Chirovsky, L. A. D'Asaro, G. Livescu, S. Hui, M. W. Focht, J. M. Freund, G. D. Guth, R. E. Leibenguth, K. G. Glogovsky, and T. K. Woodward, "4 × 4 arrays of FET-SEED embedded control 2 × 1 optoelectronic switching nodes with electrical fan-out," *IEEE Photon. Technol. Lett.*, vol. 6, pp. 1126–1129, 1994.

- [8] A. V. Krishnamoorthy, A. L. Lentine, K. W. Goossen, J. A. Walker, T. K. Woodward, J. E. Ford, G. F. Aplin, L. A. D'Asaro, S. P. Hui, B. Tseng, R. E. Leibenguth, D. Kossives, D. Dahringer, L. M. F. Chirovsky, and D. A. B. Miller, "3-D integration of MQW modulators over active submicron CMOS circuits: 375 Mb/s transimpedance receiver-transmitter circuit," *IEEE Photon. Technol. Lett.*, vol. 7, no. 11, pp. 1288–1290, 1995.

- [9] A. L. Lentine, L. M. F. Chirovsky, and T. K. Woodward, "Optical energy considerations for diode-clamped smart pixel optical receivers," *IEEE J. Quantum Electron.*, vol 30, pp. 1167–1171, 1995.

- [10] T. K. Woodward, A. L. Lentine, and L. M. F. Chirovsky, "Experimental sensitivity studies of diode-clamped FET-SEED smart pixel optical receivers," *IEEE J. Quantum Electron.*, pp. 2319–2324, 1994.