# UvA-DARE (Digital Academic Repository)

### Aspects of algorithms and complexity

Tromp, J.T.

Publication date 1993 Document Version Final published version

Link to publication

Citation for published version (APA):

Tromp, J. T. (1993). Aspects of algorithms and complexity.

#### General rights

It is not permitted to download or to forward/distribute the text or part of it without the consent of the author(s) and/or copyright holder(s), other than for strictly personal, individual use, unless the work is under an open content license (like Creative Commons).

Disclaimer/Complaints regulations

If you believe that digital publication of certain material infringes any of your rights or (privacy) interests, please let the Library know, stating your reasons. In case of a legitimate complaint, the Library will make the material inaccessible and/or remove it from the website. Please Ask the Library: https://uba.uva.nl/en/contact, or a letter to: Library of the University of Amsterdam, Secretariat, Singel 425, 1012 WP Amsterdam, The Netherlands. You will be contacted as soon as possible.

UvA-DARE is a service provided by the library of the University of Amsterdam (https://dare.uva.nl)

Aspects of Algorithms and Complexity

|  |  | + |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

# Aspects of Algorithms and Complexity

## Academisch Proefschrift

ter verkrijging van de graad van doctor aan de Universiteit van Amsterdam op gezag van de Rector Magnificus prof. dr P.W.M. de Meijer in het openbaar te verdedigen in de Aula der Universiteit (Oude Lutherse Kerk, ingang Singel 411, hoek Spui), op donderdag 16 december 1993 te 13.30 uur

door

Johannes Theodorus Tromp

geboren te Alkmaar

Promotor: prof. dr. ir. P.M.B. Vitányi

Promotie-commissie: prof. dr. K. Apt dr. P. van Emde Boas prof. dr. J. van Leeuwen dr. G. Tel dr. L. Torenvliet

Faculteit Wiskunde en Informatica Universiteit van Amsterdam

Partial support for the research described in this thesis was received as a CWI fellowship (oio plaats), and from the Dutch organization for scientific research NWO under NFI project Aladdin, project number NF 62-376.

to my parents

# Acknowledgements

The following publications form the basis of the chapters of this thesis.

- Chapter 2: A. Blum, T. Jiang, M. Li, J. Tromp, M. Yannakakis, *Linear Approximation of Shortest Superstrings*, Proc. of the 23rd annual ACM Symposiom on Theory of Computing (STOC91), New Orleans, May 1991, pp. 328–336. *Journal of the ACM*, to appear.

- Chapter 4: G. Kissin, J. Tromp, The energy complexity of threshold and other functions, CWI Technical Report CS-R9101, January 1991.

- Chapter 5: J. Tromp, P. van Emde-Boas, Associative Storage Modification Machines, in: "Complexity Theory", Ambos-Spies, Homer, and Schoning (editors), Cambridge University Press.

- Chapter 6: J. Tromp, How to Construct an Atomic Variable, Proc. of the 3rd International Workshop on Distributed Algorithms, Lecture Notes in Computer Science 392, Springer-Verlag, pp. 292–302, 1989.

- Chapter 7: M. Li, J. Tromp, P.M.B. Vitányi, How to Share Concurrent Wait-Free Variables, (under revision for Journal of the ACM).

- Chapter 8: J. Tromp, J-H. Hoepman, Binary Snapshots, Proc. of the 5th International Workshop on Distributed Algorithms, Lecture Notes in Computer Science 725, Springer-Verlag, pp. 18–25 1993.

- Chapter 9: J. Tromp, On Update-Last Schemes, Parallel Processing Letters 3(1), pp. 25–28, 1993.

The co-authors of the above papers have greatly contributed to the thesis. I would like to thank all of them for their inspiring cooperation, and the referees of the journal publications for their helpful comments.

My greatest debt is to my promotor Paul Vitányi, whose guidance and support have been most stimulating. In Evangelos Kranakis I found an excellent colleague and tutor. I thank Ming Li and Amos Israeli for giving me the opportunity to cooperate with them in Waterloo and Haifa respectively, and making those stays so enjoyable both in work and play.

My stay at CWI has been enlivened by numerous guests, each of which added a different facet to my scientific world view: Danny Krizanc, Gloria Kissin, Peter Clote, Hyunyong Shin, Amnon Shaham, Shlomo Moran, Dany Breslauer, Joerg Keller, Peter Gacs, Vladimir Uspensky, Philippas Tsigas, Marina Papatriantafilou, and Alessandro Panconesi.

Our department secretary Marja Hegt has been quite tolerant of my sometimes clumsy behaviour in administrative matters.

In addition, I want to thank all the following people for sharing their time and ideas with me: Victor Allis, Krzysztof Apt, Andries Brouwer, Harry Buhrman, David Chaum, Matthijs Coster, Shlomi Dolev, Herman Ehrenburg, Willem Jan Fokkink, Peter Grunwald, Petra van Haaften, Sibsankar Haldar, Eugene van Heijst, Ted Herman, Ray Hirschfeld, Henk de Koning, Karst Koymans, Pieter van Langen, Jan van Leeuwen, Jan van de Lune, Jeroen van Maanen, Lambert Meertens, Raymond Michiels, Eric Ristad, Marius Schilder, Anneke Schoone, Lex Schrijver, Jan van der Steen, Gerard Tel, Leen Torenvliet, K. Vidyasankar, and Freek Wiedijk.

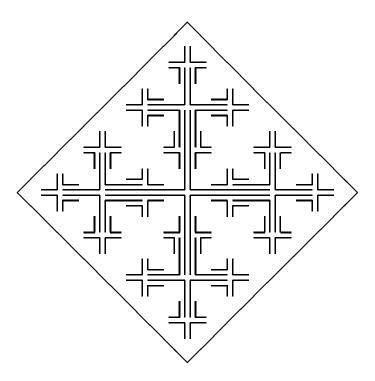

The cover illustration is a graphical depiction of the game-theoretical value of all up-to-4-ply positions in the game of connect-4. The largest disc represents the (empty) initial board, and is colored white to indicate a 1st player win. Drawn positions are colored light-green, and lost (to the 1st player) positions green.

The seven sub-discs of all but the smallest discs represent positions resulting from a move in one of the seven columns of the board, as follows:

# Contents

|          | Ack            | knowledgements                                                    | vi        |

|----------|----------------|-------------------------------------------------------------------|-----------|

|          | List           | of Figures                                                        | 1         |

| 1        | Inti           | roduction                                                         | 2         |

|          | 1.1            | Algorithms                                                        | 2         |

|          | 1.2            | Complexity                                                        | 3         |

|          | 1.3            |                                                                   | 5         |

|          | 1.4            | Overview                                                          | 5         |

| <b>2</b> | Lin            | ear Approximation of Shortest Superstrings                        | 8         |

|          | 2.1            | Introduction                                                      | 8         |

|          | 2.2            | Preliminaries                                                     | 9         |

|          | 2.3            | A $4 \cdot \mathrm{OPT}(S)$ bound for a modified greedy algorithm | 13        |

|          | 2.4            | Improving to $3 \cdot \text{OPT}(S)$                              | 16        |

|          | 2.5            | GREEDY achieves linear approximation                              | 17        |

|          | 2.6            | Which algorithm is the best?                                      | 22        |

|          | 2.7            | Lower bound                                                       | 22        |

|          | 2.8            | Open problems                                                     | 24        |

|          | $\mathbf{Bib}$ | liography                                                         | <b>25</b> |

| 3        | On             | Labyrinth Problems and Flood-Filling.                             | 27        |

|          | 3.1            | Introduction                                                      | 27        |

|          |                | 3.1.1 Properties and Operations                                   | 27        |

|          |                | 3.1.2 Terminology                                                 | 28        |

|          | 3.2            | Depth First Filling                                               | 29        |

|          | 3.3            | Breadth First Filling                                             | 30        |

|          | 3.4            | The price of disconnecting                                        | 30        |

|          | 3.5            | On planar embeddings                                              | 31        |

|   | 3.6<br>3.7 | 3.5.1 Exploring the labyrinth 3.5.2 Finding a non-cutting point 3.5.3 Termination 3.5.4 Improving Time Complexity The constant space FFA Conclusion |

|---|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Bib        | liography                                                                                                                                           |

| 4 | The        | Energy Complexity of Threshold and other functions.                                                                                                 |

|   | 4.1        | The setting                                                                                                                                         |

|   | 4.2        | 4.1.1 Model Motivation                                                                                                                              |

|   | 4.2        | 4.2.1 Energy-Efficient k-Threshold Circuit                                                                                                          |

|   | 4.3        | Conclusions                                                                                                                                         |

|   | Bib        | liography                                                                                                                                           |

| 5 | Ass        | ociative Storage Modification Machines                                                                                                              |

| _ | 5.1        | Introduction                                                                                                                                        |

|   | 5.2        | The SMM and the ASMM models                                                                                                                         |

|   | 5.3        | An illustration of the power of associativity                                                                                                       |

|   | 5.4        | $PSPACE = ASMM - (N)PTIME \dots$                                                                                                                    |

|   |            | 5.4.1 $QBF \in ASMM - TIME(n^2) \dots \dots \dots \dots \dots$                                                                                      |

|   |            | 5.4.2 $\overrightarrow{ASMM}$ - $\overrightarrow{NTIME}(t) \subseteq \overrightarrow{SPACE}(t^2)$                                                   |

|   | 5.5        | Conclusion                                                                                                                                          |

|   | Bib        | liography                                                                                                                                           |

| 6 | Hov        | w to Construct an Atomic Variable                                                                                                                   |

|   | 6.1        | Introduction                                                                                                                                        |

|   | 6.2        | Comparison with Related Work                                                                                                                        |

|   | 6.3        | Preliminaries                                                                                                                                       |

|   |            | 6.3.1 Making Safe Bits Regular                                                                                                                      |

|   | 6.4        | Problem Statement                                                                                                                                   |

|   | 6.5        | Optimal Construction of Atomic Bits                                                                                                                 |

|   |            | 6.5.1 A Lower Bound on the Number of Safe Bits needed to                                                                                            |

|   |            | Construct an Atomic Bit                                                                                                                             |

|   |            | 6.5.2 The Architecture                                                                                                                              |

|   |            | 6.5.3 The Protocols                                                                                                                                 |

|   |            | 6.5.4 Handshaking                                                                                                                                   |

|   | 0.0        | 6.5.5 Proof of Correctness                                                                                                                          |

|   | 6.6        | The 4-track Protocol                                                                                                                                |

|   |            | 6.6.1 Correctness                                                                                                                                   |

|   | o =        | 6.6.2 Space Complexity                                                                                                                              |

|   | 6.7        | The Atomicity Automaton                                                                                                                             |

|   |            | 6.7.1 Using the Automaton for Verification of a given Run                                                                                           |

|   |            | 6.7.2 Verifying the Atomic Bit Construction                                                                                                         |

|   | 0.0        | 6.7.3 Verifying the Safe Byte Switch Construction                                                                                                   |

|   | 6.8        | Correctness of Safe Byte Switch Construction                                                                                                        |

|   | 6.9                                           | Conclusions                        | 85                                                                                                        |

|---|-----------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------|

|   | Bib                                           | liography                          | 86                                                                                                        |

| 7 | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7 | Introduction                       | 88<br>88<br>89<br>90<br>91<br>92<br>94<br>94<br>96<br>97<br>100<br>101<br>102<br>102<br>104<br>105<br>107 |

|   |                                               | liography                          | 109                                                                                                       |

| 8 |                                               | ary Snapshots                      | 112                                                                                                       |

|   | 8.1<br>8.2                                    | Introduction                       | 112<br>113                                                                                                |

|   | 8.3                                           | Atomic Snapshot Memories           | $113 \\ 114$                                                                                              |

|   | 8.4                                           | The Solution                       | 114                                                                                                       |

|   | 0.4                                           | 8.4.1 The Architecture             | $114 \\ 115$                                                                                              |

|   |                                               |                                    | $115 \\ 115$                                                                                              |

|   | 0.5                                           |                                    | _                                                                                                         |

|   | 8.5<br>8.6                                    | Proof of Correctness               | 116<br>118                                                                                                |

|   |                                               |                                    |                                                                                                           |

|   |                                               | liography                          | 119                                                                                                       |

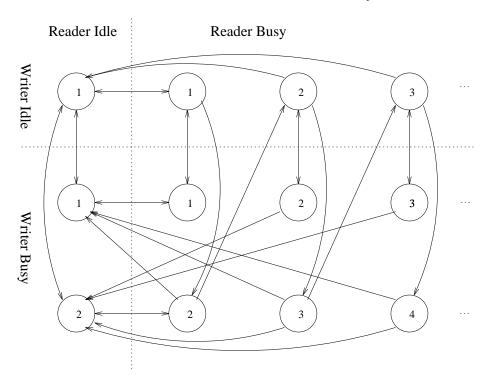

| 9 | On                                            | Update-Last Schemes                | 121                                                                                                       |

|   | 9.1                                           | Introduction                       | 121                                                                                                       |

|   | 9.2                                           | Related Work                       | 122                                                                                                       |

|   | 9.3                                           | Characterizing Update-Last schemes | 122                                                                                                       |

|   | 9.4                                           | Further Work                       | 123                                                                                                       |

|   | Bib                                           | liography                          | <b>124</b>                                                                                                |

|   | Samenvatting (Dutch)                          |                                    |                                                                                                           |

|   | San                                           | lenvarring (Dutch)                 | 125                                                                                                       |

# \_

# List of Figures

| 2.1 | The overlap and distance graphs                                             | 12  |

|-----|-----------------------------------------------------------------------------|-----|

| 2.2 | Strings and overlaps                                                        | 13  |

| 2.3 | Culprits and weak links in Greedy merge path                                | 19  |

| 2.4 | Left/middle and middle/right parts with weak links                          | 20  |

| 3.1 | A worst case example region for breadth first fill                          | 31  |

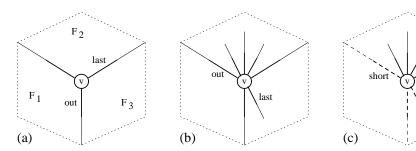

| 3.2 | Connectivity tests                                                          | 34  |

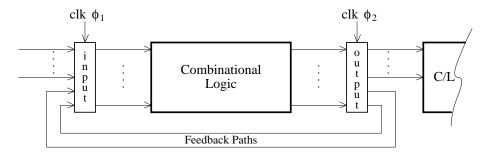

| 4.1 | Preferred Sequential Circuit: a Finite State Machine                        | 41  |

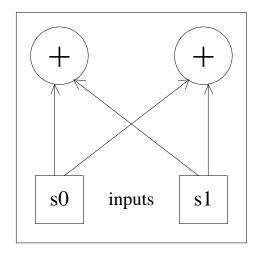

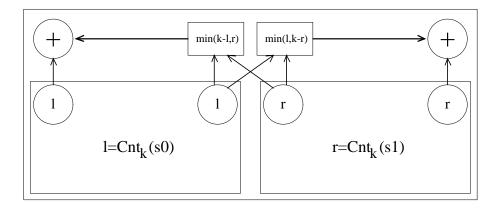

| 4.2 | Bottom Layer of an Embedding of Circuit $Cnt_k \dots \dots$                 | 43  |

| 4.3 | Middle/Upper Layer of an Embedding of Circuit $Cnt_k$                       | 43  |

| 5.1 | storage structure for $\exists x_0 \forall x_1 : x_0 \land x_1 \dots \dots$ | 56  |

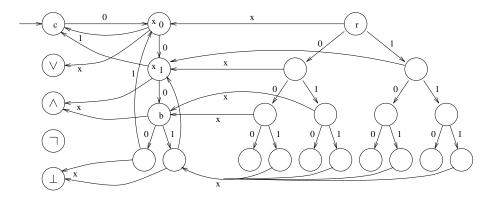

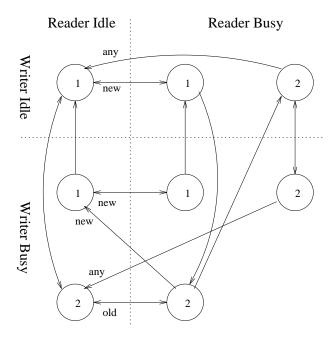

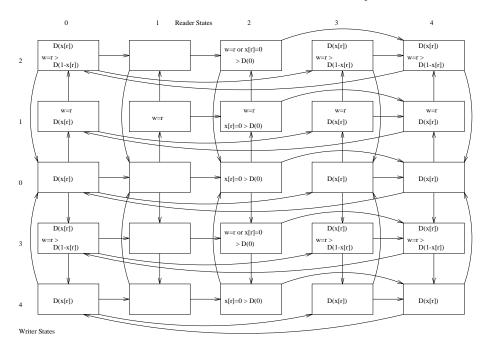

| 6.1 | state diagram of 4-track construction                                       | 75  |

| 6.2 | the general atomicity automaton                                             | 79  |

| 6.3 | the atomic bit automaton                                                    | 81  |

| 6.4 | state diagram of 4-track construction with safe byte switch $$ . $$         | 83  |

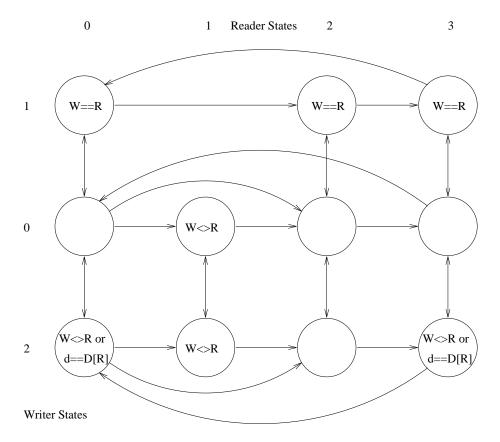

| 7.1 | Construction $0 \dots \dots \dots \dots \dots \dots$                        | 93  |

| 7.2 | Construction 1                                                              | 95  |

| 7.3 | Construction 3                                                              | 106 |

| 7 / | Construction A: single to multi reader                                      | 108 |

# Introduction

The papers collected in subsequent chapters give a fair representation of my research at CWI and the several places I visited abroad. The diversity in subject matter reflects on the one hand the multitude of interests I like to pursue and on the other hand the failure to remain focussed on a single problem area in which to make more extensive explorations.

With such diversity, a title as general as "Aspects of Algorithms and Complexity" seem inevitable, but also holds a promise of finding the links and relations that connect them. To this end, let us consider the concepts involved in some more detail.

# 1.1 Algorithms

An algorithm is normally understood to be a "recipe" for solving a (computational) problem. That is, a step by step explanation of how to get from a problem instance to a solution. A classical example is the problem of sorting. Here, a problem instance is a list of numbers, like 5, 2, 8, 3, 5, and a solution is a permutation (re-ordering) of that list, in which the numbers are non-decreasing, like 2, 3, 5, 5, 8. The problem instance is called the *input* and the solution the *output*. The solution is also sometimes called the *answer*, in particular when the problem instance can be considered a question.

The word 'algorithm' is formally reserved to those recipes that always yield an output in a finite number of steps, in other words, that always terminate. The problems considered in Chapters 2, 3, and 4 are of this type. But the word is sometimes also used for processes that aren't even supposed to terminate, like the workings of an elevator. For such processes, the word 'protocol' is more appropriate. A protocol is like a rule of behaviour. The goal of a protocol is not to find a solution to a problem instance, but rather to insure a particular, desirable, behaviour in a system. An elevator protocol must insure for instance

that people get to the floor they want to in a reasonable amount of time. A research field known as 'distributed computing' is devoted to the study of algorithms and protocols for communication, cooperation and competition between multiple, more or less independent, computing agents. Chapters 7,8, and 9 deal with some problems of this type.

As mentioned earlier, an algorithm prescribes a sequence of steps to lead from a given input to an output. This still leaves open the questions of what a step is, how the input is given, and finally how the output is obtained and/or interpreted. We see that an algorithm is not complete without a specification of its operating environment. The classical notion of an algorithm is that of a program running inside a box called computer, with some input device reading the input symbol by symbol, and an output device writing the output symbol by symbol. In this framework, the input and output are words of some input, respectively, output language. A so called 'machine model' specifies the form of programs that a box will run and what operations it can perform in a single step. In some models the steps are executed strictly in sequence, one after the other. These models are said to be sequential. A parallel model is one where the steps are not necessarily executed in sequence, but is also used for models that are in a sense more powerful than the simplest sequential ones.

The computer will have some form of *storage space* of unlimited capacity, like a tape, where intermediate results are kept. The program usually consists of a list of instructions executed in order except for branches, and each instruction modifies only a small fixed-size part of the storage. This is basically the machine model that Alan Turing envisioned as the machine-equivalent of a human working with pen and paper, and known as a 'Turing machine'. Turing's goal was to have a formal basis for deciding what it means for an input-output function to be 'computable'. He could probably not imagine the large variety of alternative machine models that have been proposed since as a subject of study in its own right. One such model is investigated in Chapter 5.

We can also view the Turing machine as a box that's travelling over a single tape that initially holds the input, and whose contents is taken as output when the box goes into a halting state. We can then replace the tape by an arbitrary graph and allow the box to drop various types of markers on the nodes to get a class of algorithms known as 'bug automata'. These are well suited to labyrinth exploration problems and come into action in Chapter 3.

In a more physical view, algorithms can take the form of *circuits* built from wires and gates. Since the number of inputs of a circuit is *hard-wired* and thus fixed, it is more precise to say that an algorithm corresponds to a *family* of circuits, working on larger and larger inputs. The gates are the steps of the algorithm, and are clearly not executed in sequence. In Chapter 4 we will see an example of a circuit family.

# 1.2 Complexity

For many problems studied in theoretical computer science, the question of whether it can be solved at all is not interesting, as the answer is invariably yes. The question becomes interesting only when the class of algorithms considered is reduced. Usually we are interested in those algorithms that are the least

complex. A complexity measure is then a way of quantifying how complex an algorithm is. One type of complexity that is of great practical importance is conceptual complexity: how hard is it to understand an algorithm? This however is rather difficult if not impossible to quantify and thus appears only in informal discussion.

If the algorithm can be written down as a sequence of symbols in a standard language, then an obvious complexity measure is the length of that sequence. Combining this with the idea of looking at all algorithms and inputs that produce a given output leads to a very interesting notion of the inherent description complexity of that output. The theory dealing with this notion, known under the names of Kolmogorov Complexity and Algorithmic Information Theory, will not be dealt with in this thesis.

Most complexity measures concern the use of resources during execution of the algorithm, the two most important ones being time and space. On a sequential machine, time is simply measured as the number of steps taken to go from the input to the output. On parallel machines, a parallel notion of time is introduced that reflects the simultaneous execution of steps. For the total number of steps executed, irrespective of timing, the term 'work' is used instead. These notions also apply to circuits, although they carry different names. The (parallel) time of a circuit is taken to be the maximum distance from an input to an output node, and is called the 'depth' of the circuit, used for this purpose, and called 'depth'. The amount of work done by a circuit equals its gate count.

Space is measured as the maximum size of the storage space used. In some machine models the precise formalization of this requires some care to ensure 'compatibility' with other models (not surprising considering the many different forms that storage space comes in). In the case of circuits space can be taken as the (rectangular) area needed by an embedding of the circuit in the plane (with limited cross-over).

In order to proceed from resources like time and space to the corresponding complexity measures, we express their use in terms of the size of the input. Size is defined to be a natural number that is roughly proportional to the length of the input in some standard notation. When inputs are words in some input language, then their size is simply defined as their length. If an input is a graph for instance, then the number of nodes plus the number of edges is a reasonable definition of size. Usually, the bigger the input, the more resources are needed. A complexity measure tells you how quickly the use of resources grows with input size: it is a function that gives for each size the maximum amount of resource used, over all inputs of that size. Apart from this worst-case measure, one can also consider an average case complexity, where the average of resource used is taken over all inputs.

Chapter 4 considers an practically significant resource for circuits, namely energy consumption. In conventional technologies, whenever the input to a circuit changes, some subset of the gates and wires will switch and the energy dissipated hereby in the from of heat is proportional to the sum area of all switching elements.

In randomized algorithms, choices can be made based on the outcome of random coin flips. Randomness is used either to ensure a high probability of giving the correct answer, or to limit the (expected) time to find the correct answer. In either case, number of coin flips is a useful resource.

Closely related to randomness, is the resource of *queries*. A query is a question that the algorithm can ask, from some set of allowed questions, to always be given the right answer. Like a random coin flip, this is one external bit of information, except it can only come out one way.

The last 'resource' we'll discuss is the size of the output. This becomes interesting when for each input, more than one output solution is possible. The closer in size a solution is to the minimal one, the better. Chapter 2 is exclusively concerned with this output approximation complexity for a specific problem.

### 1.3 Trade-offs

Complexity measures can rarely be considered in isolation. This is because one resource can often be minimized at the cost of several others. Most resources can be minimized at the cost of making the time exponential in the size of input. Since exponential time (or for that matter exponential anything) is considered an extremely bad property for an algorithm to have, this trade-off is hardly ever even considered. We are interested in trade-offs between resources that all remain polynomial.

In Chapter 3, a trade-off is established between time and space for a particular exploration-type problem. It is shown that various different algorithms have the same space-time-product complexity, up to constant factors. Sometimes algorithms are designed with a single parameter that can be varied to produce any desired trade-off of resources between two extremes.

In the domain of circuits, the familiar time-space trade-off translates into a depth-area tradeoff. It is known for instance that a logarithmic depth circuit on n inputs needs on the order of  $n \log(n)$  area to be embedded in the plane (assuming the n inputs lie on a convex boundary). If the depth is relaxed, then often a linear embedding is possible. For circuits, logarithmic depth is considered just as desirable as polynomial time is for sequential machines. Thus, in Chapter 4, the resource of energy is minimized under the requirement of logarithmic depth.

#### 1.4 Overview

In Chapter 2, we consider the following problem: given a collection of strings  $s_1, \ldots, s_m$ , find the shortest string s such that each  $s_i$  appears as a substring (a consecutive block) of s. Although this problem is known to be NP-hard, a simple greedy procedure appears to do quite well and is routinely used in DNA sequencing and data compression practice, namely: repeatedly merge the pair of (distinct) strings with maximum overlap until only one string remains. Let n denote the length of an optimal (shortest) superstring. A common conjecture states that the above greedy procedure produces a superstring of length O(n) (in fact, 2n), yet the only previous nontrivial bound known for any polynomial-time algorithm is a recent  $O(n \log n)$  result.

We show that the greedy algorithm does in fact achieve a constant factor approximation, proving an upper bound of 4n. Furthermore, we present a simple

modified version of the greedy algorithm that we show produces a superstring of length at most 3n. We also show the superstring problem to be  $MAX\ SNP$ -hard, which implies that a polynomial-time approximation scheme for this problem is unlikely.

In Chapter 3, we examine the space complexity of flood-filling. Fill algorithms are commonly used for changing the color of a region of pixels. A flood-fill algorithm (FFA) is given a *seed* pixel from which it starts exploring the region delimited by a *boundary* of arbitrary shape. Most known FFAs can be notoriously memory hungry, using in the worst case even more space than is devoted to storing the screen image. While such regions never show up in practice, it may be of interest to find an FFA with minimal worst-case memory requirements. We present an FFA that uses only a constant amount of space, in addition to that in which the image is stored. The price it pays for this memory friend-liness is a possible lack of speed—in the worst case time is quadratic in the number of pixels. It thus achieves the same space-time product of  $O(n^2)$  as do the common FFAs with linear space and linear time, illustrating a well-known time-space tradeoff.

Chapter 4 turns to the study of a *hardwired* algorithm; a novel construction is described that yields fast, minimum energy VLSI circuits that compute k-threshold and count-to-k functions. The results are obtained in the Uniswitch Model of switching energy.

In Chapter 5, we move from the study of algorithms to the study of computational models. We present a parallel version of the storage modification machine. This model, called the Associative Storage Modification Machine (ASMM), has the property that it can recognize in polynomial time exactly what Turing machines can recognize in polynomial space. The model therefore belongs to the Second Machine Class, consisting of those parallel machine models that satisfy the parallel computation thesis. The Associative Storage Modification Machine obtains its computational power from following pointers in the reverse direction.

Chapters 6,7 and 8 consider the space and time complexity of constructing certain types of shared memory out of simpler building blocks. The protocols involved are designed to be wait-free: any operation on the constructed memory can be completed with only a bounded number of accesses to the simpler memory objects, irrespective of the relative execution speeds. Such implementations, where processors need not wait for each other to get access to memory, help to exploit the amount of parallelism inherent in distributed systems.

We present solutions to the problem of simulating an atomic single-reader, single-writer variable with non-atomic bits. The first construction, for the case of a 2-valued atomic variable (bit), achieves the minimal number of non-atomic bits needed. The main construction of a multi-bit variable avoids repeated writing (resp. reading) of the value in a single write (resp. read) action on the simulated atomic variable. It improves on existing solutions of that type in simplicity and in the number of non-atomic bits used, both in presence and in accesses per read/write action. We show how to verify these constructions by machine, based on atomicity-testing automata.

Chapter 7 presents a construction of an multi-user atomic variable directly from single-writer, single-reader atomic variables. It uses a linear number of control bits, and a linear number of accesses per Read/Write running in con-

stant parallel time.

In Chapter 8 we consider the *atomic snapshot* object in its simplest form where each cell contains a single bit. We demonstrate the 'universality' of this binary snapshot object by presenting an efficient linear-time implementation of the general multi-bit atomic snapshot object using an atomic binary snapshot object as a primitive. Thus, the search for an efficient (sub-quadratic or linear time) wait-free atomic snapshot implementation may be restricted to the binary case.

In the final Chapter, number 9, we introduce the notion of Update-Last Scheme as a distributed method of storing an index, and derive exact bounds on their space complexity.

# Linear Approximation of Shortest Superstrings

### 2.1 Introduction

Given a finite set of strings, we would like to find their shortest common superstring. That is, we want the shortest possible string s such that every string in the set is a substring of s.

The question is NP-hard [5, 6]. Due to its important applications in data compression [14] and DNA sequencing [8, 9, 13], efficient approximation algorithms for this problem are indispensable. We give an example from the DNA sequencing practice. A DNA molecule can be represented as a character string over the set of nucleotides  $\{A, C, G, T\}$ . Such a character string ranges from a few thousand symbols long for a simple virus to approximately  $3 \times 10^9$  symbols for a human being. Determining this representation for different molecules, or sequencing the molecules, is a crucial step towards understanding the biological functions of the molecules. With current laboratory methods, only small fragments (chosen from unknown locations) of at most 500 bases can be sequenced at a time. Then from hundreds, thousands, sometimes millions of these fragments, a biochemist assembles the superstring representing the whole molecule. A simple greedy algorithm is routinely used [8, 13] to cope with this job. This algorithm, which we call GREEDY, repeatedly merges the pair of (distinct) strings with maximum overlap until only one string remains. It has been an open question as to how well GREEDY approximates a shortest common superstring, although a common conjecture states that GREEDY produces a superstring of length at most two times optimal [14, 15, 16].

From a different point of view, Li [9] considered learning a superstring from randomly drawn substrings in the Valiant learning model [17]. In a restricted sense, the shorter the superstring we obtain, the smaller the number of samples are needed to infer a superstring. Therefore finding a good approximation bound for shortest common superstring implies efficient learnability or inferability of DNA sequences [9]. Our linear approximation result improves Li's

$O(n \log n)$  approximation by a multiplicative logarithmic factor.

Tarhio and Ukkonen [15] and Turner [16] established some performance guarantees for GREEDY with respect to the "compression" measure. This basically measures the number of symbols saved by GREEDY compared to plainly concatenating all the strings. It was shown that if the optimal solution saves l symbols, then GREEDY saves at least l/2 symbols. But, in general this implies no performance guarantee with respect to optimal length since in the best case this only says that GREEDY produces a superstring of length at most half the total length of all the strings.

In this chapter we show that the superstring problem can be approximated within a constant factor, and in fact that algorithm GREEDY produces a superstring of length at most 4n. Furthermore, we give a simple modified greedy procedure MGREEDY that also achieves a bound of 4n, and then present another algorithm TGREEDY, based on MGREEDY, that we show achieves 3n.

The rest of the chapter is organized as follows: Section 2.2 contains notation, definitions, and some basic facts about strings. In Section 2.3 we describe our main algorithm MGREEDY with its proof. This proof forms the basis of the analysis in the next two sections. MGREEDY is improved to TGREEDY in Section 2.4. We finally give the 4n bound for GREEDY in Section 2.5. In Section 2.7, we show that the superstring problem is  $MAX\ SNP$ -hard which implies that there is unlikely to exist a polynomial time approximation scheme for the superstring problem.

### 2.2 Preliminaries

Let  $S = \{s_1, \ldots, s_m\}$  be a set of strings over some alphabet  $\Sigma$ . Without loss of generality, we assume that the set S is "substring-free" in that no string  $s_i \in S$  is a substring of any other  $s_j \in S$ . A common superstring of S is a string S such that each S in S is a substring of S. That is, for each S is a string S can be written as S is a substring of S is a substring of S in S is a substring of S. We will use S and S interchangeably for the length of the shortest common superstring for S. Our goal is to find a superstring for S whose length is as close to S as possible.

**Example.** Assume we want to find the shortest common superstring of all words in the following sentence: "Alf ate half lethal alpha alfalfa". The word "alf" is a substring of both "half" and "alfalfa", so we can immediately eliminate it. Our set of words is now  $S_0 = \{$  ate, half, lethal, alpha, alfalfa  $\}$ . A trivial superstring is "atehalflethalalphaalfalfa" of length 25, which is simply the concatenation of all substrings. A shortest common superstring is "lethalphalfalfate", of length 17, saving 8 characters over the previous one (a compression of 8). Looking at what GREEDY would make of this example, we see that it would start out with the largest overlaps from "lethal" to "half" to "alfalfa" producing "lethalfalfa". It then has 3 choices of single character overlap, two of which lead to another shortest superstring "lethalfalfalphate", and one of which is lethal in the sense of giving a superstring that is one character longer. In fact, it is easy to give an example where GREEDY outputs a string almost twice as long as the optimal one, for instance on input  $\{c(ab)^k, (ba)^k, (ab)^kc\}$ .

For two strings s and t, not necessarily distinct, let v be the longest string

such that s = uv and t = vw for some non-empty strings u and w. We call |v| the (amount of) overlap between s and t, and denote it as ov(s,t). Furthermore, u is called the prefix of s with respect to t, and is denoted pref(s,t). Finally, we call |pref(s,t)| = |u| the distance from s to t, and denote it as d(s,t). So, the string uvw = pref(s,t)t, of length d(s,t)+|t| = |s|+|t|-ov(s,t) is the shortest superstring of s and t in which s appears (strictly) before t, and is also called the merge of s and t. For  $s_i, s_j \in S$ , we will abbreviate  $pref(s_i, s_j)$  to simply pref(i,j), and  $d(s_i, s_j)$  and  $ov(s_i, s_j)$  to d(i,j) and ov(i,j) respectively. The overlap between a string and itself is called a self-overlap. As an example of self-overlap, we have for the string s = undergrounder an overlap of ov(s,s) = 5 Also, pref(s,s) = undergrounder and <math>d(s,s) = 8. The string s = alfalfa, for which ov(s,s) = 4, shows that the overlap is not limited to half the total string length.

Given a list of strings  $s_{i_1}, s_{i_2}, \ldots, s_{i_r}$ , we define the superstring  $s = \langle s_{i_1}, \ldots, s_{i_r} \rangle$  to be the string  $pref(i_1, i_2)pref(i_2, i_3) \cdots pref(i_{r-1}, i_r)s_{i_r}$ . That is, s is the shortest string such that  $s_{i_1}, s_{i_2}, \ldots, s_{i_r}$  appear in order in that string. For a superstring of a substring-free set, this order is well-defined, since substrings cannot 'start' or 'end' at the same position, and if substring  $s_j$  starts before  $s_k$ , then  $s_j$  must also end before  $s_k$ . Define  $first(s) = s_{i_1}$  and  $last(s) = s_{i_r}$ . In each iteration of GREEDY the following invariant holds:

CLAIM **2.1** For two distinct strings s and t in GREEDY's set of strings, neither first(s) nor last(s) is a substring of t.

PROOF. Initially, first(s) = last(s) = s for all strings, so the claim follows from the fact that S is substring-free. Suppose that the invariant is invalidated by a merge of two strings  $t_1$  and  $t_2$  into a string  $t = \langle t_1, t_2 \rangle$  that has, say, first(s) as a substring. Let t = u first(s) v. Since first(s) is not a substring of either  $t_1$  or  $t_2$ , it must properly 'contain' the piece of overlap between  $t_1$  and  $t_2$ , i.e.,  $|first(s)| > ov(t_1, t_2)$  and  $|u| < d(t_1, t_2)$ . Hence,  $ov(t_1, s) > ov(t_1, t_2)$ ; a contradiction.

So when GREEDY (or its variation MGREEDY that we introduce later) chooses s and t as having the maximum overlap, then this overlap ov(s,t) in fact equals ov(last(s), first(t)), and as a result, the merge of s and t is  $\langle first(s), \ldots, last(s), first(t), \ldots, last(t) \rangle$ . We can therefore say that GREEDY orders the substrings, by finding the shortest superstring in which the substrings appear in that order.

We can rephrase the above in terms of permutations. For a permutation  $\pi$  on the set  $\{1,\ldots,m\}$ , let  $S_{\pi}=\langle s_{\pi(1)},\ldots,s_{\pi(m)}\rangle$ . In a shortest superstring for S, the substrings appear in some total order, say  $s_{\pi(1)},\ldots,s_{\pi(m)}$ , hence it must equal  $S_{\pi}$ .

We will consider a traveling salesman problem on a weighted directed complete graph  $G_S$  derived from S and show that one can achieve a factor of 4 approximation for TSP on that graph, yielding a factor of 4 approximation for the shortest-common-superstring problem. Graph  $G_S = (V, E, d)$  has m vertices  $V = \{1, \ldots, m\}$ , and  $m^2$  edges  $E = \{(i, j) : 1 \le i, j \le m\}$ . Here we take as weight function the distance d(,): edge (i, j) has weight  $d(i, j) = d(s_i, s_j)$ , to obtain the distance graph. This graph is similar to one considered by Turner in the end of his paper [16]. Later we will take the overlap ov(,) as the weight function to obtain the overlap graph. We will call  $s_i$  the string associated with

vertex i, and let  $pref(i, j) = pref(s_i, s_j)$  be the string associated with edge (i, j).

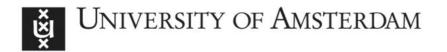

As examples we draw in Figure 2.1 the overlap graph and the distance graph for our previous example  $S_0 = \{$  ate, half, lethal, alpha, alfalfa  $\}$ . All edges not shown have overlap 0. Note that the sum of the distance and overlap weights on an edge (i, j) is the length of the string  $s_i$ .

Notice now that  $TSP(G_S) \leq OPT(S) - ov(last(s), first(s)) \leq OPT(S)$ , where  $TSP(G_S)$  is the cost of the minimum weight Hamiltonian cycle on  $G_S$ . The reason is that turning any superstring into a Hamiltonian cycle by overlapping its last and first substring saves on cost by charging last(s) for only d(last(s), first(s)) instead of its full length.

We now define some notation for dealing with directed cycles in  $G_S$ . Call two strings s, t equivalent,  $s \equiv t$ , if they are cyclic shifts of each other, i.e., if there are strings u, v such that s = uv and t = vu. If c is a directed cycle in  $G_S$  with vertices  $i_0, \ldots, i_{r-1}$  in order around c, we define strings(c) to be the equivalence class  $[pref(i_0, i_1)pref(i_1, i_2)\cdots pref(i_{r-1}, i_0)]$  and  $strings(c, i_k)$  the rotation starting with  $pref(i_k, i_{k+1})$ , i.e., the string  $pref(i_k, i_{k+1})\cdots pref(i_{k-1}, i_k)$ , where subscript arithmetic is modulo r. Let us say that an equivalence class [s] has  $periodicity k \ (k > 0)$ , if s is invariant under a rotation by k characters (s = uv = vu, |u| = k). Obviously, [s] has periodicity |s|. A moment's reflection shows that the minimum periodicity of [s] must equal the number of distinct rotations of s. This is the size of the equivalence class and denoted by card([s]). Furthermore, it is easily proven that if [s] has periodicities a and b, then it has periodicity gcd(a, b) as well. (See, e.g., [4].) It follows that all periodicities are a multiple of the minimum one. In particular, we have that |s| is a multiple of card([s]).

In general, we will denote a cycle c with vertices  $i_1, \ldots, i_r$  in the order by " $i_1 \to \cdots \to i_r \to i_1$ ." Also, let w(c), the weight of cycle c, equal  $|s|, s \in strings(c)$ . For convenience, we will say that  $s_j$  is in c, or " $s_j \in c$ " if j is a vertex of the cycle c.

Now, a few preliminary facts about cycles in  $G_S$ . Let  $c = i_0 \to \cdots \to i_{r-1} \to i_0$  and c' be cycles in  $G_S$ . For any string s,  $s^k$  denotes the string consisting of k copies of s concatenated together.

CLAIM **2.2** Each string  $s_{i_j}$  in c is a substring of  $s^k$  for all  $s \in strings(c)$  and sufficiently large k.

PROOF. By induction,  $s_{ij}$  is a prefix of  $pref(i_j, i_{j+1}) \cdots pref(i_{j+l-1}, i_{j+l}) s_{i_{j+l}}$  for any  $l \geq 0$  (addition modulo r). Taking  $k = \lceil |s_{ij}|/w(c) \rceil$  and l = kr we get that  $s_{ij}$  is a prefix of  $pref(i_j, i_{j+1}) \cdots pref(i_{j+kr-1}, i_{j+kr}) = strings(c, i_j)^k$ , which itself is a substring of  $s^{k+1}$  for any  $s \in strings(c)$ .

CLAIM 2.3 If each of  $\{s_{j_1}, \ldots, s_{j_r}\}$  is a substring of  $s^k$  for some string  $s \in strings(c)$  and sufficiently large k, then there exists a cycle of weight |s| = w(c) containing all these strings.

PROOF. In a (infinite) repetition of s, every string  $s_i$  appears as a substring at every other |s| characters. This naturally defines a circular ordering of the strings  $\{s_{j_1}, \ldots, s_{j_r}\}$  and the strings in c whose successive distances sum to |s|.  $\square$

CLAIM **2.4** The superstring  $\langle s_{i_0}, \dots, s_{i_{r-1}} \rangle$  is a substring of  $strings(c, i_0)s_{i_0}$ .

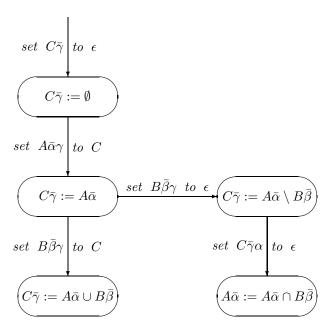

FIGURE 2.1. The overlap and distance graphs.

FIGURE 2.2. Strings and overlaps

PROOF. String  $\langle s_{i_0}, \ldots, s_{i_{r-1}} \rangle$  is clearly a substring of  $\langle s_{i_0}, \ldots, s_{i_{r-1}}, s_{i_0} \rangle$ , which by definition equals  $pref(i_0, i_1) \cdots pref(i_{r-1}, i_0)s_{i_0} = strings(c, i_0)s_{i_0}$ .

CLAIM **2.5** If strings(c') = strings(c), then there exists a third cycle  $\tilde{c}$  with weight w(c) containing all vertices in c and all those in c'. PROOF. Follows from claims 2.2 and 2.3.

CLAIM **2.6** There exists a cycle  $\tilde{c}$  of weight card(strings(c)) containing all vertices in c.

PROOF. Let u be the prefix of length card(strings(c)) of some string  $s \in strings(c)$ . By our periodicity arguments, |u| divides |s| = w(c), and  $s = u^j$  where j = w(c)/|u|. It follows that every string in strings(c) = [s] is a substring of  $u^{j+1}$ . Now use Claim 2.3 for u.

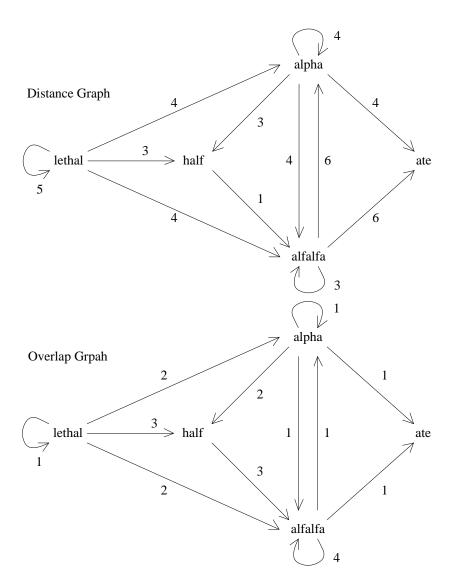

The following lemma has been proved in [15, 16]. Figure 2.2 gives a graphical interpretation of it. In the figure, the vertical bars surround pieces of string that match, showing a possible overlap between  $v^-$  and  $u^+$ , giving an upper bound on  $d(v^-, u^+)$ .

LEMMA **2.7** Let  $u, u^+, v^-, v$  be strings, not necessarily different, such that  $ov(u, v) \ge \max\{ov(u, u^+), ov(v^-, v)\}$ . Then,  $ov(u, v) + ov(v^-, u^+) \ge ov(u, u^+) + ov(v^-, v)$ , and  $d(u, v) + d(v^-, u^+) \le d(u, u^+) + d(v^-, v)$ .

That is, given the choice of merging u to  $u^+$  and  $v^-$  to v or instead merging u to v and  $v^-$  to  $u^+$ , the best choice is that which contains the pair of largest overlap. The conditions in the above Lemma are also known as "Monge conditions" in the context of transportation problems [1, 3, 7]. In this sense the Lemma follows from the observation that optimal shipping routes do not intersect. In the string context, we are transporting 'items' from the ends of substrings to the fronts of substrings.

# 2.3 A $4 \cdot \text{OPT}(S)$ bound for a modified greedy algorithm

Let S be a set of strings and  $G_S$  the associated graph. Now, although finding a minimum weight Hamiltonian cycle in a weighted directed graph is in general a hard problem, there is a polynomial-time algorithm for a similar problem known as the assignment problem [10]. Here, the goal is simply to find a decomposition of the graph into cycles such that each vertex is in exactly one cycle and the

total weight of the cycles is minimized. Let  $CYC(G_S)$  be the weight of the minimum assignment on graph  $G_S$ , so  $CYC(G_S) \leq TSP(G_S) \leq OPT(S)$ .

The proof that a modified greedy algorithm MGREEDY finds a superstring of length at most  $4 \cdot \text{OPT}(S)$  proceeds in two stages. We first show that an algorithm that finds an optimal assignment on  $G_S$ , then opens each cycle into a single string, and finally concatenates all such strings together has a performance ratio of at most 4. We then show (Theorem 2.10) that in fact, for these particular graphs, a greedy strategy can be used to find optimal assignments. This result can also be found (in a somewhat different form) as Theorem 1 in Hoffman's 1963 paper [7].

Consider the following algorithm for finding a superstring of the strings in S.

#### **Algorithm Concat-Cycles**

- 1. On input S, create graph  $G_S$  and find a minimum weight assignment C on  $G_S$ . Let C be the collection of cycles  $\{c_1, \ldots, c_p\}$ .

- 2. For each cycle  $c_i = i_1 \to \cdots \to i_r \to i_1$ , let  $\tilde{s}_i = \langle s_{i_1}, \ldots, s_{i_r} \rangle$  be the string obtained by opening  $c_i$ , where  $i_1$  is arbitrarily chosen. The string  $\tilde{s}_i$  has length at most  $w(c_i) + |s_{i_1}|$  by Claim 2.4.

- 3. Concatenate together the strings  $\tilde{s}_i$  and produce the resulting string  $\tilde{s}$  as output.

Theorem **2.8** Algorithm Concat-Cycles produces a string of length at most  $4 \cdot OPT(S)$ .

Before proving Theorem 2.8, we first need a preliminary lemma giving an upper bound on the amount of overlap possible between strings in different cycles of C. The lemma is also implied by the results in [4].

LEMMA 2.9 Let c and c' be two cycles in a minimum weight assignment C with  $s \in c$  and  $s' \in c'$ . Then, the overlap between s and s' is less than w(c) + w(c').

PROOF. Let x = strings(c) and x' = strings(c'). Since C is a minimum weight assignment, we know  $x \neq x'$ . Otherwise, by Claim 2.5, we could find a lighter assignment by combining the cycles c and c'. In addition, by Claim 2.6,  $w(c) \leq card(x)$ .

Suppose that s and s' overlap in a string u with  $|u| \geq w(c) + w(c')$ . Denote the substring of u starting at the i-th symbol and ending at the j-th as  $u_{i,j}$ . Since by Claim 2.2, s is a substring of  $t^k$  for some  $t \in x$  and large enough k and s' is a substring of  $t'^{k'}$  for some  $t' \in x'$  and large enough k', we have that  $x = [u_{1,w(c)}]$  and  $x' = [u_{1,w(c')}]$ . From  $x \neq x'$  we conclude that  $w(c) \neq w(c')$ ; assume without loss of generality that w(c) > w(c'). Then

$$u_{1,w(c)} = u_{1+w(c'),w(c)+w(c')} =$$

$$u_{1+w(c'),w(c)}u_{w(c)+1,w(c)+w(c')} = u_{1+w(c'),w(c)}u_{1,w(c')}$$

This shows that x has periodicity  $w(c') < w(c) \le card(x)$ , which contradicts the fact that card(x) is the minimum periodicity.

PROOF. (of Theorem 2.8.) Since  $C = \{c_1, \ldots, c_p\}$  is an optimal assignment,  $\operatorname{CYC}(G_S) = \sum_{i=1}^p w(c_i) \leq \operatorname{OPT}(S)$ . A second lower bound on  $\operatorname{OPT}(S)$  can be determined as follows: For each cycle  $c_i$ , let  $w_i = w(c_i)$  and  $l_i$  denote the length of the longest string in  $c_i$ . By Lemma 2.9, if we consider the longest string in each cycle and merge them together optimally, the total amount of overlap will be at most  $2\sum_{i=1}^p w_i$ . So the resulting string will have length at least  $\sum_{i=1}^p l_i - 2w_i$ . Thus  $\operatorname{OPT}(S) \geq \max(\sum_{i=1}^p w_i, \sum_{i=1}^p l_i - 2w_i)$ .

least  $\sum_{i=1}^{p} l_i - 2w_i$ . Thus  $\widetilde{\mathrm{OPT}}(S) \geq \max(\sum_{i=1}^{p} w_i, \sum_{i=1}^{p} l_i - 2w_i)$ . The output string  $\tilde{s}$  of algorithm Concat-Cycles has length at most  $\sum_{i=1}^{p} l_i + w_i$  (Claim 2.4). So,

$$|\tilde{s}| \leq \sum_{i=1}^{p} l_i + w_i$$

$$= \sum_{i=1}^{p} l_i - 2w_i + \sum_{i=1}^{p} 3w_i$$

$$\leq \text{OPT}(S) + 3 \cdot \text{OPT}(S)$$

$$= 4 \cdot \text{OPT}(S).$$

We are now ready to present the algorithm MGREEDY, and show that it in fact mimics algorithm Concat-Cycles.

### Algorithm MGREEDY

- 1. Let S be the input set of strings and T be empty.

- 2. While S is non-empty, do the following: Choose  $s, t \in S$  (not necessarily distinct) such that ov(s,t) is maximized, breaking ties arbitrarily. If  $s \neq t$ , then remove s and t from S and replace them with the merged string  $\langle s, t \rangle$ . If s = t, then just remove s from S and add it to T.

- 3. When S is empty, output the concatenation of the strings in T.

We can look at MGREEDY as choosing edges in the overlap graph  $(V = S, E = V \times V, ov(,))$ . When MGREEDY chooses strings s and t as having the maximum overlap (where t may equal s), it chooses the directed edge from last(s) to first(t) (see Claim 2.1). Thus, MGREEDY constructs/joins paths, and closes them into cycles, to end up with a collection of disjoint cycles  $M \subset E$  that cover the vertices of  $G_S$ . We will call M the assignment created by MGREEDY. Now think of MGREEDY as taking a list of all the edges sorted in the decreasing order of their overlaps (resolving ties in some definite way), and going down the list deciding for each edge whether to include it or not. Let us say that an edge e dominates another edge f if e precedes f in this list and shares its head (or tail) with the head (or tail, respectively) of f. By the definition of MGREEDY, it includes an edge f if and only if it has not yet included an edge dominating f.

Theorem 2.10 The assignment created by algorithm MGREEDY is an optimal assignment.

PROOF. Note that the overlap weight of an assignment and its distance weight add up to the total length of all strings. Accordingly, an assignment is optimal

(i.e., has minimum total weight in the distance graph) if and only if it has maximum total overlap. Among the maximum overlap assignments, let N be one that has the maximum number of edges in common with M. We shall show that M=N.

Suppose this is not the case, and let e be the edge of maximum overlap in the symmetric difference of M and N, with ties broken the same way as by MGREEDY. Suppose first that this edge is in  $N\setminus M$ . Since MGREEDY did not include e, it must have included another adjacent edge f that dominates e. Edge f cannot be in N (since N is an assignment), therefore f is in  $M\setminus N$ , contradicting our choice of the edge e. Suppose that  $e=k\to j$  is in  $M\setminus N$ . The two N edges  $i\to j$  and  $k\to l$  that share head and tail with e are not in M, and thus are dominated by e. Since  $ov(k,j)\geq \max\{ov(i,j),ov(k,l)\}$ , by Lemma 2.7,  $ov(i,j)+ov(k,l)\leq ov(k,j)+ov(i,l)$ . Thus replacing in N these two edges with  $e=k\to j$  and  $i\to l$  would yield an assignment N' that has more edges in common with M and has no less overlap than N. This would contradict our choice of N.

Since algorithm MGREEDY finds an optimal assignment, the string it produces is no longer than the string produced by algorithm Concat-Cycles. (In fact, it could be shorter since it breaks each cycle in the optimum position.)

## 2.4 Improving to $3 \cdot OPT(S)$

Recall that in the last step of algorithm MGREEDY, we simply concatenate all the strings in set T without any compression. Intuitively, if we instead try to overlap the strings in T, we might be able to achieve a bound better than  $4 \cdot \mathrm{OPT}(S)$ . Let TGREEDY denote the algorithm that operates in the same way as MGREEDY except that in the last step, it merges the strings in T by running GREEDY on them. We can show that TGREEDY indeed achieves a better bound: it produces a superstring of length at most  $3 \cdot \mathrm{OPT}(S)$ .

THEOREM **2.11** Algorithm TGREEDY produces a superstring of length at most  $3 \cdot OPT(S)$ .

PROOF. Let  $S = \{s_1, ..., s_m\}$  be a set of strings and s be the superstring obtained by TGREEDY on S. Let n = OPT(S) be the length of a shortest superstring of S. We show that  $|s| \leq 3n$ .

Let T be the set of all "self-overlapping" strings obtained by MGREEDY on S and C be the assignment created by MGREEDY. For each  $x \in T$ , let  $c_x$  denote the cycle in C corresponding to string x, and let  $w_x = w(c_x)$  be its weight. For any set R of strings, define  $||R|| = \sum_{x \in R} |x|$  to be the total length of the strings in set R. Also let  $w = \sum_{x \in T} w_x$ . Since  $\mathrm{CYC}(G_S) \leq \mathrm{TSP}(G_S) \leq \mathrm{OPT}(S)$ , we have  $w \leq n$ .

By Lemma 2.9, the compression achieved in a shortest superstring of T is less than 2w, i.e.,  $||T|| - n_T \le 2w$ . By the results in [15, 16], we know that the compression achieved by GREEDY on set T is at least half the compression achieved in any superstring of T. That is,

$$||T|| - |s| \ge (||T|| - n_T)/2 = ||T|| - n_T - (||T|| - n_T)/2 \ge ||T|| - n_T - w.$$

So,  $|s| \le n_T + w.$

For each  $x \in T$ , let  $s_{i_x}$  be the string in cycle  $c_x$  that is a prefix of x. Let  $S' = \{s_{i_x} | x \in T\}$ , n' = OPT(S'),  $S'' = \{strings(c_x, i_x)s_{i_x} | x \in T\}$ , and n'' = OPT(S'').

By Claim 2.4, a superstring for S'' is also a superstring for T, so  $n_T \leq n''$ , where  $n_T = \text{OPT}(T)$ . For any permutation  $\pi$  on T, we have  $|S''_{\pi}| \leq |S'_{\pi}| + \sum_{x \in T} w_x$ , so  $n'' \leq n' + w$ , where  $S'_{\pi}$  and  $S''_{\pi}$  are the superstrings obtained by overlapping the members of S' and S'', respectively, in the order given by  $\pi$ . Observe that  $S' \subseteq S$  implies  $n' \leq n$ . Summing up, we get

$$n_T < n'' < n' + w < n + w.$$

Combined with  $|s| \le n_T + w$ , this gives  $|s| \le n + 2w \le 3n$ .

## 2.5 GREEDY achieves linear approximation

One would expect that an analysis similar to that of MGREEDY would also work for the original GREEDY. This turns out not to be the case. The analysis of GREEDY is severely complicated by the fact that it continues processing the "self-overlapping" strings. MGREEDY was especially designed to avoid these complications, by separating such strings. Let GREEDY(S) denote the length of the superstring produced by GREEDY on a set S. It is tempting to claim that

$$GREEDY(S \cup \{s\}) \le GREEDY(S) + |s|.$$

If this were true, a simple argument would extend the  $4\cdot \mathrm{OPT}(S)$  result for MGREEDY to GREEDY. But the following counterexample disproves this seemingly innocent claim. Let

$$S = \{ca^m, a^{m+1}c^m, c^mb^{m+1}, b^mc\}, s = b^{m+1}a^{m+1}.$$

Now  $GREEDY(S) = |ca^{m+1}c^mb^{m+1}c| = 3m+4$ , whereas  $GREEDY(S \cup \{s\}) = |b^mc^mb^{m+1}a^{m+1}c^ma^m| = 6m+2 > (3m+4) + (2m+2)$ .

With a more complicated analysis we will nevertheless show that

THEOREM **2.12** GREEDY produces a string of length at most  $4 \cdot OPT(S)$ .

Before proving the theorem formally, we give a sketch of the basic idea behind the proof. If we want to relate the merges done by GREEDY to an optimal assignment, we have to keep track of what happens when GREEDY violates the maximum overlap principle, i.e. when some self-overlap is better than the overlap in GREEDY's merge. One thing to try is to charge GREEDY some extra cost that reflects that an optimal assignment on the new set of strings (with GREEDY's merge) may be somewhat longer than the optimal assignment on the former set (in which the self-overlapping string would form a cycle). If we could just bound these extra costs then we would have a bound for GREEDY. Unfortunately, this approach fails because the self-overlapping string may be merged by GREEDY into a larger string which itself becomes self-overlapping, and this nesting could go arbitrarily deep. Our proof concentrates on the innermost self-overlapping strings only. These so called culprits form a linear order in the final superstring. We avoid the complications of higher level self-overlaps

by splitting the analysis in two parts. In one part, we ignore all the original substrings that connect first to the right of a culprit. In the other part, we ignore all the original substrings that connect first to the left of a culprit. In each case, it becomes possible to bound the extra cost. This method yields a bound of  $7 \cdot \mathrm{OPT}(S)$ . By combining the two analyses in a more clever way, we can even eliminate the effect of the extra costs and obtain the same  $4 \cdot \mathrm{OPT}(S)$  bound as we found for MGREEDY. A detailed formal proof follows.

We will need some notions and lemmas. Think of both GREEDY and MGREEDY as taking a list of all edges sorted by overlap, and going down the list deciding for each edge whether to include it or not. Call an edge better (worse) if it appears before (after) another in this list. Better edges have at least the overlap of worse ones. Recall that an edge dominates another iff it is better and shares its head or tail with the other one.

At the end, GREEDY has formed a Hamiltonian path

$$s_1 \to s_2 \to \cdots \to s_m$$

of 'greedy' edges. (w.l.o.g., the strings are renumbered to reflect their order in the superstring produced by GREEDY.) For convenience we will usually abbreviate  $s_i$  to i. GREEDY does not include an edge f iff

- 1. f is dominated by an already chosen edge e, or

- 2. f is not dominated but it would form a cycle.

Let us call the latter "bad back edges"; a bad back edge  $f = j \to i$  necessarily has  $i \leq j$ . Each bad back edge  $f = j \to i$  corresponds to a string  $\langle s_i, s_{i+1}, \ldots, s_j \rangle$  that, at some point in the execution of GREEDY, has more (self) overlap than the pair that is merged. When GREEDY considers f, it has already chosen all (better) edges on the greedy path from i to j, but not yet the (worse) edges  $i-1 \to i$  and  $j \to j+1$ . The bad back edge f is said to span the closed interval  $I_f = [i,j]$ . The above observations provide a proof of the following lemma.

LEMMA 2.13 Let e and f be two bad back edges. The closed intervals  $I_e$  and  $I_f$  are either disjoint, or one contains the other. If  $I_e \supset I_f$  then e is worse than f (thus,  $ov(e) \leq ov(f)$ ).

Thus, the intervals of the bad back edges are nested and bad back edges do not cross each other. Culprits are the minimal (innermost) such intervals. Each culprit [i,j] corresponds to a culprit string  $\langle s_i, s_{i+1}, \ldots, s_j \rangle$ . Note that, because of the minimality of the culprits, if  $f = j \to i$  is the back edge of a culprit [i,j], and e is another bad back edge that shares head or tail with f, then  $I_e \supset I_f$ , and therefore f dominates e.

Call the worst edge between every two successive culprits on the greedy path a weak link. Note that weak links are also worse than all edges in the two adjacent culprits as well as their back edges. If we remove all the weak links, the greedy path is partitioned into a set of paths, called blocks. Every block consists of a nonempty culprit as the middle segment, and (possibly empty) left and right extensions. The set of strings (nodes) S is thus partitioned into three sets  $S_l, S_m, S_r$  of left, middle, and right strings. The example in Figure 2.3 has 7 substrings, of which 2 by itself and the merge of 4, 5, and 6

FIGURE 2.3. Culprits and weak links in Greedy merge path.

form the culprits (indicated by thicker lines). Bad back edges are  $2 \to 2$ ,  $6 \to 4$ , and  $6 \to 1$ . The weak link  $3 \to 4$  is the worst edge between culprits [2] and [4,5,6]. The blocks in this example are thus [1,2,3] and [4,5,6,7], and we have  $S_l = \{1\}, S_m = \{2,4,5,6\}, S_r = \{3,7\}.$

The following lemma shows that a bad back edge must be from a middle or right node to a middle or left node.

LEMMA **2.14** Let  $f = j \rightarrow i$  be a bad back edge. Node i is either a left node or the first node of a culprit. Node j is either a right node or the last node of a culprit.

PROOF. Let c = [k, l] be the leftmost culprit in  $I_f$ . Now either i = k is the first node of c, or i < k is in the left extension of c, or i < k is in the right extension of the culprit c' to the left of c. In the latter case however,  $I_f$  includes the weak link, which by definition is worse than all edges between the culprits c' and c, including the edge  $i - 1 \rightarrow i$ . This contradicts the observation preceding Lemma 2.13. A similar argument holds for  $s_j$ .

Let  $C_m$  be the assignment on the set  $S_m$  of middle strings (nodes) that has one cycle for each culprit, consisting of the greedy edges together with the back edge of the culprit. If we consider the application of the algorithm MGREEDY on the subset of strings  $S_m$ , it is easy to see that the algorithm will actually construct the assignment  $C_m$ . Theorem 2.10 then implies the following lemma.

Lemma 2.15  $C_m$  is an optimal assignment on the set  $S_m$  of middle strings.

Let the graph  $G_l = (V_l, E_l)$  consist of the left/middle part of all blocks in the greedy path, i.e.  $V_l = S_l \cup S_m$  and  $E_l$  is the set of non-weak greedy edges between nodes of  $V_l$ . Let  $M_l$  be a maximum overlap assignment on  $V_l$ , as created by MGREEDY on the ordered sublist of edges in  $V_l \times V_l$ . Let  $V_r = S_m \cup S_r$ , and define similarly the graph  $G_r = (V_r, E_r)$  and the optimal assignment  $M_r$  on the right/middle strings. Let  $l_c$  be the sum of the lengths of all culprit strings. Define  $l_l = \sum_{i \in S_l} d(s_i, s_{i+1})$  as the total length of all left extensions and  $l_r = \sum_{i \in S_r} d(s_i^R, s_{i-1}^R)$  as the total length of all right extensions. (Here  $x^R$  denotes the reversal of string x.) The length of the string produced by GREEDY is  $l_l + l_c + l_r - o_w$ , where  $o_w$  is the summed block overlap (i.e. the sum of the overlaps of the weak links).

Denoting the overlap  $\sum_{e \in E} ov(e)$  of a set of edges E as ov(E), define the cost of a set of edges E on a set of strings (nodes) V as

$$cost(E) = ||V|| - ov(E).$$

Note that the distance plus overlap of a string s to another equals |s|. Because an assignment (e.g.  $M_l$  or  $M_r$ ) has an edge from each node, its cost equals its distance weight. Since  $V_l$  and  $V_r$  are subsets of S and  $M_l$  and  $M_r$  are optimal

FIGURE 2.4. Left/middle and middle/right parts with weak links.

assignments, we have  $cost(M_l) \le n$  and  $cost(M_r) \le n$ . For  $E_l$  and  $E_r$  we have that  $cost(E_l) = l_l + l_c$  and  $cost(E_r) = l_r + l_c$ .

We have established the following (in)equalities:

$$\begin{split} l_l + l_c + l_r &= (l_l + l_c) + (l_c + l_r) - l_c \\ &= cost(E_l) + cost(E_r) - l_c \\ &= ||V_l|| - ov(E_l) + ||V_r|| - ov(E_r) - l_c \\ &= cost(M_l) + ov(M_l) - ov(E_l) + \\ &cost(M_r) + ov(M_r) - ov(E_r) - l_c \\ &\leq 2n + ov(M_l) - ov(E_l) + ov(M_r) - ov(E_r) - l_c. \end{split}$$

We proceed by bounding the overlap differences in the above equation. Our basic idea is to charge the overlap of each edge of M to an edge of E or a weak link or the back edge of a culprit in a way such that every edge of E and every weak link is charged at most once and the back edge of each culprit is charged at most twice. This is achieved through combining the left/middle and middle/right parts carefully as shown below. For convenience, we will refer to the union operation for multisets (i.e., allowing duplicates) as the disjoint union.

Let V be the disjoint union of  $V_l$  and  $V_r$ , let E be the disjoint union of  $E_l$  and  $E_r$ , and let G = (V, E) be the disjoint union of  $G_l$  and  $G_r$ . Thus each string in  $S_l \cup S_r$  occurs once, while each string in  $S_m$  occurs twice in G. We modify E to take advantage of the block overlaps. Add each weak link to E as an edge from the last node in the corresponding middle/right path of  $G_r$  to the first node of the corresponding left/middle path of  $G_l$ . This procedure yields a new set of edges E'. Its overlap equals  $ov(E') = ov(E_l) + ov(E_r) + o_w$ . A picture of (V, E') for our previous example is given in Figure 2.4.

Let M be the disjoint union of  $M_l$  and  $M_r$ , an assignment on graph G. Its overlap equals  $ov(M) = ov(M_l) + ov(M_r)$ . Every edge of M connects two  $V_l$  nodes or two  $V_r$  nodes; thus, all edges of M satisfy the hypothesis of the following lemma.

LEMMA **2.16** Let N be any assignment on V. Let  $e = t \rightarrow h$  be an edge of  $N \setminus E'$  that is not in  $V_r \times V_l$ . Then e is dominated by either

- 1. an adjacent E' edge, or

- 2. a culprit's back edge with which it shares the head h and  $h \in V_r$ , or

- 3. a culprit's back edge with which it shares the tail t and  $t \in V_l$ .

PROOF. Suppose first that e corresponds to a bad back edge. By Lemma 2.14, h corresponds to a left node or to the first node of a culprit. In the latter case, e is dominated by the back edge of the culprit (see the comment after Lemma

2.13). Therefore, either h is the first node of a culprit in  $V_r$  (and case 2 holds), or else  $h \in V_l$ . Similarly, either t is the last node of a culprit in  $V_l$  (and case 3 holds) or else  $t \in V_r$ . Since e is not in  $V_r \times V_l$ , it follows then that case 2 or case 3 holds. (Note that if e is in fact the back edge of some culprit, then both cases 2 and 3 hold.)

Suppose that e does not correspond to a bad back edge. Then e must be dominated by some greedy edge since it was not chosen by GREEDY. If the greedy edge dominating e is in E' then we have case 1. If it is not in E', then either h is the first node of a culprit in  $V_t$ , and in both cases f is dominated by the back edge of the culprit. Thus, we have case 2 or 3.

While Lemma 2.16 ensures that each edge of M is bounded in overlap, it may be that some edges of E' are double charged. We will modify M without decreasing its overlap and without invalidating Lemma 2.16 into an assignment M' such that each edge of E' is dominated by one of its adjacent M' edges.

LEMMA 2.17 Let N be any assignment on V such that  $N \setminus E'$  does not contain any edges in  $V_r \times V_l$ . Then there is an assignment N' on V satisfying the following properties.

- 1.  $N' \setminus E'$  has also no edges in  $V_r \times V_l$ ,

- 2. ov(N') > ov(N),

- 3. each edge in  $E' \setminus N'$  is dominated by one of its two adjacent N' edges.

PROOF. Since N already has the first two properties, it suffices to argue that if N violates property 3, then we can construct another assignment N' that satisfies properties 1 and 2, and has more edges in common with E'.

Let  $e = k \to j$  be an edge in E' - N that dominates both adjacent N edges,  $f = i \to j$ , and  $g = k \to l$ . By Lemma 2.7, replacing edges f and g of N with e and  $i \to l$  produces an assignment N' with at least as large overlap. To see that the new edge  $i \to l$  of  $N' \setminus E'$  is not in  $V_r \times V_l$ , observe that if  $i \in V_r$  then  $j \in V_r$  because of the edge  $f = i \to j$  ( $N \setminus E'$  does not have edges in  $V_r \times V_l$ ), which implies that k is in  $V_r$  because of the E' edge  $e = k \to j$  (E' does not have edges in  $V_l \times V_r$ ), which implies that also  $l \in V_r$  because of the N edge  $g = k \to l$ .

PROOF. (of Theorem 2.12.) By Lemmas 2.16 and 2.17, we can construct from the assignment M another assignment M' with at least as large total overlap, and such that we can charge the overlap of each edge of M' to an edge of E' or to the back edge of a culprit. Every edge of E' is charged for at most one edge of M', while the back edge of each culprit is charged for at most two edges of M': for the M' edge entering the first culprit node in  $V_r$  and the edge coming out of the last culprit node in  $V_l$ . Therefore,  $ov(M) \leq ov(M') \leq ov(E') + 2o_c$ , where  $o_c$  is the summed overlap of all culprit back edges. Denote by  $w_c$  the summed weight of all culprit cycles, i.e., the weight of the (optimal) assignment  $C_m$  on  $S_m$  from Lemma 2.15. Then  $l_c = w_c + o_c$ . As in the proof of Theorem 2.8, we have  $o_c - 2w_c \leq n$  and  $w_c \leq n$ . (Note that the overlap of a culprit back edge is less than the length of the longest string in the culprit cycle.) Putting

everything together, the string produced by GREEDY has length

$$\begin{aligned} l_l + l_c + l_r - o_w & \leq & 2n + ov(M_l) - ov(E_l) + ov(M_r) - ov(E_r) - l_c - o_w \\ & \leq & 2n + ov(M') - ov(E') - l_c \\ & \leq & 2n + 2o_c - l_c \\ & = & 2n + o_c - w_c \\ & \leq & 3n + w_c \\ & \leq & 4n. \end{aligned}$$

### 2.6 Which algorithm is the best?

Having proved various bounds for the algorithms GREEDY, MGREEDY, and TGREEDY, one may wonder what this implies about their relative performance. First of all we note that MGREEDY can never do better than TGREEDY since the latter applies the GREEDY algorithm to an intermediate set of strings that the former merely concatenates.