# ASSEMBLY INSTRUCTION LEVEL REVERSE EXECUTION FOR DEBUGGING

A Thesis Presented to The Academic Faculty

by

Tankut Akgul

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

School of Electrical and Computer Engineering Georgia Institute of Technology April 2004

Copyright © 2004 by Tankut Akgul

## ASSEMBLY INSTRUCTION LEVEL REVERSE EXECUTION FOR DEBUGGING

Approved by:

Professor Vincent J. Mooney III, Committee Chair

Professor Richard J. LeBlanc, Jr.

Professor Vijay K. Madisetti

Professor Santosh Pande

Professor Raghupathy Sivakumar

Date Approved: 7 April 2004

To my mother Betul Akgul and  $my \; father \; Kamuran \; Akgul$

#### ACKNOWLEDGMENTS

I am grateful to everyone who made this Ph.D. thesis possible. First and foremost, I owe special thanks to my advisor, Professor Vincent J. Mooney III, for his patience and guidance from the very beginning until the end. Second, I am especially grateful to Professor Santosh Pande for his valuable suggestions and guidance. Third, I would like to thank my committee members Professor Richard J. LeBlanc, Professor Vijay K. Madisetti and Professor Raghupathy Sivakumar for their constructive criticism which helped me improve this dissertation. I would also like to thank everyone in the Hardware/Software Codesign Group at Georgia Tech for their important feedback. Especially, the good times I had with my close friends Mohamed Shalan and Pramote Kuacharoen helped me bear all these years spent earning a PhD. Finally, I give special thanks to my wife Bilge whose love and support enabled me to complete this work.

## TABLE OF CONTENTS

| DE            | DIC  | ATIO   | <b>V</b>                                                              | iii  |

|---------------|------|--------|-----------------------------------------------------------------------|------|

| AC            | KNO  | OWLE   | DGMENTS                                                               | iv   |

| LIS           | вт о | F TAE  | BLES                                                                  | viii |

| LIS           | вт О | F FIG  | URES                                                                  | ix   |

| $\mathbf{SU}$ | MM.  | ARY .  |                                                                       | xi   |

| Ι             | IN   | TROE   | OUCTION                                                               | 1    |

|               | 1.1  | Motiva | ation and Aims                                                        | 1    |

|               | 1.2  | Proble | em Statement                                                          | 4    |

|               | 1.3  | Thesis | Contributions                                                         | 5    |

|               | 1.4  | Thesis | Organization and Roadmap                                              | 6    |

| II            | PΕ   | REVIO  | US WORK                                                               | 7    |

|               | 2.1  | Previo | us Work in Reverse Execution                                          | 7    |

|               |      | 2.1.1  | Reverse Execution Techniques by Restore Earlier State                 | 8    |

|               |      | 2.1.2  | Previous Work in State Regeneration at the Source Code Level          | 11   |

|               |      | 2.1.3  | Previous Work in State Regeneration at the Assembly Instruction Level | 14   |

|               | 2.2  | Previo | us Work in Program Slicing                                            | 14   |

|               |      | 2.2.1  | Static Slicing                                                        | 14   |

|               |      | 2.2.2  | Dynamic Slicing                                                       | 16   |

|               | 2.3  | Summ   | ary                                                                   | 17   |

| III           | O    | VERVI  | EW OF REVERSE CODE GENERATION                                         | 19   |

|               | 3.1  | Prelim | inary Assumptions                                                     | 20   |

|               |      | 3.1.1  | Inputs of the RCG Algorithm                                           | 21   |

|               |      | 3.1.2  | Assumptions for RCG                                                   | 22   |

|               | 3.2  | Progra | am Partitioning                                                       | 26   |

|               | 3.3  | Revers | sing an Assembly Instruction                                          | 27   |

|              | 3.4                    | Comb          | oining the Reverse Instruction Groups           | 31 |

|--------------|------------------------|---------------|-------------------------------------------------|----|

|              | 3.5                    | Summ          | nary                                            | 33 |

| IV           | $\mathbf{I}\mathbf{N}$ | 1PLEN         | MENTATION OF THE RCG ALGORITHM                  | 34 |

|              | 4.1                    | RCG           | Step 1: Program Partitioning                    | 34 |

|              | 4.2                    | RCG           | Step 2: RIG Generation                          | 38 |

|              |                        | 4.2.1         | The Redefine Technique                          | 40 |

|              |                        | 4.2.2         | The Extract-from-use Technique                  | 4  |

|              |                        | 4.2.3         | The State Saving Technique                      | 43 |

|              |                        | 4.2.4         | An Example of RIG Generation                    | 4  |

|              | 4.3                    | RCG           | Step 3: Combining the RIGs                      | 4' |

|              |                        | 4.3.1         | Constructing the RBBs                           | 4' |

|              |                        | 4.3.2         | Constructing the RPPs                           | 49 |

|              |                        | 4.3.3         | Combining the RPPs                              | 5  |

|              | 4.4                    | Summ          | nary                                            | 6  |

| $\mathbf{V}$ | SF                     | PECIA         | L RCG DETAILS                                   | 6  |

|              | 5.1                    | Detail        | ls of RIG generation                            | 6  |

|              |                        | 5.1.1         | Value Renaming                                  | 6  |

|              |                        | 5.1.2         | The Modified Value Graph (MVG)                  | 7  |

|              |                        | 5.1.3         | Recovery of a Destroyed Definition Using an MVG | 7  |

|              | 5.2                    | Comp          | olexity of RIG Generation                       | 8  |

|              | 5.3                    | Summ          | nary                                            | 8  |

| VI           | SU                     | J <b>MM</b> A | ARY OF THE OVERALL RCG ALGORITHM                | 82 |

| VI           | I D                    | YNAN          | MIC SLICING SUPPORT                             | 8  |

|              | 7.1                    | Backg         | ground                                          | 8  |

|              | 7.2                    | Overv         | riew of Slicing Approach                        | 8  |

|              | 7.3                    | The E         | Extensions to the RCG Algorithm                 | 9  |

|              |                        | 7.3.1         | The Static Analysis Part                        | 9  |

|              |                        | 732           | Debugger Support                                | g  |

|                                                  | 7.4                                          | Gener                        | ating a Reduced Reverse Program Using a Global MVG | 92  |

|--------------------------------------------------|----------------------------------------------|------------------------------|----------------------------------------------------|-----|

|                                                  | 7.5                                          | Summ                         | nary                                               | 96  |

| VIII PERFORMANCE EVALUATION                      |                                              |                              |                                                    | 98  |

|                                                  | 8.1                                          | The Experimentation Platform |                                                    |     |

|                                                  | 8.2                                          | Benchmark Programs           |                                                    |     |

|                                                  | 8.3 Results for Full-scale Reverse Execution |                              | ss for Full-scale Reverse Execution                | 100 |

|                                                  |                                              | 8.3.1                        | Comparison of Reverse Code Sizes                   | 101 |

|                                                  |                                              | 8.3.2                        | Comparison of Runtime Memory Usage                 | 102 |

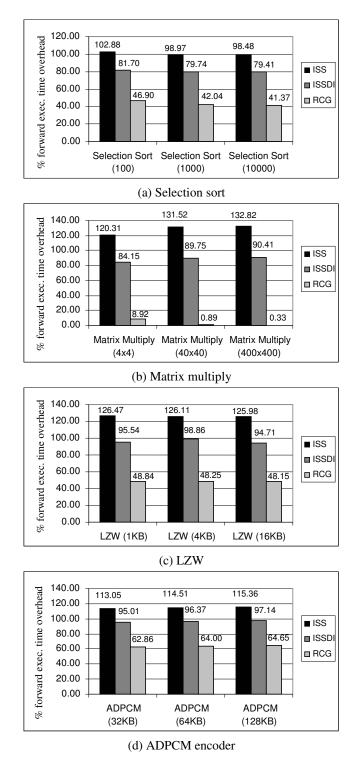

|                                                  |                                              | 8.3.3                        | Comparison of Execution Times                      | 103 |

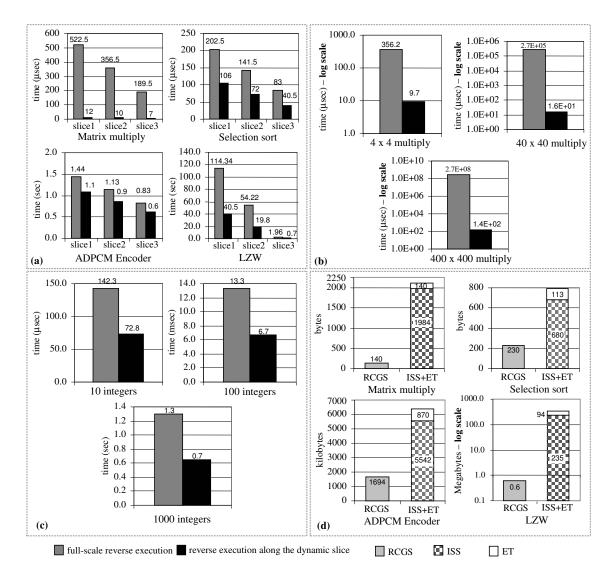

|                                                  | 8.4                                          | Result                       | es for Reverse Execution Along a Dynamic Slice     | 109 |

|                                                  |                                              | 8.4.1                        | Reverse Execution Time Measurement                 | 109 |

|                                                  |                                              | 8.4.2                        | Measurement of Runtime Memory Usage                | 112 |

| IX                                               | CO                                           | ONCL                         | USION                                              | 113 |

| APPENDIX A — HANDLING EFFECTS OF INDIRECTLY MOD- |                                              |                              |                                                    |     |

|                                                  | IFIED LOCATIONS                              |                              |                                                    | 116 |

| DE                                               | DEFEDENCES                                   |                              |                                                    | 191 |

## LIST OF TABLES

| Table 1 | Sizes of the original and the reverse codes                          | 102 |

|---------|----------------------------------------------------------------------|-----|

| Table 2 | Runtime memory requirements for state saving                         | 103 |

| Table 3 | Forward execution time measurements of the original programs         | 104 |

| Table 4 | Execution time measurements of the instrumented and reverse programs | 104 |

| Table 5 | Distribution of the instructions in $E$ and $E'$ for the MPC860      | 117 |

## LIST OF FIGURES

| Figure 1  | A typical debugging cycle                                                                                              | 1  |

|-----------|------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2  | A sample view of windows from our reverse debugger tool                                                                | 2  |

| Figure 3  | A high-level view of the RCG algorithm                                                                                 | 20 |

| Figure 4  | Inputs of the RCG algorithm                                                                                            | 21 |

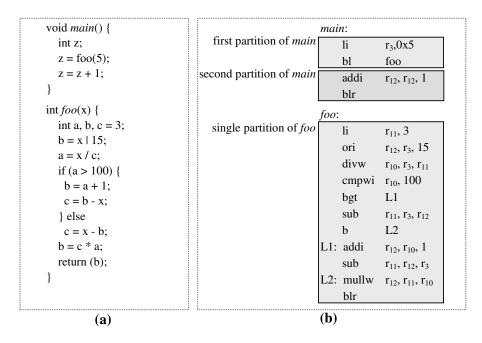

| Figure 5  | (a) An example program $T$ in C. (b) Assembly of $T$ showing the PPs.                                                  | 27 |

| Figure 6  | (a) Assembly of $T$ shown in Figure 5(a). (b) Reverse of $T$ , $RT$                                                    | 29 |

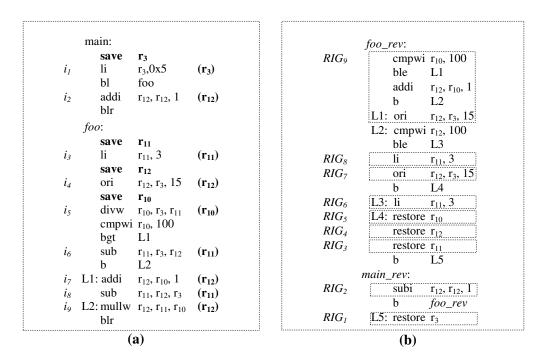

| Figure 7  | (a) PCFGs of $T$ . (b) PCFGs of $RT$                                                                                   | 32 |

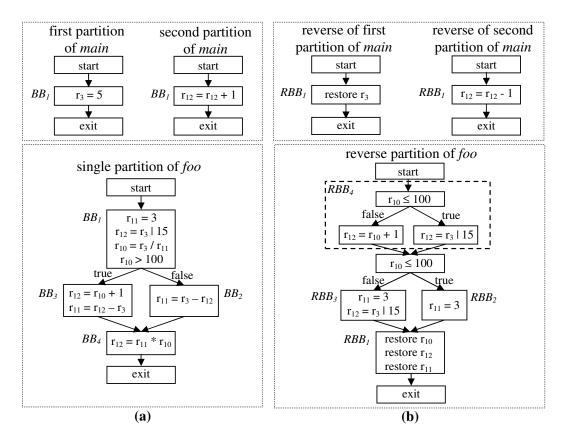

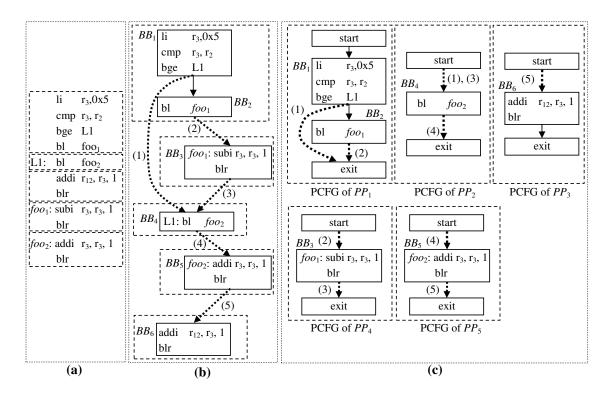

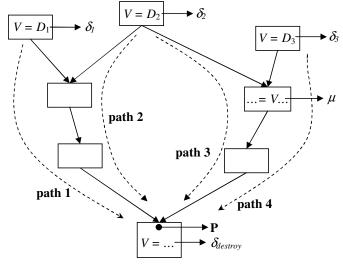

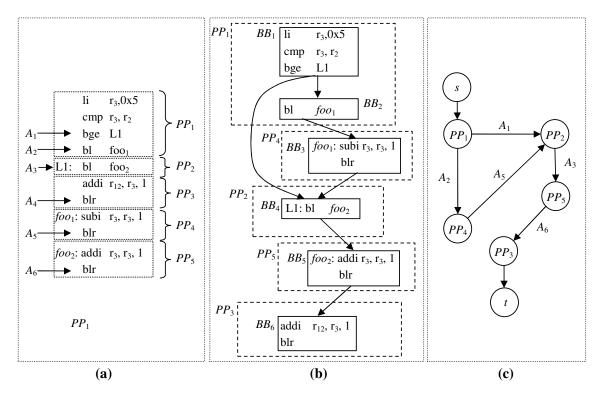

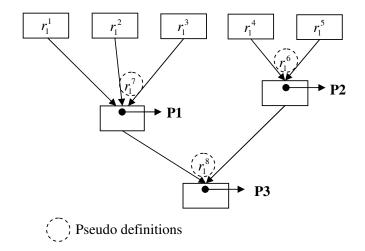

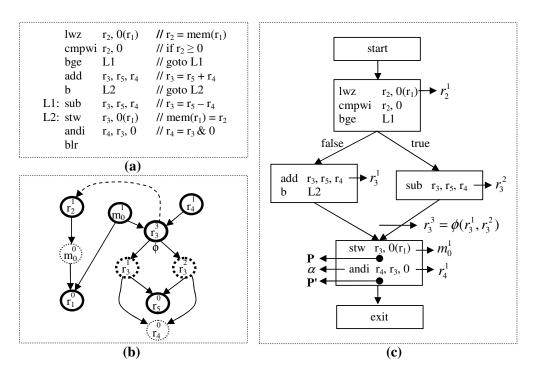

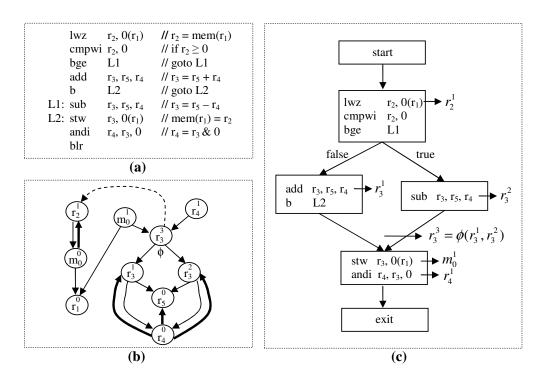

| Figure 8  | (a) A sample program portion $T$ . (b) Corresponding control flow graph. (c) Corresponding PCFGs                       | 37 |

| Figure 9  | Recovering a destroyed variable $V$                                                                                    | 39 |

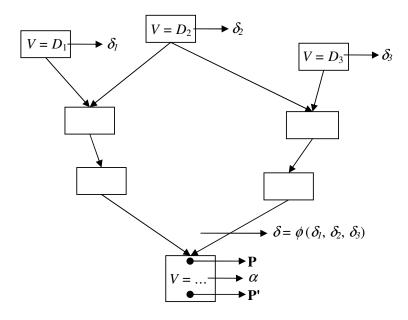

| Figure 10 | An example PCFG of a program partition $PP_x$                                                                          | 41 |

| Figure 11 | A diagram illustrating the state saving method of the RCG algorithm.                                                   | 43 |

| Figure 12 | PCFG from Figure 10                                                                                                    | 45 |

| Figure 13 | (a) PCFG of $PP_x$ from Figure 10. (b) RBBs of reverse program partition $RPP_x$                                       | 48 |

| Figure 14 | Combination of RBBs at a fork point                                                                                    | 49 |

| Figure 15 | Combination of RBBs at a confluence point                                                                              | 50 |

| Figure 16 | A diagram illustrating the combination of the RBBs                                                                     | 52 |

| Figure 17 | (a) The example program portion from Figure 8. (b) Corresponding control flow graph. (c) Corresponding call graph (CG) | 55 |

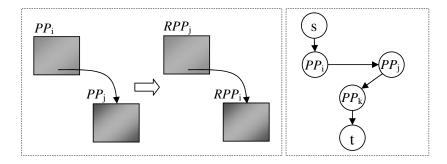

| Figure 18 | An abstract view of two PPs                                                                                            | 56 |

| Figure 19 | An example of combining the RPPs                                                                                       | 60 |

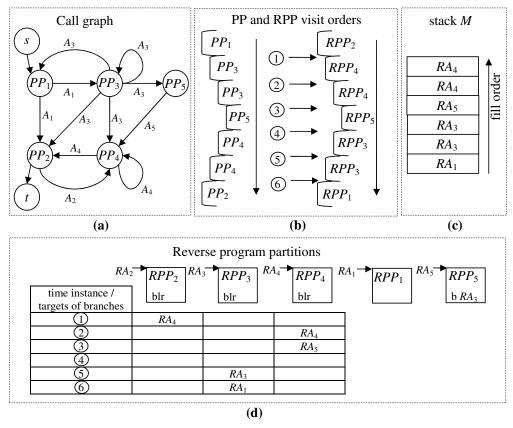

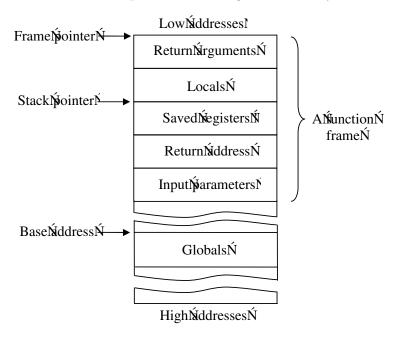

| Figure 20 | A typical memory organization made by a compiler                                                                       | 66 |

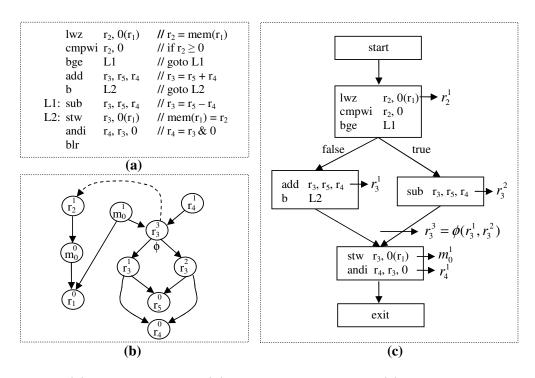

| Figure 21 | Value renaming at confluence points in a PCFG                                                                          | 70 |

| Figure 22 | (a) An example PP. (b) Corresponding MVG. (c) Corresponding PCFG                                                       | 72 |

| Figure 23 | An instruction modifying a variable $V$ at a point in a PP                                                             | 75 |

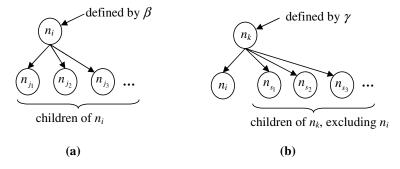

| Figure 24 | (a) Recovering a node from its children. (b) Recovering a node from one of its parents and corresponding siblings                                                                                                                                                 | 75  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 25 | (a) An example PP. (b) Corresponding MVG. (c) Corresponding PCFG                                                                                                                                                                                                  | 77  |

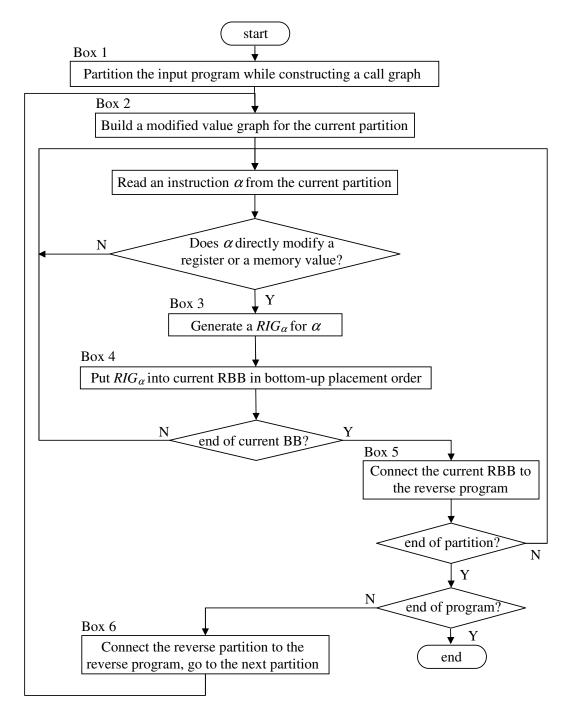

| Figure 26 | A high-level flowchart of the RCG algorithm                                                                                                                                                                                                                       | 83  |

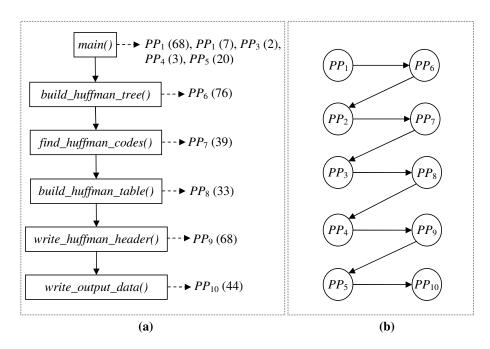

| Figure 27 | (a) Huffman encoder block diagram showing PPs for each function and MVG node count for each PP (b) Corresponding call graph                                                                                                                                       | 85  |

| Figure 28 | A code piece and a dynamic slice                                                                                                                                                                                                                                  | 89  |

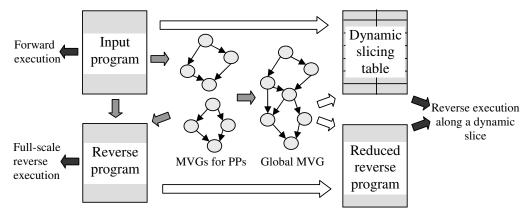

| Figure 29 | A diagram of the RCGS algorithm                                                                                                                                                                                                                                   | 90  |

| Figure 30 | (a) An example program. (b) Corresponding global MVG                                                                                                                                                                                                              | 93  |

| Figure 31 | (a) An example program. (b) Corresponding MVG. (c) The complete reverse program. (d) The reduced reverse program. (e) Table showing definition-recovering relationships                                                                                           | 96  |

| Figure 32 | The GUI of the debugger tool                                                                                                                                                                                                                                      | 99  |

| Figure 33 | Execution time overhead results of ISS, ISSDI and RCG                                                                                                                                                                                                             | 106 |

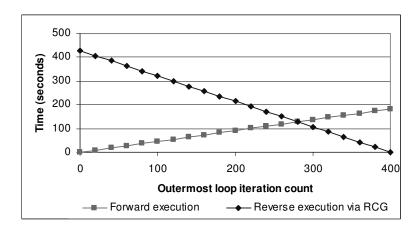

| Figure 34 | The elapsed forward/reverse execution times versus various program points in 400x400 matrix multiply                                                                                                                                                              | 108 |

| Figure 35 | (a) Reverse execution time comparison. (b) Reverse execution time comparison of matrix multiply with different matrix sizes. (c) Reverse execution time comparison of selection sort with different input array sizes. (d) Runtime memory requirement comparison. | 111 |

#### **SUMMARY**

Many of the bugs in programs show their effects much later in program execution. For this reason, even the most careful programmers equipped with the state-of-the-art debuggers might well miss the first occurrence of a bug and thus might have to restart the program being debugged. Furthermore, for difficult to find bugs, this process might have to be repeated multiple times. However, every time a restart occurs, parts of a program that already executed without errors have to be re-executed unnecessarily. These unnecessary re-executions constitute a significant portion of the debugging time.

Reverse execution can be defined as a method which recovers the states that a program attains during its execution. Therefore, reverse execution eliminates the need for repetitive program restarts every time a bug location is missed. This potentially shortens debug time considerably.

Conventional techniques for recovering a prior state rely on saving the state into a record before the state is destroyed. However, state saving causes significant memory and time overheads during execution of programs.

This thesis presents a new approach which, for the first time ever (to the best of the author's knowledge), achieves reverse execution at the assembly instruction level on general purpose processors via execution of a "reverse program." A reverse program almost always regenerates destroyed states rather than restoring them from a record and provides assembly instruction by assembly instruction execution in the backward direction. This significantly reduces state saving and thus decreases the associated memory and time costs of reverse execution support.

Furthermore, this thesis presents a new dynamic slicing algorithm that is built on top of assembly instruction level reverse execution. Dynamic slicing is a technique which isolates the code parts that influence an erroneous variable at a program point. By the help of dynamic slicing, programmers can concentrate on the parts of programs that are actually related to bugs.

Similar to reverse execution, conventional dynamic slicing methods also require runtime information in the form of program execution trajectories. An execution trajectory captures the control flow information of a program. The algorithm presented in this thesis achieves dynamic slicing via execution of a "reduced reverse program." A reduced reverse program is obtained from a full reverse program by omitting the instructions that recover states irrelevant to the dynamic slice under consideration. This provides a reverse execution capability along a designated dynamic slice only. The use of a reduced reverse program for dynamic slicing removes the need for runtime execution trajectories.

The methodology of this thesis has been implemented on a PowerPC processor with a custom made debugger. As compared to previous work, all of which heavily use state saving techniques, the experimental results show up to 2206X reduction in runtime memory usage, up to 403X reduction in forward execution time overhead and up to 2.32X reduction in forward execution time for the tested benchmarks. Measurements on the selected benchmarks also indicate that the dynamic slicing method presented in this thesis can achieve up to six orders of magnitude (1,928,500X) speedups in reverse execution.

#### CHAPTER I

#### INTRODUCTION

#### 1.1 Motivation and Aims

As human beings are quite prone to making mistakes, it is difficult for a programmer to write an error-free program without going through a debugging cycle. For this reason, debugging is an important part of software development.

Despite today's computer-aided and automated technologies, debugging is still most effectively performed by a runtime interaction with the program under consideration. In this way, a programmer can see how a program actually behaves given a set of inputs and thus can evaluate the anomalies faster.

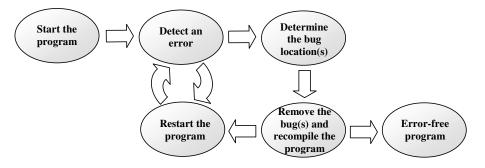

Figure 1: A typical debugging cycle.

A typical debugging cycle that many programmers go through is shown in Figure 1. Unfortunately, many of the bugs in programs do not cause errors immediately, but instead the bugs show their effects much later in program execution. For this reason, even the most careful programmer equipped with a state-of-the-art debugger might well miss the first occurrence of a bug and thus might have to restart the program. Furthermore, for difficult to find bugs, this process might have to be repeated multiple times as shown in Figure 1. However, every time a restart occurs, parts of the program

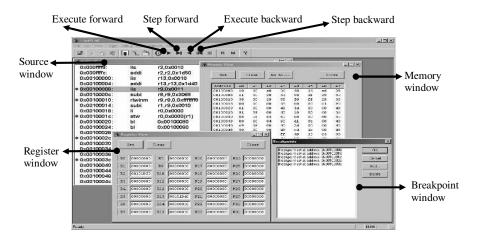

Figure 2: A sample view of windows from our reverse debugger tool.

that already executed without errors have to be re-executed unnecessarily. These unnecessary re-executions may constitute a significant portion of the debugging time. However, there is a very powerful technique which may speedup interactive debugging considerably. This technique is reverse execution.

Reverse execution provides the programmer with the ability to return to a particular previous state in program execution. When the programmer misses a bug location by executing a program too far, he or she can roll back the program to a point where the program state is considered to be correct and then re-execute from that point on without having to restart the program. This potentially reduces the overall debugging time significantly.

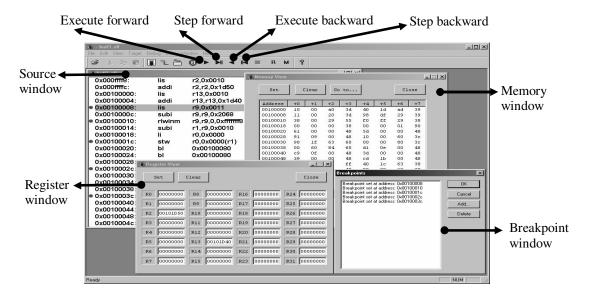

Figure 2 shows a sample view of windows from the debugger tool we have implemented. The programmer can load an assembly level program to the debugger tool and execute the program assembly instruction by assembly instruction both in the forward and the backward direction. At any desired point in execution (either in the forward or in the backward direction), the programmer can observe the values stored in registers and memory locations. Moreover, the programmer can set breakpoints at various places in the program and forward or reverse execute the program until those breakpoints.

A reader may ask, "Why is reverse execution at the assembly level important?" There are various reasons making reverse execution (or even forward execution) at the assembly instruction level available in a debugger. First, performance and memory constraints or lack of compiler support usually force assembly language programming of some software components such as small-scale embedded applications, firmware for consumer electronics, DSP libraries and operating system modules such as schedulers, high-performance I/O routines or device drivers. For instance, the majority of boot code for the computer system of the Pathfinder Spacecraft was written in assembly language because it was critical for the computer to boot up very quickly in case of a failure [44]. Furthermore, even for general purpose software, the source code may not be available at all. Therefore, during debugging of such software components, programmers have to be involved in assembly instruction level program execution.

Second, in implementing a language construct such as a pointer to an integer, sometimes the compiler generates assembly different from what the programmer expected. Similarly, compiler optimizations can move or remove instructions resulting in assembly code that does not match with the source code anymore, which makes it very difficult to debug at the source code level.

Finally, reverse execution at the assembly instruction level provides extremely fast backup capability in case the programmer executes one extra instruction too far, losing the whole program context leading to a bug.

Much like reverse execution, another powerful technique that may be used to speed up debugging is dynamic slicing. Dynamic slicing isolates the statements that influence the value of a variable at a program point in a specific execution instance of the program. In this way, the programmer can concentrate only on those statements that are relevant to the bug(s) in the program.

Therefore, it is desirable to implement both assembly instruction level reverse execution and dynamic slicing under a common framework that will help significantly reduce the time spent on debugging.

#### 1.2 Problem Statement

Note that in the rest of this thesis, the word "instruction" refers to an assembly instruction.

An execution of an assembly program T on a processor P can be represented by a transition among a series of processor states  $S = (S_0, S_1, S_2, ...)$ . From this representation, instruction level reverse execution of a program can be defined as follows.

**Definition 1.2.1** Instruction level reverse execution: Reverse execution of an assembly program T running on a processor P can be defined as taking P from its current state  $S_i$  to a previous state  $S_j$  ( $0 \le j < i$ ). The closest achievable distance between  $S_i$  and  $S_j$  determines the granularity of reverse execution. If state  $S_j$  is allowed to be as early as one instruction before state  $S_i$ , then the reverse execution is said to be instruction level reverse execution.  $\square$

The simplest approach for obtaining a previously attained state is saving that state before the state is destroyed. However, saving a state during execution of a program introduces two overheads: *memory* and *time*. A solution to reduce memory and time overheads would be to decrease the frequency of state saving during program execution. However, this prevents an *immediate* return (i.e., a return without any forward execution) to an arbitrary point in execution history where state is not saved. Therefore, in applying state saving, there usually exists a tradeoff between the closest previous state that can be restored without any forward execution and memory/time overheads due to state saving.

Similarly, dynamic slicing usually requires runtime control flow information from the execution of a program in terms of execution trajectories (see Section 2.2.2). As programs can follow more than one control flow path, the actual path the program follows determines which instructions are redundant instructions that are irrelevant to a slice. This runtime information is a significant factor making traditional dynamic slicing methods costly in terms of memory usage.

Briefly, the problem addressed by this thesis is the achievement of time and memory efficient reverse execution and dynamic slicing. In particular, an approach resulting in a dramatic reduction in state saving for both reverse execution and dynamic slicing is sought.

Having discussed the problems associated with reverse execution and dynamic slicing, we next outline the approach and the contributions of this thesis.

#### 1.3 Thesis Contributions

In this thesis, for the first time ever (to the best of the author's knowledge), an instruction level reverse execution methodology in software for general purpose processors is proposed via use of "reverse program generation." The proposed methodology is unique in the sense that it provides reverse execution at the assembly instruction level and yet still has reasonable memory and time overheads when the program is being executed.

In the proposed technique of this thesis, destroyed states are almost always regenerated instead of being restored from a previously saved record. This provides faster execution speeds and less memory space overheads as compared to traditional techniques.

This thesis also implements a new dynamic slicing algorithm on top of assembly level reverse execution. When a programmer realizes that a variable has an incorrect value at a certain program point, he or she can reverse execute the program along the corresponding dynamic slice only. Thus, instructions that are irrelevant to the bug(s) in the program are skipped and a faster return to the suspicious location can

be achieved. Most designers do not know *which* dynamic slice is needed *until* the bug appears. In this case, our approach is faster than re-running the application with the dynamic slice specified.

The dynamic slicing technique presented in this thesis not only speeds up reverse execution but also contains an advantage which is usually not offered by traditional dynamic slicing methods (see Section 2.2.2). Our technique can dynamically reconstruct the control flow information during reverse execution. Therefore, as opposed to traditional dynamic slicing methods, our technique does not require an execution trajectory to extract the control flow information from a program.

## 1.4 Thesis Organization and Roadmap

The thesis is organized as follows. Chapter 2 presents the related work. Chapter 3 gives an outline of our approach. Then, Chapter 4 explains the implementation of the proposed reverse execution technique and Chapter 5 fills in special implementation details. After explaining the reverse execution technique, Chapter 6 gives a summary of the presented work. Then, Chapter 7 discusses the extensions made to the presented algorithm with the addition of dynamic slicing support. Chapter 8 gives various experimental results. Finally, Chapter 9 concludes the thesis.

#### CHAPTER II

#### PREVIOUS WORK

The problem of how to acquire previously destroyed program states has been researched in several contexts. Similarly, there has been a considerable amount of work with regard to program slicing. In this chapter, we first present different techniques applied for reverse execution and then present the previous research efforts for program slicing.

#### 2.1 Previous Work in Reverse Execution

Reverse execution research can be divided into two different categories. The first category is the application of pure state saving approaches to restore earlier states in program execution. The second category, on the other hand, is reverse execution by a combination of state saving and state regeneration techniques.

State regeneration introduced in the second category reproduces previously destroyed values and thus achieves state recovery without state saving. This helps reduce the amount of memory usage. However, the first category covers almost all of the research performed so far to achieve reverse execution of programs. Moreover, we see very limited forms of state regeneration techniques in prior research (see Section 2.1.2). On the contrary, state regeneration constitutes the basis of this thesis.

The following two subsections provide a summary of previous work in each category mentioned above.

#### 2.1.1 Reverse Execution Techniques by Restore Earlier State

Zelkowitz provides a state restoration capability by inserting trace statements into the programming language [50]. Each trace statement includes an option that indicates either a condition or a label. Program state is captured starting from a trace statement until the condition indicated by the trace statement is satisfied or until the label indicated by the trace statement is reached. However, the programmer has to anticipate which parts of the program he or she might have to re-execute and then has to insert trace statements in those program parts beforehand.

Agrawal et al. provide a statement-level state restoration capability for programs written in a high-level programming language [3]. Agrawal et al. statically associate each assignment statement with a set of variables, called a change-set, which is modified by that statement. Then, during the execution, the associated variables in the change-set are recorded (saved to memory) for rollback. However, although this approach provides a statement-level state restoration capability, it might cause large memory and time overheads during program execution, especially with programs that modify the state frequently.

Booth and Jones associate each variable in a program with a story tag which includes the history information about how the variable is computed [14]. When a variable is used in a computation, its story is added to the story of the computed variable. At the end of a particular execution, the programmer can trace back how a variable is computed by observing the story of the variable only. However, this approach may again cause very large memory usage as the variable stories are built by pure state saving.

State restoration is also applied in so-called replay techniques for efficient debugging of programs by either hardware [7, 43] or software [19, 35, 36, 40, 42]. In the replay technique, the state of a program is first saved infrequently during execution of the program, and then the program state that is not saved is reconstructed by

replaying the program in the forward direction. In hardware approaches, state saving is handled by hardware with little or no performance overhead but with inflexibility and high cost. On the other hand, in software approaches, state saving is handled by software with flexibility and low cost but with high performance overhead. A typical drawback of these replay techniques is that since the recorded trace keeps only partial information about program state, execution can be restarted only at the beginning of a trace window where state is saved and not at an arbitrary program point. Trace windows may be fixed [19, 40] or variable [40, 36] in length and their sizes may either be determined by the programmer [40] or by a program analysis [40, 36]. For instance, in Miller and Choi's approach, trace windows which are called emulation blocks are usually chosen to be program regions that have well-defined entry points [36]. One such region is a subroutine. Generally, larger trace windows result in smaller traces but longer replay times.

Two other application areas of state restoration are optimistic or speculative computation [22, 24, 30] and fault tolerance [16, 34]. A computation is optimistic if incorrect computation is allowed during execution. Tasks executing in parallel usually have to block due to synchronization requirements on shared data. In optimistic parallel execution, tasks do not block on shared data and thus are allowed to execute independently, which potentially improves the execution performance but at the same time allows incorrect computation. Then, errors caused by possible incorrect computations are recovered by rolling back the computation of erroneous tasks to a point in time where state is known to be correct. Similarly, state restoration for fault tolerance is performed by rolling back in case software errors occur, which is usually seen in places such as database transaction systems [10, 25].

Rolling back computations or transactions is usually achieved by periodic or incremental state saving. In periodic state saving [20], the whole processor state is recorded periodically at certain checkpoints during simulation. Then, a previous state at a checkpoint can be recovered by restoring that state from the record. However, in this method, a previous state at an arbitrary point that is not a checkpoint cannot be immediately recovered. If the checkpointing interval is reduced, memory and time overheads of state saving are increased. Moreover, recording the whole processor state at each checkpoint causes redundancy because some portion of the processor state may be kept unchanged throughout several checkpoints. In incremental state saving (ISS) [48], instead of recording the whole processor state, only the modified parts of a state are recorded at each checkpoint. However, in programs where the modified state space is large, memory and time overheads of incremental state saving might again exceed affordable limits.

State restoration is also used in computer science education where students can easily navigate back and forth through well-known algorithms to understand the behavior of such algorithms. For this purpose, the common technique applied is program animation [12, 18]. Program animation constructs a virtual machine with a reversible set of instructions. Since these instructions are reversible, the program can be run backwards. However, since reversible instructions are usually constructed as stack operations, a significant amount of stack memory may be required in program animation.

Cook presents a state restoration method for Java programs [17]. A Java virtual machine is another example of a stack-based virtual machine. Most Java bytecode instructions pop the operands from the operand stack, operate on them and then push the resulting operands back into the operand stack. In his method, Cook keeps two main circular buffers for keeping the program state. The first buffer, the program counter circular buffer, keeps the program counter values. The second buffer, called the logging circular buffer, keeps the values in the operand stack that are destroyed as a result of a bytecode instruction. Then, Cook associates a reverse operation with each bytecode instruction. Basically, during a reverse operation, the program counter

is restored from the program counter circular buffer while the values in the operand stack are restored from the logging circular buffer. By using circular buffers, Cook bounds the memory requirement which otherwise would be huge due to logging of each modified operand. However, this also bounds the total number of bytecode instructions that can be reverse executed at a time and requires a runtime validation of whether there is enough data within a circular buffer for accomplishing a reverse execution request.

When compared to pure state saving saving approaches explained in this section, our reverse execution technique via generation of a reverse reverse program potentially reduces the runtime memory usage considerably. This is because most of the program state is regenerated by the reverse program. Moreover, regeneration of program states via a reverse program reduces the number of state saving instructions in the original code and thus provides faster forward execution times.

#### 2.1.2 Previous Work in State Regeneration at the Source Code Level

Floyd makes use of state regeneration in the area of nondeterministic algorithms [21]. A nondeterministic algorithm is an algorithm that may come up with a different solution to a problem at each run of the algorithm. However, the solution is not reached by a random process but by incrementally constructing a path that leads to a success. In Floyd's approach, whenever a nondeterministic algorithm enters a path leading to a dead end, the algorithm state at the most recent point where a decision is made is restored and alternative solutions are sought from that point on.

Floyd achieves reverse execution by defining a reverse operation for each operation in a nondeterministic algorithm. However, a reverse operation without state saving can only be generated for reversible constructive operations. A constructive operation is an operation where the variable being modified (the target operand) is the same as one of the source operands. The operation "x = x + 1" is an example of a

constructive operation. On the other hand, a constructive operation is reversible only if there exists an operation that can fully recover the prior value of the target operand of the constructive operation. For instance, the prior value of the target operand of " $\mathbf{x} = \mathbf{x} \oplus 1$ " can be fully recovered by executing the same operation once more. Therefore, " $\mathbf{x} = \mathbf{x} \oplus 1$ " is reversible. On the other hand, although " $\mathbf{x} = \mathbf{x} / 2$ " is constructive, this operation might not be reversible for the case where the target operand x cannot always be fully recovered due to a possible precision loss in the computed result.

State regeneration finds its application in a limited sense in the area of debugging optimized code as well [1, 28, 49]. Hennessy introduces the term "currency" of a variable [28]. A variable is current at a program point if the value of the variable at that program point is the same as the variable's expected value according to the source code. Since code optimizations such as code motion and dead variable elimination may move or remove assignments to variables in the object code, the value of a variable at a certain point in the optimized code may not be equal to the value of the variable at the corresponding point in the unoptimized code, which causes the variable to be "noncurrent" at that program point. In such a case, the current value of the variable has to be recovered to provide the user with a consistent view of the program being debugged. This recovery operation is where reverse execution comes into play.

A typical recovery technique in this field is to reevaluate noncurrent variables using appropriate definitions of those variables in the program. However, since the main focus in this area has been on the determination of whether a variable at a program point is current or not rather than on the recovery of a noncurrent variable, the recovery techniques applied in this area are generally very restrictive and ineffective. For instance, Wismuller reports that only 2-5% of all encountered noncurrent variables can be recovered in his benchmarks [49].

Carothers et al. introduce another approach for optimistic parallel simulations [15]. This approach is source transformation. In source transformation, the source code (e.g., in C) is transformed to a reversible source code version. Then, from the reversible version a reverse source code is obtained. The reverse source code reverses the effect of the original source code. However, similar to Floyd's approach [21], Carothers et al. also apply state saving for all operations except reversible constructive ones. Consequently, the execution time and memory requirements of the reverse code are increased.

Biswas and Mall also generate a reverse program from a program given in the C programming language [13]. For constructive operations in C which use operands such as "\*=" or "+=", they generate reverse statements that use the inverse operators. Thus, for instance, "\*=" becomes "/=". However, similar to other approaches presented in this section, these constructive operations are the only cases where reverse execution is performed without state saving. Moreover, in cases where the underlying processor may truncate the result (such as an overflow condition), the correctness of the reverse execution is indeterminate. For all other operations, Biswas and Mall keep a trace file that holds the necessary state to reverse execute a C program. In their paper [13], Biswas and Mall state (referring to non-constructive assignment statements in the form of a = b op c), "Thus, it is not possible to define an inverse for this [sic] type [sic] of assignment statements and the old value of the variable must be maintained in a trace file." In a similar quote, the DDD (a front-end for GNU GDB debugger) v3.2 manual on page 98 states, "DDD cannot undo what your program did. After a little bit of thought, you will find that this would be *impossible* in general." In this thesis, we show that even destructive assignment statements are indeed reversible without state saving.

The state regeneration techniques proposed in this thesis are applicable in wider range of situations than the state regeneration techniques presented in this section. Therefore, state regeneration efficiency is potentially much higher in our techniques when compared to previous techniques. This results in larger savings in terms of memory and time costs.

## 2.1.3 Previous Work in State Regeneration at the Assembly Instruction Level

We have made an exhaustive literature survey searching for a software approach that achieves reverse execution at the assembly instruction level. However, we could not find any such work. Therefore, this thesis might be the first work to achieve reverse execution at the assembly instruction level on general purpose processors by use of reverse program generation.

## 2.2 Previous Work in Program Slicing

Program slicing algorithms can be divided into two major types according to whether the slice extraction is performed at compile time (*static slicing*) or at runtime (*dynamic slicing*). In this section, we present a brief history of static slicing as well as dynamic slicing algorithms. An interested reader can find detailed surveys of slicing algorithms in [11, 27, 46].

#### 2.2.1 Static Slicing

Program slicing was first proposed by Weiser [47]. His approach statically determines the program statements that potentially affect a variable at a certain statement. Here, the variable under consideration and the statement at which it is computed form the slicing criterion. Weiser computes slices from a control flow graph of the subject program. For this purpose, Weiser iteratively finds data flow information between control flow graph nodes. This information reveals at each control flow graph node the variables, called *relevant* variables, that transitively affect the computation of

the variable in the slicing criterion. Then, the slice is found as a combination of all program statements that compute the relevant variables in a program.

In Weiser's approach the extracted slices are executable. That is, the extracted slice is itself an executable subset of the original program. Also, the slices introduced by Weiser are backward meaning that the statements affecting the variable in the slicing criterion are found by a backward traversal of the control flow graph nodes starting from the node computing the variable in the slicing criterion.

Ottenstein and Ottenstein use a different intermediate representation to compute slices [41]. Instead of a control flow graph, they use a program dependence graph (PDG). The statements and the control flow predicates in a program constitute the vertices of a PDG, while the data and control dependence relationship between the vertices are represented by the edges of a PDG. Slicing is defined as a reachability problem in a PDG. The nodes that are reachable from the vertex that computes the variable in the slicing criterion are included in the slice. Later, Horwitz et al. introduce various modifications to the PDG approach to determine static slices of a program including multiple procedures or unconditional jumps such as goto statements [29].

Bergeretti and Carre introduce forward slicing [8]. Instead of looking for variables that might affect the variable in question (as in the case of backward slicing), forward slicing specifically looks for variables that *might be affected* by the variable in question. Therefore, as opposed to backward slicing, forward slicing traces the dependencies between variables in the forward direction.

Harman and Danicic propose a different approach to slicing [26]. They define a slice called an *effect minimal slice*. An effect minimal slice is a slice that preserves the effect of the original program on the variable in the slicing criterion, but that is not necessarily constructed as a subset of the original program. Harman and Danicic convert an imperative program to its functional equivalent and then perform algebraic transformations on the resulting functional program by using the properties

of functional languages. The transformations replace the statements in the original program with less number of equivalent statements that have the same overall effect on the variable in the slicing criterion. Therefore, a thinner static slice can be obtained for the variable in the slicing criterion.

The main drawback of static slicing is that it has to be conservative in making decisions that require runtime information of a program. For instance, if two statements statically affect the variable in the slicing criterion, but one of the statements actually is never executed in a particular debugging session, static slicing has to conservatively include both statements in the slice because the decision of whether the statements will be executed or not may not be made statically. Thus, static slicing usually provides slices larger than one could potentially obtain by using a dynamic slicing technique including the dynamic slicing technique proposed in this thesis.

#### 2.2.2 Dynamic Slicing

As explained in the previous subsection, static slicing does not employ any runtime information and thus static slicing may compute large slices. This disadvantage of static slicing motivated Korel and Laski [31] to introduce dynamic slicing. Their approach incorporates runtime information to find the statements that *actually* affect a variable at a program point. Thus, the resulting slices are more compact and precise than the program slices proposed by Weiser [47]. First, the subject program is run and an execution history is obtained. The execution history tells which statements in the program actually execute. Then, using this information, statements upon which the variable in the slicing criterion is dynamically data or control dependent are extracted.

Agrawal and Horgan incorporate a dependence graph, which they call a dynamic dependence graph (DDG), to calculate dynamic slices of a program [4]. In the sense that a dependence graph is used, Agrawal and Horgan's approach can be considered

as an extension to the PDG based static slicing algorithms. Later Agrawal, DeMillo and Spafford present a solution based on DDGs for inter-procedural dynamic slicing of programs [2].

There has been research in forward computation of dynamic slices as well [9, 32]. In a forward dynamic slicing technique, a dynamic slice is obtained during execution of the program. Therefore, the runtime trace information is kept bounded. However, since forward slicing does not start from the instruction in the slicing criterion, it calculates all possible dynamic slices for all variables in a program. Therefore, forward dynamic slicing algorithms are usually slow.

In dynamic slicing techniques, the processing of a complete program trace also constitutes a large memory usage. Zhang et al. present an algorithm which keeps a record of the complete execution history and then processes only the necessary information in that record for the purpose of generating a particular dynamic slice [51]. This potentially reduces the memory cost of slice extraction.

The main drawback of traditional dynamic slicing methods is that these methods either use too much runtime information or are not performed in a demand-driven fashion starting from a specific dynamic slicing request. Moreover, the traditional dynamic slicing methods do not provide a way for reverse execution along a dynamic slice. However, the dynamic slicing method proposed in this thesis is demand-driven, can regenerate most of the control flow information required to extract the dynamic slice during reverse execution and provides a way to reverse execute the dynamic slices.

## 2.3 Summary

In this chapter, we presented various prior research in reverse execution and dynamic slicing. The reverse execution technique we present in this thesis usually causes much less memory and time overheads than the prior reverse execution techniques. Moreover, as opposed to previous approaches, the dynamic slicing technique we propose reduces runtime memory usage and provides reverse execution along dynamic slices. We will eventually show the advantages of our technique over the previous techniques with quantitative comparisons in Chapter 8. In the next chapter, we present an overview of our approach for reverse execution at the instruction level. The implementation details of our reverse execution technique and the extensions for dynamic slicing support are explained in chapters subsequent to the next chapter.

#### **CHAPTER III**

# OVERVIEW OF REVERSE CODE GENERATION

Our approach is mainly based on regenerating a previously destroyed state rather than restoring that state from a record. When state regeneration is not possible, however, we recover a destroyed state by state saving. Hereafter, we refer to the recovery of a state as *state restoration* if that recovery involves state saving. If there is no state saving involved in a particular state recovery, we refer to such recovery as *state regeneration*.

We achieve both state regeneration and state restoration by the help of a reverse program. Given an assembly program T either written directly in assembly or compiled into assembly from a high level programming language, we generate a reverse program RT from T by a static analysis at the assembly instruction level. We call our algorithm which we use to generate a reverse program the  $Reverse\ Code\ Generation\ (RCG)$  algorithm.

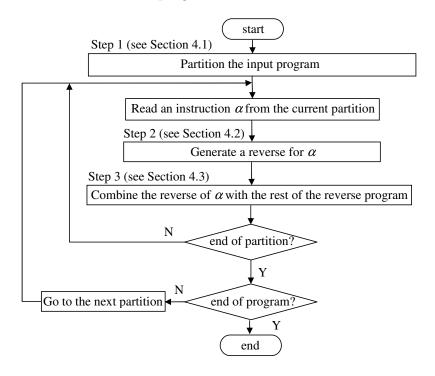

The RCG algorithm can be divided into three main steps. These steps are program partitioning, reversing an assembly instruction and combining the reverse instructions. Figure 3 shows the flow of control between these three steps. The RCG algorithm first passes over the input program and partitions the input program (Step 1). Then, the RCG algorithm goes into a main loop where each program partition is read instruction by instruction in program order (lexical order). After an instruction  $\alpha$  is read, the RCG algorithm generates the reverse of  $\alpha$  (Step 2 in Figure 3) and combines the reverse with the rest of the reverse program generated so far (Step 3).

Step 2 and Step 3 are repeated until the end of a program partition is reached. When the end of a program partition is reached, the RCG algorithm moves to the next program partition and iterates over Step 2 and Step 3 for the instructions in the next program partition. These steps are repeated until all the partitions inside a program are processed and the end of the program is reached.

**Figure 3:** A high-level view of the RCG algorithm.

In the following sections, we first state our main assumptions for the applicability of the RCG algorithm and then discuss each RCG step briefly.

## 3.1 Preliminary Assumptions

We assume a certain set of inputs to be provided to the RCG algorithm. Let us first describe our assumptions regarding the inputs of the RCG algorithm and then explain under which conditions the RCG algorithm can apply the state regeneration techniques that will be presented in the rest of this thesis.

#### 3.1.1 Inputs of the RCG Algorithm

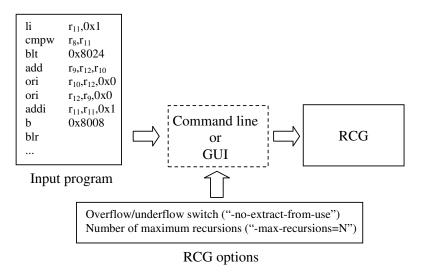

Figure 4 shows the input of the RCG algorithm. First, the RCG algorithm takes as input either through a Graphical User Interface (GUI) or as a command line argument an assembly program T without associated source code. We assume no symbol table nor any other compiler related information whatsoever. The assembly code can be hand-written or generated by a compiler. Moreover, compiler optimizations do not limit the applicability of the RCG algorithm. As will be shown in Section 8, the RCG algorithm can provide significant savings in execution time and memory usage even with highly-optimized programs as input. Also, we assume that the input program is single-threaded, is not self-modifying and does not change base addresses of program sections (such as the global data section or the stack) dynamically.

Figure 4: Inputs of the RCG algorithm.

In addition to the input program, the RCG algorithm accepts two options from the user (Figure 4). These options affect the reverse code generation process. First, in case of an overflow or an underflow during an operation to be reversed, a specific state regeneration technique, which we will name the extract-from-use technique and describe in Section 4.2.2, may not work properly. Therefore, in a program that may trigger an overflow or an underflow, the user notifies the RCG algorithm by use of a command line switch ("-no-extract-from-use") or through a GUI that overflow or underflow may occur (see Figure 4); otherwise, if "-no-extract-from-use" is not specified in the command line input (or through a GUI), RCG assumes no overflow or underflow ever occurs under any situation (e.g., for any possible data input). The use of "-no-extract-from-use" option ensures that the reverse code functions correctly in cases where overflow or underflow may occur.

Second, the user specifies by use of a command line option "-max-recursions=N" (or through a GUI) the upper limit for how many times the RCG algorithm may recursively apply the state regeneration techniques. In this option, the maximum number of recursions allowed is specified by N. As will be explained in Section 4.2, the RCG algorithm usually applies the state regeneration techniques recursively because these techniques may not give a solution after only one iteration. However, each recursive application of state regeneration techniques increases the running time of the RCG algorithm. Therefore, the upper limit N set by the "-max-recursions=N" option helps limit the time cost of the RCG algorithm. If an upper limit N is not set, the RCG algorithm applies state regeneration techniques repetitively until a point where all paths to possible solutions are traversed. If no solution can be found along those paths, state saving is dictated.

Next, we state the assumptions we make regarding the reverse code generation process.

#### 3.1.2 Assumptions for RCG

Now, suppose that an assembly program T attains a series of states  $S = (S_0, S_1, S_2, ...)$  during its execution on a processor P where the distance between two consecutive states is one instruction. Now, assume that we can generate another program RT, the instruction level reverse program of T, such that when a specific portion of RT

is executed in place of T when the current state of T is  $S_i$ , the state of T can be brought to a previous state  $S_j$  ( $0 \le j < i$ ). In other words, RT recovers a previously destroyed state. If RT contains an executable portion for changing the state of P from any state  $S_i \in S$  to any other previous state  $S_j \in S$  (j < i) for any possible state sequence S during execution of T, then the execution of T can be reversed by executing RT in place of T.

To build a complete reverse program, the RCG algorithm uses pure static information. However, in order to reverse execute a program, dynamic information may be required as well. This dynamic information mainly consists of the values that cannot be recovered by state regeneration and thus are saved dynamically. The statically generated instructions inside the reverse program use this dynamic information to undo the original instructions. Therefore, in case of state restoration, RT simply issues memory load instructions that restore the values already saved by state saving instructions inserted into T. In the case of state regeneration, RT recovers a state without any state saving code in T.

However, in practice, it might be hard to implement such a program RT which recovers 100% of the program state either by state regeneration or by state restoration. This is due to the following reasons.

1. Typically, processors include auxiliary hardware usually not accessible by the instructions directly. The processors usually manipulate this kind of hardware implicitly. Therefore, it is typically hard to recover indirectly modified state in this kind of hardware. As an example, consider the overflow register of a processor. The overflow register is written indirectly by an operation such as "c = a + b" if an overflow occurs during such an operation. However, many processors do not specify an instruction to directly write to the overflow register, which makes it hard to recover the overflow register. For a more detailed discussion of indirectly modified state in an Instruction Set Architecture

- (ISA) with a specific focus on PowerPC as a target example ISA, please see Appendix A.

- 2. Generally, writing a value to the program counter either by a branch instruction or by direct modification causes an immediate jump to the address location designated by the value written to the program counter. Therefore, as soon as RT were to recover the program counter, the execution of RT would immediately be broken. This suggests that the program counter should be recovered only at the end of the execution of a specific portion of RT and just before the user switches back to forward execution. However, since it is not known a priori what program part the user will reverse execute (i.e., which portion of RT the user will run), it is impractical to recover the program counter inside RT.

- 3. If an instruction modifies a memory location, the instruction encoding only tells us the modified address but not the physical location actually being modified in the memory hierarchy (i.e., L1 cache, L2 cache or main memory). Without the knowledge of the physical location actually being modified, it is typically hard to recover the exact physical memory state (including exact cache state).

Therefore, regarding item (1) above, we define a program state S' = (M', R') that includes only directly modified memory (M') and directly modified register (R') values (i.e., M' and R' only include the memory locations and registers that appear as operands of the instructions of T). Assuming that we can generate an instruction level reverse program RT for a program T (an assumption which is true since we can always resort to state saving if necessary), we can recover all memory and register values that are directly modified by T. Note that some indirectly modified memory/register values that have an effect on T's state may cause incorrect computation in rare cases if those values are not recovered properly. We propose two techniques that can be used to ensure correct computation in such cases. Therefore, by the help

of the two techniques we propose, we can even reverse any program that includes any combination of instructions that indirectly modify program state. For a detailed discussion of these two techniques, please refer to Appendix A.

Regarding item (2) above, since the program counter value carries important debugging information, we must provide a means for restoring the program counter value. We solve this problem by leaving the recovery of the program counter value to the debugger tool. We associate the address of each instruction in T with the beginning address of the corresponding portion in RT that reverses the effect of that instruction. In this way, when a part of T is reverse executed by executing the corresponding portion in RT, the debugger tool restores the value of the program counter by using the connection between the addresses in T and RT.

Finally, regarding item (3) above, we treat memory as a unified abstract entity which keeps the values of high-level program variables. In other words, as long as the destroyed values of a variable can be retrieved, we do not distinguish between whether the variable is actually kept in processor cache or main memory. Consequently, undoing a memory store operation on a program variable only comprises recovering the previous value of the program variable but not the exact previous state of the processor cache or main memory. For instance, a variable may originally reside in main memory but not in the L1 cache; however, after the variable is destroyed and subsequently recovered, the variable might be brought into the L1 cache. Therefore, this process recovers the value of the variable, but does not restore the original state of the L1 cache.

In addition to the three items above, there are also two other assumptions we make. First, we assume that in case of an exception, the exception handler saves the program context such as the program counter and the register state just before the exception. Therefore, exceptions can be reversed by recovering the saved program

context. Second, we assume that the external inputs/outputs to/from a program (such as file I/O) are recovered by state saving.

Having discussed some of our initial assumptions and goals, we next illustrate the highlights of the three main RCG steps.

## 3.2 Program Partitioning

Many programming language related algorithms require a certain analysis which is used to extract information from the subject program. The same is true for the RCG algorithm. The control flow analysis and the reaching definitions analysis constitute the main analyses of the RCG algorithm.

When analyzing a program, it is essential to first select the program level at which to perform the analysis. Is the analysis to be carried out on the whole program at once or on individual functions separately or on even smaller regions such as basic blocks one at a time?

It is usually difficult to perform control flow analysis across indirect calls because an indirect call may be made to a statically unknown address. Therefore, in order to simplify the RCG algorithm, we prefer to restrict the control flow analysis to inside certain regions of code in which control flow can be statically determined. We name these regions *program partitions* (*PPs*). Across PPs, on the other hand, control flow information is dynamically recorded via a state saving technique that will be explained in Section 4.3.3.2.

For most instruction sets (e.g., PowerPC, x86 and ARM), PPs are delimited by indirect branches or "function call" instructions that may exist in the code. An indirect branch delimits a PP because an indirect branch instruction may direct the control to a statically unknown address. A function call instruction, on the other hand, delimits a PP because the control may return from the called function whose address may be statically unknown to the address following the function call

**Figure 5:** (a) An example program T in C. (b) Assembly of T showing the PPs.

instruction. In the PowerPC instruction set, "bl" (branch with link register update) and "blr" (branch to link register) instructions are examples for function call and indirect branch instructions, respectively.

Figure 5 shows an example program T. In Figure 5(b), the portion of main that starts from the first instruction of main and extends until the function call instruction in main is a PP inside main. Similarly, the remaining portion of main is another PP. On the other hand, since foo does not contain any function call instructions inside, the whole body of foo is a PP by itself.

## 3.3 Reversing an Assembly Instruction

In Section 3.1, we stated that the reverse program recovers only directly modified program state. Therefore, under this assumption, reversing an assembly instruction is equivalent to recovering the register and/or the memory value(s) being directly overwritten by that instruction. In this section, we outline how the RCG algorithm recovers a directly modified value.

After the PPs are determined, the RCG algorithm goes over every instruction within all PPs in *program order* and checks whether each instruction directly modifies a register or a memory location. If an instruction directly modifies a register or a memory location, the RCG algorithm generates a group of one or more instructions which recovers the overwritten value in that register or memory location. We call such a group of instructions a reverse instruction group (RIG).

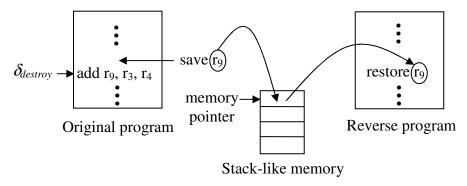

A value destroyed by an instruction can be recovered in three ways: (i) the value can be recalculated during instruction level reverse execution, which we call the *redefine technique*; (ii) the value can be extracted from a previous use during instruction level reverse execution, which we call the *extract-from-use technique*; and (iii) the value can be saved during forward execution and then restored during instruction level reverse execution, which we call the *state saving technique*.

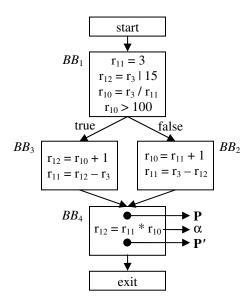

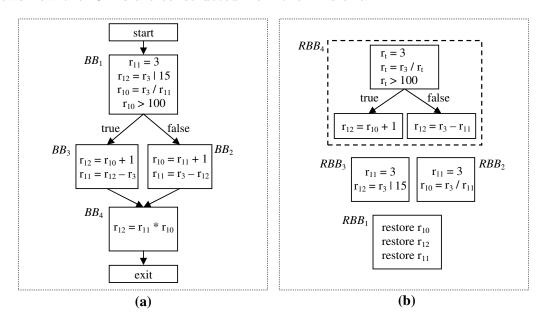

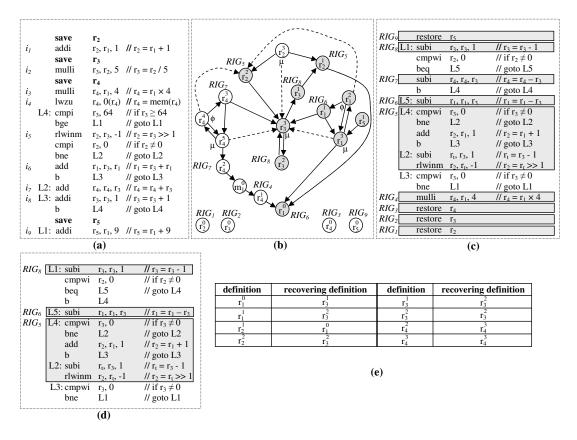

Figure 6 shows T (from Figure 5) and T's reverse RT. An instruction  $i_x$  in T and the generated RIG,  $RIG_x$ , for that instruction are marked with the same index x in Figures 6(a) and 6(b), respectively. Note that the instructions that are shown in bold are extra instructions that are inserted to the original program for state saving; thus, these instructions do not have associated RIGs. In addition, as will be explained in the next section, control flow is reversed by control flow predicates inserted into the reverse code; therefore, the control flow instructions also do not have associated RIGs in the generated reverse program. Consequently, in Figure 6, we assigned indices neither to the control flow instructions in the original program nor to the state saving instructions inserted in the original program to enable reverse execution. Now, let us have a closer look at some generated RIGs.

Example 1 Consider in Figure 6 the RIG for  $i_8$  which subtracts  $r_3$  from  $r_{12}$  and writes the result into  $r_{11}$ . Since the only value that is being directly changed by  $i_8$  is  $r_{11}$ , the generated RIG for  $i_8$ ,  $RIG_8$ , should recover  $r_{11}$ . First of all, the RCG algorithm finds the value of  $r_{11}$  that needs to be recovered. For this purpose, the RCG algorithm performs reaching definitions

**Figure 6:** (a) Assembly of T shown in Figure 5(a). (b) Reverse of T, RT.

analysis within the PP under consideration. The definition that reaches the point just above  $i_8$  is  $r_{11}=3$  which comes from  $i_3$ . Therefore, the value of  $r_{11}$  to be recovered is 3. This value is used within the division operation at  $i_5$  before being destroyed. However, the division operation does not allow the extraction of the destroyed value due to a possible loss of precision. Thus, the extract-from-use technique is inapplicable in this case. However, the redefine technique is applicable. Therefore, the RCG algorithm simply places the found reaching definition into  $RIG_8$  which redefines the destroyed value and thus recovers it.  $\Box$

Note that the regeneration of a value may require the regeneration of other values. For example, this would happen if the value of a register were to be regenerated using the value of another register that is also overwritten. Therefore, the redefine and extract-from-use techniques are usually applied recursively (see Section 4.2).

On the other hand, if there are multiple definitions reaching at a point along different control flow paths, then the definition to be recovered depends on the dynamic control flow of the program. In this case, the RCG algorithm generates instructions that recover each statically reaching definition. Then, the RCG algorithm gates these instructions using conditional branches which determine (according to the dynamic control flow of the program) which definition should actually be recovered in a particular instruction level reverse execution instance. The following example illustrates this case.

Example 2 Consider  $RIG_9$  in Figure 6. In  $RIG_9$ , the conditional branch instruction chooses the correct definition of  $r_{12}$  to be recovered based on the specific control flow path taken in forward execution of the program (see Section 4.2 for a detailed explanation).  $\square$

Finally, if a value can be recovered neither by the redefine technique nor by the extract-from-use technique, the RCG algorithm applies the state saving technique. Consider the following example.

Example 3 In Figure 6, the value of  $r_3$  that is being destroyed by  $i_1$  comes from outside of the PP in which  $i_1$  resides. Thus, this value cannot be redefined within the RIG to be generated. Moreover, this value is not used within the PP before being destroyed. Therefore, in this case, the RCG algorithm recovers  $r_3$  by state saving which is performed by the inserted save instruction before  $i_1$ . Then, the generated RIG,  $RIG_1$ , simply restores  $i_1$ 's value from the saved record.  $\square$

From what we outlined above, we can state that the RCG algorithm tries to apply state regeneration by using the redefine and the extract-from-use techniques as much as possible. The RCG algorithm applies the redefine and extract-from-use techniques in combination to produce the smallest RIG. In case neither of these techniques are applicable, a RIG is generated by employing state restoration. Generally, state saving is applied if (i) the reaching definitions analysis cannot accurately find the value that is being destroyed as in the case of memory aliasing (see Section 5.1) or (ii) the value to be recovered comes from outside of the PP under consideration and thus the extraction of the value from a previous use within the PP is not possible.

We next explain the third and final main step of the RCG algorithm.

## 3.4 Combining the Reverse Instruction Groups

In order to keep the state consistent, the instructions that are executed in a certain order during forward execution are supposed to be reversed in the opposite order during instruction level reverse execution. This is similar to reversing a sequence of movie frames where the frames during fast backwarding are shown in the opposite order they are shown during forward play of a movie. In this section, we outline how we combine the RIGs in order to establish a control flow that is exactly opposite to the control flow of the original program.

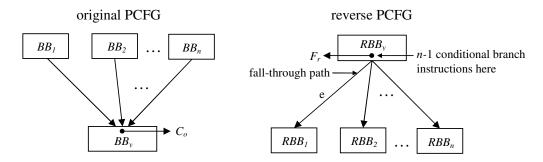

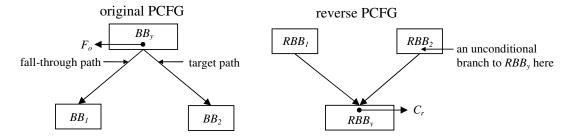

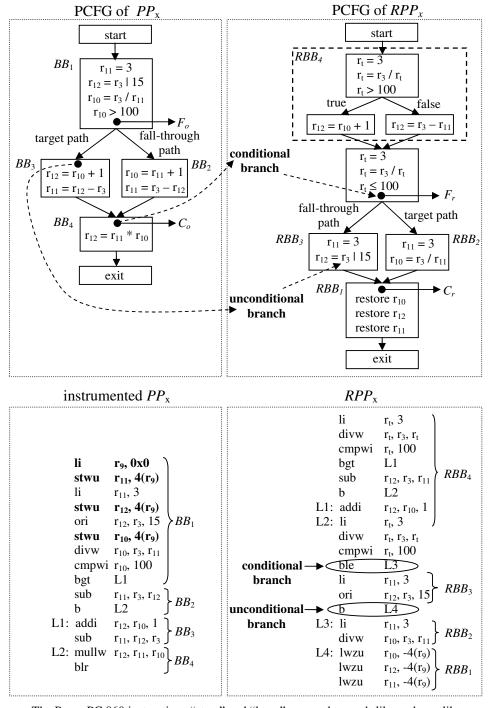

From the control flow analysis point of view, we represent each PP by a control flow graph which we call a partitioned control flow graph (PCFG). A PCFG is no different than an ordinary control flow graph except that a PCFG is not necessarily constructed for a complete function or a whole program. Figure 7 (a) shows the PCFGs for the three PPs of T defined previously in Section 3.2. As seen in the figure, each PCFG is further divided into  $basic\ blocks\ (BBs)$ . Therefore, we represent a program in a hierarchical structure. PPs form the highest level of hierarchy, then come the BBs and finally come the individual instructions.

The RIGs are combined in accordance with our hierarchical representation of a program. From the lowest level of program hierarchy to the highest level, this combination process can be outlined as follows:

- 1. Combine the RIGs generated for a BB to construct the reverse of that BB which we designate as RBB for short.

- 2. Combine the RBBs generated for a PP to construct the *reverse* of that PP which we designate as *RPP* for short.

- 3. Combine the RPPs to construct the reverse program.

Figure 7: (a) PCFGs of T. (b) PCFGs of RT.

Within basic blocks of a PP, control follows a linear path. Since we want the instructions to be reversed in the opposite order they are executed in the forward direction, linear execution within basic blocks can be reversed by simply placing the RIGs in the reverse order the original instructions are placed. We call this placement order the bottom-up placement order. For instance, as seen in Figure 7, the RIG generated for the first instruction of foo in  $BB_1$  is placed at the end of the corresponding RBB,  $RBB_1$ ; the RIG generated for the second instruction is placed on top of the previously generated RIG and so on.

We next consider the second level of hierarchy above where RBBs are to be combined into RPPs. In this case, we insert conditional branch instructions into the reverse code to provide a link between non-consecutive RBBs. Much like a railroad track changer, conditional branch instruction(s) inserted after an RBB select the correct path to be taken following that RBB. This selection is automatically performed by the predicates of the inserted conditional branch instructions. For instance, after  $RBB_4$  in Figure 7, a conditional branch is inserted which determines which RBB  $(RBB_2 \text{ or } RBB_3)$  to execute next.