Date of publication xxxx 00, 0000, date of current version xxxx 00, 0000.

Digital Object Identifier 10.1109/ACCESS.2017.Doi Number

# Asymmetrical 17-level Inverter Topology with Reduced Total Standing Voltage and Device Count

M Saad Bin Arif<sup>1,2</sup>, (Member, IEEE), Uvais Mustafa<sup>2</sup>, Shahrin Bin Md Ayob<sup>2</sup>, (Senior Member, IEEE), Jose Rodriguez<sup>3</sup>, (Life Fellow, IEEE), Abdul Nadeem<sup>1</sup>, and Mohamed Abdelrahem<sup>4,5</sup>, (Member, IEEE)

<sup>1</sup>Department of Electrical Engineering, Z. H. College of Engg. and Tech, AMU, Aligarh, India

<sup>2</sup>Power Engineering Department, School of Electrical Engineering, UTM, Johor, Malaysia

<sup>3</sup>Universidad Andres Bello, Santiago 8370146, Chile

<sup>4</sup>Chair of Electrical Drive Systems and Power Electronics (EAL), Technische Universität München, 80333 München, Germany <sup>5</sup>Electrical Engineering Department, Faculty of Engineering, Assiut University, Assiut 71516, Egypt

Corresponding authors: M. Abdelrahem (e-mail: Mohamed.abdelrahem@aun.edu.eg or Mohamed.abdelrahem@tum.de) and Shahrin Bin Md Ayob (e-mail: shahrin@fke.utm.my).

**ABSTRACT** Voltage source Multilevel Inverters (MLIs) are vital components for medium voltage and high-power applications due to their advantages like modularity and better power quality. However, the number of components used is significant. In this paper, an improved asymmetrical multilevel inverter topology is proposed producing 17-levels output voltage utilizing two dc sources. The circuit is developed to reduce the number of isolated dc-sources used without reducing output levels. The circuit utilizes six two-quadrant switches, three four-quadrant switches and four capacitors. The capacitors are self-balancing and do not require extra attention, i.e. the control system is simple for the proposed MLI. Detailed analysis of the topology under linear and non-linear loading conditions is carried out. Comparison with other similar topologies shows that the proposed topology is superior in device count, power quality, Total Standing Voltage (TSV), and cost factor. The performance of the topology is validated for different load conditions through MATLAB/Simulink environment and the prototype developed in the laboratory. Furthermore, thermal analysis of the circuit is done, and the losses are calculated via PLECS software. The topology offers a total harmonic distortion (THD) of 4.79% in the output voltage, with all the lower order harmonics being less than 5% complying with the IEEE standards.

**INDEX TERMS** Asymmetrical Converters, Multilevel Inverter (MLI), Reduced Device Count, Total Standing Voltage (TSV), Nearest Level Control (NLC)

#### I. INTRODUCTION

Multilevel Inverters (MLIs) are becoming very important for medium voltage high power applications day by day due to several advantages like improved power quality, lower switching stress, modularity of structures, no EMI, etc. [1-3]. The three basic topologies for the MLIs are Flying Capacitor (FC) MLIs, Neutral Point Clamped (NPC) MLIs, and Cascaded H-Bridge (CHB) MLIs. These were termed Conventional topologies. The main disadvantages of these topologies were the large number of devices incorporated and the complexity in the control of capacitors voltages [4]. Researchers have been looking for various topologies to remove these demerits [5-7]. Since the MLI produces stepped output, various dc sources/links are required, which are switched on in a predefined manner with semiconductor devices like IGBTs, MOSFETs, etc. Having a higher number of dc links ensures better waveforms of the output voltage and current. However, having a higher number of dc sources is a disadvantage as it increases complexity and cost to the system [8]. Capacitors can be employed to increase the dc links with a reduced number of dc sources, but this requires careful consideration. The capacitor may require extra effort to keep their voltages balanced [9]. Another method is to choose the magnitude of the dc sources in a specific ratio to maximize the number of levels. These are called asymmetric inverters [10].

Various topologies considering the above facts are available in the literature. Manjrekar [11, 12] proposed an asymmetric configuration for the CHB inverters by choosing the magnitude of dc sources in a binary manner, thus increased the

output voltage levels dramatically while keeping the number of devices the same. Another work is proposed in [13], where the author used several capacitors to increase the dc links. The main disadvantage of this work was that the capacitors required a complex control algorithm. In [14], the authors were concerned about reducing the voltage stress on the switches and producing a higher number of levels with fewer switches. The authors of [15] proposed another topology that offered lower switching stress and a higher number of levels, but the capacitors required extra attention by complex control. The topology in [16] had self-balancing capacitors, but the number of switches was high. In [17] though the topology offers high output voltage levels, it required an H-Bridge for polarity generation, thus necessitating higher rating switches.

In [18], a new topology comprised of three dc sources and eight switches is proposed. This topology can be used as symmetric or asymmetric. The topology offered 9-level output for symmetrical operation, while for asymmetrical operation where  $V_1:V_2:V_3 = 3:1:1$ , it offered 13-level output. In [19], a 17-level topology is proposed, but it requires four dc sources, four capacitors, and 16 switches. Thus the component count is too high. In [20], a new 17-level topology is proposed. The presented topology utilizes 12 switches, but the number of dc sources are four. Whereas in [21], another interesting topology producing 17-level output voltage is shown. The topology utilized 12 IGBTs (10 switches) and required 10 driver circuits, but the number of dc sources are still high, i.e. four.

Moreover, 17-level topologies are proposed in [22, 23], in both the topologies, four dc sources were utilized. Furthermore, in [23], the proposed MLI required 16 IGBTs and 14 driver circuits, which is relatively high. Apart from the above works, there are other improved recently proposed MLI topologies. Some of the notable works include [24-26]. The main limitations include higher device count or higher TSV. Device count can be reduced by asymmetrical configuration, but that increases the voltage stress on switches and, in turn, the TSV. Another attempt to increase the level generated with a low device count is made in [35]. A switched capacitor is used to boost the output. Therefore, there is a trade-off between the asymmetric configuration and the feasibility of the topology

The authors of this work proposed an improved topology capable of producing 17-output levels while utilizing a reduced number of dc sources and switches. The proposed circuit is developed to reduce the number of isolated dcsources used without reducing output levels. This is one of the main contributions of the proposed topology. The authors employ two dc sources and have added self-balancing dc-link capacitors to generate a 17-level output voltage. The capacitors are self-balancing; thus, no other complex control algorithm is required for voltage balancing. Moreover, the proposed topology offers significantly less Total Standing Voltage (TSV), making it a feasible option in high voltage applications. Thus, the contribution of this work can be summarised in the following points:

- a) The proposed topology utilizes only two DC sources and nine switches (12 IGBTs) for producing 17 levels of output voltage.

- b) Although the number of bidirectional switches is increased in the proposed topology, it offers a better  $N_L/N_{sw}$  ratio than the other compared topologies.

- c) The proposed topology utilizes dc-link capacitors, which are self-balancing; thus, no extra complex algorithm is required.

- d) The proposed topology has low TSV [p.u] than the other 17-level topologies, making it a viable option.

The paper's structure is as follows: the next section will discuss the circuit configuration, its working modes, and the Total Standing Voltage calculation. Extension of the proposed topology and its generalized equations were presented in section II. In sections III and IV, simulation analysis followed by hardware validation is discussed. The power loss analysis and the comparative analysis is presented in sections V and VI. Finally, the conclusion of the work is delivered in section VII.

# **II. PROPOSED CIRCUIT DESCRIPTION**

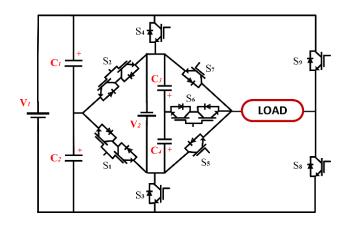

The proposed topology is shown in Fig. 1. It consists of two dc sources and nine switches. Six switches are unidirectional, while the other three are bidirectional switches. It is capable of generating 17-level output voltage by utilizing two selfbalancing capacitors across each dc source. The two dc sources are in the proportion of V<sub>1</sub>:V<sub>2</sub>=3:1. The capacitor provides a way to break each source's DC voltage into two equal magnitudes with bidirectional switches. The switches (S1, S3), (S2, S4), (S3, S4), (S5, S7), and (S8, S9) pairs should not conduct at the same time to prevent shoot-through fault. Table I shows the switching configuration and corresponding voltage level of the proposed MLI topology.

FIGURE 1. Circuit diagram of the proposed 17-Levels MLI topology

Author Name: Preparation of Papers for IEEE Access (February 2017)

TABLE I MODES AND SWITCHING SCHEME FOR ONE COMPLETE CYCLE

| MODE | Status of Switches |    |           |    |    |           |           |           |    |      |

|------|--------------------|----|-----------|----|----|-----------|-----------|-----------|----|------|

|      | <b>S1</b>          | S2 | <b>S3</b> | S4 | S5 | <b>S6</b> | <b>S7</b> | <b>S8</b> | S9 | - Vo |

| 1    | 0                  | 0  | 0         | 1  | 0  | 0         | 1         | 0         | 1  | 0V   |

| 2    | 0                  | 0  | 0         | 1  | 0  | 1         | 0         | 0         | 1  | 1V   |

| 3    | 0                  | 0  | 0         | 1  | 1  | 0         | 0         | 0         | 1  | 2V   |

| 4    | 0                  | 1  | 0         | 0  | 0  | 0         | 1         | 1         | 0  | 3V   |

| 5    | 0                  | 1  | 0         | 0  | 0  | 1         | 0         | 1         | 0  | 4V   |

| 6    | 0                  | 1  | 0         | 0  | 1  | 0         | 0         | 1         | 0  | 5V   |

| 7    | 0                  | 0  | 0         | 1  | 0  | 0         | 1         | 1         | 0  | 6V   |

| 8    | 0                  | 0  | 0         | 1  | 0  | 1         | 0         | 1         | 0  | 7V   |

| 9    | 0                  | 0  | 0         | 1  | 1  | 0         | 0         | 1         | 0  | 8V   |

| 10   | 0                  | 0  | 1         | 0  | 1  | 0         | 0         | 1         | 0  | 0V   |

| 11   | 0                  | 0  | 1         | 0  | 0  | 1         | 0         | 1         | 0  | -1V  |

| 12   | 0                  | 0  | 1         | 0  | 0  | 0         | 1         | 1         | 0  | -2V  |

| 13   | 1                  | 0  | 0         | 0  | 1  | 0         | 0         | 0         | 1  | -3V  |

| 14   | 1                  | 0  | 0         | 0  | 0  | 1         | 0         | 0         | 1  | -4V  |

| 15   | 1                  | 0  | 0         | 0  | 0  | 0         | 1         | 0         | 1  | -5V  |

| 16   | 0                  | 0  | 1         | 0  | 1  | 0         | 0         | 0         | 1  | -6V  |

| 17   | 0                  | 0  | 1         | 0  | 0  | 1         | 0         | 0         | 1  | -7V  |

| 18   | 0                  | 0  | 1         | 0  | 0  | 0         | 1         | 0         | 1  | -8V  |

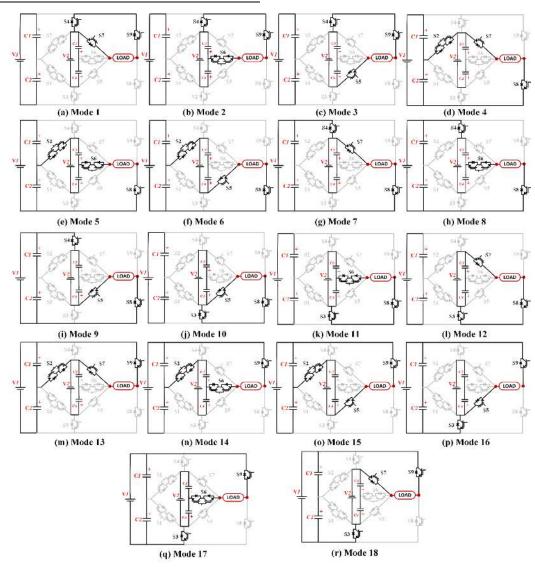

During the positive half cycle of output voltage with input voltage ( $V_1$ =6V,  $V_2$ =2V), where V is the voltage across the dc-link capacitor), voltage levels 0V, 1V, 2V, 3V, 4V, 5V, 6V, 7V, 8V are generated by modes 1, 2, 3, 4, 5, 6, 7, 8, 9 respectively. During mode 1, S4, S7, S9 switches are ON, and S1, S2, S3, S5, S6, S8 switches are OFF. It generates output voltage level 0 V. On mode 2, S4, S6, S9 switches are ON, and S1, S2, S3, S5, S7, S8 switches are OFF. During this mode, the circuit generates output voltage level 1V and so on. Similarly, during the negative half cycle, voltage levels 0V, -1V, -2V,-3V, -4V, -5V, -6V, -7V and -8V are generated by modes 10, 11, 12, 13, 14, 15, 16, 17 and 18 respectively. Fig. 2 shows the circuit configuration and current flow path during different modes of operation.

FIGURE 2. Circuit Configuration of the proposed topology during different modes of operation in one complete cycle.

## A. TOTAL STANDING VOLTAGE CALCULATION

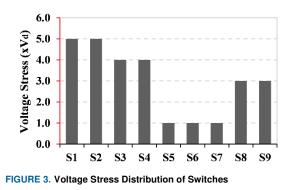

The cost of the inverter indirectly controls the rating of switches. Lowering the switches' rating less costly will be the switches, which is only feasible if the voltage to be blocked by the switch is not high. The voltage stress on different switches should be determined. The amount of voltage stress on all switches can be referred to as Total standing voltage (TSV). An indication of switch rating in topology is a lower estimate of TSV. For the above topology and considering the voltage ratio of the DC sources, i.e. V1:V2 = 3:1, different switches experience different peak withstanding voltage which can be categorized as follows:

Category 1:  $V_{S1} = V_{S2} = 2(V_1/2 + V_2) = 5V_d$ Category 2:  $V_{S3} = V_{S4} = V_1 + V_2 = 4V_d$ Category 3:  $V_{S5} = V_{S7} = V_2 = V_d$ Category 4:  $V_{S6} = 2(V_2/2) = V_d$ Category 5:  $V_{S8} = V_{S9} = V_1 = 3V_d$

Total Standing Voltage (TSV) can be obtained as [24]:

$$TSV = V_{S1}+V_{S2}+V_{S3}+V_{S4}+V_{S5}+V_{S6}+V_{S7}+V_{S8}+V_{S9}$$

= 5V\_d+5V\_d+4V\_d+4V\_d+V\_d+V\_d+3V\_d+3V\_d

or, TSV = 27V\_d (1)

Sometimes, per-unit TSV, which is the ratio of TSV and the maximum output voltage, is also calculated. In this case,

Per Unit TSV, TSV (pu) = TSV/(Peak Output Voltage)

=

$$27V_d/8V_d = 3.375 \text{ pu}$$

(2)

Fig. 3 depicts the stress distribution of the different Switches used in the proposed inverter topology.

#### **B. CAPACITOR SIZING AND INRUSH CURRENT**

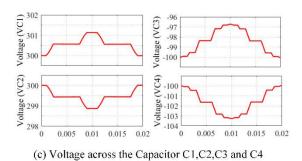

The size of the capacitor is an important factor in determining the feasibility of the converter. The capacitor size depends upon the energy required to handle by the capacitor in one cycle. Considering Fig. 7(c), it can be seen that the maximum discharging period of each capacitor is the same. Also, it is noticed that during half cycle, one of the capacitors pair is charged, and another pair is discharged. This process reverses for the rest of the half-cycle. Thus, the capacitance of the capacitors is the same. Considering the Capacitor C<sub>1</sub>, it is discharged for the interval  $[\pi-2\pi]$ . During this period, the change in charge of capacitor C1 is depicted as below:

$$\Delta Q_1 = \int_{\pi}^{2\pi} \frac{i_L}{\omega} d(\omega t) \tag{3}$$

Where  $i_L$  is the load current. For a resistive load of R, the charge ripple becomes,

$$\Delta Q_1 = \frac{8v_d}{2\pi f_s R} (2\pi - \pi) = \frac{4v_d}{f_s R}$$

(4)

Where  $f_s$  is the switching frequency, R is the resistive load applied, and Vd is the voltage step chosen so as  $8v_d$  represent the peak output voltage. For capacitor C<sub>1</sub>, the maximum voltage ripple can be calculated by equation (5), and the optimum size of the capacitor is calculated using (6). Similarly, the capacitor size is calculated for the rest of the capacitors.

$$\Delta V_{rip} = \frac{4v_d}{f_c R C_1} \tag{5}$$

$$opt. C_1 = \frac{\frac{4v_d}{f_s R \Delta V_{rip}}}{(6)}$$

For every cycle, each of the capacitors is charged and discharged. The inrush current can cause the breaking of switches involved in its path if it is not controlled and appropriately analyzed. The inrush current mainly depends on the maximum voltage difference between the capacitor voltage and the source providing the charge and various circuit parameters involved in the charging loop. The peak value of charging current (I<sub>charging\_max</sub>) is related to the maximum voltage difference,  $\Delta V_{max}$ , as follows [32]:

$$I_{charging\_max} \approx \frac{\Delta V_{max}}{r_p}$$

(7)

Where  $r_p$  is the total parasitic resistance of all the charging loop components, this maximum inrush charging current can be handled by inserting a small inductance  $L_r$  in the charging loop.  $L_r$  can be modelled based on the maximum inrush charging current. It acts as a short circuit during the steadystate operation, and during the transients, it protects against the maximum charging current. It reduces the peak of inrush charging current and provides di/dt protection. To avoid any negative impact, the value of this inductance is kept reasonably small and set below 1µH.

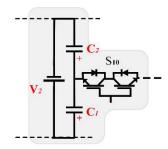

#### C. CAPACITOR CHARGE BALANCING

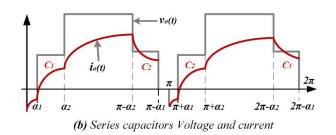

The self-balancing nature of two series capacitors connected across a DC source, shown in Fig. 4(a), depends upon the average power dissipated and absorbed by the capacitors during one complete cycle. It can be calculated as in [28,32]. The typical current and voltage waveforms for these series capacitors are depicted in Fig. 4(b). The figure shows that the voltage and current waveform follow the same path for the interval  $[0-\pi]$  and the  $[\pi-2\pi]$ . The current-voltage for  $[\alpha_1-\alpha_2]$ and  $[(\pi+\alpha_1) - (\pi+\alpha_2)]$  are precisely similar. Thus, the area

under the curve, i.e. power, remain the same. During halfcycle, one capacitor is charged while the other is utilized, and during the next half-cycle, the other capacitor is utilized. This is also evident from obtained results shown in Fig 7(c) for the proposed topology. In light of the above discussion and Fig. 4, the following equations can be materialized:

$$\int_{\alpha_1}^{\alpha_2} [i_o(t)v_o(t).d\omega t] = \int_{\pi+\alpha_1}^{\pi+\alpha_2} [i_o(t).v_o(t).d\omega t]$$

(8)

And,

$\int_{\pi-\alpha_2}^{\pi-\alpha_1} [i_o(t)v_o(t).\,d\omega t] = \int_{2\pi-\alpha_2}^{2\pi-\alpha_1} [i_o(t).\,v_o(t).\,d\omega t] \,(9)$

For the above equations, it should be noted that  $v_o$  and  $i_o$ represent the voltage and current waveform corresponding to the cell shown in Fig. 4 (a) only and does not mean the output voltage and current of the converter. Thus, the average power during the various intervals remains the same and maintaining the voltage across the capacitors. During the interval  $[(\pi - \alpha_1) - \alpha_1]$  $\pi$ ], the current falls to zero as, during this interval, the capacitors are cut off from the current path. This describes the voltage balancing for the series capacitors with a DC source acting independently.

(a) Basic cell of DC source with series capacitors

#### FIGURE 4. Self Balancing of Series Capacitors

#### D. COST ANALYSIS OF THE CIRCUIT

The cost function of a topology approximates its implementation feasibility. It depends upon various factors like the number of semiconductors used (N<sub>IGBT</sub>), number of DC sources utilized (N<sub>DC</sub>), number of driver circuits utilized (N<sub>Dr</sub>), number of capacitors used (N<sub>cap.</sub>), number of diodes used (N<sub>d</sub>) and the TSV<sub>pu</sub>. The cost function can be calculated as follows [25]:

$$CF = N_{IGBT} + N_{DC} + N_{cap} + N_{Dr} + N_d + \alpha TSV_{pu}$$

(10)

Where  $\alpha$  is the weighting coefficient for the TSV. Since the proposed topology lacks any diode, N<sub>d</sub> can be ignored, and the cost factor, CF, can be calculated as:

$$CF = N_{IGBT} + N_{DC} + N_{cap} + N_{Dr} + \alpha TSV_{pu}$$

(11)

$\alpha$  can be selected greater than unity when more importance is required for the TSV. For moderate attention to TSV, it is chosen as between 0 and unity. For the former,  $\alpha$  is selected as 1.5, and for the latter case, it is chosen 0.5.

For,

$$\alpha = 1.5$$

,

$CF = 12+2+4+9+(1.5\times3.375) = 32.06$

$CF/Level = 32.06/17 = 1.88$  (12)

Fe

or,

$$\alpha = 0.5$$

,

$CF = 12+2+4+9+(0.5\times3.375) = 28.69$

$CF/Level = 28.69/17 = 1.69$  (13)

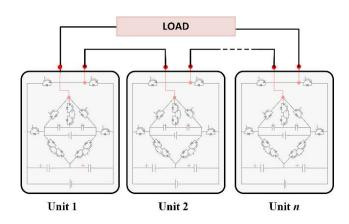

#### E. CASCADED STRUCTURE

The basic unit of the proposed topology can be easily cascaded, as shown in Fig. 5. The generalized structure of the proposed topology is extended by using n-series connected basic units. The optimal generalized structures of proposed topology, regarding several factors such as number of switches  $(N_{sw})$ , number of dc sources  $(N_{dc})$ , number of capacitors  $(N_{cap})$ , number of gate driver circuit (Ngd) and total standing voltage (TSV) on the switches are also obtained and formulated. Formulated expressions based on the number of levels generated (N<sub>L</sub>) are given below:

$$N_{dc} = (N_L - 1)/8$$

(14)

$$N_L = 2(N_L - 1)/4$$

(15)

$$N_{sw} = 5(N_L - 1)/4$$

(15)

$$N_{cap} = (N_L - 1)/4$$

(16)

$$N_{gd} = 9(N_L - 1)/16$$

(17)

$$TSV = (N_L - 1)/30$$

(18)

FIGURE 5. Cascaded Structure of the Topology

Author Name: Preparation of Papers for IEEE Access (February 2017)

#### **III. SIMULATION ANALYSIS AND DISCUSSION**

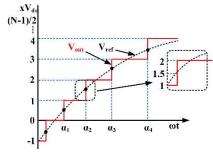

The Above topology is designed and simulated in the Matlab/Simulink environment and checked for both linear and non-linear load. For linear load, the circuit performance is analyzed for static and dynamic conditions. The value of the dc sources in simulation analysis is taken as 100V and 300V. IGBTs were used as switches. Although there are many different switching techniques available in the literature for switching and control due to the ease of implementation, Nearest Level control (NLC) is used in this work. Fig. 6 depicts the realization of the NLC algorithm as well as the switching strategy [27]. In the following section, analysis under different loading conditions and results obtained were presented and discussed in detail.

(a) Waveform synthesis of NLC

(b). Switching pulses generation FIGURE 6. Switching pulses generation implementing NLC algorithm

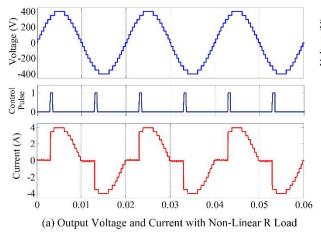

#### A. FIXED LOADING CONDITION

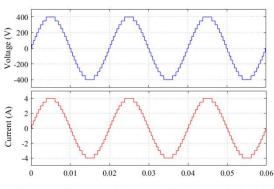

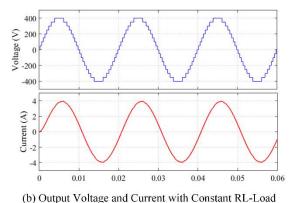

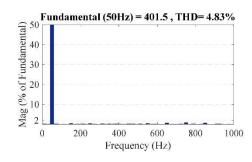

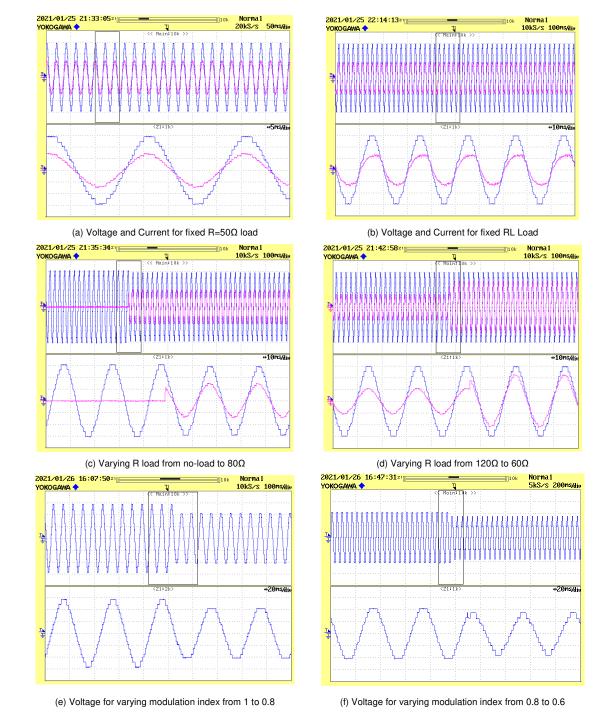

Under fixed loading conditions, constant R and RL load is considered. This kind of load can be found for household applications like heating elements, which emulate constant and varying R and RL loads. Using a fixed resistive load of R=100 $\Omega$ , the obtained output voltage and current waveforms are shown in Fig. 7(a). By using a constant RL load of Z=100 $\Omega$ +80mH, the obtained output voltage and current waveforms are shown in Fig. 7(b). By FFT analysis, it is reported that the THD of the output voltage is 4.83%. In both cases, the lower order harmonics are less than 5%.

#### B. CAPACITOR CHARGING AND DISCHARGING

The proposed topology consists of four DC link capacitors, two for each dc source.  $C_1$ ,  $C_2$  are connected in series across  $V_1$ , and  $C_3$ ,  $C_4$  are connected across  $V_2$ . To maintain equal charging and discharging times, the capacitors  $C_1$  and  $C_2$  are of equivalent capacitance. The same is true for  $C_3$  and  $C_4$ . Fig. 7(c) shows the voltage across each capacitor during one complete cycle. The voltages across  $C_1$  and  $C_2$  are complementary to each other. If one is charging, the other is discharging, but the net energy transfer in one complete cycle across both the capacitors is zero; thus, capacitors are selfbalancing. The same is true for the  $C_3$  and  $C_4$ .

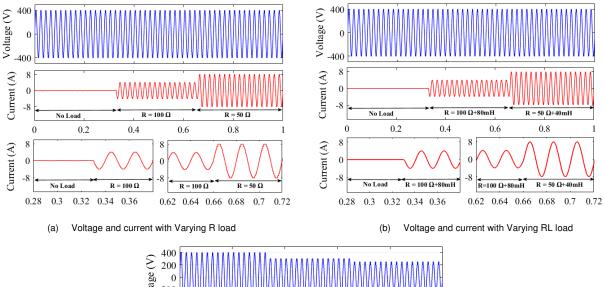

#### C. VARYING R AND RL LOAD

In real applications, the dynamic change in load condition is a widespread phenomenon. The dynamic load can either be a change in the R-type of load or RL-type of load. For example, heating loads such as heating furnaces and heating element used for room heating can be treated as R loads. Temperature change requires a change in R of the heating element. Thus, the heaters of the household can act as an R-type load of varying nature. The sudden change of load can occur in case of fault. Varying RL load can also be emulated during speed control of the motor. Therefore it becomes necessary to validate the performance of the proposed inverter topology for such type of dynamic loading conditions. The performance is assessed by the load's variation from the no-load condition to the gradual increment. This checks the stability of the topology in case of a sudden change of load. Fig. 8(a) and 8(b) depict the output voltage and current waveforms for the sudden change in R and RL load conditions, respectively. It can be seen in both cases that the voltage remains the same, and only the current waveform is changed as the load is changed. The transition in the current waveform is also smooth, as can be seen.

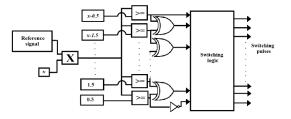

#### D. VARYING MODULATION INDEX

Fig. 8(c) shows the effect on voltage waveform due to the modulation index's variation from M=1 to 0.8 and then to 0.6. Decreasing the modulation index reduces the generated output voltage levels. As the modulation index reduced from 1 to 0.8, the output voltage levels also decreased from 17 to 13 and then finally reach 11 levels as the modulation index is further reduced to 0.6. This condition simulate a sudden fault in the control circuitry and check the dynamic stability of the circuit.

Author Name: Preparation of Papers for IEEE Access (February 2017)

(a) Output Voltage and Current with Constant R Load

(d) FFT analysis and THD in Voltage

FIGURE 7. Simulation results obtained for the proposed topology with constant R and RL load condition

FIGURE 8. Simulation results obtained with changing load and modulation Index

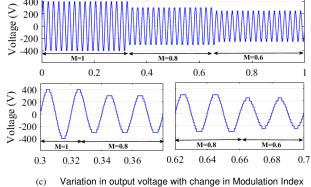

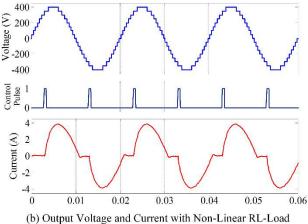

FIGURE 9. Simulation results obtained with Non-Linear Load

# E. Non-Linear Load

In many applications, the inverter is required to feed nonlinear loads such as variable speed control drives, rectifiers, computers, SMPS, etc. Unlike linear load, the current drawn by the non-linear load is non-sinusoidal. And the voltage and current don't follow proportional relation. Therefore it is vital to validate the performance of the inverter under non-linear loading condition. In this section, the performance of the inverter is evaluated considering two different non-linear loading conditions. First, the load is taken as a simple switched resistive load and is realized by a resistive impedance (R=100 ohm) connected in series with an AC phase controller (Triac). The second load considered is a variable speed control drives load and is realized as an inductive impedance (RL=100ohm+80mH) connected in series with an AC phase controller (Triac). Voltage and current waveforms for both the loading conditions are shown in Fig. 9. The analysis validates the performance and proper operation of the proposed topology with linear and non-linear loading conditions.

# **IV. HARDWARE IMPLEMENTATION**

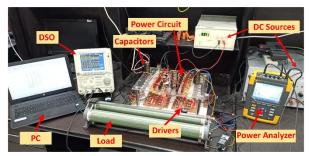

For hardware validation, a prototype of the proposed circuit is prepared in the laboratory environment. IGBTs model FGA25N120 are used as switches in the proposed circuit. The control signals are generated by using the DSP board TMS320F28379D microcontroller. For driving the IGBTs a driver circuit, TLP 250H based is utilized. Regulated dc power supplies, Scientech 4180, having a maximum channel voltage rating of 30V (individual channel) and 60V (channel in series), are used as dc sources. For the experimental validation of the circuit, the magnitude of the dc sources V1 and V2 are set to 45V and 15V, respectively. Resistive load of 50  $\Omega$  and an inductive load of 50  $\Omega$ +60mH are taken as fixed load. Load specifications for varying load and modulation index

conditions are specified in Fig. 8. Different voltage and current waveforms are recorded using Yokogawa DL 1640 digital oscilloscope. The hardware setup prepared in the laboratory is shown in Fig. 10.

Fig. 11 presents the results obtained through the hardware analysis of the proposed topology. The output voltage and current waveforms for the pure R load of  $50\Omega$  are shown in Fig. 11(a). It can be seen that all the levels are stable and precise. Also, it is noticed that the current and voltage are in phase. Fig. 11(b) depicts the trace for static RL load. An inductive RL load of  $50\Omega$ +60mH is connected, and the current and voltage waveforms are traced. The current lags behind the voltage waveform due to the inductive effect. In Fig. 11(c) and 11(d), the load is changed from no-load to  $80\Omega$  and from  $120\Omega$ to  $60\Omega$ , respectively. The current remains in phase with the voltage waveform, but the magnitude is increased, as evident from the figures. Fig. 11(e) and 11(f) depict the effect of changing the modulation index on the output voltage. The modulation index is changed from 1 to 0.8 and from 0.8 to 0.6. As a result, the levels in the output waveform are reduced from 17 to 13 to 11 levels. Thus, the hardware results validate the performance and implementation feasibility of the proposed circuit.

FIGURE 10. Photograph of the hardware setup in the Laboratory

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/ACCESS.2021.3077968, IEEE Access

**IEEE**Access

Author Name: Preparation of Papers for IEEE Access (February 2017)

FIGURE 11. Hardware results with different load and varying modulation Index conditions

# V. POWER LOSS ANALYSIS

The loss calculation for a converter is a crucial criterion for evaluating the converter's performance as it directly affects the converter's efficiency. There are mainly two types of losses associated with a converter, conduction losses and switching losses. Conduction losses are associated with the conduction current, i(t) and turn on resistance RT and RD where T and D represent Transistor and Diode. Since a switch is a combination of Transistor with antiparallel diode, both are considered to calculate losses. Thus, both the losses can be estimated as below [28,32]:

$$p_{c,T}(t) = \left[ V_T + R_T i^{\beta}(t) \right] i(t)$$

(19)

$$p_{c,D}(t) = \left[ V_D + R_D i^\beta(t) \right] i(t) \tag{20}$$

Where  $\beta$  is a constant related to the Transistor specifications and can be noted from the Datasheet, the total conduction losses of a switch are the sum of the two equations above. The average conduction loss of a converter depends upon the number of transistors and diodes conducting instantly. Considering N<sub>T</sub> transistors and N<sub>D</sub> diodes are conducting at an instant t, then the average conduction loss will be

$$P_c = \frac{1}{2\pi} \int_0^{2\pi} [N_T(t)p_{c,T}(t) + N_D(t)p_{c,D}(t)]dt \qquad (21)$$

The switching losses comprise turn off losses and turn of

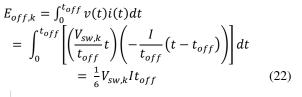

The switching losses comprise turn-off losses and turn-on losses and depend on the energy dissipated during each process. These can be calculated as below:

Similarly,

$$E_{on,k} = \int_{0}^{t_{on}} v(t)i(t)dt = \int_{0}^{t_{on}} \left[ \left( \frac{V_{sw,k}}{t_{on}} t \right) \left( -\frac{l'}{t_{on}} (t - t_{on}) \right) \right] dt = \frac{1}{6} V_{sw,k} l' t_{on}$$

(23)

Where  $E_{off,k}$  and  $E_{on,k}$  are the energy loss during the turn-off and turn-on period of the kth switch. And  $t_{off}$  and  $t_{on}$  is the turn-off and turn-on time while t is the period, I is the current through the switch just before turning off, and I' is the current through the switch just after turning it on,  $V_{sw,k}$  is the voltage of the switch after it is turned off. The power loss due to switching transitions in one complete cycle can be written as:  $P_{sw} = f \sum_{k=1}^{N_{switch}} \left( \sum_{i=0}^{N_{on,k}} E_{on,ki} + \sum_{i=0}^{N_{off,k}} E_{off,ki} \right)$  (24)

Where f is the fundamental frequency,  $N_{on,k}$  and  $N_{off,k}$  are the number of times  $k^{th}$  switch turn on or turn off in one fundamental cycle. Finally, total losses are given as:

$$P_{total \ loss} = P_c + P_{sw} \tag{25}$$

FIGURE 12. Power losses and efficiency of the proposed inverter topology with different loading conditions

IEEE ACCESS' Author Name: Preparation of Papers for IEEE Access (February 2017)

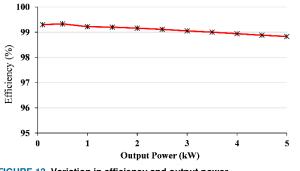

FIGURE 13. Variation in efficiency and output power

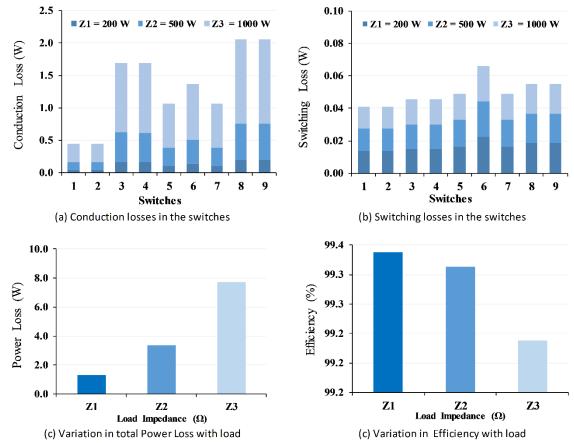

The above equations are simulated to calculate the losses and, in turn, the efficiency of the circuit through thermal modelling using PLECS software. Conduction losses and switching losses are calculated for different loads shown in Fig. 12(a) and 12(b), respectively. Three different power rating loads are considered for the analysis as Z1=200W (400 $\Omega$ ), Z2=500W  $(150\Omega+70\text{mH})$ , and Z3=1kW ( $60\Omega+100\text{mH}$ ). The switching losses are smaller than the conduction losses due to the low switching frequency. Efficiency and total power for three different loads are calculated and are shown in Fig. 12(c) and 12(d). The inverter's efficiency with the change in rated output power is analyzed and shown in Fig. 13. Maximum efficiency of 99.37% is obtained at 200W load, and a slight decrease in efficiency is noted with the increase in output power.

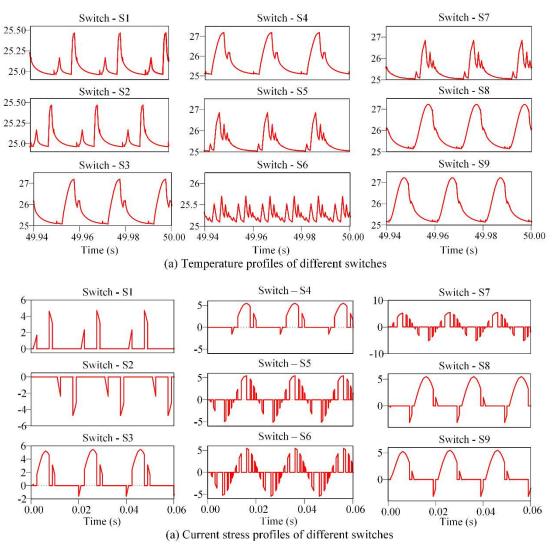

The current stress and temperature profile of the switches used in the proposed topology are shown in Fig. 14. Both the parameter is very much helpful in selecting proper rating switches for different application. The temperature profiles are obtained by thermal analysis of the proposed circuit. Fig 14(a) presents the temperature profiles of all the switches when the inverter is feeding a 1kW output load. To further enhance the selection criterion of the IGBTs, Fig. 14(b) depicts the current stress of different switches utilized.

FIGURE 14. Current stress and temperature profiles of the switches

VOLUME XX, 2017

## VI. DISCUSSION AND COMPARATIVE ANALYSIS

The above simulation and hardware results confirm the static as well as dynamic response of the proposed circuit. It performs reliably in sudden load change or load power factor change with no spike or latching of any kind. Moreover, the capacitors are self-balancing, thus reduced the complexity of balancing. The loss analysis shows that for  $Z_3 = 1$ kW, the circuit has the highest power losses due to the high conduction current. The claim of better performance of the proposed topology is further validated by comparing it with other seventeen-level topologies present in the literature. Comparison in terms of different parameters with other topologies has been carried out, and the results obtained from the analysis are tabulated in Table II.

The parameters taken for the comparison are the Number of IGBT used ( $N_{IGBT}$ ), Number of DC sources used ( $N_{dc}$ ), Number of Gate Drivers ( $N_{Dr}$ ), number of capacitors used ( $N_{cap}$ ), Cost factors per level and per unit TSV are compared. Since the topologies compared have different IGBT ( $N_{IGBT}$ ),  $N_{I}/N_{IGBT}$  ratio is used. Variety of DC sources ( $N_v$ ) and Maximum Blocking Voltage per unit (MBV<sub>p.u.</sub>) are also compared to present a fair and extensive comparison. Gate drivers add to the cost, so they are also used in the comparison. Finally, TSV is an essential aspect of the topology as it helps in deciding the switch ratings. Higher the switch rating, more would be its cost, so the TSV is also used to compare.

The proposed topology utilizes 12 IGBTs. Although the topologies in [22,29,31] use a lower number of IGBTs and driver circuits than the proposed circuit, the TSV<sub>p,u</sub> is significantly higher than the TSV<sub>p.u</sub> of the proposed MLI. Also, the MBVp.u. of the proposed topology is lower. The topology in [19] has the lowest TSV pu of 2.75 only, but it utilizes 4 DC sources and 16 IGBTs to produce the 17 level output. Though with a slight change in the DC source magnitude, it can produce 49 level output with the same IGBTs. The MLI in [30] has the best performance in terms of TSV and MBV p.u. but it utilizes 14 IGBTs, and its cost factor per level is higher. The MLI in [31] has the best Cost Factor per level among all the topologies present in the comparison, but it has higher TSV and MBV p.u. Though it is not very high, the proposed topology has lower TSV and MBV while having a comparable Cost Factor per level.

From the analysis, it can be said that the proposed topology offers a better trade-off between all the parameters. This asserts the implementation feasibility of the proposed circuit. The above discussion asserts the advantages of the proposed topology. One of the main limitations of the proposed structure is the utilization of bi-directional switches, which adds to the device count and increases the TSV p.u. Although MLIs find application in various fields, integrating renewable resources into the utility grid is one of the most prominent applications [8]. The proposed topology based on the above discussion is suitable for solar PV applications.

| Tanalaan (Daf) | N               |                |    | N <sub>I</sub> /N <sub>IGBT</sub> | N <sub>Dr</sub> | N <sub>cap</sub> . | TSV <sub>p.u.</sub> | MBV <sub>p.u.</sub> - | CF/Level |                |

|----------------|-----------------|----------------|----|-----------------------------------|-----------------|--------------------|---------------------|-----------------------|----------|----------------|

| Topology [Ref] | N <sub>dc</sub> | N <sub>v</sub> |    |                                   |                 |                    |                     |                       | α = 1.5  | $\alpha = 0.5$ |

| [19]           | 4               | 2              | 16 | 1.06                              | 14              | 4                  | 2.75                | 1.00                  | 4.02     | 3.38           |

| [20]           | 4               | 2              | 12 | 1.42                              | 09              | 0                  | 6.00                | 1.00                  | 2.00     | 1.66           |

| [21]           | 4               | 2              | 12 | 1.42                              | 10              | 0                  | 5.50                | 1.67                  | 2.01     | 1.70           |

| [22]           | 4               | 2              | 10 | 1.70                              | 08              | 0                  | 6.00                | 1.00                  | 1.82     | 1.47           |

| [29]           | 4               | 2              | 10 | 1.70                              | 10              | 0                  | 4.50                | 1.00                  | 1.81     | 1.54           |

| [30]           | 6               | 1              | 14 | 0.93                              | 14              | 0                  | 2.00                | 0.50                  | 2.84     | 2.40           |

| [31]           | 4               | 2              | 10 | 1.70                              | 10              | 0                  | 4.00                | 0.75                  | 1.77     | 1.53           |

| [14]           | 2               | 2              | 18 | 0.94                              | 14              | 4                  | 6.00                | 1.00                  | 5.52     | 4.82           |

| [ <b>P</b> ]   | 2               | 2              | 12 | 1.42                              | 09              | 4                  | 3.375               | 0.625                 | 1.88     | 1.69           |

TABLE II

Comparison of Proposed Topology with other seventeen level topologies

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/ACCESS.2021.3077968, IEEE Access

**IEEE**Access

#### **VII. CONCLUSION**

This paper presented an improved asymmetrical multilevel inverter topology. The proposed topology generates seventeen output voltage levels by utilizing two DC sources and nine switches; three of these switches are bidirectional switches. The concept of a dc-link capacitor across the sources is used to increase the output levels. The capacitors are self-balancing, and no extra effort is required for the balancing operation of the capacitors. The results obtained for different load conditions confers the static and dynamic stability of the topology. Moreover, power loss analysis gives insight into the dynamics of the switches used. Based on the comparative analysis, it can be concluded that the proposed topology offers superior performance than other compared topologies present in the literature. The topology is highly efficient and is much suitable for renewable energy applications like grid-tied solar PV systems.

#### ACKNOWLEDGMENT

J. Rodriguez acknowledges the support of AND through projects FB0008, ACT192013 and 1210208

#### REFERENCES

- Fang, Jingyang, Zhongxi Li, and Stefan M. Goetz. "Multilevel converters with symmetrical half-bridge submodules and sensorless voltage balance." *IEEE Transactions on Power Electronics* 36.1 (2020): 447-458.

- [2] E. Babaei, S. Laali and Z. Bayat, "A Single-Phase Cascaded Multilevel Inverter Based on a New Basic Unit With Reduced Number of Power Switches," in *IEEE Transactions on Industrial Electronics*, vol. 62, no. 2, pp. 922-929, 2015.

- [3] Anderson, Jon Azurza, et al. "Three Levels Are Not Enough: Scaling Laws for Multilevel Converters in AC/DC Applications." *IEEE Transactions on Power Electronics* 36.4 (2020): 3967-3986.

- [4] Rodriguez, J., Jih-Sheng, L., and Fang Zheng, P., 'Multilevel Inverters: A Survey of Topologies, Controls, and Applications', *IEEE Transactions on industrial electronics*, 2002, 49, (4), pp. 724-738.

- [5] Mustafa, Uvais, et al. "Single Phase Seven-Level Inverter topology with Single DC Source and Reduce Device Count for Medium and High-Power Applications." 2019 Innovations in Power and Advanced Computing Technologies (i-PACT). Vol. 1. IEEE, 2019.

- [6] Salem, A., Khang, H.V., Robbersmyr, K.G., Norambuena, M., and Rodriguez, J., 'Voltage Source Multilevel Inverters with Reduced Device Count: Topological Review and Novel Comparative Factors', *IEEE transactions on power electronics*, 2021, 36, (3), pp. 2720-2747.

- [7] Arif, M. Saad Bin, Shahrine Md Ayob, and Zainal Salam. "A new asymmetrical multilevel inverter topology with reduced device counts." 2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES). IEEE, 2016.

- [8] Mustafa, Uvais, et al. "Efficiency improvement of the solar PVsystem using nanofluid and developed inverter topology." *Energy Sources, Part A: Recovery, Utilization, and Environmental Effects* (2020): 1-17.

- [9] Wu, Mingzhe, Yun Wei Li, and Georgios Konstantinou. "A Comprehensive Review of Capacitor Voltage Balancing Strategies for Multilevel Converters Under Selective Harmonic Elimination

PWM." *IEEE Transactions on Power Electronics* 36.3 (2020): 2748-2767.

- [10] Babaei, Ebrahim, et al. "Reduction of dc voltage sources and switches in asymmetrical multilevel converters using a novel topology." *Electric Power Systems Research* 77.8 (2007): 1073-1085.

- [11] Manjrekar, Madhav D., and Thomas A. Lipo. "A hybrid multilevel inverter topology for drive applications." APEC'98 Thirteenth Annual Applied Power Electronics Conference and Exposition. Vol. 2. IEEE, 1998.

- [12] Manjrekar Madhav D, Peter KSteimer, Lipo Thomas "A Hybrid multilevel power conversion system: a competitive solution for high-power applications" *IEEE Trans. Ind. Appl.* 2000; 36(3):834– 41

- [13] Ounejjar, Youssef, Kamal Al-Haddad, and Luc-Andre Gregoire. "Packed U cells multilevel converter topology: theoretical study and experimental validation." *IEEE Transactions on Industrial Electronics* 58.4 (2010): 1294-1306.

- [14] Barzegarkhoo, Reza, et al. "A new boost switched-capacitor multilevel converter with reduced circuit devices." *IEEE Transactions on Power Electronics* 33.8 (2017): 6738-6754.

- [15] Taghvaie, Amir, Jafar Adabi, and Mohammad Rezanejad. "A multilevel inverter structure based on a combination of switchedcapacitors and DC sources." *IEEE Transactions on Industrial Informatics* 13.5 (2017): 2162-2171.

- [16] Siddique, Marif Daula, et al. "Switched-capacitor-based boost multilevel inverter topology with higher voltage gain" *IET Power Electronics* 13.14 (2020): 3209-3212.

- [17] Lee, Sze Sing, et al. "Hybrid cascaded multilevel inverter (HCMLI) with improved symmetrical 4-level submodule." *IEEE Transactions on Power Electronics* 33.2 (2017): 932-935.

- [18] Siddique, Marif Daula, et al. "A new configurable topology for multilevel inverter with reduced switching components." *IEEE Access* 8 (2020): 188726-188741.

- [19] Dhanamjayulu, C., Prasad, D., Padmanaban, S., Maroti, P.K., Holm-Nielsen, J.B., and Blaabjerg, F., 'Design and Implementation of Seventeen Level Inverter with Reduced Components', *IEEE Access*, 2021, 9, pp. 16746-16760.

- [20] E. Samadaei, A. Sheikholeslami, S. A. Gholamian and J. Adabi, "A Square T-Type (ST-Type) Module for Asymmetrical Multilevel Inverters," in *IEEE Transactions on Power Electronics*, vol. 33, no. 2, pp. 987-996, 2018.

- [21] R. S. Alishah, S. H. Hosseini, E. Babaei and M. Sabahi, "A New General Multilevel Converter Topology Based on Cascaded Connection of Submultilevel Units With Reduced Switching Components, DC Sources, and Blocked Voltage by Switches," in *IEEE Transactions on Industrial Electronics*, vol. 63, no. 11, pp. 7157-7164, 2016.

- [22] R. S. Alishah, S. H. Hosseini, E. Babaei, and M. Sabahi, "Optimal design of new cascaded switch-ladder multilevel inverter structure," *IEEE Trans. Ind. Electron.*, vol. 64, no. 3, pp. 2072– 2080, Mar. 2017.

- [23] Jagabar Sathik, M, Prabaharan, N, Ibrahim, SAA, Vijaykumar, K, Blaabjerg, F, "A new generalized switched diode multilevel inverter topology with reduced switch count and voltage on switches", *Int J Circ Theor Appl. 2020*; 48: 619–637.

- [24] Siddique, M. D., Mekhilef, S., Shah, N. M., & Memon, M. A. (2019). Optimal design of a new cascaded multilevel inverter topology with reduced switch count. *IEEE Access*, 7, 24498-24510.

- [25] Siddique, M. D., Mekhilef, S., Shah, N. M., Sarwar, A., Iqbal, A., & Memon, M. A. (2019). A new multilevel inverter topology with reduce switch count. *IEEE Access*, 7, 58584-58594.

- [26] Siddique, M. D., Mekhilef, S., Shah, N. M., Sarwar, A., Iqbal, A., Tayyab, M., & Ansari, M. K. (2019). Low switching frequency based asymmetrical multilevel inverter topology with reduced switch count. *IEEE Access*, 7, 86374-86383.

- [27] Meshram, Prafullachandra M., and Vijay B. Borghate. "A simplified nearest level control (NLC) voltage balancing method

for modular multilevel converter (MMC)." *IEEE Transactions on Power Electronics* 30.1 (2014): 450-462.

- [28] Babaei, Ebrahim, Mohammad Farhadi Kangarlu, and Mehran Sabahi. "Extended multilevel converters: an attempt to reduce the number of independent DC voltage sources in cascaded multilevel converters." IET Power Electronics 7.1 (2014): 157-166.

- [29] Ali, J. S. M., Alishah, R. S., Sandeep, N., Hosseini, S. H., Babaei, E., Vijayakumar, K., & Yaragatti, U. R. (2018). A new generalized multilevel converter topology based on cascaded connection of basic units. *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 7(4), 2498-2512.

- [30] Ali, J. S. M., Alishah, R. S., & Krishnasamy, V. (2018). A new generalized multilevel converter topology with reduced voltage on switches, power losses, and components. *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 7(2), 1094-1106.

- [31] Siddique, M. D., Mekhilef, S., Shah, N. M., Sarwar, A., & Memon, M. A. (2020). A new single-phase cascaded multilevel inverter topology with reduced number of switches and voltage stress. *International Transactions on Electrical Energy Systems*, 30(2), e12191.

- [32] Arif, M. S. B., Mustafa, U., Siddique, M. D., Ahmad, S., Iqbal, A., Ashique, R. H., & Ayob, S. B. (2021) "An improved asymmetrical multilevel inverter topology with boosted output voltage and reduced components count". *IET Power Electronics, early access, doi: 10.1049/pel2.12119*.

- [33] Kakar, S., Ayob, S.B.M., Iqbal, A., Nordin, N.M., Arif, M.S.B., and Gore, S., 'New Asymmetrical Modular Multilevel Inverter Topology with Reduced Number of Switches', *IEEE Access*, 2021, 9, pp. 27627-27637.

- [34] Prasad, D., Dhanamjayulu, C., Padmanaban, S., Holm-Nielsen, J.B., Blaabjerg, F., and Khasim, S.R., 'Design and Implementation of 31-Level Asymmetrical Inverter with Reduced Components', *IEEE Access*, 2021, 9, pp. 22788-22803.

- [35] Bana, P. R., Panda, K. P., Padmanaban, S., & Panda, G. (2020). Extendable Switched-Capacitor Multilevel Inverter with Reduced Number of Components and Self-Balancing Capacitors. *IEEE Transactions on Industry Applications*.

**M. SAAD BIN ARIF** (Member, IEEE) was born in Aligarh, India. He received a Graduation Degree in electrical engineering in 2010 and Post-Graduation Degree in electrical engineering with a specialization in power system and drives in 2010. He has research/teaching experience of more than eight-year. His research interests include Multilevel

Inverter, MPPT, and power electronics in renewable energy systems, energy systems, and engineering education.

**UVAIS MUSTAFA** was born in Phalawda village of Meerut district of Uttar Pradesh, India, in 1995. He received his B.Tech. Electrical Engineering from Aligarh Muslim University in 2016 and his M. Tech Degree from the same university in 2019, with Instrumentation and Control being his specialization. He was awarded Gold Medal for holding the first rank in his masters. He Joined University Polytechnic, Aligarh Muslim University as Assistant Professor as soon as he graduated in

2019. He has published journal as well as conference articles. His research interests include Power Electronics converters, Renewable Energy and control of power electronics converters.

SHAHRIN BIN MD. AYOB (Senior Member, IEEE) was born in Kuala Lumpur, Malaysia. He received a degree in electrical engineering, a master's degree in electrical engineering (power), and a PhD degree from Universiti Teknologi Malaysia in 2001, 2003, and 2009. He is currently an Associate Professor with the Faculty of Engineering, School of Electrical Engineering, Universiti Teknologi Malaysia. His current research interests include solar photovoltaic systems, electric vehicle technology, fuzzy

systems, and evolutionary algorithms for power electronics applications. He is also a registered Graduate Engineer under the Board of Engineer Malaysia (BEM).

**JOSE RODRIGUEZ** (Life Fellow, IEEE) received the Engineer degree in electrical engineering from the Universidad Técnica Federico Santa María, in Valparaíso, Chile, in 1977 and the Dr.-Ing. degree in electrical engineering from the University of Erlangen, Erlangen, Germany, in 1985. He has been with the Department of Electronics Engineering, Universidad Técnica Federico Santa María, since 1977, where he was full Professor and President. Since 2015, he is the President of Universidad

Andrés Bello in Santiago, Chile.

He has co-authored two books, several book chapters and more than 400 journal and conference papers. His main research interests include multilevel inverters, new converter topologies, control of power converters, and adjustable-speed drives. He has received a number of best paper awards from journals of the IEEE. Prof. Rodriguez is a member of the Chilean Academy of Engineering. In 2014, he received the National Award of Applied Sciences and Technology from the government of Chile. In 2015, he received the Eugene Mittelmann Award from the Industrial Electronics Society of the IEEE.

**ABDUL NADEEM** received his B.Tech. Degree in Electrical Engineering from Dr. A.P.J. Abdul Kamal Technical University in 2015. He is currently pursuing his master's from the same university, with Instrumentation and Control being his specialization. His research interests include Multilevel inverter, Switching control of Power converters, and control of power electronics converters.

**MOHAMED ABDELRAHEM** (Member, IEEE) was born in Assiut, Egypt, in 1985. He received the B.Sc. (with honors) and M.Sc. degrees in electrical engineering from Assiut University, Assiut, Egypt, in 2007 and 2011, respectively. In 2020, he received the PhD degree with distinction in electrical engineering from the Technical University of Munich (TUM), Munich, Germany. Since 2014, he has been teaching power

electronics and renewable energy systems at TUM. Furthermore, he has been supervising several master theses in the field of control of power electronics, photovoltaic energy systems, and variable-speed wind energy conversion systems. Since 2019, he is the head of the research group "Renewable Energy Systems" at the Institute for Electrical Drive Systems and Power Electronics (EAL), TUM. Furthermore, since 2020 he is an Assistant Professor at Assiut University, Assiut, Egypt. His research interests include power electronics, predictive and encoderless control of variable-speed wind generators, photovoltaic energy systems, and energy storage systems. He has received a number of best paper awards from high prestigious international conferences of the IEEE.

VOLUME XX, 2017