ATLAS pixel detector electronics and sensors

This content has been downloaded from IOPscience. Please scroll down to see the full text.

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 188.184.3.52 This content was downloaded on 09/05/2014 at 16:00

Please note that terms and conditions apply.

PUBLISHED BY INSTITUTE OF PHYSICS PUBLISHING AND SISSA

RECEIVED: *April 23, 2008* ACCEPTED: *July 3, 2008* PUBLISHED: *July 24, 2008*

# **ATLAS pixel detector electronics and sensors**

G. Aad,<sup>k</sup> M. Ackers,<sup>b</sup> F.A. Alberti,<sup>l</sup> M. Aleppo,<sup>l,m</sup> G. Alimonti,<sup>l</sup> J. Alonso,<sup>a</sup> E.C. Anderssen,<sup>a</sup> A. Andreani,<sup>l,m</sup> A. Andreazza,<sup>l,m</sup> J-F. Arguin,<sup>a</sup> K.E. Arms,<sup>o</sup> D. Barberis,<sup>g,h</sup> M.B. Barbero,<sup>b</sup> M. Bazalova,<sup>q</sup> R.B. Beccherle,<sup>g</sup> K.H. Becks,<sup>x</sup> P.K. Behera,<sup>*i*</sup> F. Bellina,<sup>*x*</sup> J. Beringer,<sup>*a*</sup> K. Bernardet,<sup>*k*</sup> J.B. Biesiada,<sup>*a*</sup> L. Blanquart,<sup>*a*</sup> J. Boek,<sup>x</sup> G.R. Boyd,<sup>p</sup> P. Breugnon,<sup>k</sup> P. Buchholz,<sup>s</sup> B. Butler,<sup>r</sup> M. Caccia,<sup>l,m</sup> A.C. Capsoni,<sup>1</sup> C. Caso,<sup>g,h</sup>\* D. Cauz,<sup>u,v</sup> M. Cepeda,<sup>a</sup> R. Cereseto,<sup>g</sup> M. Cervetto,<sup>g,h</sup> M.L. Chu,<sup>t</sup> M. Citterio,<sup>1</sup> J.C. Clemens,<sup>k</sup> Y.C. Coadou,<sup>c</sup> M. Cobal,<sup>u,v</sup> A. Coccaro,<sup>g,h</sup> S. Coelli,<sup>1</sup> S. Correard,<sup>k</sup> M. Cristinziani,<sup>b</sup> S. Cuneo,<sup>g</sup> S. D'Auria,<sup>u,v</sup> M. Dameri,<sup>g</sup> G. Darbo,<sup>g</sup> S. Dardin,<sup>a</sup> B. De Lotto,<sup>u,v</sup> U. De Sanctis,<sup>l,m</sup> J.B. De Vivie De Regie,<sup>k</sup> C. Del Papa,<sup>*u*,*v*</sup> P. Delpierre,<sup>*k*</sup> B. Di Girolamo,<sup>*c*</sup> W. Dietsche,<sup>*b*</sup> F. Djama,<sup>*k*</sup> D. Dobos,<sup>*f*</sup> M. Donega,<sup>c</sup> J. Dopke,<sup>x</sup> K. Einsweiler,<sup>a</sup> A. Eyring,<sup>b</sup> D. Fasching,<sup>w</sup> L. Feligioni,<sup>k</sup> D. Ferguson,<sup>w</sup> W. Fernando,<sup>o</sup> P. Fischer,<sup>b</sup> M.J. Fisher,<sup>o</sup> T. Flick,<sup>x</sup> G. Gagliardi,<sup>g,h</sup> E. Galyaev,<sup>e</sup> K.K. Gan,<sup>o</sup> M. Garcia-Sciveres,<sup>a</sup> N. Garelli,<sup>g,h</sup> G.G. Gariano,<sup>g</sup> G.G. Gaycken,<sup>b</sup> C. Gemme,<sup>g</sup> P. Gerlach,<sup>x</sup> M. Gilchriese,<sup>a†</sup> M.P. Giordani,<sup>u,v</sup> D. Giugni,<sup>l</sup> K.W. Glitza,<sup>x</sup> C. Gössling,<sup>f</sup> T. Golling,<sup>a</sup> F. Goozen,<sup>a</sup> I. Gorelov,<sup>n</sup> G. Gorfine,<sup>x</sup> C. Grah,<sup>x</sup> H.M. Gray,<sup>d</sup> I.M. Gregor,<sup>x</sup> J. Grosse-Knetter,<sup>b</sup> K. Grybel,<sup>s</sup> P. Gutierrez,<sup>p</sup> G.D. Hallewell,<sup>k</sup> N. Hartman,<sup>a</sup> M. Havranek,<sup>q</sup> B. Heinemann,<sup>a</sup> T. Henß,<sup>x</sup> M.R. Hoeferkamp,<sup>n</sup> D. Hoffmann,<sup>k</sup> M. Holder,<sup>s</sup> W. Honerbach,<sup>b</sup> C. Horn,<sup>r</sup> S. Hou,<sup>t</sup> G.S. Huang,<sup>p</sup> F. Huegging,<sup>b</sup> E.W. Hughes,<sup>d</sup> I. Ibragimov,<sup>s</sup> I. Ilyashenko,<sup>c</sup> M. Imhaeuser,<sup>x</sup> J.M. Izen,<sup>e</sup> J. Jackson,<sup>o</sup> D. Jana,<sup>p</sup> R.C. Jared,<sup>w</sup> P. Jez,<sup>q</sup> T. Johnson,<sup>a</sup> J. Joseph,<sup>w</sup> H. Kagan,<sup>o</sup> M. Karagounis,<sup>b</sup> R.D. Kass,<sup>o</sup> M. Keil,<sup>b</sup> S. Kersten,<sup>x</sup> P. Kind,<sup>x</sup> J. Klaiber-Lodewigs,<sup>f</sup> L. Klingbeil,<sup>b</sup> R. Klingenberg,<sup>f</sup> A. Korn,<sup>a</sup> V.V. Kostyukhin,<sup>g</sup> I. Kostyukhina,<sup>g</sup> O. Krasel,<sup>f</sup> H. Krüger,<sup>b</sup> K. Krueger,<sup>a</sup> J. Kudlaty,<sup>f</sup> T. Kuhl,<sup>b</sup> O. Kvasnicka,<sup>q</sup> K. Lantzsch,<sup>x</sup> T. Lari,<sup>1</sup> S.L. Latorre,<sup>1</sup> S.C. Lee,<sup>t</sup> T. Lenz,<sup>x</sup> G. Lenzen,<sup>x</sup> J. Lepidis,<sup>x</sup> J. Levêque,<sup>k</sup> M. Leyton,<sup>a</sup> D. Lopez Mateos,<sup>d</sup> K. F. Loureiro,<sup>o</sup> D. Lüke,<sup>f</sup> L. Luisa,<sup>*u*,*v*</sup> J. Lys,<sup>*a*</sup> R. J. Madaras,<sup>*a*</sup> P. Mättig,<sup>*x*</sup> F.M. Manca,<sup>*l*</sup> E. Mandelli,<sup>*a*</sup> M. Marcisovsky,<sup>q</sup> Z. Marshall,<sup>d</sup> G. Martinez,<sup>b</sup> L. Masetti,<sup>b</sup> M. Maß,<sup>f</sup> M. Mathes,<sup>b</sup> R. McKay,<sup>j</sup> G. Meddeler,<sup>a</sup> R. Meera-Lebbai,<sup>p</sup> C. Meroni,<sup>l</sup> J. Metcalfe,<sup>n</sup> W.T. Meyer,<sup>j</sup> D.W. Miller,<sup>r</sup> W. Miller,<sup>a</sup> S. Montesano,<sup>1,m</sup> M.M. Monti,<sup>1</sup> P. Morettini,<sup>g</sup> J.M. Moss,<sup>o</sup> T. Mouthuy,<sup>k</sup> P. Nechaeva,<sup>g</sup> W. Ockenfels,<sup>b</sup> G.A. Odino,<sup>g,h</sup> M. Olcese,<sup>g</sup> B. Osculati,<sup>g,h</sup> F. Parodi,<sup>g,h</sup> A. Pekedis,<sup>a</sup> K. Perez,<sup>d</sup> I. Peric,<sup>b</sup> C. Pizzorno,<sup>g</sup> J. Popule,<sup>q</sup> R. Post,<sup>a</sup> F. Ragusa,<sup>1,m</sup> A.M. Rahimi,<sup>o</sup> B. Raith,<sup>b</sup> S. Rajek,<sup>f</sup> K. Reeves,<sup>x</sup> I. Reisinger,<sup>f</sup>

| J.D. Richardson, <sup><i>a</i></sup> E. I. Rosenberg, <sup><i>j</i></sup> L. P. Rossi, <sup><i>g</i></sup> I. Rottländer, <sup><i>b</i></sup> A.R. Rovani, <sup><i>g</i></sup> A. Rozanov, <sup><i>k</i></sup> O. Runolfsson, <sup><i>b</i></sup> E.R. Ruscino, <sup><i>g</i></sup> A.F. Saavedra, <sup><i>a</i></sup> F.S. Sabatini, <sup><i>l</i></sup> M. Saleem, <sup><i>p</i></sup> S. Sandvoss, <sup><i>x</i></sup> B. Sanny, <sup><i>x</i></sup> L. Santi, <sup><i>u</i>,<i>v</i></sup> M.I. Scherzer, <sup><i>a</i></sup> C. Schiavi, <sup><i>g</i>,<i>h</i></sup> A. Schreiner, <sup><i>i</i></sup> J. Schultes, <sup><i>x</i></sup> A. Schwartzman, <sup><i>r</i></sup> R. Seibert, <sup><i>s</i></sup> S.C. Seidel, <sup><i>n</i></sup> H. Severini, <sup><i>p</i></sup> S. Shanava, <sup><i>c</i></sup> P. Skubic, <sup><i>p</i></sup> A.C. Smith, <sup><i>a</i></sup> D.S. Smith, <sup><i>o</i></sup> J. Snow, <sup><i>p</i></sup> T. Stahl, <sup><i>s</i></sup> T. Stockmanns, <sup><i>b</i></sup> S. Strandberg, <sup><i>a</i></sup> M. Strauss, <sup><i>p</i></sup> D. Ta, <sup><i>b</i></sup> F. Tegenfeldt, <sup><i>j</i></sup> P.K. Teng, <sup><i>t</i></sup> R. Ter-Antonyan, <sup><i>o</i></sup> J. Thadome, <sup><i>x</i></sup> T. Tic, <sup><i>q</i></sup> L. Tomasek, <sup><i>q</i></sup> M. Tomasek, <sup><i>q</i></sup> F. Tomasi, <sup><i>l</i></sup> K. Toms, <sup><i>n</i></sup> C. Tran, <sup><i>a</i></sup> J. Treis, <sup><i>b</i></sup> N. Triplett, <sup><i>j</i></sup> C. Troncon, <sup><i>l</i></sup> L. Vacavant, <sup><i>k</i></sup> S. Vahsen, <sup><i>a</i></sup> J. Valenta, <sup><i>q</i></sup> G. Vegni, <sup><i>l</i>,<i>m</i></sup> F. Vernocchi, <sup><i>g</i></sup> E. Vigeolas, <sup><i>k</i></sup> J. Virzi, <sup><i>a</i></sup> E. Viscione, <sup><i>l</i></sup> V. Vrba, <sup><i>q</i></sup> J. Walbersloh, <sup><i>f</i></sup> W. Walkowiak, <sup><i>s</i></sup> J. S. Wirth, <sup><i>a</i></sup> R. Witharm, <sup><i>a</i></sup> B. Witt, <sup><i>x</i></sup> M. Wittgen, <sup><i>r</i></sup> J. Wuestenfeld, <sup><i>f</i></sup> R. Wunstorf, <sup><i>f</i></sup> J. Wyckoff, <sup><i>a</i></sup> W-M. Yao, <sup><i>a</i></sup> C. Young, <sup><i>r</i></sup> R. Zaidan, <sup><i>k</i></sup> M. Zdrazil, <sup><i>a</i></sup> F. Zetti, <sup><i>a</i></sup> J. Zhong, <sup><i>t</i></sup> M. Ziolkowski, <sup><i>s</i></sup> G. Zizka <sup><i>a</i></sup> and M.M. Zoeller <sup><i>o</i></sup> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li><sup>a</sup>Lawrence Berkeley National Laboratory and University of California, Physics Division<br/>MS50B-6227, 1 Cyclotron Road, Berkeley, CA 94720, United States of America</li> <li><sup>b</sup>Physikalisches Institut der Universität Bonn, Nussallee 12, D - 53115 Bonn, Germany</li> <li><sup>c</sup>CERN, CH - 1211 Geneva 23, Switzerland</li> <li><sup>d</sup>Columbia University, Nevis Laboratory,<br/>136 So. Broadway, Irvington, NY 10533, United States of America</li> <li><sup>e</sup>800 West Campbell Road, Richardson, TX 75080-3021, United States of America</li> <li><sup>f</sup>Universität Dortmund, Experimentelle Physik IV, DE - 44221 Dortmund, Germany</li> <li><sup>g</sup>INFN Genova, via Dodecaneso 33, IT - 16146 Genova, Italy</li> <li><sup>h</sup>Università di Genova, Dipartimento di Fisica, via Dodecaneso 33, IT - 16146 Genova, Italy</li> <li><sup>i</sup>203 VAN ALLEN HALL, IOWA CITY IA 52242-1479, United States of America</li> <li><sup>j</sup>Iowa State University, Dept of Physics and Astronomy, Ames High Energy Physics Group,<br/>Ames, IA 50011-3160, United States of America</li> <li><sup>k</sup>CPPM, Aix-Marseille Université, CNRS/IN2P3, Marseille, France</li> <li><sup>l</sup>INFN Milano, via Celoria 16, IT - 20133 Milano, Italy</li> <li><sup>m</sup>Università di Milano, Dipartimento di Fisica, via Celoria 16, IT - 20133 Milano, Italy</li> <li><sup>m</sup>Department of Physics and Astronomy, University of New Mexico</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Albuquerque, NM 87131, United States of America<br><sup>o</sup> Ohio State University,<br>191 West Woodruff Ave, Columbus, OH 43210-1117, United States of America<br><sup>p</sup> University of Oklahoma, Homer L. Dodge Department of Physics<br>440 West Brooks, Room 100, Norman, OK 73019-0225, United States of America<br><sup>q</sup> Institute of Physics, Academy of Sciences of the Czech Republic<br>Na Slovance 2, CZ - 18221 Praha 8, Czech Republic<br><sup>r</sup> Stanford Linear Accelerator Center, Stanford, California 94309, United States of America<br><sup>s</sup> Universität Siegen, Fachbereich Physik, DE - 57068 Siegen, Germany<br><sup>1</sup> Insitute of Physics, Academia Sinica, TW - Taipei 11529, Taiwan<br><sup>w</sup> INFN Gruppo Collegato di Udine, via delle Scienze 208, IT - 33100 Udine, Italy<br><sup>w</sup> Università di Udine, Dipartimento di Fisica, via delle Scienze 208, IT - 33100 Udine, Italy<br><sup>w</sup> University of Wisconsin, Department of Physics, Madison, WI 53706, United States of America<br><sup>x</sup> Bergische Universität, Fachbereich C, Physik<br>Postfach 100127, Gauss-Strasse 20, D- 42097 Wuppertal, Germany<br>E-mail: MGGilchriese@lbl.gov                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

ABSTRACT: The silicon pixel tracking system for the ATLAS experiment at the Large Hadron Collider is described and the performance requirements are summarized. Detailed descriptions of the pixel detector electronics and the silicon sensors are given. The design, fabrication, assembly and performance of the pixel detector modules are presented. Data obtained from test beams as well as studies using cosmic rays are also discussed.

KEYWORDS: Particle tracking detectors; Electronic detector readout concepts (solid-state); Large detector systems for particle and astroparticle physics.

<sup>\*</sup>Deceased.

<sup>&</sup>lt;sup>†</sup>Corresponding author.

# Contents

| 1. | Intr | oductio | on                                                             | 3  |

|----|------|---------|----------------------------------------------------------------|----|

| 2. | Perf | forman  | ce requirements and design choices                             | 3  |

| 3. | Syst | em ove  | rview                                                          | 4  |

| 4. | Elec | tronics | systems                                                        | 8  |

|    | 4.1  | Overv   | iew                                                            | 8  |

|    |      | 4.1.1   | System architecture                                            | 8  |

|    | 4.2  | Front-  | end chip                                                       | 9  |

|    |      | 4.2.1   | Front-end chip history                                         | 9  |

|    |      | 4.2.2   | Design                                                         | 9  |

|    |      | 4.2.3   | Requirements, performance and production                       | 15 |

|    | 4.3  | Modu    | le Control Chip (MCC)                                          | 15 |

|    |      | 4.3.1   | MCC history                                                    | 15 |

|    |      | 4.3.2   | Design                                                         | 16 |

|    |      | 4.3.3   | Requirements, performance and production                       | 18 |

|    | 4.4  | Optica  | al communication                                               | 19 |

|    |      | 4.4.1   | Optical link architecture                                      | 19 |

|    |      | 4.4.2   | Opto-Board                                                     | 20 |

|    |      | 4.4.3   | Back of Crate Card (BOC)                                       | 22 |

|    |      | 4.4.4   | Opto-fibres                                                    | 22 |

|    |      | 4.4.5   | Production and testing of opto-link components                 | 23 |

|    |      | 4.4.6   | Opto-link performance                                          | 24 |

|    | 4.5  | Data A  | Acquisition System                                             | 24 |

|    |      | 4.5.1   | Architecture overview                                          | 25 |

|    |      | 4.5.2   | ROD Crate software and calibration analysis farm               | 28 |

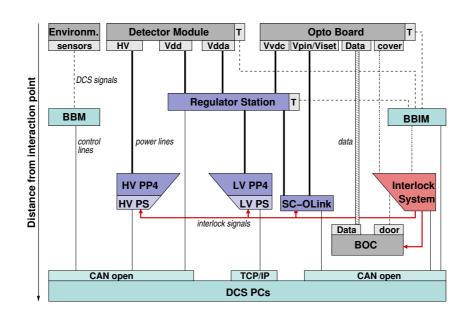

|    | 4.6  | Detect  | tor Control System (DCS), power supplies, and interlock system | 29 |

|    |      | 4.6.1   | The hardware of the DCS                                        | 29 |

|    |      | 4.6.2   | The software of the DCS                                        | 32 |

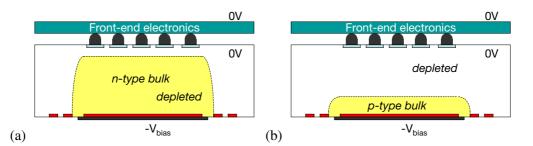

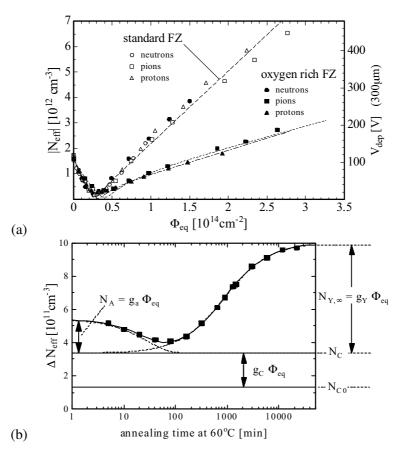

| 5. | Sens | sors    |                                                                | 33 |

|    | 5.1  | Design  | n                                                              | 33 |

|    | 5.2  | Protot  | yping and tests                                                | 36 |

|    | 5.3  | Produ   | ction and quality assurance                                    | 39 |

| 6. | Mod  | lules   |                                                              | 39 |

|----|------|---------|--------------------------------------------------------------|----|

|    | 6.1  | Overv   | iew                                                          | 39 |

|    | 6.2  | Bump    | bonding                                                      | 41 |

|    |      | 6.2.1   | The solder bumping and bonding process                       | 42 |

|    |      | 6.2.2   | The indium bump bonding process                              | 43 |

|    | 6.3  | Qualit  | y control of bump bonded assemblies                          | 43 |

|    | 6.4  | Rewor   | rking of bump bonded assemblies                              | 44 |

|    | 6.5  | Modul   | le assembly                                                  | 44 |

|    | 6.6  | Testing | g and selection procedures                                   | 45 |

|    | 6.7  | Produc  | ction yield                                                  | 49 |

| 7. | Test | beam s  | studies                                                      | 50 |

|    | 7.1  | The te  | est beam setup                                               | 51 |

|    | 7.2  | Irradia | ation of tested assemblies                                   | 51 |

|    | 7.3  | Event   | reconstruction and analysis                                  | 52 |

|    | 7.4  | Measu   | arements of detection efficiency                             | 52 |

|    |      | 7.4.1   | Noise                                                        | 53 |

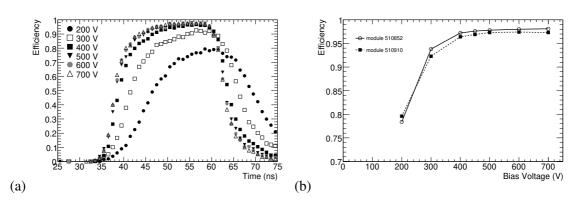

|    |      | 7.4.2   | Timing studies                                               | 54 |

|    |      | 7.4.3   | Detection efficiency and bias voltage                        | 54 |

|    |      | 7.4.4   | Detection Efficiency and Incidence Angle.                    | 55 |

|    |      | 7.4.5   | Efficiency in a high intensity beam                          | 56 |

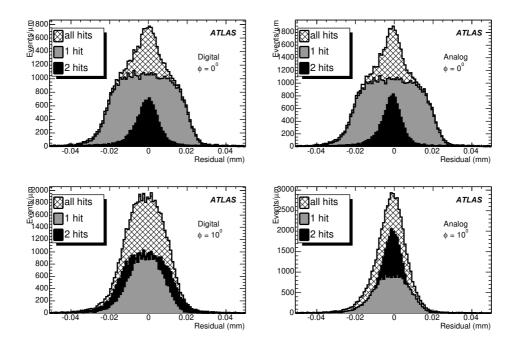

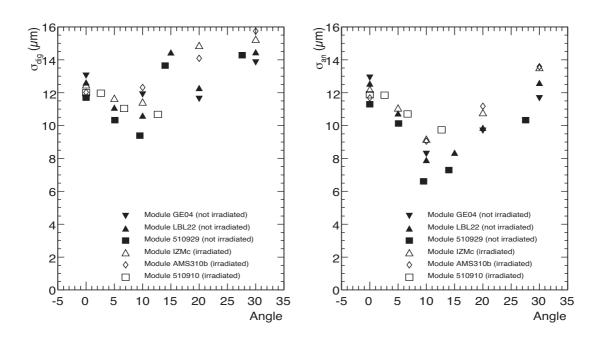

|    | 7.5  | Spatia  | l resolution                                                 | 57 |

|    |      | 7.5.1   | Determination of the telescope extrapolation uncertainty     | 59 |

|    |      | 7.5.2   | x-spatial resolution at normal incidence                     | 59 |

|    |      | 7.5.3   | x-spatial resolution as a function of the angle of incidence | 61 |

|    |      | 7.5.4   | Lorentz angle                                                | 62 |

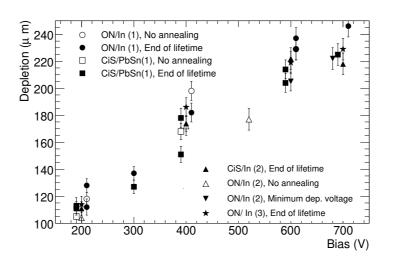

|    | 7.6  | Deplet  | tion depth of irradiated sensors                             | 63 |

|    | 7.7  | Charge  | e collection in irradiated sensors                           | 63 |

|    | 7.8  | Charge  | e trapping in irradiated sensors                             | 64 |

|    | 7.9  | Comb    | ined test beam                                               | 66 |

| 8. | Syst | em test | and cosmic rays operation                                    | 66 |

|    | 8.1  | Setup   |                                                              | 67 |

|    | 8.2  | Comm    | nissioning of the setup                                      | 67 |

|    |      | 8.2.1   | Service tests                                                | 67 |

|    |      | 8.2.2   | Cooling operation                                            | 67 |

|    |      | 8.2.3   | Calibration of the optical links                             | 68 |

|    | 8.3  | Analo   | gue performance of the modules                               | 69 |

|    | 8.4  | Cosmi   | ic ray operation                                             | 69 |

| 9. | Con  | clusion |                                                              | 71 |

|    |      |         |                                                              |    |

### 1. Introduction

This paper describes the pixel detector system for the ATLAS experiment at the Large Hadron Collider (LHC). ATLAS [1] is a general purpose detector for the study of primarily proton-proton collisions at the LHC. The pixel detector system is a critical component of the inner tracking detector of ATLAS. The ATLAS Inner Detector [2] provides charged-particle tracking with high efficiency over the pseudorapidity range  $|\eta| < 2.5$ . The pixel detector system is the innermost element of the Inner Detector [3]. The pixel detector contains approximately 80 million channels and provides pattern recognition capability in order to meet the track reconstruction requirements of ATLAS at the full luminosity of the LHC of  $\mathcal{L} = 10^{34} \text{ cm}^{-2} \text{s}^{-1}$ . It is the most important detector used in the identification and reconstruction of secondary vertices from the decay of, for example, particles containing a b-quark or for b-tagging of jets. In addition, it provides excellent spatial resolution for reconstructing primary vertices coming from the proton-proton interaction region within ATLAS even in the presence of the multiple interactions at the LHC design luminosity.

In the sections below we first present the performance requirements for the pixel detector. This is followed by an overview of the system and its relationship to the Inner Detector. We then describe the principal components of the pixel detector systems, namely the electronics, sensors and modules. Results from test beam studies of the pixel detector components are then given. Results from studies of cosmic ray tracks passing through a sub-assembly of the pixel detector, corresponding to about 10% of the pixel system, are also presented. Mechanical systems and services are described in a separate publication [4].

# 2. Performance requirements and design choices

The performance requirements for the ATLAS Inner Detector (ID) were formulated in the Inner Detector Technical Design Report (TDR) [2]. The pixel system is an important part of the ID and plays a major role in fulfilling these requirements.

The general performance requirements for the pixel system are:

- coverage of the pseudorapidity range  $|\eta| < 2.5$ ;

- transverse impact parameter resolution of better than about 15 microns;

- good resolution in the longitudinal *z*-coordinate, allowing primary vertex reconstruction of charged tracks with  $\sigma(z) < 1$  mm;

- three-dimensional-vertexing capabilities;

- very good b-jet tagging capabilities both in the high-level trigger and in the offline reconstruction;

- minimal material for all elements in the system, in order to reduce multiple scattering and secondary interactions;

- excellent efficiency for all pixel layers; and

• radiation hardness of the pixel detectors elements to operate after a total dose of 500 kGy or about  $10^{15} n_{ea} \text{cm}^{-2}$  (lifetime dose).

These performance requirements lead to the following major design choices:

- three pixel hits over the full rapidity range. The requirement to have three pixel layers is based on a detailed study comparing a layout with two-pixel-hits versus a layout with three-pixel-hits [5];

- minimal radius of the innermost layer (b-layer), set at 5 cm due to the practical limitations of clearances around the interaction region beam pipe vacuum system;

- the smallest pixel size achievable, which is set to 50  $\mu$ m × 400  $\mu$ m by electronics design limitations.

The expected dose for the innermost layer is expected to reach 500 kGy after approximately five years of LHC operation. The other layers are expected to reach a 500 kGy dose, the lifetime dose, after 10 or more years of LHC operation (at a maximum luminosity of  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>).

The expected tracking performance of the pixel system is described elsewhere [2]. For example, the effective two-track resolution and the number of merged clusters of pixel hits (where a single cluster can have contributions from two or more charged tracks) depends on the local track density and other event properties and thus is not easily characterized except through measurements of tracking performance.

# 3. System overview

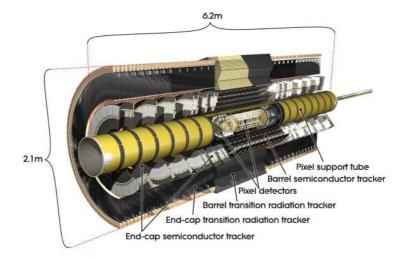

In this section we present a brief overview of the pixel system and its relationship to the Inner Detector. The basic parameters of the pixel system are also summarized in this section. The pixel detector is the innermost element of the Inner Detector as shown in figure 1. The pixel tracker is designed to provide at least three points on a charged track emanating from the collision region in ATLAS. The pixel detector and the other elements of the Inner Detector span a pseudorapidity range  $|\eta| < 2.5$ .

The principal components of the pixel tracking system are the following:

- the active region of the pixel detector, which is composed of three barrel layers and a total of six disk layers, three at each end of the barrel region;

- internal services (power, monitoring, optical input/output and cooling) and their associated mechanical support structures (also supporting the interaction region beam pipe) on both ends of the active detector region;

- a Pixel Support Tube into which the active part of the pixel detector and the services and related support structures are inserted and located; and

- external services that are connected to the internal services at the end of the Pixel Support Tube.

Figure 1. The ATLAS Inner Detector.

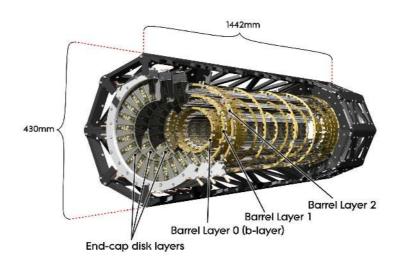

Figure 2. A schematic view of the active region of the pixel detector consisting of barrel and endcap layers.

The active region of the pixel detector is shown in a schematic view in figure 2. The active part of the pixel system consists of three barrel layers-Layer 0 (so-called b-layer), Layer 1 and Layer 2-and two identical endcap regions, each with three disk layers.

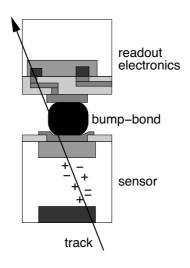

The basic building block of the active part of the pixel detector is a module (section 6) that is composed of silicon sensors (section 5), front-end electronics and flex-hybrids with control circuits (section 4). All modules are functionally identical at the sensor/integrated circuit level, but differ somewhat in the interconnection schemes for barrel modules and disk modules. The nominal pixel size is 50 microns in the  $\phi$  direction and 400 microns in *z* (barrel region, along the beam axis) or *r* (disk region). A few special pixels in the region between integrated circuits on a module have larger dimensions — see sections 5 and 6. There are 46,080 pixel electronics channels in a module.

| Layer  | Mean        | Number of      | Number of | Number of  | Active                 |  |

|--------|-------------|----------------|-----------|------------|------------------------|--|

| Number | Radius [mm] | Staves Modules |           | Channels   | Area [m <sup>2</sup> ] |  |

| 0      | 50.5        | 22             | 286       | 13,178,880 | 0.28                   |  |

| 1      | 88.5        | 38             | 494       | 22,763,520 | 0.49                   |  |

| 2      | 122.5       | 52             | 676       | 31,150,080 | 0.67                   |  |

| Total  |             | 112            | 1456      | 67,092,480 | 1.45                   |  |

Table 1. Basic parameters for the barrel region of the ATLAS pixel detector system.

Table 2. Basic parameters of the endcap region of the ATLAS pixel detector system.

| Disk             | Mean z    | Number of | Number of | Number of  | Active                 |

|------------------|-----------|-----------|-----------|------------|------------------------|

| Number [mm]      |           | Sectors   | Modules   | Channels   | Area [m <sup>2</sup> ] |

| 0                | 495       | 8         | 48        | 2,211,840  | 0.0475                 |

| 1                | 580       | 8         | 48        | 2,211,840  | 0.0475                 |

| 2 650            |           | 8         | 48        | 2,211,840  | 0.0475                 |

| Total one endcap |           | 24        | 144       | 6,635,520  | 0.14                   |

| Total both       | n endcaps | 48        | 288       | 13,271,040 | 0.28                   |

The essential parameters for the barrel region of the pixel detector system are summarized in table 1. Modules are mounted on mechanical/cooling supports, called staves, in the barrel region. Thirteen modules are mounted on a stave and the stave layout is identical for all layers. The active length of each barrel stave is about 801 mm. The staves are mounted in half-shells manufactured from a carbon-fiber composite material. Two half-shells are joined to form each barrel layer.

The two endcap regions are identical. Each is composed of three disk layers, and each disk layer is identical. The basic parameters of the endcap region are given in table 2. Modules are mounted on mechanical/cooling supports, called disk sectors. There are eight identical sectors in each disk.

The total number of pixels in the system is approximately 67 million in the barrel and 13 million in the endcaps, covering a total active area of about  $1.7 \text{ m}^2$ .

The barrel shells and the endcap disks are supported by a spaceframe also manufactured from a carbon-fiber composite material (see figure 2). Electrical, optical and cooling services are connected and routed within service panels (four on each end of the pixel detector) from patch panels (Patch Panel 0-PP0) at the ends of the supporting spaceframe to the end of the Pixel Support Tube. These services are supported by carbon fiber structures that also hold the beryllium vacuum pipe within the Pixel Support Tube. Electrical, optical and cooling connections are made at the end of the Pixel Support Tube at Patch Panel 1 (PP1). Connections and control of external services are made at additional patch panels (PP2, PP3 and PP4) located within the ATLAS detector or near the ATLAS control room complex. The principal sub-elements of the pixel detector — barrels, endcaps, service supports and eight service panels — were assembled in a surface building near the ATLAS underground cavern. The complete pixel detector along with its services was tested in part and then installed as a unit in the Inner Detector. The mechanics, services and assembly of the pixel detector are described in detail in ref. [4].

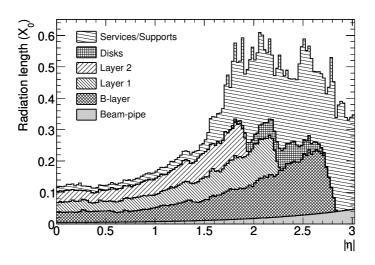

**Figure 3.** Radiation length of the pixel detector versus pseudorapidity showing the contribution from each layer and from all disks. Layer and disk contributions include services and supports directly in front of and behind the layer/disk. All remaining services and supports, including services in the region between the barrel and endcap are included in the "Services/Supports" category.

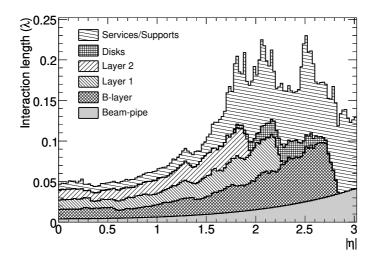

**Figure 4.** Interaction length of the pixel detector versus pseudorapidity showing the contribution from each layer and from all disks. Layer and disk contributions include services and supports directly in front of and behind the layer/disk. All remaining services and supports, including services in the region between the barrel and endcap are included in the "Services/Supports" category.

The contribution of the pixel detector to the total Inner Detector material budget as a function of pseudorapidity is given in figure 3 (radiation lengths) and figure 4 (interaction lengths). The beam pipe contribution is also presented.

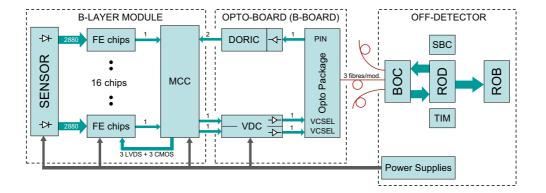

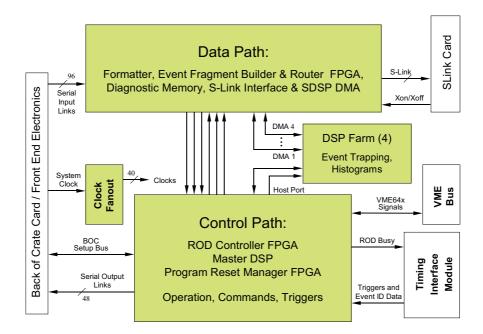

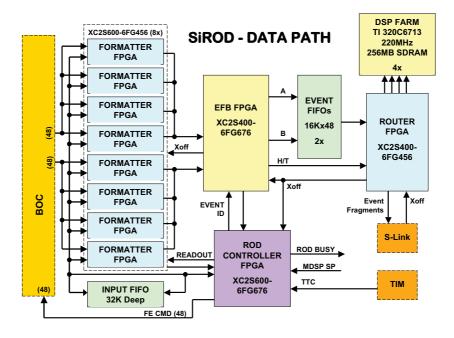

Figure 5. Block diagram of the pixel detector system architecture.

# 4. Electronics systems

#### 4.1 Overview

The first comprehensive proposal of the pixel electronic system was described in 1997-98 in the ATLAS Inner Detector and Pixel Detector Technical Design Reports [2, 3]. The complete system underwent several revisions in subsequent years. The total number of instrumented channels is about 80 million, each containing approximately 1,000 transistors and each consuming a maximum power of 100  $\mu$ W (power for on-detector circuitry only).

## 4.1.1 System architecture

A block diagram that illustrates the principal elements of the system architecture is shown in figure 5. There are 16 front-end chips (FE) in each pixel module and these are arranged in two rows of eight chips. The 16 FEs are read out by a Module Control Chip (MCC). Data are transmitted from the FE to the MCC using Low Voltage Differential Signalling (LVDS) serial links, configured in a star topology. The serial protocol minimises the number of lines to be routed, while the star topology maximizes bandwidth and reliability. Each module is then connected to the off-detector Read-out Drivers (RODs) through optical-fiber links (opto-links). One down link is used to transmit clock, trigger, commands and configuration data, while one or two up-links are used for event readout. The b-layer uses two up-links to increase the aggregate bandwidth needed for the higher average hit occupancy that occurs at the minimum radius. The readout (R/O) architecture is "datapush". This means that each component in the chain (FE, MCC) always transmits at the maximum rate, and there is no busy mechanism to stop transmission when buffers are full. Each upstream component in the R/O chain (MCC, ROD) constantly monitors the number of events received and compares the results with the number of triggers sent. If the difference of the two is bigger than a predefined value, triggers downstream are blocked and empty events are generated.

The power supply system uses a combination of customized-commercial components and fully-custom components for the low (electronics) and high (sensor bias) voltages. The use of deep sub-micron electronics and long resistive cables with significant voltage drops, required the use of low-voltage regulator boards, approximately 10 meters from the pixel detector. The absolute maximum voltage rating for the pixel electronics is 4 V. The optical-links are custom made using

commercial diode and laser array bare die with custom integrated circuits (DORIC and VDC) and packaging. An optical-interface card (Back of Crate or BOC) is also used for each ROD.

# 4.2 Front-end chip

## 4.2.1 Front-end chip history

Small scale, front-end chips that demonstrated the required analog and digital architecture were first developed in the second half of the 1990s [6–9]. The first radiation-soft functional prototypes of full-size chips were submitted for production in 1998: FE-B and FE-A/C (Pirate). The FE-B chip was designed using 0.8  $\mu$ m CMOS technology and had the same basic readout architecture used for the final chips. The FE-B charge amplifier used a direct cascode<sup>1</sup> and source follower, with a feedback capacitance of 4 fF. The DC feedback was based on a previous design [7, 8]. The discriminator used a dual threshold, with a low threshold for precise timing and a high threshold to flag a hit pixel.

FE-A was made using 0.8  $\mu$ m BiCMOS technology, whereas FE-C was a full CMOS version. The charge amplifier used a folded cascode input stage with feedback capacitance of 3 fF and a new, improved DC feedback. The discriminator was AC coupled, with an input, fully-differential, bipolar pair in the A-version and CMOS in the C-version. The FE-A column readout architecture used a shift register to transport the hit address to the bottom of the chip. Hits were associated with the level 1 trigger (L1) by counting the number of clock cycles needed for the hit to reach the bottom of the column. FE-A/B/C demonstrated all the basic ATLAS pixel performance goals in the laboratory and in beam.

The subsequent chip was developed merging the basic concept of the amplifier/discriminator from FE-A/C and the column readout architecture from FE-C into a common layout for the DMILL- $^2$  Durci Mixte sur Isolant Logico-Lineaire - technology (known as FE-D). FE-D1 was submitted in July 1999 together with the DORIC and VDC chips (see section 4.4) and a prototype MCC-D0 (see section 4.3). A new production run was submitted in Aug 2000 with two versions of FE-D2: one with dynamic and the other with static memory cells. This run included the full MCC-D2 and new DORIC and VDC chips as well. Yields of both FE and MCC were unacceptable and work with this vendor was terminated. Work in an alternative radiation-hard technology, FE-H, began in Dec 1999. The chip was almost ready but was never submitted because of large cost increases. The failure of both traditional radiation-hard vendors pushed the collaboration towards the Deep Sub-micron (DSM) approach, based upon a commercial 0.25  $\mu$ m CMOS process and a radiation-tolerant layout. A major design effort was initiated in September 2000. Three versions (FE-I1, FE-I2 and FE-I3) were eventually produced. The final chip (FE-I3) became available in late 2003. Table 3 gives a summary of the front-end designs developed for the ATLAS pixel detector.

# 4.2.2 Design

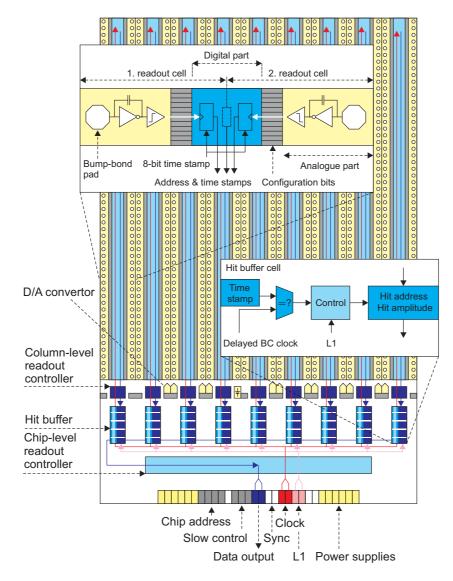

**Chip architecture.** The readout chip for the ATLAS pixel detector [15, 16], shown in figure 6, contains 2880 pixel cells of  $50 \times 400 \ \mu m^2$  size arranged in an  $18 \times 160$  matrix. Each pixel cell

<sup>&</sup>lt;sup>1</sup>The cascode is a two-stage amplifier composed of a transconductance amplifier followed by a current buffer.

<sup>&</sup>lt;sup>2</sup>DMILL technology was developed by CEA, France, and then produced under license by TEMIC Matra MHS.

|               |      |             |                                                | •        |                           |            |

|---------------|------|-------------|------------------------------------------------|----------|---------------------------|------------|

| Chip          | Year | Cell size   | $\operatorname{Col} \times \operatorname{Row}$ | Transis- | Technology                | References |

|               |      | $[\mu m^2]$ |                                                | tors     |                           |            |

| Beer & Pastis | 1996 | 50×436      | 12×63                                          | -        | AMS $0.8\mu$ m BiCMOS, 2M | [6, 9]     |

| M72b          | 1997 | 50×536      | $12 \times 64$                                 | -        | HP $0.8\mu m$ CMOS, 2M    | [6]        |

| Marebo        | 1997 | 50×397      | 12×63                                          | 0.1 M    | DMILL 0.8µm BiCMOS, 2M    | [7, 8]     |

| FE-B          | 1998 | 50×400      | 18×160                                         | 0.8 M    | HP 0.8µm CMOS, 3M         | [10 - 12]  |

| FE-A/C        | 1998 | 50×400      | 18×160                                         | 0.8 M    | AMS 0.8µm BiCMOS, 2M      | [9, 12]    |

| FE-D1         | 1999 | 50×400      | 18×160                                         | 0.8 M    | DMILL 0.8µm BiCMOS, 2M    | [12]       |

| FE-D2         | 2000 | 50×400      | 18×160                                         | 0.8 M    | DMILL 0.8µm BiCMOS, 2M    | _          |

| FE-I1         | 2002 | 50×400      | 18×160                                         | 2.5 M    | DSM $0.25\mu$ m CMOS, 6M  | [13]       |

| FE-I2/I2.1    | 2003 | 50×400      | 18×160                                         | 3.5 M    | DSM $0.25 \mu m$ CMOS, 6M | [14]       |

| FE-I3         | 2003 | 50×400      | 18×160                                         | 3.5 M    | DSM $0.25\mu$ m CMOS, 6M  | [15-18]    |

**Table 3.** Summary of the ATLAS pixel front-end chips designed and fabricated as described in the text. The chips contain two (2M), three (3M) or six (6M) metal layers as indicated.

contains an analogue block where the sensor charge signal is amplified and compared to a programmable threshold using a comparator. The digital readout part transfers the hit pixel address, a hit leading edge (LE) timestamp, and a trailing edge (TE) timestamp to the buffers at the chip periphery. In these buffers a Time-over-Threshold (ToT) is calculated by subtracting the TE from the LE timestamp. These hit-buffers monitor the time of each stored hit by inspecting the LE time stamp. When a hit time becomes longer than the latency of the L1 trigger (approximately  $3.2 \ \mu$ s) and no trigger signal is recorded, the hit information is deleted. Hits marked by trigger signals are selected for readout. Triggered hit data are then transmitted serially out of the chip in the same order as the trigger arrival.

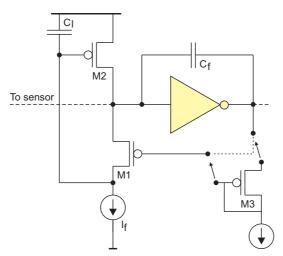

**Charge sensitive preamplifier.** The charge-sensitive amplifier uses a single-ended, folded-cascode topology, which is a common choice for low-voltage and high gain amplifiers. The amplifier is optimised for a nominal capacitive load of 400 fF and designed for the negative signals expected from n<sup>+</sup>-on-n-bulk detectors. The design of the charge amplifier was particularly influenced by requirements pertaining to sensor irradiation, which can produce leakage currents up to 100 nA. The preamplifier has a 5 fF feedback capacitor with a current-source-continuous reset, a 15 ns rise-time and operates at about 8  $\mu$ A bias. Since the input is DC-coupled, a compensation circuit is implemented that drains the leakage current and prevents it from influencing the continuous reset circuit. The implementation, shown in figure 7, uses two PMOS devices, one (M2) providing leakage current compensation and the other (M1) continuously resetting the feedback capacitor.

An important property of this feedback circuit is that the discharge current provided by the reset device saturates for high-output-signal amplitudes. The return to baseline is, therefore, nearly linear and a discriminator pulse width proportional to the input charge is obtained. The width of the discriminator output, Time-over-Threshold (ToT), can therefore be used to measure the signal amplitude. The duration of the ToT is measured by counting the cycles of the 40 MHz master chip clock. The feedback current is 4 nA for a 1  $\mu$ s return to baseline for a 20,000 electron-equivalent input. The feedback circuit has an additional diode-connected transistor M3, which acts as a level shifter so that the DC-levels of input and output nodes are nearly equal. It also simplifies the DC-coupling between the amplifier and the discriminator, as described below.

Figure 6. Schematic plan of the front-end chip (FE-I3) with main functional elements. Not to scale.

**Discriminator.** Signal discrimination is made by a two-stage circuit: a fully differential, low-gain amplifier, where the threshold control operates by modifying the input offset, and a DC-coupled, differential comparator. The first stage has a bias of about 4  $\mu$ A, whereas the second uses a current of about 5  $\mu$ A. A local threshold generator is integrated in every pixel in order to make the threshold independent of the local digital supply voltage for each pixel and on the amplifier bias current  $I_f$ . Seven-bits are used for each pixel to adjust the discriminator threshold.

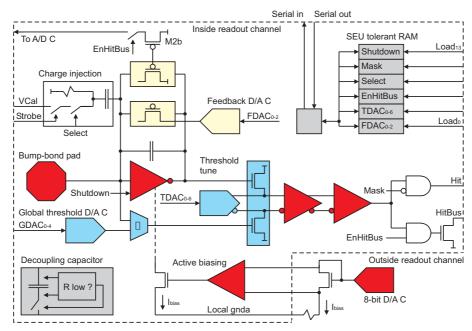

**Pixel cell control logic.** A complete block diagram of the analogue part with several additional circuit blocks is shown in figure 8. Each pixel has several parameters that can be tuned through a 14-bit control register. These bits are:

- FDAC 0-2: 3-bits to trim the feedback  $(I_f)$  current for tuning the ToT response.

- *TDAC 0-6:* 7-bits to trim the threshold in each pixel.

Figure 7. Charge preamplifier feedback circuit.

Figure 8. Pixel cell block diagram.

- MASK: the digital output of the analogue part can be switched off locally by setting this bit.

- *EnHitBus:* the digital outputs of all readout channels can be directly observed using a wired OR which is locally enabled with this bit. This bit also controls, through transistor M2b, the summing of a current proportional to the feedback plus leakage current in the preamplifier, allowing for monitoring of the feedback current and of the leakage current from the sensor.

- *Select:* enables the pixel for test charge injection. The amplitude is generated from  $V_{Cal}$  (voltage proportional to the injected calibration charge), whereas the timing comes from an external *Strobe* signal.

- *Shutdown:* disables the charge amplifier so that no output is generated from the pixel.

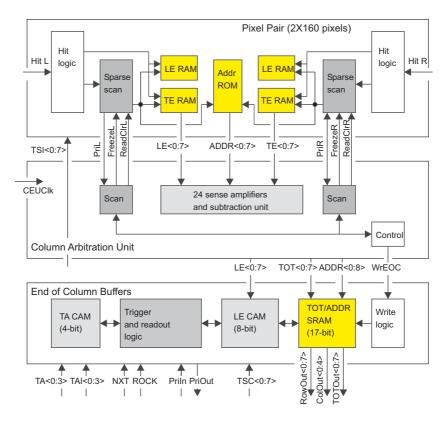

Figure 9. Block diagram of the column-pair readout.

**Pixel cell readout logic.** A block diagram of the column-pair readout is shown in figure 9. LE and TE timestamps are temporarily stored in local memories before being transferred to the hit-buffers at the chip periphery. A digital circuit generates two short (1 *ns*) strobes at the LE and TE comparator edges. These signals are used to store the 8-bit Gray-coded time stamp in two memories. The time stamps, generated at the chip periphery, running at 40 MHz, are distributed differentially in order to decrease the digital crosstalk to the analogue circuits and the sensor electrodes. The complete hit information is available after the TE of the comparator signal and data transfer starts. The time stamp of the LE (8-bits), of the TE (8-bits) and the row number (8-bits) are transferred to the end-of-column (EoC) buffers. Transfer happens by a priority mechanism that selects cells with data starting from the top row. The topmost cell with a hit transfers its data to the bus and all the cells below it are inhibited. When the cell is read out, it releases the priority encoder bus and subsequent hits are selected and put on the readout bus. The readout speed is limited by the time the priority logic needs to ripple down. Hits can ripple through at a programmable speed that is obtained from the 40 MHz clock division. The maximum speed at which bytes can be transferred to the EoC is 20 MHz.

**Column readout controller.** The readout is column based, and two columns are read out from the same controller. The first task of the controller is the generation of the readout sequence to transfer hit information: LE and TE timestamps, and the pixel-row address into an EoC buffer. This operation begins when data is complete, which is after the TE discriminator is activated. The transfer of hits from a column pair is synchronized by the Controller end-of-Column Unit (CEU),

which operates at a selectable speed of 5, 10, or 20 MHz. A total of 64 hit buffers are available for each double-column. The second task involves digital processing of the hit data. Hit information is formatted by the CEU. Formatting includes the ToT calculation: subtraction of a TE time stamp from a LE timestamp. Optionally, a digital threshold may be applied to the ToT, and a timewalk (time slewing for small charges with respect to high charge) correction may be applied (write a hit twice if below correction threshold, once with LE and once with LE - 1, or both. These operations are pipelined to minimize deadtime, but the EoC writes cannot occur faster than 20 MHz. Hit information is written to the EoC buffer, where it waits for a corresponding L1 trigger. If a trigger arrives at a time corresponding to the LE time stamp plus a programmable trigger latency, the hit is flagged as belonging to a particular 4-bit trigger number. Otherwise, it is reset and the buffer is cleared. Once the chip has received one or more L1 triggers, the trigger FIFO will no longer be empty. This initiates a readout sequence in which the EoC buffers are scanned for the presence of hits belonging to a particular trigger number. If hits are found, they are sent to the output serializer block, which encodes and transmits them to the MCC. After all hits for a given trigger number have been sent, an End-of-Event (EoE) word is appended to the data stream. All of these operations occur concurrently and without deadtime, with all column pairs operating independently and in parallel.

Event readout from the EoC buffers happens concurrently with the column readout. When the chip-level readout controller starts processing a particular L1 event, it first broadcasts the corresponding L1 readout address to all buffers. All cells with hits waiting for readout compare their stored L1 address with a request value. The readout of the selected L1 hits is controlled by a priority network, which sorts them in column and row order.

**Chip level readout controller.** The chip-level readout controller collects hit data from the EoC buffers and transmits the results off the chip serially. All hits belonging to the same L1 are grouped together into a single event, and events are transmitted out of the chip in consecutive trigger order. When a L1 trigger arrives, the current bunch-crossing time and a buffer-overflow bit are stored in a FIFO memory, which has a depth of 16 locations. This allows the chip to keep track of 16 pending L1 signals. The write-pointer of the FIFO is used as the L1 identification, which is sent to the hit buffers. The readout sequence is started as soon as the FIFO receives an L1 trigger. If the L1 priority scan in the hit buffers flags cells with matching trigger numbers, the data of the first cell in the hierarchy is sent to a global data bus, where the information is copied to a shift register. The content of the shift register is then transmitted serially. This is repeated until the priority scan shows no more hits. An End-of-Event data word, which includes error flags, is then added to the event.

**Chip configuration.** FE-I3 has 231 global configuration bits plus 14 local bits for each of the 2880 readout channels. The global bits are the settings for eleven 8-bit bias-current DACs, for one 10-bit calibration voltage DAC, for the global threshold bits, for the L1 latency, for the ToT filter thresholds, for column-enable bits, as well as for others. The configuration is loaded into the chip using a serial protocol running at 5 MHz. This protocol uses three chip input pads: a data input, a clock and a load. Each write operation begins with a 4-bit address, which permits the 16 chips in a module to receive independent configurations. The address of each chip is encoded with wire bonds during module assembly.

#### 4.2.3 Requirements, performance and production

The design requirements for the pixel front-end electronics come from operation at high radiation doses, from the time resolution of 25 ns to separate two contiguous bunch crossings, from noise, from the minimum operation threshold and dispersion and from the overall power budget. The calibration relies on a 7-bit adjustment of individual pixel thresholds (tuning). The untuned (tuned) threshold dispersion  $\sigma$  is 800 (70) electrons equivalent-input charge (e). The noise with the sensor attached is 160 e (for a pixel size of 50  $\mu$ m  $\times$  400  $\mu$ m) and the typical operating threshold is 4000 e, which results in hits with signals > 5500e appearing in the correct 25 ns time bucket (described as in-time threshold) [17, 18]. Neither the dispersion nor the noise depend on the choice of threshold. The tuned thresholds have been observed to re-disperse with moderate radiation dose in prototypes, and it is expected that periodic threshold re-tuning will be needed. However, the actual dispersion rate in the real operating environment will need to be measured. A selectable option internally duplicates near-threshold hits in two adjacent time buckets in order to allow for recovery of intime threshold inefficiencies. Measurements made on a few modules irradiated to 600 kGy show a negligible tuned threshold dispersion and a 20% increase in the noise, despite the very high induced sensor leakage current (60 nA for normal pixels at  $-7^{\circ}$ C). For a configured chip, the typical digital current is 45 mA at 2 V and the analogue current is 75 mA at 1.6 V for a total power of 220 mW.

Chip production was made in batches of 48 wafers. There are 288 chips on each 8-inch wafer. Six production batches were purchased along with the six wafers from an engineering production run. The average wafer-probing yield was about 80%. The ATLAS pixel detector contains a total of 27904 front-end chips. The wafers were probed using semi-automatic probe stations. Each chip was fully characterized including measurement of a reference calibration capacitor value using a dedicated circuit only available during probing. This removed process variations from the charge and threshold calibration scale. The test time was approximately 30 hours per wafer. Chip selections was based on the evaluation of 30 analog and digital parameters. Every chip was also probed after dicing the bumped wafers (section 6) using custom vacuum chucks to hold up to 60 chips. About 2% of the chips failed after dicing. In addition, the indium-bumped chips were photographed during probing and 160 images-per-chip archived for future reference.

# 4.3 Module Control Chip (MCC)

#### 4.3.1 MCC history

The prototype sequence leading up to the Module Controller Chip (MCC) is shown in table 4. The very first version of the chip, submitted in 1998, was fabricated in a radiation-soft process using  $0.8 \,\mu\text{m}$  CMOS technology [19]. This chip was extensively used when building radiation-soft modules. The technology was chosen as it was very close to the  $0.8 \,\mu\text{m}$  BiCMOS DMILL technology which, at the time, was the chosen radiation-hard technology for the ATLAS pixel detector.

A first prototype of the rad-hard chip (MCC-D0) was built in 1999. It contained only one Receiver, but all the remaining circuitry was implemented thereby providing a good test of the DMILL technology. The final version of the chip (MCC-D2) was submitted in August 2000. The chip worked fine but had an unacceptably low yield, for both MCC-D2 and FE-D2. Consequently, this technology was abandoned.

| (        |          | <b>(</b>  |             |                              |                          |

|----------|----------|-----------|-------------|------------------------------|--------------------------|

| Chip     | Year     | Std.Cells | Transistors | Chip size [mm <sup>2</sup> ] | Technology               |

| MCC-AMS  | Apr 1998 | 17922     | 363 000     | $10.3 \times 6.3$            | AMS 0.8µm CMOS, 2M       |

| MCC-D0   | Aug 1999 | -         | —           | 6.1 	imes 3.5                | DMILL 0.8µm BiCMOS 2M    |

| MCC-D2   | Aug 2000 | 13 446    | 328000      | $11.9 \times 8.4$            | DMILL 0.8µm BiCMOS, 2M   |

| MCC-I1   | Nov 2001 | 33 2 1 0  | 650000      | 6.38 	imes 3.98              | DSM $0.25\mu$ m CMOS, 5M |

| MCC-I2   | Feb 2003 | 67919     | 880000      | 6.84 	imes 5.14              | DSM $0.25\mu$ m CMOS, 5M |

| MCC-I2.1 | 2003     | 67919     | 880000      | 6.84 	imes 5.14              | DSM $0.25\mu$ m CMOS, 5M |

**Table 4.** Summary of the ATLAS pixel MCC chips. The number of metal layers in a chip is designated by 2M (two metal layers) or 5M (five metal layers).

At this time, the MCC was ported to the DSM  $0.25 \,\mu\text{m}$  CMOS technology, and the MCC-I1 chip was submitted in November 2001. A new version of the chip, MCC-I2, was made in 2003 in order to provide better Single Event Upset (SEU) hardening to the chip. It turned out that this chip had a small error that could be corrected by modifying only one metal line. Six additional wafers, containing the correction in the layout, were produced in 2003 leading to the final MCC-I2.1 chip.

## 4.3.2 Design

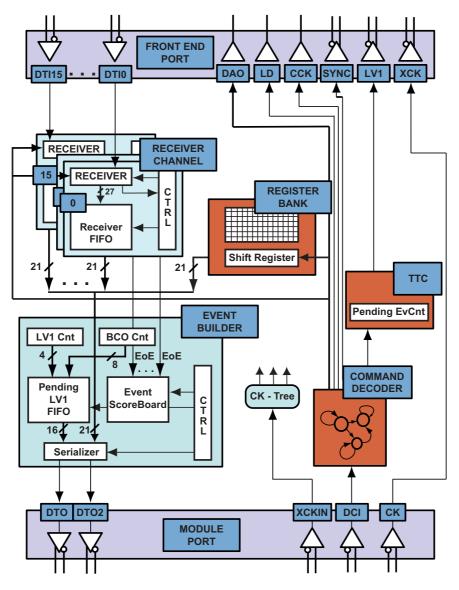

This section briefly describes the actual implementation of the production MCC chip, labeled MCC-I2.1. A simplified block diagram of the MCC internal architecture is shown in figure 10. The MCC has three main system tasks: (1) loading parameter and configuration data into the FEs and into the MCC itself; (2) distributing timing signals such as bunch-crossing, L1 trigger and resets; and (3) reading out the FE chip and event building.

**System configuration.** The FE chips and the MCC must be configured after power-up or before starting a data-taking run. It is possible to write and read to all the MCC registers and FIFOs. This is used to configure, to read status information or to test the functionality of the chip. For this last function we provide a special set of commands that allows one to write simulated events into the FIFOs and to run the Event Builder with the stored values in order to check the complete functionality of the chip. Once the MCC is embedded in the pixel detector, it will be important to test whether the event building works with known simulated events. Global FE chip registers and parameters in each of the pixel cells are written and read back through the MCC.

**Trigger, reset and timing.** The second task of the MCC is the distribution of L1 triggers, resets and calibration/timing signals for the FE chips. In *Data Taking* mode, each time a L1 trigger command is received by the MCC, the Trigger, Timing & Control (TTC) logic issues a trigger to the FEs, as long as there are less than 16 events still to be processed. In case of an overflow, the L1 trigger is not generated by the MCC and the corresponding event is lost. The information is sent to the ROD together with the number of missing events in order to keep up with event synchronisation. In addition to the triggers, the TTC logic generates a hierarchy of reset signals that can be applied either to the MCC or to one or more FE's. The last function of the TTC logic is the ability to issue calibration strobes to the FEs.This is used to calibrate the FE analogue cells on a pixel-by-pixel basis.

Figure 10. Module Control Chip block diagram.

**Event building.** The read-out logic that was chosen for the pixel detector is a data-push architecture with two levels of buffering: EoC buffers in the FE chips and 16 individual  $128 \times 27$ -bit deep FIFOs (ReceiverFIFO) at the MCC inputs.

Event readout and building is by far the most complicated task, and it occupies most of the chip area. Data received from the FEs, in response to a L1 trigger, are deserialised and buffered in 16 FIFOs, one FIFO for each receiving FE line. These FIFOs are used to derandomise the 16 data flows from the FEs and are used by the event builder to extract ordered hits and to prepare them for transmission out of the pixel module. Event building is performed by two concurrent processes running in the MCC. The first (Receiver) deals with filling the 16 input FIFOs with data received from the corresponding FE chip, while the second (Event Builder) extracts data from the FIFOs and builds up the event. Each FE sends data as soon as they are available with two constraints. Event

hits must be ordered by event number and for each event an end-of-event (EoE) word is generated. The EoE is also sent for the case of an empty event to maintain the event synchronisation.

The event transmitted to the ROD is organized by the Event Builder process on an event-byevent basis, instead of a hit-by-hit basis. If the FIFO becomes full while storing incoming hits, all subsequent hits are discarded and only the EoE word is written into the FIFO. In this case, a truncated event flag will be stored in the ReceiverFIFO and then recorded to the MCC output data stream. The mechanism ensures that reconstructed events are not corrupted by FIFO overflows.

As soon as the Event Builder finds that an event is completely received from all of the 16 FEs, it starts building up and transmitting the event. The Event Builder learns from the Scoreboard when the events are complete. The first information written to the output data stream is the bunch crossing identifier (BCID) and the L1 identifier (L1ID). At this point the Event Builder starts fetching data from the ReceiverFIFOs, until it finds an EoE in the data. Once the Event is finished, a Trailer word is sent out to inform the ROD that the Event has ended.

**I/O protocols.** Several serial protocols were defined for communication to/from the ROD/MCC and the MCC/FE. All protocols that are active during data taking use only LVDS-type signals (low-voltage differential, but not necessarily conforming to the LVDS standards), whereas signals occuring during configuration use single-ended CMOS to reduce the number of interconnection lines. Communications from the ROD to the MCC use a 40 Mb/s data line (Data Command Input – DCI) validated by the rising edge of the 40 MHz clock (CK).

The MCC to ROD link may use 40, 80 or 160 Mb/s data rates. For the case of 40 Mb/s, a new bit is transmitted at every rising edge of the CK. For the 80 Mb/s, bits are sent at both clock transitions. Finally for 160 Mb/s, both lines and clock edges are used. This can be considered as a 2-bit parallel link. Only the event readout uses the two higher bit rates. Readout of configuration data is always at 40 Mb/s. The robustness of data passing from the MCC to the ROD is improved by providing a bit-flip-safe Header and by adding synchronisation bits after a known numbers of clock cycles.

Communications from the MCC to the FE chips are accomplished using a serial CMOS data bus (Data Address Output – DAO), a CMOS control line (Load - LD) and a 5 MHz validation CMOS clock (Control Clock – CCK). Both configuration and event data from the FE to the MCC are transmitted using 16 individual LVDS serial links (Data Input - DTI). The MCC and the FE use the 40 MHz (XCK) system clock fanned out by the MCC, which is obtained from the beam crossing clock. The clock is distributed to the 16 FEs in a module using a multi-drop LVDS connections from a single MCC output.

Special care is needed in the implementation of the Data-Taking protocols in order to minimize the effect of possible Single Event Upset events. In particular, while in data taking mode, there are only two possible 5-bit commands: 'trigger' and 'exit data-taking modes'. All permutations of the trigger command, obtained by flipping one single bit, are also interpreted as a trigger command with the correct timing.

### 4.3.3 Requirements, performance and production

The design requirements include operation at high radiation dose, time resolution of 25 ns separating two contiguous bunch crossings, the expected bandwidths at the highest luminosity, the L1 trigger rate of 100 kHz and the number of FE chips that are controlled in a module.

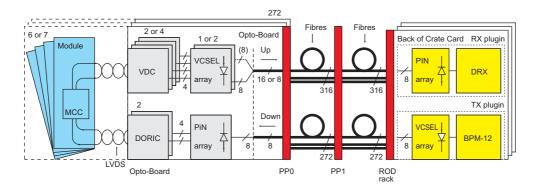

Figure 11. Optical-link system architecture.

The 16 FIFO's in the MCC were designed to handle the expected data rate of the FE chips operating at full luminosity with a L1 trigger rate of 100 kHz. In addition, the circuits were designed to be robust against a Single Event Upset (SEU). This problem was addressed using either triple redundancy majority logic or error detection and correction schemes. Several modules were irradiated up to (and in some cases beyond) the full LHC-lifetime dose, continuously reading out the data during irradiation. From these SEU studies, we expect stable operation at the LHC without a significant loss in the configuration data coming from bit-flips in the memory elements.

For a configured chip, the typical digital current is 145 mA at 2.0 V. All MCC-I2.1 chips were produced in a single batch of six wafers. The number of potentially good chips per wafer is 536. The measured yield was 83%, providing a total of 2666 good chips. A total of 1744 chips are used in the ATLAS pixel detector. The wafers were probed at a commercial vendor using supplied test vectors. Test vectors were produced using Automatic Test Pattern Generation (ATPG) design methodology together with additional hand generated vectors. The combined test vectors provided almost 100% fault coverage of the chip.

#### 4.4 Optical communication

#### 4.4.1 Optical link architecture

The communication between the detector modules and the off-detector electronics occurs via optical links. The opto-links were selected to implement electrical decoupling and to minimize the material budget. The architecture was inherited from the ATLAS SCT [20]. Modifications were made to adapt to the data-rates, modularities and radiation hardness needs of the pixel detector.

A block diagram of the optical-link system architecture is shown in figure 11. The two main components in the optical-link system are the opto-board, on the detector side, and the Back of Crate Card (BOC), on the off-detector end. In order to keep the material budget low, accommodate fiber routing requirements, control radiation exposure, and permit the use of optical arrays, the opto-components and the related receiver/driver IC's were not implemented on the detector modules. The optical components were put on the opto-boards at Patch Panel 0 (PP0), at a distance of up to about one meter from the modules and at relatively large radius, namely about 200 mm inside the Pixel Support Tube.

The transmission of the signals from the detector modules to the opto-boards uses LVDS electrical connections. These serial connections link the MCC with the VCSEL Driver Chip (VDC) and the Digital Optical Receiver IC (DORIC) sited on the opto-boards. The DORIC and VDC designs were also derived from the SCT project, but have been adapted to survive the higher radiation dose expected in the pixel detector. These chips have been fabricated on the same silicon wafers used to produce the MCC chips.

The communication with each detector module uses individual fibres: one for down-link and one or two for up-links. Trigger, clock, commands and configuration data travel on the down-link, while event data and configuration read-back data travel on the up-link(s). On the down-link, a biphase mark (BPM) encoding is used to send a 40 Mb/s control stream on the same channel as the 40 MHz Bunch Crossing (BC) clock. Decoding of the BPM channel within the DORIC recovers both the data stream and the clock signal. The use of individual links for every module permits the adjustment of the timing used to associate the hit to the bunch crossing. The timing adjustment is accomplished by changing the delay of the transmitted signal with respect to the phase of the LHC machine reference clock received in the BOC.

The readout bandwidth required to extract the hits from the detector modules depends on the LHC instantaneous luminosity, on the L1 rate and on the distance between the module and the interaction point. Simulation of the readout architecture using generated physics events [19] shows that a rate of 40 Mb/s for the Layer-2 modules, 80 Mb/s for the Layer-1 or Disk modules and 160 Mb/s for the b-layer modules are needed to keep the number of lost hits due to bandwidth saturation sufficiently low. The data transmitted in the up-links are encoded in non-return-to-zero (NRZ) format. Electrical-to-optical conversion occurs in the opto-boards on the detector side and in the optical-receiver (RX) and optical-transmitter (TX) plug-ins in the BOC.

There are two flavours of opto-boards: Disk/L1/L2-boards (D-board) with eight down-link and eight up-link channels and b-layer-boards (B-board) with seven down-links and 14 up-links. The B-boards use two 80 Mb/s channels to obtain the aggregate bandwidth of 160 Mb/s. Because of the modularity of staves (13 modules) and of sectors (six modules) D-boards use either six channels for the disk-sectors or six or seven channels for the half-staves in Layer-1 and Layer-2.

In the off-detector part of the links, one BOC serves each ROD. BOCs have a a variety of hardware options that are implemented by equipping the card with a variable number of optical-receiver or optical-transmitter plug-ins. Each plug-in, in principle, can serve up to eight modules, but, in practice, only six or seven are used due to the modularity of the detector. BOCs come with four TX plug-ins and four RX plug-ins, where the maximum bandwidth requirement is 40 Mb/s, with two TX and two RX for 80 Mb/s and with one TX and two RX for 160 Mb/s. Two custom chips have been designed by the SCT collaboration and used in the optical plug-ins: the DRX (12-channels Data Receiver ASIC in the RX) and the BPM-12 (12-channels Bi-Phase Mark encoder ASIC in the TX). In the BOC there is also the optical S-Link interface used to send the ROD output to the ATLAS Readout Buffer (ROB) units, which are the next level up in the event readout chain.

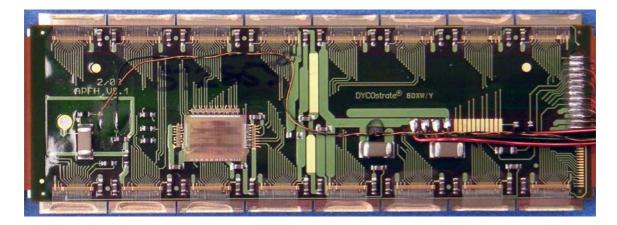

#### 4.4.2 Opto-Board

The opto-board is the optical-electrical interface on the detector side. It consists of a berylliumoxide (BeO) printed circuit board measuring  $2 \times 6.5$  cm<sup>2</sup>. As discussed in section 4.4.1, two types of opto-boards (D-boards and B-boards) exist and six or seven detector modules are connected to them. The D-boards are equipped with one PiN diode array and one VCSEL (Vertical-Cavity Surface-Emitting Laser) array, while the B-boards have a second VCSEL array. Each opto-board has two 4-channel DORIC chips, whereas two and four 4-channel VDC chips are loaded onto the D-board and B-boards, respectively. The opto-package (opto-pack), which holds the PiN/VCSEL arrays and the connector for the optical fibres, is custom designed to fulfill requirements of low mass, and be non-magnetic and radiation tolerant. The total number of opto-boards in the detector is 288. This is more than the minimum 272 (44 B-boards and 228 D-boards) needed to read out the detector so that spares are available to recover from problems during integration. Ultimately, only one spare board was used. The remaining spares are mounted on the Patch Panel 0 elements, but not connected.

**PiN diode array.** Arrays of silicon PiN diodes are used to receive the data sent by the VCSELs. Epitaxial silicon PiN diodes are used because their intrinsic layer provides a thin active layer allowing for fast operation at low PiN bias voltage. The active area of each individual PiN diode is circular with a diameter of 130  $\mu$ m, and the depth of the intrinsic region is 35  $\mu$ m [20]. A PiN current amplitude of 100  $\mu$ A ensures a Bit Error Rate (BER) less than 10<sup>-9</sup>.

**DORIC.** The Digital Optical Receiver Integrated Circuit (DORIC) amplifies the signal detected in the PiN diode and extracts the clock and data from the BPM encoded signal. Data and clock are transmitted in LVDS format to the MCC. Each DORIC chip contains four identical channels. The specification for the current from the PiN diode is in the range of 40  $\mu$ A to 1 mA. The requirements for the clock are a duty cycle of (50 ± 4) % and a time jitter better than 1 ns.

The DORIC has been designed to have a bit error rate of less than  $10^{-11}$  after a lifetimeradiation dose, for a PiN-diode bias current amplitude of  $40 \,\mu$ A. The PiN diode current amplifiers use a single-ended scheme [21], avoiding the direct application of the diode bias voltage (10 V), which is much higher than the rating of the DSM technology. The DORIC must withstand up to 170 kGy over the expected 10 years of ATLAS operation. It is, therefore, implemented in the same (0.25  $\mu$ m) CMOS technology as used for FE, MCC and VDC.

**VDC.** The VDC converts the LVDS input signal, received from the MCC, into a suitable singleended signal to drive the VCSELs in a common cathode array configuration. The VDC chips have four channels and drive one half of the VCSEL arrays. An external current used to drive the VCSEL operates up to 20 mA. The nominal current to operate the VCSEL is 10 mA. A standing (dim) current of ~1 mA is provided to improve the switching speed in the VCSEL. The dim current is remotely controlled by an external voltage. The requirement for the rise/fall time (20 to 80 %) is in the range of 0.5 to 2.0 ns, where 1.0 ns is nominal. A voltage ( $V_{I_{set}}$ ), remotely controlled, determines the current  $I_{set}$  that sets the amplitude of the VCSEL current (bright minus dim current). The chip is designed to have constant current consumption, independent of the VCSEL being bright (on) or dim (off), to avoid generating ripple (noise) on the power supply which is being shared with the two DORICs on an opto-board.

**VCSEL array.** Vertical-Cavity Surface-Emitting Laser (VCSEL) arrays are used to transmit the data optically. The main advantages of VCSELs are that they provide large optical signals at very low currents and have fast rise and fall times. In order to maintain a low laser threshold current,

VCSELs use ion-implants to selectively produce a buried current-blocking layer to funnel current through a small area of the active layer. The VCSELs [20] used in the pixel and SCT systems have an oxide implant to achieve the current confinement, which is becoming the standard VCSEL technology since it produces lower current thresholds at higher bandwidth. VCSELs are produced in arrays of eight diodes. The typical fibre-coupled-power per channel is greater than 1 mW at a drive current of 10 mA. The optical power at 10 mA is sufficient to give a noise immunity of 6.2 dB. Using a slightly higher current, it is possible to add another 1.8 dB of noise immunity [20]. The down-link, where the current is not a critical issue, can profit from this improved margin corresponding to a higher immunity to SEU and to a lower Bit Error Rate.

# 4.4.3 Back of Crate Card (BOC)

Each BOC [20, 22] is connected to one ROD through the crate back-plane. The BOC has two functions: it interfaces between the ROD and opto-links and it controls the distribution of the timing to the on- and off-detector electronics. Each BOC receives a system clock signal and redistributes it to the pixel detector modules and ROD. Each detector module needs a precise phase adjustment of its 40 MHz clock relative to the bunch-crossing time reference. The adjustment of this phase can be done for each module independently using the BPM-12 ASIC. [20] The phase of the data from the modules relative to the global BOC clock can be adjusted using the PHOS4 ASICs [23]. The adjustment range is 0–25 ns in steps of 1 ns. The clock phase can also be adjusted using the same ASIC to ensure stable data transmission to the ROD. The opto-electrical conversion and the connection to the fibres are located in two plug-in cards: TX-plug-in and RX-plug-in, respectively, for transmission and reception of optical data. The TX-plug-in has an 8-channel VCSEL array and a BPM-12 ASIC. The RX-plug-in has an 8-channel PiN diode array and a DRX ASIC. [20]

**DRX.** The DRX ASIC amplifies, discriminates and converts the signal from the PiN diode into an LVDS signal. The comparator is DC coupled and the threshold can be controlled over a current range up to  $255 \,\mu$ A by an external voltage reference generated by a DAC. The DRX chip was originally designed for the ATLAS SCT detector and contains 12 channels. Only eight channels per chip are used in the pixel BOC.

**BPM-12.** The Bi-Phase Mark (BPM-12) ASIC encodes clock and data in the Bi-Phase Mark format for the fibre optic transmission. This chip was originally designed for the SCT detector and only 8 of the 12 channels are used for the pixels. A critical specification for this component is to have a short delay between the input signals and the encoded outputs to minimize the overall L1 trigger delay. The measured delay value is 60 ns. In addition, the BPM-12 has the capability to delay data transmitted to the detector by up to 63 full clock cycles to adjust for the trigger latency. This is implemented as a coarse delay (step-size 25 ns) covering the 63 clock cylces and a fine delay (step-size of about 300 ps) to cover the full range of one clock cycle with a fine-grained phase adjustment for each module.

#### 4.4.4 Opto-fibres

The connection between the BOC and the opto-boards uses optical fibres. Two different kinds of fibres are used, Stepped Index Multi-Mode fibres (SIMM) and GRaded INdex multi-mode fibres

(GRIN). SIMM fibres have been tested to be radiation tolerant but have lower bandwidth per unit length than GRIN fibres [24]. To optimise the bandwidth and radiation tolerance, splicing of 8.1 m SIMM and 71.1 m GRIN fibres have been used. The fibres are ribbonised into 8-way ribbons, and eight ribbons are bundled together to form an optical cable. The 8.1 m length of the SIMM fibre is terminated by an MT16 connector at  $\sim 2.5$  m from PP0 (at PP1). A total of 84 cables were installed outside the Pixel Support Tube. SIMM fiber ribbons were used within the Pixel Support Tube to connect the opto-boards mounted at Patch Panel 0 with the multi-ribbon connector at PP1.

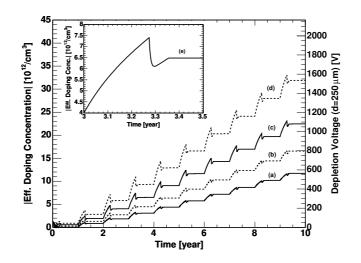

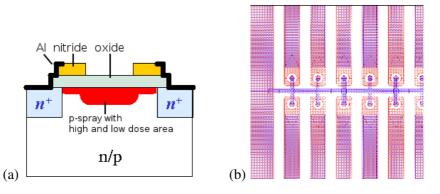

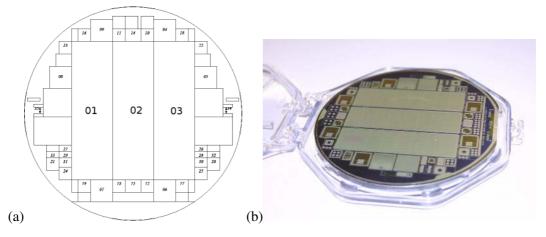

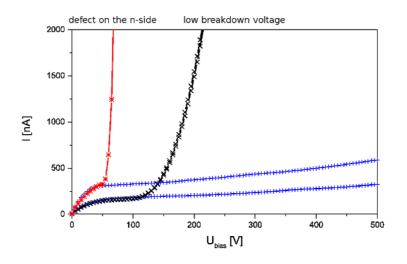

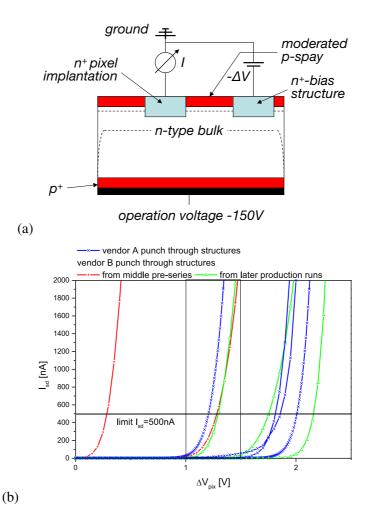

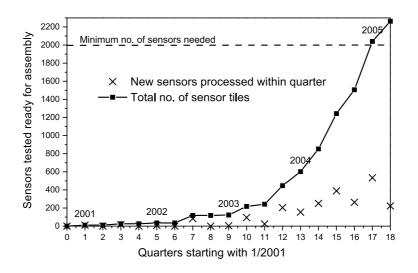

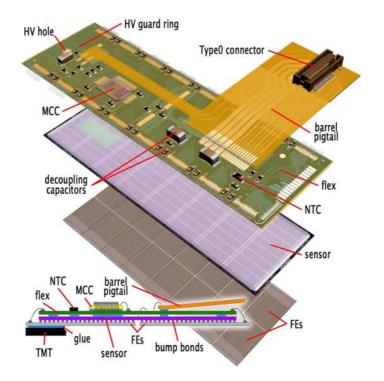

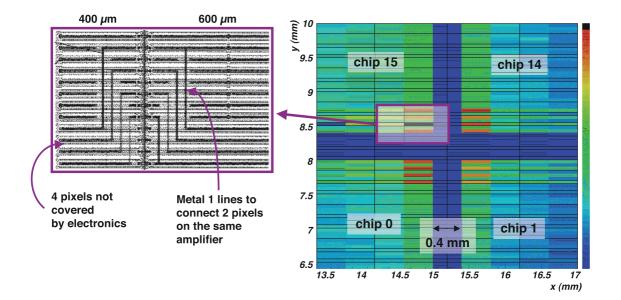

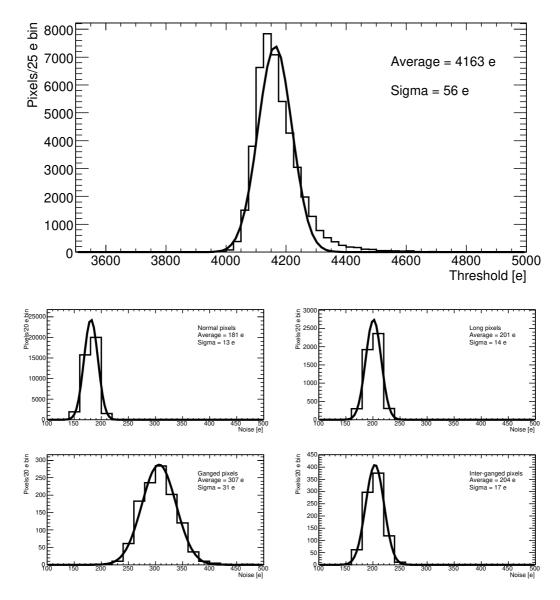

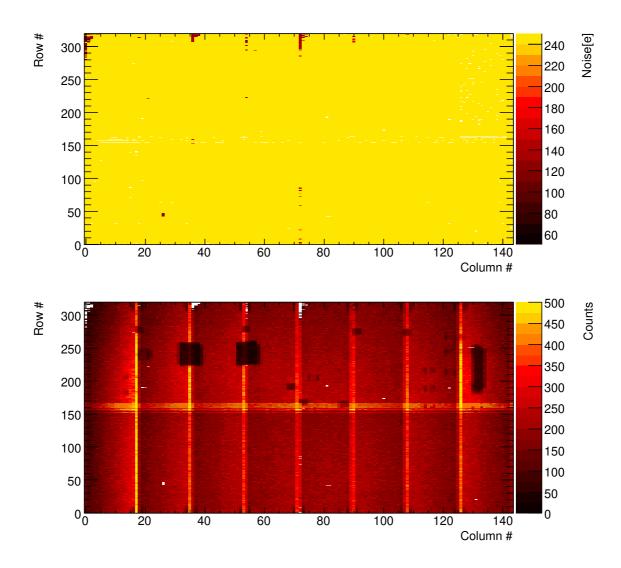

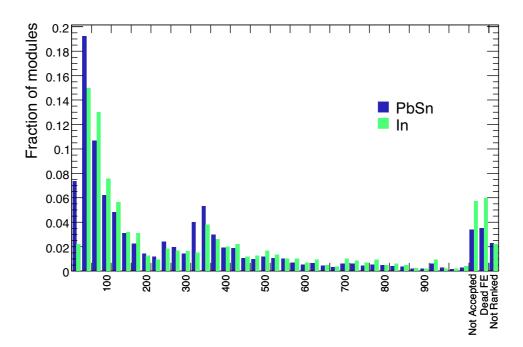

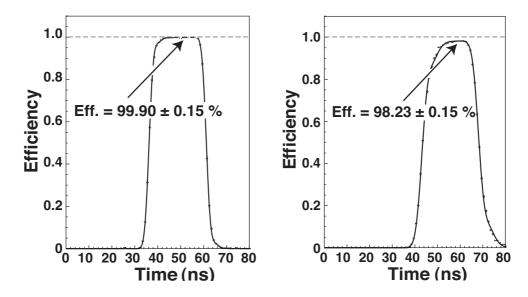

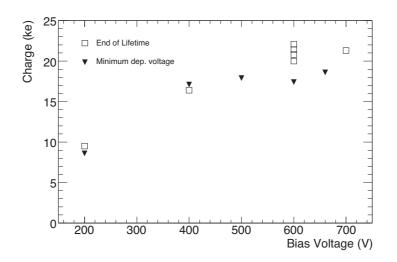

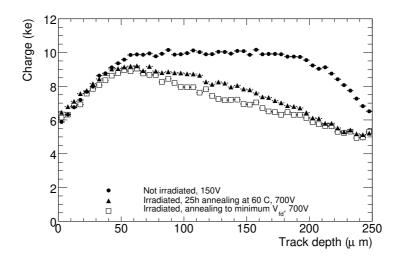

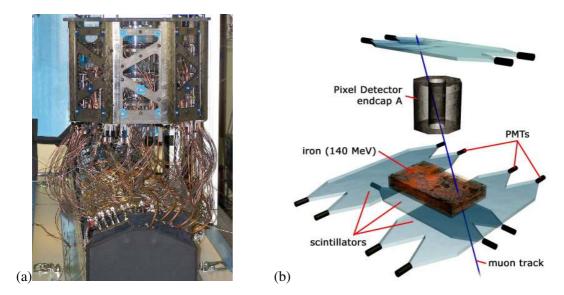

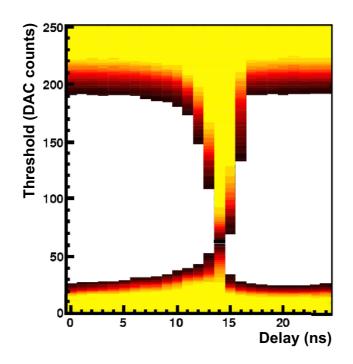

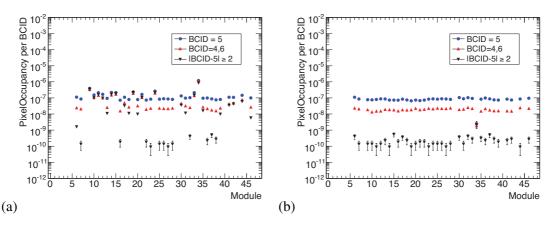

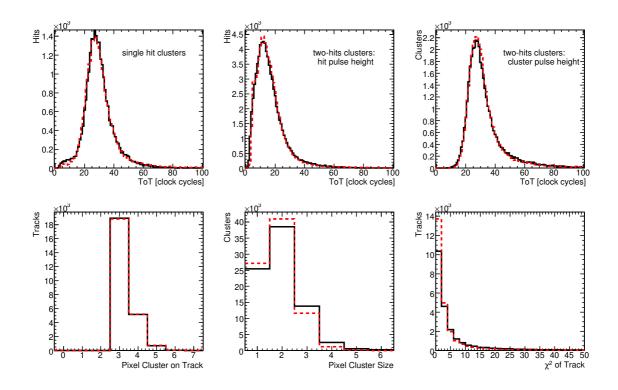

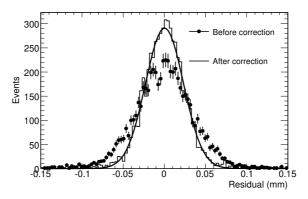

#### 4.4.5 Production and testing of opto-link components