# Atomic-scale ferroic HfO2-ZrO2 superlattice gate stack for advanced transistors

Suraj Cheema (≥ s.cheema@berkeley.edu)

University of California, Berkeley https://orcid.org/0000-0001-5878-3624

Nirmaan Shanker

University of California, Berkeley https://orcid.org/0000-0002-4102-9665

Li-Chen Wang

UC Berkeley https://orcid.org/0000-0003-0703-5030

Cheng-Hsiang Hsu

University of California, Berkeley https://orcid.org/0000-0002-6863-5606

Shang-Lin Hsu

University of california, Berkeley

Yu-Hung Liao

University of California, Berkeley

**Matthew San Jose**

University of Notre Dame

Jorge Gomez

University of Notre Dame

Wenshen Li

University of California, Berkeley

Jong-Ho Bae

University of California, Berkeley

Steve Volkman

University of California, Berkeley

**Daewoong Kwon**

University of California, Berkeley

Yoonsoo Rho

University of California Berkeley

Gianni Pinelli

Lincoln Laboratory

Ravi Rastogi

Lincoln Laboratory

**Dominick Pipitone**

Lincoln Laboratory

**Corey Stull**

Lincoln Laboratory

#### **Matthew Cook**

Lincoln Laboratory

## **Brian Tyrrell**

**Lincoln Laboratory**

#### Vladimir Stoica

Pennsylvania State University https://orcid.org/0000-0002-2734-7819

## **Zhan Zhang**

Argonne National Lab https://orcid.org/0000-0002-7618-6134

#### John Freeland

Argonne National Laboratory https://orcid.org/0000-0003-4814-5308

## **Christopher Tassone**

**SLAC National Accelerator Laboratory**

## Apurva Mehta

SLAC National Accelerator Laboratory https://orcid.org/0000-0003-0870-6932

#### **Ghazal Soheli**

**Applied Materials**

## **David Thompson**

**Applied Materials**

## Dong Ik Suh

SK Hynix Inc.

#### Won-Tae Koo

SK Hynix Inc.

#### Kab-Jin Nam

Samsung Electronics

## **Dong Jin Jung**

Samsung Electronics

## **Woo-Bin Song**

Samsung Electronics

## Chung-Hsun Lin

Intel Corporation

## Seunggeol Nam

Samsung Advanced Institute of Technology (SAIT)

## Jinseong Heo

Samsung Advanced Institute of Technology (SAIT)

## **Costas Grigoropoulos**

University of California, Berkeley https://orcid.org/0000-0002-8505-4037

## **Padraic Shafer**

Lawrence Berkeley National Laboratory https://orcid.org/0000-0001-9363-2557

## Patrick Fay

University of Notre Dame

## Ramamoorthy Ramesh

University of California, Berkeley https://orcid.org/0000-0003-0524-1332

#### Jim Ciston

Lawrence Berkeley National Laboratory

#### **Suman Datta**

University of Notre Dame

#### **Mohamed Mohamed**

Lincoln Laboratories

## Chenming Hu

Department of Electrical Engineering and Computer Science, University of California, Berkeley

## Sayeef Salahuddin

**UC** Berkeley

## Physical Sciences - Article

Keywords: transistors, HfO2-ZrO2 superlattice

Posted Date: April 16th, 2021

**DOI:** https://doi.org/10.21203/rs.3.rs-413053/v1

License: © (1) This work is licensed under a Creative Commons Attribution 4.0 International License.

Read Full License

**Version of Record:** A version of this preprint was published at Nature on April 6th, 2022. See the published version at https://doi.org/10.1038/s41586-022-04425-6.

## Atomic-scale ferroic HfO<sub>2</sub>-ZrO<sub>2</sub> superlattice gate stack for advanced transistors

- Suraj S. Cheema, 1\*† Nirmaan Shanker, 2\* Li-Chen Wang, 1 Cheng-Hsiang Hsu, 2 Shang-Lin Hsu, 2

- <sup>4</sup> Yu-Hung Liao, <sup>2</sup> Matthew San Jose, <sup>3</sup> Jorge Gomez, <sup>3</sup> Wenshen Li, <sup>2</sup> Jong-Ho Bae, <sup>2</sup> Steve Volkman, <sup>4</sup>

- 5 Daewoong Kwon,<sup>2</sup> Yoonsoo Rho,<sup>5</sup> Gianni Pinelli,<sup>6</sup> Ravi Rastogi,<sup>6</sup> Dominick Pipitone,<sup>6</sup> Corey

- <sup>6</sup> Stull, Matthew Cook, Brian Tyrrell, Vladimir A. Stoica, Zhan Zhang, John W. Freeland, <sup>8</sup>

- <sup>7</sup> Christopher J. Tassone, <sup>9</sup> Apurva Mehta, <sup>9</sup> Ghazal Soheli, <sup>10</sup> David Thompson, <sup>10</sup> Dong Ik Suh, <sup>11</sup>

- 8 Won-Tae Koo, 11 Kab-Jin Nam, 12 Dong Jin Jung, 12 Woo-Bin Song, 12 Chung-Hsun Lin, 13 Seunggeol

- 9 Nam, 14 Jinseong Heo, 14 Costas P. Grigoropoulos, 5 Padraic Shafer, 15 Patrick Fay, 3 Ramamoor-

- thy Ramesh, 1,16,17 Jim Ciston, 18 Suman Datta, 3 Mohamed Mohamed, 6 Chenming Hu, 2 Sayeef

- 11 Salahuddin<sup>2,17†</sup>

- <sup>1</sup>Department of Materials Science and Engineering, University of California, Berkeley, CA, USA

- <sup>2</sup>Department of Electrical Engineering and Computer Sciences, University of California, Berkeley,

- 14 CA, USA

- <sup>3</sup>Department of Electrical Engineering, University of Notre Dame, Notre Dame, IN, USA

- <sup>4</sup>Applied Science & Technology, University of California, Berkeley, CA, USA

- <sup>17</sup> Laser Thermal Laboratory, Department of Mechanical Engineering, University of California,

- 18 Berkeley, CA, USA

- <sup>6</sup>Lincoln Laboratory, Massachusetts Institute of Technology, Lexington, MA, USA

- <sup>20</sup> <sup>7</sup>Department of Materials Science and Engineering, Pennsylvania State University, University

- 21 Park, PA, USA

- <sup>8</sup>Advanced Photon Source, Argonne National Laboratory, Lemont, IL, USA

- <sup>9</sup>Stanford Synchrotron Radiation Lightsource, SLAC National Accelerator Laboratory, Menlo

- 24 Park, CA, USA

- <sup>25</sup> Applied Materials, Santa Clara, CA, USA

- <sup>11</sup>SK Hynix Inc., Icheon, Gyeonggi-do 17336, Korea

- $^{12}$ Semiconductor R&D Center, Samsung Electronics, Gyeonggi-do, 445-330, Korea

- <sup>13</sup>Logic Technology Development, Intel Corporation, Hillsboro, Oregon 97124, USA

- <sup>29</sup> <sup>14</sup> Samsung Advanced Institute of Technology, Samsung Electronics, Gyeonggi-do, 445-330, Korea

- 30 15 Advanced Light Source, Lawrence Berkeley National Laboratory, Berkeley, CA, USA

- <sup>31</sup> Department of Physics, University of California, Berkeley, CA, USA

- <sup>17</sup> Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, CA, USA

- <sup>18</sup>National Center for Electron Microscopy, Molecular Foundry, Lawrence Berkeley National Lab-

- oratory, Berkeley, CA, USA

- \*These authors contributed equally to this work

- <sup>†</sup>Correspondence to: s.cheema@berkeley.edu (S.S.C), sayeef@berkeley.edu (S.S.)

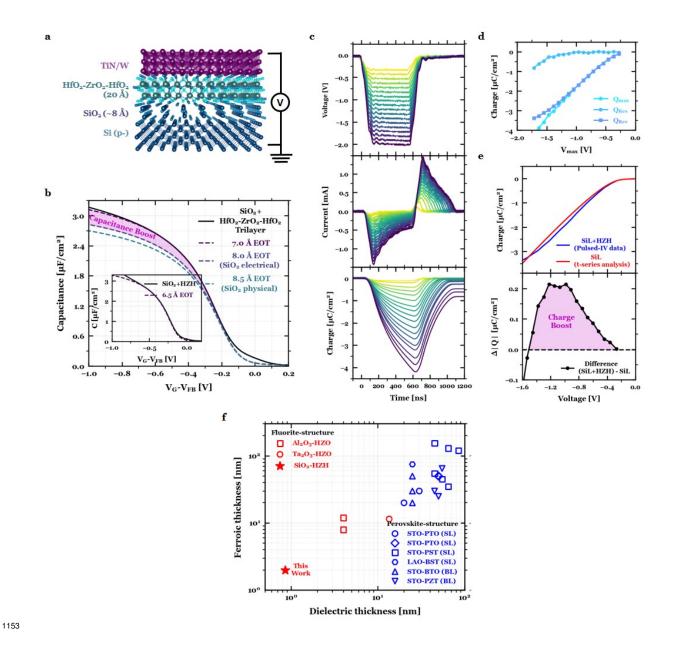

With the scaling of lateral dimensions in advanced transistors, an increased gate capacitance is desirable both to retain the control of the gate electrode over the channel and to reduce 38 the operating voltage<sup>1</sup>. This led to the adoption of high- $\kappa$  dielectric HfO<sub>2</sub> in the gate stack in 39 20082, which remains as the material of choice to date. Here, we report HfO2-ZrO2 superlattice heterostructures as a gate stack, stabilized with mixed ferroelectric-antiferroelectric order, directly integrated onto Si transistors and scaled down to  $\sim 20$  Å, the same gate oxide thickness required for high performance transistors. The overall EOT (equivalent oxide thickness) in metal-oxide-semiconductor capacitors is equivalent to  $\sim$  6.5 Å effective SiO $_2$ thickness, which is, counterintuitively, even smaller than the interfacial SiO2 thickness (8.0-8.5 Å) itself. Such a low effective oxide thickness and the resulting large capacitance cannot be achieved in conventional HfO<sub>2</sub>-based high- $\kappa$  dielectric gate stacks without scavenging the interfacial SiO<sub>2</sub>, which has adverse effects on the electron transport and gate leakage current<sup>3</sup>. Accordingly, our gate stacks, which do not require such scavenging, provide substantially lower leakage current and no mobility degradation. Therefore, our work demonstrates that HfO2-ZrO2 multilayers with competing ferroelectric-antiferroelectric order, stabilized in the 2 nm thickness regime, provides a new path towards advanced gate oxide stacks in electronic devices beyond the conventional HfO<sub>2</sub>-based high- $\kappa$  dielectrics.

With the two-dimensional scaling of silicon field-effect transistors reaching fundamental lim-54 its<sup>1</sup>, new functional improvements to transistors<sup>4</sup>, as well as novel computing paradigms and verti-55 cal device integration at the architecture-level<sup>5</sup>, are currently under intense study <sup>1,4,6</sup>. Gate oxides play a critical role in this endeavor, as it's a common performance booster for all devices, includ-57 ing silicon<sup>2</sup>, new channel materials with potential for higher performance<sup>7,8</sup>, and even materials suitable for three-dimensional integrated transistors 9,10. Indeed, the gate oxide transition from  $SiO_2$  to high- $\kappa$  dielectric (DE) is considered a paradigm shift in computing technology. In this context, ferroelectric oxides offer new functionalities 11 considered promising for energy-efficient 61 electronics<sup>4,9</sup>. The advent of atomic layer deposition (ALD) grown ferroelectric doped-HfO<sub>2</sub><sup>12</sup> has overcome much of the material compatibility issues that plague traditional perovskite-based ferroelectric materials<sup>2</sup>. In addition, considering ferroic order persists down to a thickness of 1 nm in this system 13-15 allows for integration of these oxides in the most aggressively-scaled devices in which the state-of-the-art high- $\kappa$  oxide thickness is less than 2 nm.

In an advanced silicon transistor, the gate oxide is a combination of two distinct layers. The first is an interfacial SiO<sub>2</sub> formed with a self-limiting process, resulting in  $\sim 8.0$ -8.5 Å thickness <sup>16</sup>. The next is the high- $\kappa$  (HK) dielectric HfO<sub>2</sub> layer that is typically  $\sim 2$  nm in thickness. Higher capacitance of this series combination is desirable to suppress short channel effects. The capacitance is conventionally represented by effective oxide thickness (EOT), EOT =  $t_{\text{SiO}_2} + t_{HK}/(\epsilon_{HK}/\epsilon_{\text{SiO}_2})$ , where lower EOT represents higher capacitance. Therefore, the EOT minimum value is limited by the interfacial SiO<sub>2</sub> thickness. Indeed, even integrating HfO<sub>2</sub> as the high- $\kappa$  layer, the EOT is typically  $\sim 9$  Å. To go below this value <sup>17</sup>, the semiconductor industry has implemented sophisticated scavenging techniques <sup>16,18</sup> to reduce the SiO<sub>2</sub> thickness after the full gate stack is formed. Although this technique is very effective in scaling EOT, the thinner SiO<sub>2</sub> results in undesirable leakage <sup>19</sup> and mobility degradation <sup>2,16,20,21</sup>.

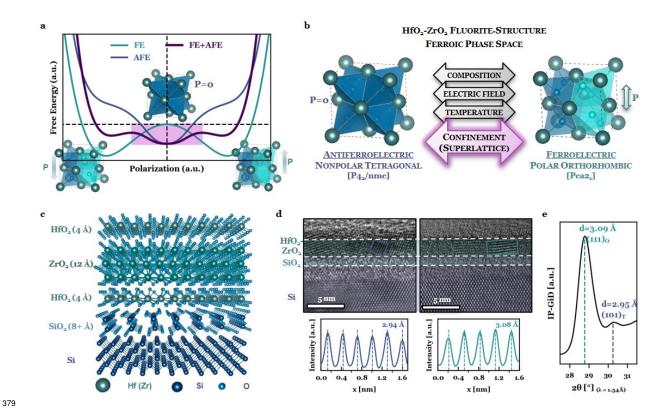

In this work, we present an ultrathin  $HfO_2$ - $ZrO_2$  superlattice gate stack that exploits mixed ferroelectric-antiferroelectric (FE-AFE) order (Fig. 1a,b). Our films demonstrate mixed ferroic order down to 2 nm thickness – the same thickness of high- $\kappa$  oxide used in advanced transis-

tors. Moreover, when integrated with silicon, it shows an overall EOT of <6.5 Å, despite the fact that both transmission electron microscopy (TEM) and electrical characterization reveal 8.0-8.5 82 Å interfacial SiO<sub>2</sub> thickness, as is typically expected. The larger capacitance than its constituent 83 layers is a signature of the charge boost stemming from the negative capacitance effect, possible in materials with ferroic order 11. The EOT shows a clear dependence on the specific sequence and layering, underlying atomic-level control of the gate oxide behavior. The fact that sub-8 Å EOT is achieved without any interfacial SiO2 scavenging results in substantially lower leakage current 87 for the same EOT compared to benchmarks established by major semiconductor industries<sup>3</sup>. In 88 addition, no mobility degradation is observed as EOT is scaled with these HfO2-ZrO2 ferroic gate stacks. Furthermore, large ON current (>  $1 \text{mA/}\mu\text{m}$ ) obtained in  $L_G = 90 \text{ nm}$  transistors indicate that there is no adverse effect on the carrier velocity. Therefore, ultrathin HfO<sub>2</sub>-ZrO<sub>2</sub> multilayers exploiting ferroic order provide a new pathway toward energy-efficient gate stacks for advanced transistors.

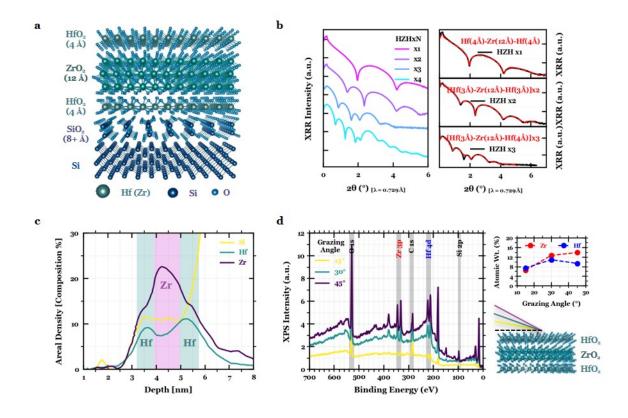

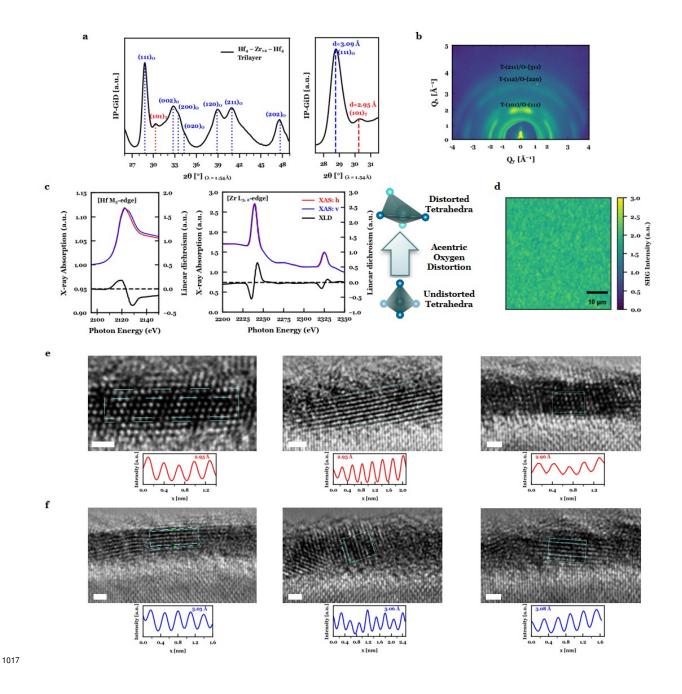

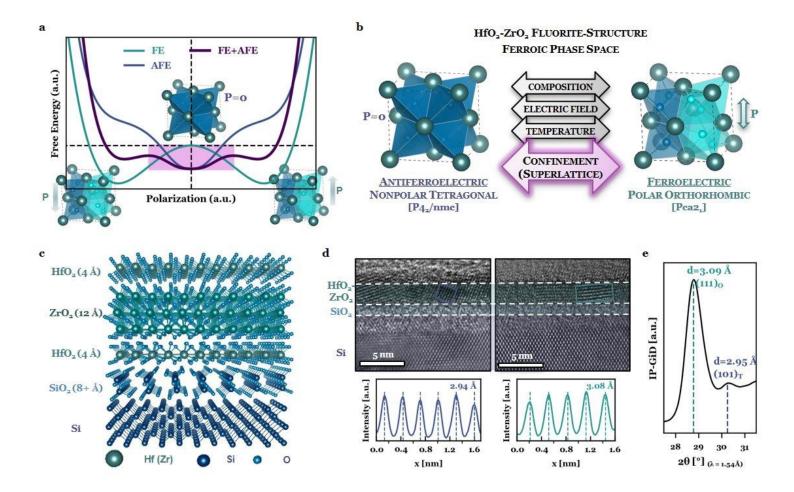

Thin films of HfO<sub>2</sub>-ZrO<sub>2</sub> are grown using ALD in which the nanolaminate periodicity is 94 dictated by the sequence of Hf:Zr (4:12) ALD cycles before the Hf-Zr superstructure is repeated 95 various times (Figure 1c, Methods). After top metal deposition, the entire gate stack undergoes a low-temperature post-metal anneal (200 C, 60s, N<sub>2</sub>) which does not interfere with the HfO<sub>2</sub>-ZrO<sub>2</sub> multilayer structure, as various characterization techniques – synchrotron x-ray reflectivity (XRR), layer-resolved electron energy loss spectroscopy (EELS) and angle-resolved X-ray photoelectric spectroscopy (XPS) - confirm the expected Hf 4 Å - Zr 12 Å periodicity (Extended Data Fig. 1). The underlying mixed ferroic order in these HfO<sub>2</sub>-ZrO<sub>2</sub> heterostructure is established by high-resolution transmission electron microscopy (TEM) (Fig. 1d, Extended Data Fig. 2e,f) and 102 in-plane grazing incidence diffraction (Fig. 1e and Extended Data Fig. 2a,b). Both techniques 103 indicate the presence of the tetragonal (P4<sub>2</sub>/nmc, T-) and orthorhombic (Pca2<sub>1</sub>, O-) phase, which 104 correspond to antiferroelctric and ferroelectric order in fluorite-structure films, respectively. Syn-105 chrotron X-ray spectroscopy and optical spectroscopy further confirm the presence of inversion symmetry breaking in the 2 nm HfO<sub>2</sub>-ZrO<sub>2</sub>-HfO<sub>2</sub> heterostructure (Extended Data Fig. 2c,d). 107

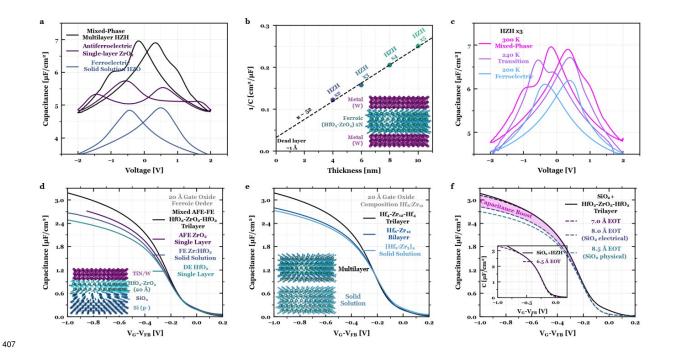

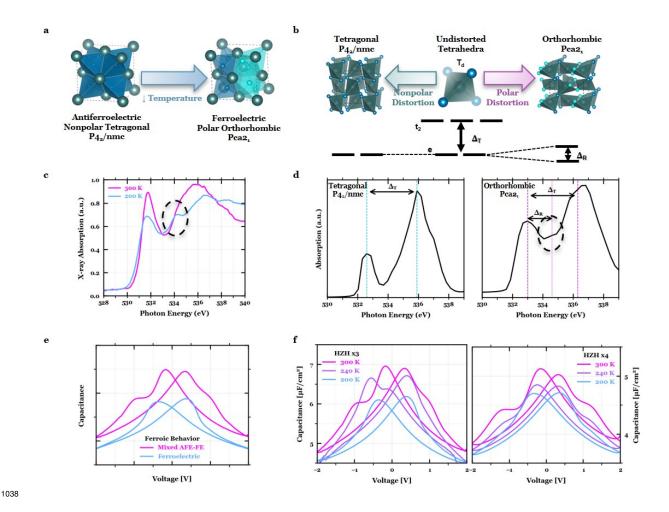

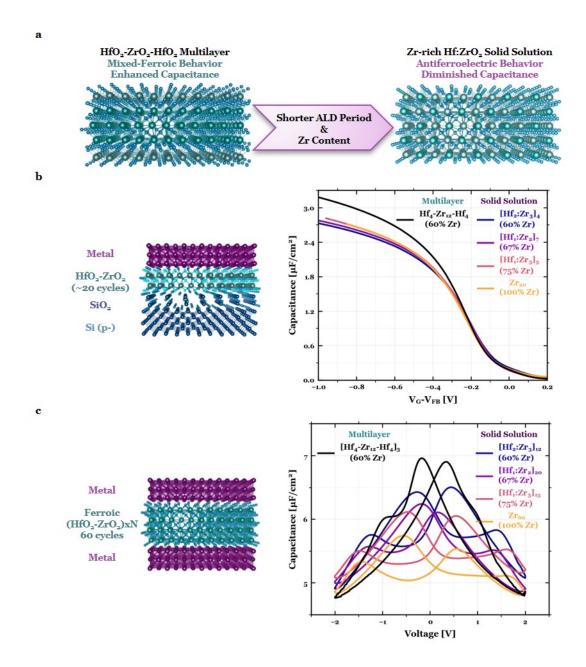

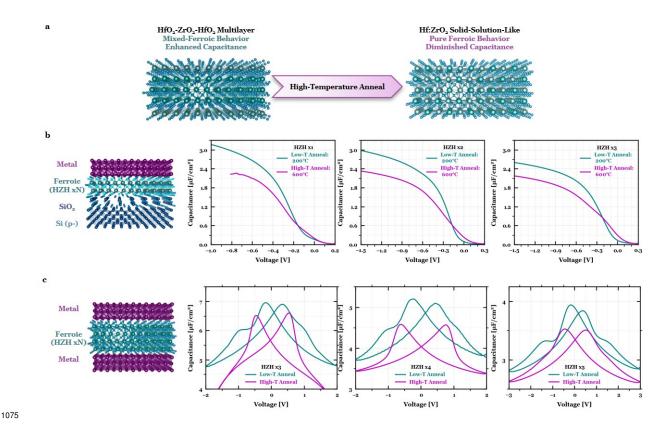

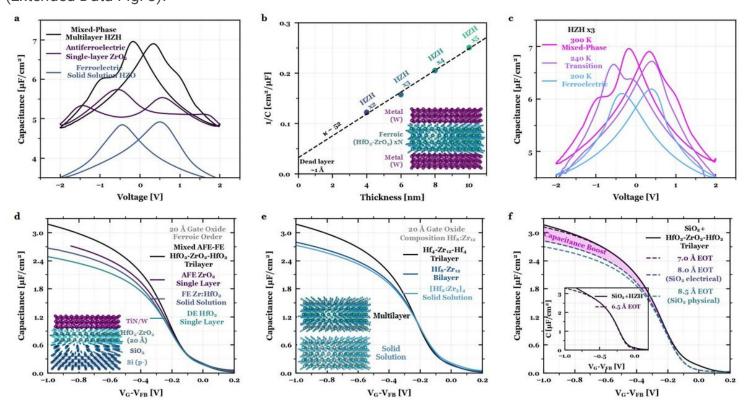

Mixed-ferroic atomic-scale  $HfO_2$ - $ZrO_2$  multilayers were designed considering FE-AFE order can tune the free energy landscape in a similar manner to the FE-DE model systems originally studied for negative capacitance stabilization  $^{11,22}$  (Fig. 1a). From the free energy landscape picture within a Landau formalism (Methods), the competition between the negative curvature (i.e. negative capacitance) of the FE and the positive curvature (i.e. positive capacitance) of the AFE can flatten the overall energy landscape, thereby substantially increasing the system's susceptibility. To confirm the higher susceptibility in the mixed AFE-FE system directly, we have performed capacitance-voltage (C-V) hysteresis loops in metal-insulator-metal (MIM) capacitor structures on thicker films with the same superlattice periodicity (Fig. 2a). Besides features indicative of mixed FE-AFE order, the total capacitance for the superlattice is larger than both conventional AFE  $ZrO_2$  and FE Zr: $HfO_2$  of the same thickness (Fig. 2a), demonstrating enhanced susceptibility. To quantify the permittivity, capacitance measurements were performed across the superlattice thickness series. These measurements yield an extracted permittivity of  $\sim 52$  (Fig. 2b, Methods), which is larger than both FE orthorhombic Zr: $HfO_2$  and AFE tetragonal  $ZrO_2$  values  $ZrO_2$ .

To further understand the ferroic evolution in these HfO<sub>2</sub>-ZrO<sub>2</sub> superlattices, we performed low temperature measurements where enhanced FE phase stabilization is expected. Indeed, temperature-dependent C-V loops for thicker HfO2-ZrO2 multilayers demonstrate an evolution from mixed-ferroic to FE-like hysteresis upon cooling slightly below room temperature (~240 K, Fig. 2c), con-sistent with temperature-dependent X-ray spectroscopy indicating transition from mixed tetragonal-orthorhombic phase to predominately orthorhombic structure at similar temperatures (Extended Data Fig. 3). The capacitance decrease upon cooling as the system moves away from the highlysusceptible mixed ferroic phase is consistent with previous work on negative capacitance in FE-DE systems<sup>22</sup> which establishes the energy landscape link between enhanced capacitance and suscep-tibility near phase transitions. Notably, the intertwined FE-AFE phases within the superlattice and resulting enhancement in susceptibility from the competition of FE and AFE phases is concep-tually similar to negative stiffness composites of ferroelastics within a metal matrix <sup>24,25</sup>, i.e. the mechanical analog to negative capacitance.

Next, the superlattices were grown on Si substrates in metal-oxide-semiconductor (MOS) 135 capacitor structures. A self-limiting chemical oxide  $SiO_2$  was grown first, resulting in  $\sim 8.0-8.5$ 136 Å thickness<sup>3</sup>, following the standard practice in advanced Si devices (Methods). Next, a 20-cycle 137 thick multilayer was grown with ALD following the same stacking as before i.e. Hf:Zr:Hf 4:12:4. 138 Accumulation C-V curves of the superlattice stack results in significantly larger capacitance in comparison to other conventional stacks – DE HfO<sub>2</sub>, AFE ZrO<sub>2</sub>, FE Zr:HfO<sub>2</sub> – of the same 20 Å 140 thickness (Fig. 2d). Furthermore, the Hf:Zr:Hf 4:12:4 trilayer demonstrates enhanced capacitance 141 compared to a bilayer (Hf:Zr 8:12) and solid solution (Hf:Zr [2:3]<sub>4</sub>) of the same thickness and 142 Hf:Zr composition (Fig. 2e). Notably, the composition in our films is close to where several previ-143 ous reports have postulated a possible morphotropic phase boundary (MPB) in thicker HfO<sub>2</sub>-ZrO<sub>2</sub> solid solution films<sup>26–30</sup>. In our ultrathin HfO<sub>2</sub>-ZrO<sub>2</sub> multilayers, the negative free energy curva-145 ture of the FE O-phase compensates the positive curvature of the AFE T-phase (Fig. 1a), leading 146 to a flattened energy landscape. Indeed, energy landscape flattening is the thermodynamic origin 147 of the MPB in the canonical perovskite ferroelectrics 31,32, in which multiple crystal symmetries 148 are nearly degenerate across a composition phase boundary<sup>33</sup>. However, a critical distinction is that here, the overall energy landscape flattening, and corresponding increase in capacitance, is 150 determined by the stacking of the atomic-scale HfO<sub>2</sub>-ZrO<sub>2</sub> layers, and not the volume fraction of 151 the constituent elements 34. For example, compared to HfO<sub>2</sub>-ZrO<sub>2</sub> solid solutions across a range of 152 typically-reported Zr-rich "MPB"-like compositions <sup>26–30</sup>, the HfO<sub>2</sub>-ZrO<sub>2</sub> multilayer demonstrates 153 larger capacitance (Extended Data Fig. 4). This indicates the enhanced capacitance in HfO<sub>2</sub>-ZrO<sub>2</sub> films is not simply driven by doping <sup>23,35</sup>, but can instead be tuned by the configuration of the 155 multilayer structure (Extended Data Fig. 4, 5). In the ultrathin regime, surface energies become 156 a more dominant consideration for determining polymorphic phase stability 36,37; accordingly, the 157 importance of stacking is amplified. Overall, these capacitor studies suggest that the exact stacking sequence plays a crucial role in stabilizing the fluorite-structure FE-AFE phase competition 159 that leads to enhanced capacitance, akin to previous reports in perovskite-based FE-DE superlat-160 tices  $^{38-42}$ . 161

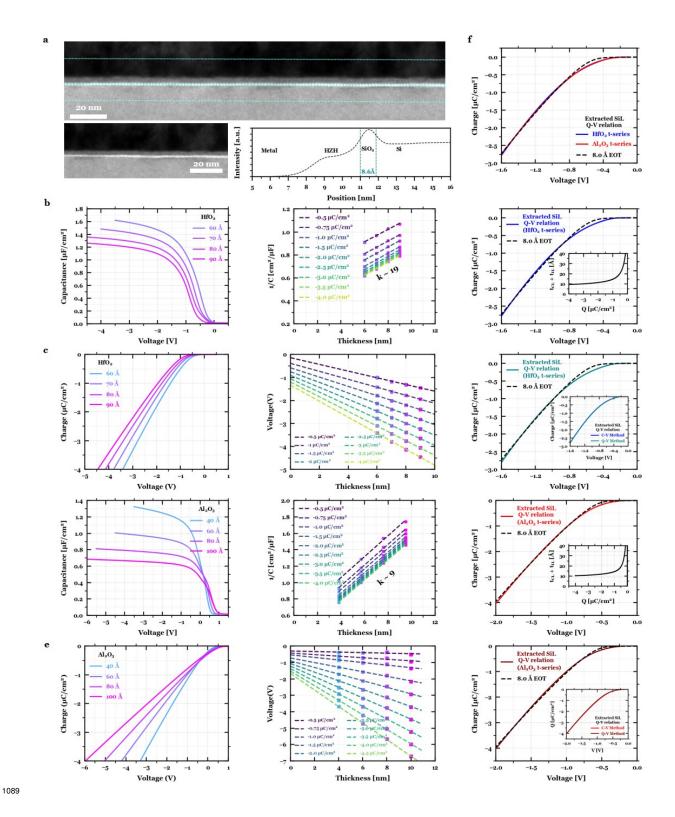

To quantify the observed capacitance, we have performed EOT simulations of MOS capac-

itors using the industry standard model Synopsys simulation platform (Methods). The Hf:Zr:Hf 4:12:4 trilayer stacks vary between 6.5-7.0 Å EOT (Fig. 2f), consistent over many measured ca-164 pacitors. Notably, this EOT is smaller than the expected thickness of the interfacial SiO<sub>2</sub> layer 165 (8.0-8.5 Å), as mentioned above. To investigate further, we performed high-resolution TEM of 166 our gate stacks (Extended Data Fig. 6), which illustrates the SiO<sub>2</sub> thickness is indeed ~8.5 Å. To supplement this physical characterization, we next implemented electrical characterization of the 168 interfacial layer via standard inverse capacitance vs thickness analysis of conventional dielectric 169 HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> thickness series grown on the same SiO<sub>2</sub> (Methods, Extended Data Fig. 6). All 170 thermal processing is kept exactly the same as the superlattice gate stack. The extracted HfO2 and 171  $Al_2O_3$  permittivity – 19 and 9, respectively – is consistent with the typical dielectric phases of these two materials. Therefore, one can reliably extract the SiO<sub>2</sub> layer thickness, yielding 8 Å (Extended Data Fig. 6), consistent with the HR-TEM results and similar to previously studies established 174 by the semiconductor industry<sup>3</sup>. Moreover, the consistent interlayer thickness extracted from both 175 material systems indicates that neither Hf nor Al encroaches into the interfacial SiO<sub>2</sub> which would 176 reduce its thickness and/or increase its permittivity. This is consistent with the fact all our stacks are processed at much lower temperature as compared to that needed for silicate formation 43. So 178 considering the interfacial layer thickness as 8 Å, the Hf:Zr:Hf 4:12:4 gate stack demonstrates an 179 overall EOT 1.0-1.5 Å lower than the constituent SiO<sub>2</sub> thickness. In other words, capacitance en-180 hancement is observed in this 20 Å mixed ferroic gate oxide integrated on Si. Therefore, the mixed 181 FE-AFE order not only improves the permittivity of the multilayer stack itself, but also couples to the SiO<sub>2</sub> in MOS capacitor structures, yielding improved overall capacitance. 183

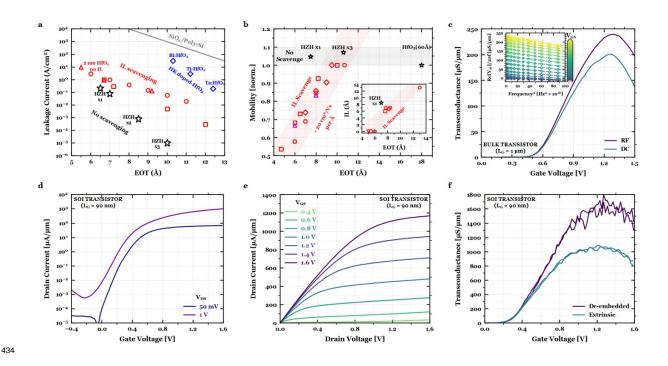

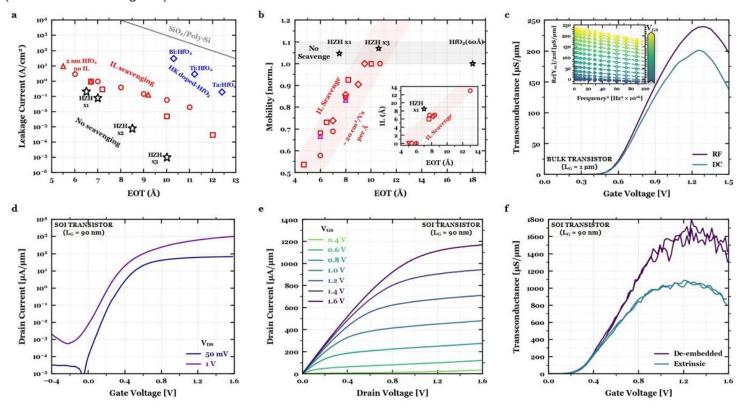

The practical implication of this capacitance enhancement can be clearly seen in Fig. 3a, which shows leakage current vs EOT behavior. The leakage current is measured at  $V_G - V_{fb} = -1$  V, where  $V_{fb}$  is the flatband voltage of the semiconductor. All other data points on this plot are taken from reported industrial gate stacks<sup>3</sup>. The leakage current for the Hf:Zr:Hf 4:12:4 stack is substantially lower at the same EOT. Note that below 9 Å, the other gate stacks need sophisticated scavenging techniques to reduce the thickness of the interfacial  $SiO_2$ <sup>3</sup>. On the other hand, we can reach  $\sim 6.5$  Å without any scavenging. This leads to the fact that the leakage current for our

184

185

186

187

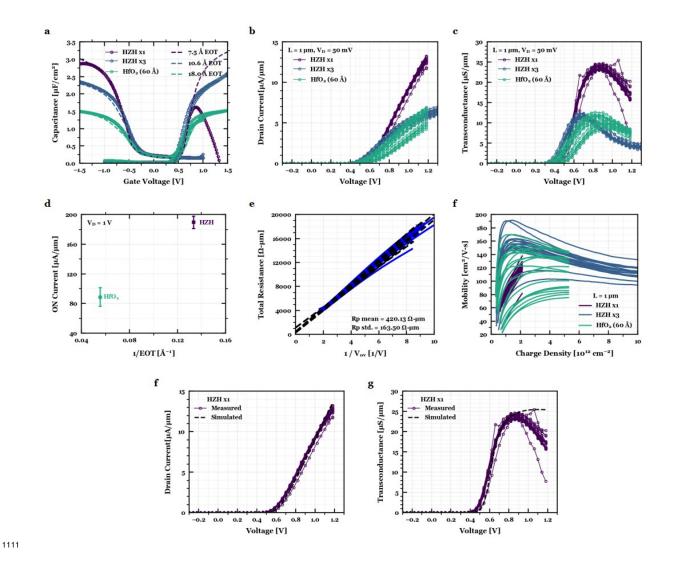

stacks is lower (Fig. 3a). Notably, the scavenging the interfacial SiO<sub>2</sub> leads to a loss of mobility due to increase in remote phonon scattering. As it has been shown 3,16, the mobility drops off with 192 a slope of  $\sim 20$  cm<sup>2</sup>/V-s per every Å of scavenged SiO<sub>2</sub>. To test how mobility is affected by 193 the superlattice gate stack, we fabricated long channel bulk transistors with two different repeats 194 of the superlattice, together with another sample that has thick (60  $\mbox{Å}$ ) HfO $_2$  as the gate stack 195 (Methods). To extract mobility, a careful fitting of the measured C-V from the transistor structures 196 is performed. In addition, series resistance is modeled from the data and de-embedded to reveal 197 the intrinsic behavior. Next, the mobility is extracted using the peak transconductance method 198 (Methods, Extended Data Fig. 8). It is found that the mobility remains essentially the same for all 199 three stacks despite the difference in materials and EOT (from 2 nm EOT for HfO2 down to sub-8 200 Å for the superlattice gate stack). First, this shows that there is no fundamental change in electron 201 transport due to the use of the superlattice gate stack compared to standard HfO2. In addition, 202 it shows that there is no penalty in mobility even below an EOT of 9 Å where conventional gate 203 stacks show a degradation due to the need for scavenging (Fig. 3b). Because the absolute value of 204 mobility depends on the specific processing technique, mobility numbers have been normalized in Fig. 3b. This clearly shows the flat mobility-EOT behavior for the superlattice gate stack compared 206 to the falling of trend for conventional gate stacks due to scavenging in the low EOT range. 207

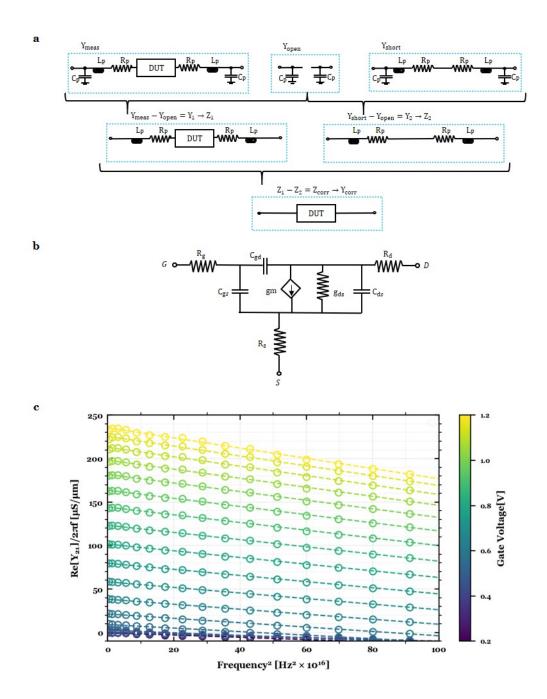

To examine how the capacitance enhancement behaves at high frequency, radio frequency (RF) measurements were performed on the same long channel ( $L_G = 1~\mu m$ ) devices (Methods, Extracted Data Fig. 9). This allows one to extract device parameters up to  $\sim 800~\text{MHz}$  for our devices (close to the cut-off frequency). Of particular interest is the transconductance ( $g_m$ ) which is proportional to the product of capacitance and electron velocity (mobility). From Y-parameter measurements one can find AC transconductance as  $Re(Y_{21}) = g_m + af^2$ , where f is the frequency (Methods). This yields an AC transconductance as a function of applied gate voltage ( $V_G$ ). This dependence is plotted together with DC transconductance ( $\partial I_D/\partial V_G$  from DC  $I_D$ - $V_G$ ) (Fig. 3c). We find that DC and AC transconductance are similar with AC transconductance roughly 15% larger at the peak value. We hypothesize that this slightly large AC transconductance results from the fact that certain interface traps, which affect the DC behavior, cannot respond at frequencies

208

209

210

212

213

214

215

217

larger than 100 MHz, leading to better gate control. More importantly, these results show that the capacitance enhancement is not limited to the low frequency regime 44-46. 220

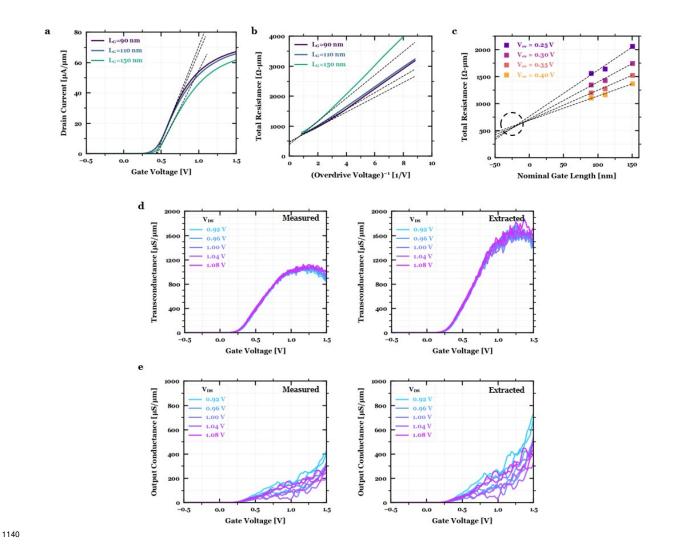

Finally, to test the ON current capability, a  $L_G = 90$  nm device was fabricated on a SOI 221 transistor with 18 nm SOI thickness and the superlattice gate stack. The transfer and output char-222 acteristic of a typical transistor are shown in Fig. 3d,e. Note that the threshold voltage of this device is 0.55 V which is consistent with the workfunction of W used as the gate metal. Because of this, the transistors have been driven up to 1.6 V gate voltage so that an overdrive voltage (Vov 225 =  $V_G$  -  $V_T$ ) of  $\sim 1$  V can be applied. It is found that at a drain voltage  $(V_D)$  and  $V_{ov}$  of 1 V, the 226 drain current exceeds 1 mA/ $\mu$ m. In addition, as shown in Fig. 3f, the measured extrinsic transcon-227 ductance is  $\sim 1.1$  mS/ $\mu$ m which gives an intrinsic transconductance of  $\sim 1.75$  mS/ $\mu$ m (Methods, 228 Extended Data Fig. 10). These values of ON current and transconductance are substantially larger than a conventional 90 nm transistor and is a result of the large capacitance provided by the super-230 lattice gate stack and the fact that the low EOT resulting from the stack does not adversely affect the electron transport. 232

223

224

231

233

234

235

236

237

238

239

241

242

243

244

With the superlattice gate stack demonstrated in integrated Si devices, we now come back to the capacitance enhancement observed in this gate stack. We have already discussed how the mixed FE-AFE order facilitates a flatter energy landscape where the negative curvature of the FE phase is compensated by the positive curvature of the AFE phase (Fig. 1a). Notably when the mixed ferroic oxide is grown on an SiO<sub>2</sub> interlayer, it can lead to similar compensation again. As we have seen from thicker FE-AFE superlattice MIM capacitors, some hysteresis still remains, which manifests at large voltages, indicative of a negative curvature regime still persisting in the superlattices. The interfacial DE SiO<sub>2</sub> can flatten out that energy landscape even further, thus leading to enhanced capacitance. This is similar to the negative capacitance and resultant capacitance enhancement observed in FE-DE series combinations<sup>22</sup>. To supplement the C-V evidence of capacitance enhancement (Fig. 2f), pulsed electrical measurements of the superlattice gate stack MOS capacitors - which can quantify the amount of stored charge as a function of voltage 47 (Methods) - demonstrate larger stored charge than if just interfacial SiO<sub>2</sub> was sitting on top of Si, providing further evidence of negative capacitance<sup>47</sup> in the gate stack (Extended Data Fig. 10). Note that previous studies have shown that negative capacitance stabilization is favored under states of high susceptibility <sup>39,40,48</sup>. Here, the competing ferroic order in HfO<sub>2</sub>-ZrO<sub>2</sub> multilayers substantially increases its susceptibility and is thus expected to facilitate negative capacitance behavior when placed on top of the interfacial SiO<sub>2</sub>.

247

248

249

250

251

252

253

254

255

258

259

260

261

263

264

265

266

267

Capacitance enhancement has been demonstrated in single-crystalline, perovskite-structure ferroelectric-dielectric superlattices by many groups <sup>38–41</sup>. This work demonstrates that the same enhancement is possible in HfO<sub>2</sub>-ZrO<sub>2</sub> fluorite-structure superlattices exhibiting mixed ferroelectricantiferroelectric order in films as thin as just  $\sim 2$  nm. The ability to control ferroic order in such ultrathin films is of critical importance for advanced electronic devices considering previous studies have shown that negative capacitance can be stabilized under states of high susceptibility<sup>39,40</sup>. Furthermore, this work establishes the critical role of atomic-layer stacking – as opposed to conventional doping techniques <sup>23,35</sup> – in controlling the ferroic phase space and permittivity of fluorite-structure oxides down to ultrathin limits, leveraging its unique size effects <sup>13–15,49</sup> and rich antiferroelectric-ferroelectric polymorphs 36,50. When this mixed phase HfO2-ZrO2 multilayer is integrated on Si, the gate stack exhibits a capacitance enhancement, lowering the EOT below the thickness of SiO2 itself, which would not be possible with a conventional dielectric. Notably, the lowest EOT achieved (6.5 Å) for the gate stack and interfacial SiO<sub>2</sub> together is lower than that used in the most advanced Si transistors today. Therefore, this work demonstrates that harnessing atomic-scale layering in ultrathin HfO<sub>2</sub>-ZrO<sub>2</sub> ferroic gate oxides presents a promising materials design platform for future Si transistors beyond conventional high- $\kappa$  dielectrics<sup>3</sup> which have enabled the semiconductor industry over the past two decades.

- 1. Theis, T. N. & Wong, H.-S. P. The End of Moore's Law: A New Beginning for Information Technology. *Computing in Science & Engineering* **19**, 41–50 (2017).

- 27. Schlom, D. G., Guha, S. & Datta, S. Gate Oxides Beyond SiO<sub>2</sub>. *MRS Bulletin* **33**, 1017–1025 (2008).

- 3. Ando, T. Ultimate Scaling of High- $\kappa$  Gate Dielectrics: Higher- $\kappa$  or Interfacial Layer Scavenging? *Materials* **5**, 478–500 (2012).

- 4. Salahuddin, S., Ni, K. & Datta, S. The era of hyper-scaling in electronics. *Nature Electronics* 1, 442–450 (2018).

- 5. Shulaker, M. M. *et al.* Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. *Nature* **547**, 74–78 (2017).

- 6. Wong, H.-S. & Salahuddin, S. Memory leads the way to better computing. *Nature Nanotechnology* **10**, 191–194 (2015).

- 7. Del Alamo, J. A. Nanometre-scale electronics with III–V compound semiconductors. *Nature* **479**, 317–323 (2011).

- 8. Butler, S. Z. *et al.* Progress, challenges, and opportunities in two-dimensional materials beyond graphene. *ACS Nano* **7**, 2898–2926 (2013).

- 9. Khan, A. I., Keshavarzi, A. & Datta, S. The future of ferroelectric field-effect transistor technology. *Nature Electronics* **3**, 588–597 (2020).

- <sup>287</sup> 10. Dutta, S. *et al.* Monolithic 3D Integration of High Endurance Multi-Bit Ferroelectric FET for Accelerating Compute-In-Memory. In *2020 IEEE International Electron Devices Meeting* (*IEDM*), 36.4.1–36.4.4 (IEEE, 2020).

- Salahuddin, S. & Datta, S. Use of Negative Capacitance to Provide Voltage Amplification for

Low Power Nanoscale Devices. *Nano Letters* 8, 405–410 (2008).

- 12. Böscke, T. S., Müller, J., Bräuhaus, D., Schröder, U. & Böttger, U. Ferroelectricity in hafnium

oxide thin films. *Applied Physics Letters* 99, 102903 (2011).

- <sup>294</sup> 13. Cheema, S. S. *et al.* Enhanced ferroelectricity in ultrathin films grown directly on silicon.

Nature **580**, 478–482 (2020).

- 14. Lee, H.-J. *et al.* Scale-free ferroelectricity induced by flat phonon bands in HfO<sub>2</sub>. *Science* **369**, 1343–1347 (2020).

- 15. Noheda, B. & Iniguez, J. A key piece of the ferroelectric hafnia puzzle. *Science* **369**, 1300–1301 (2020).

- 16. Ando, T. *et al.* Understanding mobility mechanisms in extremely scaled HfO<sub>2</sub> (EOT 0.42 nm) using remote interfacial layer scavenging technique and  $V_t$ -tuning dipoles with gate-first process. In 2009 IEEE International Electron Devices Meeting (IEDM), 1–4 (IEEE, 2009).

- 17. Wong, H. & Iwai, H. On the scaling of subnanometer EOT gate dielectrics for ultimate nano CMOS technology. *Microelectronic Engineering* **138**, 57–76 (2015).

- 18. Huang, J. Gate first high-k/metal gate stacks with zero SiOx interface achieving EOT=0.59nm for 16nm application. In *2009 Symposium on VLSI Technology* (2009).

- 19. Yeo, Y.-C., King, T.-J. & Hu, C. Direct tunneling leakage current and scalability of alternative gate dielectrics. *Applied Physics Letters* **81**, 2091–2093 (2002).

- 20. Barraud, S., Thevenod, L., Cassé, M., Bonno, O. & Mouis, M. Modeling of remote Coulomb scattering limited mobility in MOSFET with HfO<sub>2</sub>/SiO<sub>2</sub> gate stacks. *Microelectronic Engineering* **84**, 2404–2407 (2007).

- 21. Ota, H. *et al.* Intrinsic Origin of Electron Mobility Reduction in High-k MOSFETs From Remote Phonon to Bottom Interface Dipole Scattering. In *2007 IEEE International Electron Devices Meeting*, 65–68 (IEEE, 2007).

- 22. Khan, A. *et al.* Experimental evidence of ferroelectric negative capacitance in nanoscale heterostructures. *Applied Physics Letters* **99**, 113501 (2011).

- 23. Müller, J. *et al.* Ferroelectricity in Simple Binary ZrO<sub>2</sub> and HfO<sub>2</sub>. *Nano Letters* **12**, 4318–4323 (2012).

- 24. Lakes, R. S., Lee, T., Bersie, A. & Wang, Y. C. Extreme damping in composite materials with negative-stiffness inclusions. *Nature* **410**, 565–567 (2001).

- 25. Jaglinski, T., Kochmann, D., Stone, D. & Lakes, R. S. Composite Materials with Viscoelastic Stiffness Greater Than Diamond. *Science* **315**, 620–622 (2007).

- 26. Park, M. H. *et al.* Morphotropic Phase Boundary of Hf<sub>1</sub>\*<sub>x</sub>Zr<sub>x</sub>O<sub>2</sub> Thin Films for Dynamic Random Access Memories. *ACS Applied Materials & Interfaces* **10**, 42666–42673 (2018).

- 27. Ni, K. et al. Equivalent Oxide Thickness (EOT) Scaling With Hafnium Zirconium Oxide

High-κ Dielectric Near Morphotropic Phase Boundary. In 2019 IEEE International Electron

Devices Meeting (IEDM), 7.4.1–7.4.4 (IEEE, 2019).

- 28. Mehmood, F., Mikolajick, T. & Schroeder, U. Lanthanum doping induced structural changes and their implications on ferroelectric properties of Hf<sub>1</sub>\*<sub>x</sub>Zr<sub>x</sub>O<sub>2</sub> thin film. *Applied Physics Letters* **117**, 092902 (2020).

- 29. Das, D. & Jeon, S. High- $\kappa$  Hf $_x$ Zr $_{1-x}$ O $_2$  Ferroelectric Insulator by Utilizing High Pressure

Anneal. *IEEE Transactions on Electron Devices* **67**, 2489–2494 (2020).

- 333 30. Kim, S. *et al.* Method to Achieve the Morphotropic Phase Boundary in  $Hf_xZr_{1-x}O_2$  by Electric 334 Field Cycling for DRAM Cell Capacitor Applications. *IEEE Electron Device Letters* **42**, 517–520 (2021).

- 31. Budimir, M., Damjanovic, D. & Setter, N. Piezoelectric response and free-energy instability in the perovskite crystals BaTiO<sub>3</sub>, PbTiO<sub>3</sub>, and Pb(Zr, Ti)O<sub>3</sub>. *Physical Review B* **73**, 174106 (2006).

- 339 32. Fu, H. & Cohen, R. E. Polarization rotation mechanism for ultrahigh electromechanical response in single-crystal piezoelectrics. *Nature* **403**, 281–283 (2000).

- 33. Ahart, M. *et al.* Origin of morphotropic phase boundaries in ferroelectrics. *Nature* **451**, 545–548 (2008).

- 343 34. Noheda, B. *et al.* A monoclinic ferroelectric phase in the  $Pb(Zr_{1-x}Ti_x)O_3$  solid solution. 344 *Applied Physics Letters* **74**, 2059–2061 (1999).

- 345 35. Schroeder, U. *et al.* Recent progress for obtaining the ferroelectric phase in hafnium oxide based films: impact of oxygen and zirconium. *Japanese Journal of Applied Physics* **58**, SL0801 (2019).

- 348 36. Materlik, R., Künneth, C. & Kersch, A. The origin of ferroelectricity in  $Hf_{1-x}Zr_xO_2$ : A computational investigation and a surface energy model. *Journal of Applied Physics* **117**, 134109 (2015).

- 37. Bergeron, H., Lebedev, D. & Hersam, M. C. Polymorphism in Post-Dichalcogenide Two-Dimensional Materials. *Chemical Reviews* **121**, 2713–2775 (2021).

- 353 38. Gao, W. *et al.* Room-Temperature Negative Capacitance in a Ferroelectric–Dielectric Superlattice Heterostructure. *Nano Letters* **14**, 5814–5819 (2014).

- 355 39. Zubko, P. *et al.* Negative capacitance in multidomain ferroelectric superlattices. *Nature* **534**, 524–528 (2016).

- 40. Yadav, A. K. *et al.* Spatially resolved steady-state negative capacitance. *Nature* **565**, 468–471 (2019).

- 41. Das, S. *et al.* Local negative permittivity and topological phase transition in polar skyrmions.

Nature Materials **20**, 194–201 (2021).

- 42. Íñiguez, J., Zubko, P., Luk'yanchuk, I. & Cano, A. Ferroelectric negative capacitance. *Nature Reviews Materials* **4**, 243–256 (2019).

- 43. Schlom, D. G. & Haeni, J. H. A Thermodynamic Approach to Selecting Alternative Gate

Dielectrics. MRS Bulletin 27, 198–204 (2002).

- 44. Chatterjee, K., Rosner, A. J. & Salahuddin, S. Intrinsic speed limit of negative capacitance transistors. *IEEE Electron Device Letters* **38**, 1328–1330 (2017).

- 45. Kwon, D. *et al.* Response Speed of Negative Capacitance FinFETs. 2018 IEEE Symposium

on VLSI Technology 49–50 (2018).

- 46. Alam, M. A., Si, M. & Ye, P. D. A critical review of recent progress on negative capacitance field-effect transistors. *Applied Physics Letters* **114**, 090401 (2019).

- 47. Hoffmann, M. *et al.* Unveiling the double-well energy landscape in a ferroelectric layer.

Nature **565**, 464–467 (2019).

- 48. Wong, J. C. & Salahuddin, S. Negative Capacitance Transistors. *Proceedings of the IEEE* **107**, 49–62 (2019).

- <sup>375</sup> 49. Wei, Y. *et al.* A rhombohedral ferroelectric phase in epitaxially strained  $Hf_{0.5}Zr_{0.5}O_2$  thin films. *Nature Materials* **17**, 1095–1100 (2018).

- 50. Reyes-Lillo, S. E., Garrity, K. F. & Rabe, K. M. Antiferroelectricity in thin-film ZrO<sub>2</sub> from first principles. *Physical Review B* **90**, 140103 (2014).

Fig. 1. Atomic-scale design of negative capacitance in ultrathin HfO<sub>2</sub>-ZrO<sub>2</sub>. (a) Phenomenological model of negative capacitance (NC) in a mixed ferroic system. Landau free energy land-scapes for a FE, AFE, and mixed FE-AFE system (Methods). Mixed FE-AFE phase competition should suppress polarization <sup>48</sup> and enhance electric susceptibility <sup>22,40</sup> via proximity to a phase boundary, and flattens the energy landscape, desirable traits for NC stabilization. The stable energy minimum of the composite free energy landscape, corresponding to the negative curvature (NC) regime of the ferroelectric energy landscape, is highlighted. (b) Engineering ferroic phase competition in the HfO<sub>2</sub>-ZrO<sub>2</sub> fluorite-structure system. Beyond the conventionally-studied tuning parameters – composition, electric field, temperature <sup>23,35</sup> – here we introduce dimensional confinement via superlattice layering to tailor ferroic phase competition at the atomic-scale. (c) Schematic of the HfO<sub>2</sub>-ZrO<sub>2</sub> fluorite-structure multilayer on Si; the heterostructures maintain distinct layers (i.e. not solid solution alloys) based on EELS, XRR, and depth-resolved XPS (Extended Data Fig. 1). The role of the layering on the underlying ferroic order and capacitance is studied by electrical

measurements as a function of HfO<sub>2</sub>-ZrO<sub>2</sub> stacking structure and annealing temperature (Extended Data Fig. 4 and 5, respectively). (d) HR-TEM image of the atomic-scale HfO<sub>2</sub>-ZrO<sub>2</sub>-HfO<sub>2</sub> trilayer 394 (top) and extracted d-lattice spacings (bottom) corresponding to the fluorite-structure AFE tetrago-395 nal (P4<sub>2</sub>/nmc, red) and FE orthorhombic (Pca2<sub>1</sub>, blue) phases, respectively. The layer delineations 396 are approximate, as the HfO2-ZrO2 and SiO2 interlayer thicknesses are more rigorously deter-397 mined by XRR and TEM analysis (Extended Data Fig. 1 and 6, respectively). Note imaging the 398 crystallinity of the HfO<sub>2</sub>-ZrO<sub>2</sub> layers requires mistilt with respect to the Si lattice (Methods). (e) 399 Synchrotron IP-GiD demonstrating the presence of both the AFE T-phase (101) $_t$  and FE O-phase 400  $(111)_o$  reflections whose d-lattice spacings are consistent with those extracted from TEM. Detailed 401 indexing to higher-order reflections for structural identification of the ferroic phases is provided 402 by wide-angle synchrotron diffraction (Extended Data Fig. 2a). Further evidence of inversion 403 symmetry breaking is provided by second harmonic generation and synchrotron linear dichroism 404 (Extended Data Fig. 2c,d). Additionally, the evolution between these two ferroic phases are also 405 studied as a function of temperature (Extended Data Fig. 3). 406

Fig. 2. Enhanced capacitance in ultrathin HfO<sub>2</sub>-ZrO<sub>2</sub> mixed-ferroic heterostructures. (a) MIM *C-V* hysteresis loops for a mixed FE-AFE HfO<sub>2</sub>-ZrO<sub>2</sub> multilayer demonstrating higher capacitance compared against its AFE (ZrO<sub>2</sub>) and FE (Zr:HfO<sub>2</sub>) counterparts of the same thickness. (b) Inverse capacitance versus thickness of the MIM HfO<sub>2</sub>-ZrO<sub>2</sub> multilayers up to 5 superlattice repeats (10 nm), with an extracted permittivity of 52 (Methods), extremely large for HfO<sub>2</sub>-based oxides. (c) MIM *C-V* hysteresis loops for HfO<sub>2</sub>-ZrO<sub>2</sub> multilayers of the same periodicity demonstrating an evolution from mixed-ferroic to FE-like hysteresis upon cooling slightly below room temperature. The proximity to the temperature-dependent phase transition (Extended Data Fig. 3) suggests the HfO<sub>2</sub>-ZrO<sub>2</sub> heterostructures lies near its maximum electric susceptibility position, ideal for negative capacitance stabilization <sup>40,48</sup>. (d) MOS accumulation *C-V* of HfO<sub>2</sub>-ZrO<sub>2</sub>-HfO<sub>2</sub> trilayer compared to AFE ZrO<sub>2</sub>, FE Zr:HfO<sub>2</sub>, and DE HfO<sub>2</sub>, all of the same thickness (20 Å), indicating mixed-ferroic behavior is optimal for enhancing capacitance rather than purely FE or AFE behavior. (e) Accumulation *C-V* of the HfO<sub>2</sub>-ZrO<sub>2</sub>-HfO<sub>2</sub> trilayer compared to bilayer and solid solutions films of the same thickness (ALD cycles) and composition (Hf:Zr cycles). Inset: Schematic of multilayer (Hf and Zr cations vertically separated) versus solid solution (Hf and Zr cations inter-

mixed). These results suggest the capacitance enhancement in multilayer films is not simply driven by Hf:Zr composition<sup>23,35</sup>, but instead the atomic-scale stacking (Extended Data Fig. 4, 5). (f) Ac-424 cumulation C-V curves for a 2 nm HfO<sub>2</sub>-ZrO<sub>2</sub>-HfO<sub>2</sub> trilayer grown on sub-nm SiO<sub>2</sub> fit to effective 425 oxide thickness (EOT) simulations (Methods). Inset: Externally verified MOS accumulation C-426 V of the same trilayer stack (Methods), demonstrating 6.5 Å EOT. The 2 nm trilayer on top of 427 SiO<sub>2</sub> demonstrates lower EOT than the thickness of SiO<sub>2</sub> interlayer alone, carefully extracted via 428 physical (8.5 Å) and electrical (8.0 Å) methodologies (Extended Data Fig. 6), providing evidence 429 of capacitance enhancement. Furthermore, these 2 nm ferroic gate stacks demonstrate amplified 430 charge from pulsed *I-V* measurements relative to the SiO<sub>2</sub> interlayer (Extended Data Fig. 10). 431 Notably, this 2 nm HfO<sub>2</sub>-ZrO<sub>2</sub> multilayer on sub-nm SiO<sub>2</sub> provides the most scaled demonstration 432 of charge and capacitance enhancement at the capacitor-level (Extended Data Fig. 10).

Fig. 3. Device performance benefits utilizing ultrathin mixed-ferroic HfO<sub>2</sub>-ZrO<sub>2</sub> gate stacks.

(a) Leakage-effective oxide thickness ( $J_G$ -EOT) scaling of the multilayer gate stacks (black) benchmarked against reported HKMG literature<sup>3</sup>, including interlayer-scavenged 2 nm HfO<sub>2</sub> (red), high- $\kappa$  doped HfO<sub>2</sub> (blue), and SiO<sub>2</sub>/poly-Si (gray). The leakage is the lowest reported for a 6.5-7.0 Å EOT MOS capacitor on silicon<sup>3</sup>, due to the EOT reduction without requiring interlayer SiO<sub>2</sub> thickness reduction. (b) Normalized mobility versus EOT scaling of the multilayer gate stacks (black) benchmarked against reported HKMG literature<sup>3</sup>, including interlayer-scavenged 2 nm HfO<sub>2</sub> (red) and hybrid silicate-scavenged interlayer (magenta). For EOT scaling in conventional HKMG systems, the SiO<sub>2</sub> interlayer has to be reduced to lower EOT, which leads to degraded mobility<sup>3</sup>. In this case, enhanced capacitance in HfO<sub>2</sub>-ZrO<sub>2</sub> multilayers achieves scaled EOT without having to thin the SiO<sub>2</sub> interlayer; therefore, mobility is not degraded. Inset: SiO<sub>2</sub> interlayer thickness versus EOT scaling comparing the 7.0 Å EOT HfO<sub>2</sub>-ZrO<sub>2</sub>-HfO<sub>2</sub> trilayer against notable HKMG literature which employ interlayer scavenging to reduce EOT<sup>3</sup>. This scatter plot highlights the underlying reason for the enhanced leakage-EOT and mobility-EOT behavior in the ultrathin trilayer gate stacks: low EOT without reduced SiO<sub>2</sub> interlayer thickness. (c) Transconductance (g<sub>m</sub>) versus

gate voltage ( $V_G$ ) for long-channel bulk transistors ( $L_G = 1 \mu m$ ) obtained from both DC (derivative of  $I_D$ - $V_G$ ) and RF (Re[ $Y_{21}$ ]) measurements (Methods) at  $V_{DS} = 1$  V. Inset: De-embedded  $Re[Y_{21}]$ 451 (open circles) as a function of squared frequency at different DC  $V_{\it GS}$  bias points extrapolated to 452 the zero frequency limit (dotted lines) to extract the RF  $g_m$  (Extended Data Fig. 8). The high-453 frequency measurements help suppress defect contributions which would otherwise dampen the 454 intrinsic  $g_m$ . (d, e, f) DC *I-V* transfer characteristics ( $I_D$ - $V_G$ , d), DC output characteristics ( $I_D$ - $V_D$ , 455 e), and DC transconductance ( $g_m$ - $V_G$ , f) for short-channel ( $L_G$  = 90 nm) SOI transistors. Notably, 456 the maximum on-current and  $g_m$  at  $V_{DS}$  = 1 V exceeds 1 mA/ $\mu$ m and 1 mS/ $\mu$ m. DC mobility 457 and transconductance values are carefully extracted after de-embedding the series resistance from 458 double-swept *I-V* measurements (Extended Data Fig. 7 and 9, respectively).

#### 460 Methods

#### 461 Gate stack

Gate oxide Thin films of HfO<sub>2</sub>-ZrO<sub>2</sub> were grown by atomic layer deposition (ALD) in a 462 Fiji Ultratech/Cambridge Nanotech tool (U.C. Berkeley) at 270°C in which tetrakis (ethylmethy-463 lamino) hafnium and tetrakis (ethylmethylamino) zirconium precursors are heated to 75°C and water vapor is used as the oxidant. For metal-ferroelectric-insulator-semiconductor (MFIS) capac-465 itor structures, sub-nm chemically-grown  ${\rm SiO_2}$  on lightly-doped  ${\rm Si~(10^{15}~cm^{-3})}$  was prepared by 466 the standard clean (SC-1) solution (5:1:1 H<sub>2</sub>O:H<sub>2</sub>O<sub>2</sub>:NH<sub>4</sub>OH at 80°C for 10 minutes) after the Si 467 wafer was cleaned in Piranha (120°C for 10 minutes) to remove organics and HF (50:1 H<sub>2</sub>O:HF 468 at room temperature for 30 s) to remove any native oxide. Subsequently, HfO<sub>2</sub>-ZrO<sub>2</sub> multilayers are deposited at 270°C by ALD. After ALD deposition, post-deposition annealing (PDA) was per-470 formed at 175°C (20 min, forming gas N<sub>2</sub>/H<sub>2</sub> background) to help cure the SiO<sub>2</sub>-oxide interface. 471 For confirmation and reproducibility, HfO<sub>2</sub>-ZrO<sub>2</sub> multilayers of the same ALD cycling were also 472 deposited at MIT Lincoln Laboratory (MIT LL); after ALD deposition, PDA was performed at 473 250°C (1 min, N<sub>2</sub> background).

Gate metal For UC Berkeley capacitors, the first layer of the gate metal, TiN, is deposited by ALD (250°C, 20 cycles, 15 Å) in  $N_2$  and  $H_2$  plasma. Subsequently, W is deposited by sputtering (room temperature, 60 nm). For MIT LL capacitors, the gate metal, TiN, is deposited by PVD (room temperature).

Annealing The entire gate stack undergoes a low-temperature post-metal anneal (200 C, 1 min,  $N_2$ ) to cure interface defects. This low temperature does not interfere with the HfO<sub>2</sub>- $2 \text{ TrO}_2$  multilayer structure, as confirmed by various characterization techniques (Extended Data Fig. 1), and maintains the mixed ferroic behavior, as high-temperature annealing would induce purely ferroelectric behavior (Extended Data Fig. 5). X-ray diffraction and TEM confirm the

presence of crystalline ultrathin films despite the low deposition temperature, afforded by the low crystallization temperature of ZrO<sub>2</sub><sup>51</sup>. In fact, non-post-annealed ALD-grown ZrO<sub>2</sub> has previously demonstrated crystallization into the ferroelectric orthorhombic phase on Si<sup>52</sup>.

#### Device fabrication

487

MOS and MIM capacitors, Bare Structures For MOS capacitor structures, after gate stack deposition, top electrodes are defined by photolithography and dry etching. For bare structures (structural studies), the top metal is removed by chemical etching to expose the gate oxide surface. For metal-insulator-metal (MIM) capacitors, W is deposited by sputtering (room temperature, 30 nm) on a lightly-doped Si substrate as the bottom metal electrode. After ferroic film deposition by ALD, 60 nm of W is deposited by sputtering. The top electrodes are then again defined by photolithography and dry etching.

The n-type bulk transistors were fabricated by a non-self-aligned gate-**Bulk transistors** 495 last process on bulk silicon wafers ( $10^{17}$  cm $^{-3}$ ) with local oxidation of silicon (LOCOS) as device 496 isolation technique. First, a 10 nm of SiO<sub>2</sub> thermal oxide and a 30 nm of low-pressure chemical 497 vapor deposition (LPCVD) Si<sub>3</sub>N<sub>4</sub> were grown on the Si substrates. After the active region was 498 defined by photolithography and Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> etching, dry oxidation was performed to form the LOCOS isolation. Next, the source/drain regions were defined by photolithography and ion im-500 plantation with an ion dose of  $3 \times 10^{15}$  ions/cm<sup>2</sup>. The dopants were then activated by a rapid thermal 501 anneal (RTA) at 900°C for 7 min in N<sub>2</sub> ambient. The gate stacks with the sub-nm chemically-grown 502 SiO<sub>2</sub>, 2 nm HfO<sub>2</sub>-ZrO<sub>2</sub> heterostructure, and 100 nm of sputtered W gate were then deposited. Af-503 ter the gate fingers (from 500 nm to 50  $\mu$ m) were patterned by photolithography and etched by 504 inductively-coupled plasma (ICP) metal etching, the 400 nm thick interlayer dielectric (ILD) SiO<sub>2</sub> 505 was deposited using plasma-enhanced CVD (PECVD). Last, after the contact hole opening, the 506 Ti/TiN contact metal was deposited by sputtering, defined by photolithography, and then etched by 507 ICP metal etching. 508

**Short-channel SOI Transistors** The n-type short-channel transistors were fabricated by a 509 non-self-aligned gate-last process on SOI substrates with a gate length ( $L_G$ ) down to 90 nm. First, 510 the device layer was thinned down to 20 nm and the active regions were defined by photolithography with expose regions etched slightly into the buried oxide. The hydrogen silsequioxane (HSQ) 512 negative resist were written by e-beam lithography as a hard mask for the ion implantation with a dose of  $5 \times 10^{15}$  ions/cm<sup>2</sup>. The dopant activation was conducted in an RTA at 900°C for 15 seconds in N2 ambient. The gate stacks with the sub-nm chemically-grown SiO2, 2 nm HfO2-ZrO2 het-515 erostructure, 1.5 nm of PEALD TiN, and 100 nm of sputtered W were sequentially deposited. The 516 gate region (250 nm) was then patterned by photolithography. Like the back-end process for the 517 bulk transistors, a 400 nm of ILD and a sputtered Ti/TiN contact metal were deposited and defined by photolithography and ICP etching.

#### **Microscopy** 520

533

511

**Transmission electron microscopy** Electron microscopy was performed at the National 521 Center for Electron Microscopy (NCEM) facility of the Molecular Foundry at Lawrence Berkeley 522 National Laboratory (LBNL). The high-resolution bright field TEM images of HfO<sub>2</sub>-ZrO<sub>2</sub> thin 523 films were performed by FEI ThemIS 60-300 microscope with image aberration corrector operated 524 at 300 kV (Fig. 1d, Extended Data Fig. 2e,f). To prepare cross-sectional TEM samples of HfO<sub>2</sub>-ZrO<sub>2</sub> thin films, mechanical polishing was employed by using an Allied High Tech Multiprep at 526 a  $0.5^{\circ}$  wedge to thin down the total thickness of samples down to 10  $\mu$ m. Later, Ar ion milling 527 of the Gatan Precision Ion Milling System was utilized to make an electron-transparent sample, 528 starting from 4 keV down to 200 eV as final cleaning energy. For high-resolution imaging, in order 529 to capture the crystallinity of the HfO<sub>2</sub>-ZrO<sub>2</sub> layers, the zone axis alignment required varying 530 degrees of mistilt with respect to the Si lattice, explaining the slightly obscured Si atomic columns 531 (Fig. 1d, Extended Data Fig. 2e,f). 532

The local interplanar d-spacing in the ultrathin HfO<sub>2</sub>-ZrO<sub>2</sub> films (Extended Data Fig. 2e,f) was measured by DigitalMicrograph software using its line profile plus integration width analy-

sis. For the 2 nm HfO<sub>2</sub>-ZrO<sub>2</sub>-HfO<sub>2</sub> multilayer film, the extracted interplanar lattice spacings were averaged over multiple lattice periodicities and confirmed across various local regions of the film 536 (Extended Data Fig. 2e,f). The SiO<sub>2</sub> interlayer thickness from low-magnification wide field-of-537 view (FoV) imaging was determined by the same method (Extended Data Fig. 6a). In particular, 538 the intensity line scan from the wide FoV image (Extended Data Foig. 6a) is obtained from averag-539 ing across the entire FoV specified by the teal-colored box ( $\sim 150$  nm). Next, the inflection points of the intensity peak were used as the criteria to set the boundaries of the SiO<sub>2</sub> interlayer (Extended 541 Data Fig. 6a). This methodology was also utilized to determine the boundaries of the HfO<sub>2</sub>-ZrO<sub>2</sub> 542 layers from the EELS spectrum (Extended Data Fig. 1c). Regarding the wide FoV cross-sectional 543 TEM (Extended Data Fig. 6a), both the low atomic weight and lack of crystallinity of the SiO<sub>2</sub> 544 layer contribute to its weak scattering (bright color), which aids in the visual delineation of the layer boundaries and the thickness extraction from the corresponding averaged intensity line scan. 546

Optical microscopy Second harmonic generation (SHG) measurements (Extended Data Fig. 2d) were performed with a Ti:sapphire femtosecond laser (Tsunami, Spectra Physics,  $\lambda \sim 800$  nm, frequency  $\sim 80$  MHz). The linearly polarized femtosecond laser beam was focused through 50X objective lens (NA  $\sim 0.42$ ) which results in a focal spot size of 2  $\mu$ m. The generated SHG signal was collected through the same objective lens and separated from the fundamental beam by the harmonic separator. After passing through the optical bandpass filter, the SHG signals were registered to the photon multiplier tube (PMT) without a polarizer. The fundamental beam was mechanically chopped, and the signal collected by the PMT was filtered by a lock-in amplifier to reduce the background noise. For SHG spatial mapping, a two-axis piezo stage was utilized and the coordinate was synchronized with the PMT signal. The SHG intensity was obtained by averaging the mapping signals across a  $100~\mu\text{m} \times 100~\mu\text{m}$  sample area.

#### 558 X-ray characterization

547

548

550

551

552

553

555

556

**X-ray reflectivity** Synchrotron X-ray reflectivity (XRR) – performed at Sector 33-BM-C 559 beamline of the Advanced Photon Source, Argonne National Laboratory and at Beamline 2-1 of the 560 Stanford Synchrotron Radiation Lightsource, SLAC National Accelerator Laboratory – confirmed 561 the thickness of HfO<sub>2</sub>-ZrO<sub>2</sub> heterostructures (Extended Data Fig. 1b). The overall thickness of 562 the  $HfO_2$ - $ZrO_2$  heterostructures is consistent with the growth rate ( $\sim 1 \text{ Å/cycle}$ ) of ALD-grown 563 Zr:HfO<sub>2</sub> as demonstrated in our previous work <sup>13</sup>. Furthermore, the presence of irregularly spaced 564 fringes in the thicker HfO2-ZrO2 heterostructures suggests the presence of well-separated HfO2-565 ZrO<sub>2</sub> layers, i.e. not a solid solution. This is confirmed by XRR fitting (Extended Data Fig. 1b) 566 performed with the python package GenX<sup>53</sup> which considers factors such as density, roughness, 567 and thickness. 568

Grazing incidence diffraction: in-plane Synchrotron in-plane grazing-incidence diffrac-569 tion (GID) (Fig. 1e and Extended Data Fig. 2a) was performed at Sector 33-ID-D beamline of 570 the Advanced Photon Source, Argonne National Laboratory. A Pilatus-II 100K Area Detector 571 mounted on the del-arm was used to collect diffraction signal with a grazing incidence geometry. 572 The region-of-interest on the detector was set such that the ring-like signal was fully integrated. Inplane GID was collected by sweeping the in-plane angle  $\nu$  (8-50°) with a fixed out-of-plane grazing 574 angle  $\delta$  ( $\delta = 0.9^{\circ}$ ); the corrected Bragg angle ( $2\theta$ ) over which the data is plotted and indexed is de-575 termined from the relationship  $\cos 2\theta = \cos \nu \cdot \cos \delta$  set by the geometry of the diffractometer. 576 The X-ray source was fixed at 16 keV ( $\lambda = 0.775$  Å). In-plane diffraction yields more diffraction 577 peaks with better defined width, likely due to the preferred orientation and disc-shape domains in the film. Therefore, in-plane GID enables clear indexing to the ferroelectric orthorhombic (Pca2<sub>1</sub>) 579 and antiferroelectric tetragonal (P4<sub>2</sub>/nmc) fluorite structure in the ultrathin HfO<sub>2</sub>-ZrO<sub>2</sub> films, as 580 the presence of many reflections from the in-plane GID spectra (Fig. 1e, Extended Data Fig. 2a) 581 allow for clear distinction from other nonpolar fluorite-structure polymorphs. Such diffraction 582 spectra would be otherwise prohibited in typical out-of-plane geometry due to the lack of vertical 583 diffraction planes and the large linewidth inherent to ultrathin films. 584

Two-dimensional diffraction Two-dimensional reciprocal space maps (Extended Data Fig. 585 2b) were measured at Beamline 11-3 of the Stanford Synchrotron Radiation Lightsource, SLAC 586 National Accelerator Laboratory. Rayonix MX225 CCD area detector collected diffraction flux in 587 gazing incidence (< 0.20°) geometry; the X-ray source (50 microns vertical x 150 microns hor-588 izontal beam size) was fixed at 12.7 keV. The sample-detector work distance was set to 80 mm to enable detection of a wide region of reciprocal space (Q-range 0.2 to 5  $\text{\AA}^{-1}$ ) at the expense of 590 reciprocal space resolution, set by the pixel size. The two-dimensional diffraction scans – in which 591 a wide portion of the entire reciprocal space was collected simultaneously, rather than at discrete 592 regions in  $Q_x$ - $Q_y$  space – were averaged over data collection time and for repeated scans. These 593 measurement features, in tandem with the high X-ray flux afforded by the synchrotron source, en-594 abled sufficient diffraction signal detection and contrast in films just two nanometers in thickness. Data analysis was performed Nika, an Igor Pro package for correction, calibration and reduction of 596 two-dimensional areal maps into one-dimensional data<sup>54</sup>. Two-dimensional reciprocal space maps 597 on bare HfO2-ZrO2 heterostructures confirm the presence of crystalline ultrathin films despite the 598 low deposition temperature, afforded by the low crystallization temperature of ZrO<sub>2</sub> on Si<sup>51</sup>.

**Ferroic phase identification from diffraction** For fluorite-structure thin films, the main 600 phases to consider are the dielectric monoclinic (P2<sub>1</sub>/c), antiferroelectric tetragonal (P4<sub>2</sub>/nmc), 601 and ferroelectric orthorhombic (Pca2<sub>1</sub>) phases. Various diffraction reflections from the wide-angle 602 IP-GiD spectra enable indexing to the orthorhombic Pca2<sub>1</sub> phase. Lattice parameters (a, b, c) 603 - determined via Bragg's law from the  $d_{200}$  family of reflections - are self-consistently checked 604 against the (111) lattice spacing  $\frac{1}{d_{111}^2} = \frac{1}{a^2} + \frac{1}{b^2} + \frac{1}{c^2}$  as well as other higher-order reflections present 605 in the in-plane diffraction spectra (Extended Data Fig. 2a). For example, the lattice parameters 606 extracted from the {200} peaks were a = 5.36 Å, b = 5.23 Å, and c = 5.47 Å. This corresponds to a 607  $d_{211}$  lattice spacing of 2.209 Å, which agrees well with the lattice spacing (2.205 Å) obtained from Bragg's law based on the peak position (Extended Data Fig. 2a) 609

The monoclinic phase was ruled out due to a lack of two  $\{111\}$  peaks in the diffraction spectra and the  $(111)_o$  and  $(101)_t$  reflections being significantly offset from its expected peak position

in the monoclinic phase. With regards to the indexing of tetragonal (101)-t peak (Extended Data Fig. 2a), it is always reported that the tetragonal  $(101)_t$  reflection has a smaller d-spacing <sup>55</sup> in thicker HfO<sub>2</sub>-based films <sup>28</sup>, and is therefore expected to be present at a higher angle compared to the orthorhombic  $(111)_0$  reflection, which is the case in the indexed diffraction spectra (Extended Data Fig. 2a) based on the self-consistent indexing methodology outlined above provides.

In terms of extracting the phase fraction of the tetragonal and orthorhombic phases, while

Rietveld refinement has been applied to grazing incidence x-ray diffraction of thick (10 nm)

Zr:HfO<sub>2</sub><sup>56</sup> to determine the orthorhombic phase fraction, that methodology cannot be applied in

the ultrathin regime, as the films are highly oriented, as opposed to fully polycrystalline (Extended

Data Fig. 2b), which is a requirement to apply Rietveld refinement.

**X-ray absorption spectroscopy** Hard and soft synchrotron X-ray spectroscopy (Extended 622 Data Fig. 2c) was measured at beamline 4-ID-D of the Advanced Photon Source, Argonne National Laboratory and Beamline 4.0.2. of the Advanced Light Source, Lawrence Berkeley National 624 Laboratory, respectively. Spectroscopy measurements were taken at the oxygen K-edge (520-550) 625 eV), zirconium  $M_{3,2}$ -edge (325-355 eV), hafnium  $M_3$ -edge (2090-2150 eV), and zirconium  $L_{3,2}$ -626 edge (2200-2350 eV). X-rays were incident at 20° off grazing. XAS (XLD) was obtained from the 627 average (difference) of horizontal and vertical linearly polarized X-rays. To eliminate systematic artifacts in the signal that drift with time, spectra measured at ALS were captured with the order 629 of polarization rotation reversed (e.g., horizontal, vertical, vertical, and horizontal) in successive 630 scans, in which an elliptically polarizing undulator tuned the polarization and photon energy of the 631 synchrotron X-ray source<sup>57</sup>. Spectra measured at ALS were recorded under total electron yield 632 (TEY) mode<sup>57</sup> from room temperature down to 100 K. Spectra measured at APS were recorded under various modes: total electron yield (TEY), fluorescence yield (FY), and reflectivity (REF). 634

Ferroic phase identification from spectroscopy X-ray spectroscopy provides various signatures to distinguish the competing ferroelectric orthorhombic  $(Pca2_1)$  and antiferroelectric tetrag-

onal (P4<sub>2</sub>/nmc) phase. Simulated XAS spectra at the oxygen K-edge (Extended Data Fig. 3d) for ZrO<sub>2</sub> in the various fluorite-structure polymorphs (orthorhombic Pca2<sub>1</sub> and tetragonal P4<sub>2</sub>/nmc) 638 were computed through the Materials Project<sup>58</sup> open-source database for XAS spectrum<sup>59</sup>. The 639 T-phase (P4<sub>2</sub>/nmc) nonpolar distortion ( $D_{4h}$ , 4-fold prismatic symmetry) from regular tetrahe-640 dral ( $T_d$ , full tetrahedral symmetry) fluorite-structure symmetry does not split the degenerate ebands  $(d_{x^2-y^2}, d_{3z^2-r^2})$ , as confirmed by experiment <sup>60</sup> and the aforementioned XAS simulations <sup>13</sup>. 642 Meanwhile, the O-phase (Pca2<sub>1</sub>) polar rhombic pyramidal distortion ( $C_{2v}$ , 2-fold pyramidal sym-643 metry) does split the e-manifold based on crystal field symmetry, providing a spectroscopic means 644 to distinguish the T- and O-phases. The additional spectroscopic feature present between the 645 main e- and  $t_2$ - absorption features due to orthorhombic symmetry-lowering distortion is illus-646 trated by its crystal field diagram (Extended Data Fig. 3b). This provides a spectroscopic fingerprint for phase identification beyond diffraction which can often be ambiguous due to the nearly 648 identical T- and O-phase lattice parameters. For the 2 nm HfO<sub>2</sub>-ZrO<sub>2</sub>-HfO<sub>2</sub> trilayer, the exper-649 imental O K-edge XAS spectra demonstrates tetrahedral and rhombic splitting features closely 650 matching the polar O-phase (Pca2<sub>1</sub>) emerge slightly below room temperature, indicative of the mixed tetragonal-orthorhombic to orthorhombic phase transition upon cooling. This temperature-652 dependent tetragonal-orthorhombic structural evolution is expected for fluorite-structure thin films<sup>61</sup> 653 and is consistent with temperature-dependent capacitance measurements (Extended Data Fig. 3f). 654 Further XAS phase identification details are provided in previous work on ultrathin Zr:HfO<sub>2</sub> 655 films 13. 656

X-ray photoelectron spectroscopy Angle-resolved photoelectron spectroscopy (ARPES)

was performed using a Phi Versaprobe III at the Stanford Nano Shared Facilities (Extended Data

Fig. 1d). A monochromated aluminum source was used to give a photon energy of 1486.6 eV. Data

was fit and analyzed using CasaXPS. Angle-dependent XPS at various incident grazing angles

enabled depth-resolved composition analysis to help confirm the HfO<sub>2</sub>-ZrO<sub>2</sub> multilayer structure.

#### Dielectric measurements

**Metal-oxide-semiconductor (MOS) capacitance** Capacitance-voltage (C-V) measurements 663 were performed using a commercial Semiconductor Device Analyzer (Agilent B1500) with a 664 multi-frequency capacitance measuring unit (MFCMU). 19 micron W tips (d.c.P-HTR 154-001, 665 FormFactor) made electrical contact within a commercial probe station (Cascade Microtech); volt-666 age was applied to the W top electrode and the lightly-doped Si bottom electrode was grounded. To eliminate contributions from series and parasitic resistances, frequency-dependent C-V mea-668 surements were performed. In particular, C-V data was analyzed at two frequencies (100-500 kHz 669 regime) to allow for the extraction of accurate frequency-independent C-V via a three-element 670 circuit model consisting of the capacitor and the parasitic series and parallel resistors 62. The 671 frequency-independent capacitance is given by

$$C = \frac{f_1^2 C_1 (1 + D_1^2) - f_2^2 C_2 (1 + D_2^2)}{f_1^2 - f_2^2}$$

(1)

where  $C_i$  and  $D_i$  refer to the measured capacitance in parallel mode ( $C_p$ - $R_p$ ) and dissipation values 673 at frequency  $f_i$ . The dissipation factor is given by  $D = -\cot \theta$ , where  $\theta$  is the phase. In order to maximize the accuracy of this method, it is important the dissipation factors are small ( $\ll 1$ ) at 675 the frequencies chosen; therefore, high frequencies were selected. 676

**Permittivity extraction** The permittivity of Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> dielectric layers was ex-677 tracted from thickness-dependent MOS C-V measurements on lightly-doped p substrates (Ex-678 tended Data Fig. 6). In the accumulation region of the MOS C-V measurements, the MOS capacitor can be modeled as three capacitors (Al<sub>2</sub>O<sub>3</sub> or HfO<sub>2</sub> dielectric layer, SiO<sub>2</sub> interlayer, and Si 680 space charge layer) in series using the following equation,

681

$$\frac{1}{C} = \frac{1}{\epsilon_0 \epsilon_{H\kappa}} t_{H\kappa} + \frac{1}{\epsilon_0 \epsilon_{SiO_2}} \left[ t_{SiO_2}^{phys} + t_{CL} \frac{\epsilon_{SiO_2}}{\epsilon_{Si}} \right], \tag{2}$$

where  $t_{H\kappa}$  is the thickness of the high- $\kappa$  (Al<sub>2</sub>O<sub>3</sub> or HfO<sub>2</sub>) layer,  $t_{SiO_2}^{phys}$  is the physical SiO<sub>2</sub> thickness, and  $t_{\rm CL}$  is the charge layer thickness in silicon. The physical SiO<sub>2</sub> thickness is constant across all 683 of the thickness series (Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> single layers). Additionally, the capacitance values were 684 extracted at various values of fixed charge (Q = 0 to -3  $\mu$ C/cm<sup>2</sup>) which ensures that the charge-685 layer thickness is constant across all thicknesses and in the accumulation region. Therefore, from Equation 2, the inverse capacitance at a fixed charge as a function of film thickness should result in a line and the permittivity can be extracted from the slope. This yielded extracted permittivities of 9 and 19 for the  $Al_2O_3$  and  $HfO_2$  thickness series, respectively, as expected for these systems. Note that for the  $HfO_2$  thickness series, thicknesses of 6 nm and higher were used to ensure  $HfO_2$  stabilizes in the dielectric monoclinic phase ( $\kappa \sim 18$ )<sup>36</sup>.

Similarly, the permittivity of the HfO<sub>2</sub>-ZrO<sub>2</sub> heterostructures was extracted from thickness-dependent MIM *C-V* measurements (Fig. 2b). The inverse capacitance is a linear function of the film thickness, and the permittivity can be extracted from the slope.

692

693

695

696

697

699

700

701

Electrical interlayer thickness extraction The thickness of the SiO<sub>2</sub> interlayer was determined not only by TEM (Extended Data Fig. 6a), but also electrically via *C-V* measurements of both dielectric HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> thickness series on SiO<sub>2</sub>-buffered Si (Extended Data Fig. 6f). From Equation 2, the inverse capacitance at a fixed charge as a function of dielectric thickness should result in a line and the capacitance-equivalent thickness (CET) of the SiO<sub>2</sub> interlayer and Si charge layer can be extracted from the y-intercept. By extracting the CET at different charge values, the *Q-V* relation of the SiO<sub>2</sub> interlayer and Si charge layer can be calculated through the following equation

$$V - V_{fb} = \int_0^Q \frac{t_{SiO_2}^{phys} + t_{\text{CL}} \frac{\epsilon_{SiO_2}}{\epsilon_{Si}}}{\epsilon_0 \epsilon_{SiO_2}} dQ, \tag{3}$$

where  $V_{fb}$  is the flatband voltage (Extended Data Fig. 6b,d). To confirm this methodology, another 703 method for determining the Q-V relation of the SiO<sub>2</sub> interlayer and Si charge layer was extracted 704 from the Q-V relations of both the dielectric HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> thickness series. At a fixed charge, 705 the corresponding voltage values of each thickness were fit to a line and the y-intercept corresponds 706 to the voltage value for the SiO<sub>2</sub> interlayer and Si charge layer Q-V relation (Extended Data Fig. 707 6c,e). As expected, both methods lead to the same extracted Q-V relation (Extended Data Fig. 6c,e), corresponding to 8 Å EOT (Extended Data Fig. 6f) – close to the SiO<sub>2</sub> physical thickness 709 of 8.5 Å obtained via TEM (Extended Data Fig. 6a) – based on simulated TCAD Q-V relations of 710 different  $SiO_2$  thicknesses on lightly-doped Si.

Hysteretic *C-V* measurements Capacitance-voltage (*C-V*) measurements on MIM capacitors were performed using a commercial Semiconductor Device Analyzer (Agilent B1500) with a multi-frequency capacitance measuring unit. 19 micron W tips (d.c.P-HTR 154-001, FormFactor) made electrical contact within a commercial probe station (Cascade Microtech); voltage was applied to the W top electrode and the W bottom electrode was grounded.

#### 717 Electrical characterization

**Bechmarking to HKMG literature** In Figure 3a, the leakage-effective oxide thickness (J<sub>G</sub>-EOT) scaling of negative capacitance multilayer gate stack benchmarked against reported HKMG literature includes references taken from interlayer-scavenged 2 nm HfO<sub>2</sub> <sup>16,18,63</sup> (red), high- $\kappa$  doped HfO $_2$  <sup>18</sup> (blue), and SiO $_2$ /poly-Si $^3$  (gray). In Figure 3b, the normalized mobility ver-sus EOT scaling of the negative capacitance multilayer gate stack benchmarked against reported HKMG literature includes references taken from interlayer-scavenged 2 nm  $HfO_2$   $^{16,18,64}$  (red) and hybrid silicate-scavenged interlayer 16 (magenta). In the Figure 3b inset, the SiO<sub>2</sub> interlayer thickness versus EOT scaling scatter plot considers the 7.0 Å EOT HfO2-ZrO2-HfO2 trilayer to HKMG references which employ interlayer scavenging to reduce EOT<sup>16,18,63,65</sup>.

Transistor transfer and output characteristics Transistor  $I_d$ - $V_g$  and  $I_d$ - $V_d$  characterization of short-channel and long-channel transistors were performed using a commercial Semiconductor Device Analyzer (Agilent B1500). 19 micron W tips (d.c.P-HTR 154-001, FormFactor) made electrical contact within a commercial probe station (Cascade Microtech); voltage was applied to the gate and drain contacts, while the source and Si substrate were grounded.

**Mobility extraction** The low-field transistor mobility is calculated based on the channel resistance  $(R_{ch})$  and inversion sheet charge density  $(Q_{inv})$ , which are extracted respectively from transfer characteristics  $(I_D - V_{GS})$  and from the gate-to-channel capacitance-voltage  $(C_{gc} - V_{GS})$  measurements. Given the device aspect ratio of channel length (L) and channel width (W), we

736 have

$$R_{ch}(V_{GS}) = \frac{L}{W} \times \frac{1}{\mu_{eff}(V_{GS})Q_{inv}(V_{GS})}$$

$$\tag{4}$$

Firstly, the channel resistance is extracted at 50 mV drain-to-source bias  $(V_{DS})$  by subtracting the parasitic resistance  $(R_p)$  from the measured drain-to-source resistance  $(R_{DS})$ .

$$R_{DS}(V_{GS}) = \frac{V_{DS}}{I_D(V_{GS})} = R_{ch}(V_{GS}) + R_p$$

(5)

where  $R_p$  is ascribed to the resistance of the source and the drain contacts and the n+ extension regions that are extrinsic to the channel region. When the overdrive voltage  $(V_{ov} = V_{GS} - V_t)$ , where  $V_t$  is the threshold voltage) is sufficiently large,  $R_{ch}$  is known to be inversely proportional to  $V_{ov}$  according to 4. Therefore,  $R_p$  can be extracted using a linear extrapolation of the  $R_{DS} - 1/V_{ov}$  relationship (Extended Data Fig. 7e), which is derived from the  $I_D - V_{GS}$  from which the threshold voltage  $(V_t)$  can be characterized with the max- $g_m$  method. Secondly, the  $C_{gc} - V_{GS}$  of a large  $V_t$  (W=L=50 $\mu$ m) device (Extended Data Fig. 7a) is integrated and normalized to the channel area (A=2500 $\mu$ m<sup>2</sup>) to estimate the inversion charge.

$$Q_{inv}(V_{GS}) \approx \int_{-\infty}^{V_{GS}} \frac{C_{gc}(v_{gs})}{A} dv_{gs}$$

(6)

The large device dimensions minimizes the parasitic capacitance contribution to ensure  $C_{gc}$  is representative of the inversion electron responses. Finally, we combine the above characterizations to obtain the effective mobility using Equation 4 (Extended Data Fig. 7f).

Transconductance extraction The measured transconductance  $(g_m = \partial I_D/\partial V_{GS})$  and the output conductance  $(g_{ds} = \partial I_D/\partial V_{DS})$  are affected by the series resistance on the source  $(R_S)$  and the drain sides  $(R_D)$ , as they reduce the voltage drops on the channel region,

$$V_{GSi} = V_{GS} - I_D R_S \tag{7}$$

$$V_{DSi} = V_{DS} - I_D(R_S + R_D) (8)$$

where  $V_{GSi}$  and  $V_{DSi}$  are the gate-to-source and the drain-to-source voltages intrinsic to the channel, respectively.  $R_S \approx R_D \approx R_p/2$  because the transistor is symmetric.

$R_p$  can be extracted from the  $R_{DS} - 1/V_{ov}$  relationships as discussed in the "Mobility Ex-755 traction" Methods section (Extended Data Fig. 9b). Besides, devices with different gate length 756  $(L_g)$  series are fabricated on the Silicon-On-Insulator (SOI) wafer, which enables another extrac-757 tion method with  $R_{SD}-L_g$  relations. At low  $V_D$  and a given  $V_{ov}$ ,  $Q_{inv}$  and  $\mu_{eff}$  are unchanged 758 across different  $L_q$  if short-channel effect is not significant, making  $R_{ch}$  proportional to the channel length. Such condition is confirmed by the consistency of  $\mathcal{V}_t$  across measured  $\mathcal{L}_g$  (Extended Data 760 Fig. 9a). Therefore, the  $L_g$  offset as well as the  $R_p$  can be found at the intersect of the linear rela-761 tions of the  $R_{SD}-L_g$  with different  $V_{ov}$  (Extended Data Fig. 9c). The two  $R_p$  extraction methods 762 yield consistent results. 763

The following equation is solved to extract the intrinsic  $g_{mi}=\partial I_D/\partial V_{GSi}$  and  $g_{dsi}=\partial I_D/\partial V_{DSi}$  without the degradation due to  $R_S$  and  $R_D$ .