# Audio Power Amplifier Solutions for New Wireless Phones

# Salahddine Krit † and Hassan Qjidaa ††

University of sciences Dhar El Mehraz Fès Laboratory of Electronic Signaux –Systèmes and Informatique (LESSI), Morocco

#### **Summary**

This paper presents a single chip class D amplifier with two selectable gains 6dB & 9dB, 1.4 W output power and 86% efficiency with an 8 ohm load. This chip uses a frequencies trimable ramp generator. Input Clock Frequency Range with 250kHz – 550kHz and 8 bits trim, 4 bits (LSB) to trim the ramp amplitude to vdd/5 peak-to-peak, 4 bits (MSB) to adjust the ramp continuity, the trimming procedures consists on putting a zero input signal, and adjust the trim code such as to get a 50% duty cycle Pulse Wide Modulation output signal, Reduction of intermodulation in case of mixing of Audio and Voice.

It operates with a 2.5 V to 5.5V supply voltage, 0.5 um, double-poly, triple-metal BiCMOS process. It has an area of 1.5 x 1.2 mm2 and it achieves a THD as low as 0.04%, with a flatband response between 20 Hz and 20 kHz.

Keywords – single chip class D, selectable gains, trim-able ramp, output power, efficiency.

### 1. Introduction

Traditionally class AB audio amplifiers have been used for driving a speaker load in portable devices including cell phones. However, their power efficiency is typically less than 20%, which reduces the overall systems battery lifetime and increases the heat dissipation. Class-D audio amplifiers achieve higher power efficiency by using pulsewidth modulation (PWM), however a class D amplifier with conventional PWM modulation requires a bulky output filters [1 - 4]. High-end class-D amplifiers relax the output filter requirements by using extended digital signal processing to accomplish a modulation scheme that lies in between natural and uniform PWM.

This paper presents a class D amplifier for portable devices with trim able synchronous ramp generator to reduction of inter-modulation in case of mixing of Audio and Voice and eliminates the requirement of an output filter by using a double-sided natural sampling PWM [5].

Furthermore higher integration is achieved by using a fully differential architecture, which removes the need for input capacitors.

The proposed scheme was experimentally verified with a Synchronous Mode with 3 supported frequencies 294, 320 and 333, 3 kHz ramp generator prototype embedded in a class–D amplifier built in a 0.35-µm CMOS process,

which achieved 28mV amplitude accuracy with current consumption of 20  $\mu A$ .

The ramp is generated by constant charging current into the capacitors C1 and C2, which is connected between the ground and successively current source and current sink. The value of two capacitors is C1=C2=25pF.

The amplifier achieves a power efficiency of 86% delivering up to 1.4W output power to an 8 ohm load, and operates with a 2.5V-5.5V supply.

The design has been implemented in a 0.35 um, double-poly, triple-metal, BiCMOS process and occupies 1.5mm x 1.2mm. This amplifier achieves higher level of on-chip integration and power over than previously reported class-D audio amplifiers [1 - 4].

# 2. Design Theory

Currently most class D amplifiers use a binary PWM scheme in a H-bridge output configuration, which devices, or a half bridge architecture that requires high supply voltages and an output inductor [2 - 4].

Considering a pure resistive load switching the full bridge or the half bridge output of previously reported designs [2 - 4], the power supply voltage would be across the load resistance (plus resistance of the switches) with no input signal. The resulting current would be a square wave with magnitude equal to the power supply divided by the resistance of the load. For example, a full bridge using a 5V supply driving an 8 ohm load would conduct a current approximately equal to 0.5 A, and this is with no signal [5, 6]. Most designs currently solve the problem by providing some current limiting device in series with the speaker, usually a post-filter comprised of inductors and capacitors [2-4]. Another solution widely used on high end class D amplifiers requires extended signal processing capabilities in order to accomplish a modulation scheme that lies in between natural and uniform PWM and thus generates the least amount of harmonics in the audio band.

## 2.1 PWM (Pulse Width Modulation)

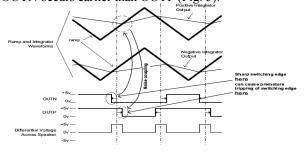

Several modulation techniques exist. The simplest is Pulse Width Modulation, where at a fixed frequency, the audio amplitude is compared to a triangle shaped wave and the duty cycle of this comparison contains the original amplitude (Fig. 1).

Fig.1. PWM signal

The differential pre-filtered output varies between positive and negative VDD, where filtered 50% duty cycle yields 0V across the load.

Since the "Average" signal can have up to 20 kHz frequency content, the amplifier runs on high frequency. 250 kHz are a common trade-off between accuracy and efficiency. A lower switching frequency offers higher amplifier efficiency and better THD but requires larger external filter. A higher switching frequency reduces the size and cost of the filter components at the expense of THD and efficiency [4].

# 2.2 Stability

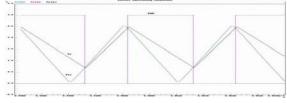

This system has stability threshold limiting the systems bandwidth [6]. This limit may be calculated, considering the slope of the ripple signal (Vr = Vripple on Fig.2) lower than the slope of the triangle wave (Vtr) as shown Fig.3. This consideration has been done for correct functioning of the system If this condition is not met, the system may produce repeated output switching at intervals equal to the delay of the chain delay, defined by the PWM stage and by the output buffer stage, as shown on Fig. 3.

Fig.2. Correct operating condition

Fig.3. Critical operating condition

By converting this concept into formulas:

Ptr = 4.Vtr.fsw (Slope of triangle waveform) (1)

$$Pvr = \frac{1}{C} \left( \pm \frac{Vcc}{Rfb} - \frac{Vin}{Rin} \right)$$

(Slope of the ripple)

Therefore, the boundary condition is

$$\left| \frac{1}{C} \left( \pm \frac{Vcc}{Rfb} - \frac{Vin}{Rin} \right) \le 4.Vtr.fsw \right|$$

(3)

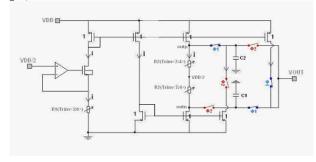

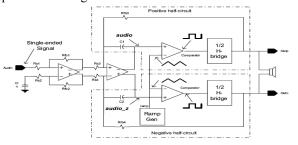

Design Implementation Top View The top schematic view of Class-D amplifier (Fig. 6) is composed by a main part (inverting input integrator, triangle generator, PWM modulator, gate driver and MOSFET H-bridge) and secondary parts like common mode voltage and bias current generator, startup and protection circuit, input gain selector and shifter. All these parts are described in this chapter.

Two analog power supplies (tailed together with decoupling capacitor on the circuit board) are used [1], PVDD/PGND supply the MOSFET H-bridge where as AVDD/AGND supply the rest of circuit. A digital VDD is used to supply level shifter.

ESD protection and bonding are not shown is this schematic but have been taken into account for simulation.

# 3. The proposed Triangle Generator

The proposed ramp is generated by constant charging current into the capacitors C1 and C2, which is connected between the ground and successively current source and current sink. The value of two capacitors is C1=C2=C=25pF.

The current through R1 is the charging current, kept constant by forcing the voltage across R1 to equal VDD/2 by op amp, configured as follower voltage.

The ramp slope is:

$$\frac{dVramp}{dt} = \pm \frac{Vdd}{2R1 * C} \tag{4}$$

The resistance R1 is adjusted by four digital bits Trim<3:0> for adjust finally the current charging, the ramp slope and Vramp peak-to-peak to equal Vdd/5.

The charge make in two phase  $\Phi 1$  and  $\Phi 2$ :

In the phase  $\Phi$ 1, the switches  $\Phi$ 2 will be open and the switches  $\Phi$ 1 will be closed, the capacitor C1 will be in

charge by constant current and the ramp output is the charge voltage of C1, thus Vout will be:

$$Vout(t) = \frac{Vdd}{2R1 * C}t + (Vdd/2 - R2 * I)$$

(5)

At the same time the capacitor C2 is in pre-charge state. VC2 (t) = (Vdd/2+R2I) (1-exp (-t/R2C))

In the phase  $\Phi 2$ , the switches  $\Phi 1$  will be open and the switches  $\Phi 2$  will closed ,the capacitor C2 will be in discharge by constant current, thus Vout will be :

$$Vout(t) = -\frac{Vdd}{2R1 * C}t + (Vdd/2 + R2 * I)$$

(6)

In the same way the capacitor C1 is in RC discharge. VC1 (t) = (Vdd/2+R2\*I)(2\*exp(-t/R2\*C)-1)

The resistor R2 is adjusted by four digital bits Trim<7:4> to adjust the value of outp and outn, such that  $\Delta V=0$  (Fig.4).

Fig.4. proposed triangle Generator Schematic.

The condition to get the continuity of the ramp output is Trim<7:4>=0001, i.e. the value of R2=23.4Kohms.

The condition to get ramp slope or ramp output peak-to-peak equal VDD/5 is Trim<3:0>=0101, i.e. the value of R1=105Kohms.

The third condition is that the half period T/2 will be large enough such that C2 voltage achieves 95% of its final value (i.e. Vdd/2+R2I), thus:

$$\exp\left(\frac{-T}{2R2C}\right) = 0.05\tag{7}$$

So the minimum input clock period is Tmin=2\*R2C\*ln20 = 3\*R2\*C = 1.725us

So the maximum input clock frequency Fmax =  $580 \, \text{kHz}$  At top classD level, we can adjust the value of two resistors R1 and R2, by putting on both inputs (positive and negative) of the class-D a constant signal equal to VDD/2 (i.e. a zero differential input signal is going to the class-D).

Then we adjust the value of Trim such as to have on both outputs of the class-D a square signal with duty cycle equal 50%.

# 4. Architecture and Circuit Design

In order to implement the new scheme, a single monoaural channel has as much complexity as a stereo version of the traditional modulation scheme. As such, the issues of crosstalk are exacerbated, with twice as many independent switching edges to cause crosstalk problems. Although layout techniques assist in isolating switching noise from coupling into sensitive nodes, circuit techniques such as chopping compensation and PWM deglitch logic, are also used to maximize performance.

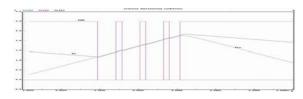

When regulating current through an inductive load using switching methods, voltage spikes are induced into the power and ground of the H-bridge. These spikes are due to the switching of current through the inductance of the bond wires and package pins, and are made worse with reverse-recovery currents in the back-body diodes of the power FETs. The voltage and current spikes can be coupled into the power and ground signals of the analog and PWM circuits. Layout techniques such as guard rings and careful power and ground routing can minimize the spikes induced onto the sensitive linear sections. For a fully integrated solution, the previously mentioned switching noise on the IC is a concern, and it is quite likely that the switching noise from one of the half-circuits will have an influence on the other half, which is much like crosstalk. In this example, the falling edge transition of OUTN occurs earlier than OUTP (Fig. 5).

Fig.5. Illustration of Cross-Coupling within a Monoaural Channel where using the Quartenary Modulation Scheme

The concern is that the switching of the negative half-circuit will couple disturbances onto the output of the positive half-circuit's integrator, making OUTP trip prior to its expected crossing point. This problem would manifest itself near zero crossing where audio signals are smallest and most likely to exist. To eliminate the potential of "crosstalk" within one channel, a time delay is introduced into the system.

This has the main effect of moving the susceptible crosstalk point away from zero crossing to a higher power level. For low-end audio applications, such as cell phones and mp3 players, this is not noticeable.

Fig. 6 shows the schematic of the class D amplifier with the new modulation method. The circuit is divided into positive and negative half-circuits.

Fig.6. Implementation system model.

These two half-circuits operate in inverse phase to each other, which requires a fully differential pre amplifier to create both an audio signal (audio) and its inverse (audio\_z). The fully-differential analog stage allows the inputs to be biased at a voltage other than mid-supply. It also eliminates the requirement for a bypass capacitor and input decoupling capacitors. It improves the RF immunity of the amplifier as well. The amplifier utilizes two feedback loops. The first one pre-shapes the audio signal before it is compared to a triangular waveform to form the PWM signal. The second loop sets the gain for the amplifier.

The output stage consists of two high gain comparators, deglitch logic and output FETs. On the positive side of the circuit, the audio frequency analog signal (audio) is compared with a signal from the ramp generator, and the resulting pulse-width modulated signal is supplied to the half-full-bridge. Similarly, the negative side of the circuit uses the same ramp signal, but uses an inverse analog signal (audio\_z). However, note that the comparator and full bridge positive and negative outputs switch at the same time when the differential input signal is zero. The resulting differential waveform across the load becomes zero.

When a positive audio signal is present, waveforms change to that shown in Fig.5, the edges of OUTP move away from each other, and the edges of OUTN move towards each other. The resulting differential signal across the bridge tied load consists of narrow pulses with polarity determined by the polarity of the audio input signal. These narrow pulses also have a secondary desired effect of doubling the differential PWM frequency. This effect also achieves the desired effect of placing current into the load only when needed, resulting in increased efficiency and less energy loss in the speaker. The modulation phase that regulates the current through the load by applying the power supply voltage at reverse polarity is eliminated; hence the output of the full bridge can be placed directly across the load.

# 5. Experimental Results

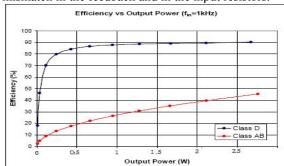

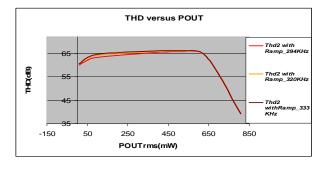

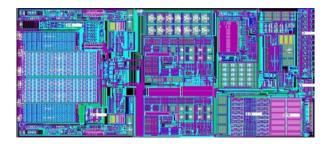

The class D audio amplifier has been integrated in a 0.25um, double-poly, triple-metal, BiCMOS process, occupying an area of 1.5 x 1.2 mm2. The measured output peak current was measured to be 0.35A into an 8 ohm load, using a 3.6V supply voltage. The IC consumed 2.5mA of quiescent current under those conditions with an rms output power of 1.4W and a power efficiency of 86%. A power efficiency of 90% was achieved at a supply voltage of 5.5V. Fig.7 shows the efficiency versus power curve in class AB and in Class D. The total harmonic distortion plus noise (THD+N) was measured with an Audio Precision (AP) measurement system. A lowpass filter had to be used at the output since the AP measurement system can not handle pure class D audio amplifiers because of the high frequency PWM waveform. The THD+N measured under the above-mentioned conditions vary from under 0.04% at low frequencies to a maximum of 0.4% at 7 kHz. Fig.8 shows a plot of the THD+N versus the power under different supply voltage levels. Fig.9 shows layout of Amplifier Class D with process 0.25 um. Table 1 summarizes the measured results. The output offset is higher than predicted in the simulations because of mismatch in the feedback and in the input resistors.

Fig.7. Efficiency versus Power Curve

Fig.8. shows the THD+N versus the power.

Fig. 9. Layout of Amplifier Class D with process 0.5um of Texas

| Parameters                                       | measurements | unity |

|--------------------------------------------------|--------------|-------|

| Supply Voltage                                   | 3.6 -5.5     | V     |

| Output Power                                     | 1.4          | V     |

| Speaker Load                                     | 4 or 8       | ohm   |

| Total Harmonic Distortion<br>Plus Noise<br>THD+N | 0.11         | %     |

| Common Mode Rejection<br>Ratio<br>CMRR           | 69           | dB    |

| Power Supply Rejection<br>PSRR                   | 75           | dB    |

Table 1: Summary of measurement results

#### 6. Conclusions

We have presented a new class D audio amplifier for low voltage applications with high efficiency and minimum system solution size. The amplifier is a great improvement over its class AB counterparts where it comes to battery powered application since it dissipates less power in the amplifier itself.

### References

- [1] Score, Michael, and Donald Dapkus. "Audio Power Amplifier Solutions for New Wireless Phones," Wireless Symposium, February 2000.

- [2] Van der Zee, Ronan A. R., and Ed van Tuijl "A Power-Efficient Audio Amplifier Combining Switching and Linear Techniques," IEEE Journal of Solid-State Circuits, vol. 34, pp. 985-987, July 1999.

- [3] Choi, Soo-chang, Jun-woo Lee, Woo-kang Jin, Jae-hwan So, and Suki Kim, "A Design of a 10-W Single Chip Class D Audio Amplifier with Very High Efficiency using CMOS Technology," IEEE Transactions on Consumer Electronics, vol. 45, pp. 465 473, August 1999.

- [4] Jeong, Jay H., Hawn H. Seong, Jeong H. Yi, Gyu H. Cho, "A class D switching power amplifier with high efficiency and wide bandwidth by dual feedback loops," Proc. of International Conference on consumer Electronics, 1995, pp. 428 –429.

- [5] Score, Michael. "Optimized Modulation Scheme Eliminates Output Filter," AES Preprint #5196, 109<sup>th</sup> Convention, pp. 22-25, September 2000.

- [6] Chen, Wayne T. and R. Clif Jones, "Concepts and Design of Filterless Class-D Audio Amplifiers," Texas Instruments Technical Journal, vol. 18, No. 2, April 2001.

- [7] Leigh, S. P, P. H. Mellor, and B. M. G. Cheetham, "Distortion Analysis and Reduction in a Completely Digital PWM Class D Power Amplifier," Inter. J. Of Modelling and Simulation, vol. 14, No. 2, pp. 75-59, 1994.

Krit Salahddine received the B.S. and M.S. degrees in Electrical Engineering from Fes Institute of Technology in 1998 and 2000, respectively. During 2002-2008, he is a team lead in power IC Research, study analog and digital, mobile satellite communication systems, and wireless access network using emos technology.

Hassan Qjidaa received his M.Sc.and PhD in Applied Physics from Claude Bernard University of Lyon France in 1983 and 1987 respectively. He got the Pr. degree in Electrical Engineering from Sidi Mohammed Ben Abdellah university, Fès, Morroco 1999. He is now an Professor in the Dept. of Physics in Sidi research interests

include Very-large-scale integration (VLSI) solution, Image manuscripts Recognition, Cognitive Science, Image Processing, Computer Graphics, Pattern Recognition, Neural Networks, Human-machine Interface, Artificial Intelligence, Robotics and so on