# AUTOMATED BUS GENERATION FOR MULTI-PROCESSOR SOC DESIGN

A Dissertation Presented to The Academic Faculty

by

# Kyeong Keol Ryu

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

School of Electrical and Computer Engineering Georgia Institute of Technology June 2004

# AUTOMATED BUS GENERATION FOR MULTI-PROCESSOR SOC DESIGN

Approved by:

Dr. Vincent J. Mooney III, Adviser

Dr. Jeffrey A. Davis

Dr. Sudhakar Yalamanchili

Dr. Paul Benkeser

Dr. Thad Starner

Date Approved: June 11, 2004

Dedicated to my wife, Hyejung Hyeon, my parents, and my parents-in-law

## ACKNOWLEDGMENTS

This work could have not been finished without the support and sacrifice of many people I had to express my gratitude. First of all, I would like to deeply thank my adviser Vincent J. Mooney III. He has supported and encouraged me to develop my dissertation with his enthusiasm and professionalism throughout all stages of my Ph.D. program. He has been a great source of ideas and provided me with invaluable feedback. In addition, Dr. Mooney has been helping me improve my English skills with his consideration. I would also like to extend my appreciation to Dr. Jeffrey Davis, Dr. Sudhakar Yalamanchili, Dr. Paul Benkeser, and Dr. Thad Starner for serving on the committee and offering constructive comments.

I have to thank all Hardware/Software Codesign group members for their helps and friendship. It is obvious that, without many helps by them, my long journey at Georgia Tech would have been much harder and lonelier. Also, I wish to thank my friends, Dr. Chang-ho Lee, Dr. Jong-seung Moon, and Chang-hyuk Cho for their friendship.

Finally, I must thank my parents and my parents-in-law who have provided me with their enormous love, support and consideration for my life. I would also like to thank my brothers and my brothers-in-law for their consideration in all aspects. Most importantly, I cannot fail to thank my wire, Hyejung Hyeon. Without her unselfish devotion and her endless love, it would not have been possible to get through all the obstacles I have met during my study. I also thank my daughter Clair Seunghyun Ryu and my son Ryan Jihun Ryu who have given me great pleasure and their precious love.

# TABLE OF CONTENTS

| DEDIC  | ATIOI  | N                                       | iii      |

|--------|--------|-----------------------------------------|----------|

| ACKN   | OWLE   | DGMENTS                                 | iv       |

| LIST O | F TAE  | BLES                                    | viii     |

| LIST O | F FIG  | URES                                    | ix       |

| LIST O | F ABI  | BREVIATIONS                             | xi       |

| SUMM   | ARY .  |                                         | xiv      |

| CHAP   | FER I  | INTRODUCTION                            | 1        |

| 1.1    | Proble | em Statement and Motivation             | 1        |

| 1.2    | Contra | ibutions                                | 2        |

| CHAPT  | FER II | RELATED WORK                            | <b>5</b> |

| 2.1    | SoC E  | Bus Architectures                       | 5        |

|        | 2.1.1  | CoreConnect                             | 5        |

|        | 2.1.2  | AMBA                                    | 6        |

|        | 2.1.3  | CoreFrame                               | 7        |

|        | 2.1.4  | Wishbone                                | 7        |

|        | 2.1.5  | SiliconBackplane $\mu$ Network          | 8        |

|        | 2.1.6  | How We Differ                           | 9        |

| 2.2    | SoC E  | Bus Interfaces                          | 9        |

|        | 2.2.1  | Open Core Protocol (OCP)                | 9        |

|        | 2.2.2  | Virtual Component Interface (VCI)       | 10       |

|        | 2.2.3  | How We Differ                           | 11       |

| 2.3    | Comm   | nercial Tools Related to Bus Generation | 11       |

|        | 2.3.1  | CoWare N2C                              | 11       |

|        | 2.3.2  | Platform Express                        | 12       |

|        | 2.3.3  | CoCentric System Studio                 | 12       |

|              | 2.3.4 Magillem                                  | 13        |

|--------------|-------------------------------------------------|-----------|

|              | 2.3.5 How We Differ                             | 14        |

| 2.4          | Additional Prior Work Related to Bus Generation | 14        |

| 2.5          | Summary                                         | 16        |

| CHAPT        | TER III     BUS SYSTEM STRUCTURE     1          | 18        |

| 3.1          | Terminology for Bus System Generation           | 18        |

| 3.2          | Bus System Structure                            | 21        |

| 3.3          | Summary                                         | 24        |

| CHAPT        | TER IV BUS SUBSYSTEM SPECIFICATION              | 25        |

| 4.1          | How to Specify Bus Subsystems                   | 25        |

| 4.2          | Communication among BANs                        | 38        |

|              | 4.2.1 Our Basic Handshake Protocol              | 38        |

|              | 4.2.2 Communication in GBAVIII                  | 40        |

|              | 4.2.3 Communication in BFBA                     | 45        |

|              | 4.2.4 Communication in HybridBA                 | 48        |

| 4.3          | Summary                                         | 48        |

| CHAPT        | TER V BUS SYSTEM SPECIFICATION                  | <b>49</b> |

| 5.1          | Bus System Examples                             | 49        |

|              | 5.1.1 How to Generate Bus Systems               | 50        |

|              | 5.1.2 Communication among BANs                  | 55        |

|              | 5.1.3 Summary                                   | 56        |

| CHAPT<br>TIC | TER VI METHODOLOGY FOR BUS SYSTEM GENERA-       | 58        |

| 6.1          | Libraries for Module Repository and Wiring      | 58        |

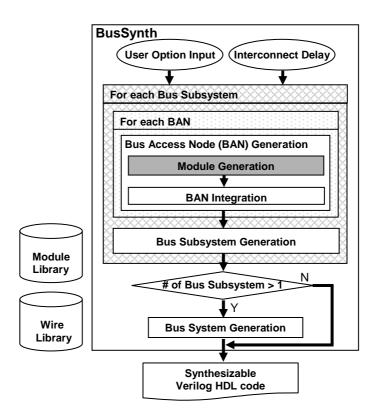

| 6.2          | Sequence of Bus System Generation               | 68        |

|              | 6.2.1 Overall Flow of Bus System Generation     | 69        |

|              | 6.2.2 User Inputs to BUSSYNTH                   | 70        |

|              | 6.2.3 Unit Generation                           | 70        |

|                | 6.2.4         | Bus Subsystem Generation                                          | 76  |

|----------------|---------------|-------------------------------------------------------------------|-----|

|                | 6.2.5         | Bus System Generation                                             | 80  |

|                | 6.2.6         | Summary                                                           | 82  |

| 6.3            | Interc        | onnect Delay Aware Bus System Generation                          | 82  |

|                | 6.3.1         | Interconnect Delay Estimation                                     | 83  |

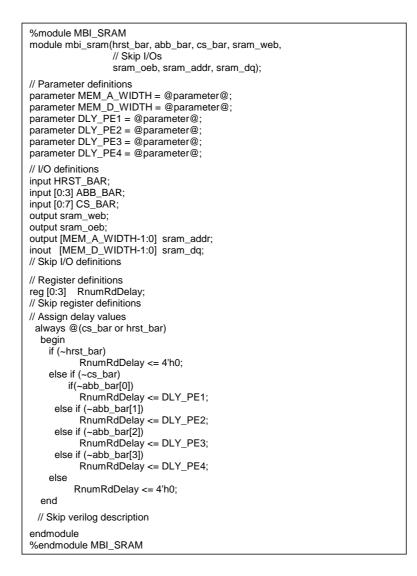

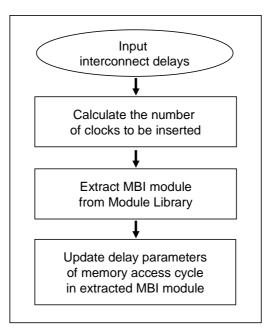

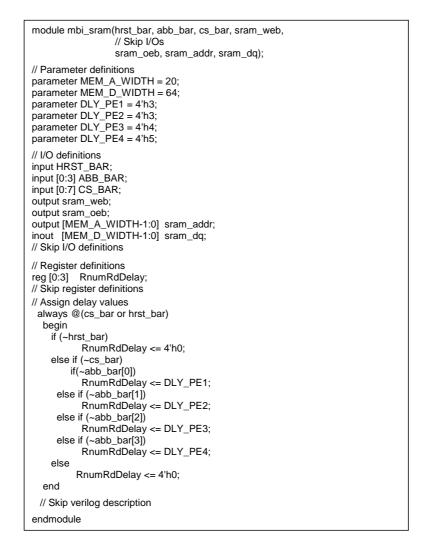

|                | 6.3.2         | Memory Bus Interface (MBI) Module Generation                      | 85  |

|                | 6.3.3         | Interconnect Delay Aware Bus System Generation                    | 91  |

| 6.4            | Comp          | utational Complexity of Bus System Generation Algorithm           | 92  |

| 6.5            | Summ          | nary                                                              | 97  |

| CHAP           | $\Gamma ER V$ | TII EXPERIMENTS AND RESULTS                                       | 98  |

| 7.1            | Applie        | cation Examples                                                   | 98  |

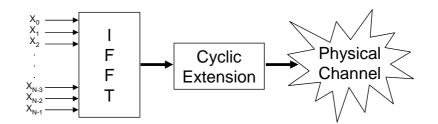

|                | 7.1.1         | OFDM Transmitter                                                  | 98  |

|                | 7.1.2         | MPEG2 Decoder                                                     | 102 |

|                | 7.1.3         | Database Example                                                  | 103 |

| 7.2            | Exper         | imental Setup                                                     | 104 |

| 7.3            | Comp          | Comparison of Results                                             |     |

|                | 7.3.1         | Performance Comparison among Bus Systems                          | 106 |

|                | 7.3.2         | Performance Comparison in Interconnect Delay Aware Bus<br>Systems | 110 |

|                | 7.3.3         | Generation Time and Gate Counts of Each Bus System $\ . \ .$ .    | 113 |

| 7.4            | Summ          | nary                                                              | 114 |

| CHAP           | TER V         | TIII CONCLUSION                                                   | 115 |

| REFE           | RENCE         | $\mathbf{ES}$                                                     | 117 |

| PUBLICATIONS 1 |               |                                                                   | 122 |

| POSTE          | ER PRI        | ESENTATIONS/DEMONSTRATIONS                                        | 123 |

# LIST OF TABLES

| Table 1  | Interconnect Length Estimation for GGBA System                      | 84  |

|----------|---------------------------------------------------------------------|-----|

| Table 2  | Estimated Total Delay of Paths between Each PE and a Shared Memory  | 88  |

| Table 3  | Number of Clock Delays in Data Paths                                | 89  |

| Table 4  | The Numbers Related to Computational Complexity                     | 93  |

| Table 5  | Example of the Numbers in Table 4                                   | 93  |

| Table 6  | The Upper Bounds of UNITGEN Algorithm in the Case of BAN Generation | 94  |

| Table 7  | The Upper Bounds of BusSubSys Algorithm                             | 95  |

| Table 8  | The Upper Bounds of BusSys Algorithm                                | 95  |

| Table 9  | The Function Assignment in Each BAN                                 | 101 |

| Table 10 | Evaluation Results in OFDM Transmitter                              | 106 |

| Table 11 | Evaluation Results in MPEG2 Decoder                                 | 108 |

| Table 12 | Evaluation Results in a Database Example                            | 109 |

| Table 13 | Performance Comparison                                              | 112 |

| Table 14 | Generation Time and Gate Count in the Generated Bus Systems .       | 113 |

# LIST OF FIGURES

| Figure 1  | A Comparison of Bus Generation Tools                                                   | 17 |

|-----------|----------------------------------------------------------------------------------------|----|

| Figure 2  | Example of a Bus System                                                                | 20 |

| Figure 3  | Example of a Bus Subsystem                                                             | 21 |

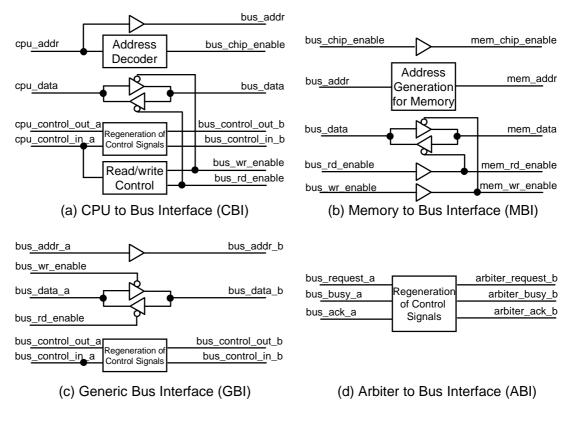

| Figure 4  | Block Diagrams of Interface Logic Blocks                                               | 22 |

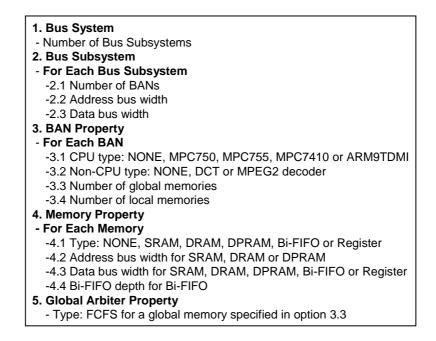

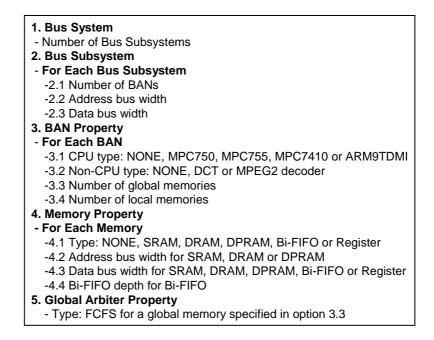

| Figure 5  | User Options to Configure a Custom Bus Subsystem                                       | 26 |

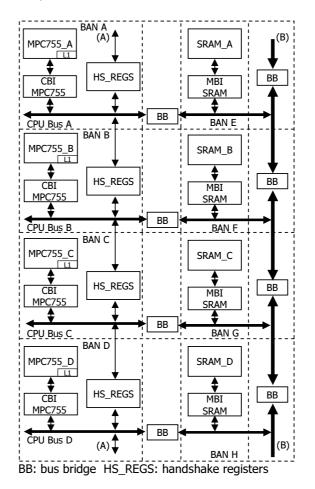

| Figure 6  | Diagram of BFBA                                                                        | 28 |

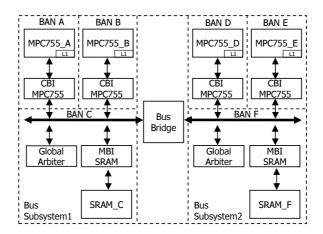

| Figure 7  | Diagram of GBAVIII                                                                     | 30 |

| Figure 8  | Diagram of HybridBA                                                                    | 33 |

| Figure 9  | Different Combination of Bus Components to Generate a New Bus<br>Architecture          | 36 |

| Figure 10 | Diagram of CCBA                                                                        | 37 |

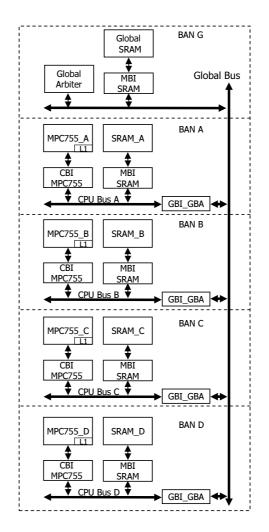

| Figure 11 | Diagram of GGBA                                                                        | 37 |

| Figure 12 | Diagram of GBAVIII (repeated from Figure 7 for convenience)                            | 41 |

| Figure 13 | Communication between BANs in GBAVIII Working in a Pipelined<br>Parallel Fashion       | 42 |

| Figure 14 | Communication between BANs in GBAVIII Working in a Functional Parallel Fashion         | 44 |

| Figure 15 | Communication between BANs in BFBA                                                     | 47 |

| Figure 16 | User Options to Configure a Custom Bus System (repeated from Figure 5 for convenience) | 49 |

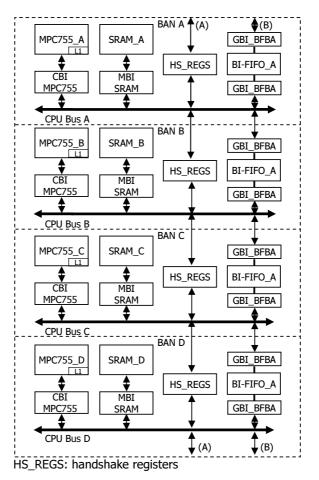

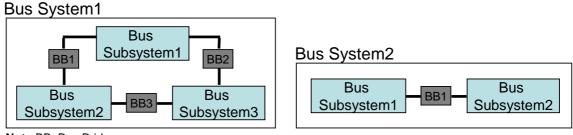

| Figure 17 | Diagram of GBAVI                                                                       | 50 |

| Figure 18 | Diagram of SplitBA                                                                     | 52 |

| Figure 19 | Different Combination of Bus Subsystems to Generate New Bus Ar-<br>chitectures         | 54 |

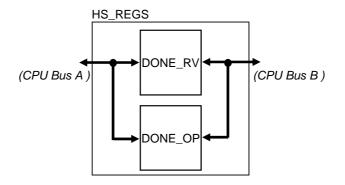

| Figure 20 | Detailed Diagram of HS_REGS in Figure 17                                               | 56 |

| Figure 21 | MBLSRAM Component in Module Library                                                    | 61 |

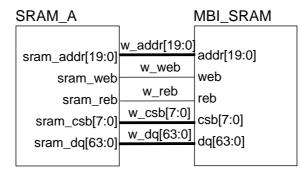

| Figure 22 | Wire Library Format                                                                    | 63 |

| Figure 23 | Diagram of BFBA (repeated from Figure 6 for convenience) $\ldots$                      | 64 |

| Figure 24 | Wire Connection Example between SRAM_A and MBI_SRAM in Figure 6                        | 64  |

|-----------|----------------------------------------------------------------------------------------|-----|

| Figure 25 | Wire Connection Example between BANs                                                   | 66  |

| Figure 26 | The Bus System Generation Sequence                                                     | 69  |

| Figure 27 | User Options to Configure a Custom Bus System (repeated from Figure 5 for convenience) | 70  |

| Figure 28 | Top Verilog HDL Code of BAN A Generated from UNITGEN                                   | 75  |

| Figure 29 | Diagram of BFBA (repeated here for convenience from Figure 6) $$ .                     | 77  |

| Figure 30 | GGBA Estimated Layout                                                                  | 84  |

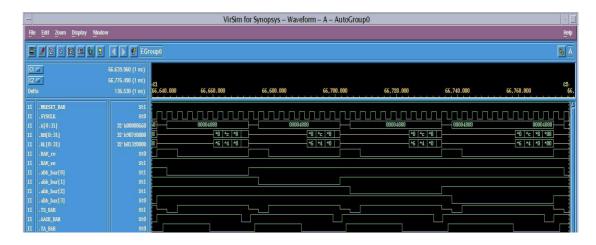

| Figure 31 | Waveform of Extended Memory Access Cycle                                               | 87  |

| Figure 32 | Sequence of MBI Module Generation                                                      | 89  |

| Figure 33 | MBI Module with Updated Delay Clock Parameters                                         | 90  |

| Figure 34 | Sequence of an Interconnect Delay Aware Bus System Generation .                        | 91  |

| Figure 35 | The Block Diagram of an OFDM Transmitter                                               | 99  |

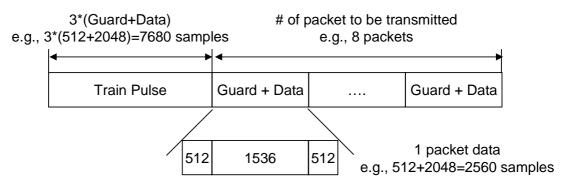

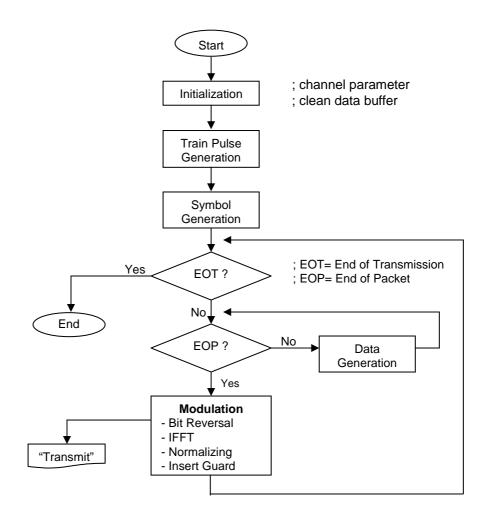

| Figure 36 | OFDM Data Format                                                                       | 99  |

| Figure 37 | The Flowchart of the OFDM Transmitter                                                  | 100 |

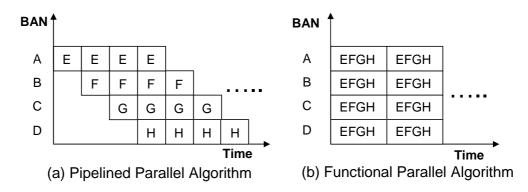

| Figure 38 | Software Programming Style in OFDM                                                     | 101 |

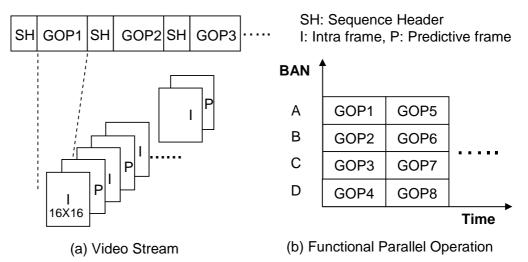

| Figure 39 | Input Video Stream and Functional Parallel Operation                                   | 102 |

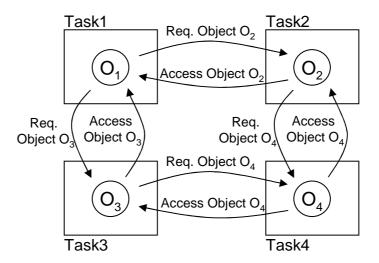

| Figure 40 | Transactions in Database Example                                                       | 103 |

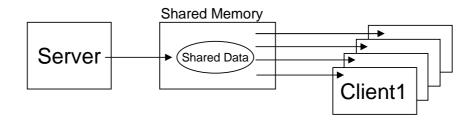

| Figure 41 | Data Transfer from a Server to Clients                                                 | 103 |

| Figure 42 | Experimental Environment                                                               | 105 |

# LIST OF ABBREVIATIONS

| ABI      | Arbiter Bus Interface                              |

|----------|----------------------------------------------------|

| AHB      | Advanced High-performance Bus                      |

| AMBA     | Advanced Micro-controller Bus Architecture         |

| APB      | Advanced Peripheral Bus                            |

| API      | Application-specific Program Interface             |

| ASB      | Advanced System Bus                                |

| BAN      | Bus Access Node                                    |

| BB       | Bus Bridge                                         |

| BFBA     | Bi-directional First-in-first-out Bus Architecture |

| BusSynth | Bus Synthesis tool                                 |

| CAD      | Computer-Aided Design                              |

| CBI      | CPU Bus Interface                                  |

| CCBA     | CoreConnect Bus Architecture                       |

| DCR      | Device Control Register                            |

| DMA      | Direct Memory Access                               |

| DRAM     | Dynamic Random Access Memory                       |

| FPA      | Functional Parallel Algorithm                      |

| GBAVI    | Global Bus Architecture Version I                  |

**GBAVII** Global Bus Architecture Version II **GBAVIII** Global Bus Architecture Version III GBI Generic Bus Interface GGBA General Global Bus Architecture GUI Graphic User Interface HDL Hardware Description Language **HybridBA** Hybrid Bus Architecture  $\mathbf{IL}$ Interface Logic  $\mathbf{IP}$ Intellectual Property ISS Instruction Set Simulator **JTAG** Joint Test Action Group MBI Memory Bus Interface OCP **Open Core Protocol OFDM** Orthogonal Frequency Division Multiplexing OPB **On-chip** Peripheral Bus Processing Element  $\mathbf{PE}$ PLB Processor Local Bus PPA Pipelined Parallel Algorithm RTL Register Transfer Level RTOS Real-Time Operating System

- SB Segment of Bus

- SoC System-on-a-Chip

- SplitBA Split Bus Architecture

- SRAM Static Random Access Memory

- **TDMA** Time Division Multiplexed Access

- **UART** Universal Asynchronous Receiver-Transmitter

- VCI Virtual Component Interface

- VLSI Very Large Scale Integration

## SUMMARY

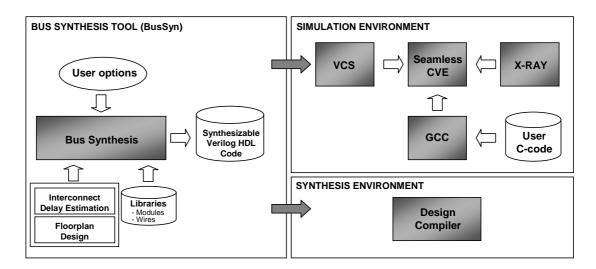

The objective of this research is to provide a Computer Aided Design (CAD) tool with which the user can quickly explore System-on-a-Chip (SoC) bus design space in search of a high performance SoC bus system. From a straightforward description of the numbers and types of Processing Elements (PEs), non-PEs, memories and buses (including, for example, the address and data bus widths of the buses and memories), our Bus Synthesis tool, called BUSSYNTH, generates a Register-Transfer Level (RTL) Verilog Hardware Description Language (HDL) description of the specified bus system. The user can utilize this RTL Verilog in bus-accurate simulations to more quickly arrive at an efficient bus architecture for a multi-processor SoC.

In the design of a multi-processor SoC, the bus architecture typically comes to the forefront because the system performance is not dependent only on the PE speed but also on the bus architecture in the system. An efficient bus architecture with effective arbitration for reducing contention on the bus plays an important role in maximizing performance. Therefore, among many issues of multi-processor SoC research, we focus on two issues related to bus architectures in this dissertation. One issue is how to quickly and easily design an efficient bus architecture for an SoC. The second issue is how to quickly explore the design space across performance influencing factors to achieve a high performance bus system.

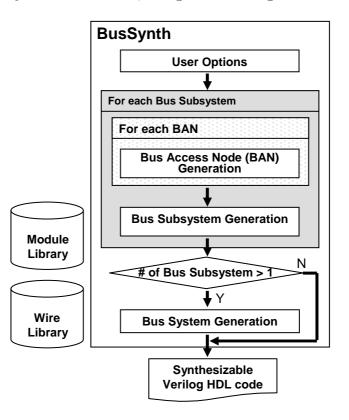

To provide a solution to such system design issues, we propose a methodology to generate custom bus systems. The methodology was used for the implementation of BUSSYNTH; thus, with BUSSYNTH, designers can quickly and easily design a custom bus system to obtain high performance. During the design of a bus system, BUSSYNTH enables a user to customize many characteristics of each module (e.g., bus, PE and memory). Based on user options, BUSSYNTH generates the required modules in the system using a module library, stitches the modules together to build a bus system and finally outputs synthesizable Verilog HDL code for the specified system. In this manner, BUSSYNTH is capable of generating differently configured custom bus systems such as a Bi-directional First-In-First-Out (Bi-FIFO) Bus Architecture (BFBA), a Global Bus Architecture Version I (GBAVI), a Global Bus Architecture Version III (GBAVIII), a Hybrid Bus Architecture (HybridBA) and a Split Bus Architecture (SplitBA) as examples.

The methodology we propose gives designers a great benefit in fast design space exploration of bus systems across a variety of performance influencing factors such as bus types, PE types and software programming styles (e.g., pipelined parallel fashion or functional parallel fashion). We also show that BUSSYNTH can efficiently generate bus systems in a matter of seconds as opposed to weeks of design effort to integrate together each system component by hand. Moreover, unlike the previous related work, BUSSYNTH can support a wide variety of PEs, memory types and bus architectures (including a hybrid bus architecture) in search of a high performance SoC.

# CHAPTER I

## INTRODUCTION

State-of-the-art chip design technology enables System-on-a-Chip (SoC) to open up new opportunities for Very Large Scale Integration (VLSI) hardware design. The ability of the semiconductor industry to continually live up to Moore's prediction [26] makes it practical to put multiple Processing Elements (PEs) on a single chip. In particular, single-chip integration allows the designer to take advantage of increased bus speed and width. This is especially critical as the performance of a multiprocessor SoC heavily depends on the efficiency of its bus architecture. This dissertation presents a methodology to generate a variety of custom bus systems using pre-designed reusable hardware modules for a multi-processor SoC.

### 1.1 Problem Statement and Motivation

In a few years, we will see an SoC with one billion transistors (memory chips with over a billion transistors already exist [58]), and we predict that the SoC will include many PEs. In the design of such a multi-processor SoC, the bus architecture of the SoC is an important performance factor due to multiple bus masters. Therefore, an efficient bus architecture with fast arbitration plays an important role in maximizing system performance. Moreover, when designing a multi-processor SoC including a bus architecture, users need to explore a diverse design space across performance-influencing factors in search of a high performance SoC. However, high performance system design via bus system design and design space exploration is very time-consuming since many performance-impacting factors are involved in the design: types of bus architectures, types of PEs, and types of memories. Thus, these issues motivate the development of a design automation tool that is capable of generating customized SoC bus systems in a Hardware Description Language (HDL) and speeding up the SoC bus design space exploration for a high performance SoC.

### 1.2 Contributions

In this dissertation, we present a new methodology to generate custom bus systems. Unlike the previous research that will be described in Section 2, our methodology provides a more flexible bus system template to generate bus systems, and the template supports multiple and heterogeneous bus architectures and various optimized wrappers to attach Intellectual Property (IP) blocks to a bus so that the generated bus system is suitable for the desired applications. Please note that "IP block" and "IP core" are used interchangeably (i.e., with the same meaning) in this dissertation. The following items are the contributions of this research.

- SoC Bus System Design Aid. A bus mechanism in an SoC is a significant performance-impacting factor and gives many challenging points with regard to performance. Based on a generic bus system architecture that we proposed, a user can design an efficient and scalable bus system in an easy and fast manner for a multi-processor SoC system. We developed five different bus systems (GBAVI, GBAVIII, BFBA, HybridBA and SplitBA) as practical examples and verified the efficiency of our custom bus architecture. Therefore, our methodology as described in this dissertation can be an expert guide to design an SoC bus system.

- Automated Bus Generation Tool. How to easily and quickly design a multi-processor SoC bus system is an important issue in the increasing complexity of on-chip bus systems and in the context of ever shortening time-to-market demands. This dissertation presents an automated Bus Synthesis tool,

BUSSYNTH, to meet this goal. Moreover, BUSSYNTH generates a custom, application specific, configurable bus system for an SoC composed of multiple heterogeneous PEs, IP blocks, bus(es) and various types of memories. Based on the user specification, BUSSYNTH can generate diverse custom bus systems (e.g., GBAVI, GBAVIII, BFBA and SplitBA), including a hybrid bus system (HybridBA), in synthesizable Verilog HDL. When compared to a typical global bus system (e.g., GGBA), the generated bus systems show superior performance (e.g., 41% reduction in execution time in the case of a database example, see Section 7.3).

- Interconnect Delay Aware Bus Architecture Generation. Due to the nature of SoC design, in which multiple IP blocks are placed together and connected with buses, interconnect delay plays a significant role in system performance as feature size is scaled down to the submicron level. In this dissertation, we describe a methodology to generate a custom bus architecture using accurate estimations of interconnect delay.

- Case Studies. This dissertation also delineates case studies of application examples of SoC designs in a component-based design approach that allows designers to explore efficient custom bus solutions with high performance. This research automatically integrates multiple and heterogeneous PEs, various types of buses (including a hybrid bus) and a variety of types of memories into an SoC. Custom bus systems in synthesizable Verilog HDL generated by BUSSYNTH are evaluated in the context of three realistic applications: an Orthogonal Frequency Division Multiplexing (OFDM) transmitter, an MPEG2 decoder and a database example. We also use a Real-Time Operating System (RTOS) to run multitasking user applications on the integrated SoC.

• Fast Design Space Exploration. The methodology describing in this dissertation gives us a great benefit in fast SoC bus design space exploration across several important performance influencing factors (e.g., types of bus architectures, types of processing elements and types of memories) in search of a high performance SoC. Based on the user options, a bus system generated by BUSSYNTH is designed in a matter of seconds instead of weeks for the hand design of a custom bus system.

## CHAPTER II

### **RELATED WORK**

We now present a review of previous work pertinent to this dissertation. First, we discuss several standard on-chip buses and standard bus interfaces, and then we depict several state-of-the-art commercial tools related to this research. Next, we show other related research in academia and industrial research labs.

### 2.1 SoC Bus Architectures

Most SoC designs are based on hardware blocks stitched together with bus signals, which are classified into groups of data, address, and control links. Several industries provide the following SoC bus architectures so that designers can easily integrate the IP blocks into a single silicon chip: CoreConnect, AMBA, CoreFrame, Wishbone, and SiliconBackplane  $\mu$ Network. Please note that all representations of commercial buses in this section are based upon publically available information at the time of publication of this thesis (June 2004).

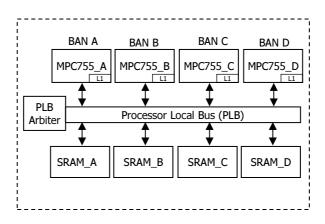

### 2.1.1 CoreConnect

The IBM CoreConnect bus architecture [20] is an open standard and provides three levels of bus hierarchy: a Processor Local Bus (PLB), an On-chip Peripheral Bus (OPB), and a Device Control Register (DCR) bus. The PLB interconnects highbandwidth devices such as PEs and memories since the PLB is a high performance and low latency processor bus with separate address bus, read data bus and write data bus for each bus master. The decoupled address and data buses support splitbus transaction capability for improved bandwidth. In contrast, the OPB provides separate low speed address and data buses for slow peripheral input/output (I/O) devices such as serial ports, parallel ports, and Universal Asynchronous Receiver-Transmitters (UARTs). A bus bridge connects the PLB and the OPB together, and the bus bridge supports burst reads and writes as well as Direct Memory Access (DMA) transfers. The daisy-chained DCR bus offers a relatively low-speed data path for passing status and configuration information between CPU and IP blocks connected to a PLB. Since control registers in slave IP blocks that can be set from a master PE can be configured through the DCR bus, the use of the DCR bus lessens bus traffic on the PLB. To ease SoC design using CoreConnect, IBM provides design toolkits which support PLB and OPB functional models, bus monitors, and a Bus Functional Language (BFL) [20] for the control of the bus functional models.

### 2.1.2 AMBA

The Advanced Microcontroller Bus Architecture (AMBA) [1] from ARM provides an on-chip communication standard for designing a high-performance SoC. AMBA has three levels of bus hierarchy: Advanced High-performance Bus (AHB), Advanced System Bus (ASB), and Advanced Peripheral Bus (APB). The AHB is a high-performance and high-speed bus connecting PEs, on-chip memories, and offchip external memory interfaces. The ASB is a general-purpose system bus and is an older version which has been superseded by AHB. The ASB also interconnects PEs and system peripherals. The APB is a peripheral interconnection bus and is optimized for minimal power consumption. The APB can be connected to either AHB or ASB through a bus bridge. Thus, any latencies due to low performance peripherals connected to APB are buffered by the bridge to the high-performance buses, AHB and ASB.

AMBA and CoreConnect share many common features. However, unlike the CoreConnect bus, AMBA does not support features such as architecture extendability up to 256-bits and deep address pipelining. Furthermore, as of this writing (June 2004), AMBA only supports a single master of a peripheral bus while CoreConnect supports multiple masters [1] [20].

### 2.1.3 CoreFrame

CoreFrame [11] [34] from Palmchip is a bus architecture with two independent bus types: PalmBus and Mbus. PalmBus is designed for connecting low-speed peripherals and for accessing from CPU cores to peripheral blocks, while Mbus is designed for high-speed accesses to a shared memory block from CPU cores and peripherals. A processing node including a single CPU core, which is referred to as a *CPU subsystem* in CoreFrame, may contain local memories for its own use on its native CPU bus, links to PalmBus through a PalmBus interface, and links to MBus through a bus bridge. Since the *CPU subsystem* has dedicated local memories, the CPU can access its local memories without interaction with the rest of the system. This reduces bandwidth constraints on the shared memory. Furthermore, the use of a specialized "cache block" helps to minimize CPU accesses to the shared memory. To ease an SoC design, Palmchip provides an interface generation tool, CoreFrame Connect Kit, which assists users with the configuration of the interface modules for PalmBus and Mbus.

#### 2.1.4 Wishbone

The Wishbone bus architecture [43] was developed by Silicore Corporation [42]. In August of 2002, Silicore placed the specification into the public domain via Open-Cores [33], which is a organization that promotes the development of open IP cores. Thus, Wishbone is not copyrighted and may be freely copied and distributed as long as all modifications to Wishbone are also provided free for copy and distribution (please see the GNU General Public License (GPL) terms [16] which OpenCores uses [13]).

The Wishbone bus architecture is very simple since it defines only one bus. In a system that needs both a high-speed processor bus and a low-speed peripheral bus, designers can use two Wishbones for buses, one operating at a high speed and one operating at a low speed. Thus, all cores are connected to the Wishbone buses by using the same bus interface. This way is simpler than using different buses for the high-speed bus versus the low-speed bus (e.g., PLB and OPB in the case of the CoreConnect). However, the Wishbone bus architecture supports various features in light of desired bus operations: multiple masters, single cycle read/write, block transfer cycles that systematically perform a set of single read cycles and/or a set of single write cycles, configurable address/data bus widths, and big versus little endian. Moreover, Wishbone supports various IP block interconnection methods: uni- and bidirectional buses, multiplexer based interconnects, tri-state based interconnections, off-chip I/O connections, and crossbar switches.

#### 2.1.5 SiliconBackplane $\mu$ Network

The SiliconBackplane  $\mu$ Network [45] from Sonics is an on-chip network that connects IP blocks in a system. The  $\mu$ Network isolates system IP from the network by requiring all system IP blocks to use a single bus interface protocol, the Open Core Protocol (OCP) (please see Section 2.2.1 for details). Thus, users can design and optimize the communication network knowing that all IP blocks which will utilize the communication network will do so using the same protocol (namely, OCP). Each IP block in a system communicates via a wrapper, which  $\mu$ Network calls an *agent*, using OCP, and the *agents* communicate with each other through  $\mu$ Network. Both OCP and the  $\mu$ Network protocol support modification of many system parameters in real time as system requirements change (e.g., arbitration scheme and address space), and the *agents* are generated by a tool called Fast Forward Development Environment provided by Sonics; therefore, designers can more easily implement an SoC that meets application requirements. The SiliconBackplane  $\mu$ Network offers fixed bandwidth by Time Division Multiplexed Access (TDMA)-based arbitration. This feature is particularly suitable for real-time applications. In addition, since the  $\mu$ Network provides fixed latency, when a data transfer is not completed in time, it is retried later, and thus wait states are not inserted in the bus pipeline. This feature can help maintain predictable network bandwidth.

#### 2.1.6 How We Differ

As compared to the buses presented in Section 2.1, our custom bus architectures (namely, GBAVI, GBAVIII, BFBA, HybridBA and SplitBA) generated based on our methodology using user options (please see the details in Sections 4 and 5) are more suitable for user specific applications. Therefore, we can obtain better performance when using one of our custom buses rather than aforementioned standard buses in an SoC. For example, in the context of a database example, SplitBA outperforms against a general global bus architecture by 41% reduction in execution time (see Section 7.3). The other performance evaluation results of the custom buses will also be shown in Section 7.3.

## 2.2 SoC Bus Interfaces

SoC design typically requires the mix and match of IP blocks on a single chip. Using a shared bus is one efficient way to connect the IP cores. However, because many types of buses are considered in high performance SoC designs, and because each bus type has different attributes, the introduction of a standard bus interface is useful so that each IP block can avoid having several interfaces to match to all available buses. Here, we describe two standard SoC bus interfaces as follows.

### 2.2.1 Open Core Protocol (OCP)

The Open Core Protocol (OCP) [44] developed by Sonics defines a bus interface for IP cores that connects the IP cores to on-chip buses. Communication requirements for an IP core can be described in this protocol format. The OCP interface is user-settable

so that designers can specify the interface's attributes (e.g., address and data bus widths). In OCP, there are four extensions beyond the Basic OCP version. The four extensions are Simple Extension, Complex Extension, Sideband Extension, and Debug and Test Interface Extension. Basic OCP includes only data flow signals, is based on a simple request and acknowledge protocol, and supports a unique data transfer on every clock cycle. However, the optional extensions support more functionality in control, verification, and test. In Simple Extension and Complex Extension, the protocols support burst transaction and pipelined writes; in addition, Sideband Extension also supports user-defined signals and synchronous resets. Moreover, Debug and Test Interface Extension supports Joint Test Action Group (JTAG) and clock control. Therefore, when OCP is integrated into an SoC, the protocol enables debugging and manufacturing test of IP blocks. OCP is available, potentially at no cost, under a license agreement that is agreed to over Sonics web site [32]. Products may use this standard without any royalty obligations.

### 2.2.2 Virtual Component Interface (VCI)

Like Sonics, the Virtual Socket Interface Alliance (VSIA) also supports the idea of a single bus interface for IP blocks and has a working group devoted to specifying such a protocol, the Virtual Component Interface (VCI) [8]. VCI defines a protocol for cycle-based and address mapped point-to-point communication. VCI is based on a handshake protocol in which each data transaction occurs on the rising edge of the clock when acknowledge and valid signals are high. Unlike OCP, VCI is a dataoriented protocol without the consideration of interrupt control and scan test signals. VCI is composed of three standards: Peripheral VCI (PVCI), Basic VCI (BVCI), and Advanced VCI (AVCI) protocol. PVCI is a subset of BVCI, which is also a subset of AVCI. PVCI and BVCI are for peripherals and for a simple processor system (e.g., a system supporting just a single read/write and DMA transfer), respectively. In contrast, AVCI is for a more complex system (e.g., a system with a pipelined structure or specialized structure for graphics).

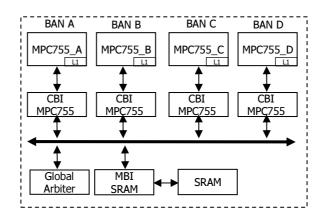

#### 2.2.3 How We Differ

While OCP and VCI provide a generic interface between an IP block and an on-chip bus, in our approach we use a specialized wrapper for each specific IP block, providing a customized interface that is well matched to the IP block. For example, our methodology supports Memory Bus Interface (MBI) for memory, CPU Bus Interface (CBI) for a PE and Arbiter Bus Interface (ABI) for an arbiter. Use of these wrappers in a system provides more suitable interfaces due to their custom architectures and leads to a competitive system performance as will be shown in Section 7.3.

### 2.3 Commercial Tools Related to Bus Generation

We now describe several state-of-the-art commercial tools for automated bus generation for SoC designs. Since a bus provides a communication channel among IP blocks in an SoC, the tools typically support several bus architectures to integrate IP blocks. Please note that all representations of commercial tools in this section are based upon publically available information at the time of publication of this thesis (June 2004).

#### 2.3.1 CoWare N2C

CoWare Napkin-to-Chip (N2C) [7] is a design environment for designing an SoC and a hardware platform at a system level. N2C provides a set of tools and methods for system-level design, hardware/software co-design, and IP block re-use. Co-Ware N2C uses C/C++/SystemC as a system-level description language and supports not only HDL design but also simulation capability. Automatic generation of glue logic and device drivers using an interface synthesis tool allows designers to integrate heterogeneous hardware/software functions into a system. In addition to such a hardware/software co-design capability, CoWare N2C provides a solution for the

decision of a bus architecture that is suitable for a user's application. A user may choose several options such as multi-layer, burst, or split transfer in two standard buses, AMBA or CoreConnect. With the CoWare N2C bus generator and simulator, the user can generate differently configured bus architectures and evaluate these generated buses with an application. Thus, users can explore a portion of the bus design space and choose a suitable bus architecture for their application.

### 2.3.2 Platform Express

Platform Express [25] from Mentor Graphics is a tool that uses IP blocks and on-chip buses, described in eXtensible Markup Language (XML), to automatically assemble heterogeneous components for an SoC design. Platform Express enables designers to quickly determine the suitability of platforms for system designs. To create a system, a designer just drags and drops library components (e.g., PEs, memories, and peripherals) in a graphical editor of a Graphic User Interface (GUI), and then the designer connects them to standard buses. After that, Platform Express automatically generates all the necessary connections among the components. Platform Express supports common on-chip standard buses such as AMBA from ARM and CoreConnect from IBM; these buses are used to link selected IP components. For design verification, Platform Express additionally invokes several verification tools (e.g., Seamless CVE, XRAY, and ModelSim from Mentor Graphics).

### 2.3.3 CoCentric System Studio

CoCentric System Studio from Synopsys provides a SystemC simulator and specification environment which enables users to verify and analyze hardware architectures and software algorithms at multiple levels of abstraction [47]. Since CoCentric System Studio supplies a unified design environment based on SystemC, users can seamlessly design a system from abstract algorithms to synthesizable SystemC. In a system architecture design, CoCentric System Studio works together with Synopsys DesignWare SystemC AMBA IP blocks. Therefore, users can quickly integrate system IP blocks with AMBA, which provides a shared communication channel. Up to recently, modeling an architecture required Register Transfer Level (RTL) hardware description that requires great effort and tedious work to design and verify the model. CoCentric System Studio, on the other hand, supports Transaction-Level Modeling (TLM) where a communication channel is modeled based on its behavior and is expressed in terms of transactions [46]. Therefore, in the design and verification phase, simulation speed can be much faster than the simulation of a traditional RTL-based model at the cost of modeling-accuracy loss. For example, in communication modeling, while an RTL model is fully pin-accurate, data accurate and cycle accurate, TLM waives such lowlevel details, instead controlling inter-module communication by use of an Interface Method Call (IMC) between modules [56]. A system verified at the transaction-level can be synthesized to logic gates by SystemC Compiler and Design Compiler from Synopsys.

### 2.3.4 Magillem

Magillem from Prosilog is a tool for importing IP blocks and graphically creating SoC architectures [36]. For the generation of an SoC, Magillem supports two standard on-chip buses (AMBA and CoreConnect) and standard bus interfaces (OCP and VCI). After a user loads required IP blocks in a graphic editor and connects them together graphically, the tool automatically generates transaction level (e.g., SystemC) or RTL (e.g., Verilog) code, enabling designers to explore the system architecture. To customize the required IP blocks, the user can specify each IP block's options (e.g., data width and arbitration scheme) through a GUI. Furthermore, Prosilog provides IP Creator, as a part of Magillem, for integration and re-use of non-VCI or non-OCP compatible IP blocks by wrapping them in a structure compatible with OCP or VCI. Thus, designers can assemble the IP blocks in an SoC that uses either the VCI or the OCP interface.

### 2.3.5 How We Differ

Unlike the commercial tools discussed above in Section 2.3, our bus synthesis tool, BUSSYNTH (please see the details in Section 5) can generate SoC bus systems with standard bus architectures (such as CoWare N2C and Platform Express) as well as custom bus architectures; furthermore, based on user options, BUSSYNTH generates a single bus architecture as well as multiple and hybrid bus architectures. For example, BUSSYNTH generates GBAVI, GBAVIII, BFBA, HybridBA and SplitBA, which will be described in Sections 4.1 and 5.1. Moreover, BUSSYNTH enables interconnect delay aware bus architecture generation that will be explained in Section 6.3. (However, please note that while we did not actually implement a large array of standard bus structures in BUSSYNTH – please see Sections 4 and 5 for details about what we did implement – nevertheless any of the standard bus structures discussed so far can be integrated into BUSSYNTH in a straightforward fashion.)

# 2.4 Additional Prior Work Related to Bus Generation

As additional research related to bus generation for SoC design, many papers present communication topology generation, IP block assembly for an SoC, and componentbased SoC design as follows.

Gasteier *et al.* [12] describe the automatic generation of a communication topology by using scheduling of data transfer operations to reduce the cost (e.g., area) of a bus architecture. However, their algorithm only supports a single type of bus topology (a single global bus topology). Our method, on the other hand, supports multiple bus types and bus topologies. Bergamaschi *et al.* [3] present design automation of an SoC using IP blocks connected via CoreConnect. In their methodology for assembling IP cores, their algorithm checks the compatibility of IP I/O ports and generates wires to connect the IP blocks. Again, we, on the other hand, support a wider variety of bus types and architectures than they present.

Pai Chou *et al.* [6] show an IP based approach to SoC building. An input description to their algorithm designates a bus topology that specifies how IP blocks are connected with each other and which bus protocol is used. Communication synthesis in their tool implements the bus topology together with the generation of device drivers, message routers and communication devices, so that the IP blocks communicate with each other by using a particular network protocol (e.g.,  $I^2C$  or CAN) chosen. Our methodology, on the other hand, assumes that high-performance direct on-chip bus connections are desired rather than using a complicated network protocol such as  $I^2C$  or CAN. Thus, our methodology targets SoC designs where direct, nonpacket based connections are desired. For this reason, our methodology focuses on generating hardware blocks of dedicated bus logic for application specific communication including handshake registers and bus arbiters for a customized bus architecture. This contrasts with the work of Pai Chou *et al.*, which did not generate customized SoC bus architectures but rather assumed that such bus architectures are already available (e.g., a CAN bus).

Several efforts [4] [5] [14] [15] [23] [30] [57] from TIMA laboratory present a component-based design flow for a heterogeneous multi-core SoC. Their design flow introduces a systematic method of wrapper generation for multi-core SoC design based on architectural parameters extracted from a high-level system specification. Lyon-nard *et al.* [23] introduce a design flow for the generation of an application-specific multi-processor architecture. They used a generic multi-processor architecture template to support two types of buses (e.g., a point-to-point connection and a shared

bus) and a communication coprocessor for the interface between a PE and a bus. To interface each heterogeneous component to other parts of the target system, they depict a generic wrapper architecture that adapts to different communication protocols based on automatic wrapper generation [14] [15] [57]. Cesário *et al.* [4] [5] and Nicolescu *et al.* [30] described a component-based design environment to enable an automatic wrapper generation tool to support various hardware interfaces, device drivers and Application Program Interfaces (APIs).

Shin *et al.* [41] show how an efficient configuration of a parameterized on-chip system bus could be found using a software tool they developed. They, however, do not discuss the generation of various bus communication topologies based on user requests; nor do they discuss any associated bus architecture generation.

Thepayasuwan *et al.* [52] describe layout conscious bus architecture synthesis. They use interconnect delay from a system layout to generate a single bus architecture operating at the maximum achievable bus speed considering worst-case interconnect delay. We, on the other hand, consider ways to alter the bus architecture – e.g., by splitting the bus into several separate buses connected by bus bridges – and, together with worst-case interconnect delay information, generate both a custom bus architecture as well as custom bus control logic able to handle, for example, multiple delays to different processors closer or further away in terms on interconnect delay. The details of how we do this are described in Section 6.3. In short, our methodology provides a more customized bus architecture that is suitable for a specific user's set of applications since the methodology generates the bus architecture based on various user-input options.

### 2.5 Summary

In this chapter, we first looked into several popular industry bus architectures (namely, CoreConnect, AMBA, CoreFrame, Wishbone, and SiliconBackplane  $\mu$ Network). Then,

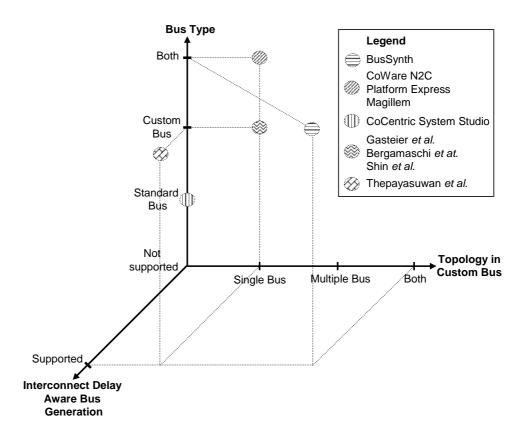

Figure 1: A Comparison of Bus Generation Tools

we discussed two bus interface protocols (namely, OCP and VCI) that allow custom IP blocks to match to the selected buses by providing a standardized protocol. Next, we described four commercial tools (namely, CoWare N2C, Platform Express, Co-Centric System Studio, and Magillem) that enable bus architecture generation for an SoC design. Finally, we introduced additional prior work related to bus generation in academia and industrial research labs. In each of the previous sections (2.1, 2.2, 2.3 and 2.4), we described key differences with the research of this thesis. Figure 1 shows a summary of the key differences. As shown in Figure 1, BUSSYNTH generates custom bus systems with a single bus topology as well as multiple bus topologies; furthermore, BUSSYNTH supports interconnect delay aware bus generation. In the next section, we will describe our methodology to generate a customized bus architecture for a multi-processor SoC.

# CHAPTER III

## BUS SYSTEM STRUCTURE

In this chapter we will begin by defining some of terms that will be used throughout this dissertation. Then, we will describe our bus system structure to be used in our bus system generation.

## 3.1 Terminology for Bus System Generation

Before proceeding to discuss our Bus Synthesis tool (BUSSYNTH), we first explain some of the terms we will be using to describe the different components of a bus architecture. Example 3.1 explains some of the terminology we have defined.

- (a) Processing Element (PE): a hardware unit that performs algorithmic processing

usually a CPU, but it may also be dedicated or reconfigurable logic.

- (b) Bus Bridge (BB): a hardware unit that is an on-off controllable connection point between two buses – if the BB is enabled, the two buses are fully connected; otherwise, the two buses are disconnected. Note that our BB does not currently support different bus speeds (i.e., different bus clock frequencies) in buses connected by the BB (see Section 5.1.1 for details).

- (c) Global Bus Architecture (GBA): a type of bus architecture having a bus through which all PEs can access shared resource(s), where BBs may be used to connect different sections of the bus.

- (d) Bi-FIFO Bus Architecture (BFBA): a type of bus architecture where bidirectional FIFOs are used to transmit and receive data between adjacent PEs.

- (e) Segment of Bus (SB): a contiguous bus (no BBs) consisting of address, data and control (e.g., read enable, write enable, request and acknowledge) wires specific to a particular bus type (in our case, BFBA).

- (f) Bus Access Node (BAN): an integrated hardware block that is composed of at most one PE, custom hardware blocks and/or memory hardware together with associated bus access hardware and SB(s).

- (g) Local Bus (LB): a contiguous bus (no BBs) internal to a particular BAN that connects bus interface hardware unit(s) (in our case, CBI and/or MBI) attached to a PE, a memory or a hardware unit (in our case, non-CPU block), where the bus is composed of address, data and control wires.

- (h) Module: a hardware unit such as PE, BB, SB, an arbiter, SRAM or interface logic blocks, where the specific interface logic blocks will be explained in more detail in Section 3.2. Note that it is possible to extend the definition of module to include newly designed hardware units that carry out specific functions. For this dissertation, however, the definition given for module suffices.

- (i) Bus Subsystem: one or more BANs connected together using the same bus or a combination of different bus architectures without a bus bridge (in our case, either GBA, BFBA or the combination of GBA and BFBA).

- (j) Bus System: a system that consists of one or more Bus Subsystems connected together by using one or more bus bridges.

### Example 3.1 Terminology

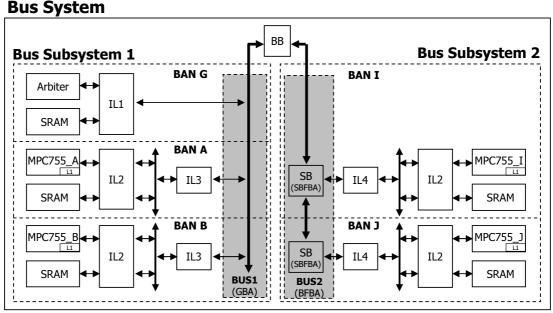

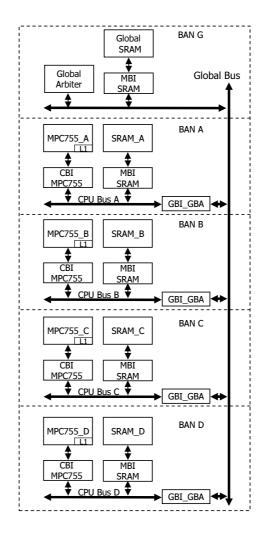

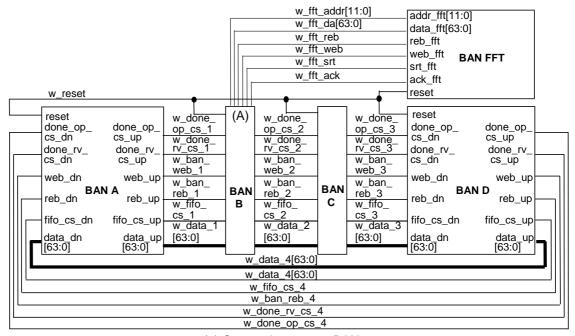

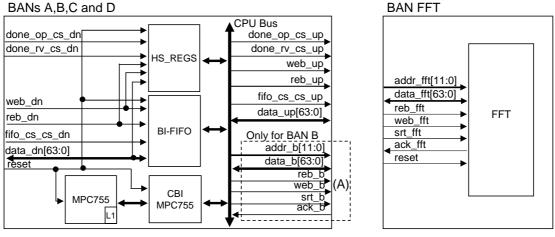

Figure 2 shows an SoC consisting of four PEs, Motorola PowerPC (MPC) 755s [28], each with an L1 cache. Each MPC755 is an example of a PE. In the bottom right of Figure 2, the SB of BAN J is a segment of bus for Bi-FIFO Bus Architecture (BFBA). The SB is

BAN: Bus Access Node, IL: Interface Logic, BB: Bus Bridge, SBFBA: an example of SB for BFBA

Figure 2: Example of a Bus System

used to connect BAN J to BAN I. The SB of BAN I is also another segment of bus for Bi-FIFO Bus Architecture (BFBA). Both SBs make a bus type, BFBA, by being connected each other. Note the use of Interface Logic blocks (IL2 and IL4) to connect MPC755\_J to the SB. The bottom right of Figure 2 also shows MPC755\_J connected to local SRAM and an SB to form Bus Access Node J (BAN J). In BANs A and B of Figure 2, LBs connecting ILs are shown between IL2 and IL3 of each BAN; similarly, in BANs I and J, LBs are shown between IL2 and IL4 of each of BAN. In BAN J, each block such as SRAM, IL2, IL4 or SB is a module. BAN J is adjacent to BAN I, and the BANs I and J together form a Bus Subsystem using bus type BFBA for communication. On the left-hand side of Figure 2, BANs A, B and G form another Bus Subsystem in which GBA is used for communication. A BB connects the two Bus Subsystems as shown in the top middle of Figure 2. On the whole, Figure 2 shows an example of a Bus System composed of two Bus Subsystems.  $\Box$

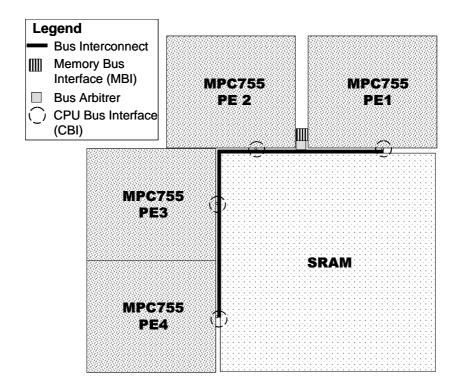

## 3.2 Bus System Structure

In this section, we show a hierarchical structure in each Bus System to be generated. Figure 2 shows an example of a hierarchically structured multi-processor Bus System that has two Bus Subsystems with two and three BANs, respectively. A Bus System is composed of one or more Bus Subsystems, and each Bus Subsystem includes one or more BANs, each of which is composed of PEs, hardware modules and/or memories together with associated control logic. Here, the Bus Subsystems are connected through bus bridges. This kind of hierarchical definition allows a Bus System to have a flexible and scalable bus architecture in a multi-processor SoC Bus System design.

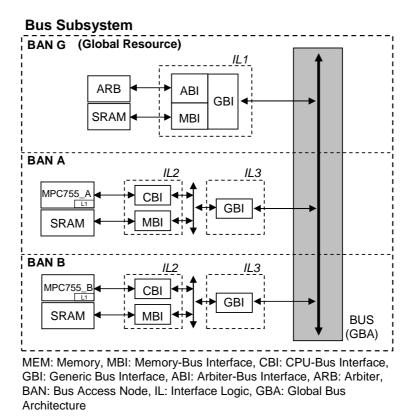

Figure 3 depicts a more detailed version of the Bus Subsystem shown on the left-hand side of Figure 2. In addition to PEs (e.g., MPC755) and memories (e.g., SRAM) in the BANs of Figure 3, additional modules are specified as Interface Logic

(IL): CPU (or PE) to Bus Interface (CBI), Memory to Bus Interface (MBI), Generic Bus Interface (GBI) and Arbiter to Bus Interface (ABI).

With these ILs, each BAN can have different types of PEs, hardware modules and/or memories because the ILs enable the heterogeneous modules to adapt to one another. For example, BAN A can have MPC755 and SRAM while BAN B can have ARM9TDMI and DRAM. Similarly, GBI also provides flexibility in selecting various types of buses for a Bus Subsystem (e.g., GBAVIII and BFBA). Each BAN can access any other BAN's memory through a bus integrated with several SBs. Based on the Bus System structure, by simply repeating generated BANs, a Bus Subsystem can be a scalable structure, and a multi-processor Bus System can be implemented in an easy manner.

Figure 4: Block Diagrams of Interface Logic Blocks

Figure 4(a) shows the CBI block that adapts between a CPU (or PE) and a bus and that is composed of an address decoder, bi-directional data buffer, a block for regeneration of control signals (e.g., AACK\_BAR and TA\_BAR in PowerPC) and a block for generation of read/write enable signals. In Figure 4(a), for the CBI for MPC755, gate counts to implement each block are as follows: 128 NAND2 gate equivalents for the address decoder, 133 NAND2 gate equivalents for the bi-directional data buffer, 1027 NAND2 gate equivalents for the block for regeneration of control signals and 29 NAND2 gate equivalents for the block for generation of read/write enable signals (please note that we use TSMC  $0.25\mu$ m technology to estimate the gate counts by using Synopsys Design Compiler [49]). The MBI block shown in Figure 4(b) adapts between a memory and a bus and is composed of a memory address generator, a bi-directional data buffer and buffers for read/write enable signals. For the MBI for SRAM shown in Figure 4(b), gate counts to implement each block are as follows: 21 NAND2 gate equivalents for the memory address generator and 133 NAND2 gate equivalents for the bi-directional data buffer. The GBI block shown in Figure 4(c) is composed of address bus buffer, a bi-direction data buffer and a block for regeneration of control signals (e.g., bus request and bus busy signals). Gate counts to implement the GBI for a global bus shown in Figure 4(c) are 133 NAND2 gate equivalents for the bi-direction data buffer and 46 NAND2 gate equivalents for the block for regeneration of control signals. Finally, the ABI block interface between an arbiter and a bus is shown in Figure 4(d), where the block regenerates arbiter control signals (e.g., arbiter request and arbiter acknowledge signals). In Figure 4(d), the ABI for a First-Come-First-Serve (FCFS) arbiter is implemented with 10 NAND2 gate equivalents.

Our current tool supports only two types of GBIs (namely, GBI\_GBA and GBI\_BFBA); however, more GBI types could easily be added to our tool after being defined. In the tool, the GBI\_GBA can be used in a Bus System that use a Global Bus Architecture (GBA) to connect BANs in each Bus Subsystem while the GBI\_BFBA can be used in a Bus System with Bi-FIFO blocks to connect BANs in each Bus Subsystem. Thus, they have different functions to adapt to either a GBA or a Bi-FIFO bus architecture. Our tool currently supports two SB types: SB\_GBA and SB\_BFBA. However, more SB types could be added to the tool after being defined. SB\_GBA is used to form a GBA that connects BANs in each Bus Subsystem while SB\_BFBA is for a Bi-FIFO architecture connecting BANs in each Bus Subsystem.

When a Bus Subsystem has a global resource such as a large global memory to be accessed from all BANs, the resource is also defined as a BAN: for example, BAN G in Figure 3. On the other hand, the Bus System structure shown Figure 2 and the Bus Subsystem structure shown in Figure 3 allows a user to adapt a standard commercial bus architecture (e.g., AMBA). As shown in Figure 3, ILs adapt hardware units (e.g., arbiter, SRAM and MPC755) to specific buses (e.g., GBA). Thus, if our Module Library that will be described in Section 6.1 provides the wrappers (i.e., ILs) for the various possible buses (e.g., a global bus or an AMBA bus), our approach enables the user to choose a custom bus topology as a Bus System. In support of the choices of a user, BUSSYNTH will generate custom Verilog HDL at the Register-Transfer Level (RTL) as will be described in Chapter 5.

## 3.3 Summary

In this chapter, we have defined some of the terms that we will use to describe Bus Systems throughout this dissertation. We have explained a basic Bus System structure used to generate Bus Systems with our tool BUSSYNTH. In the next chapter (Chapter 4), based on a user-specified bus structure, we will show how to specify a wide variety of Bus Subsystems and our method to communicate among PEs in the specified Bus Subsystems. In the chapter after next (i.e., in Chapter 5), we will show how to specify Bus Systems (as opposed to just Bus Subsystems) using our methodology.

## CHAPTER IV

## BUS SUBSYSTEM SPECIFICATION

In this chapter, we show Bus Subsystem specification based on user input, where the specified Bus Subsystems can have various bus architectures. We target the ability to generate a wide variety of Bus Subsystems by using our bus synthesis tool, BUSSYNTH. Then, we show how to communicate among PEs in the generated Bus Subsystems.

# 4.1 How to Specify Bus Subsystems

Before we describe in a later chapter (Chapter 6) our detailed methodology for Bus Subsystem generation, this chapter shows how to specify various Bus Subsystems, based on user options that are user inputs to BUSSYNTH.

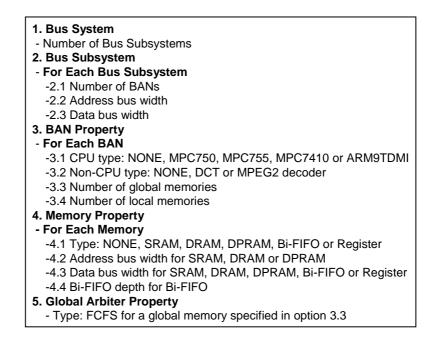

Several categories in user options are as follows:

- (1) Bus System Property: number of Bus Subsystems in a Bus System.

- (2) Bus Subsystem Property: number of BANs, address bus width and data bus width. Note that any Local Bus on a particular BAN is assumed to have the same address and data widths as the non-Local Bus(es) in the Bus Subsystem. Obviously, all buses in a Bus Subsystem have the same address and data widths.

- (3) BAN Property: CPU type, Non-CPU type, number of global memories and number of local memories for each BAN, where the CPU type is one of NONE, MPC750, MPC755, MPC7410 or ARM9TDMI, and the Non-CPU type is one of NONE, DCT or MPEG2 decoder. Note that this can be easily extended to include new CPUs or additional predesigned reusable components (Non-CPUs).

Figure 5: User Options to Configure a Custom Bus Subsystem

- (4) Memory Property: memory type, address bus width, data bus width and Bi-FIFO depth, where the memory type is one of NONE, SRAM, DRAM, DPRAM, Bi-FIFO or Register, the address bus width is an option for SRAM, DRAM or DPRAM, and the Bi-FIFO depth is an option for Bi-FIFO. Note that this can easily be extended to include additional memory types.

- (5) Global Arbiter Property: arbiter type. Currently, the type is only First-Come-First-Serve (FCFS); however, the type can easily be extended to include additional arbiter type (e.g., priority based arbiter). This property is selected only when a global memory is specified in the BAN property.

Figure 5 shows a summary of the user options (1) through (5) described above. The input sequence of the user options is as follows. First, the user enters the number of Bus Subsystems for a Bus System. Next, the user specifies the number of BANs, address bus width and data bus width for each Bus Subsystem (please note that a BAN has only one non-Local Bus that connects the BAN to the rest of the Bus Subsystem). Then, for each BAN specified in Bus Subsystem Property 2.1, the user inputs CPU type, Non-CPU type, number of global memories and number of local memories in the BAN Property option if the user wants to have these resources in a BAN. Finally, in the BAN Property option, the user inputs Memory Property (namely, memory type, address bus width, data bus width and Bi-FIFO depth) for each selected memory if any memory is required in a BAN. How to use these options to generate various Bus Subsystems is shown in Examples 4.1, 4.2 and 4.3.

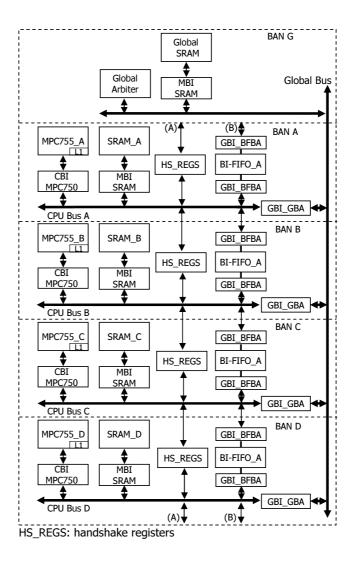

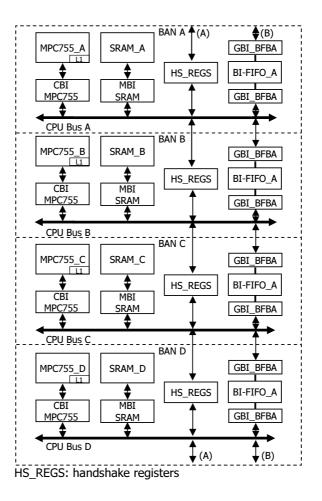

All Bus Subsystem examples shown in Figures 6, 7 and 8 have four PEs and a total of 256KB (64KB per PE) of L1 cache memory. Non-L1 cache memory size is 40MB for the examples shown in Figure 7 and 8 and 32MB for the example shown in Figure 6. The reason that Figure 6 has only 32MB is that Figure 6 does not have any global memory; in a Bi-FIFO based system, we found that a global memory tends to not increase performance at all in the applications we considered (see Chapter 7). Please note that, as defined in Chapter 3, a single Bus Subsystem can also be a Bus System, if the Bus Subsystem is not connected via bus bridge(s) to any other Bus Subsystem(s). While BUSSYNTH can generate a Bus Subsystem having any number of PEs according to the user options, the examples presented in detail in this section all have the same number of PEs in order to provide a basis for fair comparisons later in Section 7.3 (please note that the examples shown in Figure 7 and Figure 8 have 40MB total of non-L1 cache memory; nevertheless, the bus examples of Figures 7 and 8 do not result in the best performance as shown in Table 10 of Chapter 7 Experiments and Results). In all examples in this thesis, we use the Motorola PowerPC (MPC755) for the PE core, which, however, can be changed to any other core simply by adding a CBI module for the new PE core (e.g., ARM9TDMI) to be operated in the Bus System.

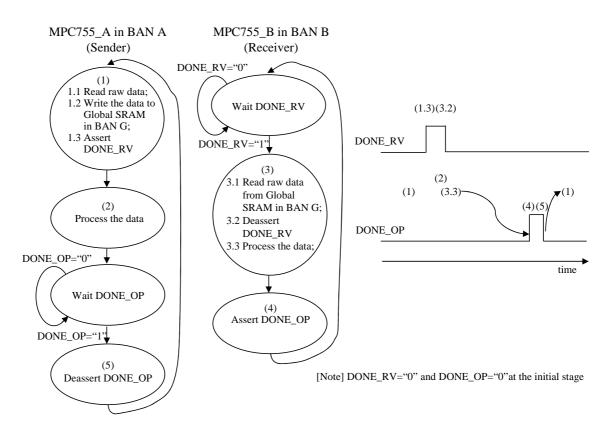

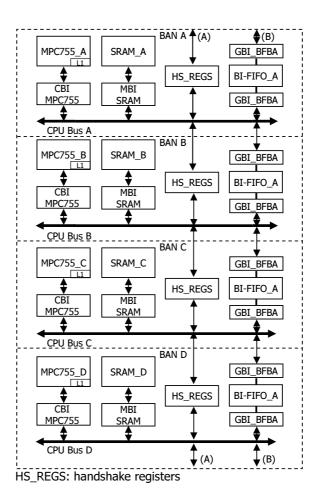

### Example 4.1 User Options to Generate BFBA

A user input sequence which specifies a Bus Subsystem we call the Bi-directional Firstin-first-out Bus Architecture (BFBA) is as follows. The user first specifies the number of Bus Subsystems by entering a "1" in Bus System Property (user option 1 in Figure 5). Then, the user inputs "4" for the number of BANs (user option 2.1), "32" for address bus width (user option 2.2) and "64" for data bus width (user option 2.3) in the Bus Subsystem property. Please note that the address and data bus widths in Figure 6 are all the exact same for all Local Buses (e.g., CPU Bus A) as well as buses to Bi-FIFOs; we could, if desired, easily update our current tool to specify particular widths for each Local Bus in each BAN separately. Next, the user inputs the fields of BAN Property for each BAN : "MPC755" for

Figure 6: Diagram of BFBA

the CPU Type (user option 3.1), "NONE" for the Non-CPU Type (user option 3.2), "0" for the number of global memories (user option 3.3) and "3" for the number of local memories (user option 3.4). Finally, the user inputs the Memory Property for three local memories chosen for each BAN. For the first local memory, the options are as follows: "SRAM" for the memory type (user option 4.1), "20" for the address bus width (user option 4.2) and "64" for the data bus width (user option 4.3) for 8MB SRAM in each BAN. For the second local memory, the user inputs "Bi-FIFO" for the memory type (user option 4.1), "64" for the data bus width (user option 4.3), "1024" for the Bi-FIFO depth (user option 4.4). After that, the user enters the third local memory property: "Register" for the memory type (user option 4.1) and "32" for the data bus width (user option 4.3). With these options, the generated Bus Subsystem BFBA is shown in Figure 6 where there are four equivalent BANs, each of which has an MPC755, an 8MB SRAM, a single 32-bit register, a 1024-entry Bi-FIFO and GBLBFBAs as a Generic Bus Interfaces (GBI) for the Bi-FIFO block. In this example, since a Bi-FIFO is specified in each BAN, our tool automatically extracts GBI\_BFBA from a library (namely, Module Library that will be described in Chapter 6 in detail) for the Bi-FIFO block connecting BANs. Here, we assume that any Bi-FIFOs specified by the user are intended to provide a path between BANs.  $\Box$

As shown in Figure 6, Bi-directional First-in-first-out Bus Architecture (BFBA) has a Bi-FIFO between adjacent BANs. This design is similar to some commercially available multi-processor Printed Circuit Boards (PCBs) such as the Quad TMS320C6701 Processor VME Board from Pentek [35]. One BAN can push data into a Bi-FIFO while an adjacent BAN can read the data from the Bi-FIFO. In this way, the PEs can carry on successive functions for a pipelined operation. A specific way to communicate over the PEs in Figure 6 will be presented in Section 4.2. Note that BFBA works well in a pipelined style of operation.

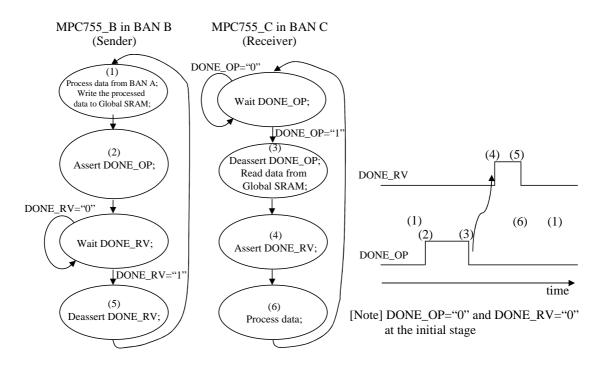

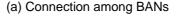

#### **Example 4.2** User Options to Generate GBAVIII

User inputs to generate a Bus Subsystem we call Global Bus Architecture Version III

Figure 7: Diagram of GBAVIII

(GBAVIII) are as follows. The user first specifies the number of Bus Subsystems by entering a "1" in Bus System Property (user option 1 in Figure 5). Then, the user inputs "5" for the number of BANs (user option 2.1), "32" for address bus width (user option 2.2) and "64" for data bus width (user option 2.3) in the Bus Subsystem property. Next, the user inputs the fields of BAN Property for four BANs (the bottom four BANs in Figure 7): "MPC755" for the CPU Type (user option 3.1), "NONE" for the Non-CPU Type (user option 3.2), "0" for the number of global memories (user option 3.3) and "1" for the number of local memories (user option 3.4). Next, the Memory Property is input for a memory in each of the four BANs (the bottom for BANs in Figure 7): "SRAM" for the memory type (user option 4.1), "20" for the address bus width (user option 4.2) and "64" for the data bus width (user option 4.3) for resulting in an 8MB memory size in each BAN. With these options, the bottom four BANs shown in Figure 7 are generated: each BAN has an MPC755 and an 8MB SRAM each with associated interface logic blocks CBL\_MPC755, MBL\_SRAM and GBL\_GBA for the interface to the global bus. Please note that in our current tool, specified bus address and data widths (in user options 2.2 and 2.3) for a Bus Subsystem (e.g., GBAVIII, HybridBA or each Bus Subsystem in SplitBA shown in Figures 7, 8 and 18) are assumed to apply to all Local Buses as well as non-Local Buses. In this specific example, since no Bi-FIFOs are specified, the tool automatically extracts GBL\_GBA from a library (namely, Module Library that will be described in Chapter 6 in detail) for the bus between BANs; however, as we explained in Example 4.1, the tool extracts GBL\_BFBA from the library as a GBI for BFBA when a Bi-FIFO is specified; we assume that any Bi-FIFOs specified by the user are intended to provide a path between BANs.

Then, continuing with the generation of Figure 7, the user inputs the fields of BAN Property for one additional BAN (the top BAN in Figure 7) as a global memory block: "NONE" for the CPU Type (user option 3.1), "NONE" for the Non-CPU Type (user option 3.2), "1" for the number of global memories (user option 3.3) and "0" for the number of local memories (user option 3.4). Finally, the Memory Property is input for the global memory in the remaining BAN: "SRAM" for the memory type (user option 4.1), "20" for the address bus width (user option 4.2) and "64" for the data bus width (user option 4.3) for resulting in an 8MB memory size in the BAN. With these options, the top BAN in Figure 7, BAN G, is generated: an 8MB SRAM with a Global Arbiter. Please note that any BAN specified to contain *only* memory automatically infers a First-Come First-Serve (FCFS) arbiter for the number of masters (in Figure 7 there are four masters) specified in the Bus Subsystem.  $\Box$

GBAVIII shown in Figure 7 is a Global Bus Architecture (GBA) with a global arbiter and a global memory (please note that in BUSSYNTH, the FCFS Global Arbiter is generated when a user wants to have a global memory). When any BAN tries to access the global memory through the global bus in Figure 7, the global arbiter resolves the case of multiple memory requests from the BANs. Currently, the only choice is an arbiter using a FIFO to implement a First-Come-First-Serve (FCFS) scheduling scheme; however, an arbiter having a different policy such as a priority-based protocol could easily be added to BUSSYNTH (and, correspondingly, to the user options of Figure 5, e.g., as option 6). The Global SRAM in Figure 7 can also be replaced with another memory type (see option 4.1 in Figure 5) by using its corresponding MBI, which adapts the interface between the memory and the bus. The local memory in each BAN can be used for relatively faster memory access than the global memory due to arbitration time. How to communicate among BANs in Figure 7 will be shown in Section 4.2.

Please note that Global Bus Architecture Version I (GBAVI) is a Bus System with bus bridges and so will be presented in the next chapter. Also, please note that Global Bus Architecture Version II (GBAVII) was presented in [38] but was not chosen for automated generation in this dissertation because its bus architecture is almost the same (in both structure and achievable performance) as GBAVIII; in addition, GBAVII shows only a tiny (<1%) performance improvement over GBAVI to be presented in Section 5.1.1. However, if desired, the GBAVII bus could easily be added to our tool.

According to the user options shown in Figure 5, the user can customize any Bus Subsystem in our bus synthesis tool BUSSYNTH. As one of the customized Bus Subsystems, the user might want to generate a bus mixing together both Bi-FIFObased and GBA-based communication. Example 4.3 describes how to generate such a customized Bus Subsystem by the user options.

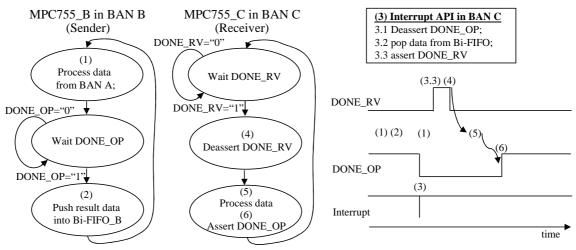

### Example 4.3 User Options to Generate HybridBA

Suppose a user wants to generate a specialized bus using several of the custom buses explained earlier: specifically, a bus combining both the Bi-FIFO blocks from BFBA and the

Figure 8: Diagram of HybridBA

global bus from GBAVIII. We call the Bus Subsystem having this combined bus type as Hybrid Bus Architecture (HybridBA). To generate such a combined bus, the user needs to input the user options shown in Figure 5 as follows.

First, the user enters "1" for the number of Bus Subsystems (user option 1 in Figure 5). Then, in the Bus Subsystem property, the user inputs "5" for the number of BANs (user option 2.1), "32" for address bus width (user option 2.2) and "64" for data bus width (user option 2.3). Next, the user inputs the fields of BAN Property for four BANs (the bottom four BANs in Figure 8): "MPC755" for the CPU Type (user option 3.1), "NONE" for the Non-CPU Type (user option 3.2), "0" for the number of global memories (user option 3.3)

and "3" for the number of local memories (user option 3.4). Next, the user inputs the Memory Property for the three local memories chosen to be in each of four BANs (BANs A through D). For the first local memory, the options are as follows: "SRAM" for the memory type (user option 4.1), "20" for the address bus width (user option 4.2) and "64" for the data bus width (user option 4.3) resulting in an 8MB SRAM. For the second local memory, the user inputs "Bi-FIFO" for the memory type (user option 4.1), "64" for the data bus width (user option 4.3), "1024" for the Bi-FIFO depth (user option 4.4). After that, the user enters the Memory Property for the third local memory: "Register" for the memory type (user option 4.1) and "32" for the data bus width (user option 4.3). With these options, each of the bottom four BANs in Figure 8 has MPC755 and three local memories, namely, 8MB SRAM, 1024-depth Bi-FIFO block and 32-bit handshake registers HS\_REGS.

Then, the user inputs the fields of BAN Property for a remaining BAN (the top BAN in Figure 8) as a global memory block: "NONE" for the CPU Type (user option 3.1), "NONE" for the Non-CPU Type (user option 3.2), "1" for the number of global memories (user option 3.3) and "0" for the number of local memories (user option 3.4). Finally, the user inputs the Memory Property for the global memory in the remaining BAN as follows: "SRAM" for the memory type (user option 4.1), "20" for the address bus width (user option 4.2) and "64" for the data bus width (user option 4.3) resulting in an 8MB memory size in BAN G.

With these options, the generated Bus Subsystem HybridBA is shown in Figure 8, where each BAN has an 8MB SRAM, and a global arbiter in BAN G arbitrates global memory requests from the bottom four BANs and is generated since the user wants to have a global memory in BAN G. Handshake register blocks HS\_REGSs in the bottom four BANs are for communication among MPC755s, and Bi-FIFOs in the bottom four BANs provide a fast data path between neighboring BANs. □

The Bus Subsystem we call HybridBA shown in Figure 8 is a combination of BFBA and GBAVIII. This combination allows the bus architecture to exploit the advantages of both BFBA and GBAVIII (i) by supplying a Bi-FIFO data transfer method between adjacent BANs and (ii) by having a global memory area that can be accessed from all BANs. This combination of features gives flexibility in communication and thus results in a higher performance, although a penalty is paid in increased chip area (see Table 14 in Section 7.3 for details).

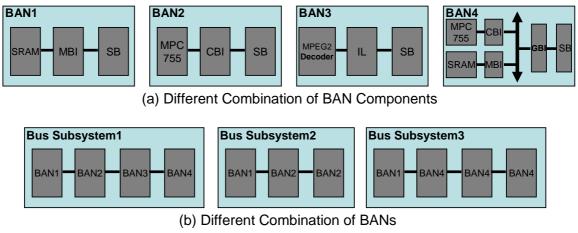

Different combination of bus components by the user options shown in Figure 5 is one way to make another Bus Subsystem as shown on the next page in Figure 9: (a) different combination of BAN components and (b) different combination of BANs. The detailed user options are introduced in Example 4.4.

### Example 4.4 User Options for Different Combination of Bus Components